Cypress W194-70 Datasheet

Frequency Multiplier and Zero Delay Buffer

W194

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

January 5, 2000, rev. *A

Features

• T wo outputs

• Configuration opti ons allow v arious mul tipl ications of

the reference frequency—refer to

Table 1

to determi ne

the specific option which meets your mul ti plication

needs

• Available in 8-pin SOIC package

Key Specific ati o n s

Operating Voltage: .............................. 3.3V±5% or 5.0±10%

Operating Range: .......................10 MHz < f

OUT1

< 133 MHz

Absolute Jitter: .........................................................±500 ps

Output to Output Skew: ...................................... ........250 ps

Propagation Delay: .................. ...................... ...........±350 ps

Propagation delay is affected by input rise time.

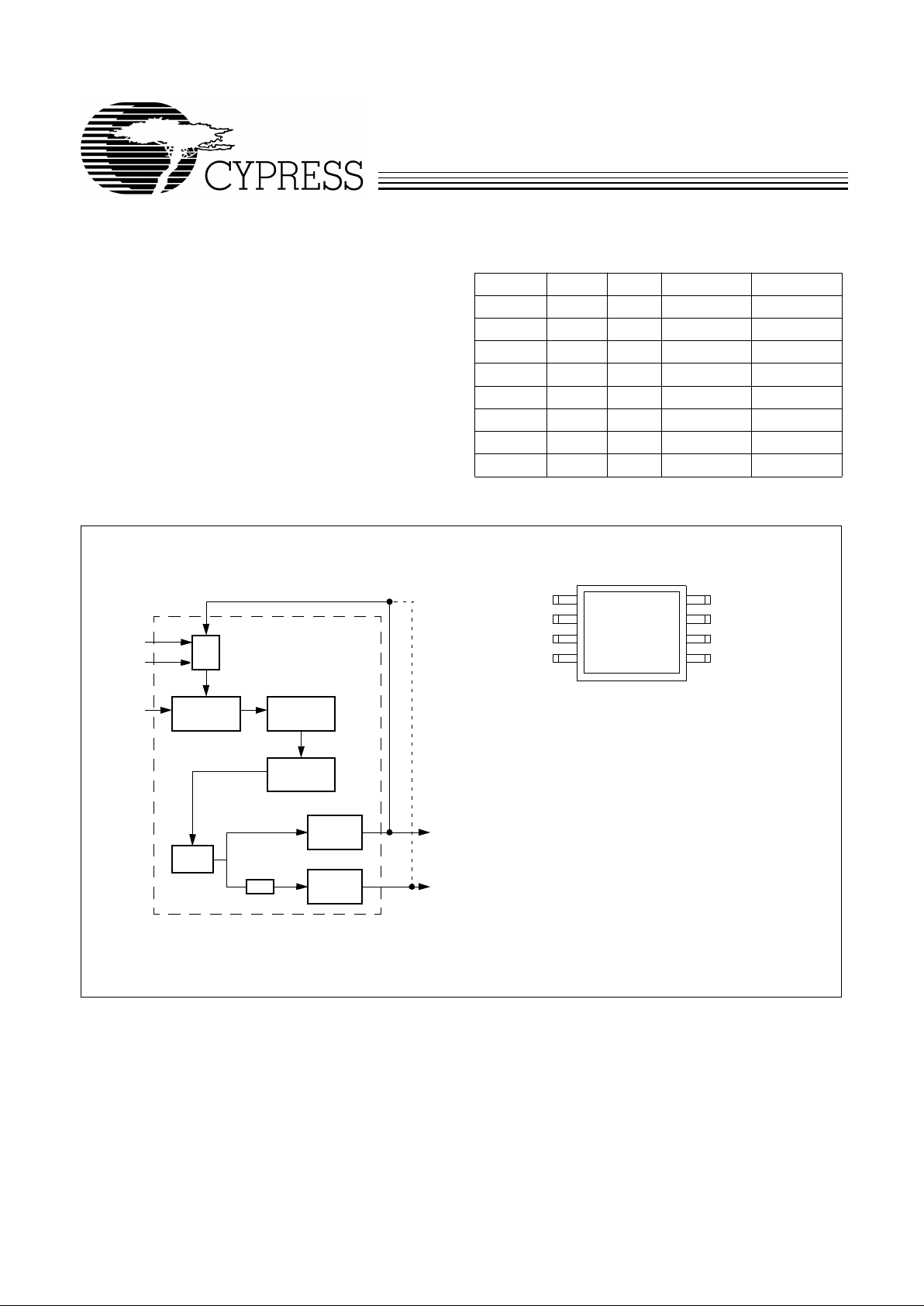

T able 1. Configuration Options

FBIN FS0 FS1 OUT1 OUT2

OUT1 0 0 2 X REF REF

OUT1 1 0 4 X REF 2 X REF

OUT1 0 1 REF REF/2

OUT1 1 1 8 X REF 4 X REF

OUT2 0 0 4 X REF 2 X REF

OUT2 1 0 8 X REF 4 X REF

OUT2 0 1 2 X REF REF

OUT2 1 1 16 X REF 8 X REF

Block Diagram

Pin Configuration

÷Q

FS0

FS1

Reference

FBIN

Phase

Detector

Charge

Pump

Loop

Filter

VCO

÷2

Output

Buffer

OUT1

OUT2

Output

Buffer

External feedback connection to

OUT1 or OUT2, not both

Input

IN

OUT2

VDD

OUT1

FS1

8

7

6

5

FBIN

IN

GND

FS0

1

2

3

4

SOIC

W194

2

Overview

The W194-70 is a two-output zero del ay buff er and frequency

multiplier. It pro vides an e xternal f eedbac k pat h allo wing maximum flexibility when implementing the Zero Delay feature.

This is explained further in the secti ons of t his d ata she et title d

“How to Implement Zero Delay,” and “Inser ting Other Devices

in Feedback Path.”

The W194-70 is a pin-compatible upgrade of the Cypress

W42C70-01. The W194-70 addresses some application dependent probl ems experienced by users of the older device.

Pin Definitions

Pin Name Pin No.

Pin

Ty pe Pin Description

IN 2 I

Reference Input:

The output signals wil l be synchronize d to this signal.

FBIN 1 I

Feedback Input :

This input must be f ed b y one of th e outputs ( OUT1 or OUT2) to ensure

proper funct ionality. If the tr ace between FBIN and t he output pin being used for feedb ack

is equal in length to the tr aces bet ween the out put s and the si gnal dest inat ions, then the

signals received at the destinations will be synchronized to the REF signal input (IN).

OUT1 6 O

Output 1:

The frequency of the signal provided by this pin is determined by the f eedback

signal connect ed to FBIN, and the FS0:1 inputs (see Table 1).

OUT2 8 O

Output 2:

The frequenc y of t he s ignal prov id ed by this pin is on e-half of t he fr equenc y of

OUT1. See Table 1.

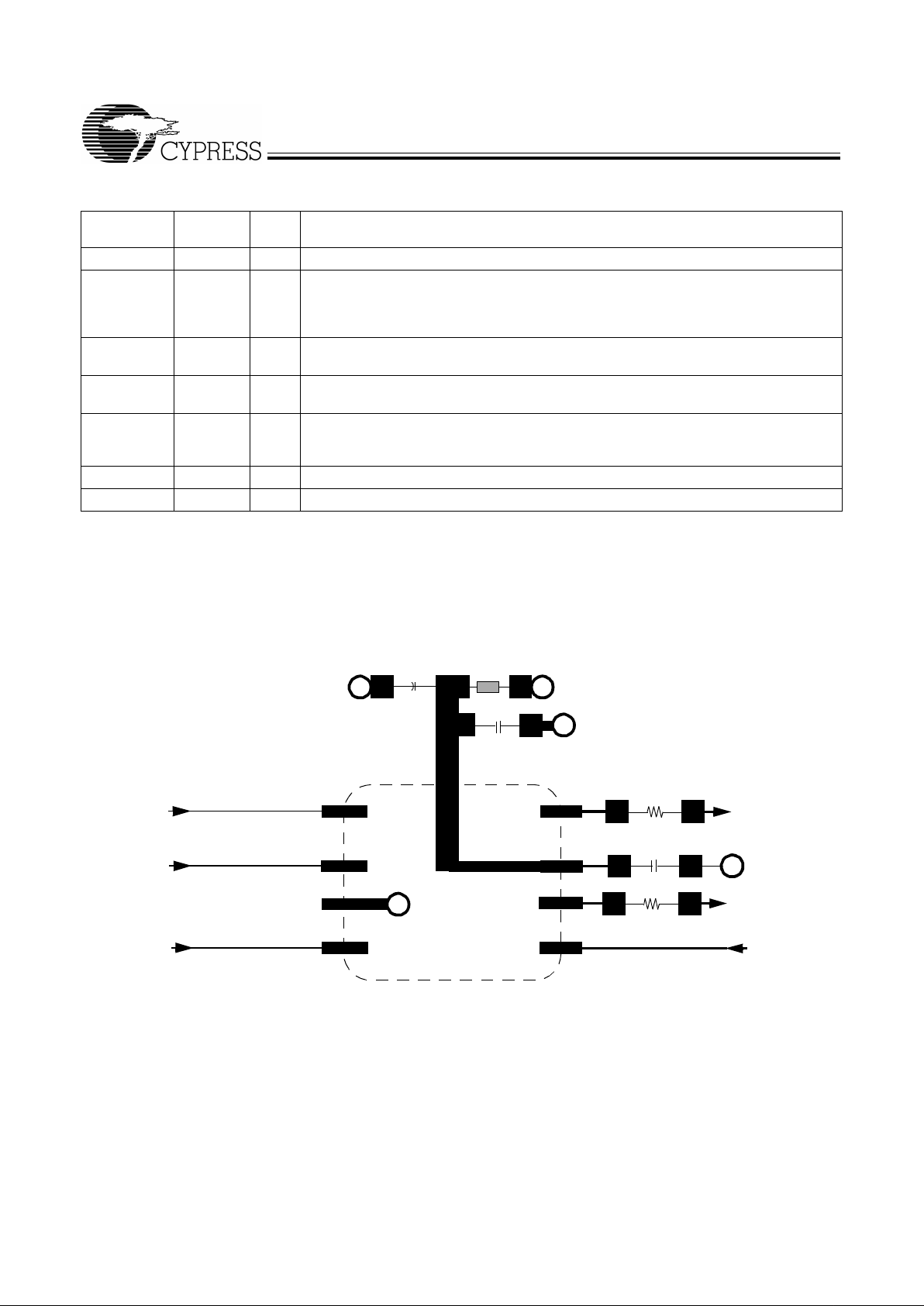

VDD 7 P

Power Connect i ons:

Connect to 3.3V or 5 V. This pin shoul d be b ypasse d with a 0. 1- µF

decoupling capacitor. Use ferrite beads to help reduce noise f or optimal jitter per formance.

GND 3 P

Ground Connection:

Connect all grounds to the common system ground plane.

FS0:1 4, 5 I

Function Select Inputs:

Tie to V

DD

(HIGH, 1) or GND (LO W, 0) as desired per Table 1.

C8

G

Ferrite

Bead

Power Supply Connection

V+G

C

A

G

FS1FS0

GND

IN

FBIN

10 µF

0.01 µF

1

2

3

4

8

7

6

5

22

Ω

22

Ω

G

C9 = 0.1 µF

OUTPUT 1

OUTPUT 2

OUT 2

V

DD

OUT 1

Figure 1. Schematic/Suggested Layout

Loading...

Loading...