Cypress W185 Datasheet

Six Output Peak Reducing EMI Solution

Features

Cypress PREMIS™ family offering

•

• Generates an EMI optimized c locking signal at the

output

• Selectable output frequency range

• Six 1.25%, 3.75%, or 0% down or center spr ead outputs

• One non-Spread output of Reference input

• Integrated loop filter components

• Operates with a 3.3V or 5V supply

• Low power CMOS design

• Available in 24-pin SSOP (Shrink Small Outline

Package)

• Outputs may be selectively disabled

Key Specifications

Suppl y Voltages: ............ .. ... ....... .. ... ....... ... ....VDD = 3.3V±5%

Fr equency Range: ................. .......... .28 MHz ≤ F

Crystal Reference Range:................. 28 MHz ≤ F

Cycle to Cy c le Ji tte r: .............. ........ .. ... ....... .. ... 300 p s (ma x .)

Selectabl e Spread Percentage: ....... .. .......... .1.2 5% or 3.75%

Output Duty Cycle: ............................... 40/60% (worst case)

Output R is e a n d Fall Tim e : . .. .. ........ .. ... ....... .. ... .... 5 ns (max.)

or V

= 5V±10%

DD

≤

75 MHz

in

≤

40 MHz

in

Table 1. Modulation Width Selection

SS%

0F

1F

in

in

≥

≥

F

out

F

out

W185

Output

≥

F

in

≥

F

in

– 1.25% F

– 3.75% F

W185-5

Output

+ 0.625% ≥ F

in

– 0.625%

+ 1.875% ≥ F

in

–1.875%

T able 2. Frequency Range Selection

FS2 FS1 Frequency Range

0 0 28 MHz ≤ F

0 1 38 MHz ≤ F

10 46 MHz ≤ F

11 58 MHz ≤ F

IN

IN

IN

IN

≤

≤

≤

≤

38 MHz

48 MHz

60 MHz

75 MHz

Table 3. Output Enable

EN1 EN2 CLK0:4 CLK5

0 0 Low Low

01Low Active

10Active Low

1 1 Active Active

W185

≥

in

in≥

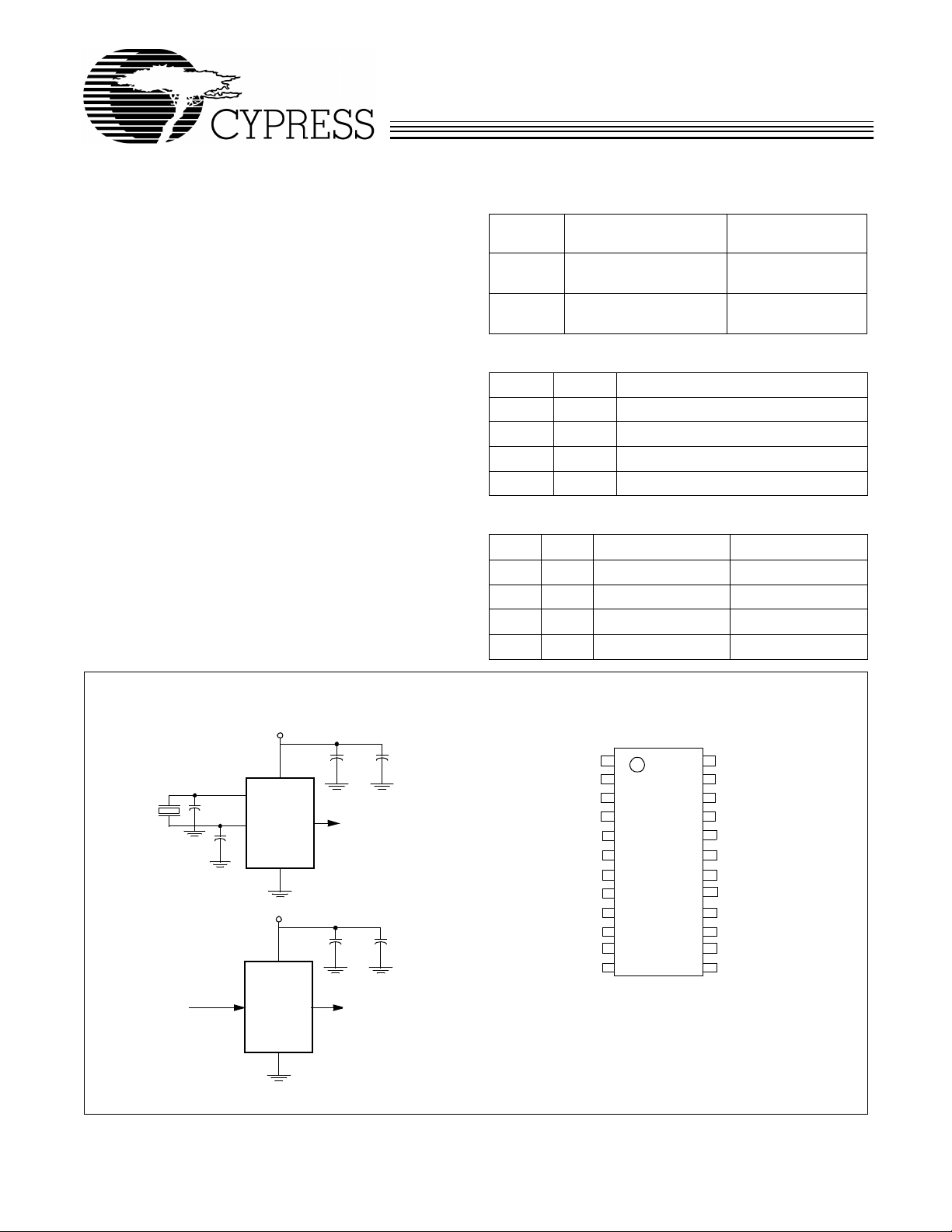

Simplified Block Diagram

3.3V or 5.0V

XTAL

Input

40MHz

max.

Oscillator or

Reference Input

PREMIS is a trademark of Cypress Semiconductor Corporation.

X1

X2

W185

3.3V or 5.0V

W185

Spread Spectrum

Output

(EMI suppressed)

Spread Spectrum

Output

(EMI suppressed)

Pin Configuration

SSOP

REFOUT

FS2

GND

SS%

EN2

GND

CLK0

VDD

CLK1

CLK2

X1

X2

1

2

3

4

5

6

7

8

9

10

11

12

24

23

W185/W185-5

22

21

20

19

18

17

16

15

14

13

SSON#

RESET

FS1

VDD

VDD

NC

EN1

CLK5

VDD

CLK4

GND

CLK3

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

July 2 5, 2000, rev. *A

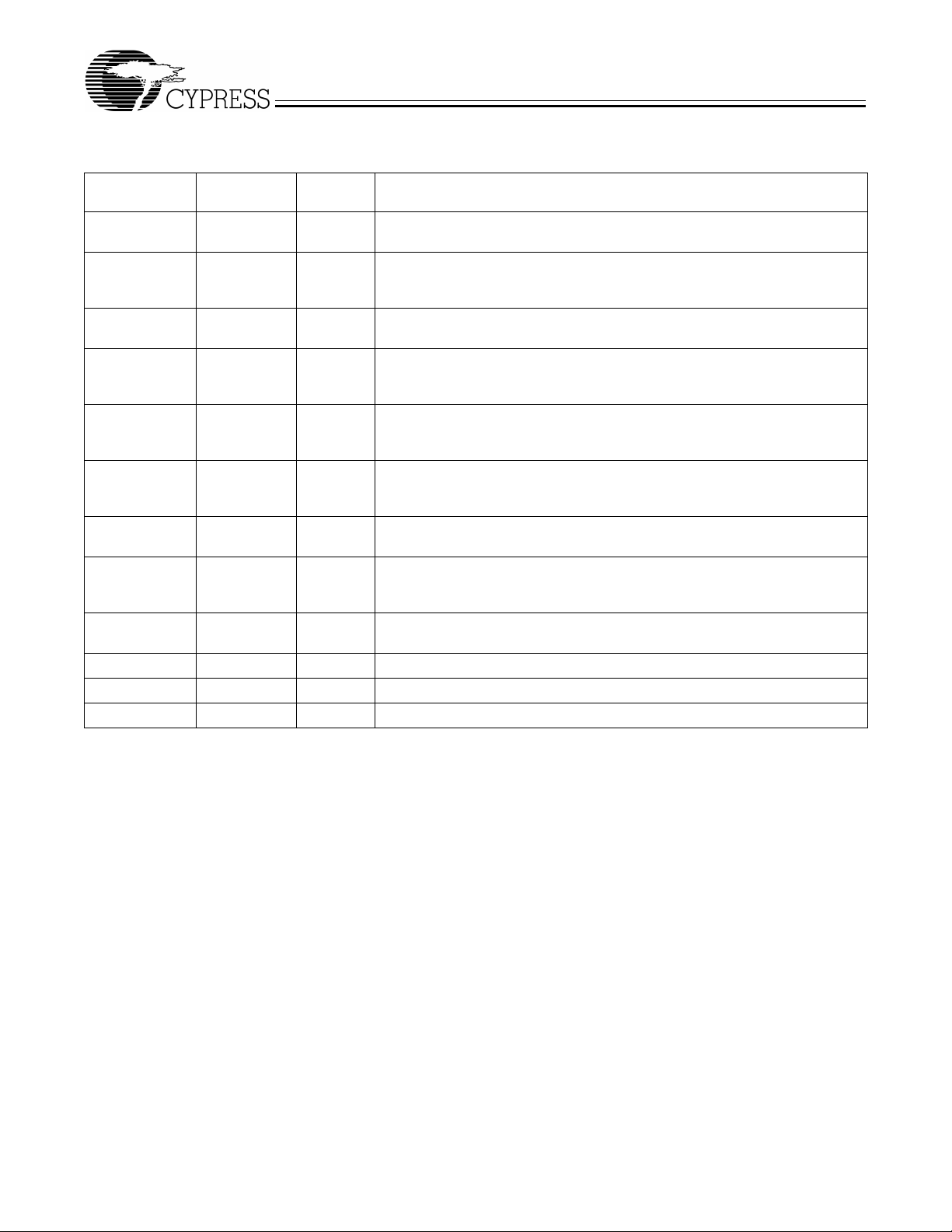

Pin Definitions

W185

Pin Name Pin No.

CLK0:5 9, 11, 12 , 13,

15, 17

CLKIN or X1 3 I

NC or X2 4 I

SS% 6 I

Reset 23 I

REFOUT 1 O

EN1:2 18, 7 I

SSON# 24 I

FS1:2 22, 2 I

VDD 10, 16, 20, 21 P

GND 5, 8, 14 G

NC 19 NC

Pin

Ty pe Pin Description

O

Modulated Frequency O utputs:

ulated input clock (SSON# asserted).

Crystal Connection or External Reference Frequency Input:

dual functions. It may ei ther be connected to an external crystal, or to an

external reference clock.

Crystal Connection:

connected.

Modulation Width Selection:

this pin is used to selec t t he am ount of v ariation and peak EM I r eduction that

is desired on the output signal. This pin has an int ernal pull-up resistor.

Modulation Profile Restart:

pattern at the begi nning of its de fined path . This pin has an internal pul l-do wn

resistor.

Non-Modulated Output:

This output will not have the Spread Spectrum feature enabled regardless of

the state of logic input SSON#.

Output Enable Select Pins:

buffers. See Table 3 on page 1.

Spread Spectrum Contro l (Active LOW):

turns the internal modul ation wav e f orm on. Thi s pin has an internal pul l-do wn

resistor.

Frequency Selection Bit 1 and 2:

tion. Refer to Table 1. These pins have internal pull-up resistors.

Po wer Connec tion:

Ground Conne ction:

No Connect:

This pin should be left float ing.

If using an external re ference, this pin must be left un-

This pin provides a copy of the ref erence frequ ency.

Connected to 3.3V or 5V po wer supply.

This should b e connected t o the common gr ound plane .

Fr equency modu lat ed copi es of th e unmod -

This pin has

When Spread Spectrum feature is turned on,

A rising edge on this input restarts the modulati on

These pins contr ol the act ivi ty of spec ifi c output

Asserting this signal (acti ve LOW )

These pins select the frequency of opera-

2

W185

Overview

The W185 products are one series of devices in the Cypress

PREMIS family. The PREMIS family incorporates the latest

advanc es in PLL spread spectrum frequency synthesizer t echniques. By frequency modulating the output with a low-frequency carrier, peak EMI is greatly reduced. Use of this technology allows s ystems to pass increasingl y diff icult EMI testin g

without resorting to costly shielding or redesign.

In a system, not only i s EMI reduce d in the v arious cl oc k li nes,

but also in all signals which are synchronized to the clock.

Therefore, the benefits of using this technology increase with

the number of address and dat a lines in the syst em. The Simplified Block Diagram sho ws a simple implementa ti on.

Functional Description

The W185 uses a Phase-Locked Loop (PLL) to frequency

modulate an input clock. The result is an output clock whose

frequency is slowly swept over a narrow band near the input

signal. The basic circuit topology is shown in Figure 1. The

input reference signal is divided by Q and fed to the phase

detector. A signal from the VCO is divided by P and fed back

to the phase detec tor als o . The PLL will f or ce the frequen cy of

the VCO output sign al to change until the divid ed output signal

and the divided reference signal match at the phase detector

input. The output frequency is then equal to the ratio of P/Q

times the ref er ence fre quenc y. (Note: Fo r the W 184 the ou tpu t

frequency is nominally equal to the input frequency.) The

unique feature of the Spread Spectrum Frequency Timing

Generator is that a modulating waveform is superimposed at

the input to th e VCO. This causes the VCO output to be s low ly

swept across a predetermined frequency band.

Because the modulating frequency is typically 1000 times

slower than the fundamental clock, the spread spectrum process has little impact on system performance.

Frequency Selection With SSFTG

In Spread Spectrum Frequency Timing Generation, EMI reduction depends on the shape, modulation percentage, and

frequency of the modulating waveform. While the shape and

frequency of the modulating waveform are fixed for a given

frequency, the modulation percent age m ay be varied .

Using frequency select bits (FS1:2 pins), the f requency range

can be set. Spreading percentage may be selected as either

1.25% or 3.75% (see Table 1).

A larger spreading per centage improv es EMI reduction. Ho w-

ever, large spread percentages may either exceed system

maximum frequ ency ra tings o r lo wer the a v er age fr eque ncy to

a point where performance is affected. For these reasons,

spreading percent age options are provided.

V

DD

Clock Input

Reference Input (EMI suppressed)

Freq. Phase

Q

Detector

Feedback

Divider

P

Charge

Pump

GND

Σ

Modulating

Waveform

VCO

PLL

Post

DividersDivider

CLKOUT

Figure 1. Functional Block Diagram

3

Loading...

Loading...