Cypress W180-03, W180-02, W180-01 Datasheet

Peak Reducing EMI Solution

W180

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

July 21 , 2000, rev. *A

Features

•

Cypress PREMIS™ family offering

• Generates an EMI optimized c locking signal at the

output

• Selectable output frequency range

• Single 1.25% or 3.75% dow n or center spread output

• Integrated loop filter components

• Operates with a 3.3V or 5V supply

• Low power CMOS design

• Available in 8-pin SOIC (Small Outline Integrated

Circuit)

Key Specifications

Supply Voltages: .... .......... ... ......... ... .. .......... ..VDD = 3.3V±5%

or V

DD

= 5V±10%

Frequency Range: ................... ...........8 M Hz ≤ F

in

≤

28 MHz

Cycle to Cy c le Ji tte r: .. ... ......... ... .. .......... ... ....... 300 ps (max .)

Selectabl e Spread Percentage: ....................1.25% or 3.75%

Output Duty Cycle: ............................... 40/60% (worst case)

Output R is e a n d Fall Tim e : .......... ... .......... .. ......... 5 ns (max.)

T able 1. Modulation Width Selection

SS%

W180-01, 02, 03

Output

W180-51, 52, 53

Output

0F

in

≥

F

out

≥

F

in

–

1.25%

F

in

+ 0.625% ≥ F

in

≥

–

0.625%

1F

in

≥

F

out

≥

F

in

–

3.75%

F

in

+ 1.875% ≥ F

in≥

–1.875%

Table 2. Frequency Range Selection

FS2 FS1

W180 Option#

-01, 51

(MHz)

-02, 52

(MHz)

-03, 53

(MHz)

008 ≤ F

IN

≤

10 8 ≤ F

IN

≤

10 N/A

0 1 10 ≤ F

IN

≤

15 10 ≤ F

IN

≤

15 N/A

1 0 15 ≤ F

IN

≤

18 N/A 15 ≤ F

IN

≤

18

1 1 18 ≤ F

IN

≤

28 N/A 18 ≤ F

IN

≤

28

PREMIS is a trademark of Cypress Semiconductor Corporation.

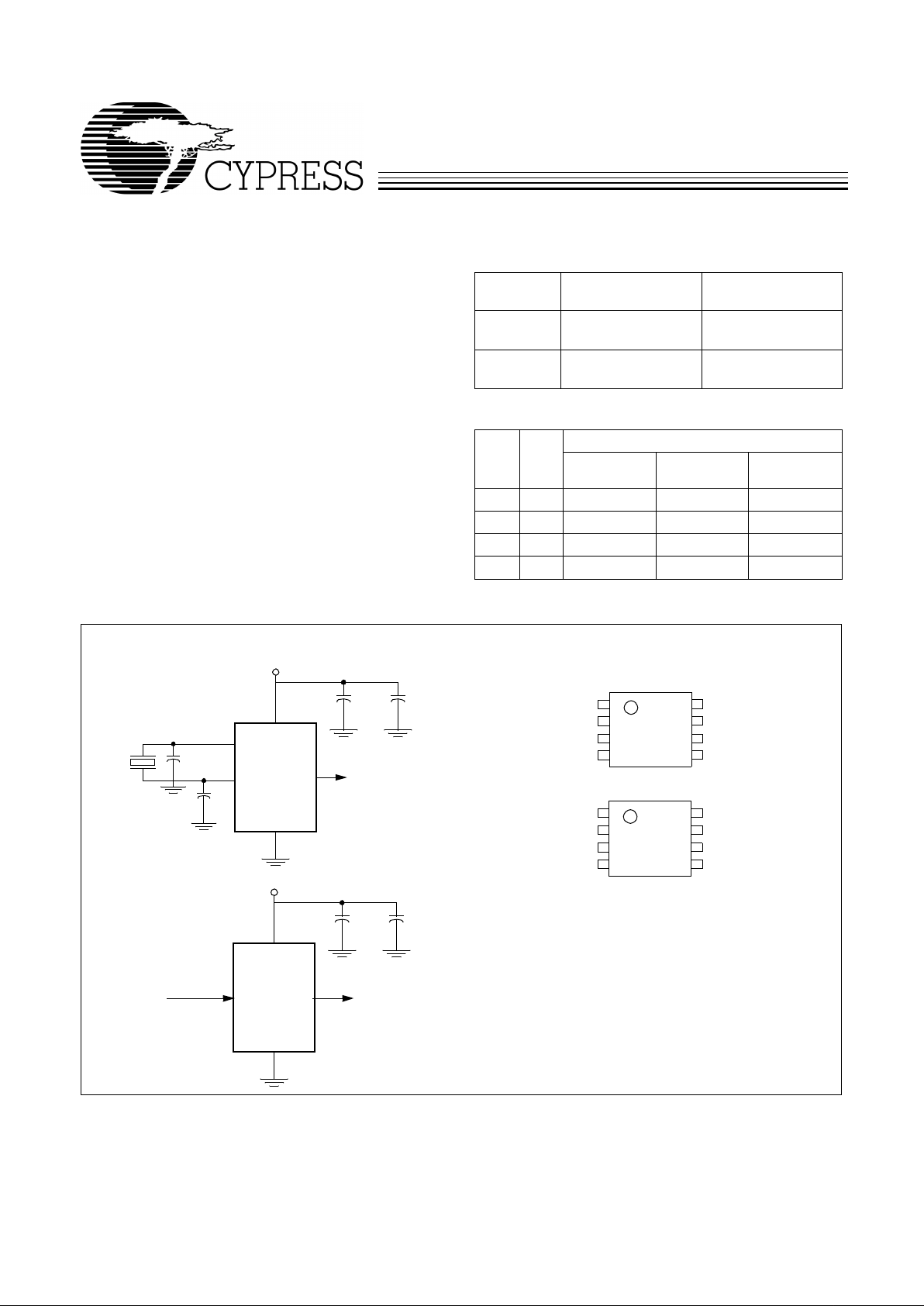

Simplified Block Diagram

Pin Configurations

Spread Spectrum

W180

(EMI su ppressed)

3.3V or 5.0V

Oscilla tor or

Spread Spectrum

W180

(EMI suppressed)

3.3V or 5.0 V

XTAL

X1

X2

Reference Input

Input

Output

Output

W180-02/03

8

7

6

5

1

2

3

4

CLKIN or X1

NC or X2

GND

SS%

SSON#

FS1

VDD

CLKOUT

W180-01/51

8

7

6

5

1

2

3

4

CLKIN or X1

NC or X2

GND

SS%

FS2

FS1

VDD

CLKOUT

SOIC

W180-52/53

W180

2

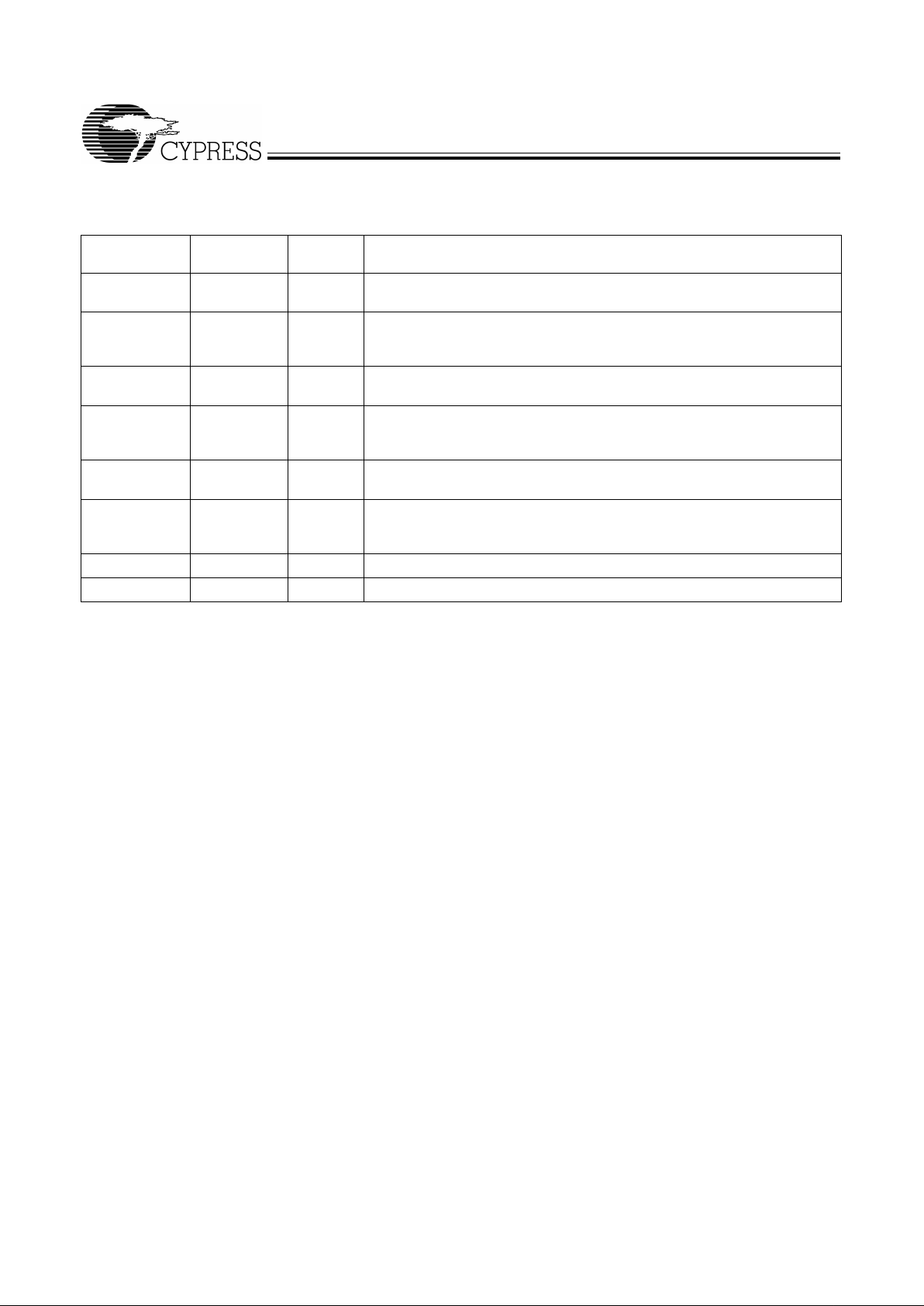

Pin Definitions

Pin Name Pin No.

Pin

Ty pe Pin Description

CLKOUT 5 O

Output Modulated Frequency

: Frequency modulated copy of the unmodu-

lated input clock (SSON# asserted).

CLKIN or X1 1 I

Crystal Connection or External Reference Frequency Input:

This pin has

dual functions. It may either be connected to an ex ternal crystal, or to an

external reference clock.

NC or X2 2 I

Crystal Connection:

Input connectio n for an external crystal. If using an ex-

ternal reference, this pin mus t be left unconnected.

SSON# 8 (-02, -03

52, 53)

I

Spread Spectrum Contro l (Active LOW):

Asserting this signal (acti ve LOW )

turns the internal modulat ion wav e f orm on. Thi s pin has an internal pul l-do wn

resistor.

FS1:2 7, 8 (-01, 51) I

Frequency Selection Bit(s) 1 and 2:

These pins select the frequency range

of operation. Refer to Table 2. These pins have internal pull-up resistors .

SS% 4 I

Modulation Width Selection:

When Spread Spectrum featu re is turned on,

this pin is used to select t he amount of v ari ati on and peak EMI reduction that

is desired on the output signal. Internal pull-up resistor.

VDD 6 P

Po wer Connec tion:

Connected to 3.3V or 5V power supply.

GND 3 G

Ground Connec tion:

This should be connected to the c ommon ground plane .

W180

3

Overview

The W180 products are one series of devices in the Cypress

PREMIS family. The PREMIS family incorporates the latest

advanc es in PLL spread spectrum frequency synthesizer t echniques. By frequency modulating the output with a low-frequency carrier, peak EMI is greatl y reduced. Use of this technology allows s ystems to pass increasingl y diff icult EMI testin g

without resorting to costly shielding or redesign.

In a system, not only i s EMI reduce d in the v arious cl oc k li nes,

but also in all signals which are synchronized to the clock.

Therefore, the benefits of using this technology increase with

the number of address and dat a lines in the syst em. The Simplified Block Diagram on page 1 shows a simple implementation.

Functional Description

The W180 uses a phase-locked loop (PLL) to frequency modulate an input clock. The result is an output clock whose frequency is slo w ly swep t over a narrow band near the i nput signal. The basic circuit topology is shown in Figur e 1. The i nput

refer ence signa l is div ided b y Q and f e d to the phase detector.

A signal from the VCO is divided by P and fed back to the

phase detector also. The PLL will force the frequency of the

VCO output signal to change until the divided output signal

and the divided reference signal match at the phase detector

input. The output frequency is then equal to the ratio of P/Q

times the ref er ence fre quenc y. (Note: F or t he W180 t he outpu t

frequency is eq ual to the input frequency.) Th e unique feature

of the Spread Spect rum Fr equ ency Timi ng Gener ator is that a

modulating wa vef orm is supe rimposed at t he input to the VCO .

This causes the VCO output to be slowly swept across a predetermined frequency ban d.

Because the modulating frequency is typically 1000 times

slower than the fundamental clock, the spread spectrum process has little impact on system performance.

Frequency Selection With SSFTG

In Spread Spectrum Frequency Timing Generation, EMI reduction depends on the shape, modulation percentage, and

frequency of the modulating waveform. While the shape and

frequency of the modulating waveform are fixed for a given

frequency, the modulation percentage may be va ried .

Using frequency s elect bits (FS2:1 pins), the frequency range

can be set (see Table 2). Spread ing percentage is set with pin

SS% as shown in Table 1.

A larger spreading per centage improves EMI reduction. However, large spread percentages may either exceed system

maximum frequ ency ra tings o r lo wer the a v er age fr equency t o

a point where performance is affected. For these reasons,

spreading percentages options are provided.

Freq. Phase

Modulating

VCO

Post

CLKOUT

Detector

Charge

Pump

Waveform

DividersDivider

Feedback

Divider

PLL

GND

V

DD

Σ

Q

P

Clock Input

Reference Input (EMI suppressed)

Figure 1. Functional Block Diagram

Loading...

Loading...