Cypress W155 Datasheet

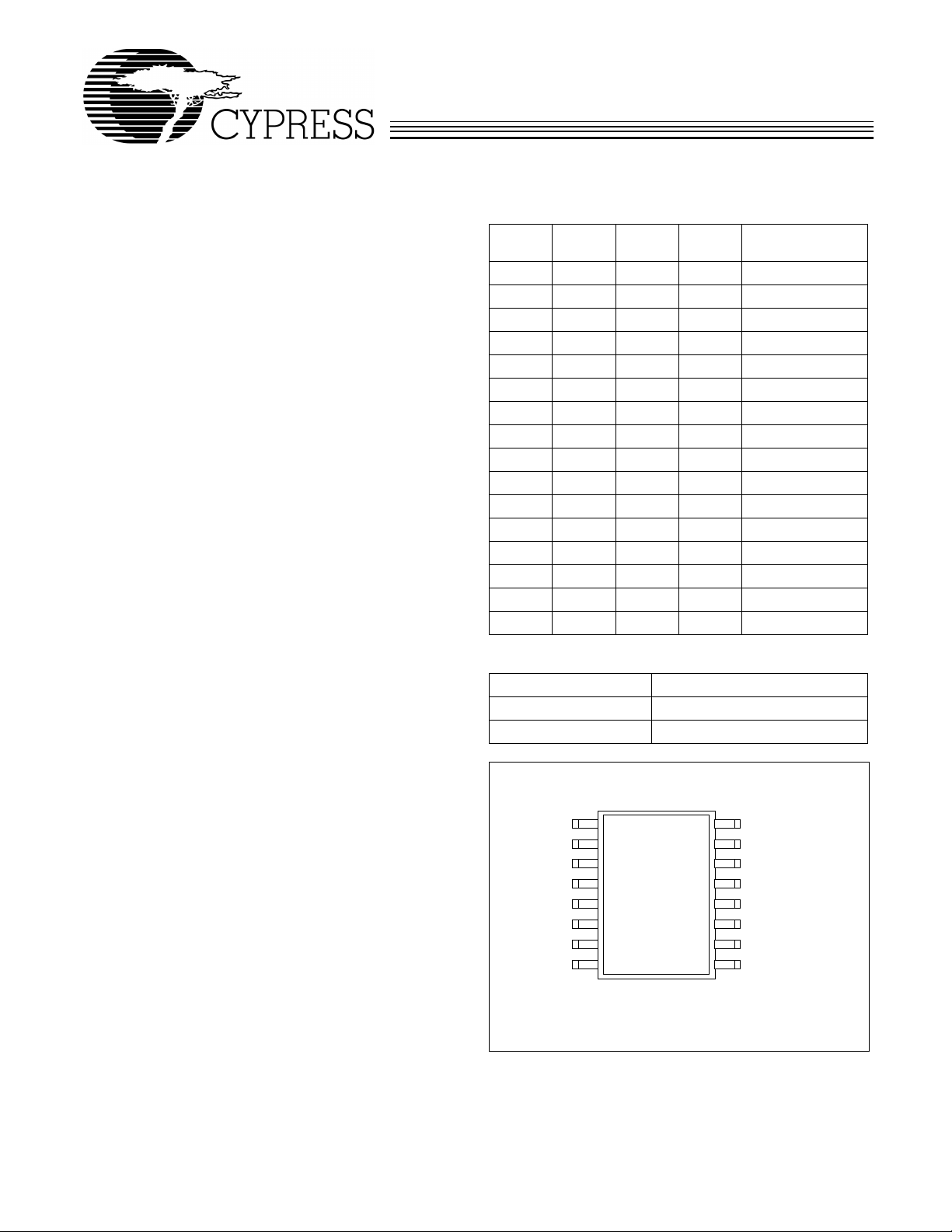

Pin Configuration

TEST

VDD

USBCLK/SS%*

GND

SYSCLK

GND

FS0*

SSON#^

16

15

14

13

12

11

10

9

VDD

X1

X2

GND

FS3*

VDD

FS2*

FS1*

1

2

3

4

5

6

7

8

W155

[1]

Note:

1. Internal pull-up resistor present on inputs marked with ‘*’ and pull-down

resistor present on input marked with ‘^’.

W155

Spread Spectrum Frequency Timing Generator

Features

• Generates a spread spectrum timin g signal (SYSCLK)

and a non-spread signal (USBCL K)

• Requires a 14.318-MHz crystal for oper a ti on

• Supports MIPS microprocessor clock frequencies

• Reduces peak EMI by as much as 12 dB

• Integrated loop filter components

• Cycle-to-cycle jitter = 250 ps (max)

• Operates with a 3.3 or 5.0V power supply

• Spread output is selectable from 10 to 133 MHz

• TEST mode supports modulation off (High-Z ) and special test input reference frequency

• Guaranteed 45/55 duty cycle

• Pack aged in a 16-pin, 300-mil -wide SOIC (Small Outli ne

Integrated Circuit)

Overview

The W155 incorporates the latest advances in PLL-based

spread spectrum frequency synthesizer technology. By frequency modulating the SYSCLK output with a low-frequency

carrier, peak EMI can be great ly reduced in a system. Use of

this technique all ows systems to pass inc reasingly difficu lt EMI

testing without resorting to costly shielding or redesi gn.

In a system that uses t he W155, not only is EMI reduce d in the

various clock lines, but also in all signals which are synchronized to SYSCLK. Therefore, the benefits of using this technique increase with the number of address and data lines in

the system.

The W1 55 is spe cif ically tar get ed towa rd MI PS micr opr oces sor based systems where EMI is of particular concern. Each

device uses a single 14. 318- MHz crystal to gen erate a selectable spread spectrum output and an unmodulated 48-MHz

USB Output.

The spreading func ti on can be disabled b y taking the SSON#

pin high. Spread percent age can be selected with the SS%

input (see

Table 2

below ).

Table 1. Frequency Selection (14.318-MHz Reference)

SYSCLK

FS3 FS2 FS1 FS0

(Output Freq.)

0000133.3 MHz

0001 120 MHz

0010 100 MHz

001174.77 MHz

0100 70 MHz

0101 66.6 MHz

0110 60 MHz

0111 50 MHz

1000 40 MHz

100133.33 MHz

1010 30 MHz

1011 25 MHz

1100 20 MHz

110116.67 MHz

1110 12 MHz

1111 10 MHz

T able 2. Spread Per centage Selection

SS% Spread Percentage

0 –1.25%

1 –3.75%

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

September 29, 1999, r ev. **

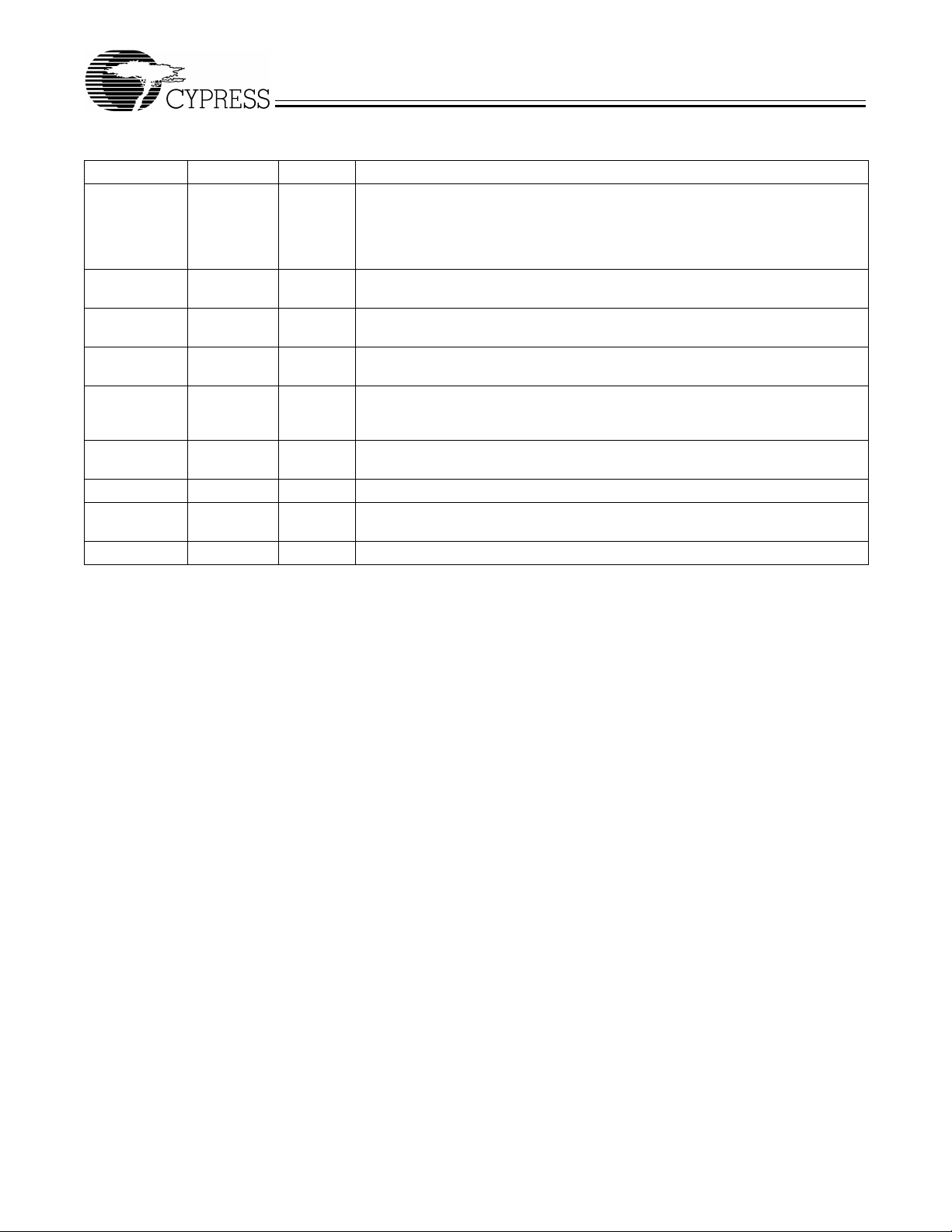

Pin Definitions

Pin Name Pin No. Pin Type Pin Description

USBCLK/

SS%

SYSCLK 12 O

FS0:3 10, 8, 7, 5 I

SSON# 9 I

X1 2 I

X2 3 I

TEST 16 I

VDD 1, 6, 15 P

GND 4, 11, 13 G

14 I/O

USB Clock Output /Modulation Width Se lection Input:

spectrum feature is enabled, this pin is used to select the amount of frequency

variation on the SYSCLK out put (see Ta bl e 2). Wider variations result in greater

peak EMI reduction. When an output: supplies a non-spread 48-MHz signal for

USB support.

System Clock Output :

ture is controlled by pins 9 & 14.

Frequency Select Pi ns:

the SYSCLK output.

Spread Spectrum Contr ol (active LO W):

internal modulati ng wavefor m off. This pin has an internal pull-down resistor.

Crystal Connection or Exter nal Reference Frequenc y Input:

functions . It can be used as either an e xternal crystal connecti on, or as an ex ternal

reference frequency input.

Crystal Connection:

nected.

Te st Mode:

Power Connection:

must be the same voltage level.

Ground Connection:

For normal operation, tie this pin to ground.

Freq uency is se lecte d per Table 1. Spread spectrum fea -

These pins set the frequency of the signal pro vided at

If using an external reference, this pin must be left uncon-

Connected to either 3.3V or 5.0V power supply . All VDD pins

Connect to t he common system ground plane.

W155

When an input; if spread

Pulling this i nput signal HIGH turns the

This pin has du al

2

Loading...

Loading...