Cypress W152-4, W152-3, W152-2, W152-12, W152-11 Datasheet

...

Spread Aware™, Eight Output Zero Delay Buffer

W152

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

June 14, 2000, rev . *B

Features

• Spread Aware™—designed to work with SSFTG

reference signals

• T wo banks of four outputs each

• Configuration options to halve, double, or quadruple

the reference frequency refer to

Ta bl e 1

to determine

the specific option which meets your multipl ication

needs

• Outputs may be three-stated

• Available in 16-pin SOIC package

• Extra strength output drive available (-11/-12 versions)

• Contact factory f or availabilit y information on 16-pin

TSSOP

Key Specific ati o n s

Operating Voltage: ............................................... 3.3V±10%

Operating Range: ... .................15 MHz < f

OUTQA

< 140 MHz

Cycle- to - C ycle Jitter: (Re fer to

Figure 3

) ....... .............225 ps

Cycle-to-Cycle Jitter: Frequency Range

25 to140 MHz ........ ........................... .. ............. .. ..... 125 ps

Output to Output Skew: Between Banks.....................215 ps

Output to Output Skew: Within Banks

(Refer to

Figure 4

) .................... ............ ............ ....... 1 0 0 p s

Total Timing Budget Impact:.......... ............................. .555 ps

Max. Phase Error Variation: ......................................±225 ps

Tracking S kew: ........... ............ ............ ............ .. .......... ± 1 3 0 p s

T able 1. Configuration Options

Device Feedback Signal QA0:3 QB0:3

W152-1/11

[1]

QA0:3 or QB0:3 REFx1 REFx1

W152-2/12

[2]

QA0:3 REFx1 REF/2

W152-2/12

[2]

QB0:3 REFx2 REFx1

W152-3 QA0:3 REFx2 REFx1

W152-3 QB0:3 REFx4 REFx2

W152-4 QA0:3 or QB0:3 REFx2 REFx2

Notes:

1. W152-11 has stronger output drive than the W152-1.

2. W152-12 has stronger output drive than the W152-2.

Spread Aware is a trademark of Cypress Semiconducto r Corporation.

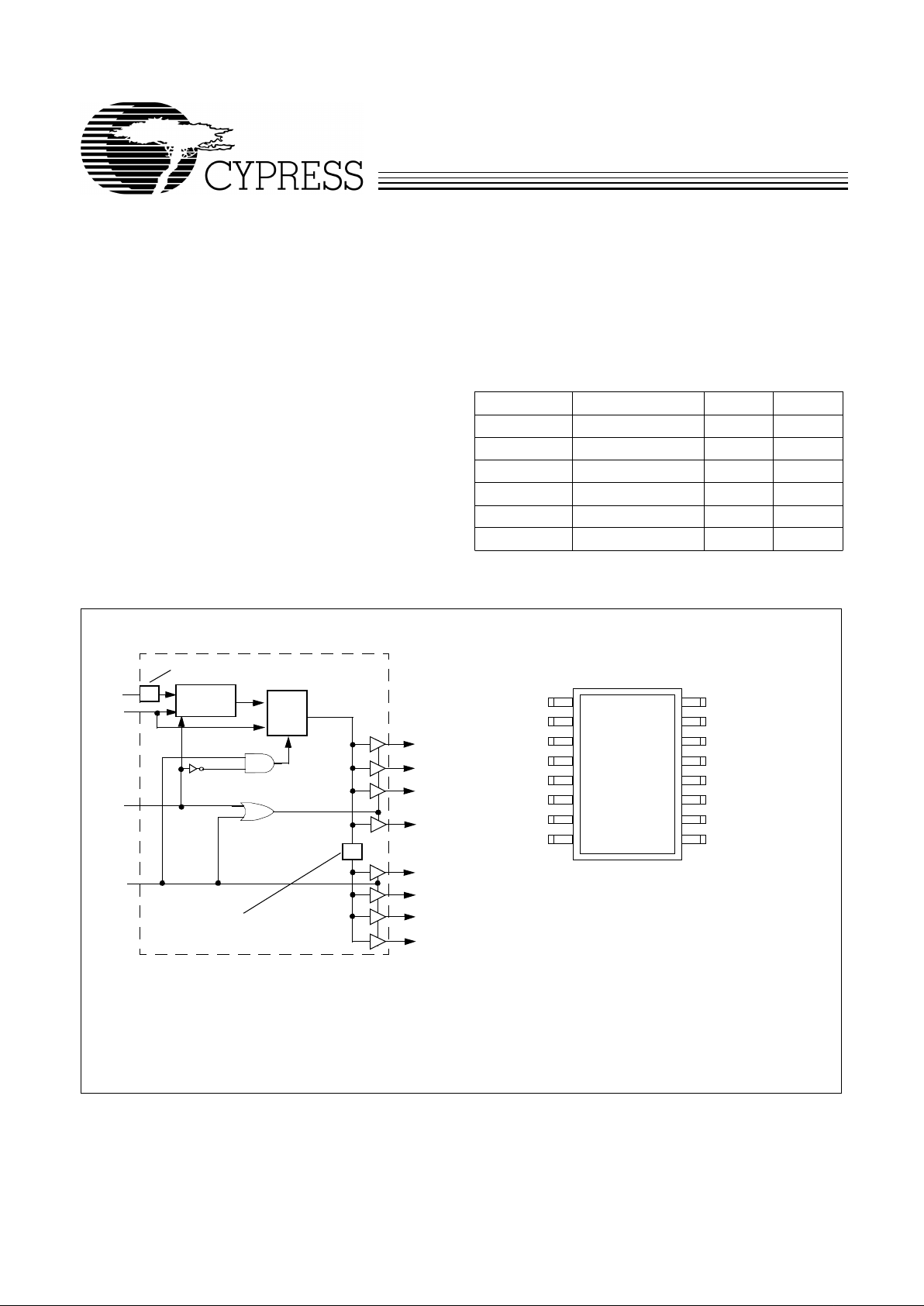

Block Diagram

Pin Configuration

QA0

PLL

REF

MUX

QA1

QA2

QA3

QB0

QB1

÷2

SEL0

FBIN

QB2

QB3

SEL1

÷2

(present on the -3 and -4 only)

(present on the -2, -12, and -3 only)

FBIN

QA3

QA2

VDD

GND

QB3

QB2

SEL0

16

15

14

13

12

11

10

9

REF

QA0

QA1

VDD

GND

QB0

QB1

SEL1

1

2

3

4

5

6

7

8

W152

2

Overview

The W152 products are eight-output zero delay buffers. A

Phase-Lock ed Loop (PLL) i s used to tak e a time- varying signal

and provide eight copies of that same signal out. The external

feedback to the PLL provides outputs in phase with the reference inputs.

Internal divid ers exist in some options allo wing the user to get

a simple multiple (/2, x2, x4) of the reference input, for details

see Table 1. Because the outputs are separated into two

banks, it is possi ble to provide some combin ation of these multiples at the sa me time.

Spread Aware

Many syst em s being designed no w utilize a tech nology called

Spread Spectrum F requency Timi ng Generation . Cypress has

been one of the pioneers of SSFTG develop me nt, and we designed this product so as not to filte r off the Spread Spectrum

featur e of the Referen ce input, assuming i t ex ists. When a z ero

delay buffer is not designed to pass the SS feature through,

the result is a significant amount of tracking skew which may

cause problems in systems requiring synch roni zation.

For more details on Spread Spectrum timing technology,

please see the Cypress application note titled, “EMI Suppression Techniques with Spread Spectrum Frequency Timing

Generator (SSFTG) ICs.”

Functional Description

Logic inputs provide the user the ability to turn off one or both

banks of clocks when not in use, as described in Table 2. Disabling a bank of unused outputs will reduce jitter and power

consumption, an d will a ls o reduce th e amount o f EMI gener ated by the W152.

These same inputs al low t he user to by pass the PLL ent irely i f

so desired. When this is done, the device no longer acts as a

zero delay buffer, it simply reverts to a standard eight-output

clock driv er.

The W152 PLL enters an auto power-down mode when there

are no rising edges on the REF inpu t. In this mode, all output s

are three-stated and t he PLL is turned off.

Pin Definitions

Pin Name Pin No.

Pin

Type Pin Description

REF 1 I

Reference Input:

The output signals QA0:3 through QB0:3 will be synchronized to

this signal unless the device is programm ed to bypass the PLL.

FBIN 16 I

Feedback Input:

When programmed to zero delay buffer mode, this input mu st be

fed by o ne of the ou tputs (QA0: 3 or QB 0:3) to e nsur e proper f unctio nality. If t he tr ace

between FBIN and the output pin being used for fe edback is equal in length to the

traces betwe en the outputs and the signal destinations, t hen the signals received at

the destinations will be synchronized to the REF signal input.

QA0:3 2, 3, 14, 15 O

Outputs from Bank A:

The frequency of the signals provided by these pins is determined by the f eedbac k signal connected to FBIN, and the sp ecific W152 op tion being

used. See Table 2.

QB0:3 6, 7, 10, 11 O

Outputs from Bank B:

The frequency of the signals provided by these pins is determined by the f eedbac k signal connected to FBIN, and the sp ecific W152 op tion being

used. See Table 2.

VDD 4, 13 P

Power Connections:

Connect to 3.3V. Use ferrite beads to help reduce noise for

optimal jitter performance.

GND 5, 12 G

Ground Connections:

Connect all grounds to the common system ground plane.

SEL0:1 9, 8 I

Function Select Inputs:

Tie to V

DD

(HIGH, 1) or GND (LOW, 0) as desired per

T able 2.

T able 2. Input Logic

SEL1 SEL0 QA0:3 QB0:3 PLL

0 0 Three-State Three-State Shutdown

0 1 Active Three-State Active, Utilized

1 0 Active Active Shutdown,

Bypassed

1 1 Active Active Active, Utilized

W152

3

How to Implement Zero Delay

Typically, zero delay buffers (ZDBs) are used because a designer wants to provide multiple copies of a clock signal in

phase with each other . The whole c oncept behin d ZDBs is that

the signals at the destination chips are all going HIGH at the

same time as the input to the ZDB. In order to achieve this,

layou t must com pensate f or tra ce length be tween the ZDB an d

the target devices. The method of compensation is described

below.

External feedbac k is the trait that allows f or thi s compensati on.

The PLL on the ZDB will cause the feedback signal to be in

phase with the reference signal. When laying out the board,

match the trace lengths between the output being used for

feedback and the FBIN input to the PLL.

If it is desirable to either add a little delay, or slightly precede

the input signal, this m ay also be affec ted by either making the

trace to the FBIN pin a little shorter or a little longer than the

traces to the devices being clocked.

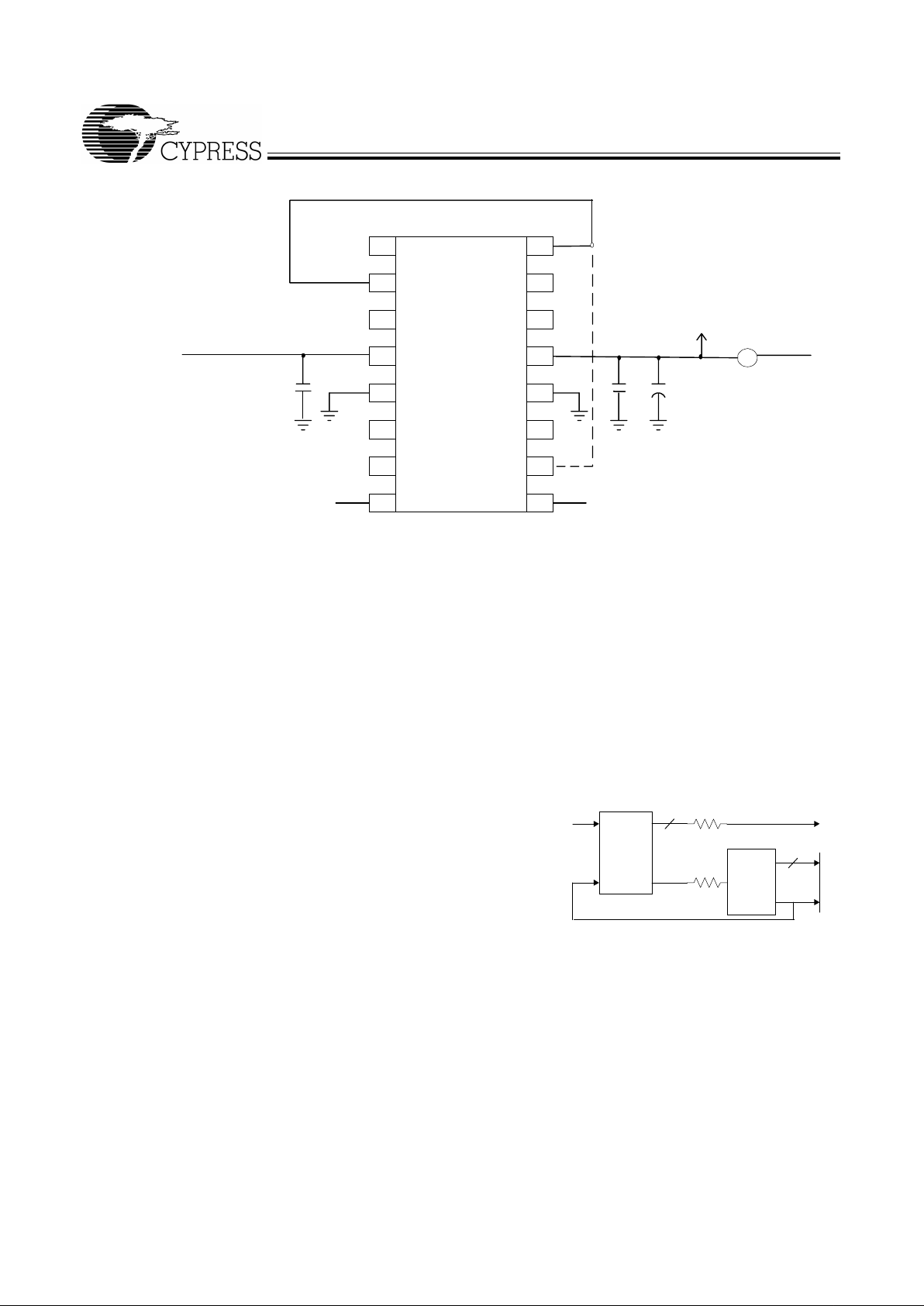

Inserti n g Other Devices in Feedback Path

Another nice feature available due to the external feedback is

the ability to synchronize signals up to the signal coming from

some other dev ic e. Thi s impl ement ation can be appl ied t o an y

device (ASIC, mult iple output cloc k buffer /driver, etc.) which is

put into the feedback path.

Referring to Figure 2 , if the traces between the ASIC/buffer

and the destination of the clock signa l(s) (A) are equal in lengt h

to the trace between the buffer and the FBIN pin, the signals

at the destination(s) device will be driven HIGH at the same

time the Reference clock provided to the ZDB goes HIGH.

Synchronizing the other out puts of t he ZDB to the outputs f orm

the ASIC/Buff er is mor e comp le x ho we v er, as any propaga tion

delay in the ASIC/Buf fer must be accounted for.

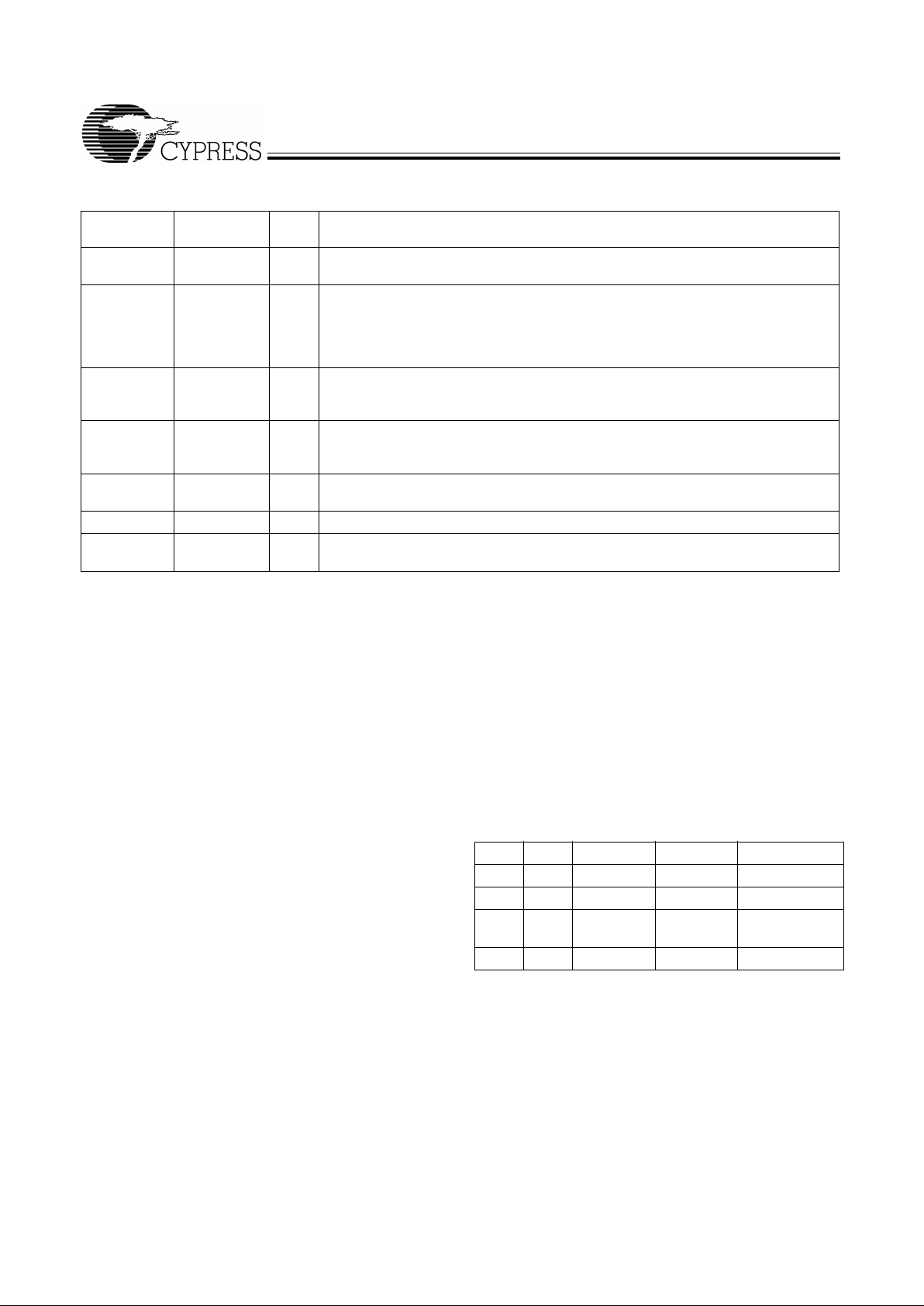

9

2

3

1

4

7

6

8

5

16

13

14

15

10

11

12

3.3V

Supply

VDD

0.1 µF

0.1 µF

10 µF

Ferrite

Bead

See Note 3

VDD or GND (for desired operation mode)

VDD or GND (for desired operation mode)

QA0

QA2QA1

QA3

Ground

PowerPower

FB InRef In

QB1

QB0

QB2

QB3

SEL1 SEL0

Ground

VDD

Figure 1. Schematic

[3]

Note:

3. Pin 16 needs to be connected to one of the outputs from either bank A or bank B, it should not be connected to both. Pins 2 and 10 are shown here as

examples. None of the outputs should be considered aas preferred for the feedback path.

Reference

Signal

Feedback

Input

ASIC/

Buffer

Zero

Delay

Buffer

A

Figure 2. 6 Output Buffer in the Feedback Path

Loading...

Loading...