Cypress W133H Datasheet

PRELIMINARY

Spread Spectrum System Frequency Synthesizer

W133

Cypress Semiconductor Corporation

• 3901 North First Street • San Jose • CA 95134 • 408-943-2600

October 13, 1999, rev. **

Features

• Maximized EMI suppression usi ng Cypress’s spread

spectrum technology

• Intel CK98 Specificat ion compliant

• 0.5% downspread out puts deliver up to 10 dB lower EMI

• Four skew-controlled copies of CPU output

• Eight copies of PCI out put (synchronous w/CPU outp ut)

• Four copies of 66-MHz fix ed frequency 3.3V clock

• T wo copies of CPU/2 outputs for synchr onous memory

reference

• Three copies of 16. 67-MHz IO APIC clock , synchr onous

to CPU clock

• One copy of 48-MHz USB output

• Two copies of 14.31818-MHz reference clock

• Programmable to 133- or 100-MHz operation

• Power management control pins for cloc k stop and sh ut

down

• Available in 56-pin SSOP

Key Specific ati o n s

Supply Voltages:...................................... V

DDQ3

= 3.3V±5%

V

DDQ2

= 2.5V±5%

CPU Ou tp u t Ji tte r: ........... .. .......... ........................ .......2 5 0 p s

CPUdiv2 Output Jitter:.................................................250 ps

48 MHz, 3V66, PCI, IOAPIC Output Jitter:..................500 ps

CPU0: 3, CP Ud iv 2 _ 0:1 O u tp u t Skew : ...... ... ......... .......1 7 5 p s

PCI_ F, PCI1:7 Out p u t Skew: ...... .. .......... .....................50 0 ps

3V66_0:3, IOAPIC0:2 Output Skew; .......... .. .. .. ...........250 ps

CPU to 3V66 Output Offset:.............0.0–1.5 ns (CPU leads)

3V66 to PCI Output Offset:.............. 1.5–4.0 ns (3V66 leads)

CPU to IOAPIC Output Offset:.........1.5–4.0 ns (CPU leads)

Logic inputs, except SEL133/100#, have 250-kΩ pull-up

resistors.

T able 1. Pin Selectable Frequency

[1]

SEL133/100# CPU0:3 (MHz) PCI

1 133 MHz 33.3 MHz

0 100 MHz 33.3 MHz

Note:

1. See

Table 2

for complete mode selection details.

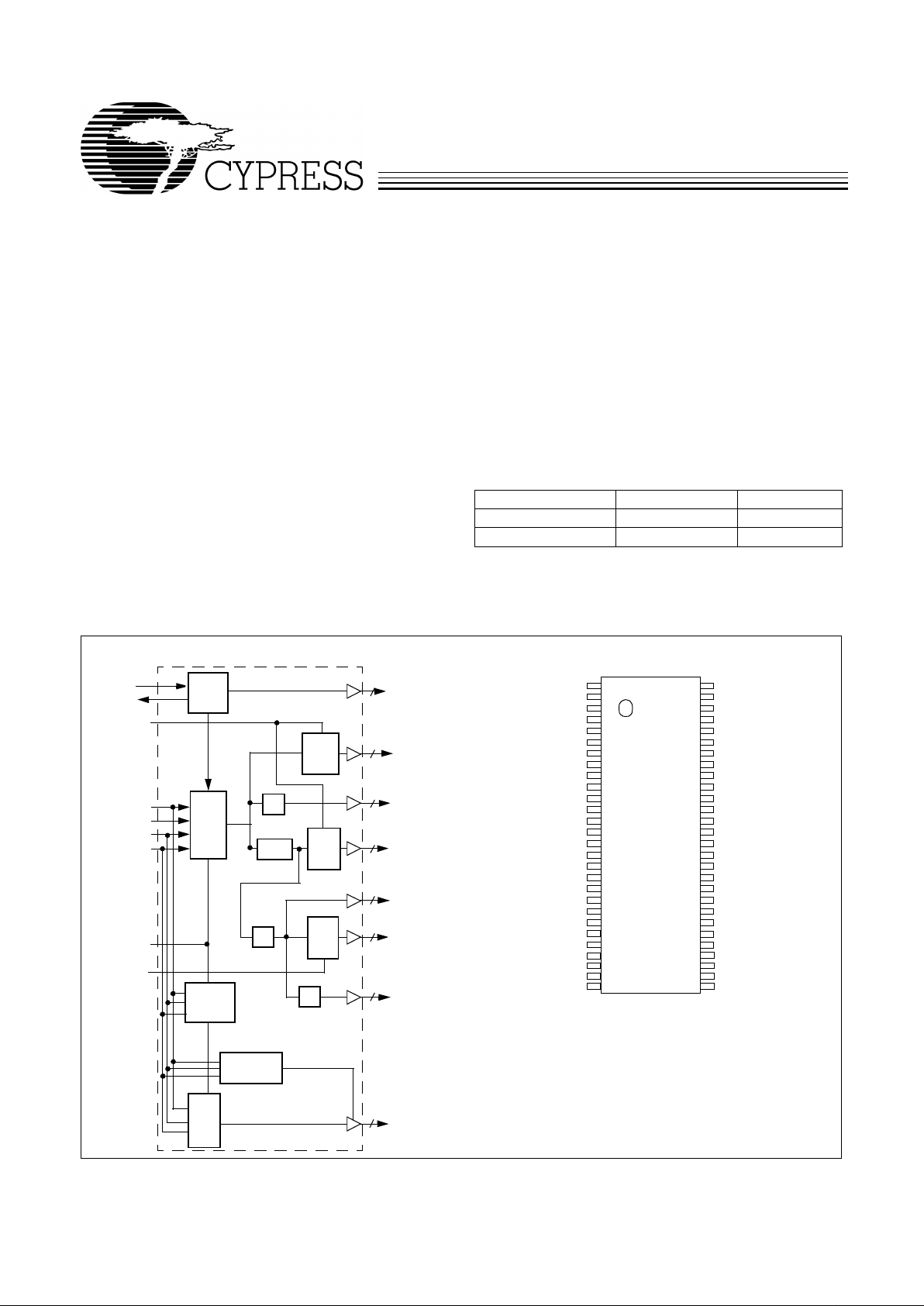

Block Diagram

Pin Configuration

REF0:1

CPU0:3

CPUdiv2_0:1

3V66_0:3

XTAL

PLL 1

SPREAD#

X2

X1

PCI_F

PCI1:7

IOAPIC0:2

48MHz

PLL2

OSC

÷2

STOP

Logic

Power

Three-state

Logic

SEL0

SEL1

SEL133/100#

Clock

CPU_STOP#

÷2/÷1.5

STOP

Logic

Clock

Down

Logic

÷2

STOP

Logic

Clock

÷2

2

4

2

4

1

7

3

1

PCI_STOP#

PWRDWN#

GND

REF0

REF1

VDDQ3

X1

X2

GND

PCI_F

PCI1

VDDQ3

PCI2

PCI3

GND

PCI4

PCI5

VDDQ3

PCI6

PCI7

GND

GND

3V66_0

3V66_1

VDDQ3

GND

W133

VDDQ2

IOAPIC2

IOAPIC1

IOAPIC0

GND

VDDQ2

CPUdiv2_1

CPUdiv2_0

GND

VDDQ2

CPU3

CPU2

GND

VDDQ2

CPU1

CPU0

GND

VDDQ3

GND

PCI_STOP#

CPU_STOP#

PWRDWN#

SPREAD#

SEL1

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

32

31

30

29

3V66_2

3V66_3

VDDQ3

SEL133/100#

SEL0

VDDQ3

48MHz

GND

W133

PRELIMINARY

2

Overview

The W133 is designed to provide the essential frequency

sources to work with advanced multiprocessing Intel® arch itecture pl atforms. Spl it voltage supply signaling provides 2.5V

and 3.3V clock f requencies operati ng up to 133 MHz.

From a low-cost 14.31818-MHz reference crystal oscillator,

the W133 generates 2.5V clock outputs to sup port CPUs, core

logic chip set , and Direct RDRAM cloc k gener ators. It also provides skew-controlled PCI and IOAPIC cl ocks synchronous to

CPU clock, 48- MHz Universal Serial Bus (USB) clock, and replicates the 14.31818-MHz reference clock.

All CPU, PCI, and IOAPIC clocks c an be synchronously modulated for spread spectrum operations. Cypress employs proprietary techniques that provide the maximum EMI reduction

while minimizing the clock skews that could reduce system

timing margins. Spread Spectrum modulation is enabled by

the active LOW control signal SPREAD#.

The W133 also includes po wer management contro l inputs. By

using these inputs, system logic can stop CPU and/or PCI

clocks or power down the entire device to conserve system

power.

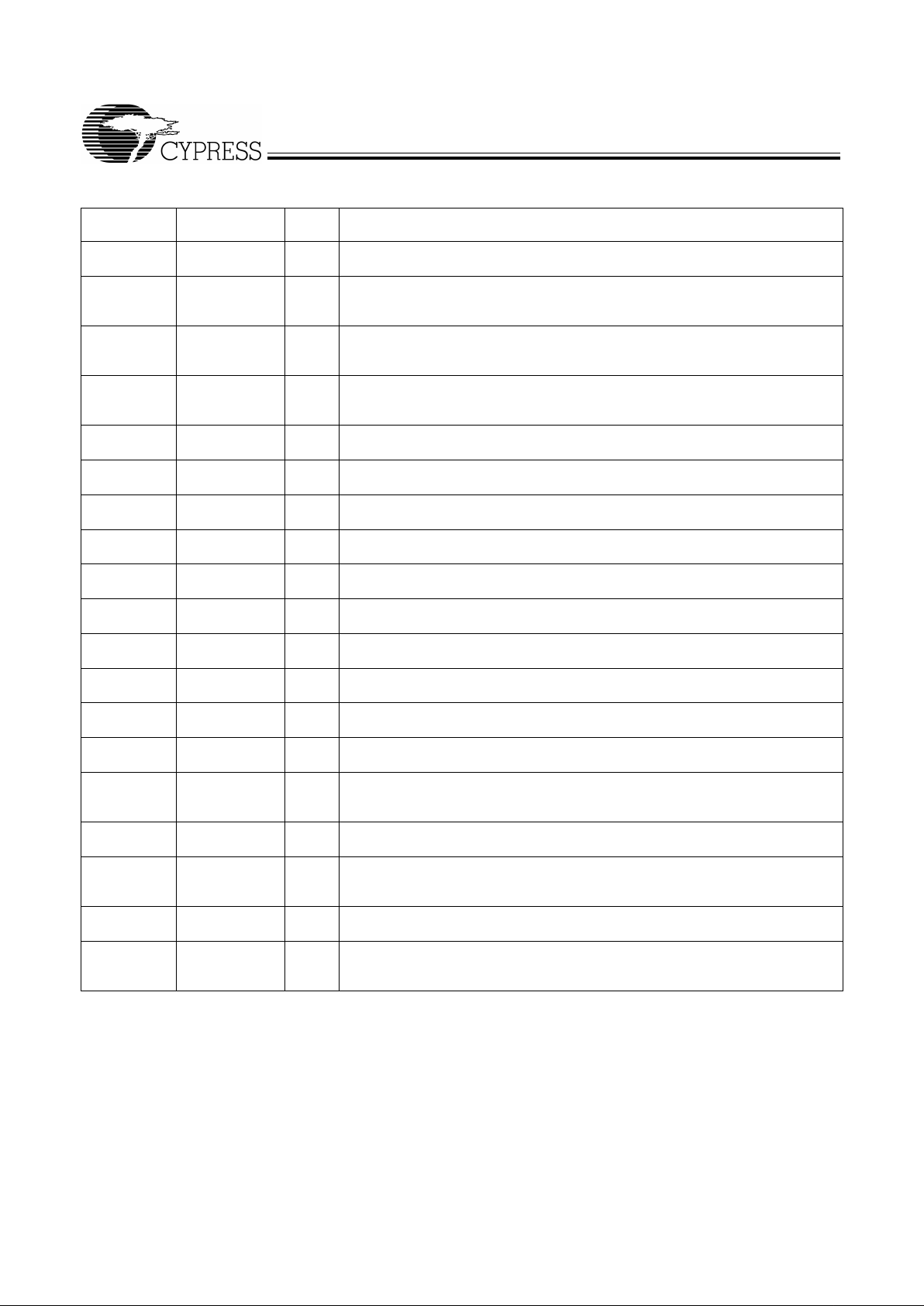

Pin Definitions

Pin Name Pin No.

Pin

Type Pin Description

CPU0:3 41, 42, 45, 46 O

CPU Clock Outputs 0 through 3:

These fo ur CPU cloc k s run at a f requ ency set b y

SEL133/100#. Output voltage swin g is set by the voltage applied to VDDQ2.

CPUdiv2_ 0:1 49,50 O

Synchronous M emory Refere nce Clock Out put 0 thr ough 1:

Reference clock f or

Direct RDRAM clock genera tors running at 1/2 CPU clock frequency. Output voltage

swing is set by the voltage applied to VDDQ2.

PCI1:7 9, 11 , 12, 14, 1 5,

17, 18

O

PCI Clock Outputs 1 t hrough 7:

These se ven PCI cloc k outp uts run sy nchronously

to the CPU clock. Voltage swing is set by the power connection to VDDQ3. PCI1:7

outputs are stopped when PCI _STOP# is held LOW .

PCI_F 8 O

PCI_F (PCI Free-running):

This PCI clock output runs synchronously to the CPU

clock. V oltag e swing is set by the power connection to VDDQ3. PCI_F is n ot affe cted

by the state of PCI_STOP#.

REF0:1 2, 3 O

14.318-MHz Reference Cloc k Output:

3.3V copies of the 14.318-MHz reference

clock.

IOAPIC0:2 53, 54, 55 O

I/O APIC Clock Output:

Provides 16.67 -MHz fixed frequenc y. The output voltage

swing is set by the power connection to VDDQ2.

48MHz 30 O

48-MHz O u tp u t:

Fixed 48-MHz USB output. Output voltage swing is controlled by

voltage app li ed to VDDQ3.

3V66_0:3 21, 22, 25, 26 O

66-MHz Output 0 through 3:

Fixed 66-MHz outputs. Output voltage swing is con-

trolled by voltage applied to VDDQ3.

SEL0:1 32, 33 I

Mode Select Input 0 through 1:

3.3V LVTTL-compatible input for selecting clock

output modes.

SEL133/100# 28 I

Frequency Selecti on Input:

3.3V L VTTL-c ompatibl e input that selects CPU output

frequency as shown in Tabl e 1.

X1 5 I

Crystal Connection or External Reference Frequency Input:

Connect to either

a 14.318-MHz crystal or an external refer ence signal.

X2 6 O

Crystal Connection:

An output connection for an external 14.318-MHz crystal. If

using an external reference, this pin must be left unconnected.

SPREAD# 34 I

Active LO W Spread Spectrum Enabl e:

3.3V L VTTL- compatib le input t hat enabl es

spre ad spec t rum m o de when held L OW.

PWRDWN# 35 I

Active LOW Power Down Input:

3.3V LVTTL-compatible asynchronous input that

requests the de vice to enter power-down mode.

CPU_STOP# 36 I

Active LOW CPU Clock Stop:

3.3V LVTTL-compatible asynchronous input that

stops all CPU and 3V66 cloc ks when held LO W . CPUdiv2 output s are unaff ected by

this input.

PCI_STOP# 37 I

Active LOW PCI Cloc k Stop:

3.3V LVTTL-compatible asynchr onous input that

stops all PCI outputs except PCI_F when held LOW.

VDDQ3 4, 10, 16, 23, 27,

31, 39

P

Power Connection:

Power suppl y for PCI output buff ers, 48-MHz USB output buff er,

Reference output buff ers, 3V66 outpu t buffers , core logic, and PLL ci rcuitry . Connect

to 3.3V supply.

VDDQ2 43, 47, 51, 56 P

Power Connection:

Power supply for IOAPIC, CPU, and CPUdiv2 output buffers.

Connect to 2.5V supply.

GND 1, 7, 13, 19, 20,

24, 29, 38, 40,

44, 48, 52

G

Ground Connecti on:

Connect all ground pin s to the common s ystem gr ound plane .

W133

PRELIMINARY

3

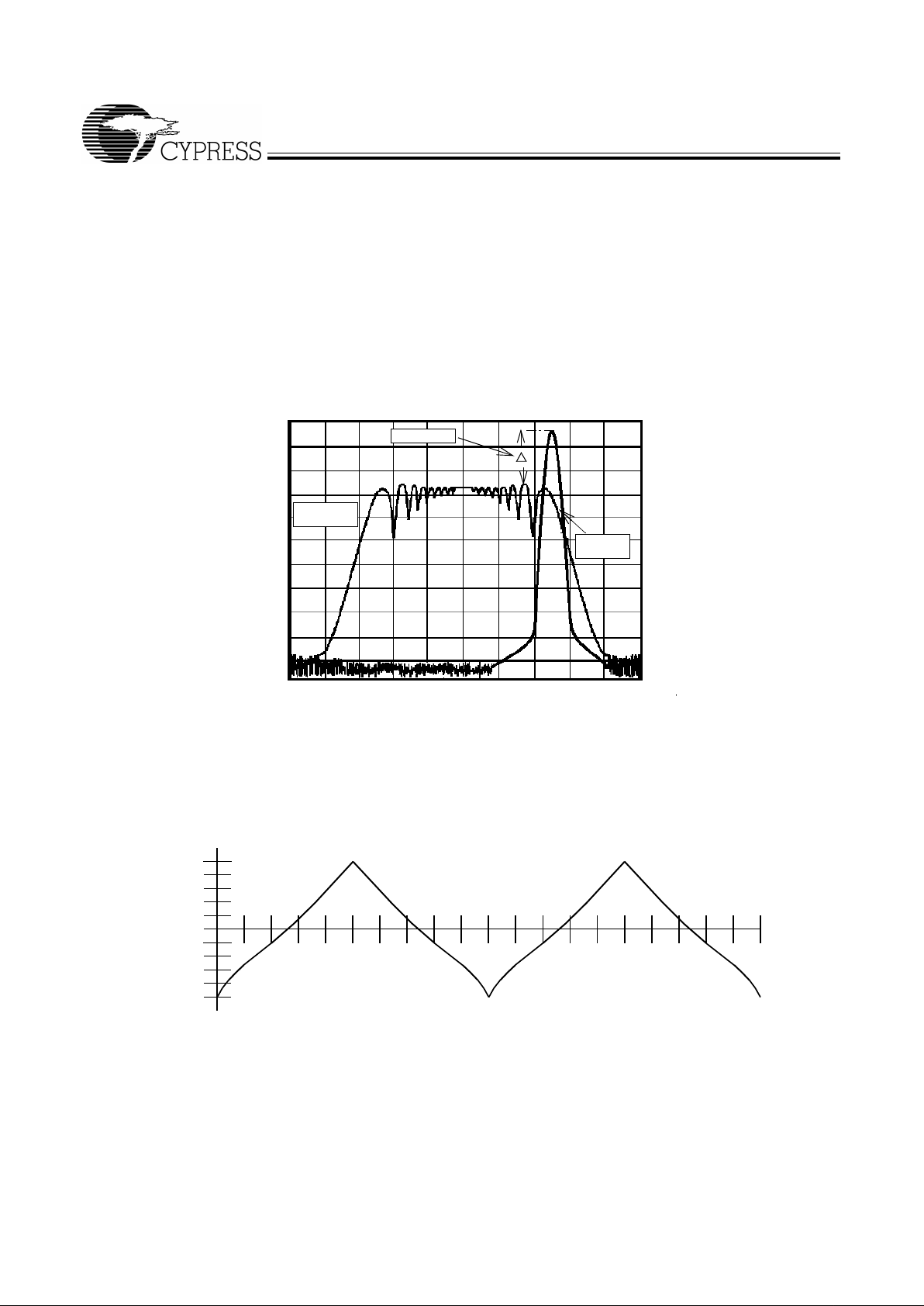

Spread Sp ectrum C locki n g

The device gener ates a clock that is frequency modulated in

order to increase the bandwidth that it occu pies. By increas ing

the bandwidth of the fundamental and its harmonics, the amplitudes of the radiated electromagnetic emissions are reduced. This effect is depicted in Figure 1.

As shown in Figure 1, a harmonic of a modulated clock has a

much low er amplitude th an that of an un modulated si gnal. The

reduction in amplitude is dependent on the harmonic number

and the frequency deviation or spread. The equation for the

reduction is

dB = 6.5 + 9*log

10

(P) + 9*log10(F)

Where P is the percentage of deviation and F is the frequency

in MHz where the reduction is measured.

The output clock is modulated with a waveform depicted in

Figure 2. This waveform, as discussed in “Spread Spect rum

Clock Generation f or the Reducti on of Radiated Emissio ns” by

Bush, Fessler, and Hardin produces the maximum reduction

in the amplitude of radiated elect romagnetic emissions. The

deviati on selec ted for this chip i s –0.5% do wnspr ead. Fi gure 2

details the Cypress spr eading pat tern. Cypress does offer options with more spread and greater EMI reduction. Cont act

your local Sales representative for details on these devices .

Spread

Spectrum

Enabled

EMI Reduction

Spread

Spectrum

Non-

Figure 1. Typical Clock and SSFTG Comparison

100%

60%

20%

80%

40%

0%

–20%

–40%

–60%

–80%

–100%

10%

20%

30%

40%

50%

60%

70%

80%

90%

100%

10%

20%

30%

40%

50%

60%

70%

80%

90%

100%

Time

Frequency Shift

Figure 2. Modulation W aveform Profile

W133

PRELIMINARY

4

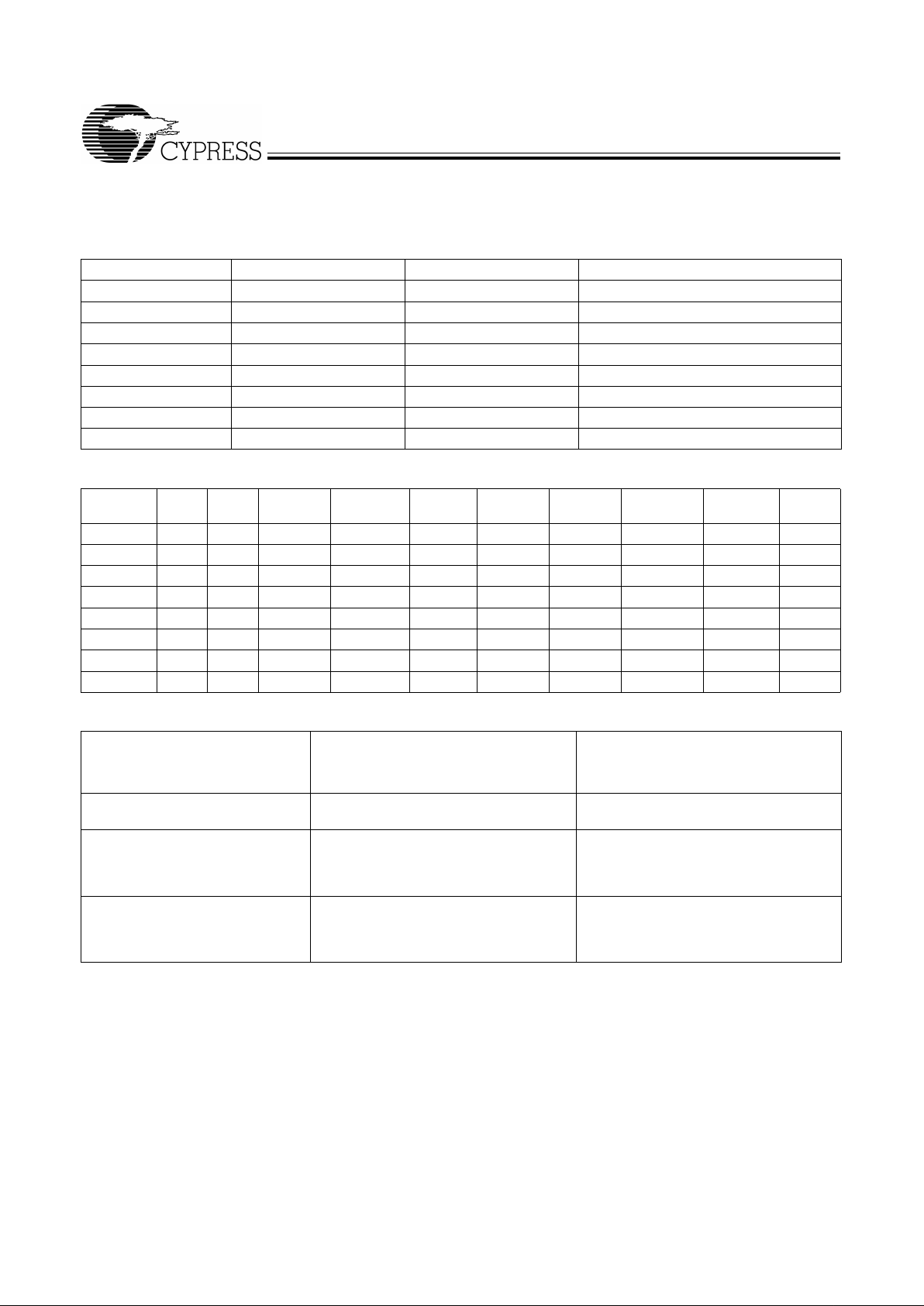

Mode Selection Functions

The W133 supports the following operating mo des controlled through the SEL133/100#, SEL0, and SEL1 inputs.

Notes:

2. Provided for board level “bed of nails” testing.

3. 48-MHz PLL disabled to reduce component jitter.

4. “Normal” mode of operation.

5. TCLK is a test clock over driven on the X1 input during test mode. TCLK mode is based on 133-MHz CPU select logic.

6. Required for DC output impedance verification.

7. Range of reference frequency is min.=14.316, nominal = 14.31818 MHz, max.=14.32 MHz.

8. Frequency accuracy of 48 MHz is +167 PPM to match USB default.

Table 2. Select Functions

SEL133/100# SEL1 SEL0 Function

0 0 0 All Outputs Three-State

00 1(Reserved)

0 1 0 Active 100 MHz, 48 MHz PLL Inactive

0 1 1 Active 100 MHz, 48 MHz PLL Active

1 0 0 Test Mode

10 1(Reserved)

1 1 0 Active 133 MHz, 48 MHz PLL Inactive

1 1 1 Active 133 MHz, 48 MHz PLL Active

Table 3. Truth Table

SEL

133/100# SEL1 SEL0 CPU CPUdiv2 3V66 PCI 48MHz REF IOAPIC Notes

0 0 0 HI-Z HI-Z HI-Z HI-Z HI-Z HI-Z HI-Z 2

0 0 1 n/a n/a n/a n/a n/a n/a n/a

0 1 0 100 MHz 50 MHz 66 MHz 33 MHz HI-Z 14.318 MHz 16.67 MHz 3

0 1 1 100 MHz 50 MHz 66 MHz 33 MHz 48 MHz 14.318 MHz 16.67 MHz 4, 7, 8

1 0 0 TCLK/2 TCLK/4 TCLK/4 TCLK/8 TCLK/2 TCLK TCLK16 5, 6

1 0 1 n/a n/a n/a n/a n/a n/a n/a

1 1 0 133 MHz 66 MHz 66 MHz 33 MHz HI-Z 14.318 MHz 16.67 MHz 3

1 1 1 133 MHz 66 MHz 66 MHz 33 MHz 48 MHz 14.318 MHz 16.67 MHz 4, 7, 8

Table 4. Maximum Supply Current

Condition

Max. 2.5V supply consumption

Max. discrete cap loads,

V

DDQ2

=2.625V

All static inputs=V

DDQ3

or GN D

Max. 3.3V supply consumption

Max. discrete cap loads,

V

DDQ3

=3.465V or GND

Powerdown Mode

(PWRDWN#=0)

100 µA 200 µA

FUll Active 100MHz

SEL133/100#=0

SEL1, 0=11

CPU_STOP#, PCI_STOP#=1

75 mA 160 mA

Full Active 133MHz

SEL133/100#=0

SEL1, 0=11

CPU_STOP#, PCI_STOP#=1

90 mA 160 mA

Loading...

Loading...