Page 1

PSoC 4000 Family

PSoC® 4 Architecture Technical Reference

PSoC 4000 TRM

Manual (TRM)

Document No. 001-89309 Rev. *D

May 31, 2017

Cypress Semiconductor

198 Champion Court

San Jose, CA 95134-1709

Phone (USA): +1.800.858.1810

Phone (Intnl): +1.408.943.2600

www.cypress.com

Page 2

Copyrights

Copyrights

© Cypress Semiconductor Corporation, 2013-2017. This document is the property of Cypress Semiconductor Corporation

and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United

States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property

rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with

Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable

license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code

form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that

are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely

for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software

is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR

IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING,

BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable l aw, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in

this document. Any information provided in this document, inclu ding any sample design info rmation o r progra mming co de, is

provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test

the functionality and safety of any application made of this information and any resulting p roduct. Cypress products are not

designed, intended, or authorized for use as critical components in systems designed o r intended for the operation of we apons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including

resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where

the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical

component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure

of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall a nd

hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress

products. You shall indemnify and hold Cypress harmless from and a gainst all claims, costs, damages, and other liabilities,

including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB,

F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the U ni ted States and other countries. For a more

complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

2 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 3

Contents Overview

Section A: Overview 11

1. Introduction ...................................................................................................................13

2. Getting Started..............................................................................................................17

3. Document Construction .................................................................................................19

Section B: CPU System 23

4. Cortex-M0 CPU .............................................................................................................25

5. Interrupts ......................................................................................................................31

Section C: Memory System 39

6. Memory Map .................................................................................................................41

Section D: System Resources Subsystem (SRSS) 43

7. I/O System ....................................................................................................................45

8. Clocking System............................................................................................................55

9. Power Supply and Monitoring ........................................................................................61

10. Chip Operational Modes ................................................................................................67

11. Power Modes ................................................................................................................69

12. Watchdog Timer ............................................................................................................73

13. Reset System ................................................................................................................77

14. Device Security .............................................................................................................79

Section E: Digital System 81

15. Inter-Integrated Circuit (I2C) ..........................................................................................83

16. Timer, Counter, and PWM...................... .................. ................ ................ ................ ....101

Section F: Analog System 125

17. CapSense ...................................................................................................................127

Section G: Program and Debug 137

18. Program and Debug Interface ....................... ................ .................. ................ ............. 139

19. Nonvolatile Memory Programming ............................................................................... 147

Glossary 161

Index 177

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 3

Page 4

Contents

4 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 5

Contents

Section A: Overview 11

1. Introduction 13

1.1 Top Level Architecture............................................................................................................13

1.2 Features..................................................................................................................................14

1.3 CPU System ...........................................................................................................................14

1.3.1 Processor...............................................................................................................14

1.3.2 Interrupt Controller...... .......................................... .... .......................................... ...14

1.4 Memory...................................................................................................................................15

1.5 System-Wide Resources ........................................................................................................15

1.5.1 Clocking System....................................................................................................15

1.5.2 Power System........................................................................................................15

1.5.3 GPIO......................................................................................................................15

1.6 Fixed-Function Digital............................................ .... ... ... ... ... .... ... ... ... ....................................15

1.6.1 Timer/Counter/PWM Block.....................................................................................15

1.6.2 Serial Communication BlocksI2C Block.................................................................15

1.7 Special Function Peripherals..................................................................................................15

1.7.1 CapSense..............................................................................................................15

1.8 Program and Debug ...............................................................................................................16

2. Getting Started 17

2.1 Support...................................................................................................................................17

2.2 Product Upgrades...................................................................................................................17

2.3 Development Kits....................................................................................................................17

2.4 Application Notes....................................................................................................................17

3. Document Construction 19

3.1 Major Sections........................................................................... ... ... ... .... ... ... ... .......................19

3.2 Documentation Conventions...................................................................................................19

3.2.1 Register Conventions.............................................................................................19

3.2.2 Numeric Naming....................................................................................................19

3.2.3 Units of Measure....................................................................................................20

3.2.4 Acronyms...............................................................................................................20

Section B: CPU System 23

4. Cortex-M0 CPU 25

4.1 Features..................................................................................................................................25

4.2 Block Diagram ........................................................................................................................26

4.3 How It Works ..........................................................................................................................26

4.4 Address Map...........................................................................................................................26

4.5 Registers.................................................................................................................................27

4.6 Operating Modes............. ... ... ... ... .... ... ... ... .... ..........................................................................28

4.7 Instruction Set........................ ... ... .... ... ... ....................................... ... ... .... ... ... ... ... ....................28

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 5

Page 6

Contents

4.7.1 Address Alignment ................................................................................................29

4.7.2 Memory Endianness.......... ... .... ... ... ... .... ... ... ... .... ...................................................29

4.8 Systick Timer...... ... ... ....................................... ... .... ... ... ... .... ...................................... .............29

4.9 Debug.....................................................................................................................................29

5. Interrupts 31

5.1 Features .................................................................................................................................31

5.2 How It Works..........................................................................................................................31

5.3 Interrupts and Exceptions - Operation....................................................................................32

5.3.1 Interrupt/Exception Handling .................................................................................32

5.3.2 Level and Pulse Interrupts.....................................................................................32

5.3.3 Exception Vector Table................ ... ... .... ... ... ..........................................................33

5.4 Exception Sources........................ ... ... ... .... ... ... ....................................... ... ... .... ... ... ... ... ..........33

5.4.1 Reset Exception ....................................................................................................33

5.4.2 Non-Maskable Interrupt (NMI) Exception ................................. ... .... ... ... ................34

5.4.3 HardFault Exception..............................................................................................34

5.4.4 Supervisor Call (SVCall) Exception.......................................................................34

5.4.5 PendSV Exception.................................................................................................34

5.4.6 SysTick Exception .................................................................................................35

5.5 Interrupt Sources....................................................................................................................35

5.6 Exception Priority.......................... ... ... ... .... ... ....................................... ... ... ... .... ... ... ... .............35

5.7 Enabling and Disabling Interrupts...........................................................................................36

5.8 Exception States..................................................................... ... ... ... .... ... ... ... .... ... ... ................36

5.8.1 Pending Exceptions...............................................................................................36

5.9 Stack Usage for Exceptions ...................................................................................................37

5.10 Interrupts and Low-Power Modes...........................................................................................37

5.11 Exceptions – Initialization and Configuration..........................................................................38

5.12 Registers ................................................................................................................................38

5.13 Associated Documents...........................................................................................................38

Section C: Memory System 39

6. Memory Map 41

6.1 Features .................................................................................................................................41

6.2 How It Works..........................................................................................................................41

Section D: System Resources Subsystem (SRSS) 43

7. I/O System 45

7.1 Features .................................................................................................................................45

7.2 GPIO Interface Overview....................... .... ... ... ... ....................................................................45

7.3 I/O Cell Architecture ...............................................................................................................46

7.3.1 Digital Input Buffer............................. ....................................... ... .... ... ... ... ... ..........47

7.3.2 Digital Output Driver . ... ... ... ... .... ... ... .......................................................................48

7.4 High-Speed I/O Matrix...........................................................................................................51

7.5 I/O State on Power Up............................................................................................................51

7.6 Behavior in Low-Power Modes...............................................................................................51

7.7 Interrupt..................................................................................................................................51

7.8 Peripheral Connections..........................................................................................................53

7.8.1 Firmware Controlled GPIO ....................................................................................53

7.8.2 CapSense..............................................................................................................53

7.8.3 Timer, Counter, and Pulse Width Modulator (TCPWM) Block ...............................53

7.9 Registers ................................................................................................................................53

6 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 7

Contents

8. Clocking System 55

8.1 Block Diagram ........................................................................................................................55

8.2 Clock Sources.................. ...................................... .... ... ... ... ... .... ... ..........................................56

8.2.1 Internal Main Oscillator...................... ... .... ... ... ... ... .... ... ... ... .... ... ... ... ... ....................56

8.2.2 Internal Low-speed Oscillator ................................................................................57

8.2.3 External Clock (EXTCLK) ......................................................................................57

8.3 Clock Distribution............................. .......................................................................................57

8.3.1 HFCLK Input Selection ..........................................................................................57

8.3.2 HFCLK Predivider Configuration............................................................................58

8.3.3 SYSCLK Prescaler Configuration..........................................................................58

8.3.4 Peripheral Clock Divider Configuration..................................................................58

8.4 Low-Power Mode Operation.............................................................................................59

8.5 Register List............................................................................................................................59

9. Power Supply and Monitoring 61

9.1 Block Diagram ........................................................................................................................62

9.2 Power Supply Scenarios.........................................................................................................63

9.2.1 Single 1.8 V to 5.5 V Unregulated Supply..............................................................63

9.2.2 Direct 1.71 V to 1.89 V Regulated Supply .............................................................63

9.2.3 VDDIO Supply....................... ... .... ... ... ... .... ... ... .......................................................64

9.3 How It Works ..........................................................................................................................64

9.3.1 Regulator Summary...............................................................................................64

9.4 Voltage Monitoring..................................................................................................................65

9.4.1 Power-On-Reset (POR)............................................ ... ... ... .... ... ... ..........................65

9.5 Register List ...........................................................................................................................65

10. Chip Operational Modes 67

10.1 Boot ........................................................................................................................................67

10.2 User........................................................................................................................................67

10.3 Privileged................................................................................................................................67

10.4 Debug.....................................................................................................................................67

11. Power Modes 69

11.1 Active Mode.................................................................................. ... ... .... ... ... ... ... .... ... .............70

11.2 Sleep Mode.............................................................................................................................70

11.3 Deep-Sleep Mode............................ ... ... ... ..............................................................................70

11.4 Power Mode Summary...........................................................................................................71

11.5 Low-Power Mode Entry and Exit ............................................................................................72

11.6 Register List............................................................................................................................72

12. Watchdog Timer 73

12.1 Features..................................................................................................................................73

12.2 Block Diagram ........................................................................................................................73

12.3 How It Works ..........................................................................................................................73

12.3.1 Enabling and Disabling WDT.................................................................................74

12.3.2 WDT Interrupts and Low-Power Modes.................................................................75

12.3.3 WDT Reset Mode ........................... ... ... .... ... ... ... ... .... ... ... ... .... ... ... ... .......................75

12.4 Register List ..........................................................................................................................75

13. Reset System 77

13.1 Reset Sources........................................................................................................................77

13.1.1 Power-on Reset.....................................................................................................77

13.1.2 Brownout Reset .....................................................................................................77

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 7

Page 8

Contents

13.1.3 Watchdog Reset....................................................................................................77

13.1.4 Software Initiated Reset.........................................................................................78

13.1.5 External Reset.......................................................................................................78

13.1.6 Protection Fault Reset...........................................................................................78

13.2 Identifying Reset Sources.......................................................................................................78

13.3 Register List............................................................................................................................78

14. Device Security 79

14.1 Features .................................................................................................................................79

14.2 How It Works..........................................................................................................................79

14.2.1 Device Security......................................................................................................79

14.2.2 Flash Security........................................................................................................80

Section E: Digital System 81

15. Inter-Integrated Circuit (I2C) 83

15.1 Features .................................................................................................................................83

15.2 General Description .. .... ... ... ... .... ... ............................................................................. ... ..........83

15.2.1 Terms and Definitions............................................................................................84

15.2.2 I2C Modes of Operation ........................................................................................84

15.2.3 Easy I2C (EZI2C) Protocol ....................................................................................86

15.2.4 I2C Registers.........................................................................................................87

15.2.5 I2C Interrupts.........................................................................................................88

15.2.6 Enabling and Initializing the I2C ............................................................................88

15.2.7 Internal and External Clock Operation in I2C ........................... ... .... ... ... ... ... .... ......89

15.2.8 Wake up from Sleep..............................................................................................91

15.2.9 Master Mode Transfer Examples...........................................................................92

15.2.10 Slave Mode Transfer Examples.............................................................................94

15.2.11 EZ Slave Mode Transfer Example.........................................................................96

15.2.12 Multi-Master Mode Transfer Example....................................................................98

16. Timer, Counter, and PWM 101

16.1 Features ...............................................................................................................................101

16.2 Block Diagram......................................................................................................................101

16.2.1 Enabling and Disabling Counter in TCPWM Block......... .... ... ... ... .... ....................102

16.2.2 Clocking...............................................................................................................102

16.2.3 Events Based on Trigger Inputs...........................................................................103

16.2.4 Output Signals.....................................................................................................104

16.2.5 Power Modes.......................................................................................................105

16.3 Modes of Operation..............................................................................................................106

16.3.1 Timer Mode........................................ .... ... ... ... .... ... ... ... ........................................107

16.3.2 Capture Mode........................................................................................... ... .... ... . 110

16.3.3 Quadrature Decoder Mode.................................................................................. 112

16.3.4 Pulse Width Modulation Mode............... ... ... ... .... ... ... ... ... .... ................................. 115

16.3.5 Pulse Width Modulation with Dead Time Mode................................................... 119

16.3.6 Pulse Width Modulation Pseudo-Random Mode............ .... ... ... ... .... ... ... ... ... .... ... .121

16.4 TCPWM Registers................................................................................................................123

Section F: Analog System 125

17. CapSense 127

17.1 Features ...............................................................................................................................127

17.2 Block Diagram......................................................................................................................127

17.3 How It Works........................................................................................................................128

8 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 9

Contents

17.4 CapSense CSD Sensing ......................................................................................................129

17.4.1 GPIO Cell Capacitance to Current Converter........................... ... ... ... .... ... ... ... .... .129

17.4.2 CapSense Clock Generator.................................................................................131

17.4.3 Sigma Delta Converter.........................................................................................131

17.5 CapSense CSD Shielding.....................................................................................................133

17.5.1 CMOD Precharge ................................................................................................134

17.6 General-Purpose Resources: IDACs and Comparator.........................................................135

17.7 Register List..........................................................................................................................135

Section G: Program and Debug 137

18. Program and Debug Interface 139

18.1 Features................................................................................................................................139

18.2 Functional Description........... ... ... .... ... ... ... .... ... ... .......................................... ... ... ..................139

18.3 Serial Wire Debug (SWD) Interface........................... ... ... ... ... .... ... ... ... .... ... ... ... .....................140

18.3.1 SWD Timing Details.............................................................................................141

18.3.2 ACK Details........................... ... .... ... ... ... .... ... ... ... ... .... ... ... .....................................141

18.3.3 Turnaround (Trn) Period Details ..........................................................................141

18.4 Cortex-M0 Debug and Access Port (DAP) ...........................................................................142

18.4.1 Debug Port (DP) Registers..................................................................................142

18.4.2 Access Port (AP) Registers ................................................................................142

18.5 Programming the PSoC 4 Device.........................................................................................143

18.5.1 SWD Port Acquisition...........................................................................................143

18.5.2 SWD Programming Mode Entry......................... ... .......................................... .... .143

18.5.3 SWD Programming Routines Executions ............................................................143

18.6 PSoC 4 SWD Debug Interface .............................................................................................144

18.6.1 Debug Control and Configuration Registers........................................................144

18.6.2 Breakpoint Unit (BPU)..........................................................................................144

18.6.3 Data Watchpoint (DWT).................................. ... ... .... ... ... ... .................................. 144

18.6.4 Debugging the PSoC 4 Device ............................................................................144

18.7 Registers...............................................................................................................................145

19. Nonvolatile Memory Programming 147

19.1 Features................................................................................................................................147

19.2 Functional Description........... ... ... .... ... ... ... .... ... ... .......................................... ... ... ..................147

19.3 System Call Implementation.................................................................................................148

19.4 Blocking and Non-Blocking System Calls.............................................................................148

19.4.1 Performing a System Call....................................................................................148

19.5 System Calls.......................... ....................................... ... ... ... .... ... ... .....................................149

19.5.1 Silicon ID.................................. .... ... ... ... .... ... ... .....................................................149

19.5.2 Configure Clock ...................................................................................................150

19.5.3 Load Flash Bytes......................... ... ... ... .... ... ... ... ... .... ... ... ... .... ..............................151

19.5.4 Write Row ............................................................................................................152

19.5.5 Program Row.......................................................................................................152

19.5.6 Erase All...............................................................................................................153

19.5.7 Checksum............................................................................................................153

19.5.8 Write Protection ...................................................................................................154

19.5.9 Non-Blocking Write Row. .....................................................................................155

19.5.10 Non-Blocking Program Row.................................................................................156

19.5.11 Resume Non-Blocking.........................................................................................157

19.6 System Call Status ...................... .... ... ... ... .... ... ... .......................................... ... ... ..................158

19.7 Non-Blocking System Call Pseudo Code .................. ... ... ... ... .... ... ... ... .... ... ... ... .....................159

Glossary 161

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 9

Page 10

Contents

Index 177

10 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 11

Section A: Overview

This section encompasses the following chapters:

■ Introduction chapter on page 13

■ Getting Started chapter on page 17

■ Document Construction chapter on page 19

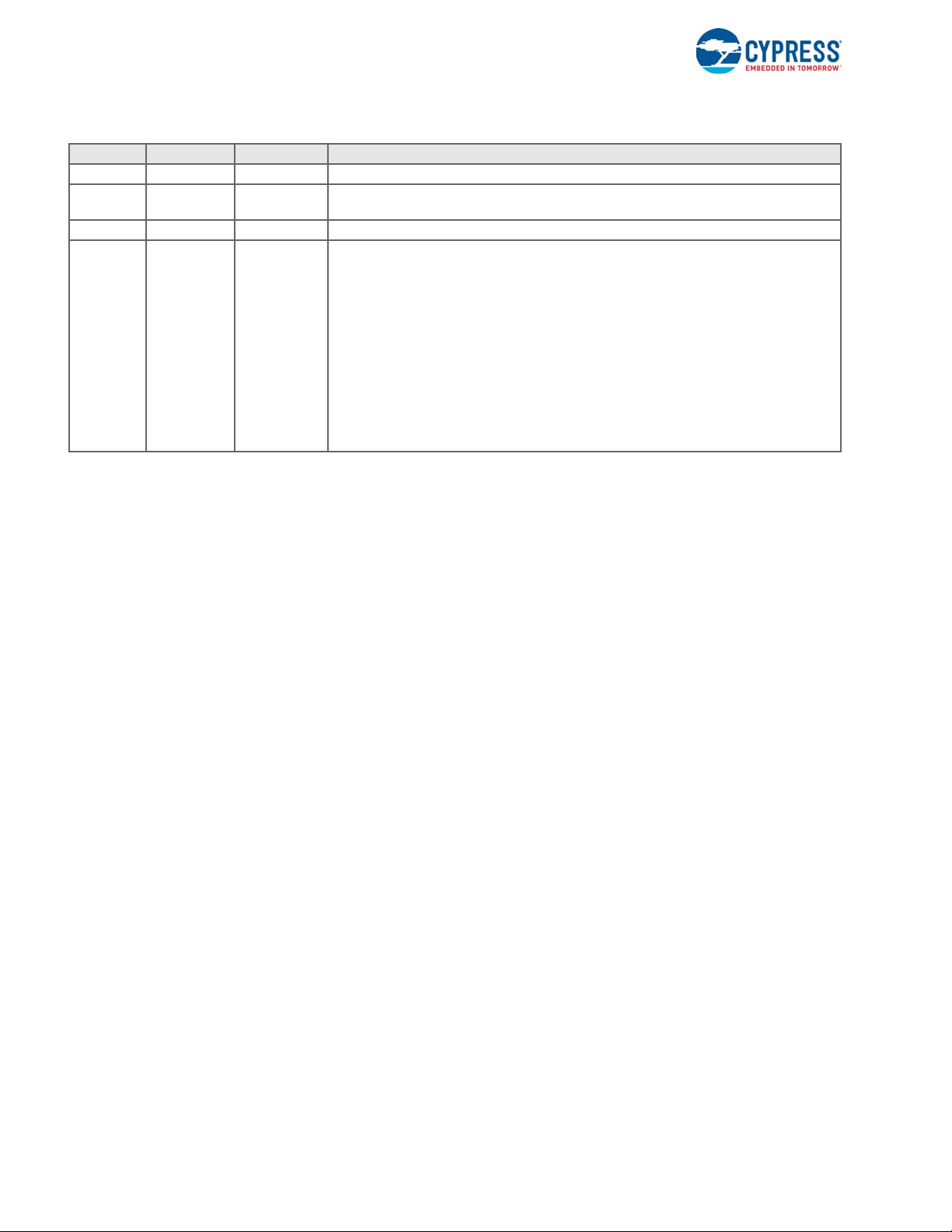

Document Revision History

Revision Issue Date

*A April 15, 2014 NIDH New PSoC 4000 TRM

*B May 09, 2016 MSUR Corrected links to the register TRM.

*C November 09, 2016 NIDH No content update; sunset review

*D May 30, 2017 SHEA Updated logo and copyright information

Origin of

Change

Description of Change

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 11

Page 12

12 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 13

1. Introduction

PSoC®4 is a programmable embedded system controller with an ARM® Cortex®-M0 CPU.CY8C4000 family is the smallest

member of the PSoC 4 family of devices and is upward-compatible with larger members of PSoC 4.

PSoC 4 devices have these characteristics:

■ High-performance, 32-bit single-cycle Cortex-M0 CPU core

■ Capacitive touch sensing (CapSense

■ Configurable Timer/Counter/PWM block

■ Configurable I

■ Low-power operating modes – Sleep and Deep-Sleep

This document describes each functional block of the PSoC 4000 device in detail. This information will help designers to create system-level designs.

2

C block with master, slave, and multi-master operating modes

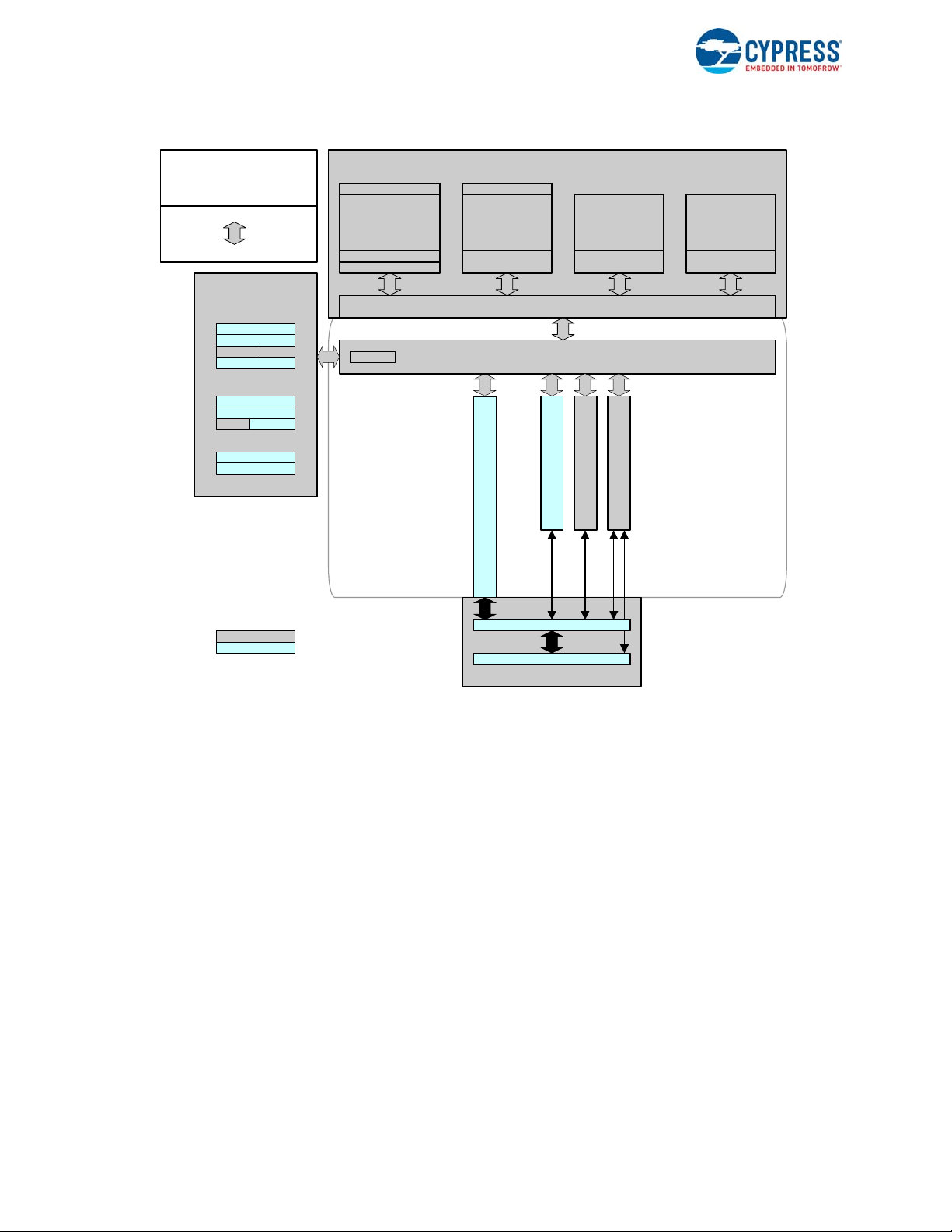

1.1 Top Level Architecture

Figure 1-1 shows the major components of the PSoC 4000 architecture.

®

)

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 13

Page 14

Introduction

Deep Sleep

Active/ Sleep

CPU Subsystem

SRAM

2 KB

SRAM Controller

ROM

4 KB

ROM Controller

Flash

16 KB

Read Accelerator

SPCIFSWD/TC

NVIC, IRQMX

Cortex

M0

16 MHz

MUL

System Interconnect (

Single/Multi Layer AHB

)

I/O Subsystem

20x GPIOs

IOS S GP IO (4x ports )

Peripherals

Peripheral Interconnect (MMIO)

PCLK

PSoC 4000

32-bit

AHB-Lite

System Resources

Lite

Power

Clock

WDT

ILO

Reset

Clock Control

IMO

Sleep Control

PWRSYS

REFPOR

WIC

Reset Control

XRES

1x SCB-I2C

CapSense

High Speed I/O Matrix

Power Modes

1x TCPWM

Figure 1-1. PSoC 4000 Family Block Diagram

1.2 Features

The PSoC 4000 family has these major components:

■ 32-bit Cortex-M0 CPU with single-cycle multiply, deliver-

ing up to 14 DMIPS at 16 MHz

■ Up to 16 KB flash and 2 KB SRAM

■ A center-aligned pulse-width modulator (PWM) with

complementary, dead-band programmable outputs

■ I2C communication block with slave, master, and multi-

master operating modes

■ CapSense

■ Low-power operating modes: Sleep and Deep-Sleep

■ Programming and debugging system through serial wire

debug (SWD)

■ Two current sourcing/sinking DACs (IDACs)

■ Comparator with 1.2 V reference

■ Fully supported by PSoC Creator™ IDE tool

1.3 CPU System

1.3.1 Processor

The heart of the PSoC 4 is a 32-bit Cortex-M0 CPU core

running up to 16 MHz for PSoC 4000. It is optimized for lowpower operation with extensive clock gating. It uses 16-bit

instructions and executes a subset of the Thumb-2 instruction set. This instruction set enables fully compatible binary

upward migration of the code to higher performance processors such as Cortex M3 and M4.

The CPU has a hardware multiplier that provides a 32-bit

result in one cycle.

1.3.2 Interrupt Controller

The CPU subsystem includes a nested vectored interrupt

controller (NVIC) with nine interrupt inputs and a wakeup

interrupt controller (WIC), which can wake the processor

from Deep-Sleep mode.

14 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 15

Introduction

1.4 Memory

The PSoC 4 memory subsystem consists of a 16 KB flash

module with a flash accelerator, 2 KB SRAM, and 4 KB

supervisory ROM options. The flash accelerator improves

the average access times from the flash block delivering

85 percent of single-cycle SRAM access performance. A

powerful and flexible protection model allows you to selectively lock blocks of memory for read and write protection,

securing sensitive information. Additionally, all device interfaces can be permanently disabled for applications concerned about phishing attacks due to a maliciously

reprogrammed device or attempts to defeat security by

starting and interrupting flash programming sequences. The

supervisory ROM is used to store the boot and configuration

routines.

1.5 System-Wide Resources

1.5.1 Clocking System

The clocking system for the PSoC 4 device consists of the

internal main oscillator (IMO) and internal low-speed oscillator (ILO) as internal clocks and has provision for an external

clock.

The system clock (SYSCLK) required for the CPU system

and the high-frequency clock (HFCLK) required by the

peripherals can be as high as 16 MHz. These clocks are

generated from the IMO.

The IMO with an accuracy of ±2 percent is the primary

source of internal clocking in the device. The default IMO

frequency is 24 MHz and it can be adjusted between 3 MHz

and 48 MHz in steps of 1 MHz. The default IMO frequency is

24 MHz and can be adjusted between 24 MHz and 48 MHz

in steps of 4 MHz. Multiple clock derivatives are generated

from the main clock frequency to meet various application

needs.

The ILO is a low-power, less accurate oscillator and is used

to generate clocks for peripheral operation in Deep-Sleep

mode. Its clock frequency is 32 kHz with ±60 percent accuracy.

An external clock source ranging from MHz to 16 MHz can

be used to generate the clock derivatives for the functiona l

blocks instead of the IMO.

frequency clock is ON and the low-frequency peripherals

are in operation.

Multiple internal regulators are available in the system to

support power supply schemes in different power modes.

1.5.3 GPIO

Every GPIO in PSoC 4 has the following characteristics:

■ Eight drive strength modes

■ Individual control of input and output disables

■ Hold mode for latching previous state

■ Selectable slew rates

■ Interrupt generation – edge triggered

The PSoC 4 also supports CapSense capability on 17 out of

20 GPIOs. The pins are organized in a port that is 8-bit wide.

A high-speed I/O matrix is used to multiplex between various signals that may connect to an I/O pin. Pin locations for

fixed-function peripherals are also fixed.

1.6 Fixed-Function Digital

1.6.1 Timer/Counter/PWM Block

The Timer/Counter/PWM block consists of a 16-bit counter

with user-programmable period length. The TCPWM block

has a capture register, period register, and compare register .

The block supports complementary, dead-band programmable outputs. It also has a kill input to force outputs to a predetermined state. Other features of the block include centeraligned PWM, clock prescaling, pseudo random PWM, and

quadrature decoding.

1.6.2 Serial Communication BlocksI2C Block

The PSoC 4 has a fixed-function I2C interface. The I2C

interface can be used for general-purpose I2C communication and for tuning the CapSense component fo r optimized

operation.

The features of the I2C block include:

■ Standard I

■ EZ function mode support with 32-byte buffer

2

C multi-master and slave function

1.5.2 Power System

The PSoC 4 operates with a single external supply in the

range 1.71 V to 5.5 V.

PSoC 4 has two low-power modes – Sleep and Deep-Sleep

– in addition to the default Active mode. In Active mode, the

CPU runs with all the logic powered. In Sleep mode, the

CPU is powered off with all other peripherals functional. In

Deep-Sleep mode, the CPU, SRAM, and high-speed logic

are in retention; the main system clock is OFF while the low-

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 15

1.7 Special Function Peripherals

1.7.1 CapSense

PSoC 4 devices have the CapSense feature, which allows

you to use the capacitive properties of your fingers to toggle

buttons and sliders. CapSense functionality is su pported on

all but three GPIO pins in PSoC 4 through a CapSense

Sigma-Delta (CSD) block. The CSD also provides waterproofing capability.

Page 16

Introduction

1.7.1.1 IDACs and Comparator

The CapSense block has two IDACs and a comparator with

a 12-V reference, which can be used for general purposes, if

CapSense is not used.

1.8 Program and Debug

PSoC 4 devices support programming and debugging features of the device via the on-chip SWD interface. The PSoC

Creator IDE provides fully integrated programming and

debugging support. The SWD interface is also fully compatible with industry standard third-party tools.

16 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 17

2. Getting S tarted

2.1 Support

Free support for PSoC®4 products is available online at www.cypress.com/psoc4. Resources include training seminars,

discussion forums, application notes, PSoC consultants, CRM technical support email, knowledge base, and application

support engineers.

For application assistance, visit www.cypress.com/support/ or call 1-800-541-4736.

2.2 Product Upgrades

Cypress provides scheduled upgrades and version enhancements for PSoC C reator free of charge. Upgrades a re available

from your distributor on DVD-ROM; you can also download them directly from www.cypress.com/psoccreator. Critical updates

to system documentation are also provided in the Documentation section.

2.3 Development Kits

The Cypress Online Store contains development kits, C compilers, and the accessories you need to successfully develop

PSoC projects. Visit the Cypress Online Store website at www.cypress.com/cypress-store. Under Products, click Program-

mable System-on-Chip to view a list of available items. Development kits are also available from Digi-Key, Avnet, Arrow, and

Future.

2.4 Application Notes

Refer to application note AN79953 - Getting Started with PSoC 4 for additional information on PSoC 4 device capabilities and

to quickly create a simple PSoC application using PSoC Creator and PSoC 4 development kits.

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 17

Page 18

Getting Started

18 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 19

3. Document Construction

This document includes the following sections:

■ Section B: CPU System on page 23

■ Section D: System Resources Subsystem (SRSS) on page 43

■ Section E: Digital System on page 81

■ Section F: Analog System on page 125

■ Section G: Program and Debug on page 137

3.1 Major Sections

For ease of use, information is organized into sections and chapters that are divided according to device functionality.

■ Section – Presents the top-level architecture, how to get started, and conventions and overview information of the prod-

uct.

■ Chapter – Presents the chapters specific to an individual aspect of the section topic. These are the detailed implementa-

tion and use information for some aspect of the integrated circuit.

■ Glossary – Defines the specialized terminology used in this technical reference manual (TRM). Glossary terms are pre-

sented in bold, italic font throughout.

■ Registers Technical Reference Manual – Supplies all device register details summarized in the technical reference man-

ual. This is an additional document.

3.2 Documentation Conventions

This document uses only four distinguishing font types, besides those found in the headings.

■ The first is the use of italics when referencing a document title or file name.

■ The second is the use of bold italics when referencing a term described in the Glossary of this document.

■ The third is the use of Times New Roman font, distinguishing equation examples.

■ The fourth is the use of Courier New font, distinguishing code examples.

3.2.1 Register Conventions

Register conventions are detailed in the PSoC 4000 Family: PSoC 4 Registers TRM.

3.2.2 Numeric Naming

Hexadecimal numbers are represented with all letters in u ppercase with an appended lowercase ‘h’ (for example, ‘14h’ or

‘3Ah’) and hexadecimal numbers may also be represented by a ‘0x’ prefix, the C coding convention. Binary numbers have an

appended lowercase ‘b’ (for example, 01010100b’ or ‘01000011b’). Numbers not indicated by an ‘h’ or ‘b’ are decimal.

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 19

Page 20

Document Construction

3.2.3 Units of Measure

This table lists the units of measure used in this document.

Table 3-1. Units of Measure

Abbreviation Unit of Measure

bps bits per second

°C degrees Celsius

dB decibels

fF femtofarads

Hz Hertz

k kilo, 1000

K kilo, 2^10

KB 1024 bytes, or approximately one thousand bytes

Kbit 1024 bits

kHz kilohertz (32.000)

k kilohms

MHz megahertz

M megaohms

µA microamperes

µF microfarads

µs microseconds

µV microvolts

µVrms microvolts root-mean-square

mA milliamperes

ms milliseconds

mV millivolts

nA nanoamperes

ns nanoseconds

nV nanovolts

ohms

pF picofarads

pp peak-to-peak

ppm parts per million

SPS samples per second

sigma: one standard deviation

V volts

3.2.4 Acronyms

This table lists the acronyms used in this document

Table 3-2. Acronyms

Acronym Definition

ABUS analog output bus

AC alternating current

ADC analog-to-digital converter

AHB

API application programming interface

AMBA (advanced microcontroller bus architecture)

high-performance bus, an ARM data transfer bus

Table 3-2. Acronyms (continued)

Acronym Definition

APOR analog power-on reset

BC broadcast clock

BOD brownout detect

BOM bill of materials

BR bit rate

BRA bus request acknowledge

BRQ bus request

CAN controller area network

CI carry in

CMP compare

CO carry out

CPU central processing unit

CRC cyclic redundancy check

CSD CapSense sigma delta

CT continuous time

CTB continuous time block

CTBm continuous time block mini

DAC digital-to-analog converter

DAP debug access port

DC direct current

DI digital or data input

DMA direct memory access

DNL differential nonlinearity

DO digital or data output

DSI digital signal interface

DSM deep-sleep mode

DW data wire

ECO external crystal oscillator

EEPROM

EMIF external memory interface

FB feedback

FIFO first in first out

FSR full scale range

GPIO general purpose I/O

HCI host-controller interface

HFCLK high-frequency clock

HSIOM high-speed I/O matrix

I2C

IDE integrated development environment

ILO internal low-speed oscillator

ITO indium tin oxide

IMO internal main oscillator

INL integral nonlinearity

I/O input/output

IOR I/O read

IOW I/O write

electrically erasable programmable read only

memory

inter-integrated circuit

20 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 21

Document Construction

Table 3-2. Acronyms (continued)

Acronym Definition

IRES initial power on reset

IRA interrupt request acknowledge

IRQ interrupt request

ISR interrupt service routine

IVR interrupt vector read

LCD liquid crystal display

LFCLK low-frequency clock

LPCOMP low-power comparator

LRb last received bit

LRB last received byte

LSb least significant bit

LSB least significant byte

LUT lookup table

MISO master-in-slave-out

MMIO memory mapped input/output

MOSI master-out-slave-in

MSb most significant bit

MSB most significant byte

NMI non-maskable interrupt

NVIC nested vectored interrupt controller

PC program counter

PCB printed circuit board

PCH program counter high

PCL program counter low

PD power down

PGA programmable gain amplifier

PM power management

PMA PSoC memory arbiter

POR power-on reset

PPOR precision power-on reset

PRS pseudo random sequence

®

PSoC

PSRR power supply rejection ratio

PSSDC power system sleep duty cycle

PWM pulse width modulator

RAM random-access memory

RETI return from interrupt

RF radio frequency

ROM read only memory

RMS root mean square

RW read/write

SAR successive approximation register

SC switched capacitor

SCB serial communication block

SIE serial interface engine

SIO special I/O

SE0 single-ended zero

Programmable System-on-Chip

Table 3-2. Acronyms (continued)

Acronym Definition

SNR signal-to-noise ratio

SOF start of frame

SOI start of instruction

SP stack pointer

SPD sequential phase detector

SPI serial peripheral interconnect

SPIM serial peripheral interconnect master

SPIS serial peripheral interconnect slave

SRAM static random-access memory

SROM supervisory read only memory

SSADC single slope ADC

SSC supervisory system call

SYSCLK system clock

SWD single wire debug

TC terminal count

TCPWM timer, counter, PWM

TD transaction descriptors

UART universal asynchronous receiver/transmitter

UDB universal digital block

USB universal serial bus

USBIO USB I/O

WCO watch crystal oscillator

WDT watchdog timer

WDR watchdog reset

XRES external reset

XRES_N external reset, active low

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 21

Page 22

Document Construction

22 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 23

Section B: CPU System

SWD/TC

Cortex-M0

16 MHz (14 DMIPS)

NVIC, IRQMX

System Interconnect (Single Layer AHB)

This section encompasses the following chapters:

■ Cortex-M0 CPU chapter on page 25

■ Interrupt schapter on page 31

Top Level Architecture

CPU System Block Diagram

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 23

Page 24

24 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 25

4. Cortex-M0 CPU

The PSoC® 4 ARM Cortex-M0 core is a 32-bit CPU optimized for low-power operation. It has an efficient three-stage pipeline,

a fixed 4-GB memory map, and supports the ARMv6-M Thumb instruction set. The Cortex-M0 also features a single-cycle 32bit multiply instruction and low-latency interrupt handling. Other subsystems tightly linked to the CPU core include a nested

vectored interrupt controller (NVIC), a SYSTICK timer, and debug.

This section gives an overview of the Cortex-M0 processor. For more details, see the ARM Cortex-M0 user guide or technical

reference manual, both available at www.arm.com.

4.1 Features

The PSoC 4 Cortex-M0 has the following features:

■ Easy to use, program, and debug, ensuring easier migration from 8- and 16-bit processors

■ Operates at up to 0.9 DMIPS/MHz; this helps to increase execution speed or reduce power

■ Supports the Thumb instruction set for improved code density, ensuring efficient use of memory

■ NVIC unit to support interrupts and exceptions for rapid and deterministic interrupt response

■ Extensive debug support including:

❐ SWD port

❐ Breakpoints

❐ Watchpoints

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 25

Page 26

Cortex-M0 CPU

ARM Cortex-M0 CPU

Sys te m I nte rco nne c t

Flash

Accelerator

SRAM

Controller

SROM

Controller

DAP

CPU Subsystem

Flash SRAM SROM

AHB Br idge

Test

Controller

Fixed In t er r up t s

DS I Inter rupts

Flash

Programming

Interface

CPU & Memory

Subsystem

Interrupt

MUX

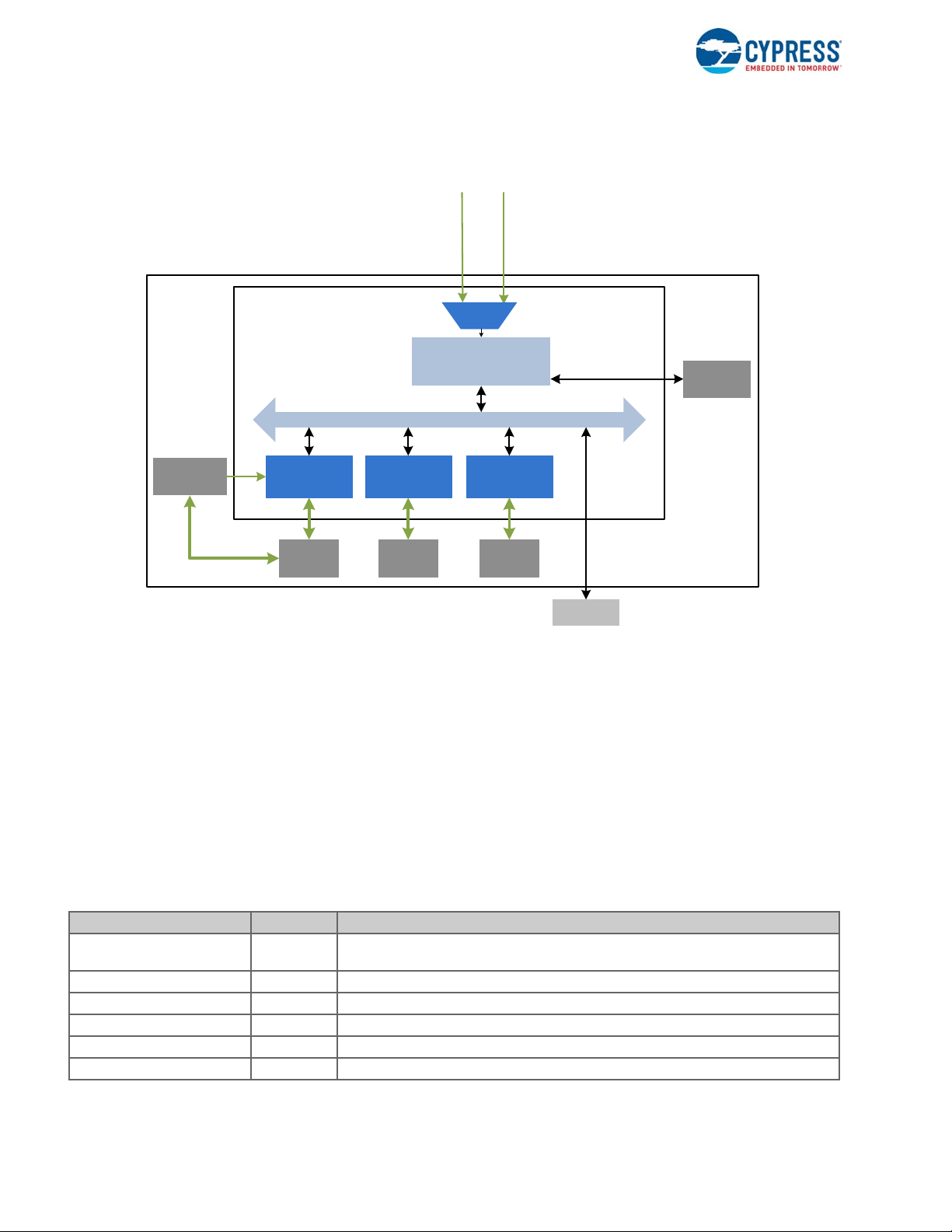

4.2 Block Diagram

Figure 4-1. PSoC 4 CPU Subsystem Block Diagram

4.3 How It Works

The Cortex-M0 is a 32-bit processor with a 32-bit data path, 32-bit registers, and a 32-bit memory interf ace. It supports most

16-bit instructions in the Thumb instruction set and some 32-bit instructions in the Thumb-2 instruction set.

The processor supports two operating modes (see “Operating Modes” on page 28). It has a single-cycle 32-bit multiplication

instruction.

4.4 Address Map

The ARM Cortex-M0 has a fixed address map allowing access t o memory and peripherals using simple memory access

instructions. The 32-bit (4 GB) address space is divided into the regions show n in Table 4-1. Note that code can be executed

from the code and SRAM regions.

Table 4-1. Cortex-M0 Address Map

Address Range Name Use

0x00000000 - 0x1FFFFFFF Code

0x20000000 - 0x3FFFFFFF SRAM Data region. You can also execute code from this region.

0x40000000 - 0x5FFFFFFF Peripheral All peripheral registers. You cannot execute code from this region.

0x60000000 - 0xDFFFFFFF Not used.

0xE0000000 - 0xE00FFFFF PPB Peripheral registers within the CPU core.

0xE0100000 - 0xFFFFFFFF Device PSoC 4 implementation-specific.

Program code region. You can also place data here. Includes the exception vector table,

which starts at address 0.

26 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 27

Cortex-M0 CPU

4.5 Registers

The Cortex-M0 has 16 32-bit registers, as Table 4-2 shows:

■ R0 to R12 – General-purpose registers. R0 to R7 can be accessed by all instructions; the other registers can be accessed

by a subset of the instructions.

■ R13 – Stack pointer (SP). There are two stack pointers, with only one available at a t i me. In th re ad mode, the CONTROL

register indicates the stack pointer to use, Main Stack Pointer (MSP) or Process Stack Pointer (PSP).

■ R14 – Link register. Stores the return program counter during function calls.

■ R15 – Program count er. This register can be written to contro l program flow.

Table 4-2. Cortex-M0 Registers

Name

R0-R12 RW Undefined R0-R12 are 32-bit general-purpose registers for data operations.

MSP (R13)

PSP (R13)

LR (R14) RW Undefined

PC (R15) RW [0x00000004]

PSR RW Undefined

APSR RW Undefined

EPSR RO [0x00000004].0 On reset, EPSR is loaded with the value bit[0] of the register [0x00000004].

IPSR RO 0 The IPSR contains the exception number of the current ISR.

PRIMASK RW 0 The PRIMASK register prevents activation of all exceptions with configurable priority.

CONTROL RW 0 The CONTROL register controls the stack used when the processor is in thread mode.

a. Describes access type during program execution in thread mode and handler mode. Debug access can differ.

a

Type

RW [0x00000000]

Reset Value Description

The stack pointer (SP) is register R13. In thread mode, bit[1] of the CONTROL register

indicates which stack pointer to use:

0 = Main stack pointer (MSP). This is the reset value.

1 = Process stack pointer (PSP).

On reset, the processor loads the MSP with the value from address 0x00000000.

The link register (LR) is register R14. It stores the return information for subroutines,

function calls, and exceptions.

The program counter (PC) is register R15. It contains the current program address. On

reset, the processor loads the PC with the value from address 0x00000004. Bit[0] of the

value is loaded into the EPSR T-bit at reset and must be 1.

The program status register (PSR) combines:

Application Program Status Register (APSR).

Execution Program Status Register (EPSR).

Interrupt Program Status Register (IPSR).

The APSR contains the current state of the condition flags from previous instruction

executions.

Table 4-3 shows how the PSR bits are assigned.

Table 4-3. Cortex-M0 PSR Bit Assignments

Bit PSR Register Name Usage

31 APSR N Negative flag

30 APSR Z Zero flag

29 APSR C Carry or borrow flag

28 APSR V Overflow flag

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 27

Page 28

Cortex-M0 CPU

Table 4-3. Cortex-M0 PSR Bit Assignments

Bit PSR Register Name Usage

27 – 25 – – Reserved

24 EPSR T

23 – 6 – – Reserved

5 – 0 IPSR N/A

Thumb state bit. Must always be 1. Attempting to execute instructions when the T bit is 0

results in a HardFault exception.

Exception number of current ISR:

0 = thread mode

1 = reserved

2 = NMI

3 = HardFault

4 – 10 = reserved

11 = SVCall

12, 13 = reserved

14 = PendSV

15 = SysTick

16 = IRQ0

…

24 = IRQ8

Use the MSR or CPS instruction to set or clear bit 0 of th e PRIM ASK regi ster. If the bit is 0, exceptions are enabled. If the bit

is 1, all exceptions with configurable priority, that is, all exceptions except HardFault, NMI, and Reset, are disabled. See th e

Interrupts chapter on page 31 for a list of exceptions.

4.6 Operating Modes

The Cortex-M0 processor supports two operating modes:

■ Thread Mode – used by all normal applications. In this mode, the MSP or PSP can be used. The CONTROL register bit 1

determines which stack pointer is used:

❐ 0 = MSP is the current stack pointer

❐ 1 = PSP is the current stack pointer

■ Handler Mode – used to execute exception handlers. The MSP is always used.

In thread mode, use the MSR instruction to set the stack pointer bit in the CONTROL register. When changing the stack

pointer, use an ISB instruction immediately after the MSR instruction. This ensures that instructions after the ISB execute

using the new stack pointer.

In handler mode, explicit writes to the CONTROL register are ignored, because the MSP is always used. The exception entry

and return mechanisms automatically update the CONTROL register.

4.7 Instruction Set

The Cortex-M0 implements a version of the Thumb instruction set, as Table4-4 shows. For details, see the Cortex-M0

Generic User Guide.

An instruction operand can be an ARM register, a constant, or another instruction-specific parameter. Instructions act on the

operands and often store the result in a destinat ion register. Many instructions a re unable to use, or have restrictions on

using, the PC or SP for the operands or destination register.

28 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 29

Cortex-M0 CPU

Table 4-4. Thumb Instruction Set

Mnemonic Brief Description

ADCS Add with carry

a

ADD{S}

ADR PC-relative address to register

ANDS Bit wise AND

ASRS Arithmetic shift right

B{cc} Branch {conditionally}

BICS Bit clear

BKPT Breakpoint

BL Branch with link

BLX Branch indirect with link

BX Branch indirect

CMN Compare negative

CMP Compare

CPSID Change processor state, disable interrupts

CPSIE Change processor state, enable interrupts

DMB Data memory barrier

DSB Data synchronization barrier

EORS Exclusive OR

ISB Instruction synchronization barrier

LDM Load multiple registers, increment after

LDR Load register from PC-relative address

LDRB Load register with word

LDRH Load register with half-word

LDRSB Load register with signed byte

LDRSH Load register with signed half-word

LSLS Logical shift left

LSRS Logical shift right

a

MOV{S}

MRS Move to general register from special register

MSR Move to special register from general register

MULS Multiply, 32-bit result

MVNS Bit wise NOT

NOP No operation

ORRS Logical OR

POP Pop registers from stack

PUSH Push registers onto stack

REV Byte-reverse word

REV16 Byte-reverse packed half-words

REVSH Byte-reverse signed half-word

RORS Rotate right

RSBS Reverse subtract

SBCS Subtract with carry

Add

Move

Table 4-4. Thumb Instruction Set

Mnemonic Brief Description

SEV Send event

STM Store multiple registers, increment after

STR Store register as word

STRB Store register as byte

STRH Store register as half-word

a

SUB{S}

SVC Supervisor call

SXTB Sign extend byte

SXTH Sign extend half-word

TST Logical AND-based test

UXTB Zero extend a byte

UXTH Zero extend a half-word

WFE Wait for event

WFI Wait for interrupt

a. The ‘S’ qualifier causes the ADD, SUB, or MOV instructions to update

APSR condition flags.

Subtract

4.7.1 Address Alignment

An aligned access is an operation where a word-aligned

address is used for a word or multiple word access, or

where a half-word-aligned address is used for a half-word

access. Byte accesses are always aligned.

No support is provided for unaligned accesses on the Cortex-M0 processor. Any attempt to perform an unaligned

memory access operation results in a HardFault exception.

4.7.2 Memory Endianness

The PSoC 4 Cortex-M0 uses the little-endian forma t, where

the least-significant byte of a word is stored at the lowest

address and the most significant byte is stored at the hi ghest address.

4.8 Systick Timer

The Systick timer is integrated with the NVIC and ge nerates

the SYSTICK interrupt. This interrupt can be used for task

management in a real-time system. The timer has a reload

register with 24 bits available to use as a countdown value.

The Systick timer uses the Cortex-M0 internal clock as a

source.

4.9 Debug

PSoC 4 contains a debug interface based on SWD; it features four breakpoint (address) comparators and two watchpoint (data) comparators.

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 29

Page 30

Cortex-M0 CPU

30 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 31

5. Interrupts

Nested

Vectored

Interrupt

Controller

(NVIC)

Cortex-M0

Processor Core

IRQ0

Cortex-M0 Processor

IRQ1

IRQ8

Interrupt signals

from PSoC 4

on-chip peripherals

The ARM Cortex-M0 (CM0) CPU in PSoC® 4 supports interrupts and exceptions. Interrupts refer to those events generated

by peripherals external to the CPU such as timers, serial communication block, and port pin signals. Exceptions refer to those

events that are generated by the CPU such as memory access faults and internal system timer events. Both interrupts and

exceptions result in the current program flow being stopped and the exception handler or interrupt service routine (ISR) being

executed by the CPU. The device provides a unified exception vector table for both interrupt handlers/ISR and exception handlers.

5.1 Features

PSoC 4 supports the following interrupt features:

■ Supports 9 interrupts

■ Nested vectored interrupt controller (NVIC) integrated with CPU core, yielding low interrupt latency

■ Vector table may be placed in either flash or SRAM

■ Configurable priority levels from 0 to 3 for each interrupt

■ Level-triggered and pulse-triggered interrupt signals

5.2 How It Works

Figure 5-1. PSoC 4 Interrupts Block Diagram

Figure 5-1 shows the interacti on between interrupt sign als and the Cortex-M0 CPU. PSoC 4 h as nine inte rrupts; these inter-

rupt signals are processed by the NVIC. The NVIC takes care of enabling/disabling individual inte rrupts, priority resolution,

and communication with the CPU core. The except ions are not shown in Figure 5-1 because they are part of CM0 core generated events, unlike interrupts, which are generated by peripherals external to the CPU.

PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D 31

Page 32

Interrupts

Rising Edge on Interrupt Line is

registered by the NVIC

CPU detects the request signal

from NVIC and stores its

current context by pushing

conte nts onto the stack

CPU receives exception

number of triggered interrupt

and fetches the address of the

specific exception handle from

vector table.

CPU branches to the received

address and executes

exception handler

CPU registers are restored

using stack upon completion of

exception handler.

IRQn

CPU

Execution

State

main

ISR ISR

main

ISR

main

IRQn is still high

IRQn

CPU

Execution

State

main

ISR

main

ISR

main

ISR

5.3 Interrupts and Exceptions Operation

5.3.1 Interrupt/Exception Handling

The following sequence of events occurs when an interrupt

or exception event is triggered:

1. Assuming that all the interrupt signals are initially low

(idle or inactive state) and the processor is executing the

main code, a rising edge on any one of the interrupt lines

is registered by the NVIC. The interrupt line is now in a

pending state waiting to be serviced by the CPU.

2. On detecting the interrupt request signal from the NVIC,

the CPU stores its current context by pushing the contents of the CPU registers onto the stack.

3. The CPU also receives the exception number of the trig-

gered interrupt from the NVIC. All interrupts and exceptions have a unique exception number, as given in

Table 5-1. By using this exception number, the CPU

fetches the address of the specific exception handler

from the vector table.

4. The CPU then branches to this address and executes

the exception handler that follows.

5. Upon completion of the exception handler, the CPU reg-

isters are restored to their original state using stack pop

operations; the CPU resumes the main code execution.

Figure 5-2. Interrupt Handling When Triggered

When the NVIC receives an interrupt request while another

interrupt is being serviced or receives multiple interrupt

requests at the same time, it evaluates the priority of all

these interrupts, sending the exception number of the hig hest priority interrupt to the CPU. Thus, a higher priority interrupt can block the execution of a lower priority ISR at any

time.

Exceptions are handled in the same way that interrupts are

handled. Each exception event has a unique exception number, which is used by the CPU to execute the appropriate

exception handler.

5.3.2 Level and Pulse Interrupts

NVIC supports both level and pulse signals on the interrupt

lines (IRQ0 to IRQ8). The classification of an interrupt as

level or pulse is based on the interrupt source.

Figure 5-3. Level Interrupts

Figure 5-4. Pulse Interrupts

Figure 5-3 and Figure 5-4 show the working of level and

pulse interrupts, respectively. Assuming the interrupt signal

is initially inactive (logic low), the following sequence of

events explains the handling of level and pulse interrupts:

1. On a rising edge event of the interrupt signal, the NVIC

registers the interrupt request. The interrupt is now in the

pending state, which means the interrupt requests have

not yet been serviced by the CPU.

2. The NVIC then sends the exception number along with

the interrupt request signal to the CPU. When the CPU

starts executing the ISR, the pending state of the interrupt is cleared.

3. When the ISR is being executed by the CPU, one or

more rising edges of the interrupt signal are logged as a

single pending request. The pending interrupt is serviced

again after the current ISR exe cu ti o n is complete (see

Figure 5-4 for pulse interrupts).

4. If the interrupt signal is still high after completing the ISR,

it will be pending and the ISR is executed again.

Figure 5-3 illustrates this for level triggered interrupts,

where the ISR is executed as long as the interrupt signal

is high.

32 PSoC 4000 Family: PSoC 4 Architecture TRM, Document No. 001-89309 Rev. *D

Page 33

Interrupts

5.3.3 Exception Vector Table

The exception vector table (Table 5-1), stores t he entry point addresses for all exception handlers. The CPU fetches the

appropriate address based on the exception number.

Table 5-1. Exception Vector Table

Exception Number Exception Exception Priority Vector Address

– Initial Stack Pointer Value Not applicable (NA)

1 Reset –3, the highest priority Base_Address + 0x04

2 Non Maskable Interrupt (NMI) –2 Base_Address + 0x08

3 HardFault –1 Base_Address + 0x0C

4-10 Reserved NA Base_Address + 0x10 to Base_Address + 0x28

11 Supervisory Call (SVCall) Configurable (0 - 3) Base_Address + 0x2C

12-13 Reserved NA Base_Address + 0x30 to Base_Address + 0x34

14 PendSupervisory (PendSV) Configurable (0 - 3) Base_Address + 0x38

15 System Timer (SysTick) Configurable (0 - 3) Base_Address + 0x3C

16 External Interrupt(IRQ0) Configurable (0 - 3) Base_Address + 0x40

… … Configurable (0 - 3) …

24 External Interrupt(IRQ8) Configurable (0 - 3) Base_Address + 0x52

Base_Address - 0x00000000 (start of flash memory) or

0x20000000 (start of SRAM)

In Table 5-1, the first word (4 bytes) is not marked as excep-

tion number zero. This is because the first word in the

exception table is used to initialize the main stack pointer

(MSP) value on device reset; it is not considered as an

exception. In PSoC 4, the vector table can be configured t o

be located either in flash memory (base address of

0x00000000) or SRAM (base address of 0x20000000). This

configuration is done by writing to the VECT_IN_RAM bit

field (bit 0) in the CPUSS_CONFIG register. When the

VECT_IN_RAM bit field is ‘1’, CPU fetches exception handler addresses from the SRAM vector table location. When

this bit field is ‘0’ (reset state), the vector table in flash memory is used for exception address fetches. You must set the

VECT_IN_RAM bit field as part of the device boot code to

configure the vector table to be in SRAM. The advantage of

moving the vector table to SRAM is that the exception handler addresses can be dynamically changed by modifying

the SRAM vector table contents. However, the nonvolatile

flash memory vector table must be modified by a flash memory write.

Reads of flash addresses 0x00000000 and 0x00000004 are

redirected to the first eight bytes of SROM to fe tch the stack

pointer and reset vectors, unless the NO_RST_OVR bit of

the CPUSS_SYSREQ register is set. To allow flash read

from addresses 0x00000000 and 0x00000004, the

NO_RST_OVR bit should be set to ‘1’. The stack pointer

vector holds the address that the stack pointer is loaded with

on reset. The reset vector holds the address of the boot

sequence. This mapping is done to use the default

addresses for the stack pointer and reset vector from SROM

when the device reset is released. For reset, boot code in

SROM is executed first and then the CPU j umps to address

0x00000004 in flash to execute the handler in flash. The

reset exception address in the SRAM vector table is never

used because VECT_IN_RAM is 0 on reset.

Also, when the SYSREQ bit of the CPUSS_SYSREQ register is set, reads of flash address 0x00000008 are redirected

to SROM to fetch the NMI vector address instead of from

flash. Reset CPUSS_SYSREQ to read the flash at address

0x00000008.

The exception sources (exception numbers 1 to 15) are

explained in 5.4 Exception Sources. The exceptions marked

as Reserved in Table 5-1 are not used, although they have