Page 1

EZ-USB® FX3™ Technical Reference Manual

Document Number: 001-76074 Rev. *F

May 9, 2019

Cypress Semiconductor

198 Champion Court

San Jose, CA 95134-1709

www.cypress.com

Page 2

Copyrights

Copyrights

© Cypress Semiconductor Corporation, 2012-2019. This document is the property of Cypress Semiconductor Corporation

and its subsidiaries (“Cypress”). This document, including any software or firmware included or referenced in this document

(“Software”), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries

worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not

accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of

the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce

the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the

Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for

use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software

(as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware

products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR

IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING,

BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress shall have no liability arising out of any security breach, such as unauthorized access to

or use of a Cypress product. CYPRESS DOES NOT REPRESENT, WARRANT, OR GUARANTEE THAT CYPRESS PRODUCTS, OR SYSTEMS CREATED USING CYPRESS PRODUCTS, WILL BE FREE FROM CORRUPTION, ATTACK,

VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION (collectively, "Security Breach").Cypress disclaims any liability relating to any Security Breach, and you shall and hereby do release Cypress

from any claim, damage, or other liability arising from any Security Breach. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further

notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this

document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the

functionality and safety of any application made of this information and any resulting product. “High-Risk Device” means any

device or system whose failure could cause personal injury, death, or property damage. Examples of High-Risk Devices are

weapons, nuclear installations, surgical implants, and other medical devices. “Critical Component” means any component of

a High-Risk Device whose failure to perform can be reasonably expected to cause, directly or indirectly, the failure of the

High-Risk Device, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do

release Cypress from any claim, damage, or other liability arising from any use of a Cypress product as a Critical Component

in a High-Risk Device. You shall indemnify and hold Cypress, its directors, officers, employees, agents, affiliates, distributors,

and assigns harmless from and against all claims, costs, damages, and expenses, arising out of any claim, including claims

for product liability, personal injury or death, or property damage arising from any use of a Cypress product as a Critical Component in a High-Risk Device. Cypress products are not intended or authorized for use as a Critical Component in any HighRisk Device except to the limited extent that (i) Cypress's published data sheet for the product explicitly states Cypress has

qualified the product for use in a specific High-Risk Device, or (ii) Cypress has given you advance written authorization to use

the product as a Critical Component in the specific High-Risk Device and you have signed a separate indemnification agreement.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, FRAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more

complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

2 EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F

Page 3

Contents

1. Introduction to EZ-USB FX3 19

1.1 Overview of USB 3.0 ..............................................................................................................19

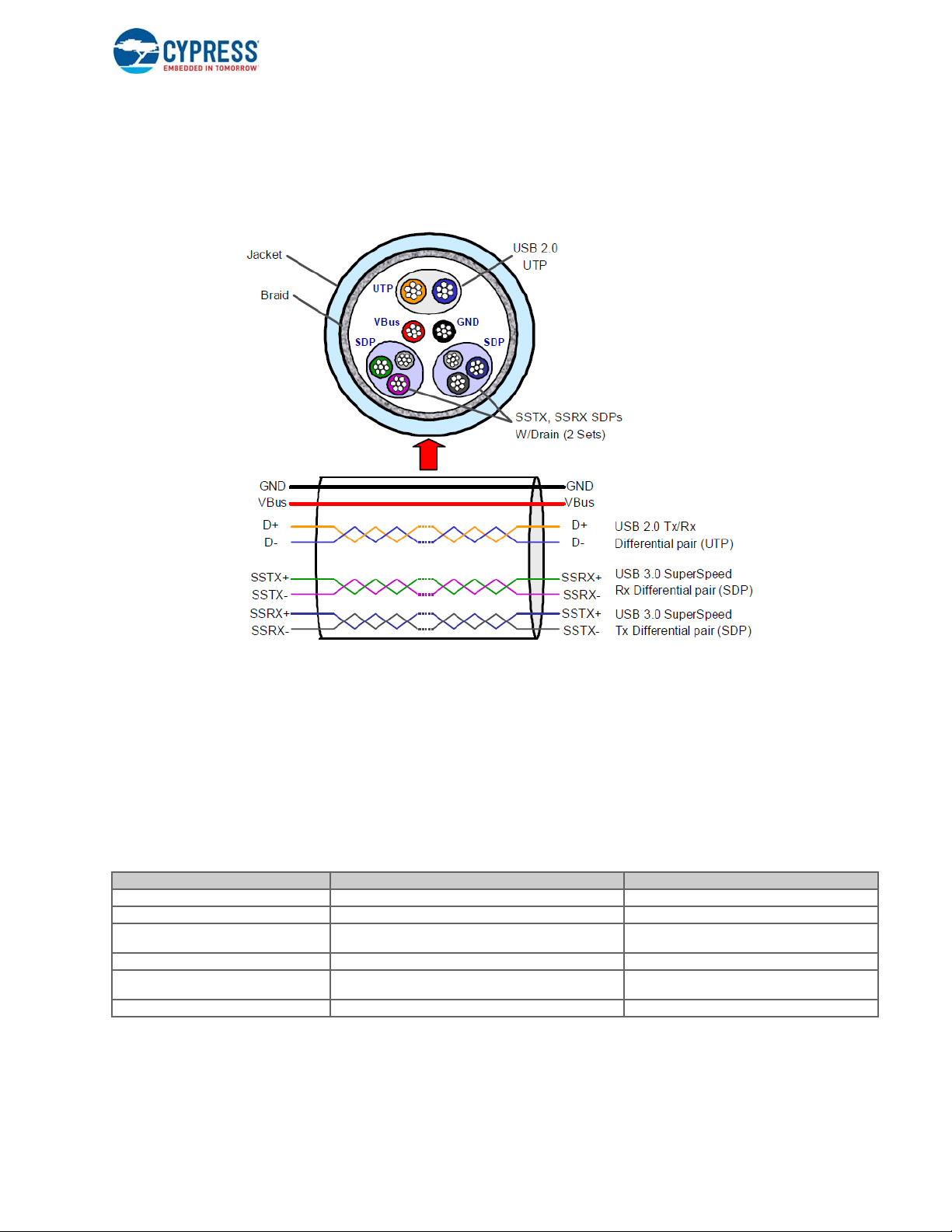

1.1.1 Physical Layer.............................................................................................................19

1.1.2 Link Layer....................................................................................................................20

1.1.3 Protocol Layer .............................................................................................................21

1.1.3.1 Unicast Transactions ...................................................................................21

1.1.3.2 Token/ Data/Handshake Sequences ...........................................................21

1.1.3.3 Data Bursting...............................................................................................23

1.1.3.4 End-to-End Flow Control .............................................................................24

1.1.3.5 Streams .......................................................................................................25

1.2 SuperSpeed Power Management...........................................................................................25

1.2.1 Function Power Management .....................................................................................26

1.3 FX3/FX3S Features ................................................................................................................26

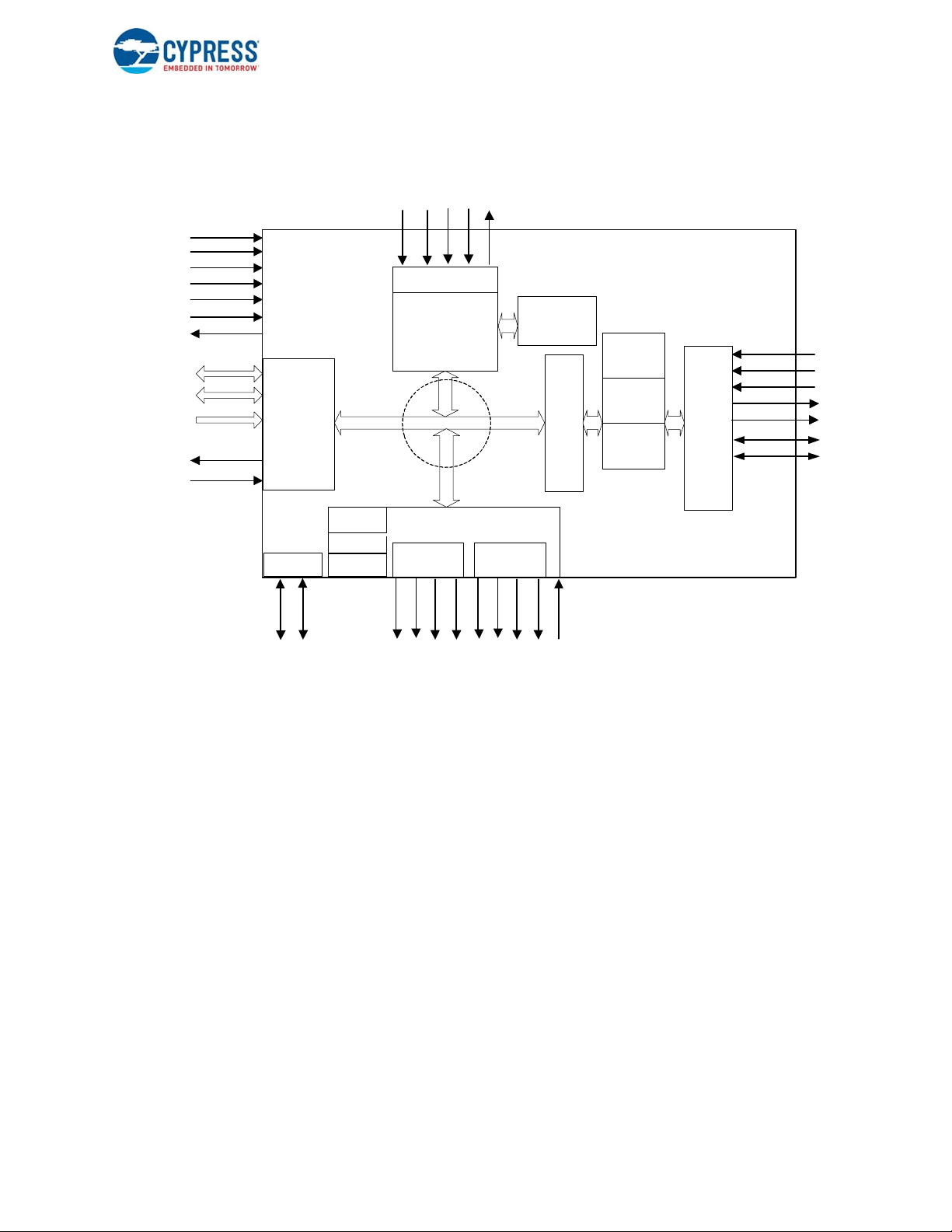

1.3.1 FX3 Block Diagram .....................................................................................................28

1.3.2 FX3S Block Diagram...................................................................................................29

1.4 Functional Overview ...............................................................................................................29

1.4.1 CPU.............................................................................................................................29

1.4.2 DMA ............................................................................................................................30

1.4.3 USB Interface..............................................................................................................30

1.4.4 GPIF II.........................................................................................................................30

1.4.5 UART Interface ...........................................................................................................31

1.4.6 I2C Interface................................................................................................................31

1.4.7 I2S Interface................................................................................................................31

1.4.8 SPI Interface ...............................................................................................................31

1.4.9 JTAG Interface ............................................................................................................31

1.4.10 Storage Interface.........................................................................................................31

1.4.10.1 SD/MMC Clock Stop....................................................................................32

1.4.10.2 SD_CLK Output Clock Stop ........................................................................32

1.4.10.3 Card Insertion and Removal Detection........................................................32

1.4.10.4 Write Protection (WP)..................................................................................32

1.4.10.5 SDIO Interrupt .............................................................................................32

1.4.10.6 SDIO Read-Wait Feature ............................................................................32

1.4.10.7 Boot Options................................................................................................32

1.4.11 Clocking ......................................................................................................................33

2. FX3 CPU Subsystem 34

2.1 Features..................................................................................................................................34

2.2 Block Diagram ........................................................................................................................35

2.3 Functional Overview ...............................................................................................................35

2.3.1 ARM926EJ-S CPU......................................................................................................35

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 3

Page 4

Contents

2.3.1.1 Processor Modes.........................................................................................36

2.3.1.2 Processor Registers ....................................................................................37

2.3.1.3 Exception Vectors........................................................................................38

2.3.1.4 MMU ............................................................................................................38

2.3.1.5 Cache Memories .........................................................................................39

2.3.1.6 Tightly Coupled Memories...........................................................................39

2.3.1.7 JTAG Interface ............................................................................................40

2.3.1.8 Vectored Interrupt Controller .......................................................................40

2.3.1.9 CPU Operating Frequency ..........................................................................42

2.3.1.10 CPU Power Modes ......................................................................................42

2.3.1.11 Timers..........................................................................................................43

3. Memory and System Interconnect 44

3.1 Features..................................................................................................................................44

3.2 Block Diagram ........................................................................................................................44

3.3 Functional Overview ...............................................................................................................45

3.3.1 Memory Regions .........................................................................................................45

3.3.2 System Interconnect ...................................................................................................47

3.3.3 Low-Power Operations................................................................................................47

3.3.4 Cache Operations .......................................................................................................48

3.3.4.1 Cache Coherency........................................................................................48

3.3.5 Memory Usage............................................................................................................49

4. Global Controller (GCTL) 51

4.1 GPIO Pins...............................................................................................................................51

4.1.1 I/O Matrix Configuration ..............................................................................................51

4.1.2 I/O Drive Strength .......................................................................................................53

4.1.3 GPIO Pull-up and Pull-down .......................................................................................53

4.1.4 Simple GPIO Override ................................................................................................53

4.1.5 Complex GPIO Override .............................................................................................53

4.1.6 I/O Power Observability ..............................................................................................54

4.1.6.1 GCTL_IOPOWER........................................................................................54

4.1.6.2 GCTL_IOPWR_INTR ..................................................................................54

4.1.6.3 GCTL_IOPWR_INTR_MASK ......................................................................54

4.2 Clock Management.................................................................................................................54

4.3 Power Management................................................................................................................56

4.3.1 Power Domains...........................................................................................................56

4.3.2 Power Modes ..............................................................................................................57

4.3.3 Reset...........................................................................................................................57

4.3.4 Hard Reset ..................................................................................................................57

4.3.5 Soft Reset ...................................................................................................................57

5. FX3 DMA Subsystem 58

5.1 DMA Introduction ....................................................................................................................58

5.2 DMA Features.........................................................................................................................58

5.3 DMA Block Diagram ...............................................................................................................58

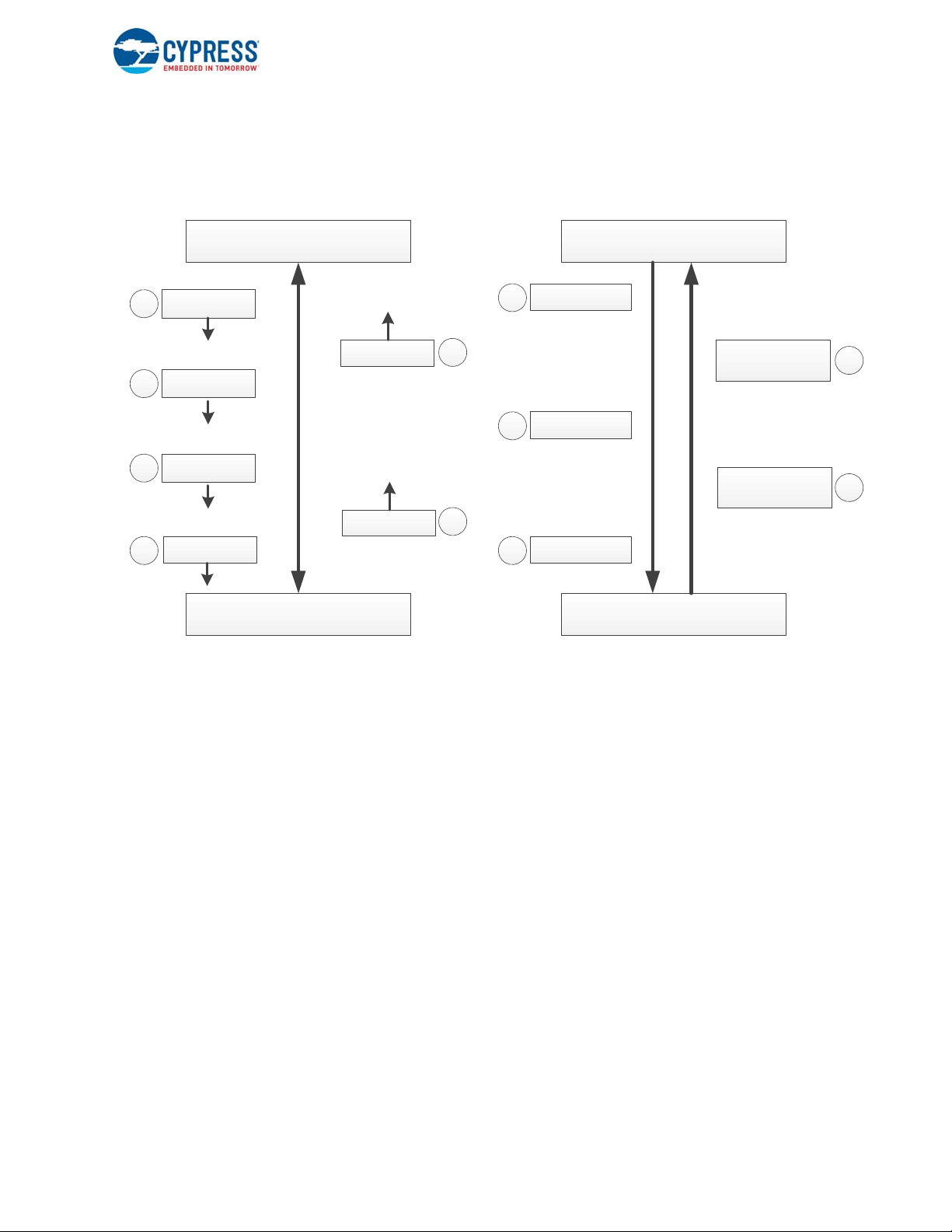

5.4 DMA Overview........................................................................................................................59

5.5 DMA Subsystem Components................................................................................................60

5.5.1 Clocking ......................................................................................................................60

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 4

Page 5

Contents

5.5.2 Descriptors Buffers, and Sockets................................................................................61

5.5.3 DMA Descriptors .........................................................................................................61

5.5.4 DMA Buffer ..................................................................................................................63

5.5.4.1 Implications of Data Cache Usage ..............................................................63

5.5.4.2 Memory Corruption Due to Cache Line Overlap .........................................64

5.5.4.3 Safe Usage of Data Cache..........................................................................64

5.5.4.4 ALIGNMENT REQUIREMENT - How Not To Share Cache Lines ..............65

5.5.5 Sockets .......................................................................................................................65

5.5.5.1 Software Manipulation of Sockets ...............................................................68

5.5.5.2 Initializing a Socket......................................................................................68

5.5.5.3 Terminating a Socket...................................................................................68

5.5.5.4 Modifying or Suspending a Socket ..............................................................68

5.5.5.5 Inspecting a Socket .....................................................................................69

5.5.5.6 Wrapping Up a Socket.................................................................................69

5.5.6 Illustration of Descriptor, Buffer and Socket Usage.....................................................69

5.5.7 Understanding DMA Operation: Peripheral to Peripheral ...........................................69

5.5.8 Interrupt Requests.......................................................................................................71

5.5.9 DMA Interrupts ............................................................................................................71

5.6 Programming Sequence .........................................................................................................72

5.6.1 Initialization .................................................................................................................72

5.6.1.1 Producer Half...............................................................................................72

5.6.1.2 Consumer Half.............................................................................................72

5.6.2 Peripheral to Peripheral Transfer ................................................................................73

5.7 CPU Intervention In Between Ingress and Egress .................................................................76

5.8 Concept of DMA Channels .....................................................................................................77

6. Universal Serial Bus (USB) 78

6.1 Introduction .............................................................................................................................78

6.2 Features..................................................................................................................................78

6.3 Block Diagram ........................................................................................................................78

6.4 Overview.................................................................................................................................79

6.4.1 USB Interface Block ....................................................................................................79

6.4.2 USB 3.0 Function Controller .......................................................................................79

6.4.3 USB 2.0 Function Controller .......................................................................................79

6.4.4 USB 2.0 Embedded Host ............................................................................................79

6.4.5 USB OTG Controller ...................................................................................................80

6.4.6 End-Point Memory ......................................................................................................80

6.4.7 DMA Adapters .............................................................................................................80

6.4.8 USB I/O System ..........................................................................................................80

6.4.8.1 USB 2.0 OTG PHY ......................................................................................80

6.4.8.2 USB 3.0 PHY...............................................................................................81

6.5 UIB Top-Level Register Interface ...........................................................................................81

6.6 USB Function Controllers .......................................................................................................83

6.6.1 USB 3.0 Function ........................................................................................................83

6.6.1.1 Clocking.......................................................................................................83

6.6.1.2 Interrupt Requests .......................................................................................83

6.6.1.3 USB 3.0 Functional Description...................................................................84

6.6.2 Physical Layer.............................................................................................................85

6.6.3 Link Layer....................................................................................................................86

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 5

Page 6

Contents

6.6.4 Protocol Layer .............................................................................................................87

6.7 USB 2.0 Function....................................................................................................................89

6.7.1 Clocking ......................................................................................................................89

6.7.2 Interrupt Requests.......................................................................................................89

6.7.3 USB 2.0 Functional Description ..................................................................................89

6.7.3.1 Serial Interface Engine ................................................................................89

6.7.3.2 Token Processor .........................................................................................89

6.7.4 USB 2.0 Function Registers........................................................................................90

6.7.5 USB Reset ..................................................................................................................90

6.7.6 USB Suspend..............................................................................................................90

6.7.7 USB Resume ..............................................................................................................90

6.7.8 Start of Frame .............................................................................................................90

6.7.9 SETUP Packet ............................................................................................................90

6.7.10 IN Packet.....................................................................................................................91

6.7.11 OUT Packet.................................................................................................................91

6.8 USB 3.0 and USB 2.0 Function Coordination .........................................................................91

6.9 USB Function Programming Model ........................................................................................92

6.9.1 USB 3.0 Initialization ...................................................................................................92

6.9.2 USB 3.0 Enable...........................................................................................................93

6.9.3 USB 3.0 Fallback to USB 2.0 ......................................................................................94

6.9.4 USB Reset ..................................................................................................................95

6.9.5 USB Connect ..............................................................................................................96

6.9.6 USB Disconnect ..........................................................................................................98

6.9.7 Control Request ..........................................................................................................99

6.9.8 USB Embedded Host ................................................................................................106

6.9.8.1 Clocking.....................................................................................................106

6.9.9 Interrupt Requests.....................................................................................................106

6.9.10 Functional Description...............................................................................................107

6.9.10.1 Embedded Host.........................................................................................107

6.9.10.2 Scheduler Memory ....................................................................................107

6.9.11 Embedded Host Programming Model .......................................................................109

6.9.11.1 Host Connect.............................................................................................109

6.9.11.2 Host Disconnect ........................................................................................109

6.9.11.3 Managing Transfers...................................................................................110

6.10 USB OTG Controller .............................................................................................................112

6.10.1 Interrupt Requests.....................................................................................................112

6.10.2 USB OTG Programming Model................................................................................. 112

6.10.2.1 USB OTG Start and Stop ..........................................................................112

6.10.2.2 Session Request Protocol ...............................

..........................................116

6.10.2.3 Host Negotiation Protocol..........................................................................118

7. General Programmable Interface II (GPIF II) 120

7.1 Features................................................................................................................................120

7.2 Block Diagram ......................................................................................................................121

7.3 Typical GPIF II interface .......................................................................................................121

7.4 Functional Overview .............................................................................................................122

7.4.1 Actions ......................................................................................................................122

7.4.1.1 Action - IN_DATA ......................................................................................124

7.4.1.2 Action - IN_ADDR......................................................................................125

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 6

Page 7

Contents

7.4.1.3 Action - DR_DATA.....................................................................................125

7.4.1.4 Action - DR_ADDR ....................................................................................126

7.4.1.5 Action - COMMIT.......................................................................................127

7.4.1.6 Action - DR_GPIO .....................................................................................127

7.4.1.7 Action - LD_ADDR_COUNT......................................................................128

7.4.1.8 Action - LD_DATA_COUNT ......................................................................128

7.4.1.9 Action - LD_CTRL_COUNT.......................................................................129

7.4.1.10 Action - COUNT_ADDR ............................................................................130

7.4.1.11 Action - COUNT_DATA .............................................................................130

7.4.1.12 Action - COUNT_CTRL .............................................................................130

7.4.1.13 Action - CMP_ADDR .................................................................................130

7.4.1.14 Action - CMP_DATA..................................................................................131

7.4.1.15 Action - CMP_CTRL ..................................................................................131

7.4.1.16 Action - INTR_CPU ...................................................................................132

7.4.1.17 Action - INTR_HOST .................................................................................132

7.4.1.18 Action - DR_DRQ ......................................................................................132

7.4.2 Triggers .....................................................................................................................133

7.4.3 Transition Conditions ................................................................................................133

7.4.4 GPIF II Designer Tool................................................................................................134

7.4.5 GPIF II Hardware Resources ....................................................................................134

7.4.5.1 Comparators..............................................................................................134

7.4.5.2 Counters ....................................................................................................135

7.4.5.3 GPIF II Interrupt.........................................................................................135

7.4.6 Threads and Sockets ................................................................................................135

7.4.6.1 Difference Between PP_MODE=0 and PP_MODE=1 ...............................135

7.4.7 Addressing ................................................................................................................137

7.4.7.1 Number of Address Lines ..........................................................................137

7.4.7.2 Assigning Sockets to Threads ...................................................................137

7.4.7.3 Addressing Methods..................................................................................137

7.4.8 Async/Sync ...............................................................................................................138

7.4.9 Configuration of Flags ...............................................................................................138

7.4.10 Developing the GPIF II State Machine......................................................................138

7.5 Designing a GPIF II Interface ...............................................................................................138

7.6 GPIF II State Machine Implementation.................................................................................141

7.6.1 Add a State ...............................................................................................................141

7.6.2 Add Actions to a State...............................................................................................142

7.6.3 Draw Transitions Between Actions............................................................................142

7.6.4 Add a Transition Equation.........................................................................................143

7.6.5 Set State Properties ..................................................................................................143

7.6.6 Analyzing the Signal Timing of the GPIF II Interface.................................................144

7.6.6.1 Selection of Time Frame ...........................................................................144

7.6.6.2 Automatic Timing Scale Selection .............................................................144

7.6.7 Scenario Entry...........................................................................................................144

7.6.8 Macro ........................................................................................................................146

7.7 GPIF II Constraints .........................................

......................................................................146

7.7.1 Mirror States..............................................................................................................146

7.7.2 Mirror State Rules .....................................................................................................147

7.7.3 Mirror State Example ................................................................................................148

7.7.4 Guidelines for Transition Equation Entry...................................................................149

7.7.5 Intermediate States ...................................................................................................150

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 7

Page 8

Contents

7.8 Initialization and Configuration of GPIF II Block ...................................................................151

7.8.1 GPIF II State Machine Control ..................................................................................151

7.9 Performing Read and Write Operations Using GPIF II .........................................................151

7.10 DMA Channel Creation in FX3 Firmware to Perform GPIF II to USB Data Transfers ..........153

7.11 GPIF II State Machine to Read Data into a Socket ..............................................................153

7.12 DMA Channel Creation in FX3 Firmware to Perform USB to GPIF II Data Transfers ..........154

7.13 GPIF II State Machine to Drive Data from Socket as Data Source ......................................155

7.13.1 Alpha Values .............................................................................................................156

7.14 GPIF II Read and Write over Registers ................................................................................156

7.15 Implementing Synchronous Slave FIFO Interface ................................................................158

7.16 Synchronous Slave FIFO Access Sequence and Interface Timing......................................161

7.16.1 Synchronous Slave FIFO Read Sequence Description ............................................162

7.16.2 Synchronous Slave FIFO Write Sequence Description ............................................164

7.16.3 Slave FIFO Interface Logical Diagram ......................................................................165

7.16.4 GPIF II State Machine of Slave FIFO Interface.........................................................165

8. Low Performance Peripherals (LPP) 167

8.1 I2C Interface .........................................................................................................................168

8.1.1 I2C Block Features....................................................................................................168

8.1.2 I2C Interface Overview..............................................................................................169

8.2 FX3 I2C Operations Overview ..............................................................................................170

8.2.1 Reset and Initialization ..............................................................................................170

8.2.2 Preamble...................................................................................................................170

8.2.3 Data Transfer ............................................................................................................170

8.2.3.1 Programming Model ..................................................................................170

8.2.3.2 Register-Based I2C Transfers ...................................................................171

8.2.3.3 DMA-Based I2C Transfers ........................................................................171

8.2.3.4 Starting a Transaction ...............................................................................171

8.2.3.5 Terminating Transactions: Software and Hardware Aborts .......................172

8.2.3.6 Multimaster Arbitration...............................................................................172

8.2.3.7 Error Conditions.........................................................................................172

8.2.4 Examples ..................................................................................................................172

8.2.4.1 Initialize I2C Block .....................................................................................172

8.2.4.2 Configure I2C Block...................................................................................173

8.2.4.3 Reads and Writes Using Register Transfers .............................................173

8.2.4.4 Reads and Writes Using DMA Transfers...................................................174

8.3 Serial Peripheral Interface ....................................................................................................175

8.3.1 SPI Block Features ...................................................................................................175

8.3.2 SPI Interface Overview .............................................................................................176

8.3.3 FX3 SPI Operations Overview ..................................................................................177

8.3.3.1 Reset and Initialization ..............................................................................177

8.3.3.2 Modes Governing Transfers ......................................................................177

8.3.4 SSN Control Configurations ......................................................................................177

8.3.5 Data Transfers...........................................................................................................178

8.4 Programming Model .............................................................................................................178

8.4.1 Register-Based Transfers .........................................................................................178

8.4.2 DMA-Based Transfers...............................................................................................178

8.5 Examples ..............................................................................................................................179

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 8

Page 9

Contents

8.5.1 Initialize SPI Block.....................................................................................................179

8.5.2 Configure SPI Block ..................................................................................................179

8.5.3 Reads and Writes Using Register Transfers.............................................................180

8.5.4 Reads and Writes Using DMA Transfers...................................................................181

8.6 Universal Asynchronous Receiver Transmitter.....................................................................183

8.6.1 UART block features .................................................................................................183

8.6.2 UART Overview ........................................................................................................183

8.7 FX3 UART Operations Overview ..........................................................................................184

8.7.1 Reset and Initialization ..............................................................................................184

8.7.2 Programming Model..................................................................................................184

8.7.3 Register-Based Transfers .........................................................................................184

8.7.3.1 DMA-Based Transfers ...............................................................................184

8.7.3.2 Error Conditions.........................................................................................185

8.7.4 Examples ..................................................................................................................185

8.7.4.1 Initialize UART Block .................................................................................185

8.7.4.2 Send UART Messages and Receive Fixed Bytes of Text .........................185

8.8 Integrated Interchip Sound Interface ....................................................................................187

8.8.1 I2S Block Features....................................................................................................187

8.8.2 I2S Overview.............................................................................................................187

8.8.3 FX3 I2S Operations Overview...................................................................................188

8.8.4 Programming Model..................................................................................................188

8.8.4.1 Start Transmission.....................................................................................188

8.8.4.2 Mute Condition ..........................................................................................188

8.8.4.3 Pause Condition ........................................................................................188

8.8.4.4 Buffer Underflow........................................................................................189

8.8.4.5 Stop Event .................................................................................................189

8.8.4.6 Fixed Clock Mode......................................................................................189

8.8.4.7 Data Shift Mode.........................................................................................189

8.8.4.8 Padding .....................................................................................................189

8.8.4.9 Error Conditions.........................................................................................189

8.8.4.10 Examples...................................................................................................189

8.8.4.11 Initialize I2S Block .....................................................................................190

8.8.4.12 Configure I2S Interface..............................................................................190

8.8.4.13 Transfer Data from USB to I2S Interface Using DMA Transfers ...............190

8.9 GPIO.....................................................................................................................................192

8.9.1 GPIO Features ..........................................................................................................192

8.9.2 GPIO Overview .........................................................................................................192

8.9.3 Programming Model..................................................................................................192

8.9.3.1 Reset and Initialization ..............................................................................192

8.9.4 Examples ..................................................................................................................193

8.9.4.1 Initialize GPIO Block..................................................................................193

8.9.4.2 Configure GPIO[45] as Input Pin and GPIO[21] as Output Pin .................194

8.9.4.3 Configure GPIO[50] to Generate PWM Output .........................................196

9. Storage Ports 197

9.1 Storage Interface Block Features .........................................................................................197

9.2 Block Diagram ......................................................................................................................197

9.3 Storage Interface (S-Port).....................................................................................................199

9.4 SD/ MMC/ SDIO Interface ....................................................................................................201

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 9

Page 10

Contents

9.4.1 SD/MMC Interface Overview.....................................................................................201

9.4.2 SDIO Interface Overview ..........................................................................................203

9.5 FX3S S-Port Operations Overview .......................................................................................203

9.5.1 S-port Initialization and Configuration .......................................................................204

9.5.1.1 Configuring the FX3S I/O Matrix................................................................204

9.5.1.2 Setting S-Port Interface Parameters..........................................................204

9.5.1.3 Starting the Storage Driver ........................................................................205

9.5.1.4 Setting the S-Port Clock ............................................................................206

9.5.1.5 Sending SD/MMC/SDIO Commands.........................................................206

9.5.1.6 Handling SIB Events..................................................................................208

9.5.2 Reads and Writes to SD/ MMC Using DMA Transfers ..............................................210

9.5.2.1 Sending Vendor Commands to SD/ MMC.................................................212

9.5.2.2 Setting the Granularity of Write Operations...............................................212

9.5.2.3 Checking Card Status................................................................................212

9.5.2.4 Aborting Ongoing Transaction to S-Port....................................................212

9.5.3 Working with SDIO Cards .........................................................................................213

9.5.3.1 Configuration and Initialization ..................................................................213

9.5.3.2 Reads and Writes from SDIO Card Registers ...........................................213

9.5.3.3 IO_RW_DIRECT Command (CMD52) ......................................................213

9.5.3.4 Setting Function Block Size.......................................................................218

9.5.3.5 Initialization and Operation of SDIO Functions..........................................218

9.5.3.6 SDIO Interrupts..........................................................................................218

9.5.3.7 Enabling and Disabling SDIO Interrupts....................................................219

9.5.3.8 Handling SDIO Interrupts ..........................................................................219

9.6 FX3S-Specific Features........................................................................................................220

9.6.1 Card Insertion and Removal Detection Mechanism..................................................220

9.6.2 Handling Card Detection in Software ........................................................................221

9.6.3 Write Protection.........................................................................................................222

9.6.4 SD/MMC CLOCK STOP ...........................................................................................222

9.6.5 SD_CLK Output Clock Stop ......................................................................................222

9.6.6 SDIO Read-Wait/ Suspend-Resume Feature ...........................................................222

9.6.6.1 Read-Wait..................................................................................................222

9.6.6.2 Suspend-Resume Feature ........................................................................223

9.6.6.3 SD3.0 Host Tuning Feature.......................................................................223

9.6.6.4 Normal and Alternate eMMC4.4 Boot........................................................224

10. Registers 228

10.1 Introduction ...........................................................................................................................228

10.2 Register Conventions ...........................................................................................................229

10.3 Vectored Interrupt Controller (VIC) Registers .......................................................................230

10.3.1 VIC_IRQ_STATUS ...............................................................................................230

10.3.2 VIC_FIQ_STATUS ...............................................................................................231

10.3.3 VIC_RAW_STATUS .............................................................................................232

10.3.4 VIC_INT_SELECT ...............................................................................................233

10.3.5 VIC_INT_ENABLE ...............................................................................................234

10.3.6 VIC_INT_CLEAR .................................................................................................235

10.3.7 VIC_PRIORITY_MASK ........................................................................................236

10.3.8 VIC_VEC_ADDRESS ..........................................................................................237

10.3.9 VIC_VECT_PRIORITY .........................................................................................238

10.3.10 VIC_ADDRESS ....................................................................................................239

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 10

Page 11

Contents

10.4 Global Controller Registers...................................................................................................240

10.4.1 GCTL_IOMATRIX ................................................................................................240

10.4.2 GCTL_GPIO_SIMPLE .........................................................................................241

10.4.3 GCTL_GPIO_COMPLEX .....................................................................................243

10.4.4 GCTL_DS .............................................................................................................245

10.4.5 GCTL_WPU_CFG ................................................................................................247

10.4.6 GCTL_WPD_CFG ................................................................................................249

10.4.7 GCTL_IOPOWER ................................................................................................251

10.4.8 GCTL_IOPOWER_INTR ......................................................................................253

10.4.9 GCTL_IOPOWER_INTR_MASK ..........................................................................255

10.4.10 GCTL_SW_INT ....................................................................................................257

10.4.11 GCTL_PLL_CFG ..................................................................................................258

10.4.12 GCTL_CPU_CLK_CFG .......................................................................................260

10.4.13 GCTL_UIB_CORE_CLK ......................................................................................261

10.4.14 GCTL_PIB_CORE_CLK ......................................................................................262

10.4.15 GCTL_GPIO_FAST_CLK ....................................................................................263

10.4.16 GCTL_GPIO_SLOW_CLK ...................................................................................265

10.4.17 GCTL_I2C_CORE_CLK .......................................................................................266

10.4.18 GCTL_UART_CORE_CLK ..................................................................................267

10.4.19 GCTL_SPI_CORE_CLK ......................................................................................268

10.4.20 GCTL_I2S_CORE_CLK .......................................................................................269

10.5 Global Controller Always On Registers ................................................................................270

10.5.1 GCTL_WAKEUP_EN ...........................................................................................270

10.5.2 GCTL_WAKEUP_POLARITY ..............................................................................272

10.5.3 GCTL_WAKEUP_EVENT ....................................................................................274

10.5.4 GCTL_FREEZE ...................................................................................................276

10.5.5 GCTL_WATCHDOG_CS .....................................................................................277

10.5.6 GCTL_WATCHDOG_TIMER0 .............................................................................279

10.5.7 GCTL_WATCHDOG_TIMER1 .............................................................................280

10.6 PIB Registers........................................................................................................................281

10.6.1 PIB_CONFIG .......................................................................................................281

10.6.2 PIB_INTR .............................................................................................................283

10.6.3 PIB_INTR_MASK .................................................................................................285

10.6.4 PIB_CLOCK_DETECT .........................................................................................287

10.6.5 PIB_RD_MAILBOX ..............................................................................................288

10.6.6 PIB_WR_MAILBOX .............................................................................................290

10.6.7 PIB_ERROR ........................................................................................................292

10.6.8 PIB_EOP_EOT ....................................................................................................294

10.6.9 PIB_DLL_CTRL ...................................................................................................295

10.6.10 PIB_WR_THRESHOLD .......................................................................................297

10.6.11 PIB_RD_THRESHOLD ........................................................................................298

10.6.12 PIB_ID ..................................................................................................................299

10.6.13 PIB_POWER ........................................................................................................300

10.7 GPIF Registers .....................................................................................................................301

10.7.1 GPIF_CONFIG .....................................................................................................301

10.7.2 GPIF_BUS_CONFIG ...........................................................................................303

10.7.3 GPIF_BUS_CONFIG2 .........................................................................................305

10.7.4 GPIF_AD_CONFIG ..............................................................................................306

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 11

Page 12

Contents

10.7.5 GPIF_STATUS .....................................................................................................308

10.7.6 GPIF_INTR ..........................................................................................................310

10.7.7 GPIF_INTR_MASK ..............................................................................................312

10.7.8 GPIF_CTRL_BUS_DIRECTION ..........................................................................314

10.7.9 GPIF_CTRL_BUS_DEFAULT ..............................................................................315

10.7.10 GPIF_CTRL_BUS_POLARITY ............................................................................316

10.7.11 GPIF_CTRL_BUS_TOGGLE ...............................................................................317

10.7.12 GPIF_CTRL_BUS_SELECT ................................................................................318

10.7.13 GPIF_CTRL_COUNT_CONFIG ...........................................................................319

10.7.14 GPIF_CTRL_COUNT_RESET .............................................................................320

10.7.15 GPIF_CTRL_COUNT_LIMIT ...............................................................................321

10.7.16 GPIF_ADDR_COUNT_CONFIG ..........................................................................322

10.7.17 GPIF_ADDR_COUNT_RESET ............................................................................323

10.7.18 GPIF_ADDR_COUNT_LIMIT ...............................................................................324

10.7.19 GPIF_STATE_COUNT_CONFIG ........................................................................325

10.7.20 GPIF_STATE_COUNT_LIMIT .............................................................................326

10.7.21 GPIF_DATA_COUNT_CONFIG ..........................................................................327

10.7.22 GPIF_DATA_COUNT_RESET ............................................................................328

10.7.23 GPIF_DATA_COUNT_LIMIT ...............................................................................329

10.7.24 GPIF_CTRL_COMP_VALUE ...............................................................................330

10.7.25 GPIF_CTRL_COMP_MASK ................................................................................331

10.7.26 GPIF_DATA_COMP_VALUE ...............................................................................332

10.7.27 GPIF_DATA_COMP_MASK ................................................................................333

10.7.28 GPIF_ADDR_COMP_VALUE ..............................................................................334

10.7.29 GPIF_ADDR_COMP_MASK ................................................................................335

10.7.30 GPIF_DATA_CTRL ..............................................................................................336

10.7.31 GPIF_INGRESS_DATA .......................................................................................337

10.7.32 GPIF_EGRESS_DATA ........................................................................................338

10.7.33 GPIF_INGRESS_ADDRESS ...............................................................................339

10.7.34 GPIF_EGRESS_ADDRESS ................................................................................340

10.7.35 GPIF_THREAD_CONFIG ....................................................................................341

10.7.36 GPIF_LAMBDA_STAT .........................................................................................343

10.7.37 GPIF_ALPHA_STAT ............................................................................................344

10.7.38 GPIF_BETA_STAT ..............................................................................................345

10.7.39 GPIF_WAVEFORM_CTRL_STAT ................................

.......................................346

10.7.40 GPIF_WAVEFORM_SWITCH .............................................................................348

10.7.41 GPIF_WAVEFORM_SWITCH_TIMEOUT ...........................................................350

10.7.42 GPIF_BETA_DEASSERT ....................................................................................351

10.7.43 GPIF_FUNCTION ................................................................................................352

10.7.44 GPIF_LEFT_WAVEFORM ...................................................................................353

10.7.45 GPIF_RIGHT_WAVEFORM ................................................................................356

10.8 P-Port Registers ...................................................................................................................359

10.8.1 PP_ID ...................................................................................................................359

10.8.2 PP_INIT ................................................................................................................360

10.8.3 PP_CONFIG ........................................................................................................361

10.8.4 PP_INTR_MASK ..................................................................................................363

10.8.5 PP_DRQR5_MASK ..............................................................................................364

10.8.6 PP_SOCK_MASK ................................................................................................365

10.8.7 PP_ERROR .........................................................................................................366

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 12

Page 13

Contents

10.8.8 PP_DMA_XFER ...................................................................................................367

10.8.9 PP_DMA_SIZE ....................................................................................................368

10.8.10 PP_WR_MAILBOX ..............................................................................................369

10.8.11 PP_MMIO_ADDR ................................................................................................371

10.8.12 PP_MMIO_DATA .................................................................................................372

10.8.13 PP_MMIO .............................................................................................................373

10.8.14 PP_EVENT ..........................................................................................................374

10.8.15 PP_RD_MAILBOX ...............................................................................................376

10.8.16 PP_SOCK_STAT .................................................................................................378

10.8.17 PP_BUF_SIZE_CNT ............................................................................................379

10.9 USB Port Registers...............................................................................................................380

10.9.1 UIB_INTR .............................................................................................................380

10.9.2 UIB_INTR_MASK .................................................................................................382

10.9.3 UIB_ID ..................................................................................................................384

10.9.4 UIB_POWER ........................................................................................................385

10.10 USB2 HS/FS/LS PHY Registers ...........................................................................................386

10.10.1 PHY_CLK_AND_TEST ........................................................................................386

10.10.2 PHY_CONF ..........................................................................................................388

10.10.3 PHY_CHIRP .........................................................................................................390

10.11 USB2 Device Controller Registers........................................................................................391

10.11.1 DEV_CS ...............................................................................................................391

10.11.2 DEV_FRAMECNT ................................................................................................393

10.11.3 DEV_PWR_CS ....................................................................................................394

10.11.4 DEV_SETUPDAT .................................................................................................395

10.11.5 DEV_TOGGLE .....................................................................................................397

10.11.6 DEV_EPI_CS .......................................................................................................399

10.11.7 DEV_EPI_XFER_CNT .........................................................................................401

10.11.8 DEV_EPO_CS .....................................................................................................402

10.11.9 DEV_EPO_XFER_CNT .......................................................................................404

10.11.10 DEV_CTRL_INTR_MASK ....................................................................................405

10.11.11 DEV_CTRL_INTR ................................................................................................406

10.11.12 DEV_EP_INTR_MASK ........................................................................................407

10.11.13 DEV_EP_INTR .....................................................................................................408

10.12 USB Controller Miscellaneous Registers ..............................................................................409

10.12.1 CHGDET_CTRL ...................................................................................................409

10.12.2 CHGDET_INTR ....................................................................................................411

10.12.3 CHGDET_INTR_MASK .......................................................................................412

10.12.4 OTG_CTRL ...............................................

...........................................................413

10.12.5 OTG_INTR ...........................................................................................................415

10.12.6 OTG_INTR_MASK ...............................................................................................416

10.12.7 OTG_TIMER ........................................................................................................417

10.13 USB End Point Manager Registers ......................................................................................418

10.13.1 EEPM_CS ............................................................................................................418

10.13.2 IEPM_CS .............................................................................................................420

10.13.3 IEPM_MULT .........................................................................................................421

10.13.4 EEPM_ENDPOINT ..............................................................................................422

10.13.5 IEPM_ENDPOINT ................................................................................................423

10.13.6 IEPM_FIFO ..........................................................................................................424

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 13

Page 14

Contents

10.14 USB2 Host Controller Registers ...........................................................................................425

10.14.1 HOST_CS ............................................................................................................425

10.14.2 HOST_EP_INTR ..................................................................................................426

10.14.3 HOST_EP_INTR_MASK ......................................................................................427

10.14.4 HOST_TOGGLE ..................................................................................................428

10.14.5 HOST_SHDL_CS .................................................................................................430

10.14.6 HOST_SHDL_SLEEP ..........................................................................................432

10.14.7 HOST_RESP_BASE ............................................................................................433

10.14.8 HOST_RESP_CS ................................................................................................434

10.14.9 HOST_ACTIVE_EP .............................................................................................435

10.14.10 OHCI_REVISION .................................................................................................436

10.14.11 OHCI_CONTROL .................................................................................................437

10.14.12 OHCI_COMMAND_STATUS ...............................................................................438

10.14.13 OHCI_INTERRUPT_STATUS .............................................................................439

10.14.14 OHCI_INTERRUPT_ENABLE .............................................................................440

10.14.15 OHCI_INTERRUPT_DISABLE ............................................................................441

10.14.16 OHCI_FM_INTERVAL .........................................................................................442

10.14.17 OHCI_FM_REMAINING .......................................................................................443

10.14.18 OHCI_FM_NUMBER ...........................................................................................444

10.14.19 OHCI_PERIODIC_START ...................................................................................445

10.14.20 OHCI_LS_THRESHOLD ......................................................................................446

10.14.21 OHCI_RH_PORT_STATUS .................................................................................447

10.14.22 OHCI_EOF ...........................................................................................................449

10.14.23 EHCI_HCCPARAMS ............................................................................................450

10.14.24 EHCI_USBCMD ...................................................................................................451

10.14.25 EHCI_USBSTS ....................................................................................................452

10.14.26 EHCI_USBINTR ...................................................................................................453

10.14.27 EHCI_FRINDEX ...................................................................................................454

10.14.28 EHCI_CONFIGFLAG ...........................................................................................455

10.14.29 EHCI_PORTSC ....................................................................................................456

10.14.30 EHCI_EOF ...........................................................................................................458

10.14.31 SHDL_CHNG_TYPE ............................................................................................459

10.14.32 SHDL_STATE_MACHINE ...................................................................................460

10.14.33 SHDL_INTERNAL_STATUS ................................................................................462

10.14.34 SHDL_OHCI .........................................................................................................464

10.14.35 SHDL_EHCI .........................................................................................................468

10.15 USB3 Link Controller Registers ............................................................................................472

10.15.1 LNK_CONF ..........................................................................................................472

10.15.2 LNK_INTR ...............................................

.............................................................473

10.15.3 LNK_INTR_MASK ................................................................................................475

10.15.4 LNK_ERROR_CONF ...........................................................................................477

10.15.5 LNK_ERROR_STATUS .......................................................................................479

10.15.6 LNK_ERROR_COUNT ........................................................................................481

10.15.7 LNK_ERROR_COUNT_THRESHOLD ................................................................482

10.15.8 LNK_PHY_CONF .................................................................................................483

10.15.9 LNK_PHY_MPLL_STATUS .................................................................................484

10.15.10 LNK_PHY_TX_TRIM ...........................................................................................485

10.15.11 LNK_PHY_ERROR_CONF ..................................................................................486

10.15.12 LNK_PHY_ERROR_STATUS ..............................................................................487

EZ-USB FX3 Technical Reference Manual, Document Number: 001-76074 Rev. *F 14

Page 15

Contents

10.15.13 LNK_DEVICE_POWER_CONTROL ....................................................................489

10.15.14 LNK_LTSSM_STATE ...........................................................................................491

10.15.15 LNK_LFPS_OBSERVE ........................................................................................492

10.15.16 LNK_COMPLIANCE_PATTERN_0 ......................................................................493

10.15.17 LNK_COMPLIANCE_PATTERN_1 ......................................................................494

10.15.18 LNK_COMPLIANCE_PATTERN_2 ......................................................................495

10.15.19 LNK_COMPLIANCE_PATTERN_3 ......................................................................496

10.15.20 LNK_COMPLIANCE_PATTERN_4 ......................................................................497

10.15.21 LNK_COMPLIANCE_PATTERN_5 ......................................................................498

10.15.22 LNK_COMPLIANCE_PATTERN_6 ......................................................................499

10.15.23 LNK_COMPLIANCE_PATTERN_7 ......................................................................500

10.15.24 LNK_COMPLIANCE_PATTERN_8 ......................................................................501