CYWUSB6932

CYWUSB6934

WirelessUSB™ LS 2.4 GHz DSSS Radio SoC

1.0 Features

• 2.4 GHz radio transceiver

• Operates in the unlicensed Industrial, Scientific, and

Medical (ISM) band (2.4 GHz–2.483 GHz)

• -90 dBm receive sensitivity

• Up to 0 dBm output power

• Range of up to 10 meters or more

• Data throughput of up to 62.5 kbits/sec

• Highly integrated low cost, mini mal number of external

components required

• Dual DSSS reconfigurable baseband correlators

• SPI microcontroller interface (up to 2 MHz data rate)

• 13 MHz

• Low standby current ~ 1 µA

• Integrated 32 bit Manufacturing ID

• Operating voltage from 2.7V to 3.6V

• Operating temperature from 0° to 70°C

• Offered in a small footprint 48 Quad Flat Pack No Leads

(QFN) or cost saving 28-lead exposed paddle SOIC

± 50 ppm input clock operation

2.0 Functional Description

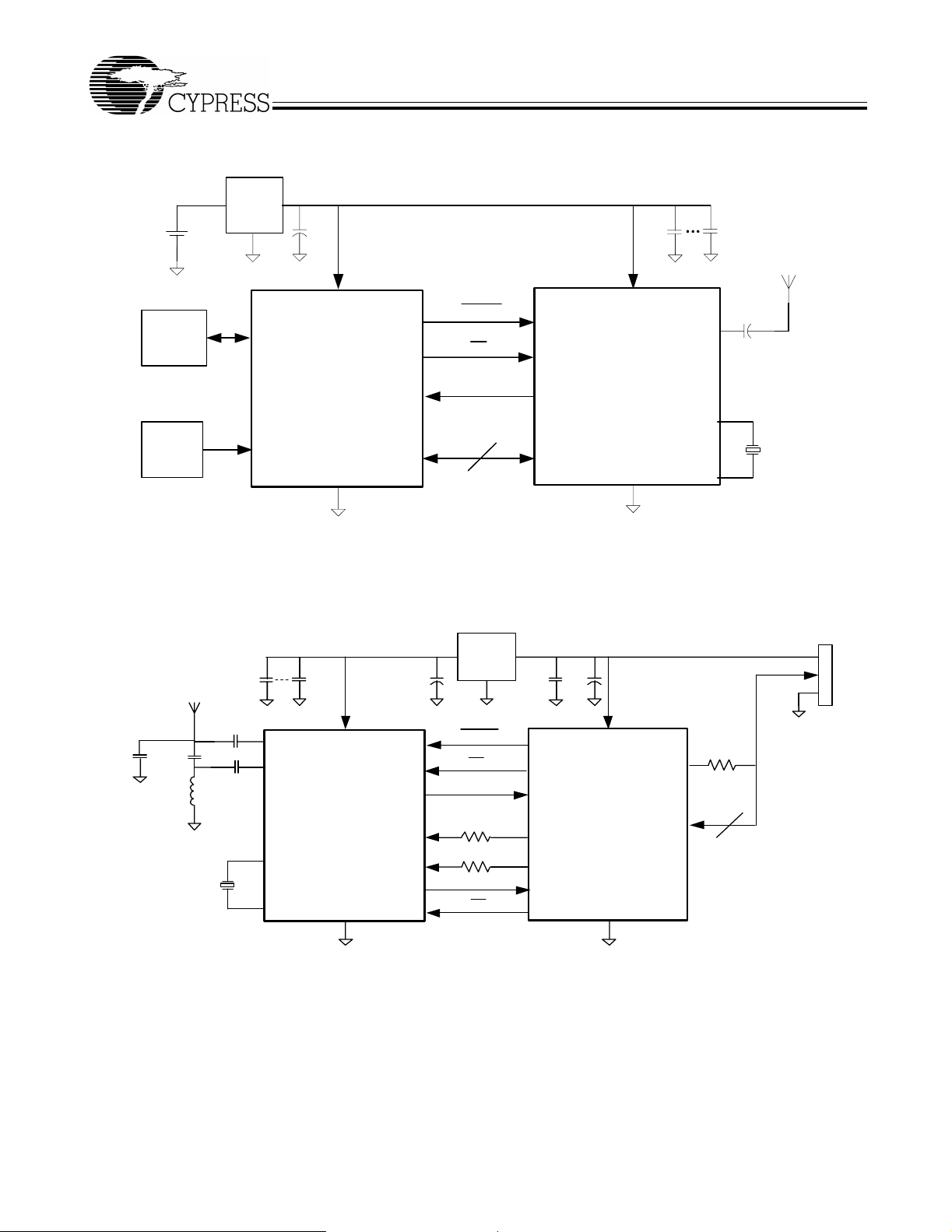

The CYWUSB6932/CYWUSB6934 Integrated Circuits (ICs)

are highly integrated 2.4 GHz Direct Sequence Spread

Spectrum (DSSS) Radio System-on-Chip (SoC) ICs. From the

Serial Peripheral Interf ace (SPI) to the an tenna, these IC s are

single-chi p 2.4 GHz D SSS G aus sian Freq uen cy S hift K eying

(GFSK) baseband modems that connect directly to a USB

controller or a standard microcontroller as shown in

Figure 3-1.

The CYWUSB6932 is a transmit-only IC and is available in a

cost saving 28 -pin SOIC package. The CYWUSB6934 is a

transceiver IC and is offered in both a 28-pin SOIC package

and a small fo otprint 48-pin QFN package .

3.0 Applications

• PC Human Interface Devices (HID)

• Mice

• Keyboards

• Joysticks

• Peripheral Gaming Devices

• Game Controllers

• Con so le Key boa rds

• General

• Pre senter Tools

• Remote Controls

• Consumer Electronics

• Barcode Scanners

• POS Peripherals

• Toys

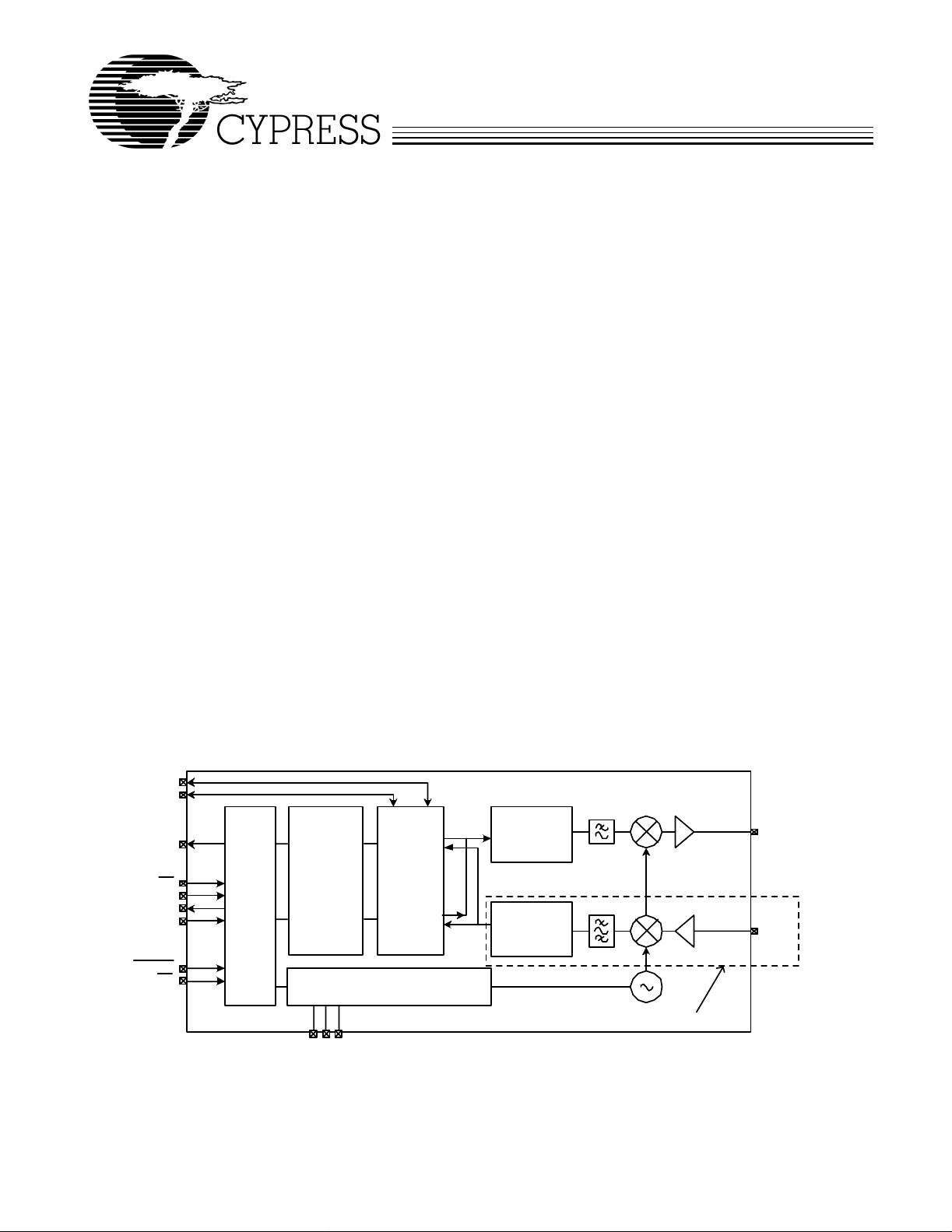

DIOVAL

DIO

GFSK

Modulator

GFSK

Demodulator

RFOUT

RFIN

CYWUSB6934 Only

IRQ

SS

SCK

MISO

MOSI

RESET

PD

Digital

SERDES

A

SERDES

B

X13

X13IN

DSSS

Baseband

A

DSSS

Baseband

B

Synthesizer

X13OUT

Figure 3-1. CYWUSB6932/CYWUSB6934 Simplified Block Diagram

Cypress Semiconductor Corporation • 3901 North First Street • San Jose, CA 95134 • 408-943-2600

Document 38-16007 Rev. *F Revised August 6, 2004

CYWUSB6932

CYWUSB6934

3.1 Applications Support

The CYWUSB6932/CYWUSB6934 ICs are supported by the

CY3632 WirelessUSB Development Kit. The development kit

provides all of the materi als an d docum ent s nee ded to c ut the

cord on wired applications including two radio modules that

connect directly to two prototyping platform boards, comprehensive WirelessUSB protoc ol code examples a WirelessUS B

Listener tool and all o f the a ssociat ed sc hemat ics, g erber fi les

and bill of materials.

The CY4632 WirelessUSB LS Keyboard Mouse Reference

Design provides a production-worthy example of a wireless

mouse and keyboard system.

The CY3633 WirelessUSB LS Gaming Development Kit

provides support for designing a wireless gamepad for the

major gaming consoles and is offered as an accessory to the

CY3632 WirelessUSB.

4.0 Functional Overview

The CYWUSB6932/CYWUSB6934 ICs provide a complete

WirelessUS B LS SPI to antenn a radio modem. Th e SoC is

designed to implement wireless devices operating in the

worldwide 2.4 GHz Industrial, Scientific, and Medical (ISM)

frequency band (2.400 GHz - 2.4835 GHz). It is intended for

systems compliant with world-wide regulations covered by

ETSI EN 301 489-1 V1.4.1, ETSI EN 300 328-1 V1.3.1

(European Countries); FCC CFR 47 Part 15 (USA and

Industry Canada) and ARIB STD-T66 (Japan).

The CYWUSB6934 IC cont ain s a 2.4 GHz ra dio transc eiver, a

GFSK modem and a dual DSSS reconfigurable baseband.

The CYWUSB6932 IC conta ins a 2.4 G Hz radio tra nsmit-on ly,

a GFSK modem and a DSSS baseband. The radio and

baseband are both code- and frequency-agile. Forty-nine

spreading codes selected for optimal performance (Gold

codes) are supported across 78 1 MHz channels yielding a

theoretical spectral capacity of 3822 channels. Both ICs

support a range of up to 10 meters or more.

4.1 2.4 GHz Radio

The receiver and trans mitter are a single-conve rsion low-Intermediate Frequency (low-IF) architecture with fully integrated

IF channel matched filters to achieve high performance in the

presence of interference. An integrated Power Amplifier (PA)

provides an output power control range of 30 dB in seven

steps.

Both the receiver and transmitter integrated Voltage

Controlled Oscillator (VCO) and synthes izer have the ag ility to

cover the complete 2. 4 GHz GFSK radio transmitte r ISM band.

The VCO loop filter is also integrated on-chip.

4.2 GFSK Modem

The transmitter uses a DSP-based vector modulator to

convert the 1 MHz chips to an accurate GFSK carrier.

The receiver uses a fully integrated Freq uency Modulator (FM )

detector with automatic data slicer to demodulate the GFSK

signal.

4.3 Dual DSSS Baseband

Data is converted to DSSS chips by a digital spreader.

De-spreading is p erformed by an oversam pled correlat or . Th e

DSSS baseband cancels spurious noise and assembles

properly correlated data bytes.

The DSSS baseband has four operating modes: 64 chips/bit

Single Channel, 32 chip s/bit Dual Channe l, 32 chi ps/bi t Single

Channel 2x Oversampled, and 32 chips/bit Single Channel

Dual Data Rate (DDR).

4.3.1 64 chips/bit Single Channel

The baseband supports a single data stream operating at

15.625 kbits/sec. The advantage of selecting this mode is its

ability to tolerate a noisy environment. This is because the

15.625 kbits/sec data stream utilizes the longest PN Code

resulting in the high es t p r oba bil ity for recovering packe t s ov er

the air. This mode can also be selected for systems requiring

data transmissi ons over lon ger ranges.

4.3.2 32 chips/bit Dual Channel

The baseband supports two non-simultaneous data streams

each operating at 31.25 kbits/sec.

4.3.3 32 chips/bit Single Channel 2x Oversampled

The baseband supports a single data stream operating at

31.25 kbits/sec that is sampled twice as much as the other

modes. The advantage of selecting this mode is its ability to

tolerate a noisy environment.

4.3.4 32 chips/bit Single Channel Dual Data Rate (DDR)

The baseband spread s bits in p airs and s upports a si ngle data

stream operating at 62.5 kbits/sec.

4.4 Serializer/Deserializer (SERDES)

Both ICs provide a data Serializer/Deserializer (SERDES),

which provides byte-l evel framing of transmi t and receive dat a.

Bytes for transmission are loaded into the SERDES and

receive bytes are read from the SERDES via the SPI in terface.

The SERDES provides double buffering of transmit and

receive data. While one byte is being transmitted by the radio

the next byte can be written to the SERDES data register

insuring there are no breaks in transmitted data.

After a receive byte has been received it is loaded into the

SERDES data register and can be read at any time until the

byte is received, at which time the old contents of the

next

SERDES data register wil l be overwritten.

4.5 Application Interfaces

Both ICs have a fully synchronous SPI slave interface for

connectivity to the application MCU. Configuration and

byte-oriented data transfer can be performed over this

interface. An interrupt is provided to trigger real time events.

An optional SERDES Bypas s mode (DIO) is provided for a pplications that require a synchronous serial bit-oriented data

path. This interface is for data only.

4.6 Clocking and Power Management

A 13 MHz crystal (±50 ppm or better) is directly connected to

X13IN and X13 without the need for ex ter nal capacitors. Both

ICs have a programmable trim capability for adjusting the

on-chip load capacitance supplied to the crystal. The Radio

Frequency (RF) circuitry has on-chip decoupling capacitors.

Document 38-16007 Rev. *F Page 2 of 33

CYWUSB6932

CYWUSB6934

Both devices are po wered from a 2.7V to 3.6V DC s upply . Both

devices can be shutdown to a fully static state using the PD

pin.

Below are the requirements for the crystal to be directly

connected to X13IN and X13:

• Nominal Frequency: 13 MHz

• Operating Mode: Fundam ental Mode

• Resonance Mode: Paral le l Reson ant

• Frequency Stability :

• Series Resistanc e: ≤ 100 ohms

• Load Capacitance: 10 pF

• Drive Level: 10 uW–100 uW

± 50 ppm

4.7 Receive Signal Strength Indicator (RSSI)

The RSSI register (Reg 0x22) returns the relative signal

strength of the ON-channel signal power and can be used to:

1) determine the connec tio n qu ali ty, 2) determine the value of

the noise floor, and 3) check for a quiet channel before transmitting.

The internal RSSI voltage is sampled through a 5-bit

analog-to-digital converter (ADC). A state machine controls

the conversion process. Under normal conditions, the RSSI

state machine initiates a conversion when an ON-channel

carrier is detected and remains above the noise floor for over

50uS. The conversion produces a 5-bit value in the RSSI

register (Reg 0x22, bits 4:0) along with a valid bit, RSSI

register (Reg 0x22, bit 5). The state machine then remains in

HALT mode and does not reset for a new conversion until the

receive mode is toggled off and on. Once a connection has

been established, the RSSI register can be read to determine

the relative connec ti on quality of the ch ann el. A R SSI reg is ter

value lower than 10 indi cates that the receive d signal str ength

is low, a value greater than 28 indicates a strong signal level.

To check for a quiet channel before transmitting, first set up

receive mode properl y and read the RSSI register (Reg 0 x22).

If the valid bit is zero, then force the Carrier Detect register

(Reg 0x2F, bit 7=1) to initiate an ADC conversion. Then, wait

greater than 50uS and read the RSSI register again. Next,

clear the Carrier Detect Register (Reg 0x2F, bit 7=0) and turn

the receiver OFF. Measuring the noise floor of a quiet channe l

is inherently a 'noisy' process so, for best results, this

procedure should be repeated several times (~20) to compute

an average no ise floor level. A RSSI re gister value of 0-10

indicates a channel that is relatively quiet. A RSSI register

value greater than 10 indicates the channel is probably being

used. A RSSI register value greater than 28 indicates the

presence of a strong signal.

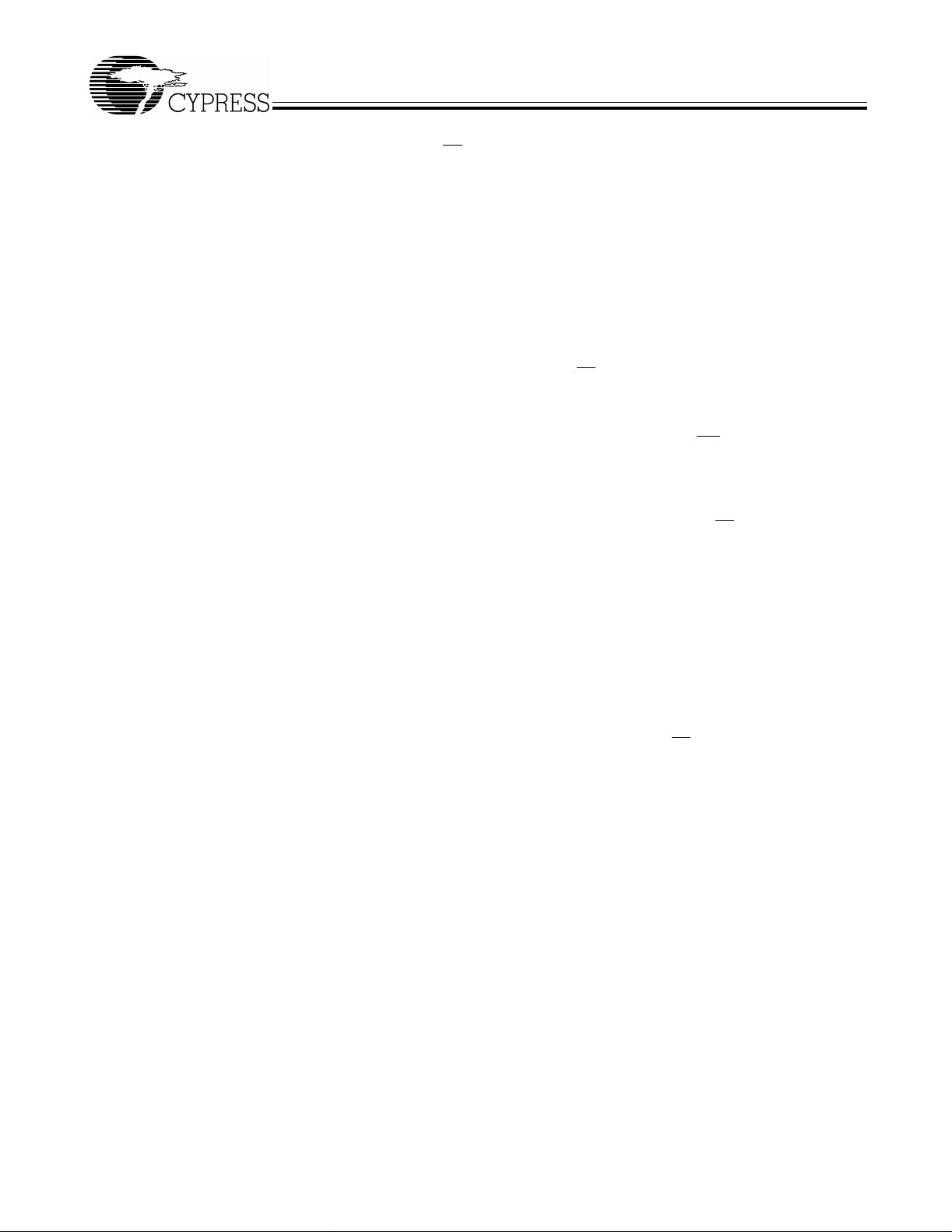

5.0 Application Interfaces

5.1 SPI Interface

The CYWUSB6932/CYWUSB6934 ICs have a four-wire SPI

communication interface between an application MCU and

one or more slave devices. The SPI interface supports

single-byte and multi-byte serial transfers. The four-wire SPI

communications interface consists of Master Out-Slave In

(MOSI), Master In-Slave Out (MISO), Serial Clock (SCK), and

Slave Select (SS

The SPI receives SCK from an application MCU on the SCK

pin. Data from the application MCU is shifted in on the MOSI

pin. Data to the application MCU is shifted out on the MISO

pin. The active-low Slave Selec t (SS)

initiate a SPI transfer.

The application MCU can initiate a SPI data transfer via a

multi-byte transact ion. T he first byt e is the Command/Add ress

byte, and the following bytes are the data bytes as shown in

Figure 5-1 through Figure 5-4. The SS

deasserted between bytes. The SPI communications is as

follows:

• Command Direct ion (b it 7) = “0” En ables SPI rea d tran saction. A “1” enables SPI write transactions.

• Command Incremen t (bit 6) = “1” Enables SPI auto address

increment. When se t, the addres s field automa tically i ncrements at the en d of each data byte in a bur s t access, ot herwise the same address is accessed.

• Six bits of address.

• Eight bits of data.

The SPI communications interface has a burst mechanism,

where the command byte can be followed by as many data

bytes as desired. A burst transaction is terminated by

deasserting the slave select (SS

The SPI communications i nter fac e s ing le re ad a nd b urs t rea d

sequences are shown in Figure 5-2 and Figure 5-3, respectively.

The SPI communication s interfac e single write and burs t write

sequences are shown in Figure 5-4 and Figure 5-5, respectively.

).

pin must be asserted to

signal should not be

= 1).

Document 38-16007 Rev. *F Page 3 of 33

CYWUSB6932

CYWUSB6934

Figure 5-1. SPI Transaction Format

Byte 1 Byte 1+N

Bit # 7 6 [5:0] [7:0]

Bit Name DIR INC Address Data

SCK

SS

addrcm d

A0A1A2A3A4A5

MOSI

DIR INC

00

data to mcu

MISO

D6D7

D0D1D2D3D4D5

Figure 5-2. SPI Single Read Sequence

SCK

SS

MOSI

MISO

DIR INC

01

addrcm d

A0A1A2A3A4A5

da ta to mcu

D6D7

1

D0D1D2D3D4D5

data to mcu

D6D7

1+N

D0D1D2D3D4D5

SCK

SS

MOSI

MISO

SCK

SS

MOSI

MISO

DIR INC

10

DIR INC

11

Figure 5-3. SPI Burst Read Sequence

addrcmd

D6D7

A0A1A2A3A4A5

data fro m mcu

Figure 5-4. SPI Single Write Sequence

addrcm d

da ta fro m mcu

D6D7

A0A1A2A3A4A5

Figure 5-5. SPI Burst Write Sequence

D0D1D2D3D4D5

1

data from mcu

D0D1D2D3D4D5

D6D7

1+N

D0D1D2D3D4D5

Document 38-16007 Rev. *F Page 4 of 33

CYWUSB6932

CYWUSB6934

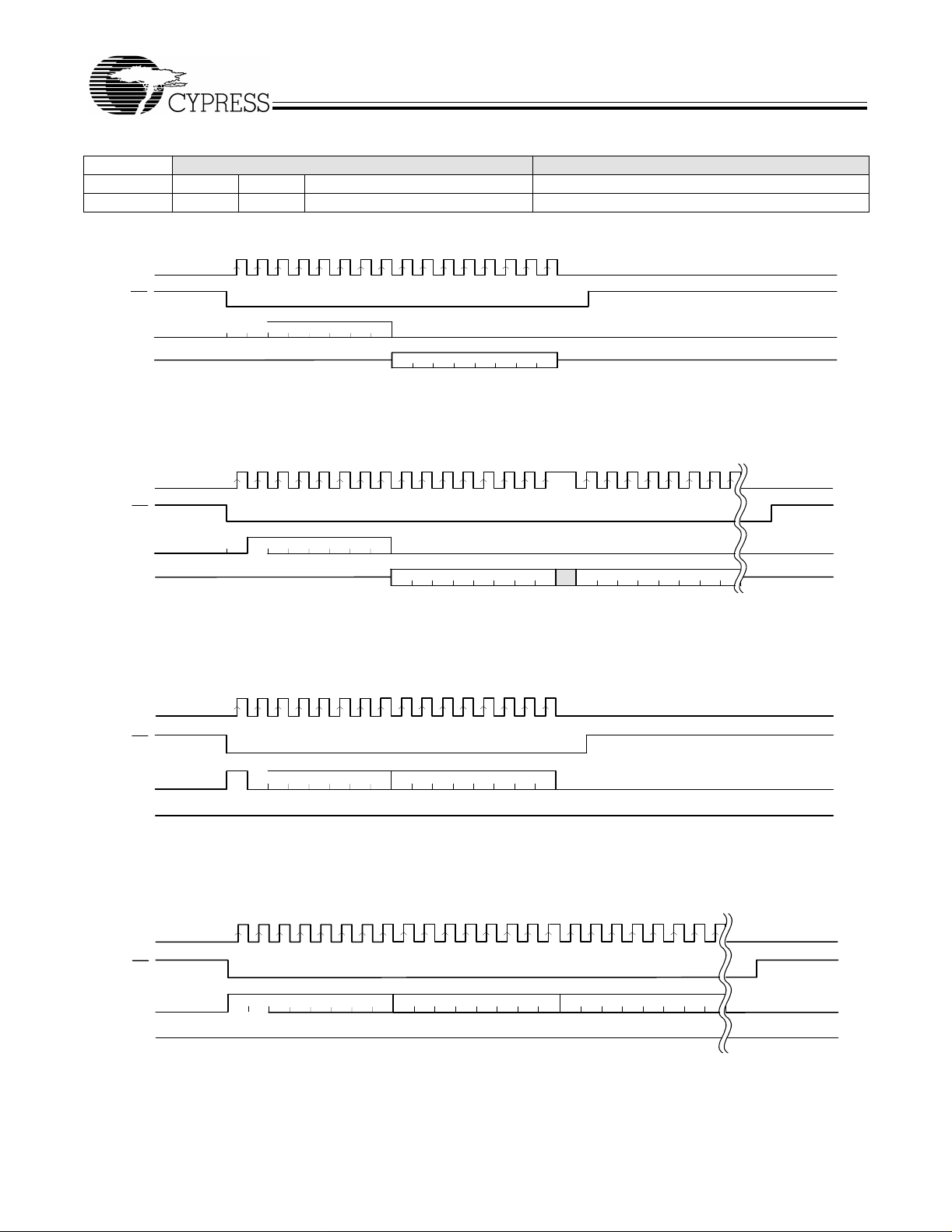

5.2 DIO Interface

The DIO communications interface is an optional SERDES

bypass data-only transfer interface. In receive mode, DIO and

DIOVAL are valid after the falling edge of IRQ, which clocks

IRQ

DIOVAL

v7v6v5v4v3v2

v9v8v1v0

data to mcu

DIO

d1d0

d7d6d5d4d3d2

Figure 5-6. DIO Receive Sequence

IRQ

DIOVAL

v1v0

v9v8

v7v6v5v4v3v2

data from mcu

DIO

d1d0

d7d6d5d4d3d2

Figure 5-7. DIO Transmit Sequence

the data as shown in

Figure 5-6. In transmit mode, DIO and

DIOVAL are sampled on the falling edge of the IRQ, which

clocks the data as shown in

Figure 5-7. The application MCU

samples the DIO and DIOVAL on the rising edge of IRQ.

v...v14v1 3v12v11v10

d...d14d13d12d11d1 0d9d8

v...v1 4v13v12v11v10

d...d1 4d13d12d11d10d9d8

5.3 Interrupts

The CYWUSB6932/CYWUSB6934 ICs feature three sets of

interrupts: transmit, received (CYWUSB6932 only), and a

wake interrupt. These interrupts all share a single pin (IRQ),

but can be independ ently enab led/disa bled. In tran smit mod e,

all receive interru pts are automa tically disab led, and in receive

mode all transmit interrupts are automatically disabled.

However, the contents of the enable registers are preserved

when switching between tran sm it and receiv e mod es .

Interrupts are ena bled and the st atus read thr ough 6 registers:

Receive Interrupt Enable (Reg 0x07), Recei ve Interrupt S t atus

(Reg 0x08), Transmit Interrupt Enable (Reg 0x0D), Transmit

Interrupt Status (Reg 0x0E), Wake Enable (Reg 0x1C), Wake

Status (Reg 0x1D).

If more than 1 interrupt is enabled at any time, it is necessary

to read the relevant interrupt st atus register to determine which

event caused the IRQ pin to assert. Even when a given

interrupt source is disabled, the status of the condition that

would otherwise cause an interrupt can be determined by

reading the appropriate int errupt st atus regis ter. It is therefore

possible to use th e devic es with out mak ing us e of the I RQ pin

at all. Firmware can poll the interrupt status register(s) to wait

for an event, rather than using the IRQ pin.

The polarity of all interrupt s can be s et by writing to the Co nfiguration register (Reg 0x05), and it is possible to configure the

IRQ pin to be o pen drain (if a ctive low) o r open source (if active

high).

5.3.1 Wake Interrupt

When the PD pin is low, the oscillator is stopped. After PD is

deasserted, the oscillator takes time to start, and until it has

done so, it is not safe to use the SPI interface. The wake

interrupt indicates that the oscillator has started, and that the

device is ready to receive SPI transfers.

The wake interrupt is enabled by setting bit 0 of the Wake

Enable register (Reg 0x1C, bit 0=1). Whether or not a wake

interrupt is pendin g is indicated by the state of bit 0 of the Wake

Status register (Reg 0x1D, bit 0). Reading the Wake Status

register (Reg 0x1D) clears the interrupt.

5.3.2 Transmit Interrupts

Four interrupts a re p rov id ed t o fl ag the oc cu rren ce of t rans m it

events. The interrupts are enabled by writing to the Transmit

Interrupt Enable register (Reg 0x0D), and their status may be

determined by reading the Transmit Interrupt Status register

(Reg 0x0E). If more than 1 interrupt i s enabled , it is neces sary

to read the Transmit Interrupt Status register (Reg 0x0E) to

determine which event caused the IRQ pin to assert.

The function and operatio n of these interrupts are des cribed in

detail in

Section 7.0.

5.3.3 Receive Interrupts

Eight interrupts are provided to flag the occurrence of receive

events, four each fo r SERDES A and B. In 64 c hips /bit and 3 2

chips/bit DDR modes, only the SERDES A interrupts are

available, and the SERDES B interrupts will never trigger,

even if enabled. The interrupts are enabled by writing to the

Receive Interrupt Enab le regis ter (Reg 0x 07), and their st atu s

may be determin ed by reading the Rece ive Interrupt Status

register (Reg 0x08 ). If m ore th an on e int errup t i s en abl ed, it i s

necessary to read the Receive Interrupt Status register (Reg

0x08) to determine whic h e ven t ca us ed th e IRQ pin to as se rt.

The function and operatio n of these interrupts are des cribed in

detail in

Section 7.0.

Document 38-16007 Rev. *F Page 5 of 33

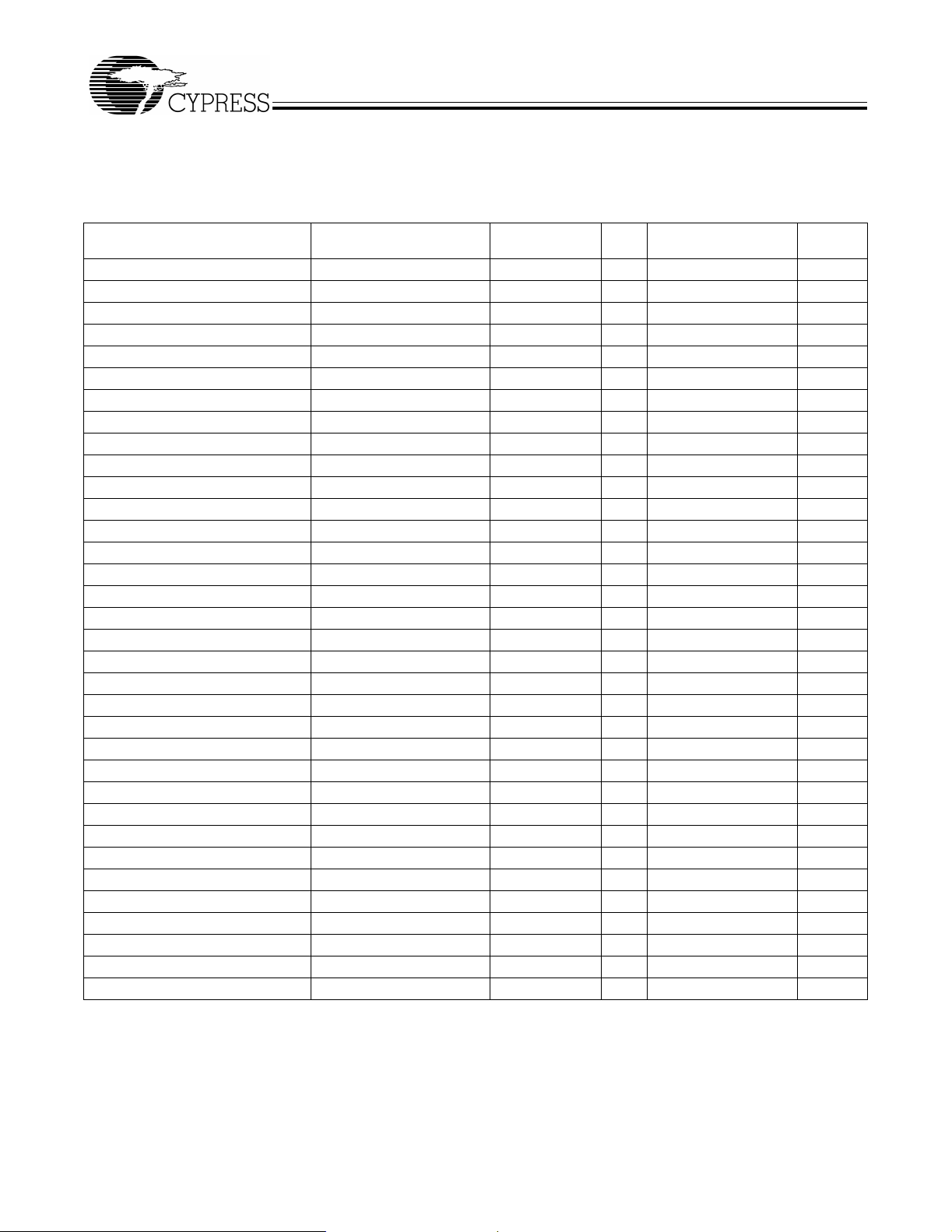

6.0 Application Examples

CYWUSB6932

CYWUSB6934

Battery

Optical

Mouse

Sensor

Buttons

LDO/

DC2DC

+

-

Vcc

3.3 V

RESET

Vcc

0.1µF

10pF

PCB Trace

Inverted “F”

Antenna

(PIFA)

RFOUT

PD

Application MCU

IRQ

SPI

WUSB LS

13MHz

Crystal

4

Figure 6-1. CYWUSB6932 Transmit-Only Battery-Powered Device

1.2 pF

PCB Tr ace

Inverted “F”

Antenna

(PIFA)

3.0 pF

3.3 nH

0.1 µF

3.6 pF

1.0 pF

13MHz

Cry stal

3.3V

1µF

RFOUT

RFIN

W irelessUSB L S

LDO

RESET

PD

IRQ

2.2K

2.2K

MISO

SS

0.1µF 4.7µF

SCK

MOSI

Figure 6-2. CYWUSB6934 USB Bridge Transceiver

5V

Vcc

Cypr ess

enCoRe

USB MCU

USB I/F

1.3K

D+/D-

2

Document 38-16007 Rev. *F Page 6 of 33

CYWUSB6932

CYWUSB6934

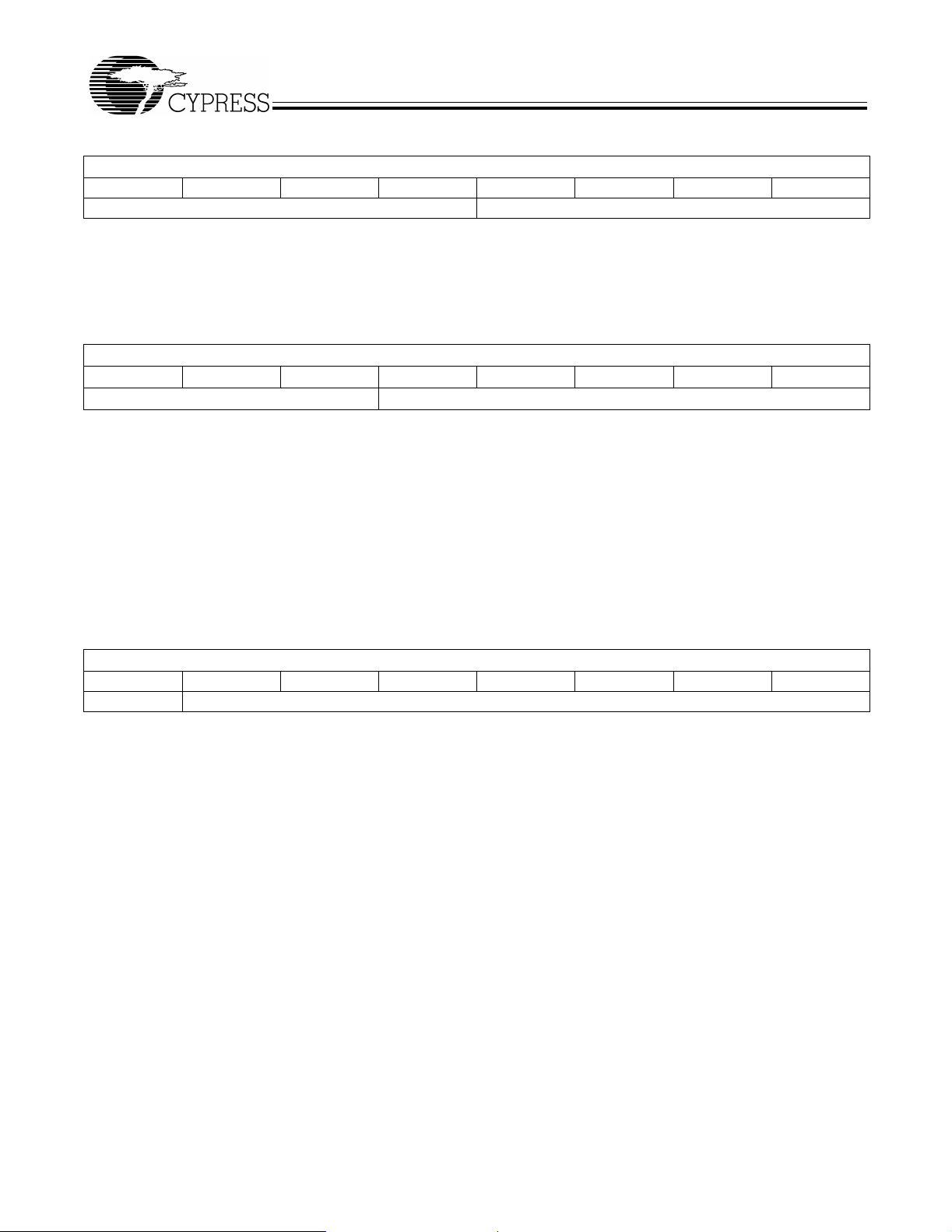

7.0 Register Descriptions

through the SPI interface. All registers are read and writable,

except where noted.

Table 7-1 displays the list of registers inside the

CYWUSB6932/CYWUSB6934 ICs that are addressable

Table 7-1. CYWUSB6932/CyWUSB6934 Register Map

[2]

CYWUSB6934

Register Name Mnemonic

Address Page Default Access

Revision ID REG_ID 0x00 8 0x07 RO

Synthesizer A Counter REG_SYN_A_CNT 0x01 8 0x00 RW

Synthesizer N Counter REG_SYN_N_CNT 0x02 8 0x00 RW

Control REG_CONTROL 0x03 9 0x00 RW

Data Rate REG_DATA_RATE 0x04 10 0x00 RW

Configuration REG_CONFIG 0x05 10 0x01 RW

SERDES Control REG_SERDES_CTL 0x06 11 0x03 RW

Receive Interrupt Enable REG_RX_INT_EN 0x07

Receive Interrupt Status REG_RX_INT_STAT 0x08

Receive Data A REG_RX_DATA_A 0x09

Receive Valid A REG_RX_VALID_A 0x0A

Receive Data B REG_RX_DATA_B 0x0B

Receive Valid B REG_RX_VALID_B 0x0C

[1]

[1]

[1]

[1]

[1]

[1]

12 0x00 RW

13 0x00 RO

14 0x00 RO

14 0x00 RO

14 0x00 RO

14 0x00 RO

Transmit Interrupt Enable REG_TX_INT_EN 0x0D 15 0x00 RW

Transmit Interrupt Status REG_TX_INT_STAT 0x0E 16 0x00 RO

Transmit Data REG_TX_DATA 0x0F 17 0x00 RW

Transmit Valid REG_TX_VALID 0x10 17 0x00 RW

PN Code REG_PN_CODE 0x11–0x18 17

Threshold Low REG_THRESHOLD_L 0x19

Threshold High REG_THRESHOLD_H 0x1A

[1]

[1]

0x1E8B6A3DE0E9B222 RW

18 0x08 RW

18 0x38 RW

Wake Enable REG_WAKE_EN 0x1C 18 0x00 RW

Wake Status REG_WAKE_STAT 0x1D 19 0x01 RO

Analog Control REG_ANALOG_CTL 0x20 19 0x04 RW

Channel REG_CHANNEL 0x21 20 0x00 RW

Receive Signal Strength Indicator REG_RSSI 0x22

[1]

20 0x00 RO

Power Control REG_PA 0x23 20 0x00 RW

Crystal Adjust REG_CRYSTAL_ADJ 0x24 21 0x00 RW

VCO Calibration REG_VCO_CAL 0x26 21 0x00 RW

AGC Control REG_AGC_CTL 0x2E 21 0x00 RW

Carrier Detect REG_CARRIER_DETECT 0x2F 21 0x00 RW

Clock Manual REG_CLOCK_MANUAL 0x32 22 0x00 RW

Clock Enable REG_CLOCK_ENABLE 0x33 22 0x00 RW

Synthesizer Lock Count REG_SYN_LOCK_CNT 0x38 22 0x64 RW

Manufacturing ID REG_MID 0x3C–0x3F 22 – RO

Notes:

1. Register not applicable to CYWUSB6932.

2. All registers are accessed Little Endian.

Document 38-16007 Rev. *F Page 7 of 33

CYWUSB6932

CYWUSB6934

Figure 7-1. Revision ID Register

Addr: 0x00 REG_ID Default: 0x07

76543210

Silicon ID Product ID

Bit Name Description

7:4 Silicon ID

3:0 Product ID These are the Product ID revision bits. Fixed at value 0111. These bits are read-only.

These are the Silicon ID revision bits. 0000 = Rev A, 0001 = Rev B, etc. These bits are read-only.

Figure 7-2. Synthesizer A Counter

Addr: 0x01 REG_SYN_A_CNT Default: 0x00

76543210

Reserved Count

Bit Name Description

7:5 Reserved These bits are reserved and should be written with zeros.

4:0 Count The Synthesizer A Counter register is used for diagnostic purposes and is not recommended for normal operation. The

Channel register is the recommended method of setting the Synthesizer frequency.

The Synthesizer A Count along with the Synthesizer N Count can be used to generate the Synthesizer frequency. The

range of valid values of the Synthesizer A Count is 0 through 31. Using the Synthesizer A and N Count register is an

alternative to using the Channel register. Selection between the use of the Channel register or the A and N registers is

done through the Channel register (Reg 0x21, bit 7). When in Channel mode the A and N Count bits can be used to read

the A and N values derived directly from the Channel.

Figure 7-3. Synthesizer N Counter

Addr: 0x02 REG_SYN_N_CNT Default: 0x00

76543210

Reserved Count

Bit Name Description

7 Reserved This bit is reserved and should be written with zero.

6:0 Count The Synthesizer N Counter register is used for diagnostic purposes and therefore is not recommended for normal

operation. The Channel register is the recommended method of setting the Synthesizer frequency.

The Synthesizer N Count along with the Synthesizer A Count can be used to generate the Synthesizer frequency. The

range of valid values of the Synthesizer N Count is 74 through 76. Using the Synthesizer A and N Count register is an

alternative to using the Channel register. Selection between the use of the Channel register or the A and N registers is

done through the Channel register (Reg 0x21, bit 7). When in Channel mode the A and N Count bits can be used to read

the A and N values derived directly from the Channel.

Document 38-16007 Rev. *F Page 8 of 33

CYWUSB6932

CYWUSB6934

Figure 7-4. Control

Addr: 0x03 REG_CONTROL Default: 0x00

76543210

RX

Enable

Bit Name Description

7 RX Enable The Receive Enable bit is used to place the IC in receive mode.

6 TX Enable The Transmit Enable bit is used to place the IC in transmit mode.

5 PN Code Select The Pseudo-Noise Code Select bit selects between the upper or lower half of the 64 chips/bit PN code.

4 Auto Syn Count

Select

3 Auto PA Disable The Auto Power Amplifier Disable bit is used to determine the method of controlling the Power Amplifier. The two options

2 PA Enable The PA Enable bit is used to enable or disable the Power Amplifier.

1 Auto Syn

Disable

0 Syn Enable The Synthesizer Enable bit is used to enable or disable the Synthesizer.

TX

Enable

1 = Receive Enabled

0 = Receive Disabled

1 = Transmit Enabled

0 = Transmit Disabled

1 = 32 Most Significant Bits of PN code are used

0 = 32 Least Significant Bits of PN code are used

This bit applies only when the Code Width bit is set to 32 chips/bit PN codes (Reg 0x04, bit 2=1).

The Auto Synthesizer Count Select bit is used to select the method of determining the settle time of the synthesizer. The

two options are a programmable settle time based on the value in Syn Lock Count register (Reg 0x38), in units of 2 us,

or by the auto detection of the synthesizer lock.

1 = Synthesizer settle time is based on a count in Syn Lock Count register (Reg 0x38)

0 = Synthesizer settle time is based on the internal synthesizer lock signal

It is recommended that the Auto Syn Count Select bit is set to 1 as that guarantees a consistent settle time for the

synthesizer.

are automatic control by the baseband or by firmware through register writes.

1 = Register controlled PA Enable.

0 = Auto PA Enable.

When this bit is set to 1 the state of PA enable is directly controlled by bit PA Enable (Reg 0x03, bit 2). It is recommended

that this bit is set to 0 leaving

1 = Power Amplifier Enabled

0 = Power Amplifier Disabled

This bit only applies when the Auto PA Disable bit is selected (Reg 0x03, bit 3=1), otherwise this bit is don’t care.

The Auto Synthesizer Disable bit is used to determine the method of controlling the Synthesizer. The two options are

automatic control by the baseband or by firmware through register writes.

1 = Register controlled Synthesizer Enable.

0 = Auto Synthesizer Enable.

When this bit is set to 1 the state of the Synthesizer is directly controlled by bit Syn Enable (Reg 0x03, bit 0). When this

bit is set to 0 the state of the Synthesizer is controlled by the Auto Syn Count Select bit (Reg 0x03, bit 4). It is recommended that this bit is set to 0 leaving the Synthesizer control to the baseband.

1 = Synthesizer Enabled

0 = Synthesizer Disabled

This bit only applies when Auto Syn Disable bit is selected (Reg 0x03, bit 1=1), otherwise this bit is don’t care.

PN Code

Select

Auto Syn

Count Select

Auto PA

Disable

the PA control to the baseband.

PA Enable Auto Syn

Disable

Syn Enable

Document 38-16007 Rev. *F Page 9 of 33

CYWUSB6932

CYWUSB6934

Figure 7-5. Data Rate

Addr: 0x04 REG_DATA_RATE Default: 0x00

76543210

Reserved Code Width Data Rate Sample Rate

Bit Name Description

7:3 Reserved

[3]

Code Width The Code Width bit is used to select between 32 chips/bit and 64 chips/bit PN codes.

2

[3]

Data Rate The Data Rate bit allows the user to select Double Data Rate mode of operation which delivers a raw data rate of

1

[3]

Sample

0

Rate

These bits are reserved and should be written with zeros.

1 = 32 chips/bit PN codes

0 = 64 chips/bit PN codes

The number of chips/bit used impacts a number of factors such as data throughput, range and robustness to interference.

By choosing a 32 chips/bit PN-code, the data throughput can be doubled or even quadrupled (when double data rate is

set). A 64 chips/bit PN code offers improved range over its 32 chips/bit counterpart as well as more robustness to

interference. By selecting to use a 32 chips/bit PN code a number of other register bits are impacted and need to be

addressed. These are PN Code Select (Reg 0x03, bit 5), Data Rate (Reg 0x04, bit 1), and Sample Rate (Reg 0x04, bit 0).

62.5kbits/sec.

1 = Double Data Rate - 2 bits per PN code (No odd bit transmissions)

0 = Normal Data Rate - 1 bit per PN code

This bit is applicable only when using 32 chips/bit PN codes which can be selected by setting the Code Width bit (Reg

0x04, bit 2=1). When using Double Data Rate, the raw data throughput is 62.5 kbits/sec because every 32 chips/bit PN

code is interpreted as 2 bits of data. When using this mode a single 64 chips/bit PN code is placed in the PN code register.

This 64 chips/bit PN code is then split into two and used by the baseband to offer the Double Data Rate capability.

using Normal Data Rate, the raw data throughput is 32kbits/sec.

potentially correlate data using two differing 32 chips/bit PN codes.

The Sample Rate bit allows the use of the 12x sampling when using 32 chips/bit PN codes and Normal Data Rate.

1 = 12x Oversampling

0 = 6x Oversampling

Using 12x oversampling improves the correlators receive sensitivity. When using 64 chips/bit PN codes or Double Data

Rate this bit is don’t care. When in the Normal Data Rate setting and choosing 12x oversampling, eliminates the ability to

receive from two different PN codes. Therefore the only time when 12x oversampling is to be selected is when a 32 chips/bit

PN code is being used and there is no need to receive data from sources with two different PN codes.

Additionally , Normal Data Rate enables the user to

When

Figure 7-6. Configuration

Addr: 0x05 REG_CONFIG Default: 0x01

76543210

Reserved Receive Invert Transmit Invert Reserved IRQ Pin Select

Bit Name Description

7:5 Reserved These bits are reserved and should be written with zeros.

4 Receive Invert The Receive Invert bit is used to invert the received data.

3 Transmit Invert The Transmit Invert bit is used to invert the data that is to be transmitted.

2 Reserved This bit is reserved and should be written with zero.

1:0 IRQ Pin Select The Interrupt Request Pin Select bits are used to determine the drive method of the IRQ pin.

Note:

3. The followin g Reg 0x04, bits 2:0 values are not valid:

• 001 - Not Valid

• 010 - Not Valid

• 011 - Not Valid

• 111 - Not Valid

1 = Inverted over-the-air Receive data

0 = Non-inverted over-the-air Receive data

1 = Inverted Transmit Data.

0 = Non-inverted Transmit Data.

11 = Open Source (asserted = 1, deasserted = Hi-Z)

10 = Open Drain (asserted = 0, deasserted = Hi-Z)

01 = CMOS (asserted = 1, deasserted = 0)

00 = CMOS Inverted (asserted = 0, deasserted = 1)

Document 38-16007 Rev. *F Page 10 of 33

Loading...

Loading...