CYPRESS CYW15G0201DXB, CYV15G0201DXB, CYP15G0201DXB User Manual

查询CYP15G0201DXB-BBXC供应商

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

Dual-channel HOTLink II™ Transceiver

Features

• Second-generation HOTLink® technology

• Compliant to multiple standards

— ESCON, DVB-ASI, Fibre Channel and Gigabit

Ethernet (IEEE802.3z)

— CPRI™ compliant

— CYW15G0201DXB compliant to OBSAI-RP3

— CYV15G0201DXB compliant to SMPTE 259M and

SMPTE 292M

— 8B/10B encoded or 10-bit unencoded data

• Dual channel transceiver operates from 195 to

1500 MBaud serial data rate

— CYW15G0201DXB operates from 195 to 1540 MBaud

serial data rate

— Aggregate throughput of 6 GBits/second

• Selectable parity check/generate

• Selectable dual-channel bonding option

— One 16-bit channels

• Skew alignment support for multiple bytes of offset

• Selectable input/output clocking options

• MultiFrame™ Receive Framer

— Bit and Byte alignment

— Comma or full K28.5 detect

— Single- or multi-byte framer for byte alignment

— Low-latency option

• Synchronous LVTTL parallel interface

• Internal phase-locked loops (PLLs) with no external

PLL components

• Optional Phase-Align Buffer in transmit path

• Optional Elasticity Buffer in receive path

• Dual differential PECL-compatible serial inputs per

channel

— Internal DC-restoration

• Dual differential PECL-compatible serial outputs per

channel

— Source matched for 50Ω transmission lines

— No external bias resistors required

— Signaling-rate controlled edge-rates

• Compatible with

— Fiber-optic modules

— Copper cables

— Circuit board traces

• JTAG boundary scan

• Built-In Self-Test (BIST) for at-speed link testing

• Per-channel Link Quality Indicator

— Analog signal detect

— Digital signal detect

• Low power 1.8W @ 3.3V typical

• Single 3.3V supply

• 196-ball BGA

• Pb-Free package option available

• 0.25µ BiCMOS technology

Functional Description

The CYP(V)15G0201DXB

Transceiver is a point-to-point or point-to-multipoint communications building block allowing the transfer of data over

high-speed serial links (optical fiber, balanced, and unbalanced copper transmission lines) at signaling speeds ranging

from 195- to 1500-MBaud per serial link.

The CYV15G0201DXB satisfies the SMPTE 259M and

SMPTE 292M compliance as per the EG34-1999 Pathological

Test Requirements.

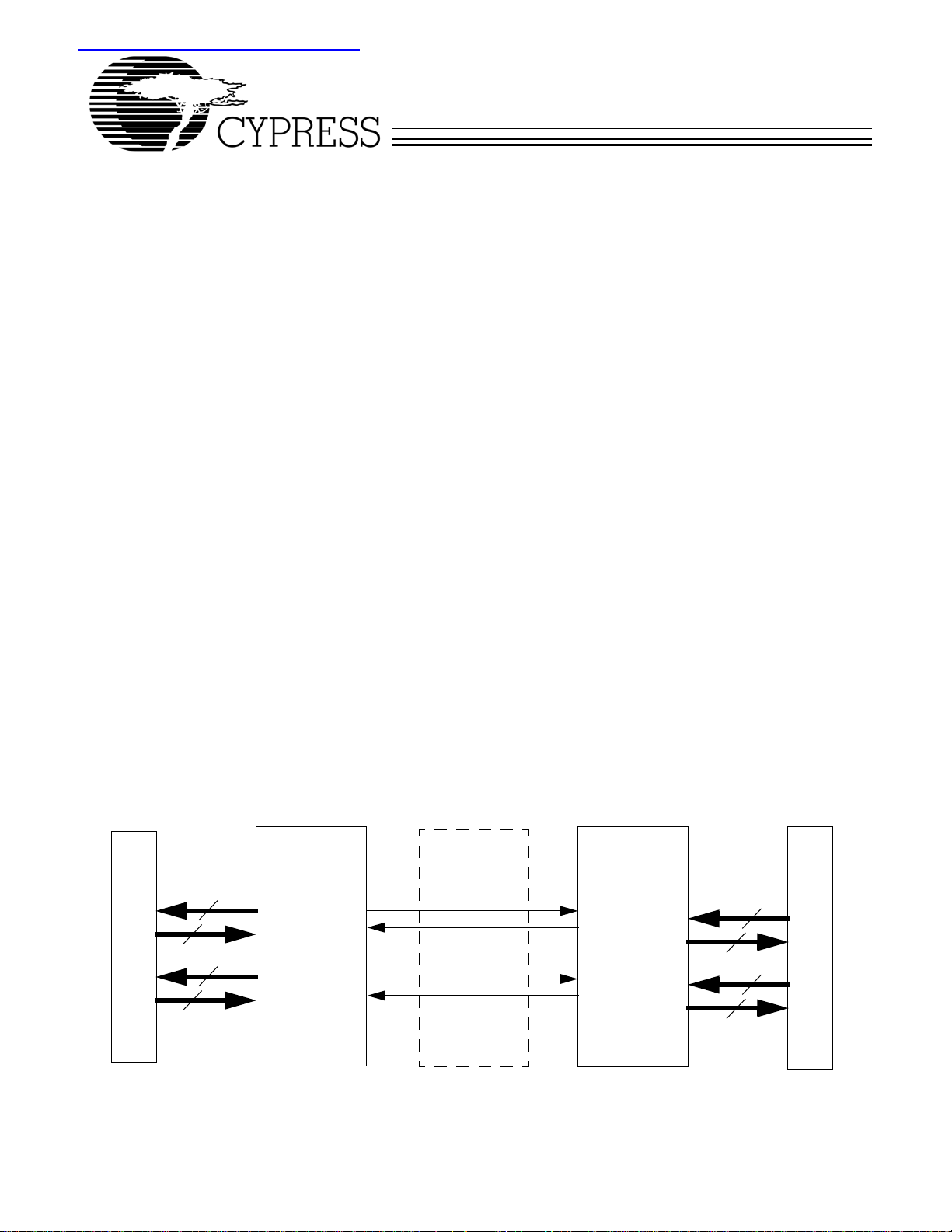

[1]

Dual-channel HOTLink II™

10

10

10

10

CYP(V)(W)15G0201DXB

System Host

Serial Links

Serial Links

Backplane or

Cabled

Connections

CYP(V)(W)15G0201DXB

10

10

10

10

System Host

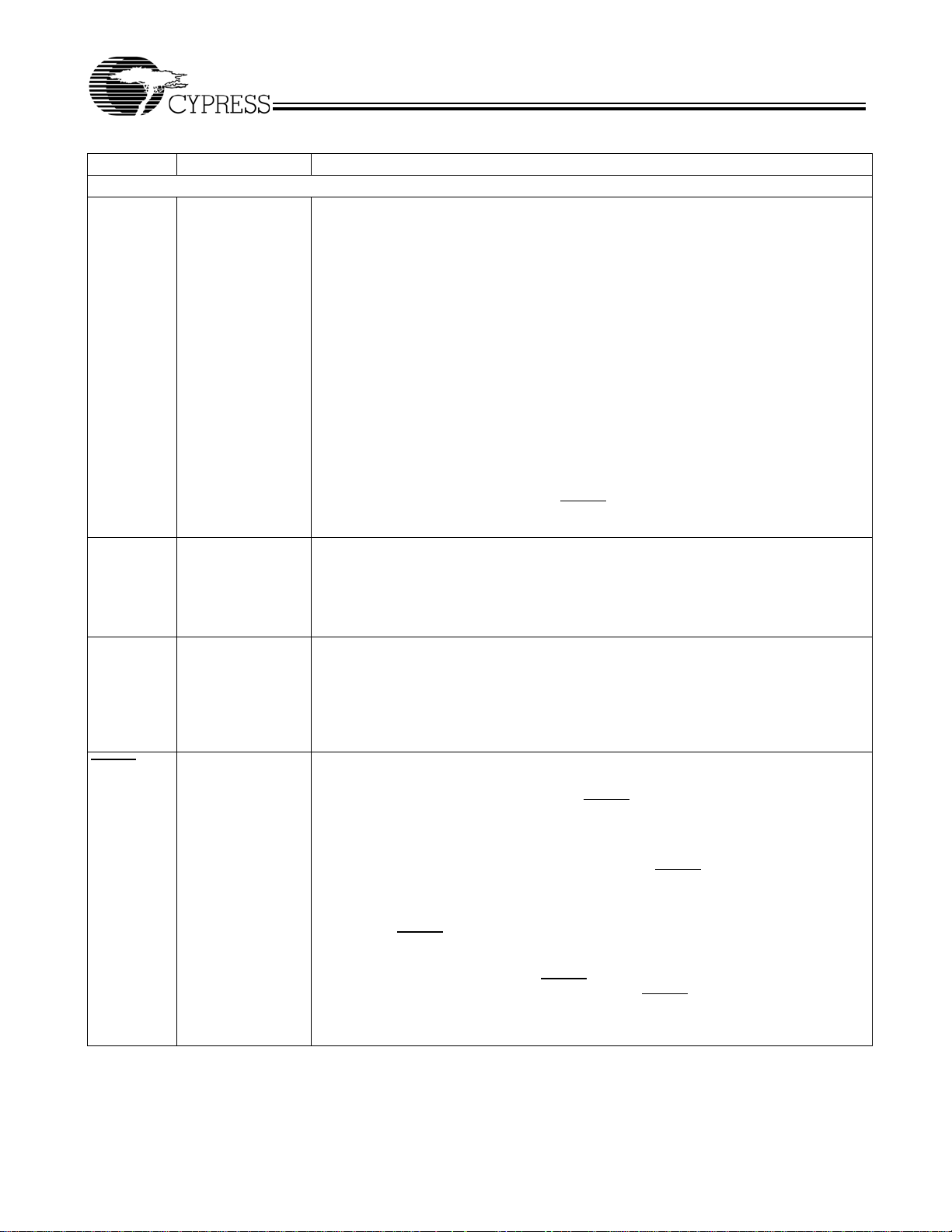

Figure 1. HOTLink II™ System Connections

Note:

1. CYV15G0201DXB refers to SMPTE 259M and SMPTE 292M compliant devices. CYW15G0201DXB refers to OBSAI RP3 compliant devices (maximum

operating data rate is 1540 MBaud). CYP15G0201DXB refers to devices not compliant to SMPTE 259M and SMPTE 292M pathological test requirements and

also OBSAI RP3 operating datarate of 1536 MBaud. CYP(V)(W)15G0201DXB refers to all three devices.

Cypress Semiconductor Corporation • 3901 North First Street • San Jose, CA 95134 • 408-943-2600

Document #: 38-02058 Rev. *H Revised March 25, 2005

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

The CYW15G0201DXB

which includes operation at the OBSAI RP3 datarate of both

1536 MBaud and 768 MBaud.

The two channels may be combined to allow transport of wide

buses across significant distances with minimal concern for

offsets in clock phase or link delay. Each transmit channel

accepts parallel characters in an Input Register, encodes each

character for transport, and converts it to serial data. Each

receive channel accepts serial data and converts it to parallel

data, decodes the data into characters, and presents these

characters to an Output Register. Figure 1 illustrates typical

connections between independent host systems and corresponding CYP(V)(W)15G0201DXB parts. As a second-generation HOTLink device, the CYP(V)(W)15G0201DXB extends

the HOTLink family with enhanced levels of integration and

faster data rates, while maintaining serial-link compatibility

(data, command, and BIST) with other HOTLink devices.

The transmit (TX) section of the CYP(V)(W)15G0201DXB

Dual HOTLink II consists of two byte-wide channels that can

be operated independently or bonded to form wider buses.

Each channel can accept either 8-bit data characters or

pre-encoded 10-bit transmission characters. Data characters

are passed from the Transmit Input Register to an embedded

8B/10B Encoder to improve their serial transmission characteristics. These encoded characters are then serialized and

output from dual Positive ECL (PECL) compatible differential

transmission-line drivers at a bit-rate of either 10 or 20 times

the input reference clock.

The receive (RX) section of the CYP(V)(W)15G0201DXB Dual

HOTLink II consists of two byte-wide channels that can be

operated independently or synchronously bonded for greater

bandwidth. Each channel accepts a serial bit-stream from one

of two PECL-compatible differential line receivers and, using

a completely integrated PLL Clock Synchronizer, recovers the

timing information necessary for data reconstruction. Each

recovered bit-stream is deserialized and framed into

characters, 8B/10B decoded, and checked for transmission

[1]

operates from 195 to 1540 MBaud,

errors. Recovered decoded characters are then written to an

internal Elasticity Buffer, and presented to the destination host

system. The integrated 8B/10B Encoder/Decoder may be

bypassed for systems that present externally encoded or

scrambled data at the parallel interface.

For those systems using buses wider than a single byte, the

two independent receive paths can be bonded together to

allow synchronous delivery of data across a two-byte-wide

(16-bit) path.

The parallel I/O interface may be configured for numerous

forms of clocking to provide the highest flexibility in system

architecture. In addition to clocking the transmit path interfaces

from one of multiple sources, the receive interface may be

configured to present data relative to a recovered clock or to a

local reference clock.

Each transmit and receive channel contains independent

Built-In Self-Test (BIST) pattern generators and checkers. This

BIST hardware allows at-speed testing of the high-speed

serial data paths in each transmit and receive section, and

across the interconnecting links.

HOTLink II devices are ideal for a variety of applications where

parallel interfaces can be replaced with high-speed,

point-to-point serial links. Some applications include

interconnecting backplanes on switches, routers,

base-stations, servers and video transmission systems.

The CYV15G0201DXB is verified by testing to be compliant to

all the pathological test patterns, documented in SMPTE

EG34-1999 for both the SMPTE 259M and 292M signaling

rates. The tests ensure that the receiver recovers data with no

errors for the following patterns:

1. Repetitions of 20 ones and 20 zeros.

2. Single burst of 44 ones or 44 zeros.

3. Repetitions of 19 ones followed by 1 zero or 19 zeros

followed by 1 one.

Document #: 38-02058 Rev. *H Page 2 of 46

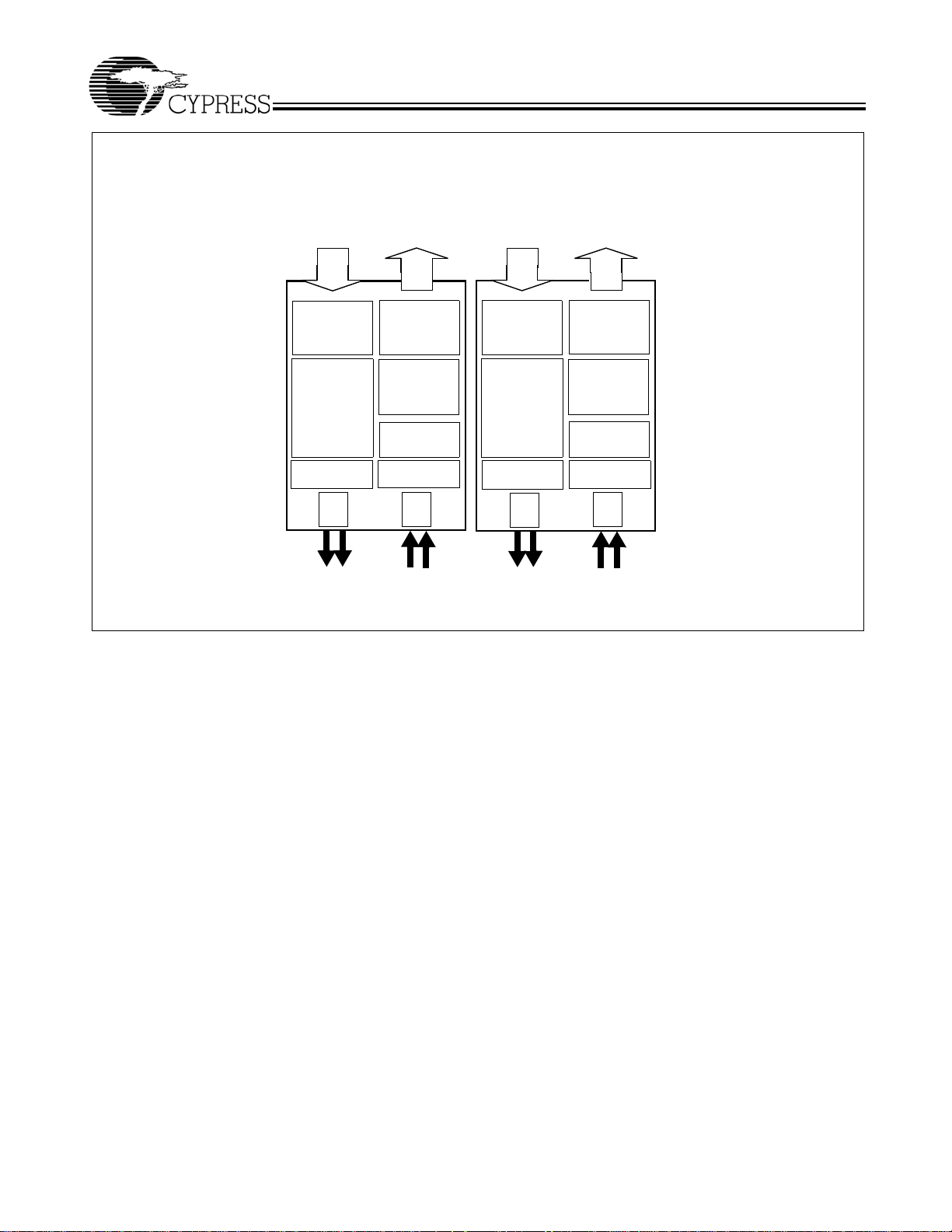

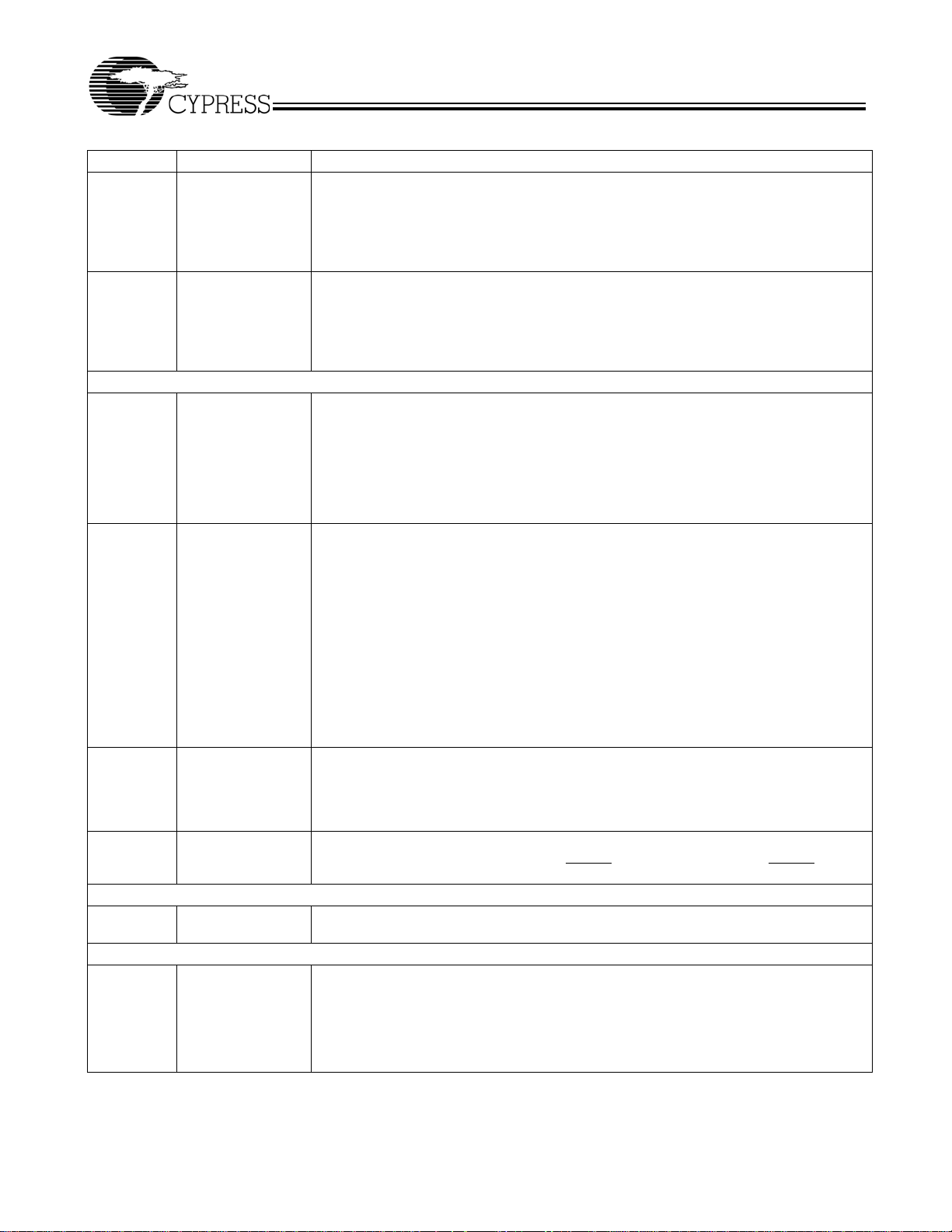

Transceiver Logic Block Diagram

TXDA[7:0]

TXCTA[1:0]

x10

RXDA[7:0]

RXSTA[2:0]

x11

TXDB[7:0]

TXCTB[1:0]

x10

RXDB[7:0]

RXSTB[2:0]

x11

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

Phase

Align

Buffer

Encoder

8B/10B

Serializer

TX

OUTA1±

OUTA2±

Elasticity

Buffer

Decoder

8B/10B

Framer

Deserializer

RX

INA1±

INA2±

Phase

Align

Buffer

Encoder

8B/10B

Serializer

TX

OUTB1±

OUTB2±

Elasticity

Buffer

Decoder

8B/10B

Framer

Deserializer

RX

INB1±

INB2±

Document #: 38-02058 Rev. *H Page 3 of 46

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

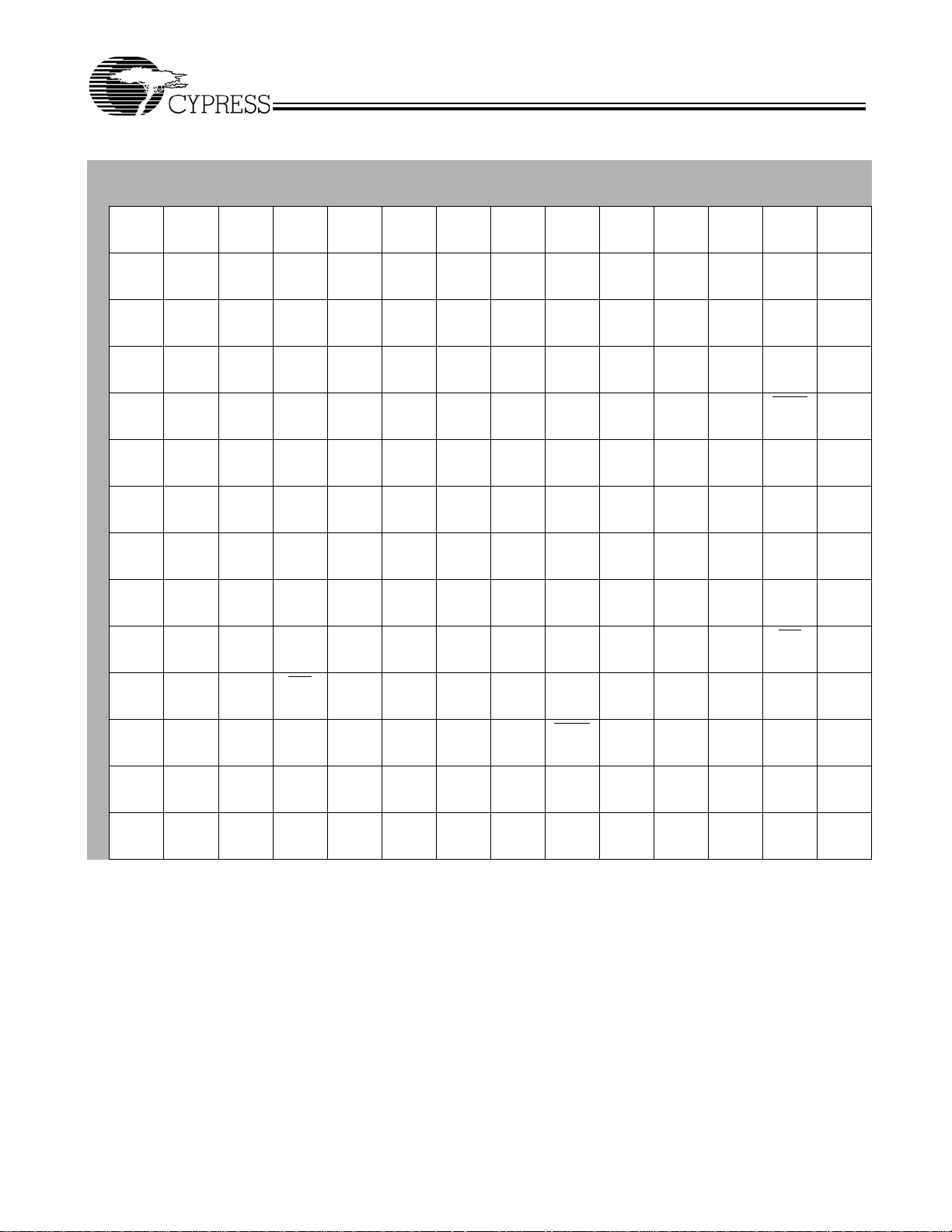

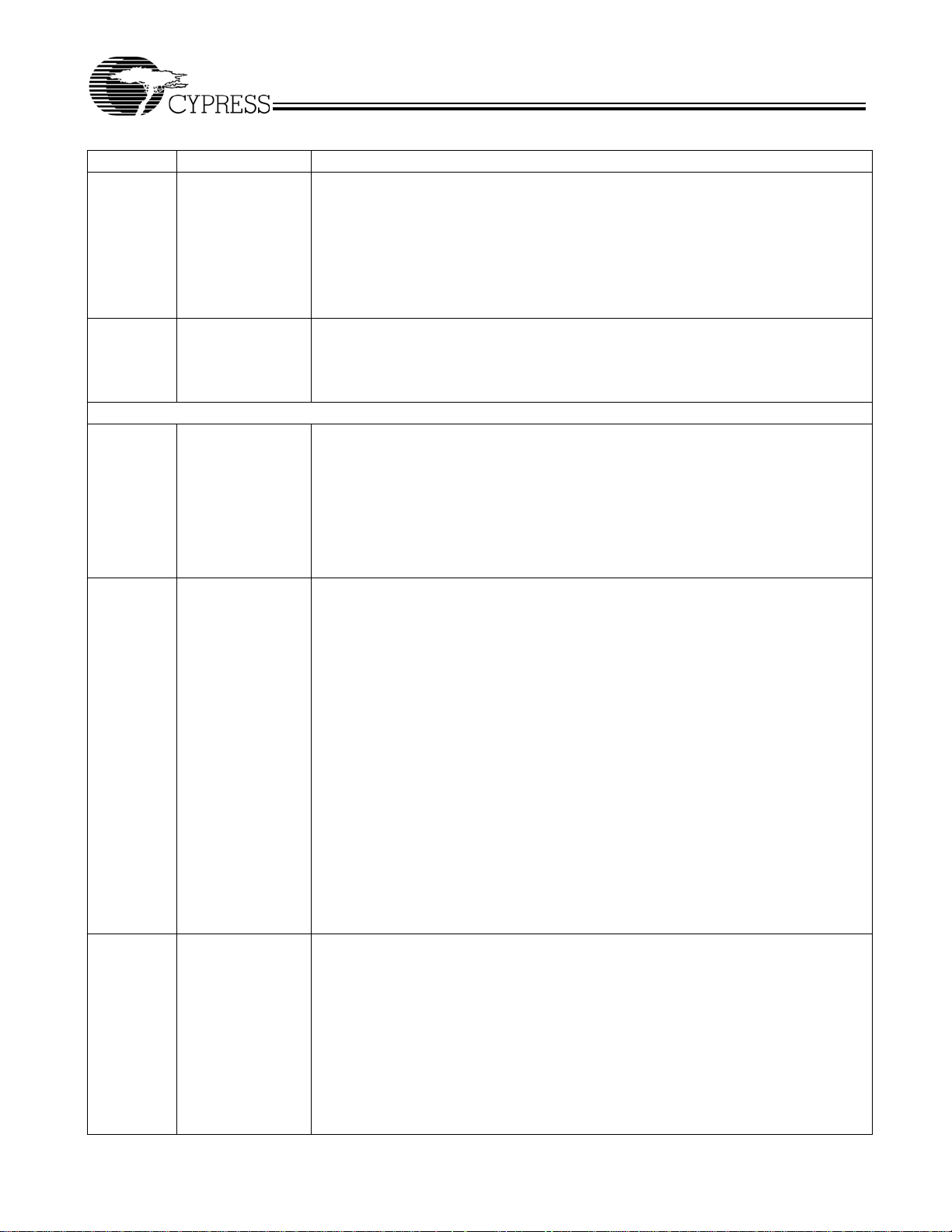

Pin Configuration (Top View)

[2]

1 2 3 4 5 6 7 8 9 10 11 12 13 14

V

INA2+ OUTA2– V

CC

INA1+ OUTA1– V

CC

CC

V

INB2+ OUTB2– V

CC

INB1+ OUTB1– V

CC

A

TDO INA2– OUTA2+ V

INA1– OUTA1+ NC NC INB2– OUTB2+ V

CC

INB1– OUTB1+ BOE[3]

CC

B

NC RFEN V

LPEN RXLE RXRATE GND GND SPDSEL PARCTL RFMODE V

CC

SDASEL BOE[2]

CC

C

V

CC

V

CC

NC TXRATE RXMODE[1]RXMODE[0]GND GND TCLK TDI INSELB INSELA V

CC

D

BISTLE FRAMCHARTXMODE[1]TXMODE[0]BOE[0] BOE[1] GND GND TXOPB TXPERB TXCKSEL RXCKSEL TRSTZ TMS

E

DECMODEOELE RXCLKC+ RXSTA[2] RXSTA[1] GNDGNDGNDGNDTXDB[4] TXDB[3] TXDB[2] TXDB[1] TXDB[0]

F

V

CC

NC GNDGNDGNDGNDGNDGNDGNDGNDGNDGND NC V

G

V

CC

NC GNDGNDGNDGNDGNDGNDGNDGNDGNDGND NC V

H

RXSTA[0] RXOPA RXDA[0] RXDA[1] RXDA[2] GNDGNDGNDGNDTXCTB[0] TXCTB[1] TXDB[7] TXDB[6] TXDB[5]

J

RXDA[3] RXDA[4] RXDA[5] RXDA[6] TXDA[4] TXCLKA GND GND NC RXOPB RXCLKB+ RXCLKB- LFIB TXCLKB

K

V

CC

V

RXDA[7] LFIA TXDA[3] TXOPA GND GND SCSEL RXSTB[2] RXSTB[1] RXDB[7] V

CC

CC

L

RXCLKA- TXCTA[1] V

CC

NC TXDA[2] TXPERA GND GND TXRST NC RXSTB[0] V

RXDB[5] RXDB[6]

CC

M

RXCLKA+ TXCTA[0] TXDA[6] V

TXDA[1] NC NC NC REFCLK- TXCLKO+ V

CC

RXDB[2] RXDB[3] RXDB[4]

CC

N

V

TXDA[7] TXDA[5] V

CC

TXDA[0] NC V

CC

CC

V

REFCLK+ TXCLKO- V

CC

RXDB[1] RXDB[0] V

CC

P

Note:

2. NC = Do not connect.

CC

V

CC

CC

CC

V

CC

CC

Document #: 38-02058 Rev. *H Page 4 of 46

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

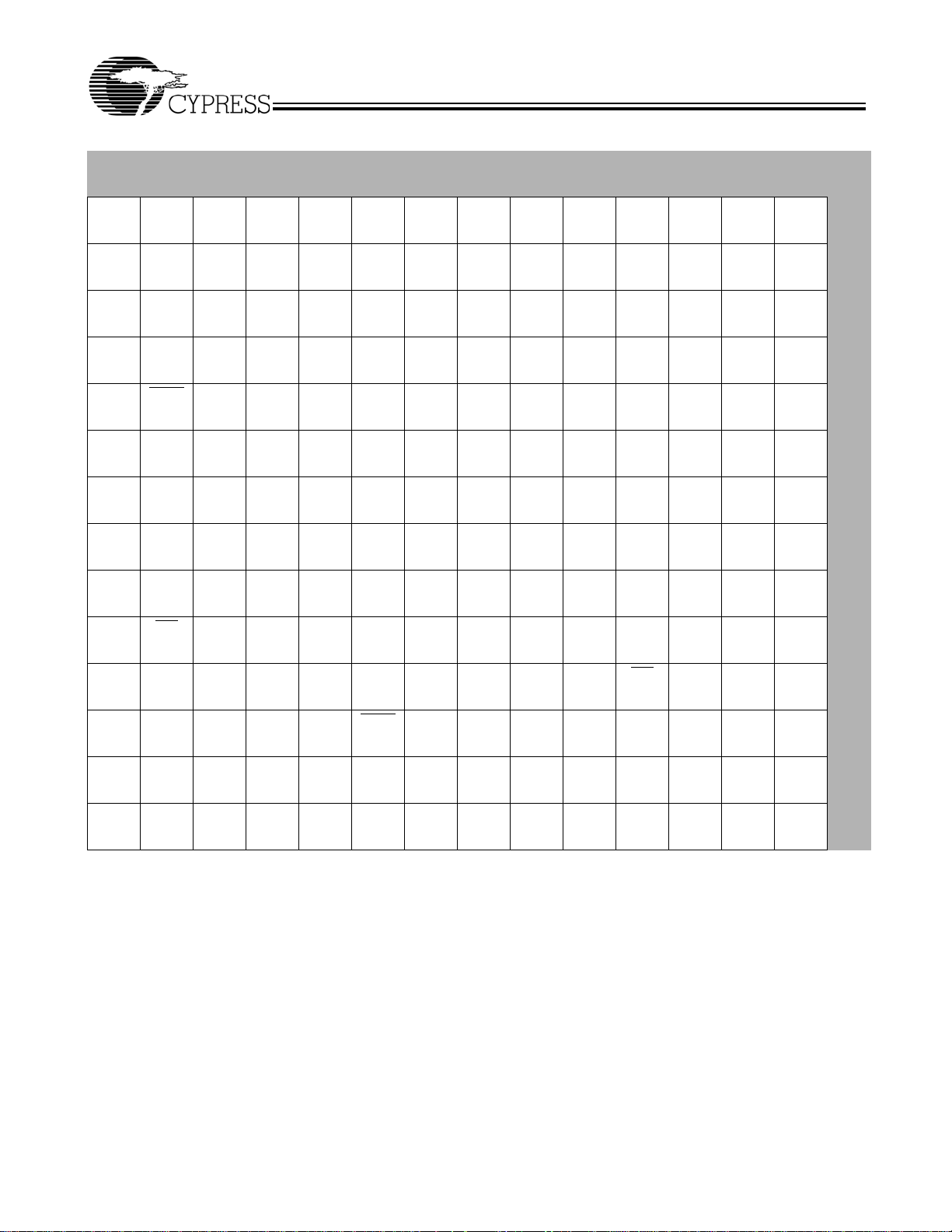

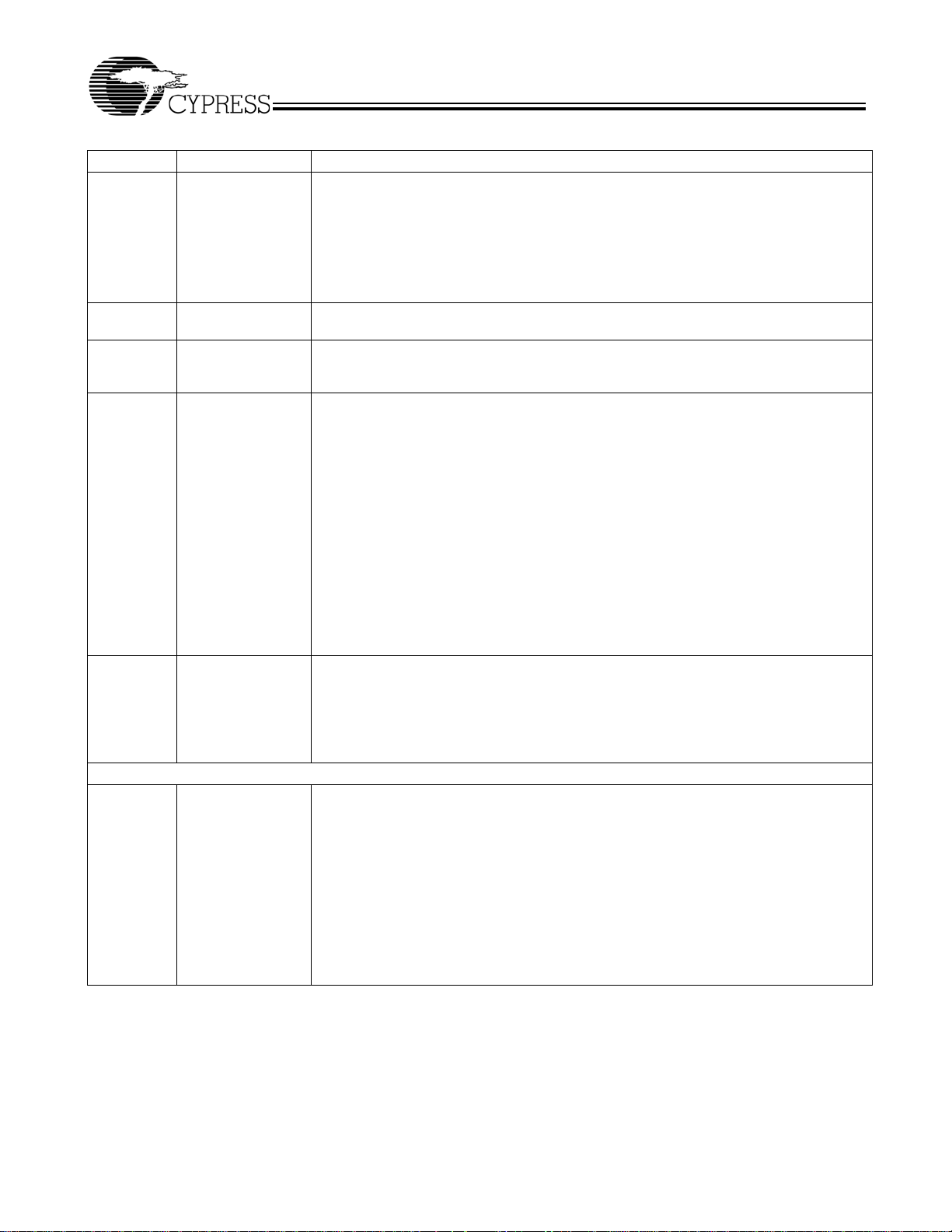

Pin Configuration (Bottom View)

[2]

14 13 12 11 10 9 8 7 6 5 4 3 2 1

V

OUTB1– INB1+ V

CC

BOE[3] OUTB1+ INB1– V

BOE[2] SDASEL V

V

TMS TRSTZ RXCKSEL TXCKSEL TXPERB TXOPB GND GND BOE[1] BOE[0] TXMODE[0] TXMODE[1]FRAMCHAR BISTLE

TXDB[0] TXDB[1] TXDB[2] TXDB[3] TXDB[4] GNDGNDGNDGNDRXSTA[1] RXSTA[2] RXCLKC+ OELE DECMODE

V

V

TXDB[5] TXDB[6] TXDB[7] TXCTB[1] TXCTB[0] GNDGNDGNDGNDRXDA[2] RXDA[1] RXDA[0] RXOPA RXSTA[0]

TXCLKB LFIB RXCLKB- RXCLKB+ RXOPB NC GND GND TXCLKA TXDA[4] RXDA[6] RXDA[5] RXDA[4] RXDA[3]

V

RXDB[6] RXDB[5] V

RXDB[4] RXDB[3] RXDB[2] VCCTXCLKO+ REFCLK- NC NC NC TXDA[1] V

V

V

CC

CC

CC

CC

CC

CC

NC GND GND GND GND GND GND GND GND GND GND NC V

NC GND GND GND GND GND GND GND GND GND GND NC V

V

CC

RXDB[0] RXDB[1] V

INSELA INSELB TDI TCLK GND GND RXMODE[0] RXMODE[1] TX RA TE N C V

RXDB[7] RXSTB[1] RXSTB[2] SCSEL GND GND TXOPA TXDA[3] LFIA RXDA[7] V

RFMODE PARCTL SPDSEL GND GND RXRATE RXLE LPEN V

CC

RXSTB[0] NC TXRST GND GND TXPERA TXDA[2] NC V

CC

OUTB2– INB2+ V

CC

OUTB2+ INB2– NC NC OUTA1+ INA1– V

CC

TXCLKO- REFCLK+ V

CC

CC

CC

V

OUTA1– INA1+ V

CC

V

CC

NC TXDA[0] V

OUTA2– INA2+ V

CC

OUTA2+ INA2– TDO

CC

RFEN NC

CC

TXCTA[1] RXCLKA-

CC

TXDA[6] TXCTA[0] RXCLKA+

CC

TXDA[5] TXDA[7] V

CC

CC

CC

CC

V

CC

CC

CC

V

CC

CC

A

B

C

D

E

F

G

H

J

K

L

M

N

P

Document #: 38-02058 Rev. *H Page 5 of 46

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

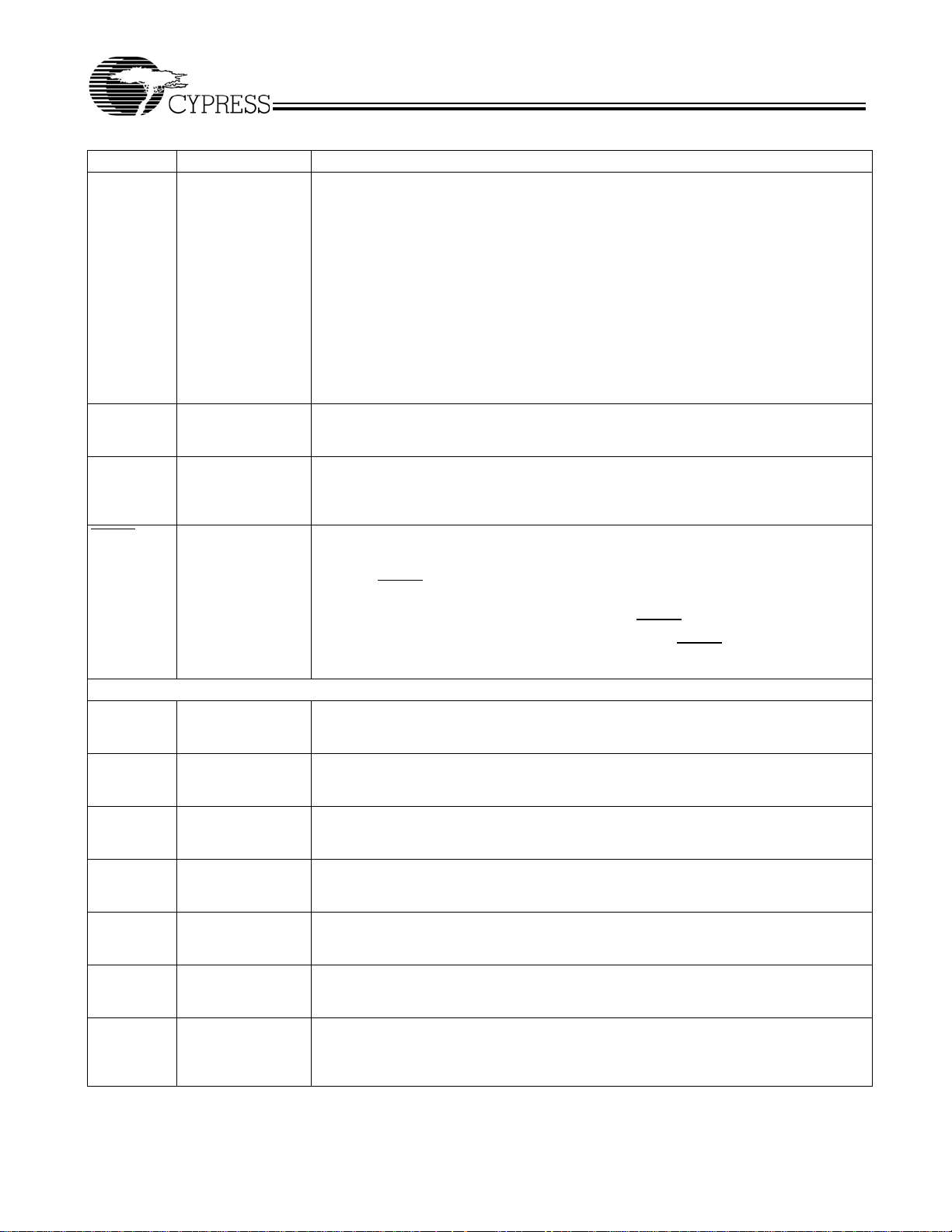

Pin Descriptions CYP(V)(W)15G0201DXB Dual HOTLink II Transceiver

Pin Name I/O Characteristics Signal Description

Transmit Path Data Signals

TXPERA

TXPERB

TXCTA[1:0]

TXCTB[1:0]

TXDA[7:0]

TXDB[7:0]

TXRST

Note:

3. When REFCLK is configured for half-rate operation (TXRATE = HIGH), these inputs are sampled (or the outputs change) relative to both the rising and falling

edges of REFCLK.

LVTTL Output,

changes relative to

REFCLK↑

LVTTL Input,

synchronous,

sampled by the

selected TXCLKx↑

or REFCLK↑

LVTTL Input,

synchronous,

sampled by the

selected TXCLKx↑

or REFCLK↑

LVTTL Input,

asynchronous,

internal pull-up,

REFCLK↑

[3]

[3]

[3]

[3]

Transmit Path Parity Error. Active HIGH. Asserted (HIGH) if parity checking is enabled

and a parity error is detected at the Encoder. This output is HIGH for one transmit character

clock period to indicate detection of a parity error in the character presented to the Encoder.

If a parity error is detected, the character in error is replaced with a C0.7 character to force

a corresponding bad-character detection at the remote end of the link. This replacement

takes place regardless of the encoded/non-encoded state of the interface.

When BIST is enabled for the specific transmit channel, BIST progress is presented on

these outputs. Once every 511 character times (plus a 16-character Word Sync Sequence

when the receive channels are clocked by a common clock, i.e., RXCKSEL = LOW or

HIGH), the associated TXPERx signal pulses HIGH for one transmit-character clock period

(if RXCKSEL = MID) or seventeen transmit- character clock periods (if RXCKSEL = LOW

or HIGH) to indicate a complete pass through the BIST sequence. For RXCKSEL = LOW

or HIGH, if TXMODE[1:0] = LL, then no Word Sync Sequence is sent in BIST, and TXPERx

pulses HIGH for one transmit-character clock period.

These outputs also provide indication of a transmit Phase-Align Buffer underflow or

overflow. When the transmit Phase-Align Buffers are enabled (TXCKSEL ≠ LOW, or

TXCKSEL = LOW and TXRATE = HIGH), if an underflow or overflow condition is detected,

TXPERx for the channel in error is asserted and remains asserted until either an atomic

Word Sync Sequence is transmitted or TXRST

Phase-Align Buffers.

Transmit Co ntrol. These inputs are captured on the rising edge of the transmit interface

clock as selected by TXCKSEL, and are passed to the Encoder or Transmit Shifter. They

identify how the associated TXDx[7:0] characters are interpreted. When the Encoder is

bypassed, these inputs are interpreted as data bits. When the Encoder is enabled, these

inputs determine if the TXDx[7:0] character is encoded as Data, a Special Character code,

or replaced with other Special Character codes. See Table 1 for details.

Transmit Data Inputs. These inputs are captured on the rising edge of the transmit

interface clock (selected by TXCKSEL) and passed to the Encoder or Transmit Shifter.

When the Encoder is enabled (TXMODE[1:0] ≠ LL), TXDx[7:0] specify the specific data or

command character to be sent.

When the Encoder is bypassed, these inputs are interpreted as data bits of the 10-bit input

character. See Tabl e 1 for details.

Transmit Clock Phase Reset. Transmit Clock Phase Reset. Active LOW. When sampled

LOW, the transmit Phase-align Buffers are allowed to adjust their data-transfer timing

(relative to the selected input clock) to allow clean transfer of data from the Input Register

to the Encoder or Transmit Shifter. When TXRST

relationship between the associated TXCLKx and the internal character-rate clock is fixed

and the device operates normally.

When configured for half-rate REFCLK sampling of the transmit character stream

(TXCKSEL = LOW and TXRATE = HIGH), assertion of TXRST

Phase-align buffer faults caused by highly asymmetric REFCLK periods or REFCLKs with

excessive cycle-to-cycle jitter. During this alignment period, one or more characters may be

added to or lost from all the associated transmit paths as the transmit Phase-align Buffers

are adjusted. TXRST

of REFCLK to ensure the reset operation is initiated correctly on all channels. This input is

ignored when both TXCKSEL and TXRATE are LOW, since the phase align buffer is

bypassed. In all other configurations, TXRST

to ensure proper operation of the Phase-align buffer. TXRST

presence of a valid TXCLKx and after allowing enough time for the TXPLL to lock to the

reference clock (as specified by parameter t

must be sampled LOW by a minimum of two consecutive rising edges

is sampled LOW to re-center the transmit

is sampled HIGH, the internal phase

is only used to clear

should be asserted during device initialization

should be asserted after

).

TXLOCK

Document #: 38-02058 Rev. *H Page 6 of 46

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

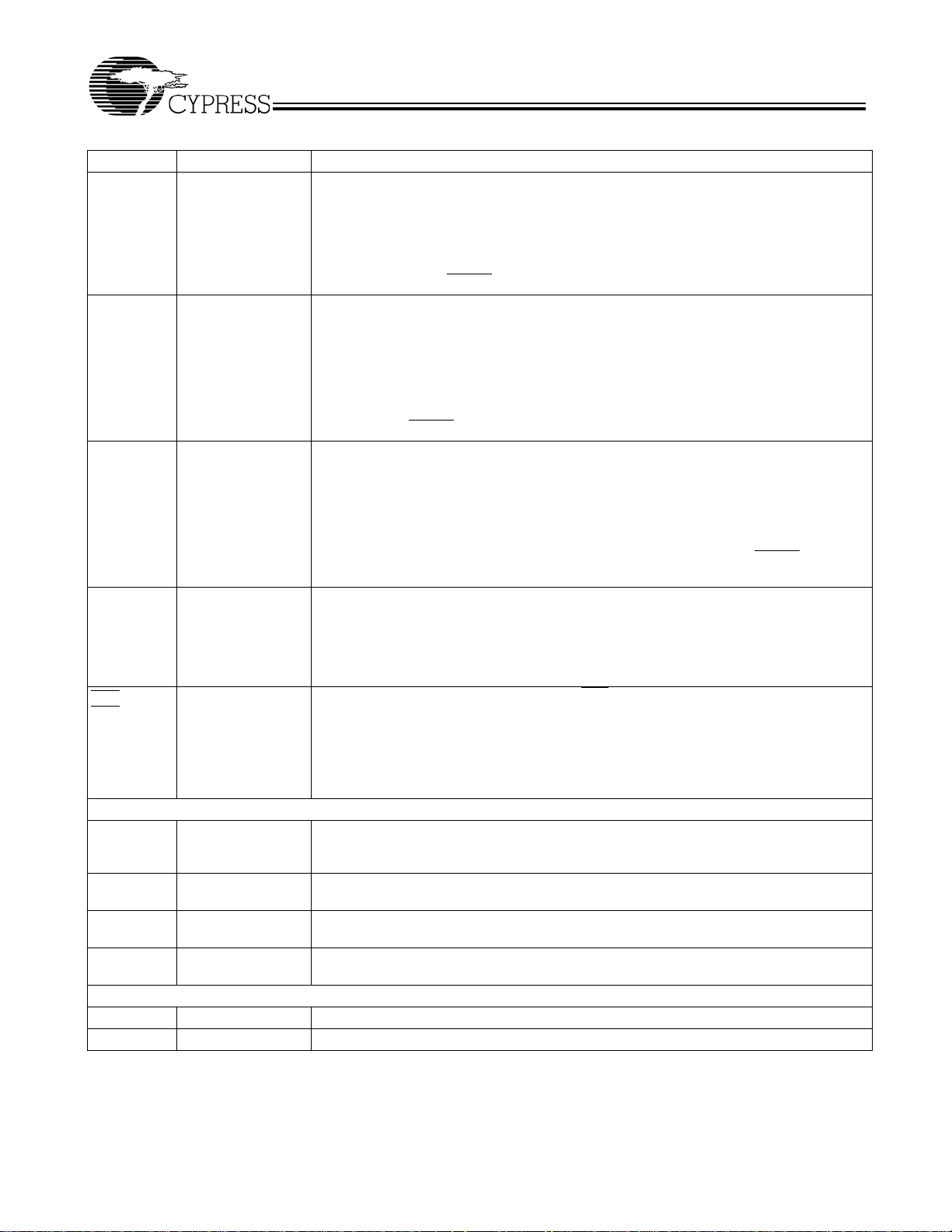

Pin Descriptions CYP(V)(W)15G0201DXB Dual HOTLink II Transceiver (continued)

Pin Name I/O Characteristics Signal Description

SCSEL LVTTL Input,

synchronous,

internal pull-down,

sampled by

TXOPA

TXOPB

TXCLKA↑

or REFCLK↑

LVTTL Input,

synchronous,

[3]

internal pull-up,

sampled by the

respective TXCLKx↑

or REFCLK↑

[3]

Transmit Path Clock and Clock Control

TXCKSEL 3-Level Select

Static Control Input

TXRATE LVTTL Input,

Static Control input,

internal pull-down

TXCLKO± LVTTL Output Transmit Clock Output. This true and complement output clock is synthesized by the

TXCLKA

TXCLKB

LVTTL Clock Input,

internal pull-down

Transmit Path Mode Control

TXMODE[1:0] 3-Level Select

Static Control inputs

Receive Path Data Signals

RXDA[7:0]

RXDB[7:0]

LVTTL Output,

synchronous to the

selected RXCLKx↑

output or

REFCLK↑

Note:

4. 3-Level select inputs are used for static configuration. They are ternary (not binary) inputs that make use of non-standard logic levels of LOW, MID, and HIGH.

The LOW level is usually implemented by direct connection to V

not connected or allowed to float, a 3-Level select input will self-bias to the MID level.

[3]

input

Special Character Select. Used in some transmit modes along with TXCTx[1:0] to encode

special characters or to initiate a Word Sync Sequence. When the transmit paths are

configured for independent inputs clocks (TXCKSEL = MID), SCSEL is captured relative to

TXCLKA↑.

Transmit Path Odd Parity. When parity checking is enabled (PARCTL ≠ LOW), the parity

captured at these inputs is XORed with the data on the associated transmit data TXDx bus

to verify the integrity of the captured character.

[4]

Transmit Clock Select. Selects the clock source, used to write data into the Transmit Input

Register, of the transmit channel(s).

When LOW, both Input Registers are clocked by REFCLK↑

[3]

. When MID, TXCLKx↑ is used

as the Input Register clock for TXDx[7:0] and TXCTx[1:0]. When HIGH, TXCLKA↑ is used

to clock data into the Input Register of each channel.

When TXCKSEL = MID or HIGH (TXCLKx or TXCLKA selected to clock input register),

configuring TXRATE = HIGH (Half-rate REFCLK) is an invalid mode of operation.

Transmit PLL Clock Rate Select. When TXRATE = HIGH, the Transmit PLL multiplies

REFCLK by 20 to generate the serial symbol-rate clock. When TXRATE = LOW, the transmit

PLL multiples REFCLK by 10 to generate the serial symbol-rate clock. See Ta ble 1 0 for a

list of operating serial rates.

When REFCLK is selected to clock the receive parallel interfaces (RXCKSEL = LOW), the

TXRATE input also determines if the clocks on the RXCLKA± and RXCLKC± outputs are

full or half-rate. When TXRATE = HIGH (REFCLK is half-rate), the RXCLKA± and RXCLKC±

output clocks are also half-rate clocks and follow the frequency and duty cycle of the

REFCLK input. When TXRATE = LOW (REFCLK is full-rate), the RXCLKA± and RXCLKC±

output clocks are full-rate clocks and follow the frequency and duty cycle of the REFCLK

input.

When TXCKSEL = MID or HIGH (TXCLKx or TXCLKA selected to clock input register),

configuring TXRATE = HIGH (Half-rate REFCLK) is an invalid mode of operation.

transmit PLL and operates synchronous to the internal transmit character clock. It operates

at either the same frequency as REFCLK (when TXRATE = LOW), or at twice the frequency

of REFCLK (when TXRATE = HIGH). This output clock has no direct phase relationship to

REFCLK.

Transmit Path Input Clocks. These clocks must be frequency-coherent to TXCLKO±, but

may be offset in phase. The internal operating phase of each input clock (relative to

REFLCK or TXCLKO±) is adjusted when TXRST = LOW and locked when TXRST =HIGH.

[4]

Transmit Operating Mode. These inputs are interpreted to select one of nine operating

modes of the transmit path. See Tab le 3 for a list of operating modes.

Parallel Data Output. These outputs change following the rising edge of the selected

receive interface clock.

When the Decoder is enabled (DECMODE = HIGH or MID), these outputs represent either

received data or special characters. The status of the received data is represented by the

values of RXSTx[2:0]. When the Decoder is bypassed (DECMODE = LOW), RXDx[7:0]

become the higher order bits of the 10-bit received character. See Table 16 for details.

(ground). The HIGH level is usually implemented by direct connection to VCC (power). When

SS

Document #: 38-02058 Rev. *H Page 7 of 46

Pin Descriptions CYP(V)(W)15G0201DXB Dual HOTLink II Transceiver (continued)

Pin Name I/O Characteristics Signal Description

RXSTA[2:0]

RXSTB[2:0]

RXOPA

RXOPB

Receive Path Clock and Clock Control

RXRATE LVTTL Input

RXCLKA±

RXCLKB±

RXCKSEL 3-Level Select

LVTTL Output,

synchronous to the

selected RXCLKx↑

output or

REFCLK↑

3-state, LVTTL

Output, synchronous

to the selected

RXCLKx↑ output or

REFCLK↑

Static Control Input,

internal pull-down

3-state, LVTTL

Output clock or

Static control input

Static Control Input

[3]

[3]

input

input

[4]

Parallel Status Output. These outputs change following the rising edge of the selected

receive interface clock.

When the Decoder is bypassed (DECMODE = LOW), RXSTx[1:0] become the two

low-order bits of the 10-bit received character, while RXSTx[2] = HIGH indicates the

presence of a Comma character in the Output Register. See Tabl e 1 6 for details.

When the Decoder is enabled (DECMODE = HIGH or MID), RXSTx[2:0] provide status of

the received signal. See Table 18, Ta bl e 19 and Tab le 20 for a list of Receive Character

status.

Receive Path Odd Parity. When parity generation is enabled (PARCTL ≠ LOW), the parity

output at these pins is valid for the data on the associated RXDx bus bits. When parity

generation is disabled (PARCTL = LOW) these output drivers are disabled (High-Z).

Receive Clock Rate Select. When LOW, the RXCLKx± recovered clock outputs are

complementary clocks operating at the recovered character rate. Data for the associated

receive channels should be latched on the rising edge of RXCLKx+ or falling edge of

RXCLKx–. When HIGH, the RXCLKx± recovered clock outputs are complementary clocks

operating at half the character rate. Data for the associated receive channels should be

latched alternately on the rising edge of RXCLKx+ and RXCLKx–.

When REFCLK± is selected to clock the output registers (RXCKSELx = LOW), RXRATEx

is not interpreted. The RXCLKA± and RXCLKC± output clocks will follow the frequency and

duty cycle of REFCLK±.

Receive Character Clock Output or Clock Select Input. When configured such that all

output data paths are clocked by the recovered clock (RXCKSEL = MID), these true and

complement clocks are the receive interface clocks which are used to control timing of

output data (RXDx[7:0], RXSTx[2:0] and RXOPx). These clocks are output continuously at

either the dual-character rate (1/20

serial symbol-rate) of the data being received, as selected by RXRATE.

When configured such that all output data paths are clocked by REFCLK instead of a

recovered clock (RXCKSEL = LOW), the RXCLKA± and RXCLKC+ output drivers present

a buffered and delayed form of REFCLK. RXCLKA± and RXCLKC+ are buffered forms of

REFCLK that are slightly different in phase. This phase difference allows the user to select

the optimal setup/hold timing for their specific interface.

When RXCKSEL = HIGH and dual-channel bonding is enabled, one of the recovered clocks

from channels A or B is selected to present bonded data from channels A and B. RXCLKA±

output the recovered clock from either receive channel A or receive channel B as selected

by RXCLKB+ to clock the bonded output data from channels A and B. See Table 14 for

details.

When RXCKSEL = LOW and dual-channel bonding is enabled, REFCLK is selected to

present bonded data from channels A and B. RXCLKA± and RXCLKC+ output drivers

present a buffered and delayed form of REFCLK. The master channel for bonding is

selected by RXCLKB+ (which acts as an input in this mode) to clock the bonded output data

from channels A and B. See Ta bl e 1 4 for details.

Receive Clock Mode. Selects the receive clock-source used to transfer data to the Output

Registers.

When LOW, both Output Registers are clocked by REFCLK. RXCLKB± outputs are disabled

(High-Z), and RXCLKA± and RXCLKC+ present buffered and delayed forms of REFCLK.

When MID, each RXCLKx± output follows the recovered clock for the respective channel,

as selected by RXRATE. When the 10B/8B Decoder and Elasticity Buffer are bypassed

(DECMODE = LOW), RXCKSEL must be MID.

When HIGH, and channel bonding is enabled in dual-channel mode (RX modes 2 and 3),

RXCLKA± outputs the recovered clock from either receive channel A or receive channel B

as selected by RXCLKB+. These output clocks may operate at the character-rate or half the

character-rate as selected by RXRATE.

th

the serial symbol-rate) or character rate (1/10th the

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

Document #: 38-02058 Rev. *H Page 8 of 46

Pin Descriptions CYP(V)(W)15G0201DXB Dual HOTLink II Transceiver (continued)

Pin Name I/O Characteristics Signal Description

DECMODE 3-Level Select

Static Control Input

RXMODE[1:0]3-Level Select

Static Control Inputs

RFEN LVTTL input,

asynchronous,

internal pull-down

RFMODE 3-Level Select

Static Control Input

FRAMCHAR 3-Level Select

Static Control Input

Device Control Signals

PARCTL 3-Level Select

Static Control Input

[4]

Decoder Mode Select. This input selects the behavior of the Decoder block.

When LOW, the Decoder is bypassed and raw 10-bit characters are passed to the Output

Register. When the Decoder is bypassed, RXCKSEL must be MID.

When MID, the Decoder is enabled and the Cypress Decoder table for Special Code

characters is used. When HIGH, the Decoder is enabled and the alternate Decoder table

for Special Code characters is used. See Table 25 for a list of the Special Codes supported

in both encoded modes.

[4]

Receive Operating Mode. These inputs are interpreted to select one of nine operating

modes of the receive path. See Table 13 for details.

Reframe Enable for All Channels. Active HIGH. When HIGH, the framers in both channels

are enabled to frame per the presently enabled framing mode and selected framing

character.

[4]

Reframe Mode Select. Used to control the type of character framing used to adjust the

character boundaries (based on detection of one or more framing characters in the received

serial bit stream). This signal operates in conjunction with the presently enabled channel

bonding mode, and the type of framing character selected.

When LOW, the low-latency framer is selected. This will frame on each occurrence of the

selected framing character(s) in the received data stream. This mode of framing stretches

the recovered clock for one or multiple cycles to align that clock with the recovered data.

When MID, the Cypress-mode multi-byte parallel framer is selected. This requires a pair of

the selected framing character(s), on identical 10-bit boundaries, within a span of 50 bits,

before the character boundaries are adjusted. The recovered character clock remains in the

same phasing regardless of character offset.

When HIGH, the alternate mode multi-byte parallel framer is selected. This requires

detection of the selected framing character(s) of the allowed disparities in the received serial

bit stream, on identical 10-bit boundaries, on four directly adjacent characters. The

recovered character clock remains in the same phasing regardless of character offset.

[4]

Framing Character Select. Used to control the character or portion of a character used for

character framing of the received data streams.

When MID, the framer looks for both positive and negative disparity versions of the 8-bit

Comma character. When HIGH, the framer looks for both positive and negative disparity

versions of the K28.5 character. Configuring FRAMCHAR to LOW is reserved for

component test.

[4]

Parity Check/Generate Control. Used to control the different parity check and generate

functions.

When LOW, parity checking is disabled, and the RXOPx outputs are all disabled (High-Z).

When MID, and the Encoder/Decoder are enabled (TXMODE[1] ≠ LOW,

DECMODE ≠ LOW), TXDx[7:0] inputs are checked (along with TXOPx) for valid ODD parity,

and ODD parity is generated for the RXDx[7:0] outputs and presented on RXOPx. When

the Encoder and Decoder are disabled (TXMODE[1] = LOW, DECMODE = LOW), the

TXDx[7:0] and TXCTx[1:0] inputs are checked (along with TXOPx) for valid ODD parity, and

ODD parity is generated for the RXDx[7:0] and RXSTx[1:0] outputs and presented on

RXOPx. When HIGH, parity checking and generation are enabled. The TXDx[7:0] and

TXCTx[1:0] inputs are checked (along with TXOPx) for valid ODD parity, and ODD parity is

generated for the RXDx[7:0] and RXSTx[2:0] outputs and presented on RXOPx.

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

Document #: 38-02058 Rev. *H Page 9 of 46

Pin Descriptions CYP(V)(W)15G0201DXB Dual HOTLink II Transceiver (continued)

Pin Name I/O Characteristics Signal Description

REFCLK± Differential LVPECL

or single-ended

LVTTL input clock

RXCLKC+ 3-state LVTTL

SPDSEL 3-Level Select

TRSTZ

Analog I/O and Control

OUTA1±

OUTB1±

OUTA2±

OUTB2±

INA1±

INB1±

INA2±

INB2±

INSELA

INSELB

SDASEL 3-Level Select

LPEN LVTTL Input,

Output

static control input

LVTTL Input,

internal pull-up

CML Differential

Output

CML Differential

Output

LVPECL Differential

Input

LVPECL Differential

Input

LVTTL Input,

asynchronous

static configuration

input

asynchronous,

internal pull-down

Reference Clock. This clock input is used as the timing reference for the transmit and

receive PLLs. This input clock may also be selected to clock the transmit and receive parallel

interfaces. When driven by a single-ended LVCMOS or LVTTL clock source, connect the

clock source to either the true or complement REFCLK input, and leave the alternate

REFCLK input open (floating). When driven by an LVPECL clock source, the clock must be

a differential clock, using both inputs. When TXCKSEL = LOW, REFCLK is also used as the

clock for the parallel transmit data (input) interface. When RXCKSEL = LOW, the Elasticity

Buffer is enabled and REFCLK is used as the clock for the parallel receive data (output)

interface.

If the Elasticity Buffer is used, framing characters will be inserted or deleted to/from the data

stream to compensate for frequency differences between the reference clock and recovered

clock. When addition happens, a K28.5 will be appended immediately after a framing

character is detected in the Elasticity Buffer. When deletion happens, a framing character

will be removed from the datastream when detected in the Elasticity Buffer.

Delayed REFCLK+ when RXCKSEL=LOW. Delayed form of REFCLK+, used for transfer

of recovered data to a host system. This output is only enabled when the receive parallel

interface is configured to present data relative to REFCLK (RXCKSEL = LOW).

[4]

,

Serial Rate Select. This input specifies the operating bit-rate range of both transmit and

receive PLLs. LOW = 195–400 MBaud, MID = 400–800 MBaud, HIGH = 800–1500 MBaud

(800–1540 MBaud for CYW15G0201DXB). When SPDSEL is LOW, setting TXRATE =

HIGH (Half-rate Reference Clock) is invalid.

Device Reset. Active LOW. Initializes all state machines and counters in the device.

When sampled LOW by the rising edge of REFLCK, this input resets the internal state

machines and sets the Elasticity Buffer pointers to a nominal offset. When the reset is

removed (TRSTZ

deterministic in less than 16 REFCLK cycles.

The BISTLE, OELE, and RXLE latches are reset by TRSTZ.

If the Elasticity Buffer or the Phase Align Buffer are used, TRSTZ

power up to initialize the internal pointers into these memory arrays.

Primary Differential Serial Data Outputs. These PECL-compatible CML outputs (+3.3V

referenced) are capable of driving terminated transmission lines or standard fiber-optic

transmitter modules.

Secondary Differential Serial Data Outputs. These PECL-compatible CML outputs

(+3.3V referenced) are capable of driving terminated transmission lines or standard

fiber-optic transmitter modules.

Primary Differential Serial Data Inputs. These inputs accept the serial data stream for

deserialization and decoding. The INx1± serial streams are passed to the receiver Clock

and Data Recovery (CDR) circuits to extract the data content when INSELx = HIGH.

Secondary Differential Serial Data Inputs. These inputs accept the serial data stream for

deserialization and decoding. The INx2± serial streams are passed to the receiver Clock

and Data Recovery (CDR) circuits to extract the data content when INSELx = LOW.

Receive Input Selector. Determines which external serial bit stream is passed to the

receiver Clock and Data Recovery circuit. When HIGH, the INx1± input is selected. When

LOW, the INx2± input is selected.

[4]

,

Signal Detect Amplitude Level Select. Allows selection of one of three predefined

amplitude trip points for a valid signal indication, as listed in Table 11.

All-Port Loop-Back-Enable. Active HIGH. When asserted (HIGH), the transmit serial data

from each channel is internally routed to the associated receiver Clock and Data Recovery

(CDR) circuit. All serial drivers are forced to differential logic “1”. All serial data inputs are

ignored.

sampled HIGH by REFCLK↑), the status and data outputs will become

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

should be applied after

Document #: 38-02058 Rev. *H Page 10 of 46

Pin Descriptions CYP(V)(W)15G0201DXB Dual HOTLink II Transceiver (continued)

Pin Name I/O Characteristics Signal Description

OELE LVTTL Input,

asynchronous,

internal pull-up

RXLE LVTTL Input,

asynchronous,

internal pull-up

BISTLE LVTTL Input,

BOE[3:0] LVTTL Input,

LFIA

LFIB

JTAG Interface

TMS LVTTL Input,

TCLK LVTTL Input,

TDO 3-State

TDI LVTTL Input,

Power

V

CC

GND Signal and Power Ground for all internal circuits.

asynchronous,

internal pull-up

asynchronous,

internal pull-up

LVTTL Output,

Asynchronous

internal pull-up

internal pull-down

LVTTL Output

internal pull-up

Serial Driver Output Enable Latch Enable. Active HIGH. When OELE = HIGH, the signals

on the BOE[3:0] inputs directly control the OUTxy± differential drivers. When the BOE[x]

input is HIGH, the associated OUTxy± differential driver is enabled. When the BOE[x] input

is LOW, the associated OUTxy± differential driver is powered down. When OELE returns

LOW, the last values present on BOE[3:0] are captured in the internal Output Enable Latch.

The specific mapping of BOE[3:0] signals to transmit output enables is listed in Tab le 9 .

If the device is reset (TRSTZ

Receive Channel Power-Control Latch Enable. Active HIGH. When RXLE = HIGH, the

signals on the BOE[3:0] inputs directly control the power enables for the receive PLLs and

analog logic. When the BOE[3:0] input is HIGH, the associated receive channel A and

receive channel B PLL and analog logic are active. When the BOE[3:0] input is LOW, the

associated receive channel A and receive channel B PLL and analog logic are placed in a

non-functional power saving mode. When RXLE returns LOW, the last values present on

BOE[3:0] are captured in the internal RX PLL Enable Latch. The specific mapping of

BOE[3:0] signals to the associated receive channel enables is listed in Ta bl e 9 . When the

device is reset (TRSTZ

Transmit and Receive BIST Latch Enable. Active HIGH. When BISTLE = HIGH, the

signals on the BOE[3:0] inputs directly control the transmit and receive BIST enables. When

the BOE[x] input is LOW, the associated transmit or receive channel is configured to

generate or compare the BIST sequence. When the BOE[x] input is HIGH, the associated

transmit or receive channel is configured for normal data transmission or reception. When

BISTLE returns LOW, the last values present on BOE[3:0] are captured in the internal BIST

Enable Latch. The specific mapping of BOE[3:0] signals to transmit and receive BIST

enables is listed in Table 9. When the latch is closed, if the device is reset (TRSTZ

LOW), the latch is reset to disable BIST on all transmit and receive channels.

BIST, Serial Output, and Receive Channel Enables. These inputs are passed to and

through the Output Enable Latch when OELE = HIGH, and captured in this latch when

OELE returns LOW. These inputs are passed to and through the BIST Enable Latch when

BISTLE = HIGH, and captured in this latch when BISTLE returns LOW. These inputs are

passed to and through the Receive Channel Enable Latch when RXLE = HIGH, and

captured in this latch when RXLE returns LOW.

Link Fault Indication Output. Active LOW. LFIx is the logical OR of four internal conditions:

1. Received serial data frequency outside expected range.

2. Analog amplitude below expected levels.

3. Transition density lower than expected.

4. Receive Channel disabled.

Test Mode Select. Used to control access to the JTAG Test Modes. If maintained HIGH for

>5 TCLK cycles, the JTAG test controller is reset. The TAP controller is also reset automatically upon application of power to the device.

JTAG Test Clock.

Test Dat a O u t . JTAG data output buffer which is High-Z while JTAG test mode is not

selected.

Test Dat a In . JTAG data input port.

+3.3V power.

is sampled LOW), the latch is reset to disable all outputs.

is sampled LOW), the latch is reset to disable both receive channels.

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

is sampled

Document #: 38-02058 Rev. *H Page 11 of 46

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

CYP(V)(W)15G0201DXB HOTLink II Operation

The CYP(V)(W)15G0201DXB is a highly configurable device

designed to support reliable transfer of large quantities of data,

using high-speed serial links, from one or multiple sources to

one or multiple destinations. This device supports two

single-byte or single-character channels that may be

combined to support transfer of wider buses.

CYP(V)(W)15G0201DXB Transmit Data Path

Operating Modes

The transmit path of the CYP(V)(W)15G0201DXB supports

two character-wide data paths. These data paths are used in

multiple operating modes as controlled by the TXMODE[1:0]

inputs.

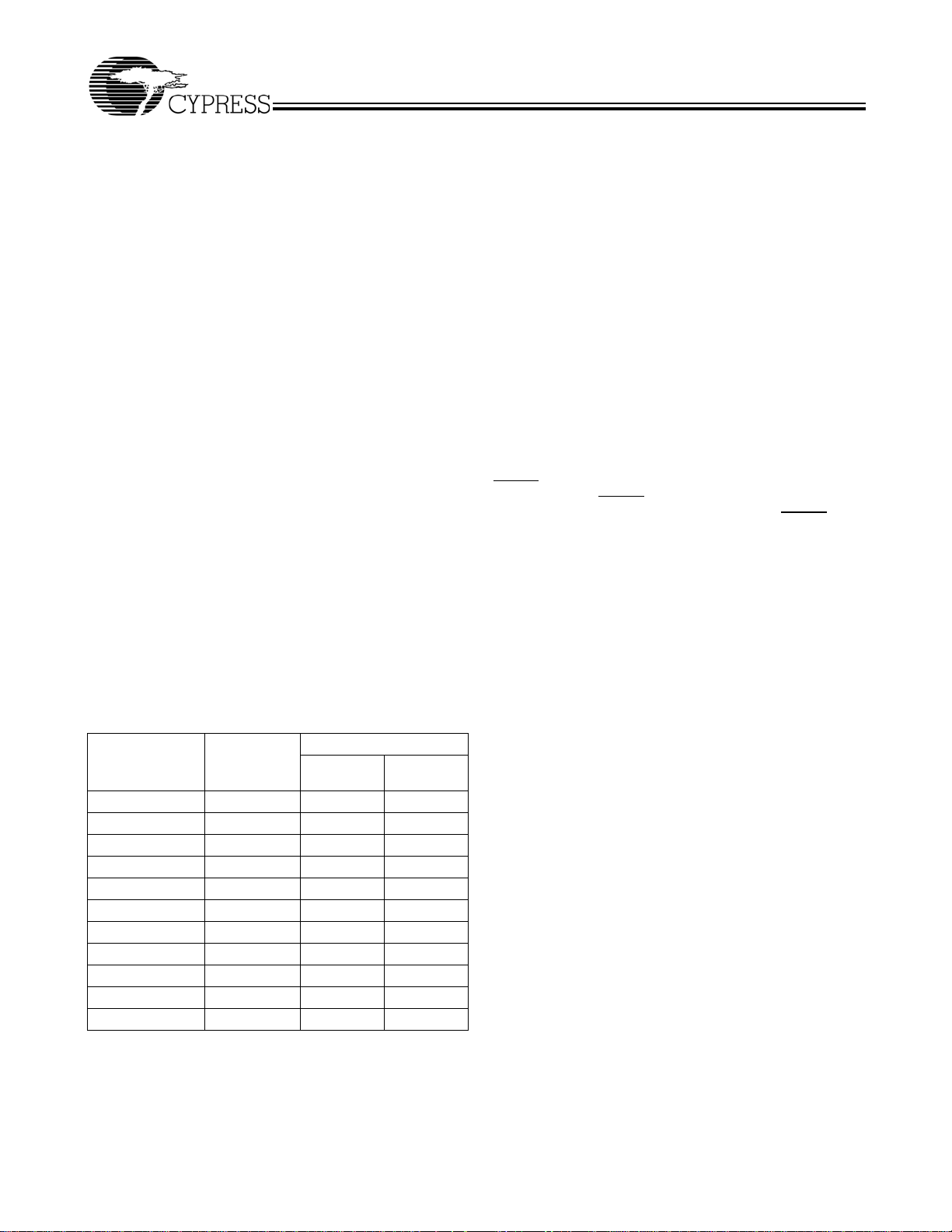

Input Register

The bits in the Input Register for each channel support

different assignments, based on if the character is unencoded,

encoded with two control bits, or encoded with three control

bits. These assignments are shown in Tab le 1 .

Each Input Register captures a minimum of eight data bits and

two control bits on each input clock cycle. When the Encoder

is bypassed, the TXCTx[1:0] control bits are part of the

pre-encoded 10-bit character.

When the Encoder is enabled (TXMODE[1] ≠ LOW), the

TXCTx[1:0] bits are interpreted along with the associated

TXDx[7:0] character to generate the specific 10-bit transmission character. When TXMODE[0] ≠ HIGH, an additional

special character select (SCSEL) input is also captured and

interpreted. This SCSEL input is used to modify the encoding

of the associated characters. When the transmit Input

Registers are clocked by a common clock (TXCLKA↑ or

REFCLK↑), this SCSEL input can be changed on a

clock-by-clock basis and affects both channels.

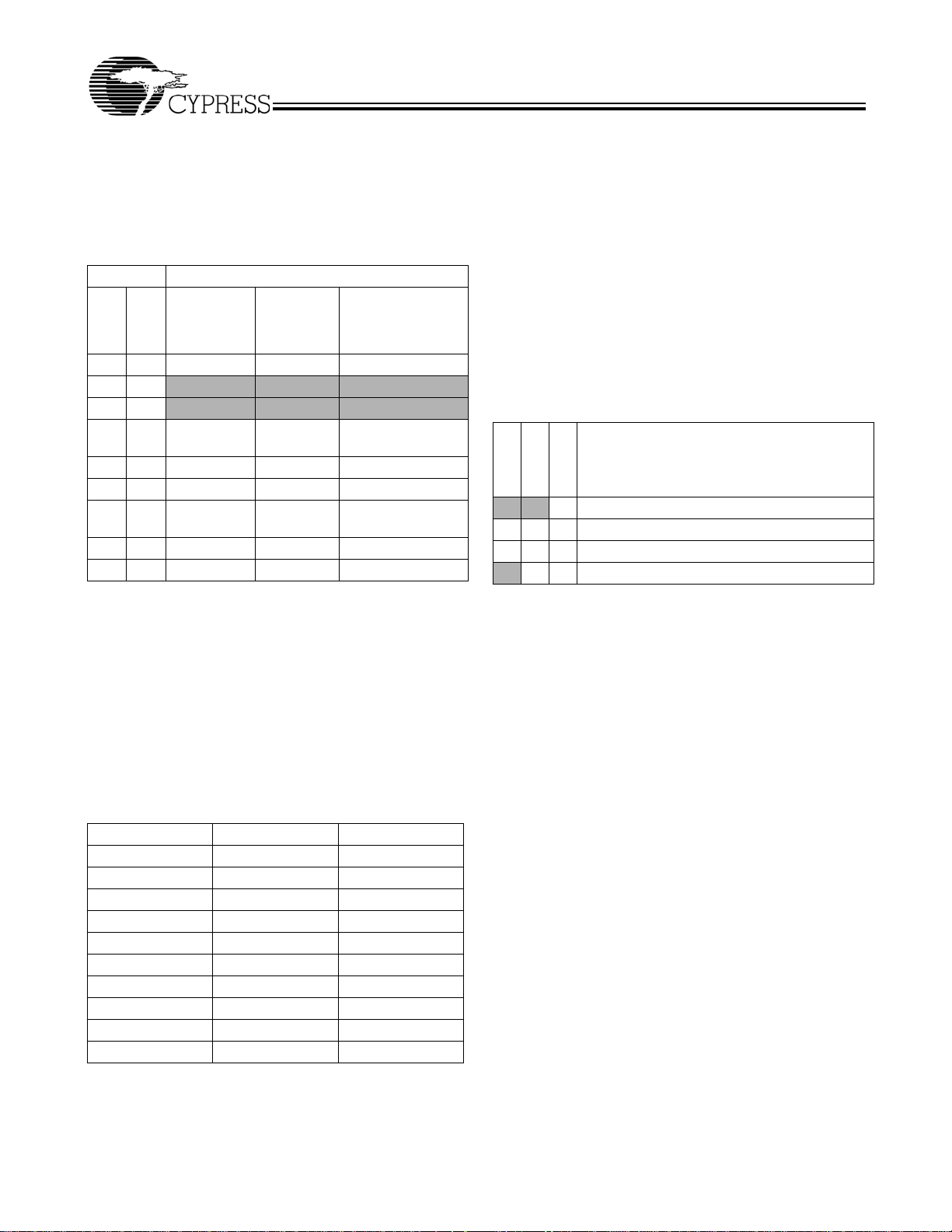

Table 1. Input Register Bit Assignments

Signal Name Unencoded

TXDx[0]

(LSB) DINx[0] TXDx[0] TXDx[0]

TXDx[1] DINx[1] TXDx[1] TXDx[1]

TXDx[2] DINx[2] TXDx[2] TXDx[2]

TXDx[3] DINx[3] TXDx[3] TXDx[3]

TXDx[4] DINx[4] TXDx[4] TXDx[4]

TXDx[5] DINx[5] TXDx[5] TXDx[5]

TXDx[6] DINx[6] TXDx[6] TXDx[6]

TXDx[7] DINx[7] TXDx[7] TXDx[7]

TXCTx[0] DINx[8] TXCTx[0] TXCTx[0]

TXCTx[1]

(MSB) DINx[9] TXCTx[1] TXCTx[1]

SCSEL N/A N/A SCSEL

[5]

Encoded

2-bit

Control

3-bit

Control

When operated with a separate input clock on each transmit

channel, this SCSEL input is sampled synchronous to

TXCLKA↑. While the value on SCSEL still affects both

channels, it is interpreted when the character containing it is

read from the transmit Phase-Align Buffer (where both paths

are internally clocked synchronously).

Phase-Align Buffer

Data from the Input Registers is passed either to the Encoder

or to the associated Phase-Align Buffer. When the transmit

paths are operated synchronous to REFCLK↑ (TXCKSEL =

LOW and TXRATE = LOW), the Phase-Align Buffers are

bypassed and data is passed directly to the parity check and

Encoder blocks to reduce latency.

When an Input-Register clock with an uncontrolled phase

relationship to REFCLK is selected (TXCKSEL ≠ LOW) or if

data is captured on both edges of REFCLK

(TXRATE = HIGH), the Phase-Align Buffers are enabled.

These buffers are used to absorb clock phase differences

between the presently selected input clock and the internal

character clock.

Initialization of these Phase-Align buffers takes place when the

TXRST

input is sampled by two consecutive rising edges of

REFCLK. When TXRST

clock phase relative to REFCLK↑ is set. TXRST

is returned HIGH, the present input

is an

asynchronous input, but is sampled internally to synchronize

it to the internal transmit path state machines.

Once set, the input clocks are allowed to skew in time up to

half a character period in either direction relative to REFCLK↑;

i.e., ±180°. This time shift allows the delay paths of the

character clocks (relative to REFLCK↑) to change due to

operating voltage and temperature, while not affecting the

design operation.

If the phase offset, between the initialized location of the input

clock and REFCLK↑, exceeds the skew handling capabilities

of the Phase-Align Buffer, an error is reported on the

associated TXPERx output. This output indicates a continuous

error until the Phase-Align Buffer is reset. While the error

remains active, the transmitter for the associated channel

outputs a continuous C0.7 character to indicate to the remote

receiver that an error condition is present in the link.

In specific transmit modes, it is also possible to reset the

Phase-Align Buffers individually and with minimal disruption of

the serial data stream. When the transmit interface is

configured for generation of atomic Word Sync Sequences

(TXMODE[1] = MID) and a Phase-Align Buffer error is

present, the transmission of a Word Sync Sequence will

recenter the Phase Align Buffer and clear the error condition.

[6]

Notes:

5. The TXOPx inputs are also captured in the associated Input Register, but their interpretation is under the separate control of PARCTL.

6. One or more K28.5 characters may be added or lost from the data stream during this reset operation. When used with non-Cypress devices that require a

complete 16-character Word Sync Sequence for proper receive Elasticity Buffer alignment, it is recommend that the sequence be followed by a second Word

Sync Sequence to ensure proper operation.

Document #: 38-02058 Rev. *H Page 12 of 46

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

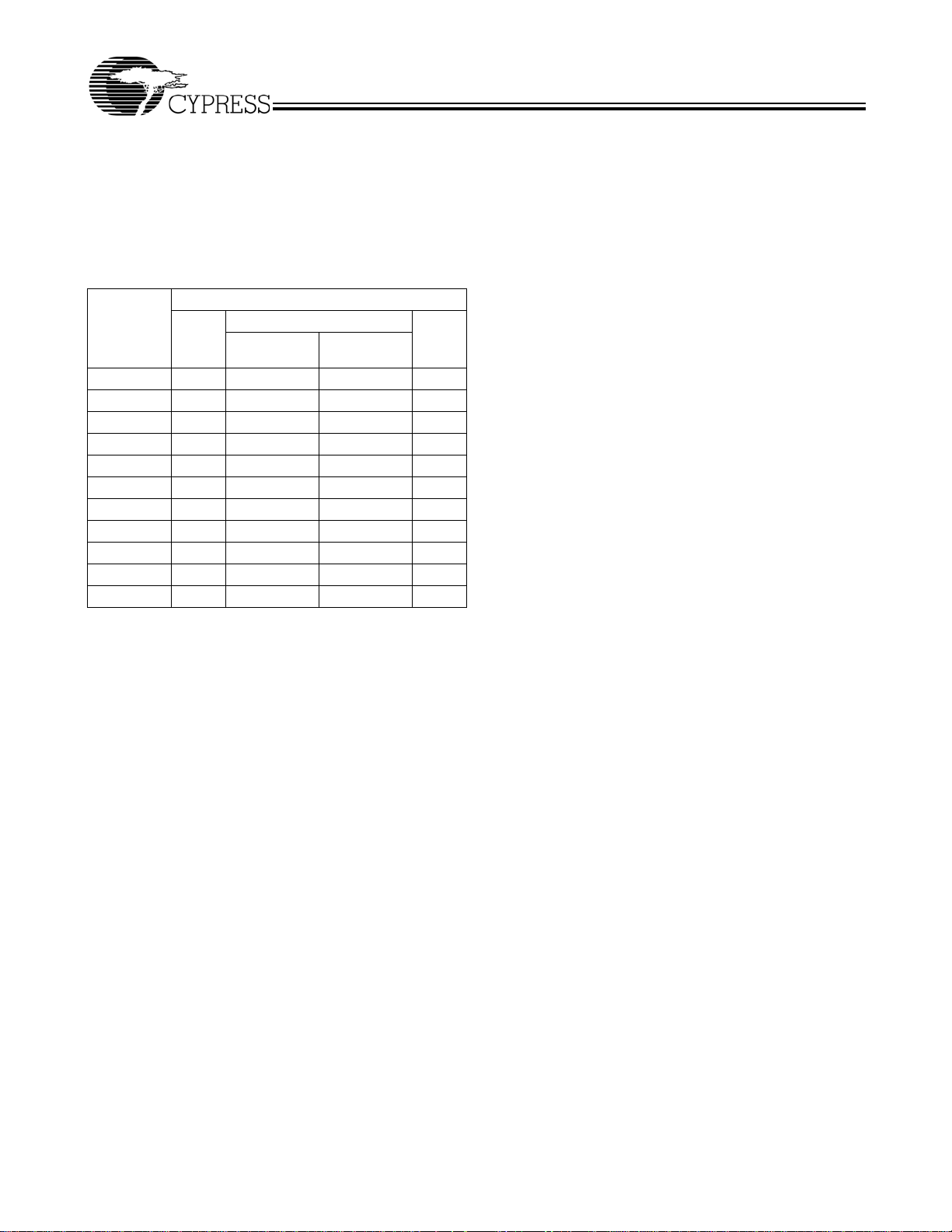

Parity Support

In addition to the ten data and control bits that are captured at

each transmit Input Register, a TXOPx input is also available

on each channel. This allows the CYP(V)(W)15G0201DXB to

support ODD parity checking for each channel. This parity

checking is available for all operating modes (including

Encoder Bypass). The specific mode of parity checking is

controlled by the PARCTL input, and operates per Tab le 2.

Table 2. Input Register Bits Checked for Parity

Transmit Parity Check Mode (PARCTL)

MID

Signal

Name

TXDx[0] X

TXDx[1] X X X

TXDx[2] X X X

TXDx[3] X X X

TXDx[4] X X X

TXDx[5] X X X

TXDx[6] X X X

TXDx[7] X X X

TXCTx[0] X X

TXCTx[1] X X

TXOPx X X X

When PARCTL is MID (open) and the Encoders are enabled

(TXMODE[1] ≠ L), only the TXDx[7:0] data bits are checked for

ODD parity along with the associated TXOPx bit. When

PARCTL = HIGH with the Encoder enabled (or MID with the

Encoder bypassed), the TXDx[7:0] and TXCTx[1:0] inputs are

checked for ODD parity along with the associated TXOPx bit.

When PARCTL = LOW, parity checking is disabled.

When parity checking and the Encoder are both enabled

(TXMODE[1] ≠ LOW), the detection of a parity error causes a

C0.7 character of proper disparity to be passed to the Transmit

Shifter. When the Encoder is bypassed (TXMODE[1] = LOW),

detection of a parity error causes a positive disparity version

of a C0.7 transmission character to be passed to the Transmit

Shifter.

Encoder

The character, received from the Input Register or

Phase-Align Buffer and Parity Check logic, is then passed to

the Encoder logic. This block interprets each character and

any associated control bits, and outputs a 10-bit transmission

character.

Depending on the configured operating mode, the generated

transmission character may be

• the 10-bit pre-encoded character accepted in the Input

Register

• the 10-bit equivalent of the 8-bit Data character accepted in

the Input Register

• the 10-bit equivalent of the 8-bit Special Character code

accepted in the Input Register

Notes:

7. Transmit path parity errors are reported on the associated TXPERx output.

8. Bits marked as X are XORed together. Result must be a logic-1 for parity to be valid.

LOW

TXMODE[1]

= LOW

[8]

TXMODE[1]

≠ LOW

[7]

HIGH

XX

The selection of the specific characters generated is controlled

by the TXMODE[1:0], SCSEL, TXCTx[1:0], and TXDx[7:0]

inputs for each character.

Data Encoding

Raw data, as received directly from the Transmit Input

Register, is seldom in a form suitable for transmission across

a serial link. The characters must usually be processed or

transformed to guarantee

When the Encoder is enabled (TXMODE[1] ≠ LOW), the

characters to be transmitted are converted from Data or

Special Character codes to 10-bit transmission characters (as

selected by their respective TXCTx[1:0] and SCSEL inputs),

using an integrated 8B/10B Encoder. When directed to encode

the character as a Special Character code, it is encoded using

the Special Character encoding rules listed in Table 25. When

directed to encode the character as a Data character, it is

encoded using the Data Character encoding rules in Table 24.

The 8B/10B Encoder is standards compliant with ANSI/NCITS

ASC X3.230-1994 (Fibre Channel), IEEE 802.3z (Gigabit

Ethernet), the IBM

Digital Video Broadcast DVB-ASI standards for data transport.

Many of the Special Character codes listed in Table 25 may be

generated by more than one input character. The

CYP(V)(W)15G0201DXB is designed to support two

independent (but non-overlapping) Special Character code

tables. This allows the CYP(V)(W)15G0201DXB to operate in

mixed environments with other CYP(V)(W)15G0201DXBs

using the enhanced Cypress command code set, and the

reduced command sets of other non-Cypress devices. Even

when used in an environment that normally uses non-Cypress

Special Character codes, the selective use of Cypress

command codes can permit operation where running disparity

and error handling must be managed.

Following conversion of each input character from eight bits to

a 10-bit transmission character, it is passed to the Transmit

Shifter and is shifted out LSB first, as required by ANSI and

IEEE standards for 8B/10B coded serial data streams.

Transmit Modes

The operating mode of the transmit path is set through the

TXMODE[1:0] inputs. These 3-level select inputs allow one of

nine transmit modes to be selected. The transmit modes are

listed in Table 3.

• the 10-bit equivalent of the C0.7 SVS character if parity

checking was enabled and a parity error was detected

• the 10-bit equivalent of the C0.7 SVS character if a

Phase-Align Buffer overflow or underflow error is present

• a character that is part of the 511-character BIST sequence

• a K28.5 character generated as an individual character or

as part of the 16-character Word Sync Sequence.

• a minimum transition density (to allow the serial receive PLL

to extract a clock from the data stream)

• a DC-balance in the signaling (to prevent baseline wander)

• run-length limits in the serial data (to limit the bandwidth

requirements of the serial link)

• the remote receiver a way of determining the correct

character boundaries (framing).

®

ESCON® and FICON® channels, and

Document #: 38-02058 Rev. *H Page 13 of 46

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

The encoded modes (TX Modes 3 through 8) support multiple

encoding tables. These encoding tables vary by the specific

combinations of SCSEL, TXCTx[1], and TXCTx[0] that are

used to control the generation of data and control characters.

These multiple encoding forms allow maximum flexibility in

interfacing to legacy applications, while also supporting

numerous extensions in capabilities.

Table 3. Transmit Operating Modes

TX Mode Operating Mode

Word Sync

Mode

Number

[1:0]

TXMODE

Sequence

Support

SCSEL

Control TXCTx Function

0 LL None None Encoder Bypass

1LM

2LH

3 ML Atomic Special

None None Reserved for test

None None Reserved for test

Encoder Control

Character

4 MM Atomic Word Sync Encoder Control

5 MH Atomic None Encoder Control

6 HL Interruptible Special

Encoder Control

Character

7 HM Interruptible Word Sync Encoder Control

8 HH Interruptible None Encoder Control

TX Mode 0—Encoder Bypass

When the Encoder is bypassed, the character captured in the

TXDx[7:0] and TXCTx[1:0] inputs is passed directly to the

Transmit Shifter without modification. If parity checking is

enabled (PARCTL ≠ LOW) and a parity error is detected, the

10-bit character is replaced with the 1001111000 pattern

(+C0.7 character).

With the Encoder bypassed, the TXCTx[1:0] inputs are

considered part of the data character and do not perform a

control function that would otherwise modify the interpretation

of the TXDx[7:0] bits. The bit usage and mapping of these

control bits when the Encoder is bypassed is shown in Table 4.

Table 4. Encoder Bypass Mode (TXMODE[1:0] = LL)

Signal Name Bus Weight 10B Name

TXDx[0]

(LSB)

[9]

TXDx[1] 2

TXDx[2] 2

TXDx[3] 2

TXDx[4] 2

TXDx[5] 2

TXDx[6] 2

TXDx[7] 2

TXCTx[0] 2

TXCTx[1]

Note:

9. LSB is shifted out first.

(MSB) 2

0

2

1

2

3

4

5

6

7

8

9

a

b

c

d

e

i

f

g

h

j

TX Modes 1 and 2—Factory Test Modes.

In Encoder Bypass the SCSEL input is ignored. All clocking

modes interpret the data the same, with no internal linking

between channels.

These modes enable specific factory test configurations. They

are not considered normal operating modes of the device.

Entry or configuration into these test modes will not damage

the device.

TX Mode 3—Atomic Word Sync and SCSEL Control of Special

Codes

When configured in TX Mode 3, the SCSEL input is captured

along with the associated TXCTx[1:0] data control inputs.

These bits combine to control the interpretation of the

TXDx[7:0] bits and the characters generated by them. These

bits are interpreted as listed in Table 5.

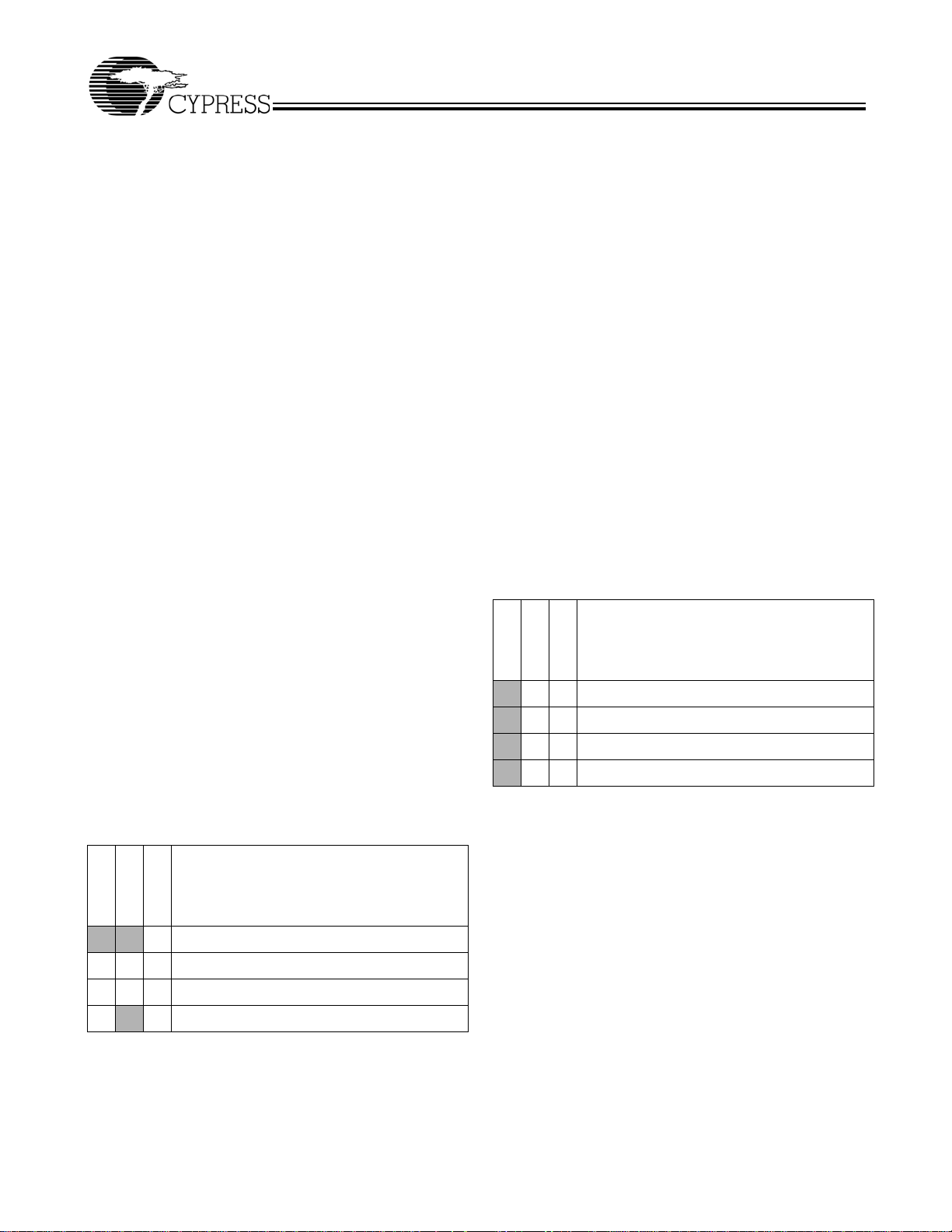

Table 5. TX Modes 3 and 6 Encoding

SCSEL

TXCTx[1]

TXCTx[0]

Characters Generated

X X 0 Encoded data character

0 0 1 K28.5 fill character

1 0 1 Special character code

X 1 1 16-character Word Sync Sequence

When TXCKSEL = MID, both transmit channels capture data

into their Input Registers using independent TXCLKx clocks.

The SCSEL input is sampled only by TXCLKA↑. When the

character (accepted in the Channel-A Input Register) has

passed through the Phase-Align Buffer and any selected parity

validation, the level captured on SCSEL is passed to the

Encoder of Channel-B during this same cycle.

To avoid the possible ambiguities that may arise due to the

uncontrolled arrival of SCSEL relative to the characters in the

alternate channel, SCSEL is often used as a static control

input.

Word Sync Sequence

When TXCTx[1:0] = 11, a 16-character sequence of K28.5

characters, known as a Word Sync Sequence, is generated on

the associated channel. This sequence of K28.5 characters

may start with either a positive or negative disparity K28.5 (as

determined by the current running disparity and the 8B/10B

coding rules). The disparity of the second and third K28.5

characters in this sequence are reversed from what normal

8B/10B coding rules would generate. The remaining K28.5

characters in the sequence follow all 8B/10B coding rules. The

disparity of the generated K28.5 characters in this sequence

would follow a pattern of either

++––+–+–+–+–+–+– or

––++–+–+–+–+–+–+.

When TXMODE[1] = MID (open, TX modes 3, 4, and 5), the

generation of this character sequence is an atomic (non-interruptible) operation. Once it has been successfully started, it

cannot be stopped until all 16 characters have been

generated. The content of the associated Input Register(s) is

ignored for the duration of this 16-character sequence.

Document #: 38-02058 Rev. *H Page 14 of 46

CYP15G0201DXB

CYV15G0201DXB

CYW15G0201DXB

At the end of this sequence, if the TXCTx[1:0] = 11 condition

is sampled again, the sequence restarts and remains uninterruptible for the following 15 character clocks.

If parity checking is enabled, the character used to start the

Word Sync Sequence must also have correct ODD parity.

Once the sequence is started, parity is not checked on the

following 15 characters in the Word Sync Sequence.

When TXMODE[1] = HIGH (TX modes 6, 7, and 8), the generation of the Word Sync Sequence becomes an interruptible

operation. In TX Mode 6, this sequence is started as soon as

the TXCTx[1:0] = 11 condition is detected on a channel. In

order for the sequence to continue on that channel, the

TXCTx[1:0] inputs must be sampled as 00 for the remaining

15 characters of the sequence.

If at any time a sample period exists where TXCTx[1:0] ≠ 00,

the Word Sync Sequence is terminated, and a character representing the associated data and control bits is generated by

the Encoder. This resets the Word Sync Sequence state

machine such that it will start at the beginning of the sequence

at the next occurrence of TXCTx[1:0] = 11.

When parity checking is enabled and TXMODE[1] = HIGH, all

characters (including those in the middle of a Word Sync

Sequence) must have correct parity. The detection of a

character with incorrect parity during a Word Sync Sequence

(regardless of the state of TXCTx[1:0]) will interrupt that

sequence and force generation of a C0.7 SVS character. Any

interruption of the Word Sync Sequence causes the sequence

to terminate.

When TXCKSEL = LOW, the Input Registers for both transmit

channels are clocked by REFCLK

HIGH, the Input Registers for both transmit channels are

clocked with TXCLKA↑. In these clock modes both sets of

TXCTx[1:0] inputs operate synchronous to the SCSEL

[10]

input.

TX Mode 4—Atomic Word Sync and SCSEL Control of

Word Sync Sequence Generation

When configured in TX Mode 4, the SCSEL input is captured

along with the associated TXCTx[1:0] data control inputs.

These bits combine to control the interpretation of the

TXDx[7:0] bits and the characters generated by them. These

bits are interpreted as listed in Table 6.

Table 6. TX Modes 4 and 7 Encoding

SCSEL

X X 0 Encoded data character

0 0 1 K28.5 fill character

0 1 1 Special character code

1

When TXCKSEL = MID, both transmit channels operate

independently. The SCSEL input is sampled only by

Note:

10. When operated in any configuration where receive channels are bonded together, TXCKSEL must be either LOW or HIGH (not MID) to ensure that associated

TXCTx[0]

TXCTx[1]

X 1 16-character Word Sync Sequence

characters are transmitted in the same character cycle.

Characters Generated

[3]

. When TXCKSEL =

TXCLKA↑. When the character accepted in the Channel-A

Input Register has passed any selected validation and is ready

to be passed to the Encoder, the level captured on SCSEL is

passed to the Encoder of Channel-B during this same cycle.

Changing the state of SCSEL changes the relationship of the

characters on the alternate channel. SCSEL should either be

used as a static configuration input or changed only when the

state of TXCTx[1:0] on the alternate channel are such that

SCSEL is ignored during the change.

TX Mode 4 also supports an Atomic Word Sync Sequence.

Unlike TX Mode 3, this sequence is started when both SCSEL

and TXCTx[0] are sampled HIGH. With the exception of the

combination of control bits used to initiate the sequence, the

generation and operation of this Word Sync Sequence is the

same as that documented for TX Mode 3.

TX Mode 5—Atomic Word Sync, No SCSEL

When configured in TX Mode 5, the SCSEL signal is not used.

In addition to the standard character encodings, both with and

without atomic Word Sync Sequence generation, two

additional encoding mappings are controlled by the Channel

Bonding selection made through the RXMODE[1:0] inputs.

For non-bonded operation, the TXCTx[1:0] inputs for each

channel control the characters generated by that channel. The

specific characters generated by these bits are listed in

Tabl e 7 .

Table 7. TX Modes 5 and 8 Encoding, Non-Bonded

(RXMODE[1] = LOW)

SCSEL

X 0 0 Encoded data character

X 0 1 K28.5 fill character

X 1 0 Special character code

X 1 1 16-character Word Sync Sequence

TX Mode 5 also has the capability of generating an atomic

Word Sync Sequence. For the sequence to be started, the

TXCTx[1:0] inputs must both be sampled HIGH. With the

exception of the combination of control bits used to initiate the

sequence, the generation and operation of this Word Sync

Sequence is the same as that documented for TX Mode 3.

Two additional encoding maps are provided for use when

receive channel bonding is enabled. When dual-channel

bonding is enabled (RXMODE[1] = HIGH), the

CYP(V)(W)15G0201DXB is configured such that channels A

and B are bonded together to form a two-character-wide path.

When operated in this two-channel bonded mode, the

TXCTA[0] and TXCTB[0] inputs control the interpretation of the

data on both the A and B channels. The characters on each

half of these bonded channels are controlled by the associated

TXCTx[1] bit. The specific characters generated by these

control bit combinations are listed in Table 8.

TXCTx[0]

TXCTx[1]

Characters Generated

Document #: 38-02058 Rev. *H Page 15 of 46

Loading...

Loading...