PRELIMINARY

CY9C62256

32K x 8 Magnetic Nonvolatile CMOS RAM

Features

• 100% form, fit, function-compatible with 32K × 8

micropower SRAM (CY62256)

— Fast Read and Write access: 70 ns

— Voltage range: 4.5V–5.5V operation

— Low power: 330 mW Active; 495 µW standby

— Easy memory expansion with CE

and OE features

— TTL-compatible inputs and outputs

— Automatic power-down when deselected

• Replaces 32K × 8 Battery Backed (BB)SRAM, SRAM,

EEPROM, FeRAM or Flash memory

• Data is automatically Write protected during power loss

• Write Cycles Endurance: > 10

15

cycles

• Data Retention: > 10 Years

• Shielded from external magnetic fields

• Extra 64 Bytes for device identification and tracking

• Temperature ranges

— Commercial: 0°C to 70°C

— Industrial: – 40°C to 85°C

• JEDEC STD 28-pin DIP (600-mil), 28-pin (300-mil) SOIC,

and 28-pin TSOP-1 packages. Also available in 450-mil

wide (300-mil body width) 28-pin narrow SOIC.

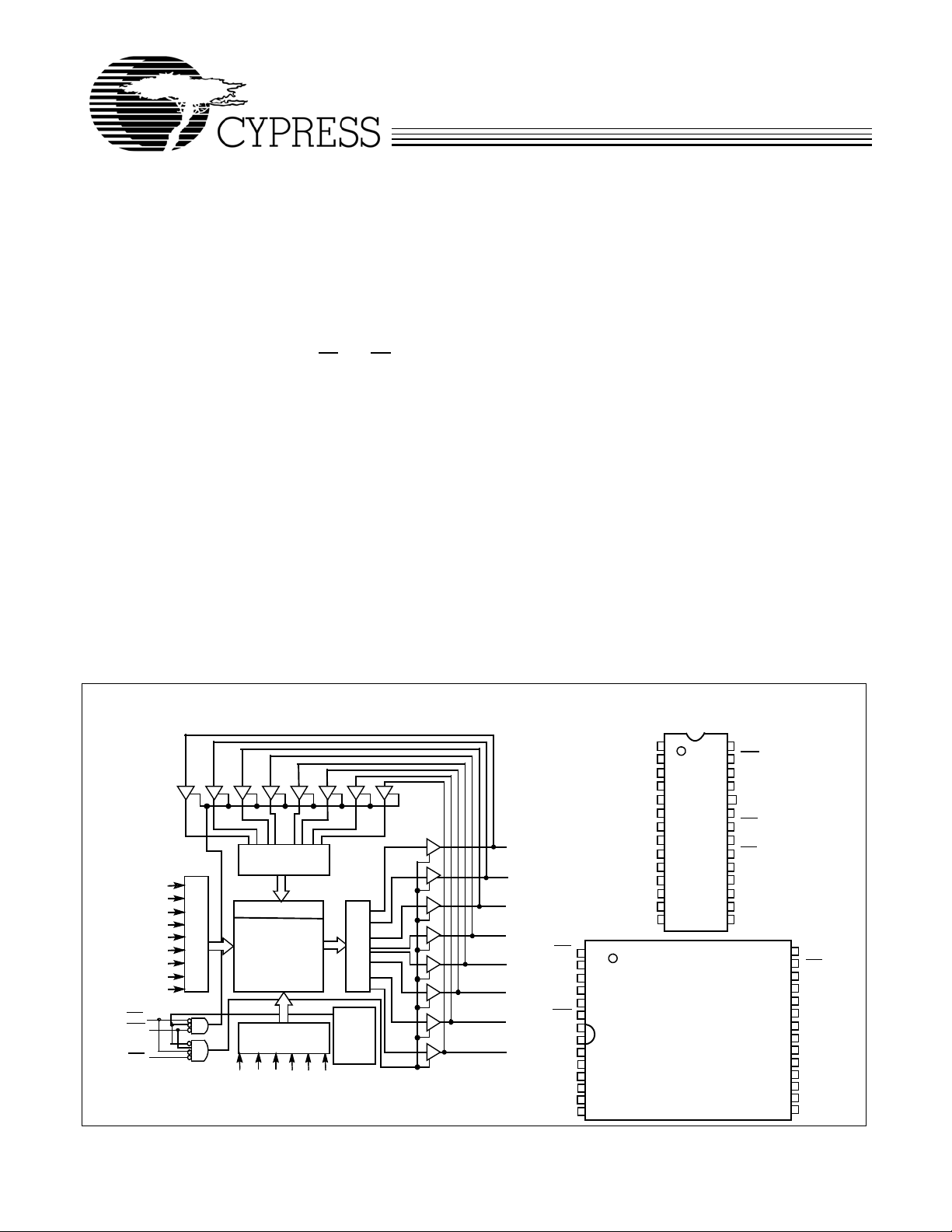

Logic Block Diagram

INPUTBUFFER

A

11

A

10

A

CE

WE

OE

9

A

8

A

7

A

6

A

3

A

2

A

ROW DECODER

1

Silicon Sig.

512x512

ARRA

COLUMN

DECODER

4A13A14

A

A

Y

SENSE AMPS

POWER

DOWN &

WRITE

PROTECT

0

12

A5A

Functional Description

The CY9C62256 is a high-performance CMOS nonvolatile

RAM employing an advanced magnetic RAM (MRAM)

process. An MRAM is nonvolatile memory that operates as a

fast read and write RAM. It provides data retention for more

than ten years while eliminating the reliability concerns,

functional disadvantages and system design complexities of

battery-backed SRAM, EEPROM, Flash and FeRAM. Its fast

writes and high write cycle endurance makes it superior to

other types of nonvolatile memory.

The CY9C62256 operates very similarly to SRAM devices.

Memory read and write cycles require equal times. The MRAM

memory is nonvolatile due to its unique magnetic process.

Unlike BBSRAM, the CY9C62256 is truly a monolithic nonvolatile memory. It provides the same functional benefits of a fast

write without the serious disadvantages associated with

modules and batteries or hybrid memory solutions.

These capabilities make the CY9C62256 ideal for nonvolatile

memory applications requiring frequent or rapid writes in a

bytewide environment.

The CY9C62256 is offered in both commercial and industrial

temperature ranges.

Pin Configurations

SOIC/DIP

Top View

28

27

26

25

24

23

22

21

20

19

18

17

16

15

V

WE

A

A

A

A

OE

A

CE

I/O

I/O

I/O

I/O

I/O

CC

4

3

2

1

0

7

6

5

4

3

21

A

0

20

CE

19

I/O

7

18

I/O

6

17

I/O

5

16

I/O

4

I/O

15

3

14

GND

13

I/O

2

12

I/O

1

11

I/O

0

10

A

14

9

A

13

8

A

12

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

A

1

5

A

2

6

A

3

7

A

4

8

A

5

9

A

10

6

A

7

11

A

8

0

1

2

3

OE

A

1

4

A

2

A

3

5

A

4

WE

6

V

CC

A

5

A

6

7

A7

A

8

A

9

A

10

A

11

12

A

9

13

A

10

14

11

I/O

0

12

I/O

1

I/O

13

2

GND

14

22

23

24

25

26

27

28

1

2

3

4

5

6

7

TSOP I

Top View

(not to scale)

Cypress Semiconductor Corporation • 3901 North First Street • San Jose, CA 95134 • 408-943-2600

Document #: 38-15001 Rev. *E Revised November 15, 2004

PRELIMINARY

CY9C62256

Overview

The CY9C62256 is a byte wide MRAM memory. The memory

array is logically organized as 32,768 x 8 and is accessed

using an industry standard parallel asynchronous SRAM-like

interface. The CY9C62256 is inherently nonvolatile and offers

write protect during sudden power loss. Functional operation

of the MRAM is similar to SRAM-type devices, otherwise.

Memory Architecture

Users access 32,768 memory locations each with eight data

bits through a parallel interface. Internally, the memory array

is organized into eight blocks of 512 rows x 64 columns each.

The access and cycle time are the same for read and write

memory operations. Unlike an EEPROM or Flash, it is not

necessary to poll the device for a ready condition since writes

occur at bus speed.

Memory Operation

The CY9C62256 is designed to operate in a manner similar to

other bytewide memory products. For users familiar with

BBSRAM, the MRAM performance is superior. For users

familiar with EEPROM, Flash and FeRAM, the obvious differences result from higher write performance of MRAM

technology and much higher write endurance.

All memory array bits are set to logic “1” at the time of

shipment.

Read Operation

A read cycle begins whenever WE

inactive (HIGH) and CE

(Chip Enable bar) and OE (Output

Enable bar) are active LOW. The unique address specified by

the 15 address inputs (A0–A14) defines which of the 32,768

bytes of data is to be accessed. Valid data will be available at

the eight output pins within t

address input is stable, providing that CE

are also satisfied. If CE

AA

and OE access times are not satisfied

then the data access must be measured from the

later-occurring signal (CE

either t

access.

for CE or t

ACE

or OE) and the limiting parameter is

for the OE rather than address

DOE

Write Cycle

The CY9C62256 initiates a write cycle whenever the WE

CE

signals are active (LOW) after address inputs are stable.

The later occurring falling edge of CE

start of the write cycle. The write cycle is terminated by the

earlier rising edge of CE

or WE. All address inputs must be

kept valid throughout the write cycle. The OE

should be kept inactive (HIGH) during write cycles to avoid bus

contention. However, if the output drivers are enabled (CE

OE

active) WE will disable the outputs in t

falling edge.

Unlike other nonvolatile memory technologies, there is no

write delay with MRAM. The entire memory operation occurs

in a single bus cycle. Therefore, any operation including read

or write can occur immediately following a write. Data Polling,

a technique used with EEPROMs to determine if the write is

complete is unnecessary. Page write, a technique used to

enhance EEPROM write performance is also unnecessary

because of inherently fast write cycle time for MRAM.

The total Write time for the entire 256K array is 2.3 ms.

(Write Enable bar) is

(access time) after the last

and OE access times

and

or WE will determine the

control signal

and

from the WE

HZWE

Write Inhibit and Data Retention Mode

This feature protects against the inadvertent write. The

CY9C62256 provides full functional capability for V

than 4.5V and write protects the device below 4.0V. Data is

greater

CC

maintained in the absence of VCC. During the power-up,

normal operation can resume 20 µs after V

Refer to page 8 for details.

is reached.

PFD

Sudden Power Loss—“Brown Out”

The nonvolatile RAM constantly monitors V

supply voltage decay below the operating range, the

. Should the

CC

CY9C62256 automatically write-protects itself, all inputs

become don’t care, and all outputs become high-impedance.

Refer to page 8 for details.

Silicon Signature/Device ID

An extra 64 bytes of MRAM are available to the user for Device

ID. By raising A9 to V

00(Hex) to 3F(Hex) on address pins A7, A6, A14, A13, A12

+ 2.0V and by using address locations

CC

and A0 (MSB to LSB) respectively, the additional Bytes may

be accessed in the same manner as the regular memory array,

with 140 ns access time. Dropping A9 from input high

(V

+ 2.0V) to < VCC returns the device to normal operation

CC

after 140-ns delay.

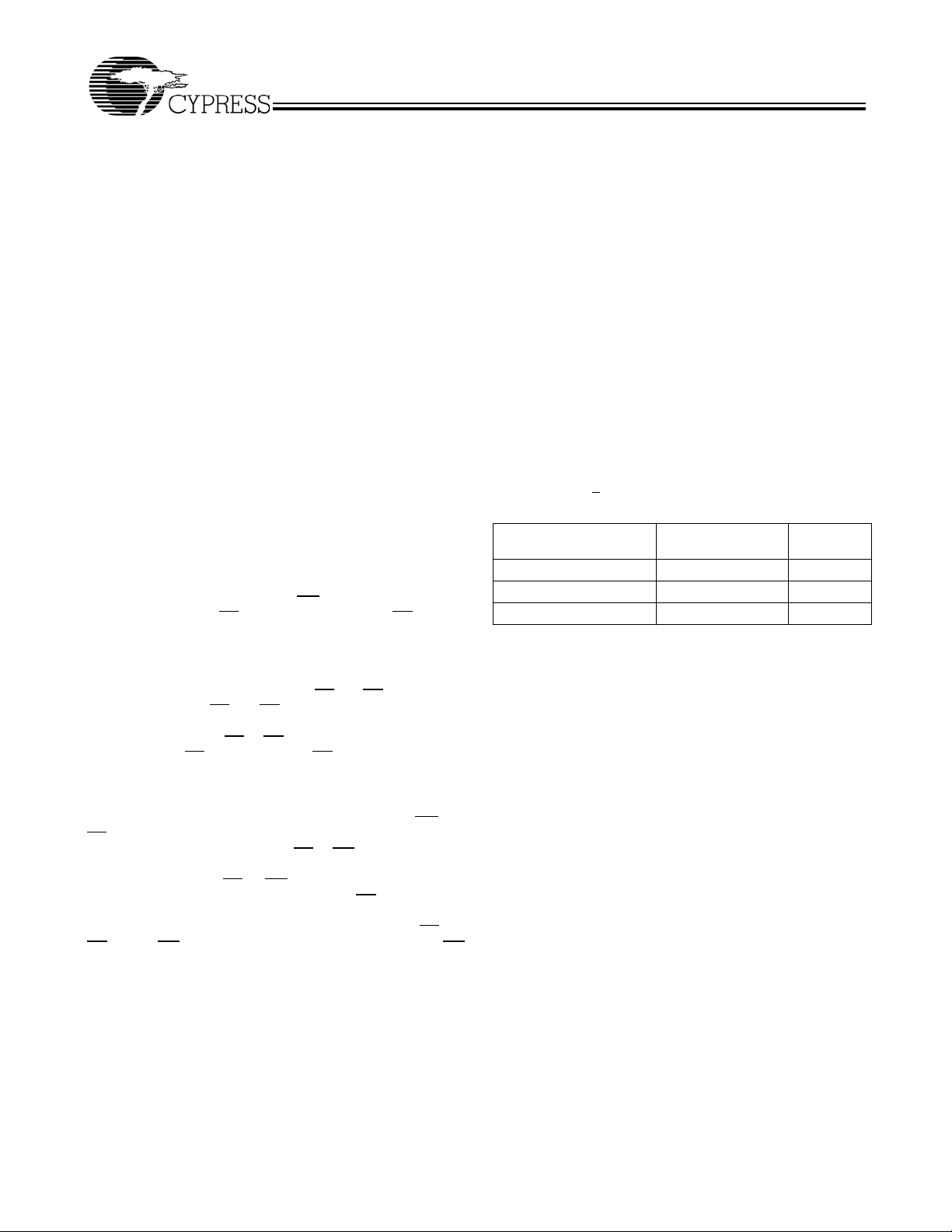

Address (MSB to LSB)

A7 A6 A14 A13 A12 A0 Description ID

00h Manufacturer ID 34h

01h Device ID 40h

02h – 3Fh User Space 62 Bytes

All User Space bits above are set to logic “1” at the time of

shipment.

Magnetic Shielding

CY9C62256 is protected from external magnetic fields through

the application of a “magnetic shield” that covers the entire

memory array.

Applications

Battery-Backed SRAM (BB SRAM) Replacement

CY9C62256 is designed to replace (plug and play) existing

BBSRAM while eliminating the need for battery and V

monitor IC, reducing cost and board space and improving

CC

system reliability.

The cost associated with multiple components and assemblies

and manufacturing overhead associated with battery-backed

SRAM is eliminated by using monolithic MRAM. CY9C62256

eliminates multiple assemblies, connectors, modules, field

maintenance and environmental issues common with BB

SRAM. MRAM is a true nonvolatile RAM with high performance, high endurance, and data retention.

Battery-backed SRAMs are forced to monitor V

switch to the backup battery. Users that are modifying existing

in order to

CC

designs to use MRAM in place of BB SRAM, can eliminate the

V

controller IC along with the battery. MRAM performs this

CC

function on chip.

Cost: The cost of both the component and manufacturing

overhead of battery-backed SRAM is high. In addition, there is

a built in rework step required for battery attachment in case

Document #: 38-15001 Rev. *E Page 2 of 11

PRELIMINARY

CY9C62256

of surface mount assembly. This can be eliminated with

MRAM. In case of DIP battery backed modules, the assembly

techniques are constrained to through-hole assembly and

board wash using no water.

System Reliability: Battery-backed SRAM is inherently

vulnerable to shock and vibration. In addition, a negative

voltage, even a momentary undershoot, on any pin of a

battery-backed SRAM can cause data loss. The negative

voltage causes current to be drawn directly from the battery,

weakens the battery, and reduces its capacity over time. In

general, there is no way to monitor the lost battery capacity.

MRAM guarantees reliable operation across the voltage range

with inherent nonvolatility.

Space: Battery-backed SRAM in DIP modules takes up board

space height and dictates through-hole assembly. MRAM is

offered in surface mount as well as DIP packages.

Field Maintenance: Batteries must eventually be replaced

and this creates an inherent maintenance problem. Despite

projections of long life, it is difficult to know how long a battery

will last, considering all the factors that degrade them.

Environmental: Lithium batteries are a potential disposal

burden and considered a fire hazard. MRAM eliminates all

such issues through a truly monolithic nonvolatile solution.

Users replacing battery-backed SRAMs with integrated Real

Time Clock (RTC) in the same package may need to move

RTC function to a different location within the system.

EEPROM Replacement

CY9C62256 can also replace EEPROM in current applications. CY9C62256 is pinout and functionally compatible to

bytewide EEPROM, however it does not need data-bar polling,

page write and hardware write protect due to its fast write and

inadvertent write protect features.

Users replacing EEPROMs with MRAM can eliminate the

page mode operation and simplify to standard asynchronous

write. Additionally, data-bar polling can be eliminated, since

every byte write is completed within same cycle. All writes are

completed within 70 ns.

FeRAM Replacement

FeRAM requires addresses to be latched on falling edge of

CE

, which adds to system overhead in managing the CE and

latching function. MRAM eliminates this overhead by offering

a simple asynchronous SRAM interface.

Users replacing FeRAM can simplify their address decoding

since CE

for each address. This overhead is eliminated when using

MRAM.

Secondly, MRAM read is nondestructive and no precharge

cycle is required like the one used with FeRAM.This has no

apparent impact to the design, however the read cycle time

can now see immediate improvement equal to the precharge

time.

Boot-up PROM (EPROM, PROM) Function Replacement

The CY9C62256 can be accessed like an EPROM or PROM.

When CE

the memory location determined by the address pins is

asserted on the outputs. MRAM may be used to accomplish

system boot up function using this condition.

does not need to be driven active and then inactive

and OE are low and WE is high, the data stored at

Document #: 38-15001 Rev. *E Page 3 of 11

PRELIMINARY

CY9C62256

Maximum Ratings

except in case of Super Voltage pin (A9) while accessing 64

device ID and Silicon signature Bytes.........−0.5V to VCC + 2.5V

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature .................................–65°C to +150°C

Ambient Temperature with

Power Applied...............................................–40°C to +85°C

Supply Voltage to Ground Potential

(Pin 28 to Pin 14) ........................................... –0.5V to +7.0V

DC Voltage Applied to Outputs

in High-Z State

DC Input Voltage

[1]

....................................–0.5V to VCC + 0.5V

[1]

.................................–0.5V to VCC + 0.5V

Output Current into Outputs (LOW)............................. 20 mA

Static Discharge Voltage ........................................> 2001V

(per MIL-STD-883, Method 3015)

Latch-up Current.....................................................> 200 mA

Maximum Exposure to Magnetic Field

@ Device Package

[2,3]

............................................ < 20 Oe

Operating Range

Range Ambient Temperature V

Commercial 0°C to +70°C 5V ± 10%

CC

Industrial –40°C to +85°C 5V ± 10%

Electrical Characteristics Over the Operating Range

CY9C62256-70

Parameter Description Test Conditions

V

OH

V

OL

V

IH

V

IL

[4]

I

IX

I

OZ

I

CC

I

SB1

I

SB2

Capacitance

Output HIGH Voltage VCC = Min., IOH = −1.0 mA 2.4 V

Output LOW Voltage VCC = Min., IOL = 2.1 mA 0.4 V

Input HIGH Voltage 2.2 VCC + 0.5V V

Input LOW Voltage –0.5

Input Leakage Current GND < VI < V

CC

Output Leakage Current GND < VO < VCC, Output Disabled –0.5 +0.5 µA

VCC Operating Supply Current VCC = Max.,

= 0 mA,

I

OUT

f = f

= 1/t

Automatic CE

Power-down Current—

TTL Inputs

Automatic CE

Power-down Current—

CMOS Inputs

[6]

MAX

Max. V

V

> VIH or

IN

V

< VIL, f = f

IN

Max. V

CE

> VCC − 0.3V

> VCC − 0.3V

V

IN

or V

IN

RC

, CE > VIH,

CC

MAX

,

CC

< 0.3V, f = 0

[1]

–0.5 +0.5 µA

[5]

Parameter Description Test Conditions Max. Unit

C

IN

C

OUT

Notes:

1. V

(min.) = –2.0V for pulse duration of 20 ns.

IL

2. Magnetic field exposure is highly dependent on the distance from the magnetic field source. The magnetic field falls off as 1/R squared, where R is the distance

from the magnetic source.

3. Exposure beyond this level may cause loss of data.

during access to 64 device ID and silicon signature bytes with super voltage pin at V

4. I

IX

5. Typical specifications are the mean values measured over a large sample size across normal production process variations and are taken at nominal conditions

= 25°C, VCC). Parameters are guaranteed by design and characterization, and not 100% tested.

(T

A

6. Tested initially and after any design or process changes that may affect these parameters.

Input Capacitance TA = 25°C, f = 1 MHz,

V

= 5.0V

Output Capacitance 8 pF

CC

+ 2.0V will be 100 µA max.

CC

6pF

Max.

UnitMin. Typ.

0.8 V

60 mA

500 µA

90 µA

Document #: 38-15001 Rev. *E Page 4 of 11

PRELIMINARY

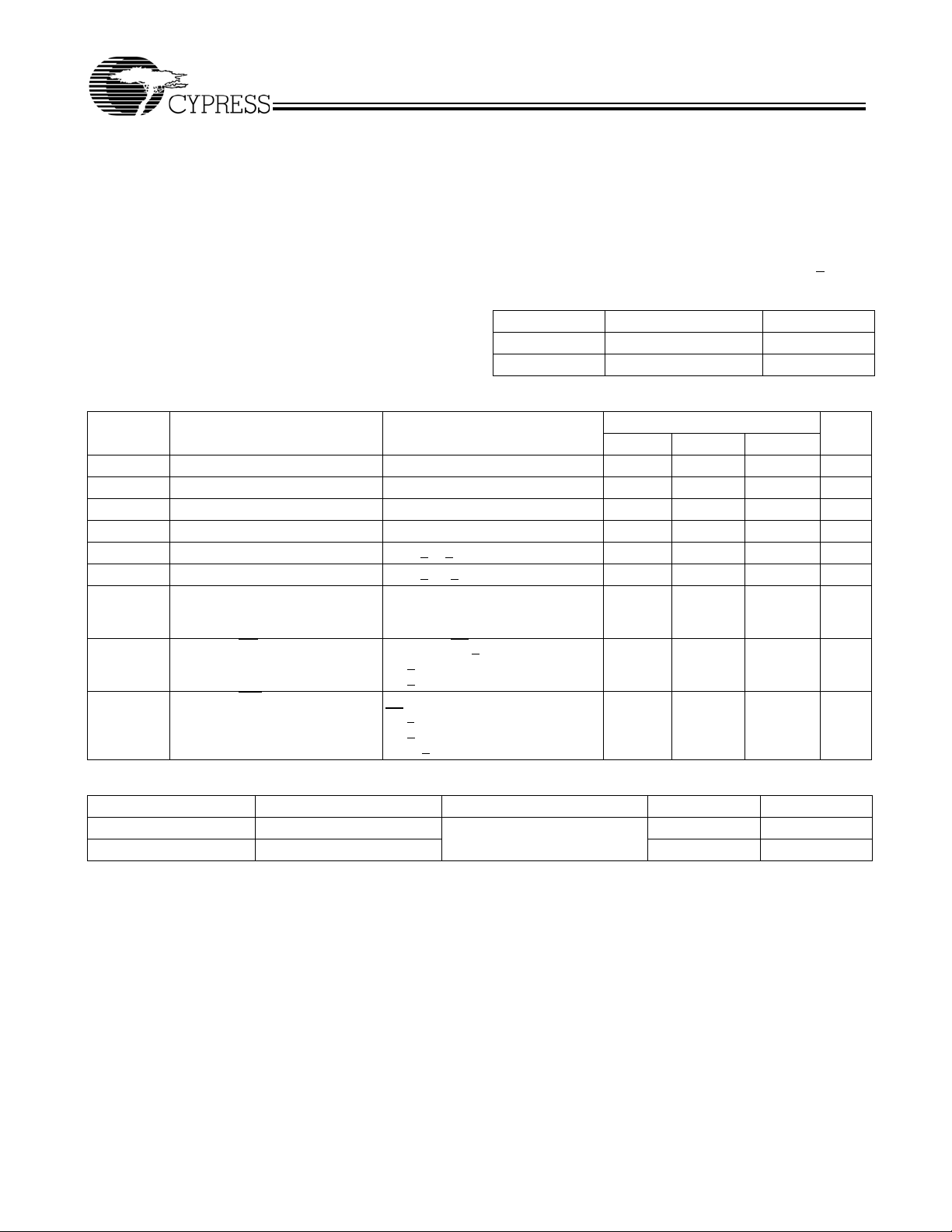

AC Test Loads and Waveforms

5V

R1 1800

OUTPUT

100 pF

INCLUDING

JIG AND

SCOPE

Ω

5V

OUTPUT

R2

990Ω

5pF

INCLUDING

(a) (b)

JIG AND

SCOPE

Switching Characteristics Over the Operating Range

R1 1800

Ω

R2

990Ω

[7]

3.0V

GND

10%

90%

<5ns

Equivalent to: THEVENIN EQUIVALENT

OUTPUT 1.77V

ALL INPUT PULSES

CY9C62256

90%

10%

<5ns

639Ω

CY9C62256-70

Parameter Description

UnitMin. Max.

Read Cycle

t

RC

t

AA

t

OHA

t

ACE

t

DOE

t

LZOE

t

HZOE

t

LZCE

t

HZCE

t

PU

t

PD

Write Cycle

t

WC

t

SCE

t

AW

t

HA

t

SA

t

PWE

t

SD

t

HD

t

HZWE

t

LZWE

Notes:

7. Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified

I

OL/IOH

8. At any given temperature and voltage condition, t

9. t

HZOE

10. The internal write time of the memory is defined by the overlap of CE

terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

11. The minimum write pulse width for write cycle #3 (WE

[10,11]

and 100-pF load capacitance.

, t

, and t

HZCE

HZWE

Read Cycle Time 70 ns

Address to Data Valid 70 ns

Data Hold from Address Change 5 ns

CE LOW to Data Valid 70 ns

OE LOW to Data Valid 35 ns

OE LOW to Low Z

OE HIGH to High Z

CE LOW to Low Z

CE HIGH to High Z

[8]

[8]

[8,9]

[8,9]

5ns

25 ns

5ns

25 ns

CE LOW to Power-up 0 ns

CE HIGH to Power-down 70 ns

Write Cycle Time 70 ns

CE LOW to Write End 60 ns

Address Set-up to Write End 60 ns

Address Hold from Write End 0 ns

Address Set-up to Write Start 0 ns

WE Pulse Width 50 ns

Data Set-up to Write End 30 ns

Data Hold from Write End 0 ns

WE LOW to High Z

WE HIGH to Low Z

are specified with CL = 5 pF as in part (b) of AC Test Loads. Transition is measured ±500 mV from steady-state voltage.

[8, 9]

[8]

is less than t

HZCE

controlled, OE LOW) is the sum of t

, t

LZCE

HZOE

LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can

is less than t

LZOE

HZWE

, and t

and tSD.

HZWE

is less than t

25 ns

5ns

for any given device.

LZWE

Document #: 38-15001 Rev. *E Page 5 of 11

Switching Waveforms

Read Cycle No. 1

[12, 13]

ADDRESS

DATA OUT PREVIOUS DATA VALID

t

OHA

PRELIMINARY

t

RC

t

AA

CY9C62256

DATA VALID

Read Cycle No. 2

[13,14]

CE

OE

DATA OUT

V

CC

SUPPLY

HIGH IMPEDANCE

t

LZCE

t

PU

CURRENT

Write Cycle No. 1 (WE Controlled)

ADDRESS

CE

t

WE

SA

t

ACE

t

LZOE

50%

[10,15,16]

t

DOE

t

AW

t

RC

t

HZOE

t

DATA VALID

HZCE

t

PD

HIGH

IMPEDANCE

ICC

50%

ISB

t

WC

t

HA

t

PWE

OE

DATA I/O

Notes:

12. Device is continuously selected. OE

is HIGH for read cycle.

13. WE

14. Address valid prior to or coincident with CE

15. Data I/O is high impedance if OE

goes HIGH simultaneously with WE HIGH, the output remains in a high-impedance state.

16. If CE

17. During this period, the I/Os are in output state and input signals should not be applied.

NOTE

17

= VIH.

t

HZOE

, CE = VIL.

transition LOW.

t

SD

DATA IN VALID

t

HD

Document #: 38-15001 Rev. *E Page 6 of 11

Switching Waveforms (continued)

PRELIMINARY

CY9C62256

Write Cycle No. 2 (CE Controlled)

ADDRESS

CE

WE

DATA I/O

[10,15,16]

t

SA

Write Cycle No. 3 (WE Controlled, OE LOW)

ADDRESS

CE

t

WE

SA

t

[11,16]

AW

t

AW

t

WC

t

WC

t

SCE

t

SD

DATA IN VALID

t

HA

t

HD

t

HA

DATA I/O

NOTE 17

t

HZWE

t

SD

DATA IN VALID

t

LZWE

t

HD

Truth Table

CE WE OE V

CC

H X X 4.5V–5.5V High Z Deselect/Power-down Standby (I

L H L 4.5V–5.5V Data Out Read Active (I

L L X 4.5V–5.5V Data In Write Active (I

L H H 4.5V–5.5V High Z Deselect, Output Disabled Active (I

X X X <4.0V Inputs = X, Outputs = Hi-Z Write Inhibit Active (I

Inputs/Outputs Mode Power

CC

CC

CC

CC

SB

)

)

)

)

)

Document #: 38-15001 Rev. *E Page 7 of 11

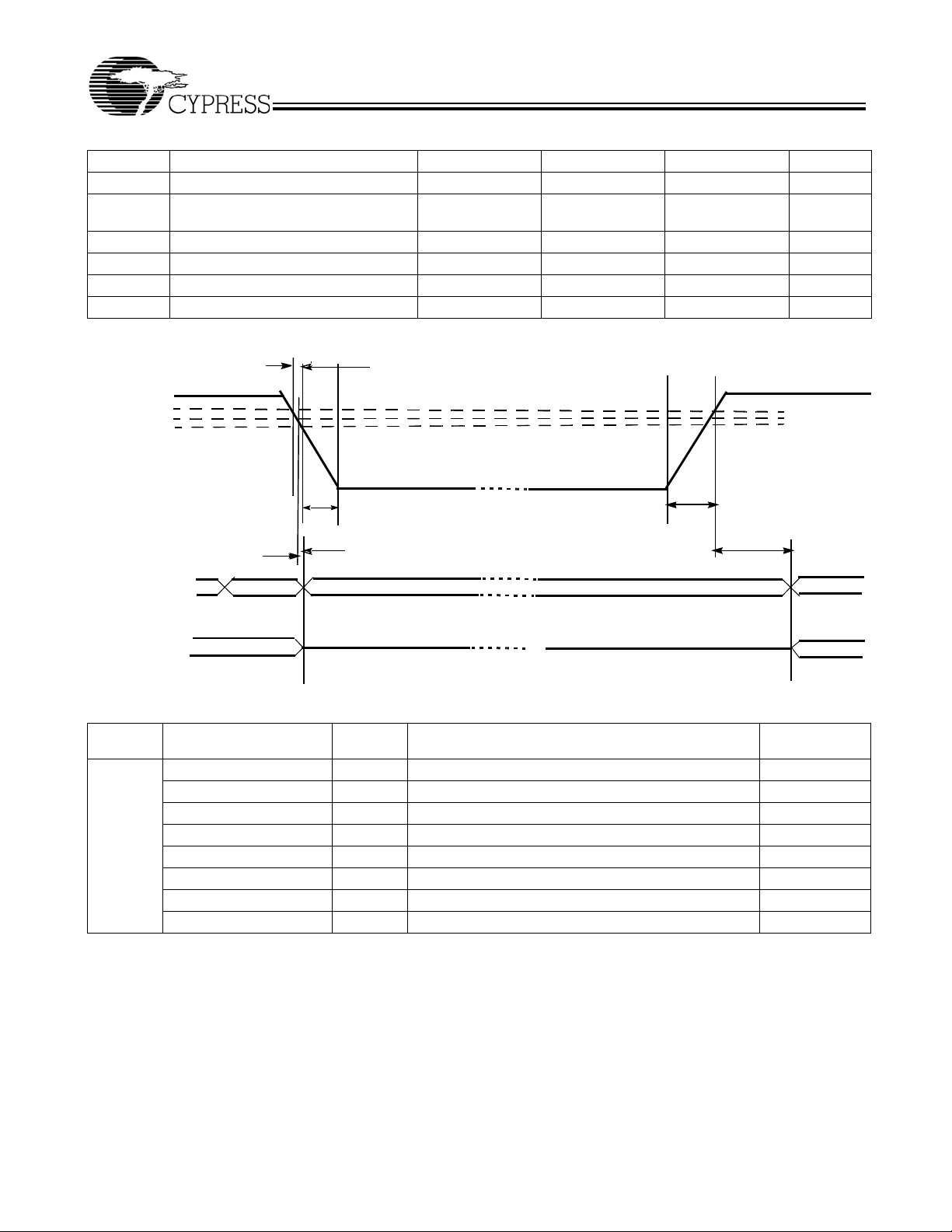

PRELIMINARY

V

CY9C62256

Power-down/-up Mode AC Waveforms

Parameter Description Min. Typ. Max. Unit

V

t

F

t

FB

t

R

t

WP

t

REC

V

PFD

[18]

PFD

PFD

Vcc

(max)

Power-fail Deselect Voltage 4.2 4.35 4.5 V

V

(max.) to V

PFD

Time

V

(min.) to VSS VCC Fall Time 50 µs

PFD

VSS to V

Write Protect Time On V

V

(max.) to Inputs Recognized 500 µs

PFD

(min)

(max.) Rise Time 20 µs

PFD

(min.) VCC Fall

PFD

CC

t

F

100 µs

= V

(typ) 20 µs

PFD

V

PFD

(typ)

t

R

t

R

t

REC

RECOGNIZED

VAL ID

INPUTS

OUTPUTS

t

RECOGNIZED

VAL ID

WP

t

FB

DON’T CARE

HIGH-Z

Ordering Information

Speed

(ns) Ordering Code

70 CY9C62256−70SC S21 28-lead (300-mil) Molded SOIC Commercial

CY9C62256-70SI S21 28-lead (300-mil) Molded SOIC Industrial

CY9C62256-70SNC SN28 28-lead (300-mil) Narrow Body SOIC Commercial

CY9C62256-70SNI SN28 28-lead (300-mil) Narrow Body SOIC Industrial

CY9C62256−70ZC Z28 28-lead Thin Small Outline Package Commercial

CY9C62256−70ZI Z28 28-lead Thin Small Outline Package Industrial

CY9C62256−70PC P15 28-lead (600-mil) Molded DIP Commercial

CY9C62256-70PI P15 28-lead (600-mil) Molded DIP Industrial

Note:

(max.) to V

18. V

PFD

(min.) fall time of less than tF may result in deselection/ write protection not occurring until 20 µs after VCC passes V

PFD

Package

Name Package Type

Operating

Range

(min.).

PFD

Document #: 38-15001 Rev. *E Page 8 of 11

Package Diagrams

()

PRELIMINARY

28-lead (600-mil) Molded DIP P15

28-Lead (300-Mil) Molded SOIC S21

PIN 1 ID

CY9C62256

51-85017-*A

0.050[1.27]

TYP.

15 28

0.697[17.70]

0.713[18.11]

0.013[0.33]

0.019[0.48]

114

0.291[7.39]

0.300[7.62]

0.026[0.66]

0.032[0.81]

0.092[2.33]

0.105[2.67]

0.004[0.10]

0.0118[0.30]

0.394[10.01]

0.419[10.64]

*

SEATING PLANE

0.004[0.10]

DIMENSIONS IN INCHES[MM]

*

REFERENCE JEDEC MO-119

PACKAGE WEIGHT 0.85gms

PAR T #

SZ28.3 LEAD FREE PKG.

0.015[0.38]

0.050[1.27]

MIN.

MAX.

PART #

S28.3 STANDARDPKG.

SZ28.3 LEAD FREE PKG.

MIN.

MAX.

0.0091[0.23]

0.0125[3.17]

51-85026-*C

*

Document #: 38-15001 Rev. *E Page 9 of 11

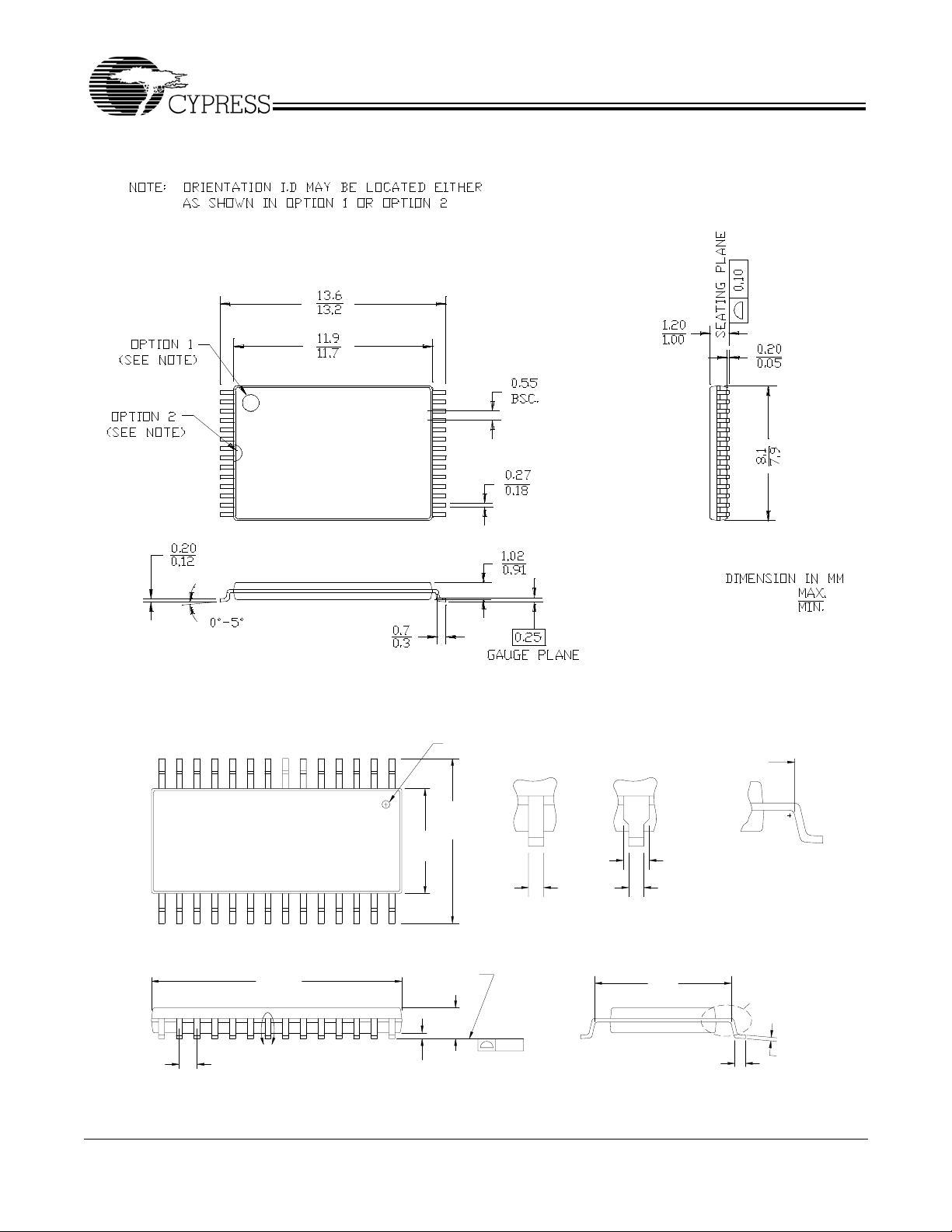

Package Diagrams (continued)

28-lead Thin Small Outline Package Type 1 (8 × 13.4 mm) Z28

PRELIMINARY

CY9C62256

450-mil Wide (300-mil Body Width) 28-pin Narrow SOIC (SN28)

0.390

0.420

0.015

0.020

MIN.

MAX.

0.020

0.042

0.390

0.420

DETAIL "B"

B

0.050

TYP.

0.702

0.710

A

PIN 1 ID

0.291

0.300

0.002

0.014

0.463

0.477

0.014

0.020

SEATING PLANE

0.094

0.110

DIMENSIONS IN INCHES

OMEDATA

0.026

0.032

DETAIL "A"

0.004

CSPI

All product and company names mentioned in this document may be the trademarks of their respective holders.

51-85071-*G

0.008

0.012

51-85092-*B

Document #: 38-15001 Rev. *E Page 10 of 11

© Cypress Semiconductor Corporation, 2004. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be

used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its

products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

PRELIMINARY

CY9C62256

Document History Page

Document Title: CY9C62256 32K x 8 Magnetic Nonvolatile CMOS RAM

Document Number: 38-15001

REV. ECN NO. Issue Date

** 115831 05/29/02 NBP New data sheet

*A 116770 07/25/02 NBP Add state of memory bits at the time of shipment

*B 117612 07/26/02 LJN Minor Change needed to change footer from 38-15003 to 38-15001

*C 208424 SEE ECN NBP Icc, Isb1, Isb2, Non-Operating Shielding Specification, Condition to emulate

*D 227582 SEE ECN NBP Changed Magnetic Shielding Specification

*E 285756 SEE ECN NBP Added SNC 28-pin SOIC package and Changed V

Orig. of

Change Description of Change

Boot PROM functionality

and tWP specification

PFD

Document #: 38-15001 Rev. *E Page 11 of 11

Loading...

Loading...