Page 1

PSoC™ Mixed Signal Array Final Data Sheet

Features

CY8C22113 and CY8C22213

■ Powerful Harvard Architecture Processor

■ Advanced Peripherals (PSoC Blocks)

❐ M8C Processor Speeds to 24 MHz

❐ Low Power at High Speed

❐ 3.0 to 5.25 V Operating Voltage

❐ Industrial Temperature Range: -40°C to +85°C

❐ 3 Rail-to-Rail Analog PSoC Blocks Provide:

- Up to 14-Bit ADCs

- Up to 9-Bit DACs

- Programmable Gain Amplifiers

- Programmable Filters and Comparators

❐ 4 Digital PSoC Blocks Provide:

- 8- to 32-Bit Timers, Counters, and PWMs

- CRC and PRS Modules

- Full-Duplex UART

- SPI Masters or Slaves

- Connectable to all GPIO Pins

❐ Complex Peripherals by Combining Blocks

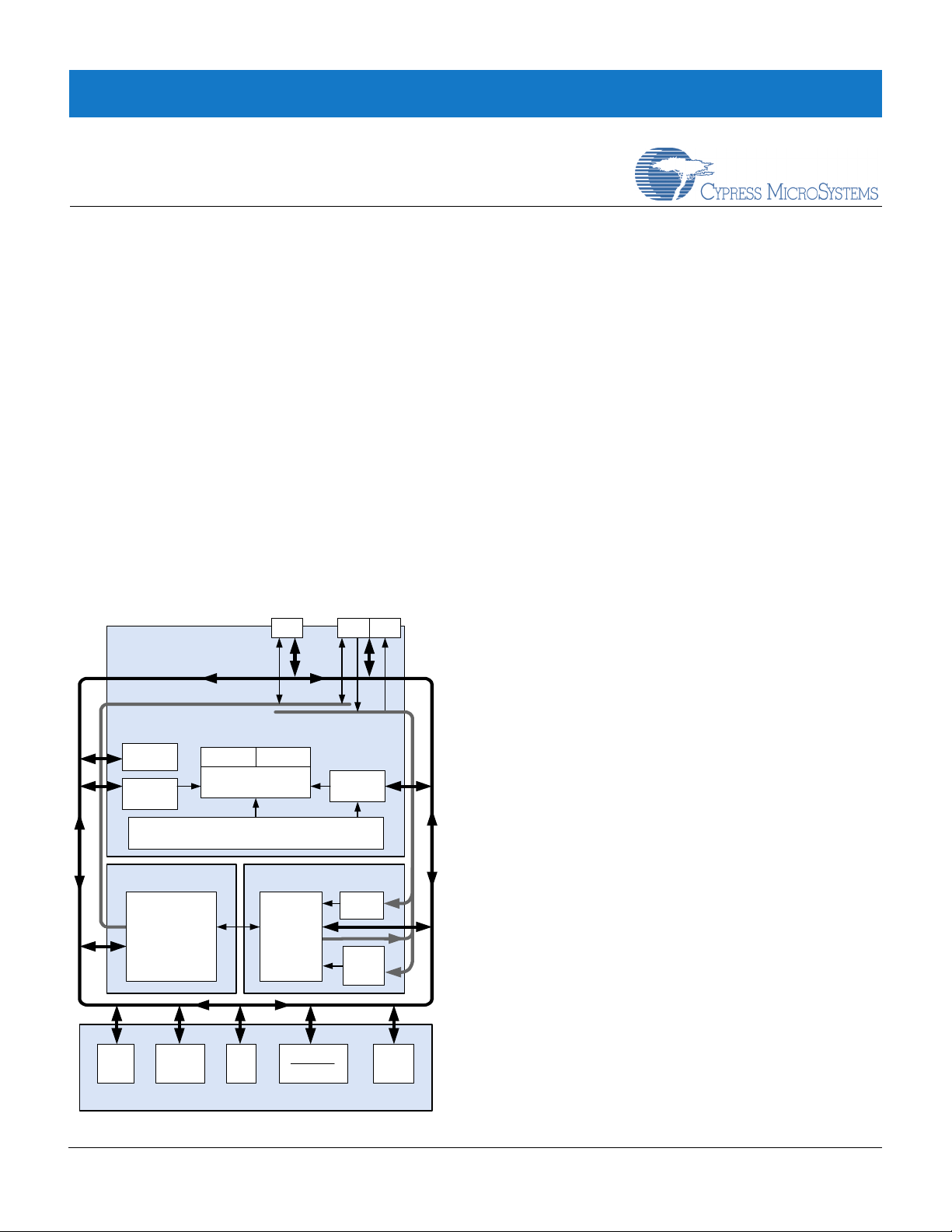

Port 1 Port 0

PSoC CORE

SYSTEM BUS

Global Digital Interconnect

SRAM

256 Bytes

Interrupt

Controller

SROM Flash 2K

CPU Core (M8C)

Multiple Clock Sources

(Includes IMO, ILO, PLL, and ECO)

DIGITAL SYSTE M

Digital

Block Array

(1 Row,

4 Blocks)

Global Analog Interconnect

ANALOG SYSTEM

Analog

Block

Array

(1 Column,

3 Blocks)

■ Precision, Programmable Clocking

❐ Internal ±2.5% 24/48 MHz Oscillator

❐ High-Accuracy 24 MHz with Optional 32.768

kHz Crystal and PLL

❐ Optional External Oscillator, up to 24 MHz

❐ Internal Oscillator for Watchdog and Sleep

■ Flexible On-Chip Memory

❐ 2K Bytes Flash Program Storage 50,000

Erase/Write Cycles

❐ 256 Bytes SRAM Data Storage

❐ In-System Serial Programming (ISSP )

❐ Partial Flash Updat es

❐ Flexible Protection Modes

❐ EEPROM Emulation in Flash

■ Programmable Pin Configurations

❐ 25 mA Sink on all GPIO

❐ Pull up, Pull down, High Z, Strong, or Open

Drain Drive Modes on all GPIO

❐ Up to 8 Analog Inputs on GPIO

❐ One 30 mA Analog Outputs on GPIO

❐ Configurable Interrupt on all GPIO

Analog

Drivers

PSoC™ Functional Overview

The PSoC™ family consists of many Mixed Signal Array with

On-Chip Controller devices. These devices are designed to

replace multiple traditional MCU-based system components

with one, low cost single-chip programmable device. PSoC

devices include configurable blocks of analog and digital logic,

as well as programmable interconnects. This architecture

allows the user to create customized peripheral configurations

Sleep and

Watchdog

that match the requirements of each individual application.

Additionally, a fast CPU, Flash program memory, SRAM data

memory, and configurable IO are included in a range of convenient pinouts and packages.

The PSoC architecture, as illustrated on the left, is com pri se d of

four main areas: PSoC Core, Digital System, Analog System,

Analog

Ref

and System Resources. Configurable global busing allows all

the device r esources to be c ombined into a compl ete custom

system. The PSoC CY8C22x13 family can have up to two IO

ports that connec t to the gl obal di git al and a nalog i ntercon ne cts ,

Analog

Input

Muxing

providing access to 4 digital blocks and 3 analog blocks.

The PSoC Core

■ Additional System Resources

2

❐ I

C Slave, Master, and Multi-Master to

400 kHz

❐ Watchdog and Sleep Timers

❐ User-Configurable Low Voltage Detection

❐ Integrated Supervisory Circuit

❐ On-Chip Precision Voltage Reference

■ Complete Development Tools

❐ Free Development Software

(PSoC™ Designer)

❐ Full-Featured, In-Circuit Emulator and

Programmer

❐ Full Speed Emulation

❐ Complex Breakpoint Structure

❐ 128K Bytes Trace Memory

The PSoC Core is a powerful engine that supports a rich feature set. Th e co re in cl ud es a C PU , memo r y, clocks, and c on fig urable GPIO (General Purpose IO).

The M8C C PU core is a powerfu l proce ssor wit h spee ds up t o

24 MHz, providing a four MI PS 8-bit Harvar d archit ecture m icro-

Digital

Clocks

Decimator

I2C

SYSTEM RESOURCES

POR and LVD

System Resets

Internal

Voltage

Ref.

June 2004 © Cypress MicroSystems, Inc. 2004 — Document No. 38-12009 Rev. *E 1

[+] Feedback

Page 2

CY8C22x13 Final Data Sheet PSoC™ Overview

processor. The CPU utilizes an interrupt controller with 10 vectors, to simplify programming of real time embedded events.

Program execution is timed and protected using the included

Sleep and Watch Dog Timers (WDT).

Memory encompasses 2 KB of Flash for program storage, 256

bytes of SRAM for data storage, and up to 2 KB of EEPROM

emulated using the Flash. Program Flash utilizes four protection levels on blocks of 64 bytes, allowing customized software

IP protection.

The PSoC device incorporates flexible internal clock generators, including a 24 MHz IMO (internal main oscillator) accurate

to 2.5% over temperature and voltage. The 24 MHz IMO can

also be doubled to 48 MHz for use by the digital system. A low

power 32 kHz ILO (internal low speed oscillator) is provided for

the Sleep timer and WDT. If crystal accuracy is desired, the

ECO (32.768 kHz external crystal oscillator) is available for use

as a Real Time Cloc k (RT C) and can opti onally genera te a crys tal-accurate 24 MHz system clock using a PLL. The clocks,

together with programmable clock dividers (as a System

Resource), provide the flexibility to integrate almost any timing

requirement into the PSoC device.

PSoC GPIOs provide conne ct ion t o the CP U, di gital and analog

resources of the devi ce. Each pin’ s dri ve mod e may b e selec te d

from eight options, allowing great flexibility in external interfacing. Every pin also has the c apa bility to gen erate a syste m inte rrupt on high level, low level, and change from last read.

The Digital System

The Digital System is composed of 4 digital PSoC blocks. Each

block is an 8-bit resource that can be used alone or combined

with other blocks to fo rm 8, 16 , 24, and 32-bit p eriphe rals, wh ich

are called user module references.

Port 1 Port 0

To System Bus

o

C

l

c

a

k

g

l

i

D

i

F

r

s

t

C

o

o

m

r

e

DIGITAL SYSTEM

Digital PSoC Block Array

8

DBB00 DBB01 DCB02 DCB03

Row Input

Configuration

Row 0

To Analog

System

4

4

Configuration

Row Output

8

Digital peripheral configurations include those listed below.

■ PWMs (8 to 32 bit)

■ PWMs with Dead band (8 to 32 bit)

■ Counters (8 to 32 bit)

■ Timers (8 to 32 bit)

■ UART 8-bit with selectable parity (up to 1)

■ SPI master and slave (up to 1)

■ I2C slave and master (1 available as a System Resource)

■ Cyclical Redundancy Checker/Generator (8 to 32 bit)

■ IrDA (up to 1)

■ Pseudo Random Sequence Generators (8 to 32 bit)

The digital blocks can be connected to any GPIO through a

series of global buses that can route any signal to any pin. The

buses also allow for signal multiplexing and for performing logic

operations. This co nfig ura bil ity free s y our d e si gn s fro m th e co nstraints of a fixed peripheral controller.

Digital blocks are provided in rows of four, where the number of

blocks varies by PSoC device family. This allows you the optimum choice of system resources for your application. Family

resources are shown in the table titled “PSoC Device Charac-

teristics” on page 3.

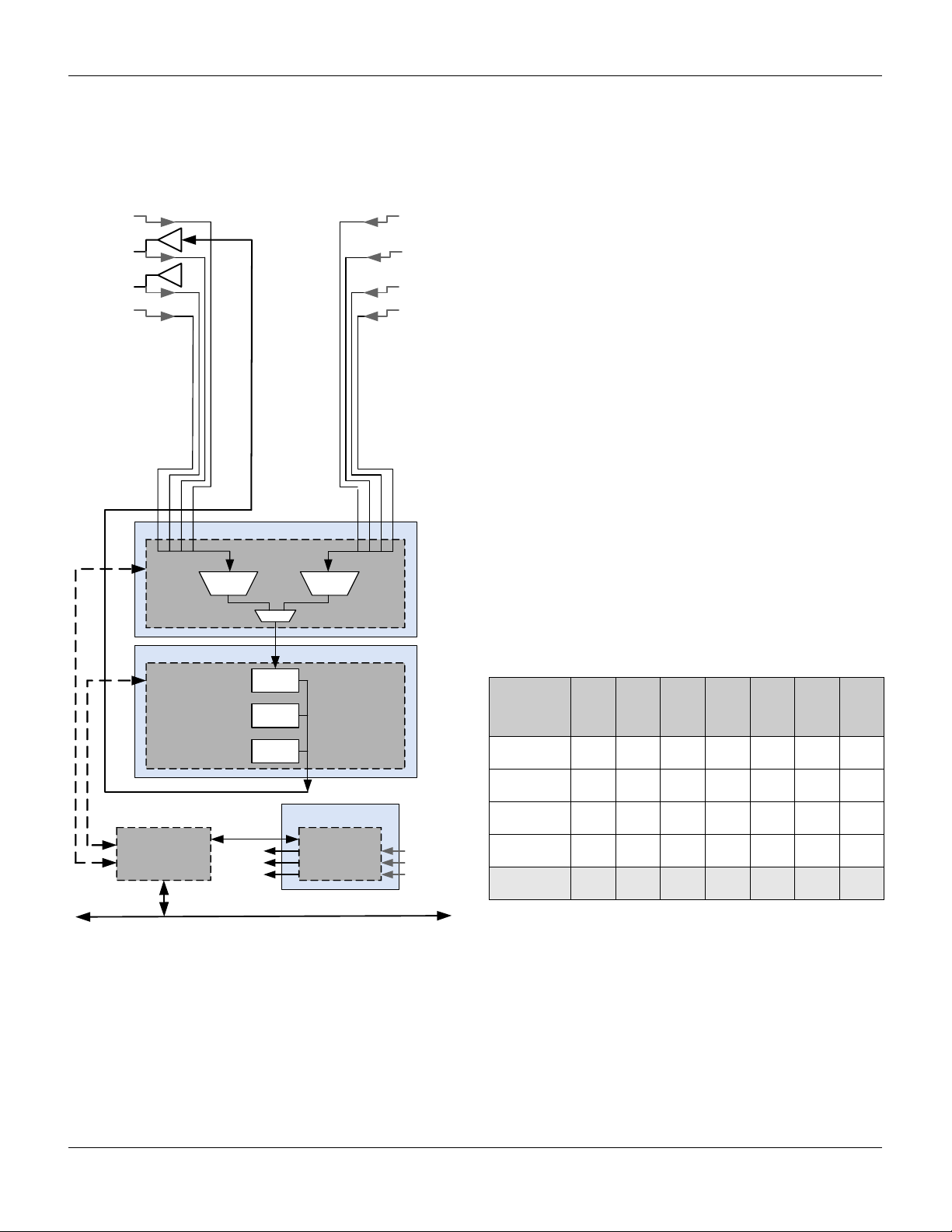

The Analog System

The Analog System is com posed of 3 configurable blocks, eac h

comprised of an opamp circuit allowing the creation of complex

analog signal flows. Analog peripherals are very flexible and

can be customized to support specific application requirements .

Some of the more common PSoC analog functions (most available as user modules) are listed below.

■ Analog-to-digital converters (one with 6- to 14-bit resolution,

selectable as Incremental, Delta Sigma, and SAR)

■ Filters (two pole band-pass, low-pass, and notch)

■ Amplifiers (one with selectable gain to 48x)

■ Comparators (one with 16 sel ectable thresholds)

■ DACs (one with 6- to 9-bit resolution)

■ Multiplying DACs (one with 6- to 9-bit resolution)

■ High current output drivers (one with 30 mA drive as a Core

Resource)

■ 1.3V refer ence (as a System Resource)

■ Many other topologies possible

88

GIE[7:0]

GIO[7:0]

Global Digital

Interconnect

GOE[7:0]

GOO[7:0]

Digital System Block Diagram

June 3, 2004 Document No. 38-12009 Rev. *E 2

[+] Feedback

Page 3

CY8C22x13 Final Data Sheet PSoC™ Overview

p

Analog blocks are provided in columns of three, which includes

one CT (Continuous Time) and two SC (Switched Capacitor)

blocks. The number of bloc ks is depe ndant on the device family

which is detailed in the table titled “PSoC Device Characteris-

tics” on page 3.

P0[7]

P0[5]

P0[3]

P0[1]

Array Input Configuration

P0[6]

P0[4]

P0[2]

P0[0]

Additional System Resources

System Resources, some of which have been previously listed,

provide additional capability useful to complete systems. Additional resources inclu de a deci mator, low voltage detection, and

power on reset. Brief statements describing the merits of each

system resource are presented below.

■ Digital clock dividers provide three customizable clock fre-

quencies for use in applic ations . The clo cks c an be route d to

both the digital a nd analog systems. Additiona l clocks c an be

generated using digital PSoC blocks as clock dividers.

■ The decimator provides a custom hardware filter for digital

signal processing applications inc lud in g t he c r eati on of D e lta

Sigma ADCs.

■ The I2C module provides 100 and 400 kHz communication

over two wires. Slave, master, and multi-master modes are

all supported.

■ Low Voltage Detection (LVD) interrupts can signal the appli-

cation of f alling voltage levels, w hile the adv anced POR

(Power On Reset) circuit eliminates the need for a system

supervisor.

■ An internal 1.3 voltage reference provides an absolute refer-

ence for the analog system, including ADCs and DACs.

PSoC Device Characteristics

Block Array

ACB01

ASD11

ASC21

Analog Reference

Interface to

Digital System

M8C Interface (Address Bus, Data Bus, Etc.)

RefHi

RefLo

AGND

Analog System Block Diagram

ACI1[1:0]ACI0[1:0]

Reference

Generators

AGNDIn

RefIn

Bandga

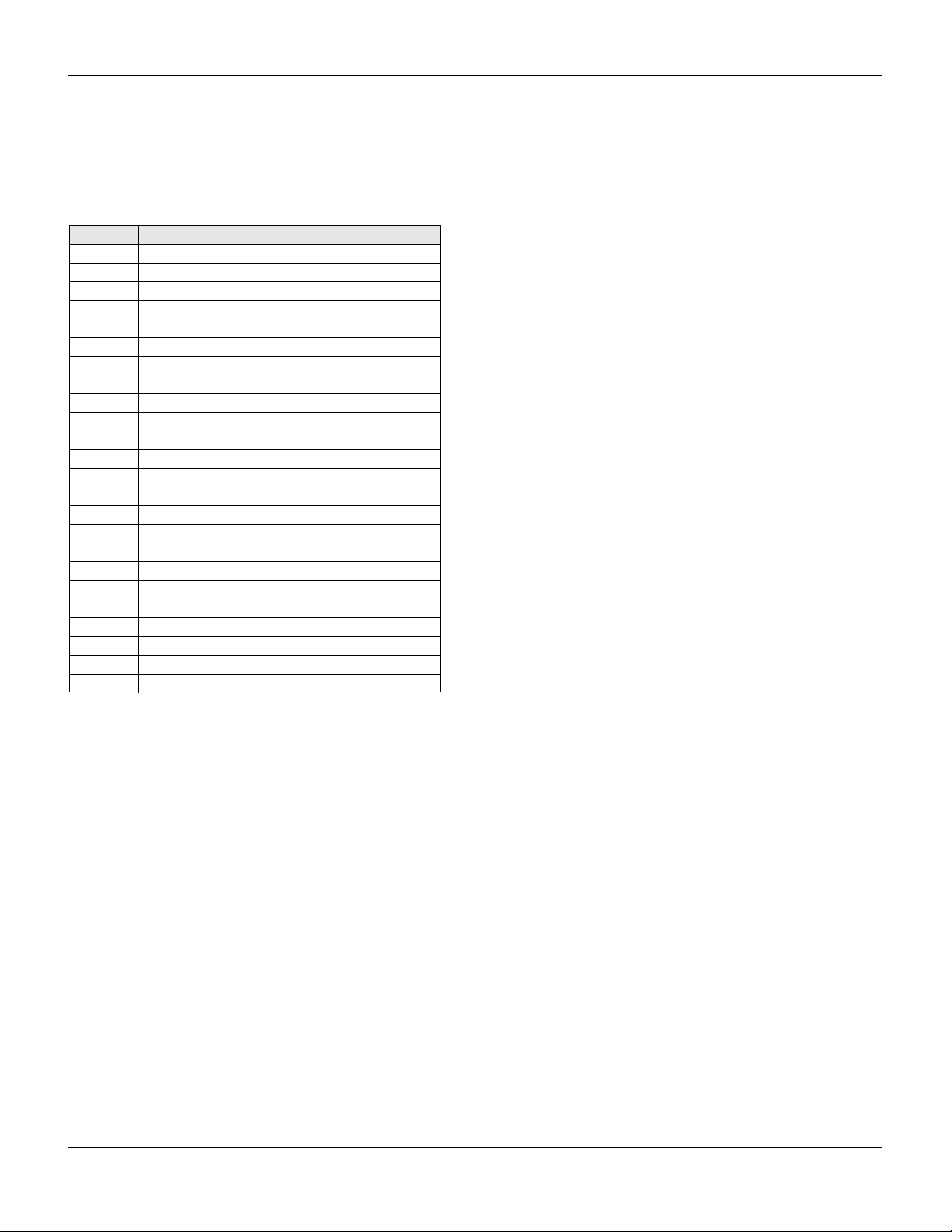

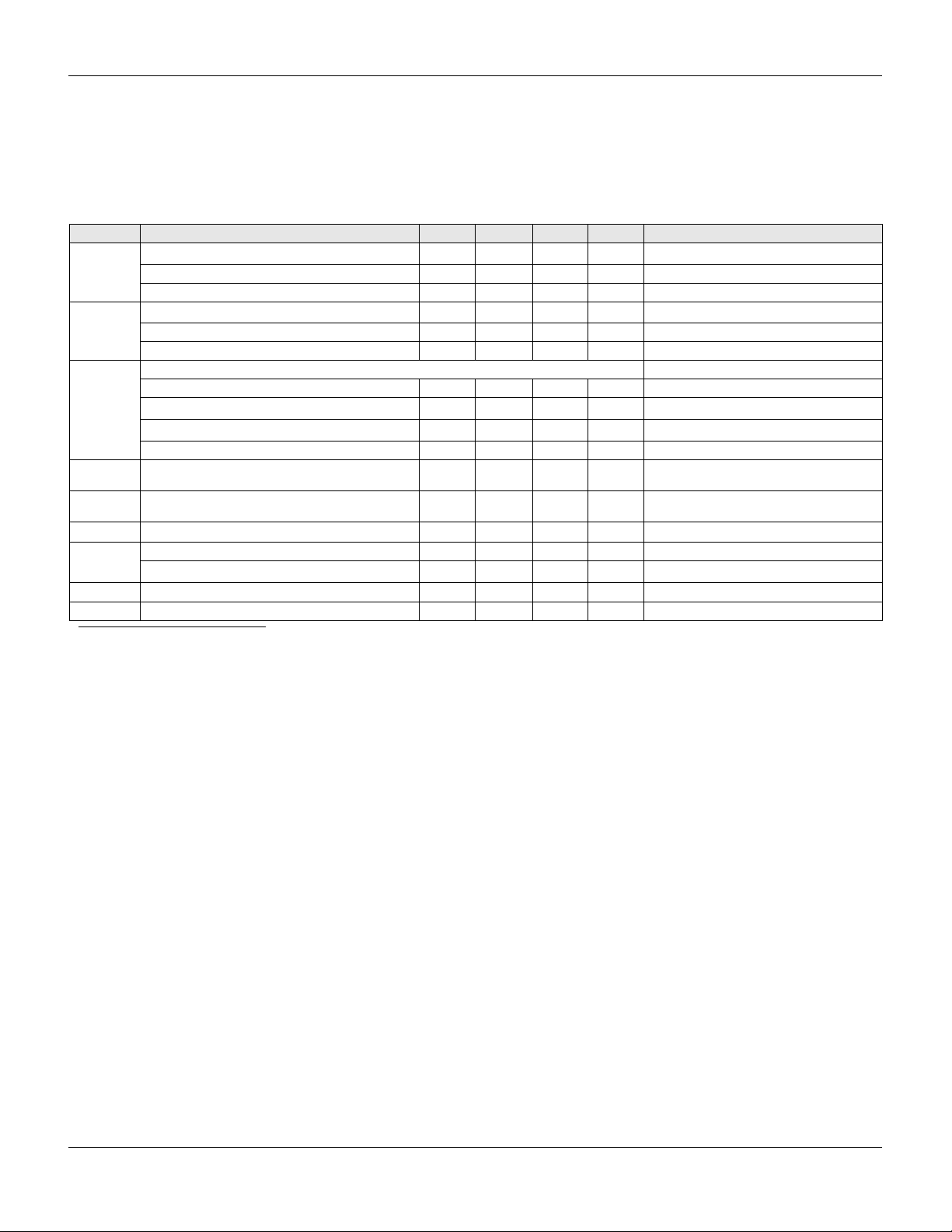

Depending on your PSoC device characteristics, the digital and

analog systems can have 16, 8, or 4 digital blocks and 12, 6, or

3 analog blocks. The following table lists the resources

available for specific PSoC device groups.

PSoC Device Characteristics

PSoC Part

Number

CY8C29x66

CY8C27x66

CY8C27x43

CY8C24x23

CY8C22x13

Digital

up to

64

up to

44

up to

44

up to

24

up to

16

IO

Rows

Digital

Digital

4 16 12 4 4 12

2 8 12 4 4 12

2 8 12 4 4 12

1 4 12 2 2 6

1 4 8 1 1 3

Blocks

Inputs

Analog

Analog

Outputs

Analog

Analog

Columns

Blocks

June 3, 2004 Document No. 38-12009 Rev. *E 3

[+] Feedback

Page 4

CY8C22x13 Final Data Sheet PSoC™ Overview

Getting Started

The quickest path to understanding th e PSoC s ili co n is by rea ding this data sheet and using the PSoC Designer Integrated

Development Environment (IDE). This data sheet is an overview of the PSoC integrated circuit and presents specific pin,

register, and electrical specifications. For in-depth information,

along with detailed programming information, reference the

PSoC™ Mixed Signal Array Technical Reference Manual.

For up-to-date Ordering, Packag ing, an d Electri cal Specification

information, reference the latest PSoC device data sheets on

the web at http://www.cypress.com/psoc.

Development Kits

Development Kits are available from the following distributors:

Digi-Key, Avnet, Arrow, and Future. The Cypress Online Store

at http://www.onfulfillment.com/cypressstore/ contains develop-

ment kits, C compilers, and all accessories for PSoC development. Click on PSoC (Programmable System-on-Chip) to view

a current list of available items.

Tele-Training

Free PSoC "Tele-training" is available for beginners and taught

by a live marketing or appli ca tio n eng in eer ov er th e pho ne . F ive

training cl asses are availabl e to accelerate th e learning curve

including introduction, designing, debugging, advanced design,

advanced analog, as well as application-specific classes covering topics like PSoC and the LIN bus. For days and times of the

tele-training, see http://www.cypress.com/support/training.cfm.

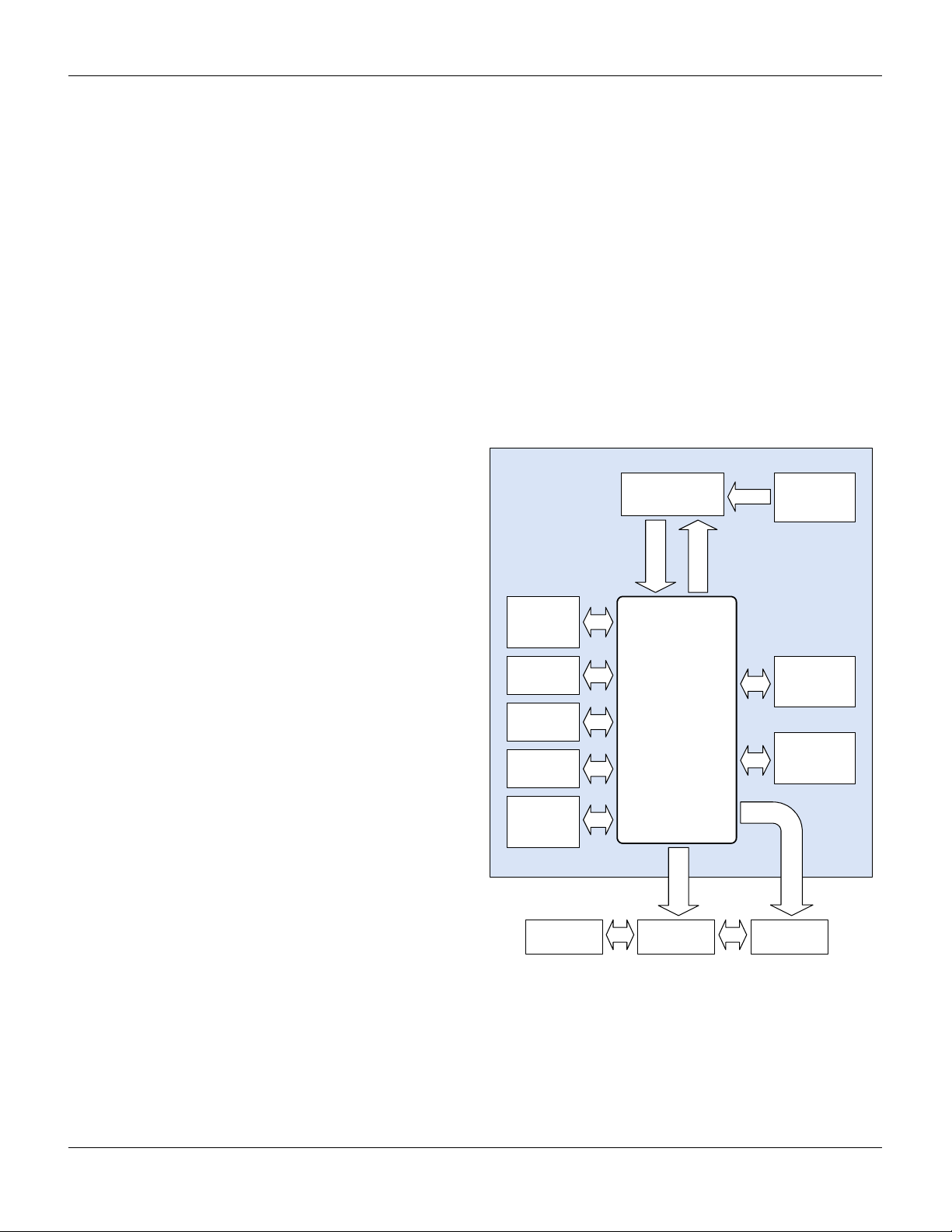

Development Tools

The Cypress MicroSystems PSoC Designer is a Microsoft

Windows-based, integrated development environment for the

Programmable System-on-Chip (PSoC) devices. The PSoC

Designer IDE and application runs on Windows 98, Windows

NT 4.0, Windows 2000, Windows Millennium (Me), or Windows

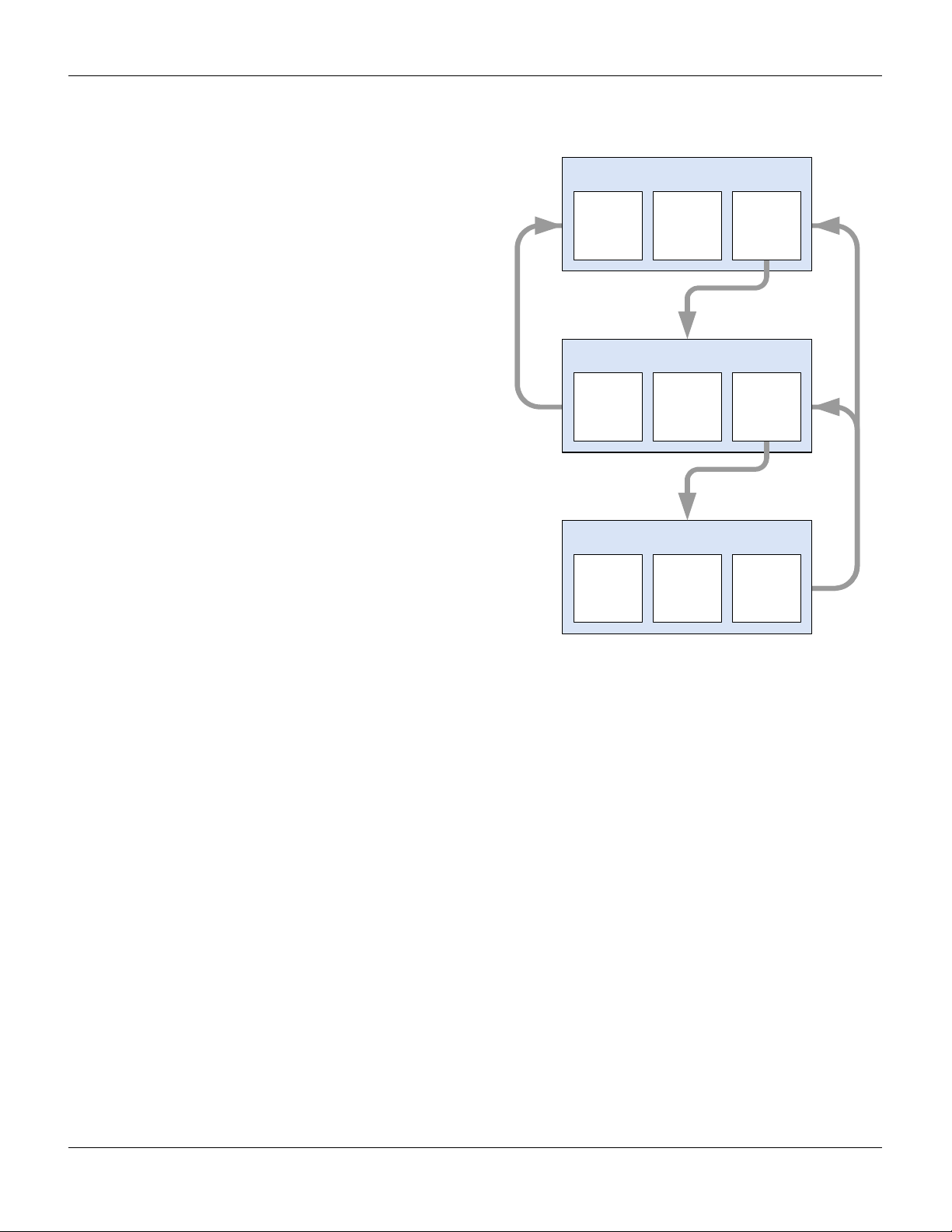

XP. (Reference the PSoC Designer Functional Flow diagram

below.)

PSoC Designer helps the customer to select an operating configuration for the PSoC, write application code that uses the

PSoC, and debug the application. This system provides design

database management by project, an integrated debugger with

In-Circuit Emulator, in-system programming support, and the

CYASM macro assembler for the CPUs.

PSoC Designer also supports a high-level C language compiler

developed specifically for the devices in the family.

TM

PSoC

Designer

Importable

Design

Database

Graphical Designer

Interface

Results

Commands

Context

Sensitive

Help

®

Consultants

Certified PSoC Consultants offer everything from technical

assistance to complete d PSoC d esign s. To contact or be come a

PSoC Consultant, go to the following Cypress support web site:

http://www.cypress.com/support/cypros.cfm.

Technical Support

PSoC application engineers take pride in fast and accurate

response. They can be reached with a 4-hour guaranteed

response at http://www.cypress.com/support/login.cfm.

Application Notes

A long list of application notes will assist you in every aspect of

your design effort. To locate the PSoC application notes, go to

http://www.cypress.com/design/results.cfm.

Device

Database

Application

Database

Project

Database

User

Modules

Library

Emulation

Pod

TM

PSoC

Designer

Core

Engine

In-Circuit

Emulator

Programmer

PSoC Designer Subsystems

PSoC

Configuration

Sheet

Manufacturing

Information

File

Device

June 3, 2004 Document No. 38-12009 Rev. *E 4

[+] Feedback

Page 5

CY8C22x13 Final Data Sheet PSoC™ Overview

PSoC Designer Software Subsystems

Device Editor

The Device Edi tor su bsyst em al lows th e use r to se lect di ffere nt

onboard analog and digital components called user modules

using the PSoC blocks. Examples of user modules are ADCs,

DACs, Amplifiers, and Filters.

The device editor also supports easy development of multiple

configurations and dynamic reconfiguration. Dynamic configuration allows for changing configurations at run time.

PSoC Designer sets up power-on initialization tables for

selected PSoC block configurations and creates source code

for an application framework. The framework contains software

to operate the selected components and, if the project uses

more than one operating configuration, contains routines to

switch between different sets of PSoC block configurations at

run time. PSoC Designer can print out a configuration sheet for

a given project configuration for use during application programming in conj unc tion with the D evice Data S heet . Once the

framework is generated, the user can add application-specific

code to flesh out the fr am ew ork . It’s also possible to change the

selected components and regenerate the framework.

Design Browser

The Design Browser allows users to select and import preconfigured desi g ns into th e u se r’s project. Use rs ca n ea s il y br ow se

a catalog of preconfigured designs to facilitate time-to-design.

Examples provided in the tool s i nclude a 300-baud modem , LIN

Bus master and slave, fan controller, and magnetic card reader.

Application Editor

Debugger

The PSoC Designer Debugger subsystem provides hardware

in-circuit emulation, allowing the designer to test the program in

a physical system while providing an internal view of the PSoC

device. Debugger commands allow the designer to read and

program and read and write data memory, read and write IO

registers, read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The

debugger also allows the designer to create a trace buffer of

registers and memory locations of interest.

Online Help System

The online help system displays online, context-sensitive help

for the user. Designed for procedural and quick reference, each

functional subsystem has its own context-sensitive help. This

system also provides tutorials and links to FAQs and an Online

Support Forum to aid the designer in getting started.

Hardware Tools

In-Circuit Emulator

A low cost, high functionality ICE (In-Circuit Emulator) is available for development support. This hardware has the capability

to program single devices.

The emulator consist s of a bas e unit th at conne ct s to th e PC by

way of the parallel or USB port. The base unit is universal and

will operate with all PSoC devices. Emulation pods for each

device family ar e ava ilabl e sep arate ly. The emulation pod t akes

the place of the PSoC device in the target board and performs

full speed (24 MHz) operation.

In the Application Editor you can edit your C language and

Assembly language source code. You can also assemble, compile, link, and build.

Assembler. The macro assembler allows the assembly code

to be merged seamlessly with C code. The link libraries automatically use abso lut e addre ssing or ca n be co mpil ed in relat ive

mode, and linked with other software modules to get absolute

addressing.

C Language Compiler. A C language compiler is available

that supports Cypress MicroSystems’ PSoC family devices.

Even if you have never worked in the C language before, the

product quickly allows you to create complete C programs for

the PSoC family devices.

The embedded, optimizing C compiler provides all the features

of C tailored to the PSoC architecture. It comes complete with

embedded libraries providing port and bus operations, standard

keypad and display support, and extended math functionality.

PSoC Development Tool Kit

June 3, 2004 Document No. 38-12009 Rev. *E 5

[+] Feedback

Page 6

CY8C22x13 Final Data Sheet PSoC™ Overview

User Modules and the PSoC

Development Process

The development process for the PSoC device differs from that

of a traditional fixed function microprocessor. The configurable

analog and d igital hard ware blocks give the PS oC archite cture

a unique flexibility that p ays d ivide nds in mana gi ng specifi catio n

change during development and by lowering inventory costs.

These configurable resources, called PSoC Blocks, have the

ability to implement a wide variety of user-selectable functions.

Each block has several registers that determine its fu nction and

connectivity to other blocks, multiplexers, buses, and to the IO

pins. Iterative devel op men t cy cl es perm it y ou to adapt the hardware as well as the software. This substantially lowers the risk

of having to select a different part to meet the final design

requirements.

To speed the development process, the PSoC Designer Integrated Development Environment (IDE) provides a library of

pre-built, pre-tested hardware peripheral functions, called “User

Modules.” User modules make selecting and implementing

peripheral devices simple, and come in analog, digital, and

mixed signal varieties. The standard User Module library contains over 50 common peripherals such as ADCs, DACs Timers, Counters, UARTs, and other not-so common peripherals

such as DTMF Generators and Bi-Quad analog filter sections.

Each user module establishes the basic register settings that

implement the selected function. It also provides parameters

that allow you to tailor its precise configuration to your particular

applicati on. For exam ple, a Pulse Width Modula tor User Module configures one or more digital PSoC blocks, one for each 8

bits of resolution. The user module parameters permit you to

establish the pulse width and duty cycle. User modules also

provide tested software to cut your development time. The user

module application programming interface (API) provides highlevel functions to control and respond to hardware events at

run-time. The API als o provides o ptional inte rrupt servic e routines that you can adapt as needed.

The API functions are documented in user module data sheets

that are viewed directly in the PSo C Desi gn er ID E. Th es e data

sheets explain the internal operation of the user module and

provide performance specifications. Each data sheet describes

the use of each user mod ule p ara me ter a nd d oc um ent s the setting of each register controlled by the user module.

The development process starts when you open a new project

and bring up the Devi ce Edi t or, a pictorial environment (GUI) for

configuring the hardware. You pick the user modules you need

for your project and map them onto the PSoC blocks with pointand-click simplicity. Next, you build signal chains by interconnecting user modules to each other and the IO pins. At this

stage, you also configure the clock source connections and

enter parameter values directly or by selecting values from

drop-down menus. When you are ready to test the hardware

configuration or move on to develo ping co de for the proj ect, yo u

perform the “Generate Application” step. This causes PSoC

Designer to generate source code that automatically configures

the device to your speci fic ati on an d pro vi des the hig h-le ve l us er

module API functions.

Device Editor

User

Module

Selection

Placement

and

Parameter

-ization

Source

Code

Generator

Generate

Application

Application Edito r

Project

Manager

Source

Code

Editor

Build

Manager

Build

All

Debugger

Interface

to ICE

Storage

Inspector

User Modules and Development Process Flow Chart

The next step is to write your main program, and any sub-routines using PSoC Designer’s Application Editor subsystem.

The Application Editor includes a Project Manager that allows

you to open the project source code files (including all generated code files) from a hierarchal view. The source code editor

provides syntax coloring and advanced edit features for both C

and assembly language. File search capabilities include simple

string searches and recursive “grep-style” patterns. A single

mouse click invokes the Build Manager. It employs a professional-strength “makefile” system to automatically analyze all

file dependencies and run the compiler and assembler as necessary. Project-level options control optimization strategies

used by the compiler and linker. Syntax errors are displayed in

a console window. Double clicking the error message takes you

directly to the offending line of source code. When all is correct,

the linker builds a ROM file image suitable for programming.

The last step in the devel opm en t proc es s t ak es pla ce insi de the

PSoC Designer’s Debugger subsystem. The Debugger downloads the ROM image to the In-Circuit Emulator (ICE) where it

runs at full speed. Debugger capabilities rival those of systems

costing many times more. In addition to traditional single-step,

run-to-breakpoint and watch-variable features, the Debugger

provides a large trace buffer and allows you define complex

breakpoint event s tha t inc lu de m oni tori ng ad dres s and da t a bu s

values, memory locations and external signals.

Event &

Breakpoint

Manager

June 3, 2004 Document No. 38-12009 Rev. *E 6

[+] Feedback

Page 7

CY8C22x13 Final Data Sheet PSoC™ Overview

Document Conventions

Acronyms Used

The following table lists the acronyms that are used in this document.

Acronym Description

AC alternating current

ADC analog-to-digital converter

API application programming interface

CPU central processing unit

CT continuous time

DAC digital-to-analog converter

DC direct current

EEPROM electrically erasable programmable read-only memory

FSR full scale range

GPIO general purpose IO

IO input/output

IPOR imprecise power on reset

LSb least-significant bit

LVD low voltage detect

MSb most-significant bit

PC program counter

POR power on reset

PPOR precision power on reset

PSoC™ Programmable System-on-Chip

PWM pulse width modulator

RAM random access memory

ROM read only memory

SC switched capacitor

SMP switch mode pump

Units of Measure

A units of measure table is located in the Electrical Specifications section. Table 3-1 on page 13 lists all the abbreviations

used to measure the PSoC devices.

Numeric Naming

Hexidecimal numbers are represented with all letters in uppercase with an appended lowercase ‘h’ (for example, ‘14h’ or

‘3Ah’). Hexi d ec im al nu mber s ma y al so be re p res en t ed by a ‘0x’

prefix, the C coding convention. Binary numbers have an

appended lowercase ‘b’ (e.g., 01010100b’ or ‘01000011b’).

Numbers not indicated by an ‘h’ or ‘b’ are decimal.

Table of Contents

For an in depth discussion and more information on your PSoC

device, obtain the PSoC Mixed Signal Array Technical Refer-

ence Manual. This document encompasses and is organized

into the following chapters and sections.

1. Pin Information .............................. ..... ...... .................... 8

1.1 Pinouts ................................................................... 8

1.1.1 8-Pin Part Pinout ...................................... 8

1.1.2 20-Pin Part Pinout .....................................8

1.1.3 32-Pin Part Pinout .....................................9

2. Register Reference ..................................................... 10

2.1 Register Conventions ...........................................10

2.1.1 Abbreviations Used ..................................10

2.2 Register Mapping Tables ..................................... 10

3. Electrical Specifications ............................................ 13

3.1 Absolute Maximum Ratings ............................... 14

3.2 Operating Temperature ......................................14

3.3 DC Electrical Characteristics ................................ 15

3.3.1 DC Chip-Level Specifications ................... 15

3.3.2 DC General Purpose IO Specifications .... 15

3.3.3 DC Operational Amplifier Specifications ... 16

3.3.4 DC Analog Output Buffer Specifications ... 18

3.3.5 DC Analog Reference Specifications ....... 19

3.3.6 DC Analog PSoC Block Specifications ..... 19

3.3.7 DC POR and LVD Specifications ............. 20

3.3.8 DC Programming Specifications ............... 21

3.4 AC Electrical Characteristics ................................22

3.4.1 AC Chip-Level Specifications ................... 22

3.4.2 AC General Purpose IO Specifications .... 24

3.4.3 AC Operational Amplifier Specifications ... 25

3.4.4 AC Digital Block Specifications ................. 27

3.4.5 AC Analog Output Buffer Specifications ... 28

3.4.6 AC External Clock Specifications ............. 29

3.4.7 AC Programming Specifications ............... 29

3.4.8 AC I2C Specifications ...............................30

4. Packaging Information ............................................... 31

4.1 Packaging Dimensions ......................................... 31

4.2 Thermal Impedances ..........................................34

4.3 Capacitance on Crystal Pins ............................... 34

5. Ordering Information .................................................. 35

5.1 Ordering Code Definitions ...................................35

6. Sales and Company Information ...............................36

6.1 Revision History .................................................. 36

6.2 Copyrights ............................................................ 36

June 3, 2004 Document No. 38-12009 Rev. *E 7

[+] Feedback

Page 8

1. Pin Information

A

A

This chapter describes, lists, and illustrates the CY8C22x13 PSoC device pins and pinout configurations.

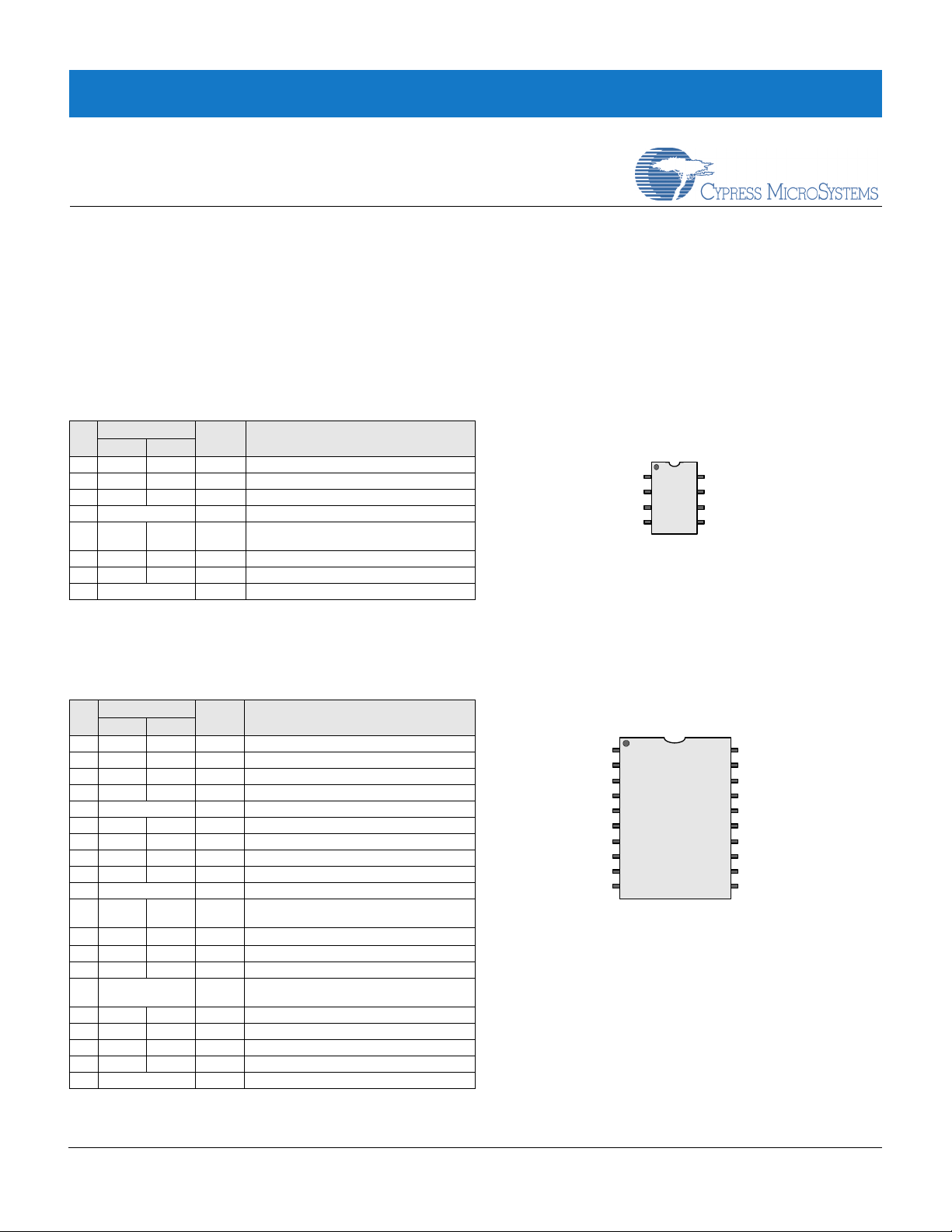

1.1 Pinouts

The CY8C22x13 PSoC device is available in a variety of packages which are listed and illustrated in the following tables. Every port

pin (labeled with a “P”) is capab le of Digital IO. However, Vss, Vdd, SMP, and XRES are not capable of Digital IO.

1.1.1 8-Pin Part Pinout

Table 1-1. 8-Pin Part Pinout (PDIP, SOIC)

Pin

No.

1 IO IO P0[5] Analog column mux input and column output.

2 IO I P0[3] Analog column mux input.

3 IO P1[1] Crystal Input (XTALin), I2C Serial Clock (SCL)

4 Power Vss Ground connection.

5 IO P1[0] Crystal Output (XTALout), I2C Serial Data

6 IO I P0[2] Analog column mux input.

7 IO I P0[4] Analog column mux input.

8 Power Vdd Supply voltage.

LEGEND: A = Analog, I = Input, and O = Output.

Type

Digital Analog

Pin

Name

Description

(SDA)

CY8C22113 8-Pin PSoC Device

AIO, P0[5]

AI, P0[3]

I2C SCL, XTALin, P1[1]

Vss

1

PDIP

2

SOIC

3

4

8

7

6

5

Vdd

P0[4], AI

P0[2], AI

P1[0], XTALout, I2C SD

1.1.2 20-Pin Part Pinout

Table 1-2. 20-Pin Part Pinout (PDIP, SSOP, SOIC)

Pin

No.

1 IO I P0[7] Analog column mux input.

2 IO IO P0[5] Analog column mux input and column output.

3 IO I P0[3] Analog column mux input.

4 IO I P0[1] Analog column mux input.

5 Power Vss Ground connection.

6 IO P1[7] I2C Serial Clock (SCL)

7 IO P1[5] I2C Serial Data (SDA)

8 IO P1[3]

9 IO P1[1] Crystal Input (XTALin), I2C Serial Clock (SCL)

10 Power Vss Ground connection.

11 IO P1[0] Crystal Output (XTALout), I2C Serial Data

12 IO P1[2]

13 IO P1[4] Optional External Clo ck Input (EXTCLK)

14 IO P1[6]

15 Input XRES Active high external reset with internal pull

16 IO I P0[0] Analog column mux input.

17 IO I P0[2] Analog column mux input.

18 IO I P0[4] Analog column mux input.

19 IO I P0[6] Analog column mux input.

20 Power Vdd Supply voltage.

LEGEND: A = Analog, I = Input, and O = Output.

Type

Digital Analog

Pin

Name

Description

(SDA)

down.

CY8C22213 20-Pin PSoC Device

AI, P0[7]

AIO, P0[5]

AI, P0[3]

AI, P0[1]

Vss

I2C SCL, P1[7]

I2C SDA, P1[5]

P1[3]

I2C SCL, XTALin, P1[1]

Vss

10

1

2

3

4

5

6

7

8

9

PDIP

SSOP

SOIC

Vdd

20

P0[6], AI

19

18

P0[4], AI

P0[2], AI

17

P0[0], AI

16

XRES

15

P1[6]

14

P1[4], EXTCLK

13

P1[2]

12

P1[0], XTALout, I2C SD

11

June 2004 Document No. 38-12009 Rev. *E 8

[+] Feedback

Page 9

CY8C22x13 Final Data Sheet 1. Pin Information

I

I

I

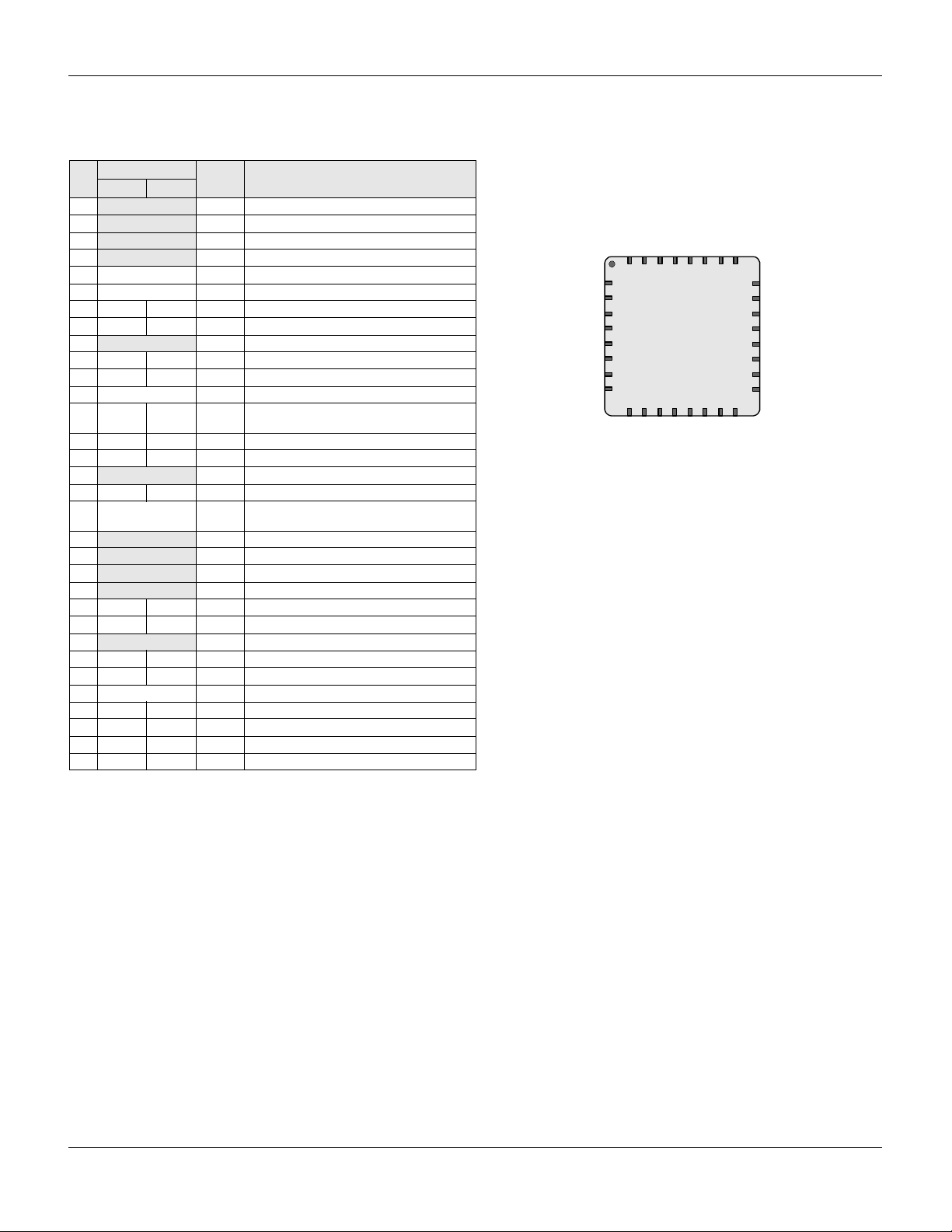

1.1.3 32-Pin Part Pinout

Table 1-3. 32-Pin Part Pinout (MLF*)

Pin

No.

1 NC No connection. Do not use.

2 NC No connection. Do not use.

3 NC No connection. Do not use.

4 NC No connection. Do not use.

5 Power Vss Ground connection.

6 Power Vss Ground connection.

7 IO P1[7] I2C Serial Clock (SCL)

8 IO P1[5] I2C Serial Data (SDA)

9 NC No connection. Do not use.

10 IO P1[3]

11 IO P1[1] Crystal Input (XTALin), I2C Serial Clock (SCL)

12 Power Vss Ground connection.

13 IO P1[0] Crystal Output (XTALout), I2C Serial Data

14 IO P1[2]

15 IO P1[4] Optional External Clock Input (EXTCLK)

16 NC No connection. Do not use.

17 IO P1[6]

18 Input XRES Active high external reset with internal pull

19 NC No connection. Do not use.

20 NC No connection. Do not use.

21 NC No connection. Do not use.

22 NC No connection. Do not use.

23 IO I P0[0] Analog column mux input.

24 IO I P0[2] Analog column mux input.

25 NC No connection. Do not use.

26 IO I P0[4] Analog column mux input.

27 IO I P0[6] Analog column mux input.

28 Power Vdd Supply voltage.

29 IO I P0[7] Analog column mux input.

30 IO IO P0[5] Analog column mux input and column output.

31 IO I P0[3] Analog column mux input.

32 IO I P0[1] Analog column mux input.

Type

Digital Analog

Pin

Name

Description

(SDA)

down.

I2C SCL, P1[7]

2C SDA, P1[5]

CY8C22213 PSoC Device

P0[1], A I

P0[3], A I

P0[5], A IO

P0[7], A I

Vdd

P0[6], A I

NC

NC

NC

NC

Vss

Vss

32313029282726

1

2

3

4

5

6

7

8

(Top View)

9

101112

NC

P1[3]

MLF

Vss

I2C SCL, XTALin, P1[1]

131415

P1[2]

I2C SDA, XT ALo u t, P1[0]

P0[4], A I

NC

25

P0[2], A

24

P0[0], A

23

22

NC

21

NC

20

NC

NC

19

XRES

18

P1[6]

17

16

NC

EXTCLK, P1[4]

LEGEND: A = Analog, I = Input, and O = Output.

* The MLF package has a center pad that must be connected to the same ground

as the Vss pin.

June 3, 2004 Document No. 38-12009 Rev. *E 9

[+] Feedback

Page 10

2. Register Reference

This chapter lists the registers of the CY8C22x13 PSoC device by way of mapping tables, in offset order. For detailed register information, reference the PSoC™ Mixed Signal Array Technical Reference Manual.

2.1 Register Conventions

2.1.1 Abbreviations Used

The register conventions specific to this section are listed in the

following table.

Convention Description

RW Read and write register or bit(s)

R Read register or bit(s)

W Write register or bit(s)

L Logical register or bit(s)

C Clearable register or bit(s)

# Access is bit specific

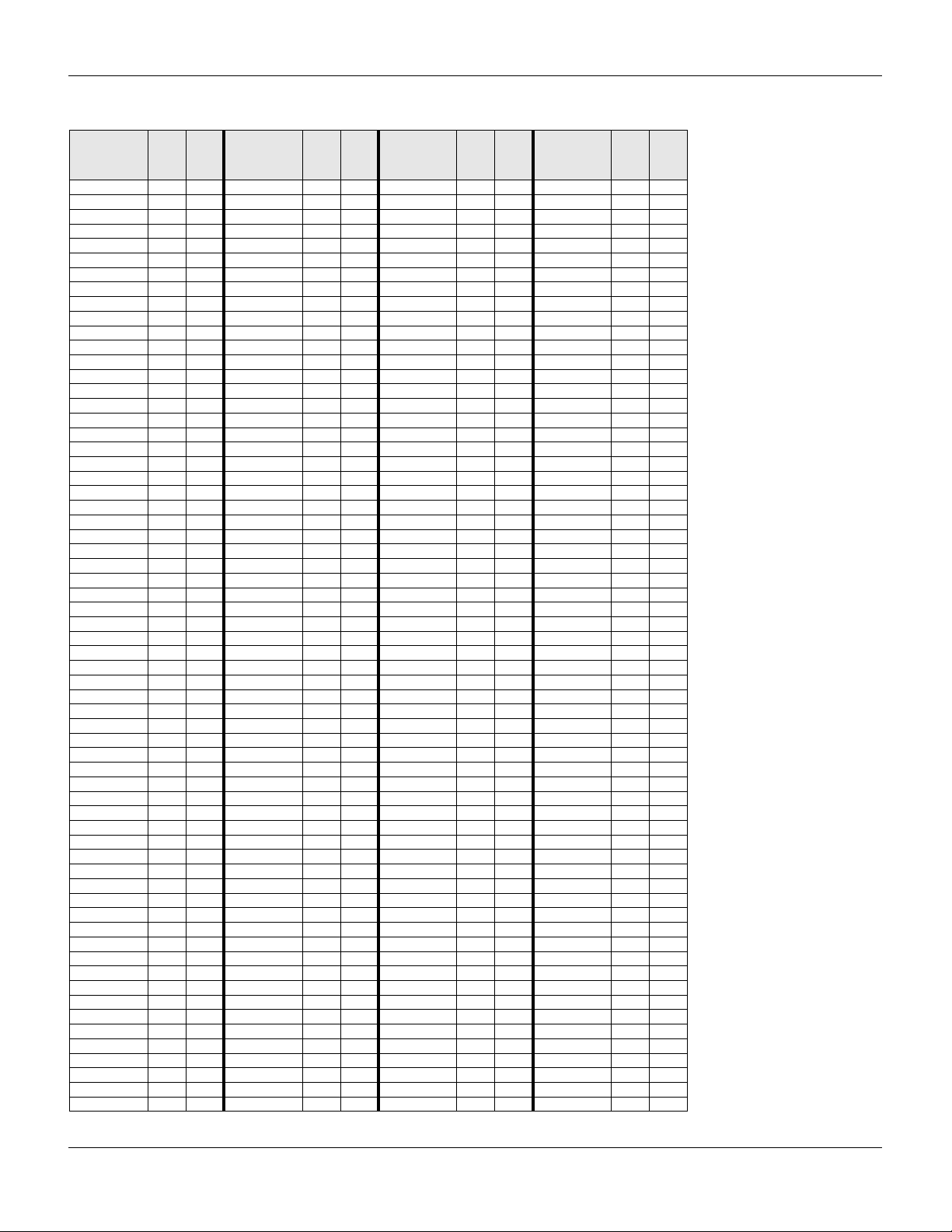

2.2 Register Mapping Tables

The PSoC device has a total register address space of 512

bytes. The register space is also referred to as IO space and is

broken into two parts. The XOI bit in the Flag register determines which bank the user is currently in. When the XOI bit is

set, the user is said to be in the “extended” address space or

the “configuration” registers.

Note In the following register mapping tables, blank fields are

Reserved and should not be accessed.

May 2004 © Cypress MicroSystems, Inc. 2003 — Document No. 38-12009 Rev. *E 10

[+] Feedback

Page 11

CY8C22x13 Final Data Sheet 2. Register Reference

Register Map Bank 0 Table: User Space

Access

Name

PRT0DR 00 RW 40 80 C0

PRT0IE 01 RW 41 81 C1

PRT0GS 02 RW 42 82 C2

PRT0DM2 03 RW 43 83 C3

PRT1DR 04 RW 44 ASD11CR0 84 RW C4

PRT1IE 05 RW 45 ASD11CR1 85 RW C5

PRT1GS 06 RW 46 ASD11CR2 86 RW C6

PRT1DM2 07 RW 47 ASD11CR3 87 RW C7

DBB00DR0 20 # AMX_IN 60 RW A0 INT_MSK0 E0 RW

DBB00DR1 21 W 61 A1 INT_MSK1 E1 RW

DBB00DR2 22 RW 62 A2 INT_VC E2 RC

DBB00CR0 23 # ARF_CR 63 RW A3 RES_WDT E3 W

DBB01DR0 24 # CMP_CR0 64 # A4 DEC_DH E4 RC

DBB01DR1 25 W ASY_CR 65 # A5 DEC_DL E5 RC

DBB01DR2 26 RW CMP_CR1 66 RW A6 DEC_CR0 E6 RW

DBB01CR0 27 # 67 A7 DEC_CR1 E7 RW

DCB02DR0 28 # 68 A8 E8

DCB02DR1 29 W 69 A9 E9

DCB02DR2 2A RW 6A AA EA

DCB02CR0 2B # 6B AB EB

DCB03DR0 2C # 6C AC EC

DCB03DR1 2D W 6D AD ED

DCB03DR2 2E RW 6E AE EE

DCB03CR0 2F # 6F AF EF

Blank fields are Reserved and should not be accessed. # Access is bit specific.

(0,Hex)

Addr

08 48 88 C8

09 49 89 C9

0A 4A 8A CA

0B 4B 8B CB

0C 4C 8C CC

0D 4D 8D CD

0E 4E 8E CE

0F 4F 8F CF

10 50 90 D0

11 51 91 D1

12 52 92 D2

13 53 93 D3

14 54 ASC21CR0 94 RW D4

15 55 ASC21CR1 95 RW D5

16 56 ASC21CR2 96 RW I2C_CFG D6 RW

17 57 ASC21CR3 97 RW I2C_SCR D7 #

18 58 98 I2C_DR D8 RW

19 59 99 I2C_MSCR D9 #

1A 5A 9A INT_CLR0 DA RW

1B 5B 9B INT_CLR1 DB RW

1C 5C 9C DC

1D 5D 9D INT_CLR3 DD RW

1E 5E 9E INT_MSK3 DE RW

1F 5F 9F DF

30 70 RDI0RI B0 RW F0

31 71 RDI0SYN B1 RW F1

32 72 RDI0IS B2 RW F2

33 73 RDI0LT0 B3 RW F3

34 ACB01CR3 74 RW RDIOLT1 B4 RW F4

35 ACB01CR0 75 RW RDI0RO0 B5 RW F5

36 ACB01CR1 76 RW RDI0RO1 B6 RW F6

37 ACB01CR2 77 RW B7 CPU_F F7 RL

38 78 B8 F8

39 79 B9 F9

3A 7A BA FA

3B 7B BB FB

3C 7C BC FC

3D 7D BD FD

3E 7E BE CPU_SCR1 FE #

3F 7F BF CPU_SCR0 FF #

Name

Access

(0,Hex)

Addr

Name

Access

(0,Hex)

Addr

Name

Access

(0,Hex)

Addr

June 3, 2004 Document No. 38-12009 Rev. *E 11

[+] Feedback

Page 12

CY8C22x13 Final Data Sheet 2. Register Reference

Register Map Ba nk 1 Table: Con figuration Space

Access

Name

PRT0DM0 00 RW 40 80 C0

PRT0DM1 01 RW 41 81 C1

PRT0IC0 02 RW 42 82 C2

PRT0IC1 03 RW 43 83 C3

PRT1DM0 04 RW 44 ASD11CR0 84 RW C4

PRT1DM1 05 RW 45 ASD11CR1 85 RW C5

PRT1IC0 06 RW 46 ASD11CR2 86 RW C6

PRT1IC1 07 RW 47 ASD11CR3 87 RW C7

DBB00FN 20 RW CLK_CR0 60 RW A0 OSC_CR0 E0 RW

DBB00IN 21 RW CLK_CR1 61 RW A1 OSC_CR1 E1 RW

DBB00OU 22 RW ABF_CR0 62 RW A2 OSC_CR2 E2 RW

DBB01FN 24 RW 64 A4 VLT_CMP E4 R

DBB01IN 25 RW 65 A5 E5

DBB01OU 26 RW AMD_CR1 66 RW A6 E6

DCB02FN 28 RW 68 A8 IMO_TR E8 W

DCB02IN 29 RW 69 A9 ILO_TR E9 W

DCB02OU 2A RW 6A AA BDG_TR EA RW

DCB03FN 2C RW 6C AC EC

DCB03IN 2D RW 6D AD ED

DCB03OU 2E RW 6E AE EE

Blank fields are Reserved and should not be accessed. # Access is bit specific.

(1,Hex)

Addr

08 48 88 C8

09 49 89 C9

0A 4A 8A CA

0B 4B 8B CB

0C 4C 8C CC

0D 4D 8D CD

0E 4E 8E CE

0F 4F 8F CF

10 50 90 GDI_O_IN D0 RW

11 51 91 GDI_E_IN D1 RW

12 52 92 GDI_O_OU D2 RW

13 53 93 GDI_E_OU D3 RW

14 54 ASC21CR0 94 RW D4

15 55 ASC21CR1 95 RW D5

16 56 ASC21CR2 96 RW D6

17 57 ASC21CR3 97 RW D7

18 58 98 D8

19 59 99 D9

1A 5A 9A DA

1B 5B 9B DB

1C 5C 9C DC

1D 5D 9D OSC_GO_EN DD RW

1E 5E 9E OSC_CR4 DE RW

1F 5F 9F OSC_CR3 DF RW

23 63 A3 VLT_CR E3 RW

27 ALT_CR0 67 RW A7 E7

2B 6B AB ECO_TR EB W

2F 6F AF EF

30 70 RDI0RI B0 RW F0

31 71 RDI0SYN B1 RW F1

32 72 RDI0IS B2 RW F2

33 73 RDI0LT0 B3 RW F3

34 ACB01CR3 74 RW RDIOLT1 B4 RW F4

35 ACB01CR0 75 RW RDI0RO0 B5 RW F5

36 ACB01CR1 76 RW RDI0RO1 B6 RW F6

37 ACB01CR2 77 RW B7 CPU_F F7 RL

38 78 B8 F8

39 79 B9 F9

3A 7A BA FA

3B 7B BB FB

3C 7C BC FC

3D 7D BD FD

3E 7E BE CPU_SCR1 FE #

3F 7F BF CPU_SCR0 FF #

Name

Access

(1,Hex)

Addr

Name

Access

(1,Hex)

Addr

Name

Access

(1,Hex)

Addr

June 3, 2004 Document No. 38-12009 Rev. *E 12

[+] Feedback

Page 13

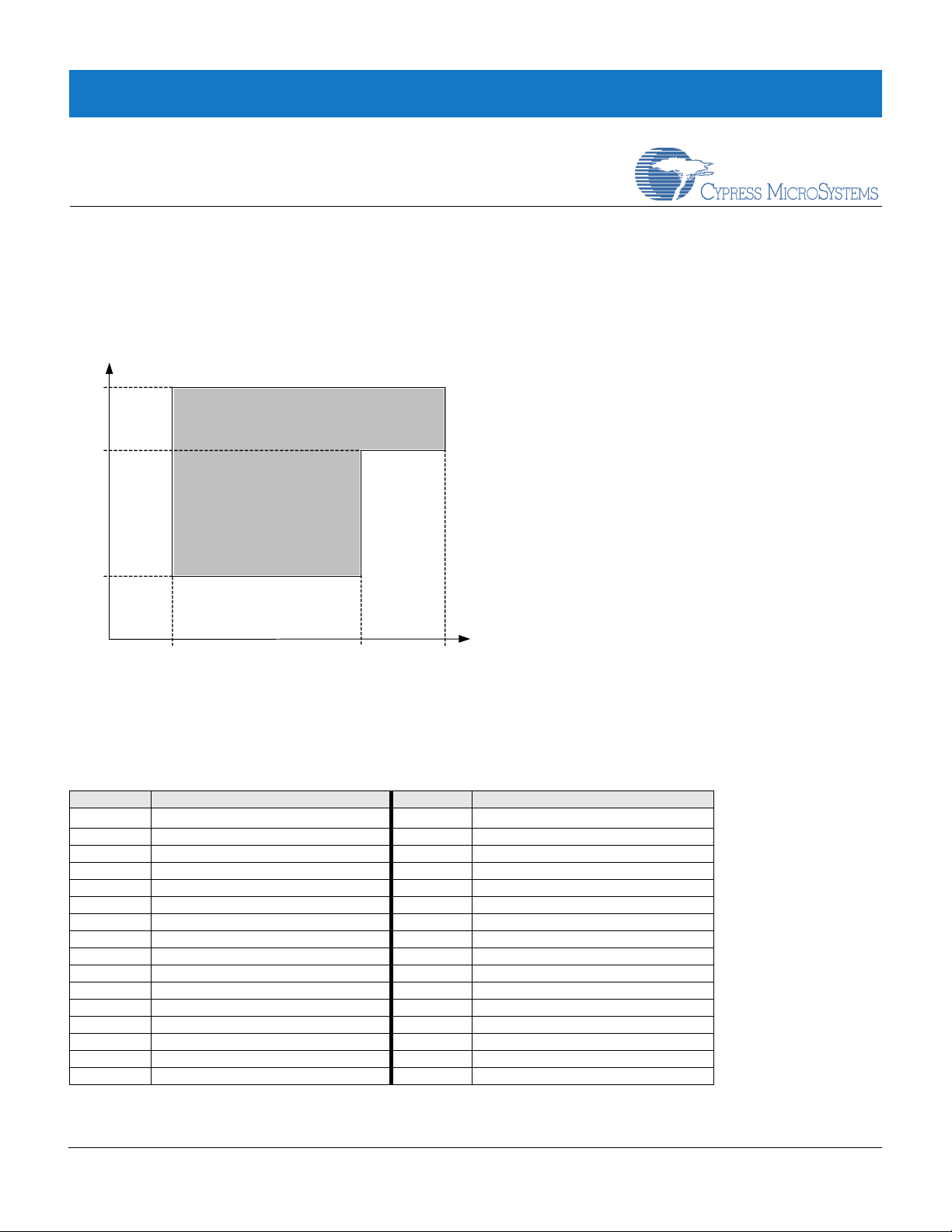

3. Electrical S pecifications

This chapter presents the DC and AC electrical specifications of the CY8C22x13 PSoC device. For the most up to date electrical

specifications, confirm that you have the most recent data sheet by referencing the web at http://www.cypress.com/psoc.

Specifications are v alid for -40

at greater than 12 MHz are valid for -40

5.25

4.75

Vdd Voltage

o

C ≤ TA ≤ 85oC and TJ ≤ 100oC as specified, except where noted. Specifications for devices running

o

C ≤ TA ≤ 70oC and TJ ≤ 82oC.

O

V

p

a

l

e

R

i

d

r

a

e

t

g

i

n

i

o

g

n

3.00

93 kHz 12 MHz 24 MHz

CPU Frequency

Figure 3-1. Voltage versus Operating Frequency

The following table lists the units of measure that are used in this chapter.

Table 3-1: Units of Measure

Symbol Unit of Measur e Symbol Unit of Measure

o

dB decibels mA milli-ampere

fF femto farad ms milli-second

Hz hertz mV milli-volts

KB 1024 bytes nA nano amper e

Kbit 1024 bits ns nanosecond

kHz kilohertz nV nanovolts

kΩ kilohm Ω ohm

MHz megahertz pA pico ampere

MΩ megaohm pF pico farad

µA micro ampere pp peak-to-peak

µF micro farad ppm parts per million

µH micro henry ps picosecond

µs microsecond sps samples per second

µV micro volts σ sigma: one standard deviation

µVrms micro volts root-mean-square V volts

degree Celsius µW micro watts

C

June 2004 Document No. 38-12009 Rev. *E 13

[+] Feedback

Page 14

CY8C22x13 Final Data Sheet 3. Electrical Specifications

3.1 Ab solute Maximum Ratings

Table 3-2. Absolute Maximum Rat ings

Symbol Description Min Typ Max Units Notes

T

STG

T

A

Vdd Supply Voltage on Vdd Relative to Vss -0.5 – +6.0 V

V

IO

– DC Voltage Applied to Tri-state Vss - 0.5 – Vdd + 0.5 V

I

MIO

I

MAIO

– Static Discharge Voltage 2000 – – V

– Latch-up Current – – 200 mA

Storage Temperature -55 – +100

Ambient Temperature with Power Applied -40 – +85

DC Input Voltage Vss - 0.5 – Vdd + 0.5 V

Maximum Current into any Port Pin -25 – +50 mA

Maximum Current into any Port Pin Configured as Analog

Driver

-50 – +50 mA

o

C

o

C

Higher storage temperatures will reduce data

retention time.

3.2 Operating Temperature

Table 3-3. Operating Temperature

Symbol Description Min Typ Max Units Notes

T

A

T

J

Ambient Temperature -40 – +85

Junction Temperature -40 – +100

o

C

o

C

The temperature rise from ambient to junction is

package specific. See “Thermal Impedances”

on page 34. The user must limit the power con-

sumption to comply with this requirement.

June 3, 2004 Document No. 38-12009 Rev. *E 14

[+] Feedback

Page 15

CY8C22x13 Final Data Sheet 3. Electrical Specifications

3.3 DC Electrical Characteristics

3.3.1 DC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

Table 3-4. DC Chip-Level Specifications

Symbol Description Min Typ Max Units Notes

Vdd Supply Voltage 3.00 – 5.25 V

I

DD

I

DD3

I

SB

I

SBH

I

SBXTL

I

SBXTLH

V

REF

a. Standby current includes all functions (POR, LVD, WDT, Sleep Time) needed for reliable system operation. This should be compared with devices tha t ha ve si mi la r fu n ct i o ns

enabled.

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

Supply Current – 5 8 mA

Supply Current – 3.3 6.0 mA

Sleep (Mode) Current with POR, LVD, Sleep Timer, and

a

WDT.

Sleep (Mode) Current with POR, LVD, Sleep Timer, and

WDT at high temperature.

Sleep (Mode) Current with POR, LVD, Sleep Timer, WDT,

and external crystal.

Sleep (Mode) Current with POR, LVD, Sleep Timer, WDT,

and external crystal at high temperature.

Reference Voltage (Bandgap) 1.275 1.3 1.325 V Trimmed for appropriate Vdd.

a

a

a

– 3 6.5 µA Conditions are with internal slow speed oscilla-

– 4 25 µA Conditions are with internal slow speed oscilla-

– 4 7.5 µA Conditions are with properly loaded, 1 µW max,

– 5 26 µA Conditions are with properly loaded, 1 µW max,

Conditions are Vdd = 5.0V, 25 oC, CPU = 3

MHz, 48 MHz disabled. VC1 = 1.5 MHz, VC2 =

93.75 kHz, VC3 = 93.75 kHz.

Condition s are Vdd = 3.3V, TA = 25 oC, CPU = 3

MHz, 48 MHz = Disabled, VC1 = 1.5 MHz, VC2

= 93.75 kHz, VC3 = 93.75 kHz.

tor, Vdd = 3.3V, -40

tor, Vdd = 3.3V, 55

32.768 kHz crystal. Vdd = 3.3V, -40

o

C.

55

32.768 kHz crystal. Vdd = 3.3V, 55

o

C.

85

o

C <= TA <= 55 oC.

o

C < TA <= 85 oC.

o

C <= TA <=

o

C < TA <=

3.3.2 DC General Purpose IO Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

Table 3-5. DC GPIO Specifications

Symbol Description Min Typ Max Units Notes

R

PU

R

PD

V

OH

V

OL

V

IL

V

IH

V

H

I

IL

C

IN

C

OUT

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

Pull up Resistor 4 5.6 8 kΩ

Pull down Resistor 4 5. 6 8 kΩ

High Output Level Vdd - 1.0 – – V IOH = 10 mA, Vdd = 4.75 to 5.25V (80 mA max-

Low Output Level – – 0.75 V IOL = 25 mA, Vdd = 4.75 to 5.25V (1 50 mA

Input Low Level – – 0.8 V Vdd = 3.0 to 5.25

Input High Level 2.1 – V Vdd = 3.0 to 5.25

Input Hysterisis – 60 – mV

Input Leakage (Absolute Value) – 1 – nA Gross tested to 1 µA.

Capacitive Load on Pins as Input – 3.5 10 pF

Capacitive Load on Pins as Output – 3.5 10 pF

imum combined IOH budget)

maximum combined IOL budget)

Package and pin dependent. Temp = 25oC.

Package and pin dependent. Temp = 25oC.

June 3, 2004 Document No. 38-12009 Rev. *E 15

[+] Feedback

Page 16

CY8C22x13 Final Data Sheet 3. Electrical Specifications

3.3.3 DC Operational Amplifier Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

The Operational Amplifier is a component of both the Analog Continuous Time PSoC blocks and the Analog Switched Cap PSoC

blocks. The guaranteed specifications are measured in the Analog Continuous Time PSoC block. Typical parameters apply to 5V at

25°C and are for design guidance only.

T able 3-6. 5V DC Operatio nal A mpli fier Sp eci fica tions

Symbol Description Min Typ Max Units Notes

V

OSOA

TCV

OSOA

I

EBOA

C

INOA

V

CMOA

G

OLOA

V

OHIGHOA

V

OLOWOA

I

SOA

PSRR

OA

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

Input Offset Voltage (absolute value) Low Power

Input Offset Voltage (absolute value) Mid Power

Input Offset Voltage (absolute value) High Power

Average Input Offset Voltage Drift – 7.0 35.0

Input Leakage Current (Port 0 Analog Pins) – 20 – pA Gross tested to 1 µA.

Input Capacitance (Port 0 Analog Pins) – 4.5 9.5 pF

Common Mode Voltage Range

Common Mode Voltage Range (high power or high

opamp bias)

Open Loop Gain

Power = Low

Power = Medium

Power = High

High Output Voltage Swing (worst case internal load)

Power = Low

Power = Medium

Power = High

Low Output Voltage Swing (worst case internal load)

Power = Low

Power = Medium

Power = High

Supply Current (including associated AGND buffer)

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High

Power = High, Opamp Bias = High

Supply Voltage Rejection Ratio 60 – – dB

–1.6

–

–

0.0 – Vdd

0.5 –

60

60

80

Vdd - 0.2

Vdd - 0.2

Vdd - 0.5

–

–

–

–

–

–

–

–

–

1.3

1.2

– – dB Specification is applicable at high power. For all

–

–

–

–

–

–

150

300

600

1200

2400

4600

10

8

7.5

Vdd - 0.5

–

–

–

0.2

0.2

0.5

200

400

800

1600

3200

6400

mV

mV

mV

o

µV/

C

Package and pin dependent. Temp = 25

V The common-mode input voltage range is mea-

V

V

V

V

V

V

µA

µA

µA

µA

µA

µA

sured through an analog output buffer. The

specification includes the limitations imposed

by the characteristics of the analog output

buffer.

other bias modes (except high power, high

opamp bias), minimum is 60 dB.

o

C.

June 3, 2004 Document No. 38-12009 Rev. *E 16

[+] Feedback

Page 17

CY8C22x13 Final Data Sheet 3. Electrical Specifications

Table 3-7. 3.3V DC Operational Amplifier Specifications

Symbol Description Min Typ Max Units Notes

V

OSOA

TCV

I

EBOA

C

INOA

V

CMOA

G

OLOA

V

OHIGHOA

V

OLOWOA

I

SOA

PSRR

OSOA

Input Offset Voltage (absolute value) Low Power

Input Offset Voltage (absolute value) Mid Power

–

–

1.65

1.32

10

8

mV

mV

High Power is 5 Volt Only

Average Input Offset Voltage Drift – 7.0 35.0

µV/

o

C

Input Leakage Current (Port 0 Analog Pins) – 20 – pA Gross tested to 1 µA.

Input Capacitance (Port 0 Analog Pins) – 4.5 9.5 pF

Package and pin dependent. Temp = 25

Common Mode Voltage Range 0.2 – Vdd - 0.2 V The common-mode input voltage range is

measured through an analog output buffer.

The specification includes the limitations

imposed by the characteristics of the analog

output buffer.

Open Loop Gain

Power = Low

Power = Medium

Power = High

60

60

80

– – dB Specification is applicable at high power. For

all other bias modes (except high power, high

opamp bias), minimum is 60 dB.

High Output Voltage Swing (worst case internal load)

Power = Low

Power = Medium

Power = High is 5V only

Vdd - 0.2

Vdd - 0.2

Vdd - 0.2

–

–

–

–

–

–

V

V

V

Low Output Voltage Swing (worst case internal load)

Power = Low

Power = Medium

Power = High

–

–

–

–

–

–

0.2

0.2

0.2

V

V

V

Supply Current (including associated AGND buffer)

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High

Power = High, Opamp Bias = High

Supply Voltage Rejection Ratio 50 – – dB

OA

–

–

–

–

–

–

150

300

600

1200

2400

4600

200

400

800

1600

3200

6400

µA

µA

µA

µA

µA

µA

o

C.

June 3, 2004 Document No. 38-12009 Rev. *E 17

[+] Feedback

Page 18

CY8C22x13 Final Data Sheet 3. Electrical Specifications

3.3.4 DC Analog Output Buffer Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

Table 3-8. 5V DC Analog Output Buffer Specifications

Symbol Description Min Typ Max Units Notes

V

OSOB

TCV

OSOB

V

CMOB

R

OUTOB

V

OHIGHOB

V

OLOWOB

I

SOB

PSRR

OB

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

Input Offset Voltage (Absolute Value) – 3 12 mV

Average Input Offset Vol tage Drift – +6 – µV/°C

Common-Mode Input Voltage Range 0.5 – Vdd - 1.0 V

Output Resistance

Power = Low

Power = High

High Output Voltage Swing (Load = 32 ohms to Vdd/2)

Power = Low

Power = High

Low Output Voltage Swing (Load = 32 ohms to Vdd/2)

Power = Low

Power = High

Supply Current Including Bias Cell (No Load)

Power = Low

Power = High

Supply Voltage Rejection Ratio 60 – – dB

–

–

0.5 x Vdd + 1.1

0.5 x Vdd

–

–

–

–

+ 1.1

1

1

–

–

–

–

1.1

2.6

–

–

–

–

0.5 x Vdd - 1.3

0.5 x Vdd

5.1

8.8

- 1.3

Ω

Ω

V

V

V

V

mA

mA

Table 3-9. 3.3V DC Analog Output Buffer Specifications

Symbol Description Min Typ Max Units Notes

V

OSOB

TCV

V

CMOB

R

OUTOB

V

OHIGHOB

V

OLOWOB

I

SOB

PSRR

OSOB

Input Offset Voltage (Absolute Value) – 3 12 mV

Average Input Offset Voltage Drift – +6 – µV/°C

Common-Mode Input Voltage Range 0.5 - Vdd - 1.0 V

Output Resistance

Power = Low

Power = High

High Output Voltage Swing (Load = 1K ohms to Vdd/2)

Power = Low

Power = High

Low Output Voltage Swing (Load = 1K ohms to Vdd/2)

Power = Low

Power = High

Supply Current Including Bias Cell (No Load)

Power = Low

Power = High

Supply Voltage Rejection Ratio 50 – – dB

OB

–

–

0.5 x Vdd + 1.0

0.5 x Vdd

–

–

–

+ 1.0

1

1

–

–

–

–

0.8

2.0

–

–

–

–

0.5 x Vdd - 1.0

0.5 x Vdd

2.0

4.3

- 1.0

Ω

Ω

V

V

V

V

mA

mA

June 3, 2004 Document No. 38-12009 Rev. *E 18

[+] Feedback

Page 19

CY8C22x13 Final Data Sheet 3. Electrical Specifications

3.3.5 DC Analog Reference Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

The guaranteed specific ations are measure d throug h the Anal og Con tinuou s T im e PSoC block s. The powe r level s for AGND refer to

the power of the Analog Continuous Time PSoC block. The power levels for RefHi and RefLo refer to the Analog Reference Control

register. The limits stated for AGND include the offset error of the AGND buffer local to the Analog Continuous Time PSoC block.

Table 3-10. 5V DC Analog Reference Specifications

Symbol Description Min Typ Max Units

–

a. AGND tolerance includes the offsets of the local buffer in the PSoC block. Bandgap voltage is 1.3V ± 2%.

Table 3-11. 3.3V DC Analog Reference Specifications

Symbol Description Min Typ Max Units

–

a. AGND tolerance includes the offsets of the local buffer in the PSoC block. Bandgap voltage is 1.3V ± 2%

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

AGND = Vdd/2

CT Block Power = High

AGND = Vdd/2

CT Block Power = High

a

Vdd/2 - 0.043 Vdd/2 - 0.025 Vdd/2 + 0.003 V

a

Vdd/2 - 0.037 Vdd/2 - 0.020 Vdd/2 + 0.002 V

3.3.6 DC Analog PSoC Block Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

Table 3-12. DC Analog PSoC Block Specifications

Symbol Description Min Typ Max Units Notes

R

CT

C

SC

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

Resistor Unit Value (Continuous Time) – 12.24 – kΩ

Capacitor Unit Value (Switch Cap) – 80 – fF

June 3, 2004 Document No. 38-12009 Rev. *E 19

[+] Feedback

Page 20

CY8C22x13 Final Data Sheet 3. Electrical Specifications

3.3.7 DC POR and LVD Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

Note The bits PORLEV and VM in the table below refer to bits in the VLT_CR register. See the PSoC Mixed Signal Array Technical

Reference Manual for more information on the VLT_CR register.

Table 3-13. DC POR and LVD Specifications

Symbol Description Min Typ Max Units Notes

V

PPOR0R

V

PPOR1R

V

PPOR2R

V

PPOR0

V

PPOR1

V

PPOR2

V

PH0

V

PH1

V

PH2

V

LVD0

V

LVD1

V

LVD2

V

LVD3

V

LVD4

V

LVD5

V

LVD6

V

LVD7

a. Always greater than 50 mV above PPOR (PORLEV = 00) for f alling supply.

b. Always greater than 50 mV above PPOR (PORLEV = 10) for f alling supply.

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

Vdd Value for PPOR Trip (positive ramp)

PORLEV[1:0] = 00b

PORLEV[1:0] = 01b

PORLEV[1:0] = 10b

–

2.908

4.394

4.548

V

–

V

V

Vdd Value for PPO R Trip (negative ramp)

PORLEV[1:0] = 00b

PORLEV[1:0] = 01b

PORLEV[1:0] = 10b

–

2.816

4.394

4.548

V

–

V

V

PPOR Hysteresis

PORLEV[1:0] = 00b

PORLEV[1:0] = 01b

PORLEV[1:0] = 10b

–

–

–

92

0

0

–

–

–

mV

mV

mV

Vdd Value for LVD Trip

VM[2:0] = 000b

VM[2:0] = 001b

VM[2:0] = 010b

VM[2:0] = 011b

VM[2:0] = 100b

VM[2:0] = 101b

VM[2:0] = 110b

VM[2:0] = 111b

2.863

2.963

3.070

3.920

4.393

4.550

4.632

4.718

2.921

3.023

3.133

4.00

4.483

4.643

4.727

4.814

2.979

3.083

3.196

4.080

4.573

4.736

4.822

4.910

a

V

V

V

V

V

V

b

V

V

V

June 3, 2004 Document No. 38-12009 Rev. *E 20

[+] Feedback

Page 21

CY8C22x13 Final Data Sheet 3. Electrical Specifications

3.3.8 DC Programming Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

Table 3-14. DC Programming Specifications

Symbol Description Min Typ Max Units Notes

I

DDP

V

ILP

V

IHP

I

ILP

I

IHP

V

OLV

V

OHV

Flash

ENPB

Flash

ENT

Flash

DR

a. A maximum of 36 x 50,000 block endurance cycles is allowed. This may be balanced between operations on 36x1 blocks of 50,000 maximum cycles each, 36x2 blocks of

25,000 maximum cycles each, or 36x4 blocks of 12,500 maximum cycles each (and so forth to limit the total number of cycles to 36x50,000 and that no single block ever

sees more than 50,000 cycles).

For the full industrial range, the user must employ a temperature sensor user module (FlashTemp) and feed the result to the temperature argument before writing. Refer to

the Flash APIs Application Note AN2015 at http://www.cypress.com under Application Notes for more information.

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

Supply Current During Programming or Verify – 5 25 mA

Input Low Voltage During Programming or Verify – – 0.8 V

Input High Voltage During Programming or Verify 2.2 – – V

Input Current when Applying Vilp to P1[0] or P1[1] During

Programming or Verify

Input Current when Applying Vihp to P1[0] or P1[1] During

Programming or Verify

Output Low Voltage During Programming or Verify – – Vss + 0.75 V

Output High Voltage During Programming or Verify Vdd - 1.0 – Vdd V

Flash Endurance (per block) 50,000 – – – Erase/write cycles per block.

Flash Endurance (total)

Flash Data Retention 10 – – Years

a

– – 0.2 mA Driving internal pull-down resistor.

– – 1.5 mA Driving internal pull-down resistor.

1,800,000 – – – Erase/write cycles.

June 3, 2004 Document No. 38-12009 Rev. *E 21

[+] Feedback

Page 22

CY8C22x13 Final Data Sheet 3. Electrical Specifications

E

3.4 AC Electrical Characteristics

3.4.1 AC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

Table 3-15. AC Chip-Level Specifications

Symbol Description Min Typ Max Units Notes

F

IMO

F

CPU1

F

CPU2

F

48M

F

24M

F

32K1

F

32K2

F

PLL

Jitter24M2 24 MHz Period Jitter (PLL) – – 600 ps

T

PLLSLEW

T

PLLSLEWS-

LOW

T

OS

T

OSACC

Jitter32k 32 kHz Period Jitter – 100 ns

T

XRST

DC24M 24 MHz Duty Cycle 40 50 60 %

Step24M 24 MHz Trim Step Size – 50 – kHz

Fout48M 48 MHz Output Frequency 46.8 48.0

Jitter24M1 24 MHz Period Jitter (IMO) – 600 ps

F

MAX

T

RAMP

a. 4.75V < Vdd < 5.25V.

b. Accuracy derived from Internal Main Oscillator with appropriate trim for Vdd range.

c. 3.0V < Vdd < 3.6V. See Application Note AN2012 “Adjusting PSoC Microcontroller Trims for Dual Voltage-Range Operation” for information on trimming for operation at 3.3V.

d. See the individual user module data sheets for information on maximum frequencies for user modules.

e. 3.0V < 5.25V.

f. The crystal oscillator frequency is within 100 ppm of its final value by the end of the T

32.768 kHz crystal. 3.0V ≤ Vdd ≤ 5.5V, -40

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

Internal Main Oscillator Frequency 23.4 24

CPU Frequency (5V Nomi nal) 0.93 24

CPU Frequency (3.3V Nominal) 0.93 12

Digital PSoC Block Frequency 0 48

Digital PSoC Block Frequency 0 24

Internal Low Speed Oscillator Frequency 15 32 64 kHz

External Crystal Oscillator – 32.768 – kHz

24.6

24.6

12.3

49.2

24.6

a

MHz Trimmed. Utilizing factory trim values.

a,b

MHz

b,c

MHz

a,b,d

MHz Refer to the AC Digital Block Specifications

b,e,d

MHz

below.

Accuracy is capacitor and crystal dependent.

50% duty cycle.

PLL Frequency – 23.986 – MHz

PLL Lock Time 0.5 – 10 ms

PLL Lock Time for Low Gain Setting 0.5 – 50 ms

External Crystal Oscillator Startup to 1% – 1700

External Crystal Oscillator Startup to 100 ppm – 2800

External Reset Pulse Width 10 – – µs

Maximum frequency of signal on row input or row output. – – 12.3 MHz

Supply Ramp Time 0 – – µs

o

C ≤ TA ≤ 85 oC.

osacc

2620

3800

49.2

period. Correct operation assumes a properly loaded 1 uW maximum drive level

ms

f

ms

a,c

MHz Trimmed. Utilizing factory trim values.

Is a multiple (x732) of crystal frequency.

PLL

nable

F

PLL

Gain

PLL

T

PLLSLEW

0

24 MHz

Figure 3-2. PLL Lock Timing Diagram

June 3, 2004 Document No. 38-12009 Rev. *E 22

[+] Feedback

Page 23

CY8C22x13 Final Data Sheet 3. Electrical Specifications

E

S

F

F

PLL

nable

T

PLLSLEWLOW

F

PLL

24 MHz

PLL

Gain

1

Figure 3-3. PLL Lock for Low Gain Setting Timing Diagram

32K

elect

T

OS

F

32K2

Figure 3-4. External Crystal Oscillator Startup Timing Diagram

Jitter24M1

24M

Figure 3-5. 24 MHz Period Jitter (IMO) Timing Diagram

32 kHz

Jitter32k

32K2

Figure 3-6. 32 kHz Period Jitter (ECO) Timing Diagram

June 3, 2004 Document No. 38-12009 Rev. *E 23

[+] Feedback

Page 24

CY8C22x13 Final Data Sheet 3. Electrical Specifications

G

3.4.2 AC General Purpose IO Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

Table 3-16. AC GPIO Specifications

Symbol Description Min Typ Max Units Notes

F

GPIO

TRiseF Rise Time, Normal Strong Mode, Cload = 50 pF 3 – 18 ns Vdd = 4.5 to 5.25V, 10% - 90%

TFallF Fall Time, Normal Strong Mode, Cload = 50 pF 2 – 18 ns Vdd = 4.5 to 5.25V, 10% - 90%

TRiseS Rise Time, Slow Strong Mode, Cload = 50 pF 10 27 – ns Vdd = 3 to 5.25V, 10% - 90%

TFallS Fall Time, Slow Strong Mode, Cload = 50 pF 10 22 – ns Vdd = 3 to 5.25V, 10% - 90%

PIO

Pin

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

GPIO Operating Frequenc y 0 – 12 MHz

90%

10%

TRiseF

TRiseS

Figure 3-7. GPIO Timing Diagram

TFallF

TFallS

June 3, 2004 Document No. 38-12009 Rev. *E 24

[+] Feedback

Page 25

CY8C22x13 Final Data Sheet 3. Electrical Specifications

3.4.3 AC Operational Amplifie r Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

Note Settling times, slew rates, and gain bandwidth are based on the Analog Continuous Time PSoC block.

Table 3-17. 5V AC Operational Amplifier Specifications

Symbol Description Min Typ Max Units Notes

T

ROA

T

SOA

SR

ROA

SR

FOA

BW

OA

E

NOA

≤ 85°C, or 3.0V to 3.6V and -40°C ≤ TA ≤ 85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and

A

Rising Settling Time from 80% of ∆V to 0.1% of ∆V (10 pF

load, Unity Gain)

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High

Power = High, Opamp Bias = High

Falling Settling Time from 20% of ∆V to 0.1% of ∆V (10 pF

load, Unity Gain)

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High

Power = High, Opamp Bias = High

Rising Slew Rate (20% to 80%)(10 pF load, Unity Gain)

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High

Power = High, Opamp Bias = High

Falling Slew Rate (20% to 80%)(10 pF load, Unity Gain)

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High

Power = High, Opamp Bias = High

Gain Bandwidth Product

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High

Power = High, Opamp Bias = High

Noise at 1 kHz (Power = Medium, Opamp Bias = High) – 200 – nV/rt-Hz

–

–

–

–

–

–

–

–

–

–

–

–

0.15

1.7

6.5

0.01

0.5

4.0

0.75

3.1

5.4

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

3.9

0.72

0.62

5.9

0.92

0.72

µs

µs

µs

µs

µs

µs

µs

µs

µs

µs

µs

µs

V/

V/

V/

V/

V/

V/

V/

V/

V/

V/

V/

V/

MHz

MHz

MHz

MHz

MHz

MHz

Specification maximums for low power and

high opamp bias, medium power, and

medium power and high opamp bias levels

are between low and high power levels.

Specification maximums for low power and

high opamp bias, medium power, and

medium power and high opamp bias levels

are between low and high power levels.

Specification minimums for low power and

high opamp bias, medium power, and

µs

medium power and high opamp bias levels

µs

are between low and high power levels.

µs

µs

µs

µs

Specification minimums for low power and

high opamp bias, medium power, and

µs

medium power and high opamp bias levels

µs

are between low and high power levels.

µs

µs

µs

µs

Specification minimums for low power and

high opamp bias, medium power, and

medium power and high opamp bias levels

are between low and high power levels.

June 3, 2004 Document No. 38-12009 Rev. *E 25

[+] Feedback

Page 26

CY8C22x13 Final Data Sheet 3. Electrical Specifications

Table 3-18. 3.3V AC Operational Amplifier Specifications

Symbol Description Min Typ Max Units Notes

T

T

SR

SR

BW

E

ROA

SOA

NOA

ROA

FOA

OA

Rising Settling Time from 80% of ∆V to 0.1% of ∆V (10 pF

load, Unity Gain)

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High (3.3 V olt High Bias Operation not support ed)

Power = High, Opamp Bias = High (3.3 Volt High Power,

High Opamp Bias not supported)

–

–

3.92

–

–

–

–

–

–

–

–

0.72

–

–

µs

µs

µs

µs

µs

µs

Falling Settling Time from 20% of ∆V to 0.1% of ∆V (10 pF

load, Unity Gain)

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High (3.3 V olt High Bias Operation not support ed)

–

–

–

–

–

–

–

–

5.41

0.72

–

µs

µs

µs

µs

µs

Power = High, Opamp Bias = High (3.3 Volt High Power,

High Opamp Bias not supported)

–

–

–

µs

Rising Slew Rate (20% to 80%)(10 pF load, Unity Gain)

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High (3.3 V olt High Bias Operation not support ed)

0.31

2.7

–

–

–

–

–

V/

V/

V/

V/

V/

Power = High, Opamp Bias = High (3.3 Volt High Power,

High Opamp Bias not supported)

–

–

–

V/

Falling Slew Rate (20% to 80%)(10 pF load, Unity Gain)

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High (3.3 V olt High Bias Operation not support ed)

Power = High, Opamp Bias = High (3.3 Volt High Power,

High Opamp Bias not supported)

0.24

1.8

–

–

–

–

–

–

–

–

V/

V/

V/

V/

V/

V/

Gain Bandwidth Product

Power = Low

Power = Low, Opamp Bias = High

Power = Medium

Power = Medium, Opamp Bias = High

Power = High (3.3 V olt High Bias Operation not support ed)

Power = High, Opamp Bias = High

(3.3 Volt High Power,

High Opamp Bias not supported)

0.67

2.8

–

–

–

MHz

MHz

MHz

–

–

–

–

–

MHz

MHz

MHz

Noise at 1 kHz (Power = Medium, Opamp Bias = High) – 200 – nV/rt-Hz

Specification maximums for low power and

high opamp bias, medium power, and

medium power and high opamp bias levels

are between low and high power levels.

Specification maximums for low power and

high opamp bias, medium power, and

medium power and high opamp bias levels

are between low and high power levels.

Specification minimums for low power and

high opamp bias, medium power, and

µs

medium power and high opamp bias levels

µs

are between low and high power levels.

µs

µs

µs

µs

Specification minimums for low power and

high opamp bias, medium power, and

µs

medium power and high opamp bias levels

µs

are between low and high power levels.

µs

µs

µs

µs

Specification minimums for low power and

high opamp bias, medium power, and

medium power and high opamp bias levels

are between low and high power levels.

June 3, 2004 Document No. 38-12009 Rev. *E 26

[+] Feedback

Page 27

CY8C22x13 Final Data Sheet 3. Electrical Specifications

3.4.4 AC Digital Block Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40°C ≤ T

are for design guidance only or unless otherwise specified.

Table 3-19. AC Digital Block Specifications

Function Description Min Typ Max Units Notes

Timer Capture Pulse Width