Page 1

September 2008

Silicon Errata for the CY8C21x34 PSoC

®

Mixed Signal Arrays

CY8C21x34

This document describes the errata for the PSoC® Mixed Signal Arrays CY8C21x34. Details include errata trigger

conditions, scope of impact, available workarounds, and silicon revision applicability. Compare this document to the

device’s data sheet for a complete functional description.

Contact your local Cypress Sales Representative if you have questions.

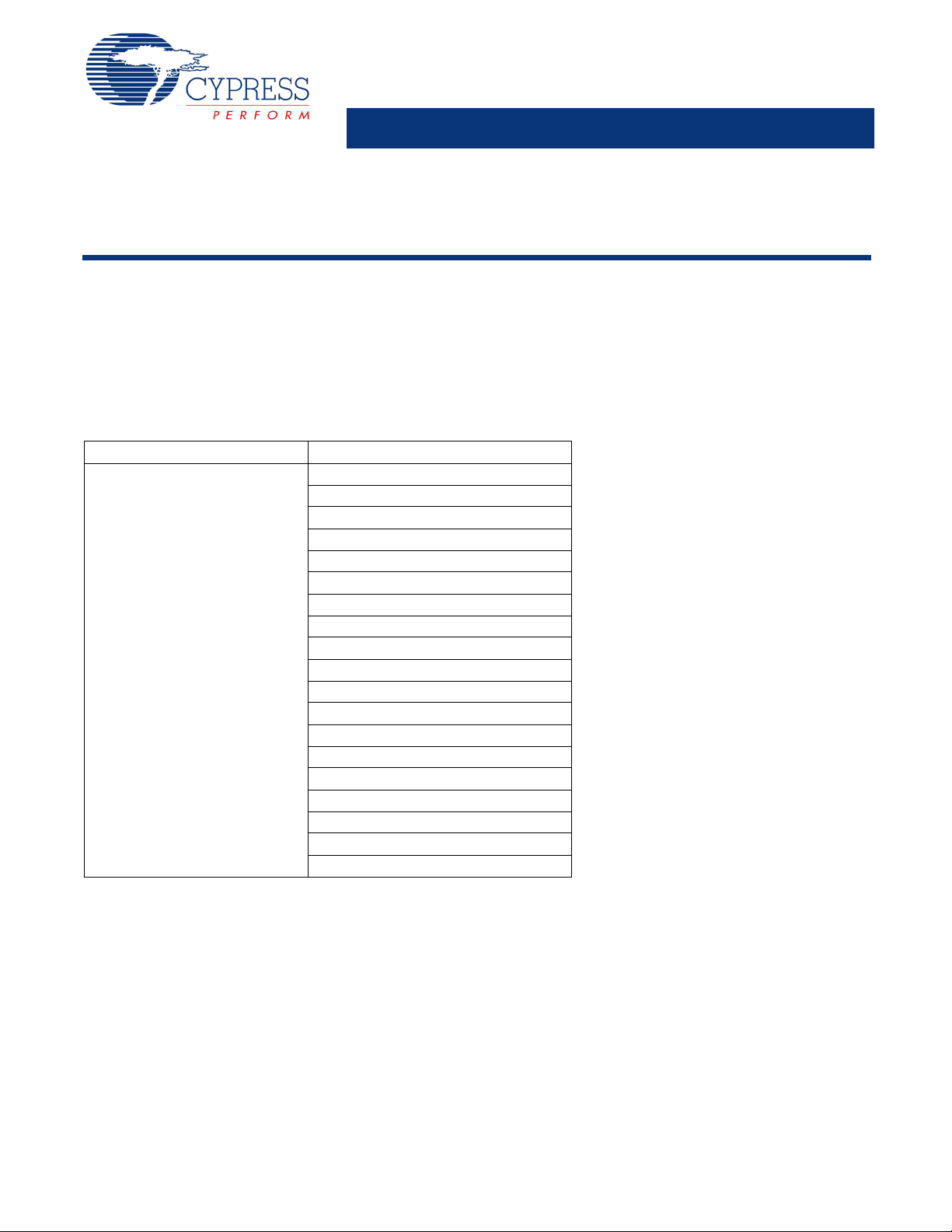

Part Numbers Affected

Part Number Ordering Information

CY8C21x34 CY8C21234-24SXI

CY8C21234-24SXIT

CY8C21334-24PVXI

CY8C21334-24PVXIT

CY8C21534-24PVXI

CY8C21534-24PVXIT

CY8C21434-24LFXI

CY8C21434-24LFXIT

CY8C21434-24LKXI

CY8C21434-24LKXIT

CY8C21634-24LFXI

CY8C21634-24LFXIT

CY8C21434-24LTXI

CY8C21434-24LTXIT

CY8C21434-24LQXI

CY8C21434-24LQXIT

CY8C21634-24LTXI

CY8C21634-24LTXIT

CY8C21001-24PVXI

CY8C21x34 Qualification Status

Product Status: Production

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134 • 408.943.2600

September 11, 2008 Document No. 001-48789 Rev. ** 1

[+] Feedback

Page 2

CY8C21x34

Errata Document

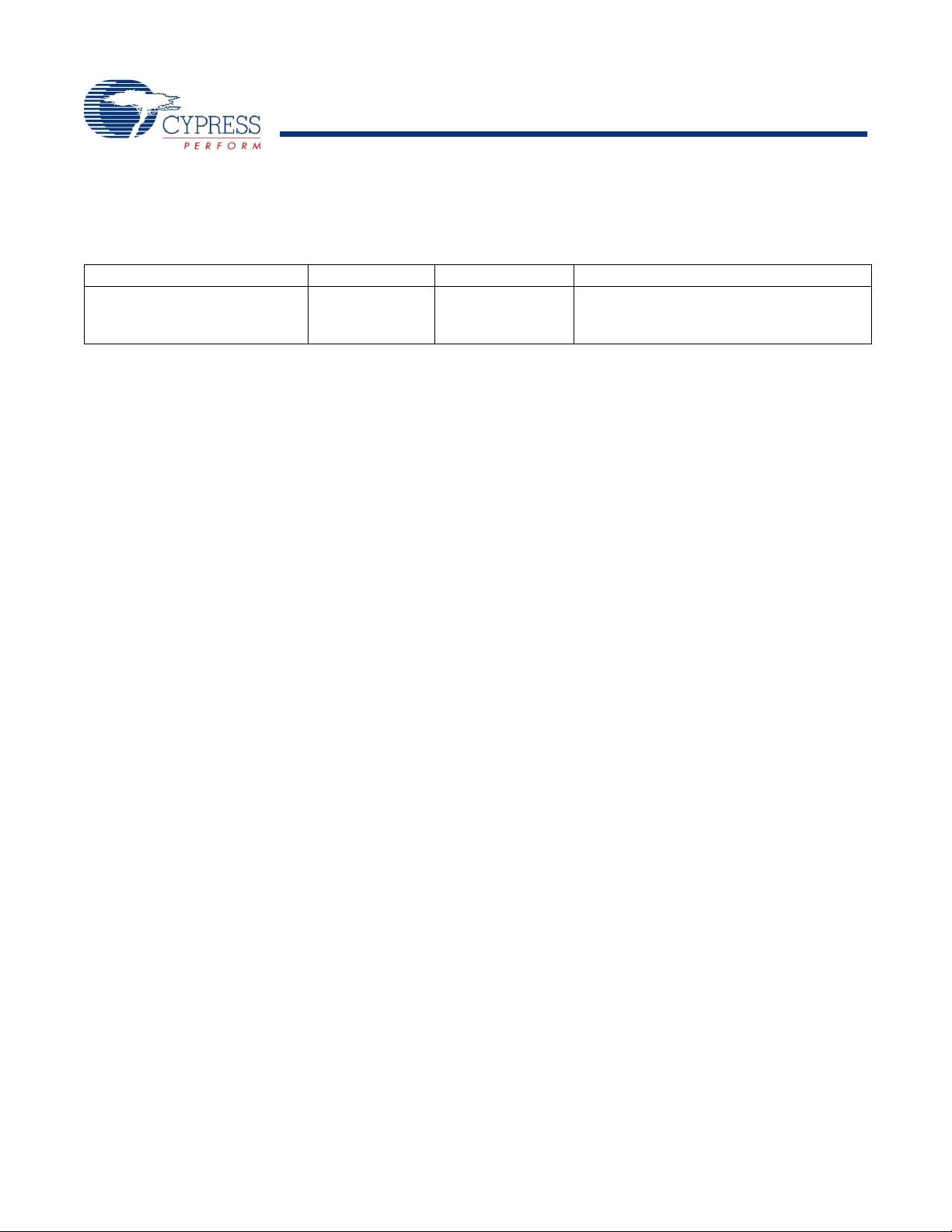

CY8C21x34 Errata Summary

The following table defines the errata applicability to available CY8C21x34 family devices. An "X" indicates that the

errata pertains to the selected device.

Note Errata items, in the table below, are hyperlinked. Click on any item entry to jump to its description.

Items Part Number Silicon Revision Fix Status

[1]. Internal Main Oscillator

CY8C21x34 A

(IMO) Tolerance Deviation at

Temperature Extremes

1. Internal Main Oscillator (IMO) Tolerance Deviation at Temperature Extremes

■ PROBLEM DEFINITION

Asynchronous Digital Communications Interfaces may fail framing beyond 0 to 70°C. This problem does not

affect end-product usage between 0 and 70°C.

■ PARAMETERS AFFECTED

The IMO frequency tolerance. The worst case deviation when operated below 0°C and above +70°C and within

the upper and lower datasheet temperature range is ±5%.

■ TRIGGER CONDITION(S)

The asynchronous Rx/Tx clock source IMO frequency tolerance may deviate beyond the data sheet limit of

±2.5% when operated beyond the temperature range of 0 to +70°C.

■ SCOPE OF IMPACT

This problem may affect UART, IrDA, and FSK implementations.

■ WORKAROUND

Implement a quartz crystal stabilized clock source on at least one end of the asynchronous digital

communications interface.

■ FIX STATUS

The cause of this problem and its solution has been identified. Silicon fix is planned to correct the deficiency

in silicon.

Silicon fix is planned.

References

[1] Document # 38-12025, CY8C21234/CY8C21334/CY8C21434/CY8C21534/CY8C21634 PSoC® Mixed-Signal

Array Final Data Sheet

September 11, 2008 Document No. 001-48789 Rev. ** 2

[+] Feedback

Page 3

CY8C21x34

Errata Document

Document History Page

Document Title: Silicon Errata for the CY8C21x34 PSoC® Mixed Signal Arrays

Document Number: 001-48789

Rev. ECN No.

Date

** 2567361 09/16/08 XSG/AESA IMO tolerance deviation

Issue

Orig. of

Change Description of Change

PSoC is a registered trademark of Cypress Semiconductor Corp. EZ-Color, PSoC Designer, and PSoC Ex\press are trademarks of Cypress

Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor

198 Champion Court

San Jose, CA 95134-1709

Phone: 408-943-2600

Fax: 408-943-4730

http://www.cypress.com

© Cypress Semiconductor Corporation, 2008. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes

no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights.

Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express

written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or

failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the

manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection

(United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, nontransferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating

custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement.

Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written

permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED

TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without

further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein.

Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result

in significant injury to the user. The inclusion of Cypress’ product in a life-support systems application implies that the manufacturer assumes all risk of such use and

in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

September 11, 2008 Document No. 001-48789 Rev. ** 3

[+] Feedback

Loading...

Loading...