Page 1

November 7, 2008

Errata Document for PSoC® CY8C20x46, CY8C20x66

CY8C20x46, CY8C20x66

This document describes the errata for the PSoC® CY8C20x46 and CY8C20x66. Details include errata trigger

conditions, scope of impact, available workarounds, and silicon revision applicability . Compare this document to the

device’s data sheet for a complete functional description. This document is not available on the external Cypress

web site.

Contact your local Cypress Sales Representative if you have questions.

CY8C20x46 and CY8C20x66 Errata Summary

The following Errata items apply to the CY8C20x46 and CY8C20x66 data she et 001 -12696.

1. Latch-up susceptibility when maximum I/O sink current exceeded

n PROBLEM DEFINITION

P1[3], P1[6], and P1[7] pins are susceptible to latch-up when the I/O sink curr ent excee ds 25 m A per pin on

these pins.

n PARAMETERS AFFECTED

LU – Latch-up Current. Per JESD78A, the maximum allowable latch-up current per pin is 100 mA. Cypress

internal specification is 200 mA latch-up current limit.

n TRIGGER CONDITION(S)

Latch-up occurs when both of the following two conditions are met:

A. The offending I/O is externally connected to a voltage higher than the I/O high state, ca using a current to

flow into the pin that exceeds 25 mA

B. A Port1 I/O adjacent (P1[1], P1[4] and P1[5] respectively) to the offending I/O is connected to a voltage

lower than the I/O low state, causing a signal that drops below Vss (signal undershoot), causing a current

greater than 200 mA to flow out of the pin

n SCOPE OF IMPACT

The trigger conditions outlined above exceed the maximum ratings specified in the CY8C20x46 and

CY8C20x66 datasheet 001-12696.

n WORKAROUND

Add a series resistor >300Ω to P1[3], P1[6], and P1[7] pins to restrict current to within latch-up limits.

n FIX STATUS

This issue will be corrected in the next new silicon revision.

The following Errata item applies only to the CY8C20666 and CY8C20066 parts on the Capsense Data sheet.

2. Does not meet USB 2.0 specification for D+ and D- rise/f all matching when supply voltage is under 3.3V

n PROBLEM DEFINITION

Rising to falling rate matching of the USB D+ and D- lines has a corner case at lower supply voltages, such

as those under 3.3V.

n PARAMETERS AFFECTED

Rising to falling rate matching of the USB data lines.

n TRIGGER CONDITION(S)

Operating the VCC supply voltage at the low end of the chip’s specification (under 3.3V) may cause a

missmatch in the rising to falling rate.

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134 • 408.943.2600

November 7, 2008 Document No. 001-32940 Re v . *C 1

[+] Feedback

Page 2

CY8C20x46, CY8C20x66

Errata Document

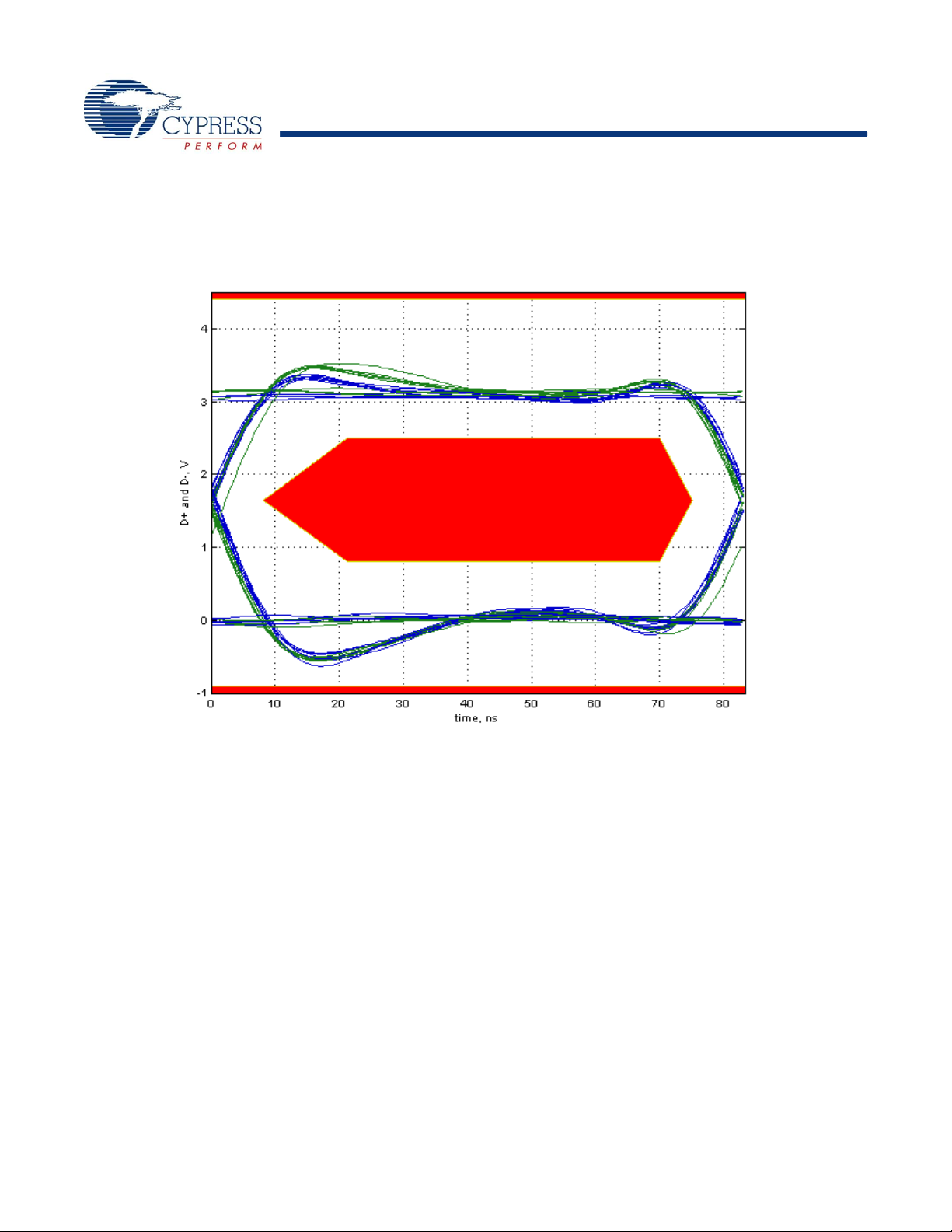

n SCOPE OF IMPACT

This condition does not affect USB communicat ions but could cause corner case issues with USB lines’

rise/fall matching specification. Signal integrity tests were run using the Cypress development kit for the part

and excellent eye was observed with supply voltage of 3.15V.

Figure 1. Eye Diagram

n WORKAROUND

Avoid the trigger condition by using lower tolerance voltage regulators.

n FIX STATUS

This issue will be corrected in the next new silicon revision.

November 7, 2008 Document No. 001-32940 Rev. *C 2

[+] Feedback

Page 3

CY8C20x46, CY8C20x66

Errata Document

Document History Page

Document Title: Errata Document for: PSoC® CY8C20x46, CY8C20x66

Document Number: 001-32940

REV. ECN NO. Issue Date

** 1506743 Sept. 25, 2007 SFV First release.

*A 1685823 Oct. 30, 2007 SFVTMP3 Minor formatting changes.

*B 2507644 See ECN MNU/AESA Update the errata for revB krypton Silicon. Added part number

*C 2603185 See ECN DTB Update the errata for revB3 krypton Silicon. Added Latch-up and

Orig. of

Change Description of Change

CY8C20x46. Updated document to current Errata template.

USB errata. Removed Higher Sleep Current errata and On Chip

Debugger errata as solved by new silicon.

Cypress Semiconductor

198 Champion Court

San Jose, CA 95134-1709

Phone: 408-943-2600

Fax: 408-943-4730

http://www.cypress.com

© Cypress Semiconductor Corporation, 2008. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes

no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights.

Cypress products are not warranted nor intended to be used for medical, life supp ort, life saving, criti cal control or safety a pplications, unless pursuant to an expre ss

written agreement with Cypress. Furthermore, Cypress does not authorize it s product s for use as crit ical component s in life- support systems where a malfu nction or

failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the

manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) a nd is protected by and subject to worldwide patent protection

(United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, nontransferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating

custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement.

Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written

permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED

TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without

further notice to the materials described herein. Cypress does not assume any liability ari sing out of the applicati on or use of a ny produ ct or circuit d escribed he rein.

Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result

in significant injury to the user. The inclusion of Cypress’ produ ct in a life-support systems appli cation imp lies that the manufacture r assumes all risk of such use and

in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

November 7, 2008 Document No. 001-32940 Rev. *C 3

[+] Feedback

Loading...

Loading...