Page 1

C66011

CY7C66013

CY7C66113

CY7C66013

CY7C66113

Full-Speed USB (12 Mbps) Peripheral

Controller with Integrated Hub

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

Document #: 38-08024 Rev. ** Revised March 26, 2002

Page 2

CY7C66013

CY7C66113

TABLE OF CONTENTS

1.0 FEATURES .....................................................................................................................................6

2.0 FUNCTIONAL OVERVIEW ...... ...................... ........................ ............................................. ............7

3.0 PIN CONFIGURATIONS ..................................... .. .. .. ................................. .....................................9

4.0 PRODUCT SUMMARY TABLES ..................................................................................................10

4.1 Pin Assignments . .............. .. ............. .. .............. .. ............. .. .. .............. .. ............. .. .........................10

4.2 I/O Registe r Su mmary ......... ............. .. .............. .. ............. .. ............. ... ............. ............. .. .. ............10

4.3 Instruction Set Summary ............................................................................................................12

5.0 PROGRAMM I N G M OD E L ..... .. .. .............. .. ............. .. ............. ... ............. .. ............. ... ............. .. .......13

5.1 14-Bit Program Counter (PC) ......................................................................................................13

5.1.1 Program Memory Organization .........................................................................................................14

5.2 8-Bit Accumu la tor (A) ............ .. .. .............. .. ............. .. .............. .. .. ............. ... ............. .. ..................14

5.3 8-Bit Temporary Register (X) ......................................................................................................14

5.4 8-Bit Program Stack Pointer (PSP) ............................................................................................15

5.4.1 Data Memory Organization ................................................................................................................15

5.5 8-Bit Data Stack Pointer (DSP) ................................................................................................... 15

5.6 Address Mo d e s ............... ... ............. .. ............. ... ............. .. ............. .. .............. .. ............. ................16

5.6.1 Data (Immediate) .................................................................................................................................16

5.6.2 Direct ...................................................................................................................................................16

5.6.3 Indexed ................................................................................................................................................16

6.0 CLOCKING ....................................................................................................................................16

7.0 RESET ................................................................. ..........................................................................17

7.1 Power-On Reset (POR) ................................................................................................................17

7.2 Watch Dog Reset (WDR) .............................................................................................................17

8.0 SUSPEND MODE ............................ .. .. .. .................................. .. .. .. .. .. ............................................18

9.0 GENERAL-PURPOSE I/O (GPIO) PORTS ...................................................................................18

9.1 GPIO Configuration Port .............................................................................................................19

9.2 GPIO Interrupt Enable Ports .......................................................................................................20

10.0 DAC PORT ..................................................................................................................................21

10.1 DAC Isink Registers ..................................................................................................................21

10.2 DAC Port Interrupts ...................................................................................................................22

11.0 12-BIT FREE-RUNNING TIMER ............................................................ .. ............................. ......22

11.1 Timer (LSB ) ........ ... .. ............. .. .............. .. ............. .. ............. ... ............. .. ............. ... ......................22

11.2 Timer (MSB) .... ............. .. .............. .. ............. .. ... ............. .. ............. .. .............. .. .............................22

12.0 I

13.0 I

2

C AND HAPI CONFIGURATION REGISTER ..........................................................................23

2

C COMPATIB L E CO N T R O L L ER ......... ............. .. ............. ... ............. .. ............. ... ............. .. .. .....24

14.0 HARDWARE ASSISTED PARALLEL INTERFACE (HAPI) .................................... .. .. .. .............25

15.0 PROCESSOR STATUS AND CONTROL REGISTER ................................. .. ............................26

16.0 INTERRUPTS ..............................................................................................................................27

16.1 Interrup t V e c to r s ........... ... ............. .. ............. ... ............. .. ............. .. .............. .. .............................28

16.2 Interrup t L a te n c y ..................... ... ............. .. ............. ... ............. .. .. .............. .. ............. ..................30

16.3 USB Bus Reset Interrupt ...........................................................................................................30

16.4 Timer Inter rupt .......... .. ............. ... ............. .. ............. ... ............. .. ............. ... ............. .. ..................30

Document #: 38-08024 Rev. ** Page 2 of 53

Page 3

CY7C66013

CY7C66113

16.5 USB Endpoint Interrup ts ....... .............. .. ............. .. ............. ... ............. .. .. .............. .. ....................30

16.6 USB Hub Int e rr u p t ................... ... ............. .. ............. ... .. ............. .. .............. .. ............. .. ................30

16.7 DAC Interrupt .............................................................................................................................31

16.8 GPIO/HAPI Interrupt ..................................................................................................................31

16.9 I

17.0 USB OVERV I E W .......... .. .............. .. ............. .. ... ............. .. ............. .. .............. .. ............. .. . .............32

17.1 USB Serial Interface Engine (SIE) ..................................................................... .......................32

17.2 USB Enume ra tion ....... .. .............. .. .. ............. ... ............. .. ............. .. .............. .. ............. .. . .............32

18.0 USB HUB ....................................................................................................................................33

18.1 Connecting/Disconnecting a USB Device ...............................................................................33

18.2 Enablin g/ D is a b l in g a U SB D e vice .......... .. ............. ... ............. .. ............. ... ............. ............. .. .....34

18.3 Hub Downstream Ports Status and Control ............................................................................34

18.4 Downstream Port Suspend and Resume ................................................................................35

18.5 USB Upstream Port Status and Control ..................................................................................36

19.0 USB SERIAL IN T E R F A CE ENGINE OP ER A T ION ..................... .. .............. .. ............. .. ..............37

19.1 USB Device Addresses .............................................................................................................37

19.2 USB Device Endpoints ..............................................................................................................37

19.3 USB Contr o l E n dp o i n t M o d e Re g i sters ... .. .............. .. ............. .. .............. .. ............. .. ............. ...38

19.4 USB Non-Control Endpoint Mode Registers ............................... ............................................38

19.5 USB Endpoint Counter Registers ............................................................................................39

19.6 Endpoint Mode/Count Registers Update and Locking Mechanism ....................... ...............39

20.0 USB MODE T A B L E S .............. .............. .. ............. .. ............. ... ............. .. ............. ... ............. .........41

2

C Interrupt ........................ ............. .. .............. .. ............. .. ............. ... ............. .. ............. . .............31

21.0 SAMPLE SC H E M ATIC ............. ... ............. .. ............. ... ............. ............. .. .............. .. ....................45

22.0 ABSOLUTE M A X I M U M R A T INGS ......... ............. .. .. .............. .. ............. .. .............. .. ............. .. .....46

23.0 ELECTRICAL CHARACTERISTICS ............................................... ............................................46

24.0 SWITCHING CHARACTERISTICS ............................................... .. ................................ ............48

25.0 ORDERIN G IN F O RMATION .............. ... ............. .. .. ............. ... ............. .. ............. ... ............. .. .......50

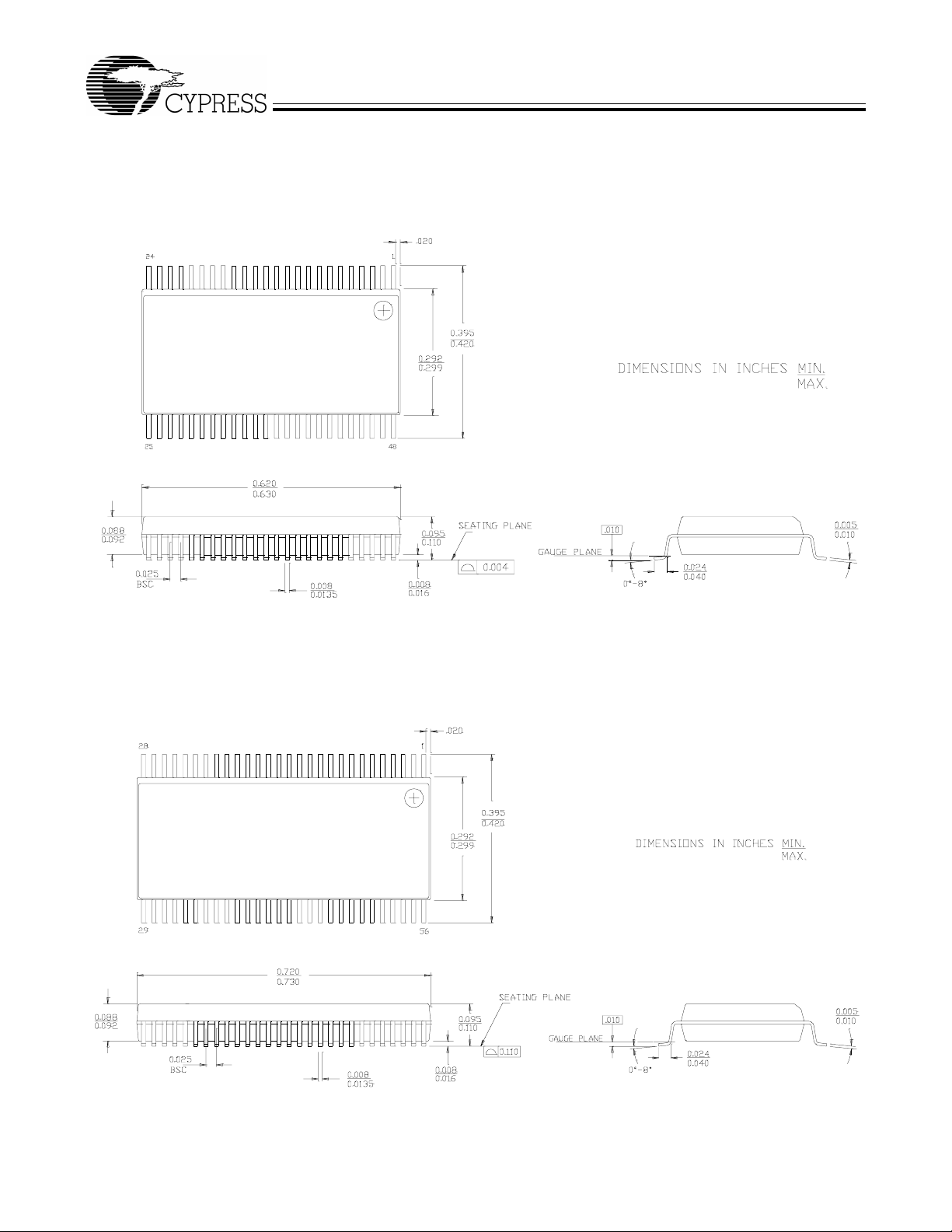

26.0 PACKAGE DIAGRAMS ................................. ................................. ............................................51

Document #: 38-08024 Rev. ** Page 3 of 53

Page 4

CY7C66013

CY7C66113

LIST OF FIGURES

Figure 5-1. Program Memory Space with Interrupt Vector Table ..................................................14

Figure 6-1. Clock Oscillator On-Chip Circuit ...................................................................................16

Figure 7-1. Watch Dog Reset (WDR) .......................................... ............................................ ..........17

Figure 9-1. Block Diagram of a GPIO Pin ........................................................................................ 18

Figure 9-2. Port 0 Data 0x00 (read/write) ................................... .......................... .. ..........................19

Figure 9-3. Port 1 Data 0x01 (read/write) ................................... .......................... .. ..........................19

Figure 9-4. Port 2 Data 0x02 (read/write) ................................... .......................... .. ..........................19

Figure 9-5. Port 3 Data 0x03 (read/write) ................................... .......................... .. ..........................19

Figure 9-6. GPIO Configuration Register 0x08 (read/write) ............................................... ............20

Figure 9-7. Port 0 Interrupt Enable 0x04 (write only) ............... ..................... ...................... ............20

Figure 9-8. Port 1 Interrupt Enable 0x05 (write only) ............... ..................... ...................... ............20

Figure 9-9. Port 2 Interrupt Enable 0x06 (write only) ............... ..................... ...................... ............20

Figure 9-10. Port 3 Interrupt Enable 0x07 (write only) .................. ........................ ........................ ..20

Figure 10-1. Block Diagram of a DAC Pin ........................................................................................ 21

Figure 10-2. DAC Port Data 0x30 (read/write) .................................................................................21

Figure 10-3. DAC Port Isink 0x38 to 0x3F (write only) ............................................... .....................21

Figure 10-4. DAC Port Interrupt Enable 0x31 (write only) ................... ........................ .. .................22

Figure 10-5. DAC Port Interrupt Polarity 0x32 (write only) ....................... .....................................22

Figure 11-1. Timer Register 0x24 (read only) .............. .. ....................... ........................ .. .................22

Figure 11-2. Timer Register 0x25 (read only) .............. .. ....................... ........................ .. .................22

Figure 11-3. Timer Block Diagram .................................................................................................... 23

Figure 12-1. HAPI/I

Figure 13-1. I

Figure 13-2. I

Figure 15-1. Processor Status and Control Register 0xFF ............................................................26

Figure 16-1. Global Interrupt Enable Register 0x20 (read/write) ...................................................27

Figure 16-2. USB Endpoint Interrupt Enable Register 0x21 (read/write) .............................. ........27

Figure 16-3. Interrupt Controller Functional Diagram ....................................................................29

Figure 16-4. Interrupt Vector Register 0x23 (read only) .................................................................30

Figure 16-5. GPIO Interrupt Structure ..............................................................................................31

Figure 18-1. Hub Ports Connect Status 0x48 (read/write), 1 = Connect, 0 = Disconnect ............33

Figure 18-2. Hub Ports Speed 0x4A (read/write), 1 = Low-Speed, 0 = Full-Speed ....................... 34

Figure 18-3. Hub Ports Enable Register 0x49 (read/write), 1 = Enabled, 0 = Disabled ............... .34

Figure 18-4. Hub Downstream Ports Control Register 0x4B (read/write) ................ .....................34

Figure 18-5. Hub Ports Force Low Register (read/write) 0x51, 1 = Force Low, 0 = No Force .....35

Figure 18-6. Hub Ports SE0 Status Register 0x4F (read only), 1 = SE0, 0 = Non-SE0 .................35

Figure 18-7. Hub Ports Data Register 0x50 (read only), 1 = (D+ > D–), 0 = (D+ < D–) .............. ....35

Figure 18-8. Hub Ports Suspend Register 0x4D (read/write), 1 = Port is Selectivel y Su spended36

Figure 18-9. Hub Ports Resume Status Register 0x4E (read only), 1 = Port is in Resume State 36

Figure 18-10. USB Status and Control Register 0x1F (read/write) .......................................... ......36

Figure 19-1. USB Device Address Registers 0x10, 0x40 (read/write) ............................ ...............37

Figure 19-2. USB Device Endpoint Zero Mode Registers 0x12 and 0x42, (read/write) ...............38

Figure 19-3. USB Non-Control Device Endpoint Mode Registers 0x14, 0x16, 0x44, (read/wr it e) 39

Figure 19-4. USB Endpoint Counter Registers 0x11, 0x13, 0x15, 0x41, 0x43 (read/w rite) ..........39

Figure 19-5. Token/Data Packet Flow Diagram ................ .......................... .. ...................................40

Figure 21-1. Sample Schematic ........................................................................................................45

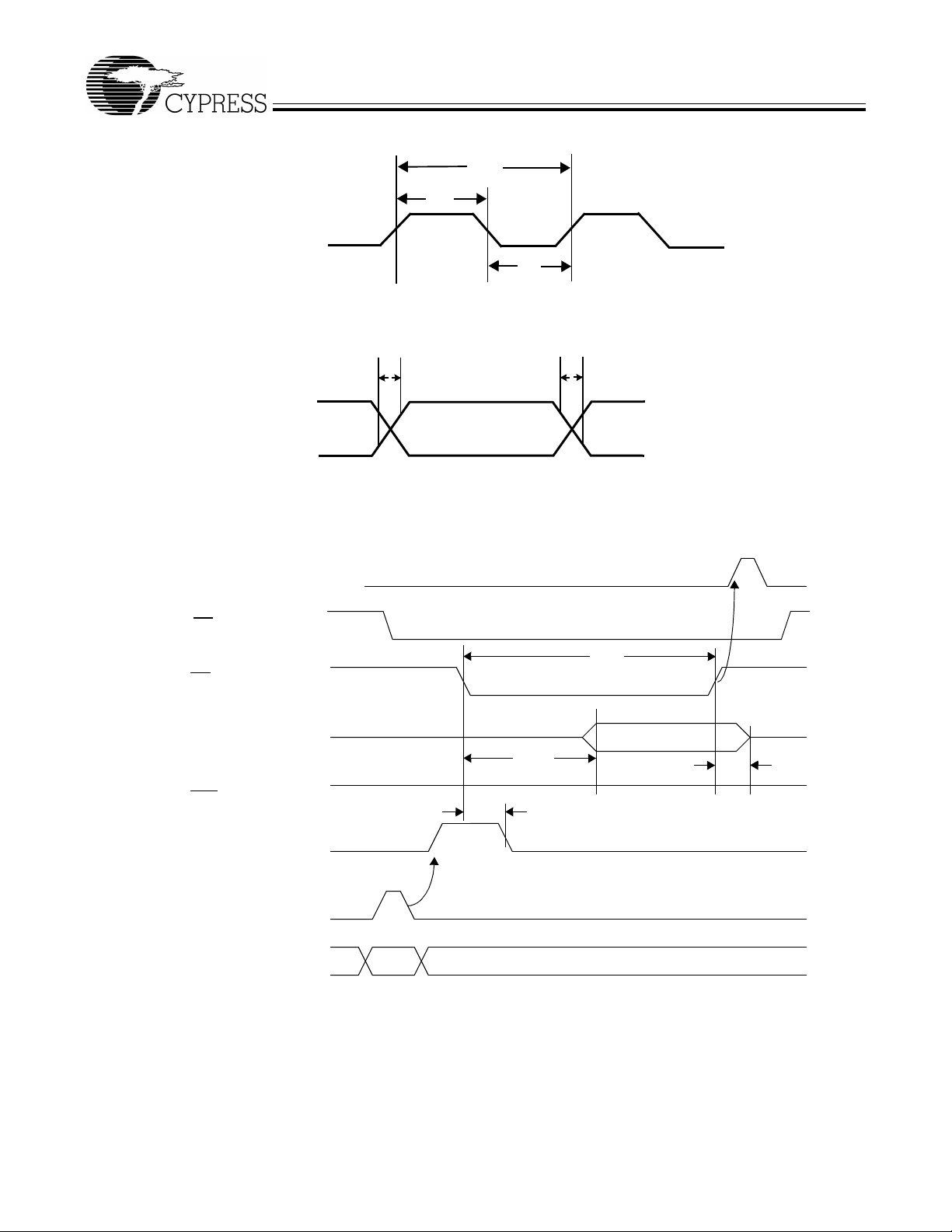

Figure 24-1. Clock Timing ................................................................................................................. 49

Figure 24-2. USB Data Signal Timing ............................................................................................... 49

Figure 24-3. HAPI Read by External Interface from USB Microcontroller ....................................49

Figure 24-4. HAPI Write by External Device to USB Microcontroller ............................................ 50

2

2

2

C Configuration Register 0x09 (read/write) ........................................... ........23

C Data Register 0x29 (separate read/write registers) .............................................24

C Status and Control Register 0x28 (read/write) ....................................................24

Document #: 38-08024 Rev. ** Page 4 of 53

Page 5

CY7C66013

CY7C66113

LIST OF TABLES

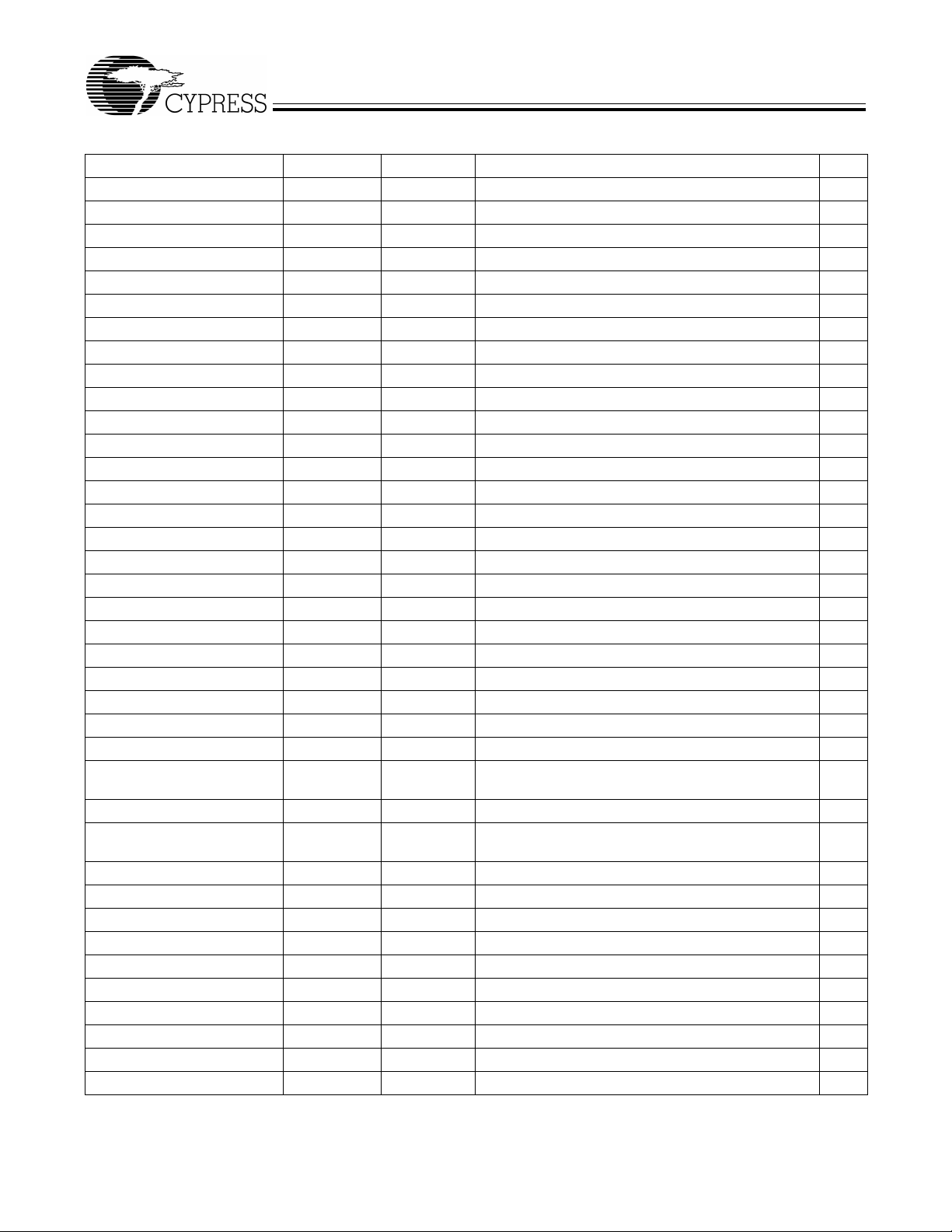

Table 4-1. Pin Assignments ..............................................................................................................10

Table 4-2. I/O Register Summary ......................................................................................................10

Table 4-3. Instruction Set Summary .................................................................................................12

Table 9-1. Port Configurations .........................................................................................................19

Table 12-1. HAPI Port Configuration ................................................................................................23

Table 12-2. I

Table 13-1. I

Table 14-1. Port 2 Pin and HAPI Configuration Bit Definitions .....................................................26

Table 16-1. Interrupt Vector Assignments .......................................................................................29

Table 18-1. Control Bit Definition for Downstream Ports ..............................................................35

Table 18-2. Control Bit Definition for Upstream Port .....................................................................37

Table 19-1. Memory Allocation for Endpoints ......................... .......................................................38

Table 20-1. USB Register Mode Encoding ......................................................................................41

Table 20-2. Decode table for Table 20-3: “Details of Modes for Differing Traffic Conditions” ...42

Table 20-3. Details of Modes for Differing Traffic Conditions .......................................................43

2

C Port Config u r a tio n . ... ............. .. ............. ... ............. .. ............. ... .. ............. .. ............. ...23

2

C Status and Co n t ro l Register Bit Def in itions ................ .. ............. .. ... ............. .. .......24

Document #: 38-08024 Rev. ** Page 5 of 53

Page 6

CY7C66013

CY7C66113

1.0 Features

• Full-speed USB Peripheral Microcontroller with an integrated USB hub

—Well suited for USB compound devices such as a keyboard hub function

• 8-bit USB Optimized Microcontroller

—Harvard architecture

—6-MHz external clock source

—12-MHz internal CPU clock

—48-MHz internal Hub clock

• Internal memory

—256 bytes of RAM

—8 KB of PROM (CY7C66013, CY7C66113)

• Integrated Master/Slave I2C-Compatible Controller (100 kHz) enabled through General-Purpose I/O (GPIO) pins

• Hardware Assisted Parallel Interface (HAPI) for data transfer to external devices

• I/O ports

—Three GPIO ports (Port 0 to 2) capable of sinking 8 mA per pin (typical)

—An additional GPIO port (Port 3) capable of sinking 12 mA per pin (typical) for high current requirements: LEDs

—Higher current drive achievable by connecting multiple GPIO pins together to drive a common output

—Each GPIO port can be configured as inputs w ith internal pull-ups or open drain outputs or traditional CMO S outputs

—A Digital to Analog Conversion (DAC) port with programma ble current sink outputs is available on the CY7C66 113

device

—Maskable interrupts on all I/O pins

• 12-bit free-running timer with one microsecond clock ticks

• Watch Dog Timer (WDT)

• Internal Power-On Reset (POR)

• USB Specification Compliance

—Conforms to USB Specification, Version 1.1

—Conforms to USB HID Specification, Version 1.1

—Supports one or two device addresses with up to 5 user configured endpoints

Up to two 8-byte control endpoints

Up to four 8-byte data endpoints

Up to two 32-byte data endpoints

—Integrated USB transceivers

—Supports 4 Downstream USB ports

—GPIO pins can provide individual power control outputs for each Downstream USB port

—GPIO pins can provide individual port over current inputs for each Downstream USB port

• Improved output drivers to reduce EMI

• Operating voltage from 4.0V to 5.5V DC

• Operating temperature from 0 to 70 degrees Celsius

• CY7C66013 available in 48-pin PDIP (-PC) or 48-pin SSOP (-PVC) packages

• CY7C66113 available in 56-pin SSOP (-PVC) packages

• Industry-standard programmer support

Document #: 38-08024 Rev. ** Page 6 of 53

Page 7

CY7C66013

CY7C66113

2.0 Functional Overview

The CY7C66013 and CY 7C66 113 are compound devices with a ful l-s pee d U SB mi cro co ntro lle r in c om bin ati on with a USB hub.

Each device is well suited for combination peripheral functions with hubs, such as a keyboard hub function. The 8-bit

one-time-programmable microcontroller with a 12-MBps USB Hub supports as many as 4 downstream ports.

The CY7C66013 feat ures 29 GP IO pins to s upport USB a nd other appli cations . The I/O pins are groupe d into four ports (P0[7:0 ],

P1[7:0], P2[7:0], P3[4:0]) where each port can be configured as inputs with internal pull-ups, open drain outputs, or traditional

CMOS outputs. Ports 0 to 2 are rated at 8 mA per pin (typical) sink current. Port 3 pins are rated at 12 mA per pin (typical) sink

current, which allows these pins to drive LEDs. Multiple GPIO pins can be connected together to drive a single output for more

drive current capac ity. Additio nal ly, eac h I /O pi n c an be us ed to g ene rate a GPIO interrupt to the micro co ntro lle r. All of the GPIO

interrupts all share the same “GPIO” interrupt vector.

The CY7C66113 has 31 GPIO p ins (P0 [7:0 ], P1 [7:0 ], P2 [7:0 ], P3 [6:0 ]). Additionally, the CY7C66113 featur es an ad diti ona l 8 I/O

pins in the Digital to Analog Conversion (DAC) port (P4[7:0] ). Every DAC pin includes an in tegrated 14-k Ω pull-up resistor. When

a ‘1’ is wr itten to a DAC I/O pin, th e output current sink is disabled a nd the output pin i s driven HIGH by the internal pull-up re sistor.

When a ‘0’ is written to a DAC I/ O pin, the internal p ull-up is disable d and the o utput pin p rovides the program med amount of sink

current. A DAC I/O pin can be used as an input with an internal pull-up by writing a ‘1’ to the pin.

The sink current for each DAC I/O pin can be individually programmed to one of sixteen values using dedicated Isink registers.

DAC bits DAC[1:0] can be used as high current outputs with a programmable sink current range of 3.2 to 16 mA (typical). DAC

bits DAC[7:2] have a programmable current sink range of 0.2 to 1.0 mA (typical). Multiple DAC pins can be connected together

to drive a single output that requires more sink current capacity. Each I/O pin can be used to generate a DAC interrupt to the

microcontroller. Also, the interrupt polarity for each DAC I/O pin is individually programmable.

The microcontroller uses an external 6-MHz crystal and an internal oscillator to provide a reference to an internal PLL-based

clock generator. This technology allow s the c ustom er appli cation to use an i nexpe nsive 6-MHz fundam ental crysta l that redu ce s

the clock-related noise emissions (EMI). A PLL clock generator provides the 6-, 12-, and 48-MHz clock signals for distribution

within the microcontroller.

The CY7C66013 and CY7C 66113 have 8 KB of PROM . These parts als o include Power-on Reset lo gic, a W atch Dog T imer, and

a 12-bit free-running timer. The Power-On Reset (POR) logic detects when power is applied to the device, resets the logic to a

known state, and begins executing instructions at PROM address 0x0000. The Watch Dog Timer is used to ensure the microcontroller recovers after a peri od of inac tiv ity. The firmw are may beco me inac tive for a va riety of reasons, including errors in the

code or a hardware failure such as waiting for an interrupt that never occurs.

2

The microcontroller can communicate with external electronics through the GPIO pins. An I

dates a 100-kHz serial link with an external device. There is also a Hardware Assisted Parallel Interface (HAPI) which can be

used to transfer data to an external device.

The free-running 12-bit timer clocked at 1 MHz provides two interrupt sources, 128-µs and 1.024-ms. The timer can be used to

measure the duration of an event under firmware control by reading the timer at the start of the event and after the event is

complete. The difference between the two readings indicates the duration of the event in microseconds. The upper four bits of

the timer are latched into a n internal register whe n the firmware reads the lower eight bits. A rea d from the upper four bits actually

reads data from the internal register, instead of the timer. This feature eliminates the need for firmware to try to compensate if

the upper four bits increment immediately after the lower eight bits are read.

The microcontroller su pports 11 m as kab le in terru pts in the vectored interrupt control ler. Interrupt s ou rces i nc lud e th e 1 28-µs (bit

6) and 1.024-ms (bit 9) outpu ts from the free-runn ing timer, five USB endpoints , the USB hub, the DAC po rt, the GPIO ports, an d

2

C-compatible master mode interface. The timer bits cause an interrupt (if enabled) when the bit toggles from LOW ‘0’ to

the I

HIGH ‘1.’ The USB en dpoints interrupt after the USB host h as written data to the endpoint FIFO or af ter the USB controlle r sends

a packet to the USB host. The DAC ports have an additional level of masking that allows the user to select which DAC inputs

can cause a DAC interrupt. Th e GPIO ports a lso have a level of m asking to select which GPIO inpu ts can cause a GPIO int errupt.

For additional flexibility, the input transition polarity that causes an interrupt is programmable for each pin of the DAC port. Input

transition polarity can be programmed for each GPIO port as part of the port configuration. The interrupt polarity can be rising

edge (‘0’ to ‘1’) or falling edge (‘1’ to ‘0’).

The CY7C66013 and CY7C66113 include an integrated USB Serial Interface Engine (SIE) that supports the integrated peripherals and the hub controller function. The hardware supports up to two USB device addresses with one device address for the

hub (two endpoints) and a dev ice address for a compound de vice (three endpoints). The SIE allows the USB host to communi cate

with the hub and functions integrated into the microcontroller. The part includes a 1:4 hub repeater with one upstream port and

four downstream po rts . Th e USB H ub al lows p ow er-management control of th e dow n stre am po rts by u si ng GPI O pin s as si gne d

by the user firmware. The user has the o ption of ganging t he downstre am ports together wi th a sing le pair o f power-mana gement

pins, or providing power management for each port with four pairs of power-management pins.

C-compatible interface accommo-

Document #: 38-08024 Rev. ** Page 7 of 53

Page 8

.

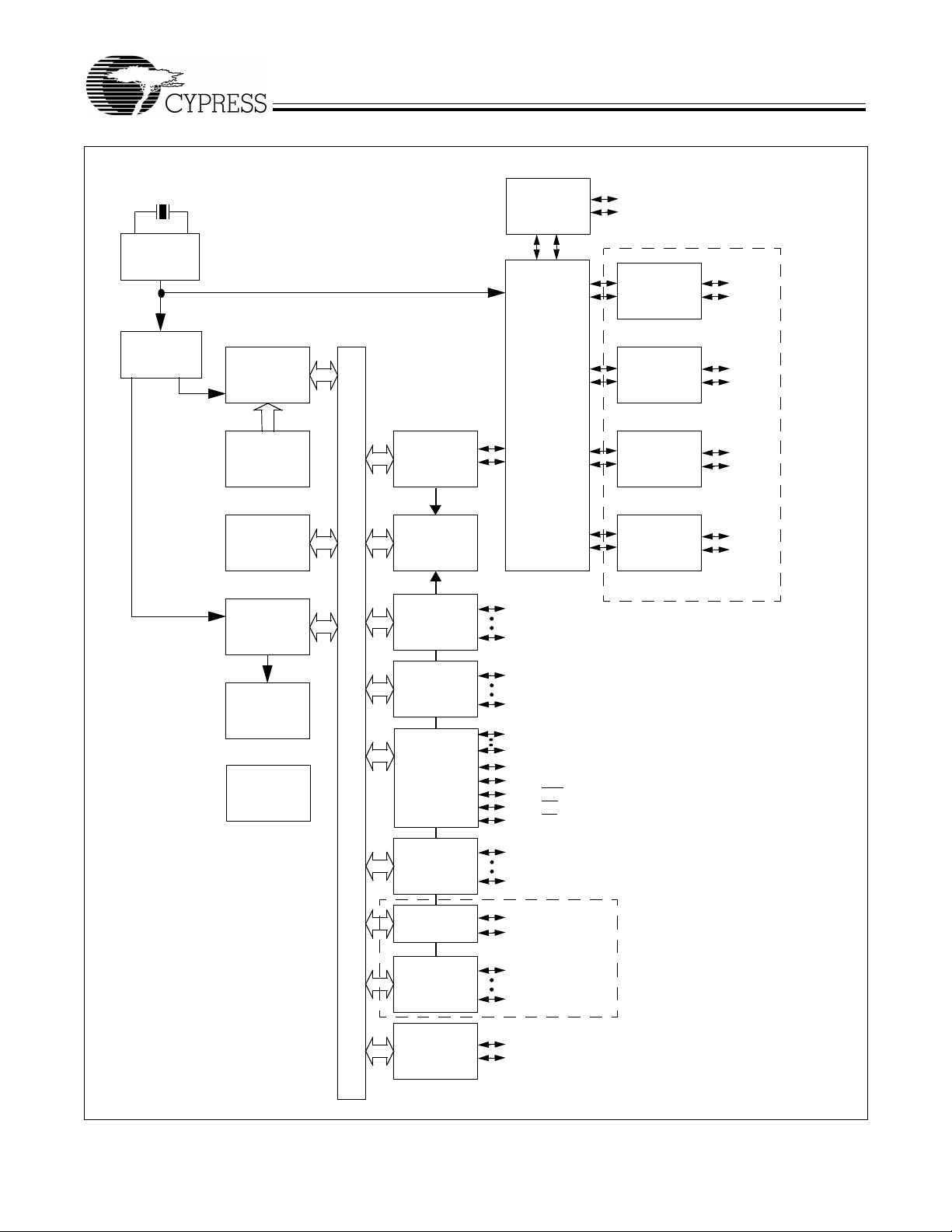

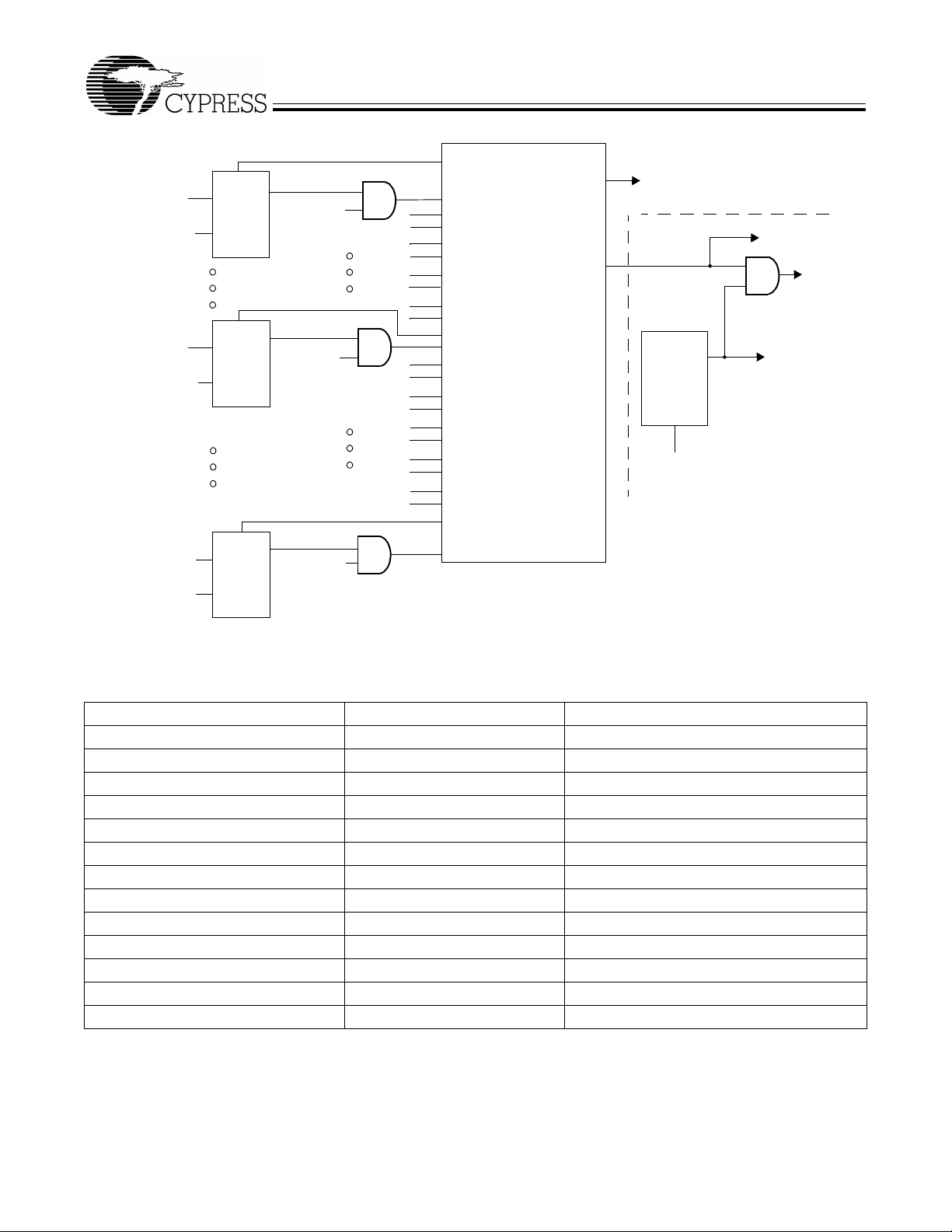

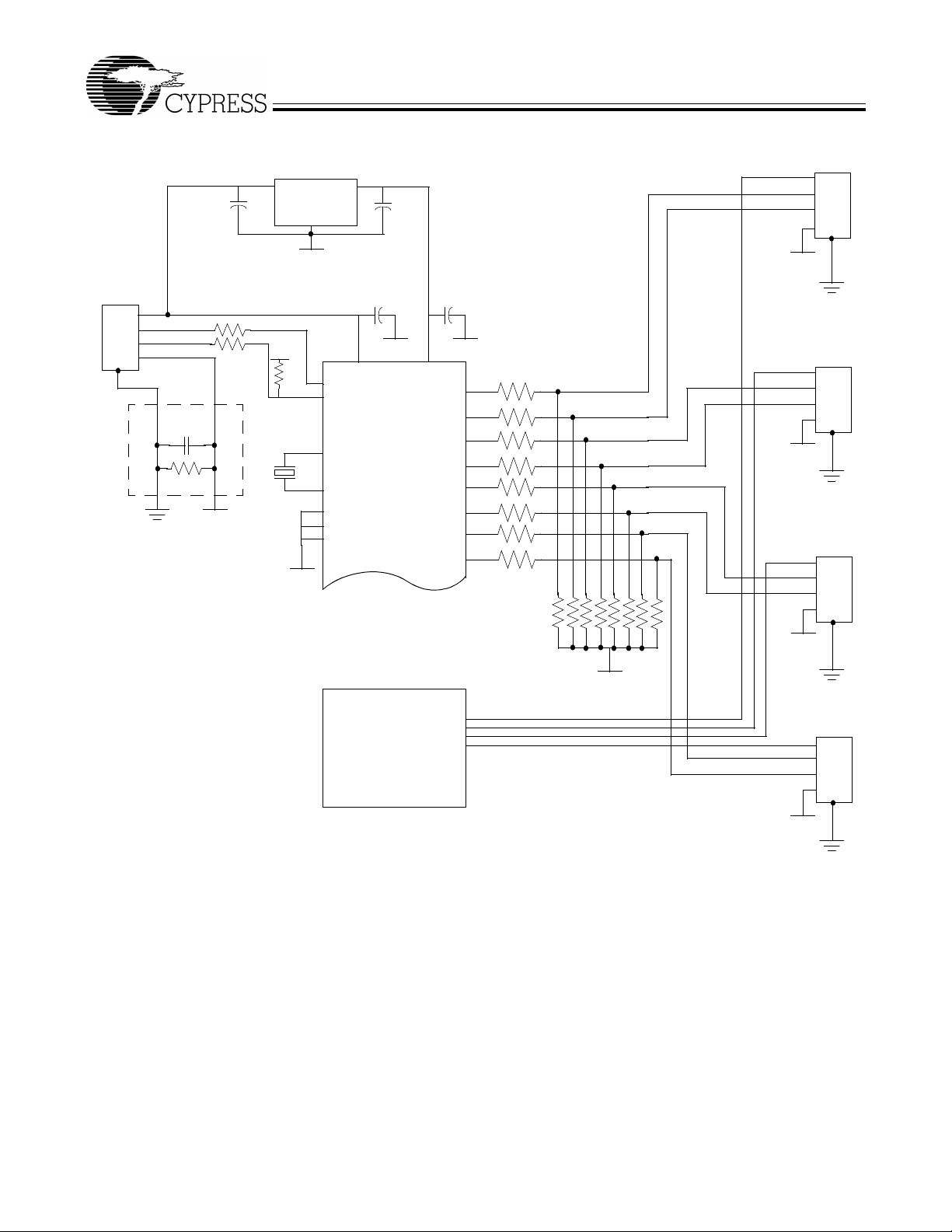

Logic Block Diagram

CY7C66013

CY7C66113

6-MHz crystal

PLL

48 MHz

Clock

Divider

12 MHz

6 MHz

12-MHz

8-bit

CPU

PROM

8 KB

RAM

256 byte

12-bit

Timer

8-bit Bus

USB

SIE

Interrupt

Controller

GPIO

PORT 0

USB

Transceiver

Repeater

P0[0]

P0[7]

D+[0]

Upstream

USB Port

D–[0]

USB

Transceiver

USB

Transceiver

USB

Transceiver

USB

Transceiver

Downstream USB Ports

Power management under firmware

control using GPIO pins

D+[1]

D–[1]

D+[2]

D–[2]

D+[3]

D–[3]

D+[4]

D–[4]

Watch Dog

Timer

Power-On

Reset

GPIO

PORT 1

GPIO/

HAPI

PORT 2

GPIO

PORT 3

GPIO

PORT 3

DAC

PORT

I2C

Interface

*I2C Compatible interface enabled by firmware through

P2[1:0] or P1[1:0]

P1[0]

P1[7]

P2[0:1,7]

P2[2]; Latch_Empty

P2[3]; Data_Ready

P2[4]; STB

P2[5]; OE

P2[6]; CS

P3[0]

P3[4]

P3[5]

P3[6]

DAC[0]

DAC[7]

CY7C66113 only

SCLK

SDATA

High Current

Outputs

Additional

High Current

Outputs

Document #: 38-08024 Rev. ** Page 8 of 53

Page 9

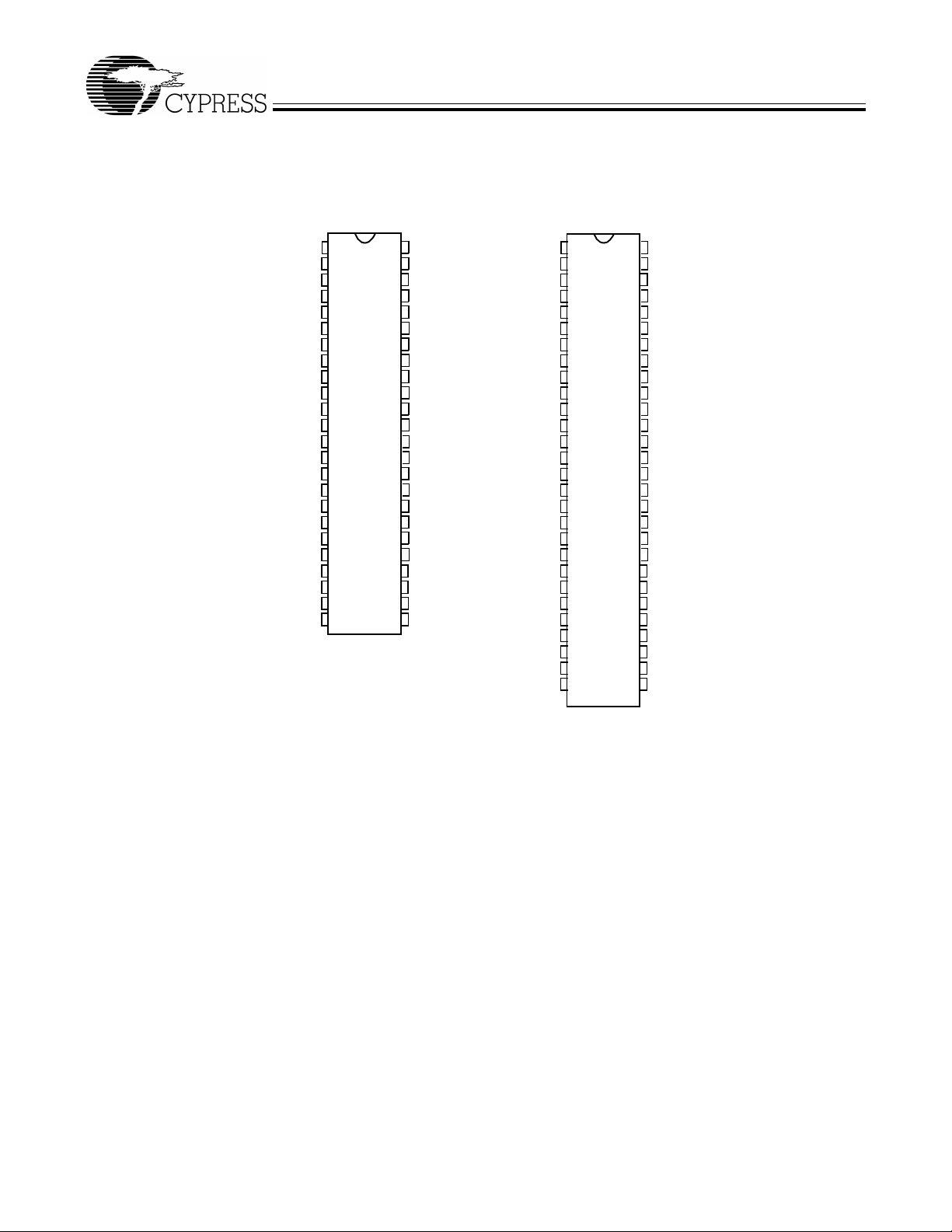

3.0 Pin Configurations

CY7C66013

CY7C66113

CY7C66013

48-pin PDIP/SSOP

REF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

XTALOUT

XTALIN

V

P1[3]

P1[5]

P1[7]

P3[1]

D+[0]

D–[0]

P3[3]

GND

D+[1]

D–[1]

P2[1]

D+[2]

D–[2]

P2[3]

P2[5]

P2[7]

GND

P0[7]

P0[5]

P0[3]

P0[1]

TOP VIEW

CY7C66113

56-pin SSOP

48

V

CC

47

P1[1]

46

P1[0]

P1[2]

45

P1[4]

44

P1[6]

43

P3[0]

42

D–[3]

41

D+[3]

40

39

P3[2]

38

GND

37

P3[4]

D–[4]

36

35

D+[4]

34

P2[0]

33

P2[2]

32

GND

31

P2[4]

30

P2[6]

29

V

PP

P0[0]

28

P0[2]

27

P0[4]

26

25

P0[6]

XTALOUT

XTALIN

V

REF

P1[3]

P1[5]

P1[7]

P3[1]

D+[0]

D–[0]

P3[3]

GND

P3[5]

D+[1]

D–[1]

P2[1]

D+[2]

D–[2]

P2[3]

P2[5]

P2[7]

DAC[7]

P0[7]

P0[5]

P0[3]

P0[1]

DAC[5]

DAC[3]

DAC[1]

56

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

V

CC

55

P1[1]

54

P1[0]

P1[2]

53

P1[4]

52

P1[6]

51

P3[0]

50

D–[3]

49

48

D+[3]

47

P3[2]

46

P3[4]

45

D–[4]

D+[4]

44

43

P3[6]

42

P2[0]

41

P2[2]

GND

40

39

P2[4]

38

P2[6]

37

DAC[0]

V

36

PP

P0[0]

35

P0[2]

34

P0[4]

33

32

P0[6]

31

DAC[2]

30

DAC[4]

29

DAC[6]

Document #: 38-08024 Rev. ** Page 9 of 53

Page 10

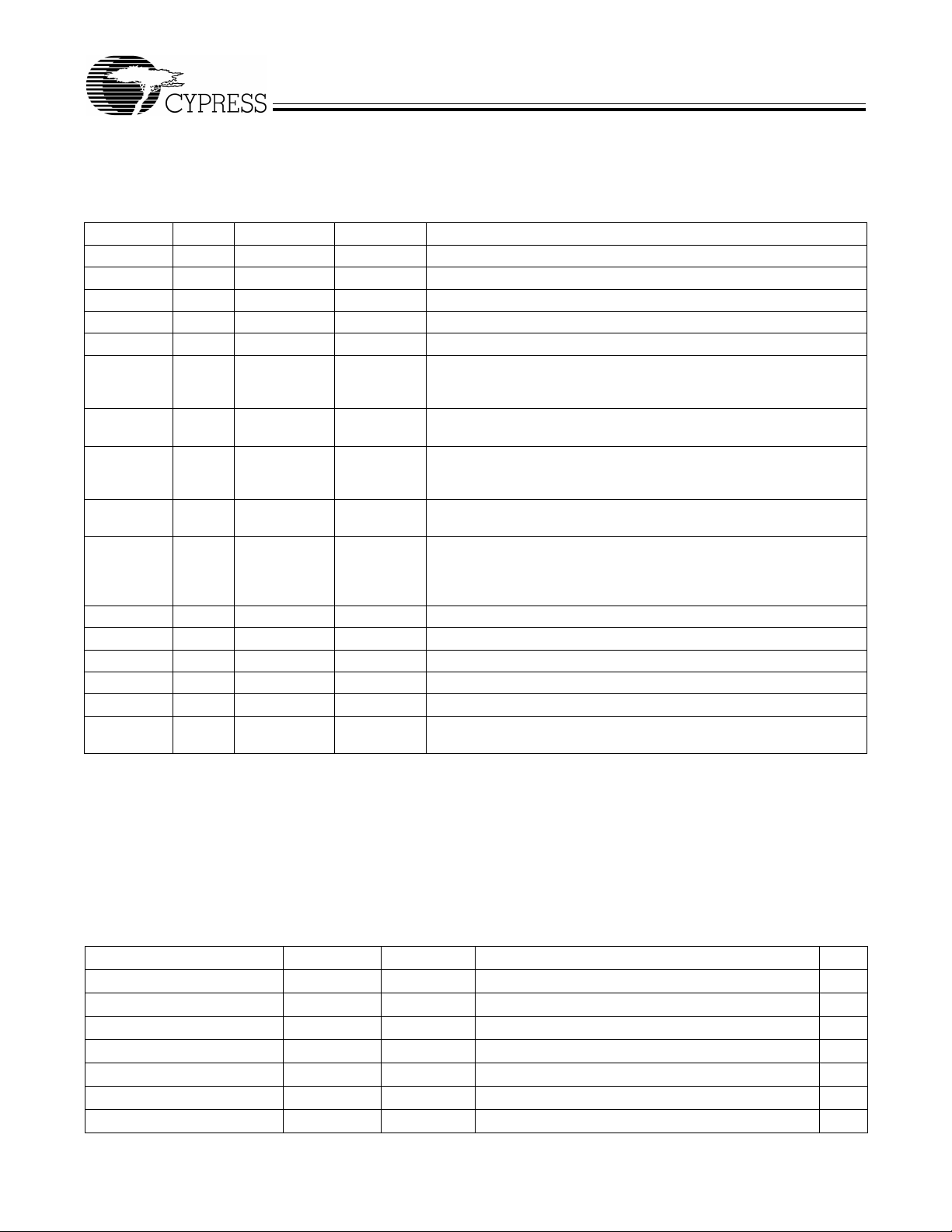

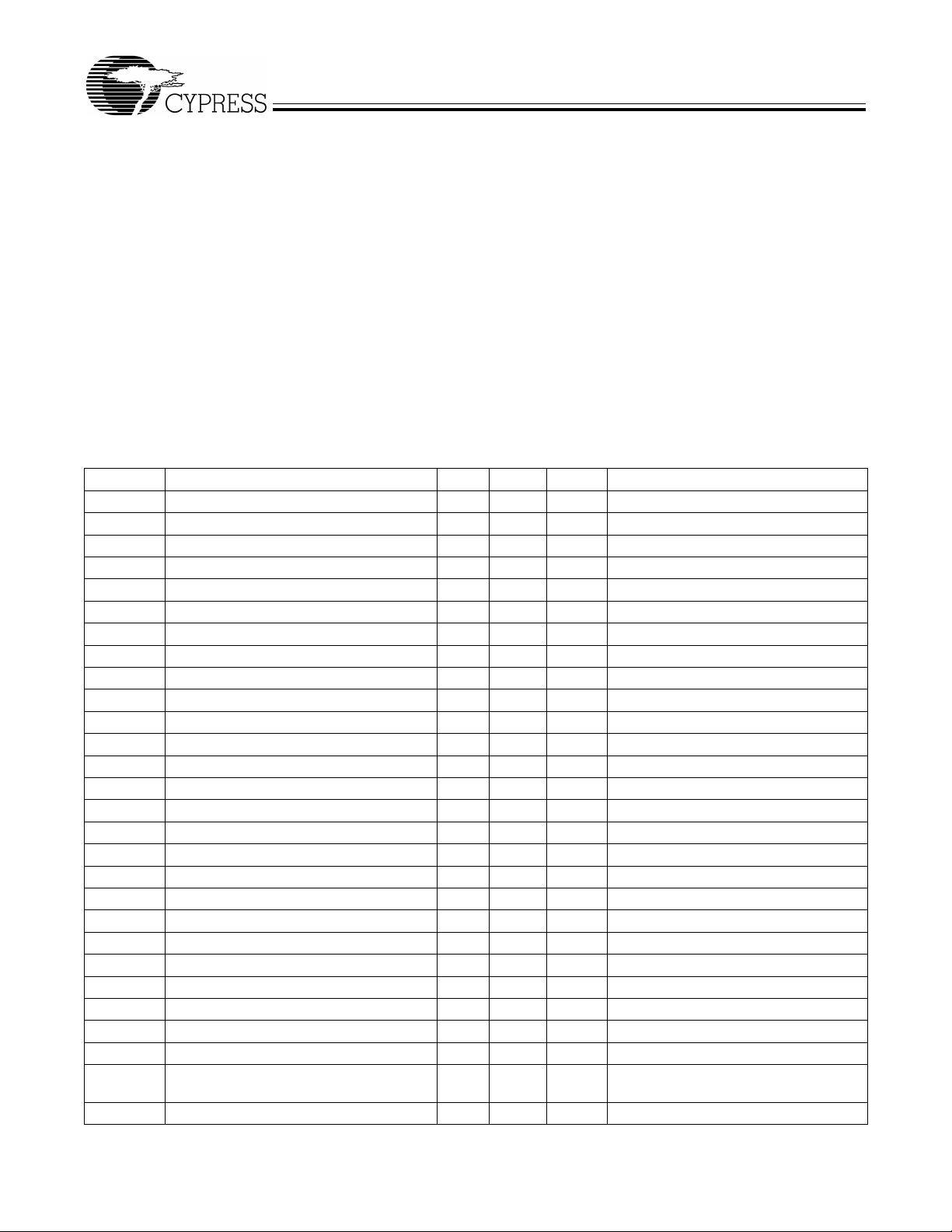

4.0 Product Summary Tables

4.1 Pin Assignments

Table 4-1. Pin Assignments

Name I/O 48-Pin 56-Pin Description

D+[0], D–[0] I/O 8, 9 8, 9 Upstream port, USB differential data.

D+[1], D–[1] I/O 12, 13 13, 14 Downstream port 1, USB differential data.

D+[2], D–[2] I/O 15, 16 16, 17 Downstream port 2, USB differential data.

D+[3], D–[3] I/O 40, 41 48, 49 Downstream port 3, USB differential data.

D+[4], D–[4] I/O 35, 36 44, 45 Downstream port 4, USB differential data.

P0[7:0] I/O 21, 25, 22, 26,

P1[7:0] I/O 6, 43, 5, 44, 4,

P2[7:0] I/O 19, 30, 18, 31,

P3[6:0] I/O 37, 10, 39, 7, 4243, 12, 46,

DAC[7:0] I/O n/a 21, 29, 26,

XTAL

IN

XTAL

OUT

V

PP

V

CC

GND 11, 20, 32, 38 11, 40 Ground.

V

REF

OUT 1 1 6-MHz crystal out.

23, 27, 24, 28

45, 47, 46

17, 33, 14, 34

IN 2 2 6-MHz crystal or external clock input.

29 36 Programming voltage supply, tie to ground during normal operation.

48 56 Voltage supply.

IN 3 3 External 3.3V supply voltage for the differ ential data output buf fers and

22, 32, 23,

33, 24, 34,

25, 35

6, 51, 5, 52,

4, 53, 55, 54

20, 38, 19,

39, 18, 41,

15, 42

10, 47, 7, 50

30, 27, 31,

28, 37

GPIO Port 0.

GPIO Port 1.

GPIO Port 2.

GPIO Port 3, capable of sinking 12 mA (typical).

Digital to Analog Converter (DAC) Port with programmable current sink

outputs. DAC[1:0] offer a progra mmable range of 3.2 to 16 mA typ ical.

DAC[7:2] have a programmable sink current range of 0.2 to 1.0 mA

typical.

the D+ pull up.

CY7C66013

CY7C66113

4.2 I/O Register Summary

I/O registers are access ed via the I/O Read (IO RD) and I/O Wr ite (IOWR, IOWX) instr uctions. IORD read s data from the sele cted

port into the accum ulato r. IOWR performs the re verse; it write s dat a f rom th e accum ulator to the sele cted port. In dexed I/O W ri te

(IOWX) adds the con t en ts of X to th e address in the instructio n to form the port addres s and writes data from the ac cu mu lator to

the specified port. Specifying address 0 (e.g., IOWX 0h) means the I/O register is selected solely by the contents of X.

All undefined registers are reserved. It is important not to write to reserved registers as this may cause an undefined operation

or increased current consumption dur ing operati on. When writing to registers wit h reserved bits, the reserved bits mus t be written

with ‘0.’

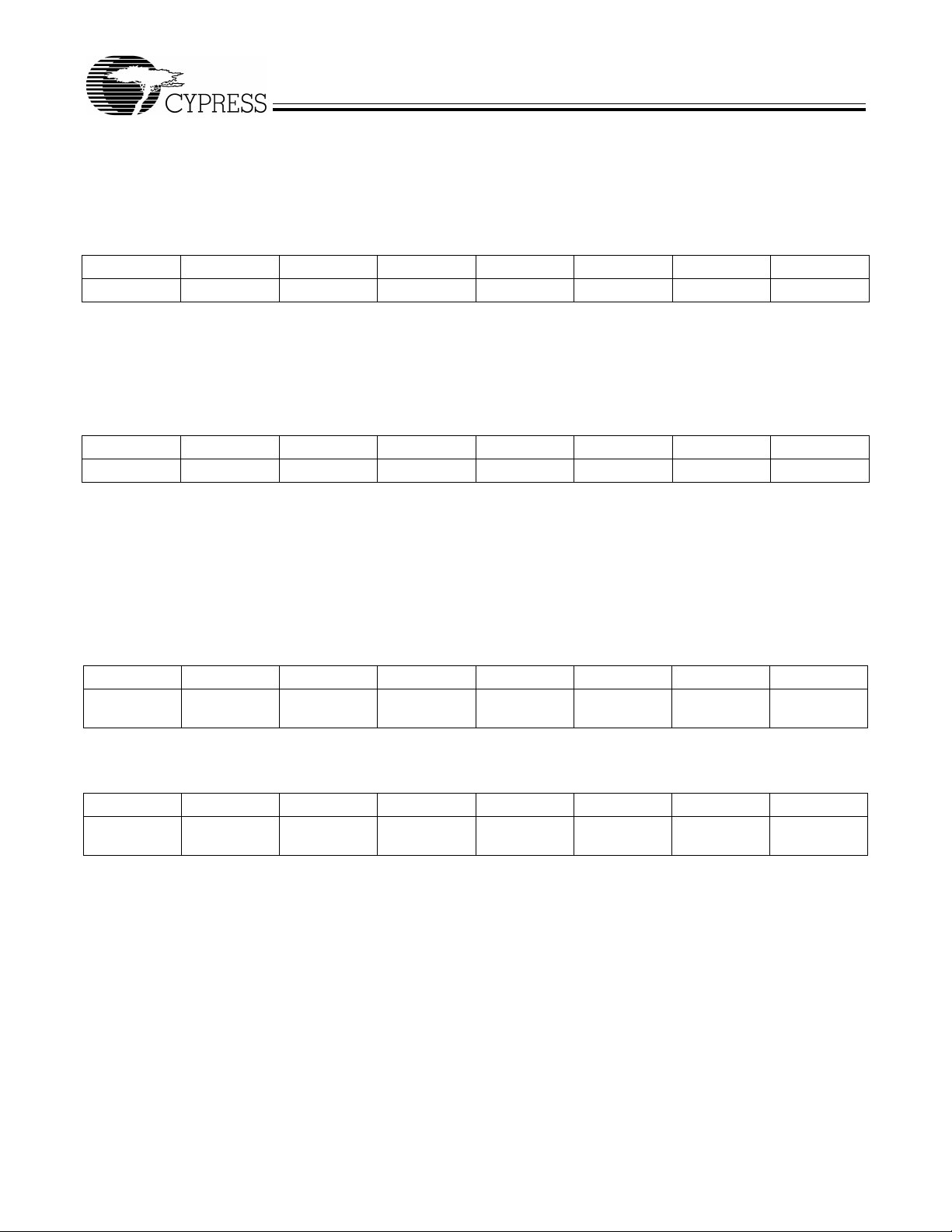

Table 4-2. I/O Register Summary

Register Name I/O Address Read/Write Function Page

Port 0 Data 0x00 R/W GPIO Port 0 Data 19

Port 1 Data 0x01 R/W GPIO Port 1 Data 19

Port 2 Data 0x02 R/W GPIO Port 2 Data 19

Port 3 Data 0x03 R/W GPIO Port 3 Data 19

Port 0 Interrupt Enable 0x04 W Interrupt Enable for Pins in Port 0 20

Port 1 Interrupt Enable 0x05 W Interrupt Enable for Pins in Port 1 20

Port 2 Interrupt Enable 0x06 W Interrupt Enable for Pins in Port 2 20

Document #: 38-08024 Rev. ** Page 10 of 53

Page 11

CY7C66013

CY7C66113

Table 4-2. I/O Register Summary (continued)

Register Name I/O Address Read/Write Function Page

Port 3 Interrupt Enable 0x07 W Interrupt Enable for Pins in Port 3 20

GPIO Configuration 0x08 R/W GPIO Port Configurations 20

2

HAPI and I

USB Device Address A 0x10 R/W USB Device Address A 37

EP A0 Counter Register 0x11 R/W USB Address A, Endpoint 0 Counter 39

EP A0 Mode Register 0x12 R/W USB Address A, Endpoint 0 Configuration 38

EP A1 Counter Register 0x13 R/W USB Address A, Endpoint 1 Counter 39

EP A1 Mode Register 0x14 R/W USB Address A, Endpoint 1 Configuration 39

EP A2 Counter Register 0x15 R/W USB Address A, Endpoint 2 Counter 39

EP A2 Mode Register 0x16 R/W USB Address A, Endpoint 2 Configuration 39

USB Status & Control 0x1F R/W USB Upstream Port Traffic Status and Control 36

Global Interrupt Enable 0x20 R/W Global Interrupt Enable 27

Endpoint Interrupt Enable 0x21 R/W USB Endpoint Interrupt Enables 27

Interrupt Vector 0x23 R Pending Interrupt Vector Read/Clear 29

Timer (LSB) 0x24 R Lower 8 Bits of Free-running Timer (1 MHz) 22

Timer (MSB) 0x25 R Upper 4 Bits of Free-running Timer 22

WDT Clear 0x26 W Watch Dog Timer Clear 17

2

C Control & Status 0x28 R/W I2C Status and C ontrol 24

I

2

C Data 0x29 R/W I2C Data 24

I

DAC Data 0x30 R/W DAC Data 21

DAC Interrupt Enable 0x31 W Interrupt Enable for each DAC Pin 22

DAC Interrupt Polarity 0x32 W Interrupt Polarity for each DAC Pin 22

DAC Isink 0x38-0x3F W Input Sink Current Control for each DAC Pin 21

USB Device Address B 0x40 R/W USB Device Address B (not used in 5-endpoin t mode) 37

EP B0 Counter Register 0x41 R/W USB Address B, Endpoint 0 Counter 39

EP B0 Mode Register 0x42 R/W USB Address B, Endpoint 0 Configuration, or

EP B1 Counter Register 0x43 R/W USB Address B, Endpoint 1 Counter 39

EP B1 Mode Register 0x44 R/W USB Address B, Endpoint 1 Configuration, or

Hub Port Connect Status 0x48 R/W Hub Downstream Port Connect Status 33

Hub Port Enable 0x49 R/W Hub Downstream Ports Enable 34

Hub Port Speed 0x4A R/W Hub Downstream Ports Speed 34

Hub Port Control (Ports [4:1]) 0x4B R/W Hub Downstream Ports Control 34

Hub Port Suspend 0x4D R/W Hub Downstream Port Suspend Control 36

Hub Port Resume Status 0x4E R Hub Downstream Ports Resume Status 36

Hub Ports SE0 Status 0x4F R Hub Downstream Ports SE0 Status 35

Hub Ports Data 0x50 R Hub Downstream Ports Differential data 35

Hub Downstream Force Low 0x51 R/W Hub Downstream Ports Force LOW 35

Processor Status & Control 0xFF R/W Microprocessor Status and Control Register 26

C Configuration 0x09 R/W HAPI Width and I2C Position Configuration 23

USB Address A, Endpoint 3 in 5-endpoint mode

USB Address A, Endpoint 4 in 5-endpoint mode

38

39

Document #: 38-08024 Rev. ** P age 11 of 53

Page 12

CY7C66013

CY7C66113

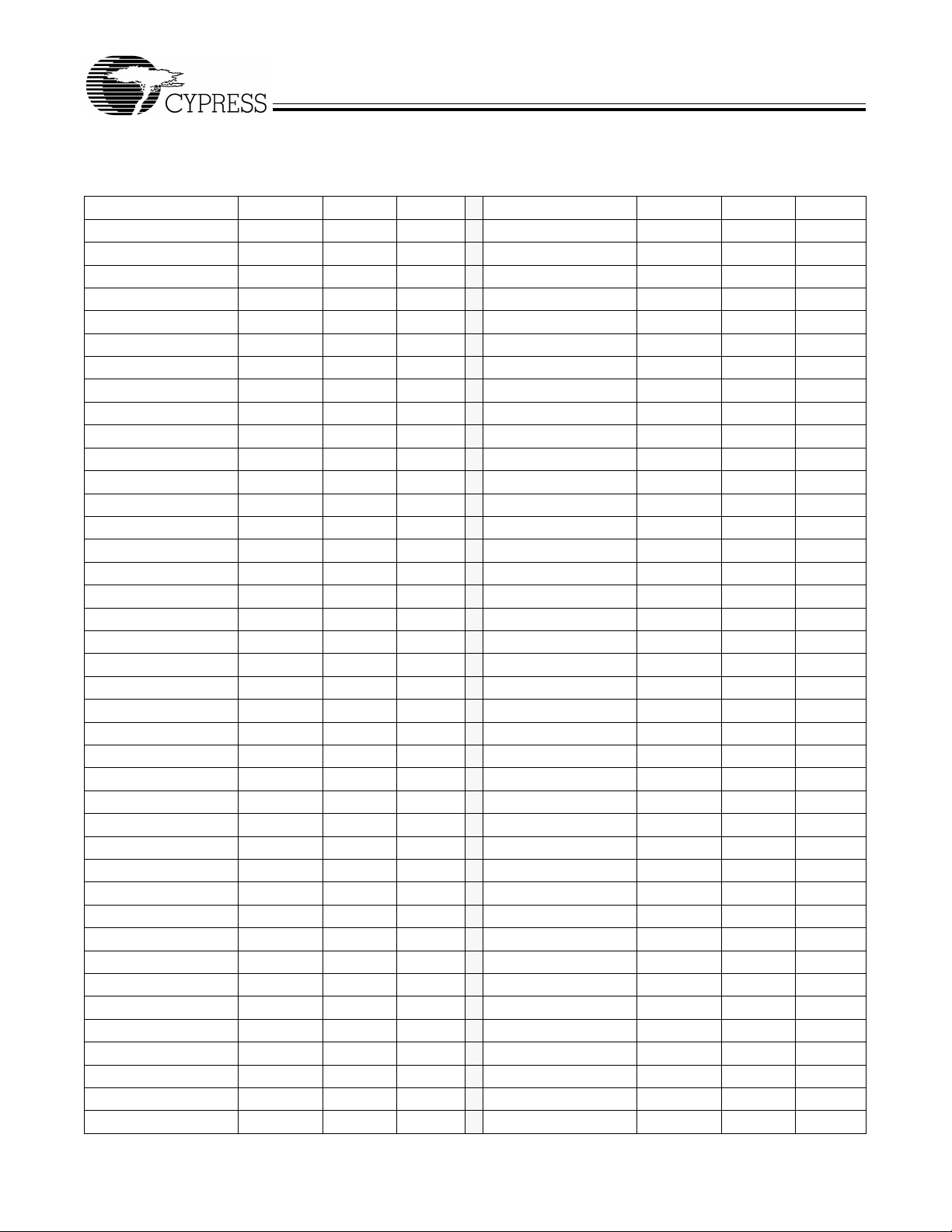

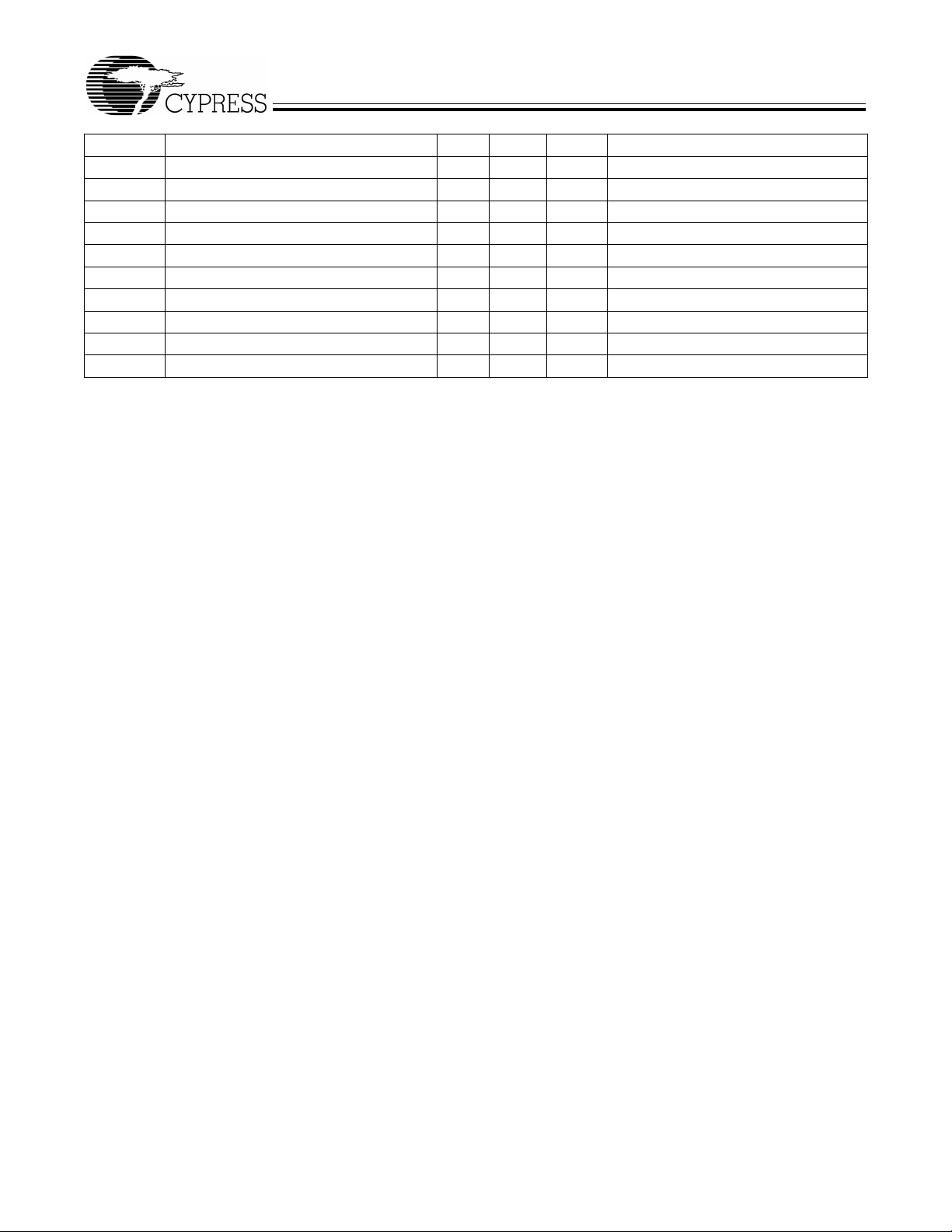

4.3 Instruction Set Summary

Refer to the CYASM Assembler User’s Guide for more details.

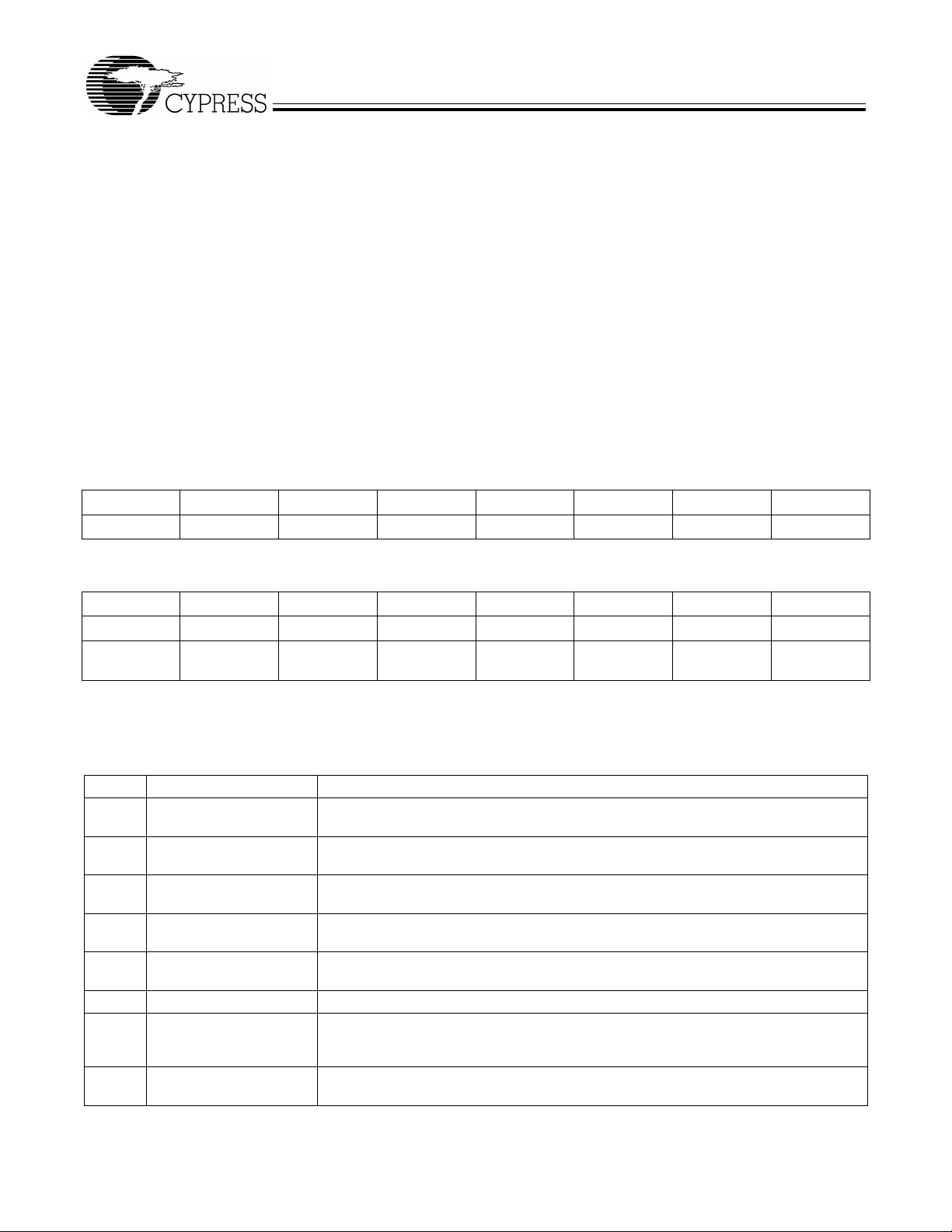

Table 4-3. Instruction Set Summary

MNEMONIC operand opcode cycles MNEMONIC operand opcode cycles

HAL T 00 7 NOP 20 4

ADD A,expr data 01 4 INC A acc 21 4

ADD A,[expr] direct 02 6 INC X x 22 4

ADD A,[X+expr] index 03 7 INC [expr] direct 23 7

ADC A,expr data 04 4 INC [X+expr] index 24 8

ADC A,[expr] direct 05 6 DEC A acc 25 4

ADC A,[X+expr] index 06 7 DEC X x 26 4

SUB A,expr data 07 4 DEC [expr] direct 27 7

SUB A,[expr] direct 08 6 DEC [X+expr] index 28 8

SUB A,[X+expr] index 09 7 IORD expr address 29 5

SBB A,expr data 0A 4 IOWR expr address 2A 5

SBB A,[expr] direct 0B 6 POP A 2B 4

SBB A,[X+expr] index 0C 7 POP X 2C 4

OR A,expr data 0D 4 PUSH A 2D 5

OR A,[expr] direct 0E 6 PUSH X 2E 5

OR A,[X+expr] index 0F 7 SWAP A,X 2F 5

AND A,expr data 10 4 SWAP A,DSP 30 5

AND A,[expr] direct 11 6 MOV [expr],A direct 31 5

AND A,[X+expr] index 12 7 MOV [X+expr],A index 32 6

XOR A,expr data 13 4 OR [expr],A direct 33 7

XOR A,[expr] direct 14 6 OR [X+expr],A index 34 8

XOR A,[X+expr] index 15 7 AND [expr],A direct 35 7

CMP A,expr data 16 5 AND [X+expr],A index 36 8

CMP A,[expr] direct 17 7 XOR [expr],A direct 37 7

CMP A,[X+expr] index 18 8 XOR [X+expr],A index 38 8

MOV A,expr data 19 4 IOWX [X+expr] index 39 6

MOV A,[expr] direct 1A 5 CPL 3A 4

MOV A,[X+expr] index 1B 6 ASL 3B 4

MOV X,expr data 1C 4 ASR 3C 4

MOV X,[expr] direct 1D 5 RLC 3D 4

reserved 1E RRC 3E 4

XPAGE 1F 4 RET 3F 8

MOV A,X 40 4 DI 70 4

MOV X,A 41 4 EI 72 4

MOV PSP,A 60 4 RETI 73 8

CALL addr 50 - 5F 10 JC addr C0-CF 5

JMP addr 80-8F 5 JNC addr D0-DF 5

CALL addr 90-9F 10 JACC addr E0-EF 7

JZ addr A0-AF 5 INDEX addr F0-FF 14

JNZ addr B0-BF 5

Document #: 38-08024 Rev. ** Page 12 of 53

Page 13

CY7C66013

CY7C66113

5.0 Programming Model

5.1 14-Bit Program Counter (PC)

The 14-bit Program Counter (PC) allows acc es s to up to 8 KB of PROM avail abl e wi th the CY7C 66 x1 3 arch ite ctu re. The top 32

bytes of the ROM in the 8K part are reserved for testing purposes. The program counter is cleared during reset, such that the

first instruction e xe cut ed afte r a re se t is at add res s 0 x0 000 h. Typicall y, this is a ju mp in stru ction to a reset handler tha t initializes

the application (see Interrupt Vectors on page 28).

The lower eight bits of the program counter are incremented as instructions are loaded and executed. The upper six bits of the

program counter are increm ented by exe cuting an XPAGE instr uction . As a result, the la st instruc tion execu ted within a 256 -byte

“page” of sequential code should be an XPAGE instruction. The assembler directive “XPAGEON” causes the assembler to insert

XPAGE instructions automatically. Because instructions can be either one or two bytes long, the assembler may occasionally

need to insert a NOP followed by an XPAGE to execute correctly.

The address of the nex t inst ruction to be execu ted, the ca rry flag , and th e zero flag are save d as two bytes on the program sta ck

during an interrupt acknowledge or a CALL instruction. The program counter, carry flag, and zero flag are restored from the

program stack during a RETI instruction. Only the program counter is restored during a RET instruction.

The program counter cann ot be acc es se d di rec tly by t he fi rmwa re. Th e pro gram st ack ca n be examined by reading SRAM from

location 0x00 and up.

Document #: 38-08024 Rev. ** Page 13 of 53

Page 14

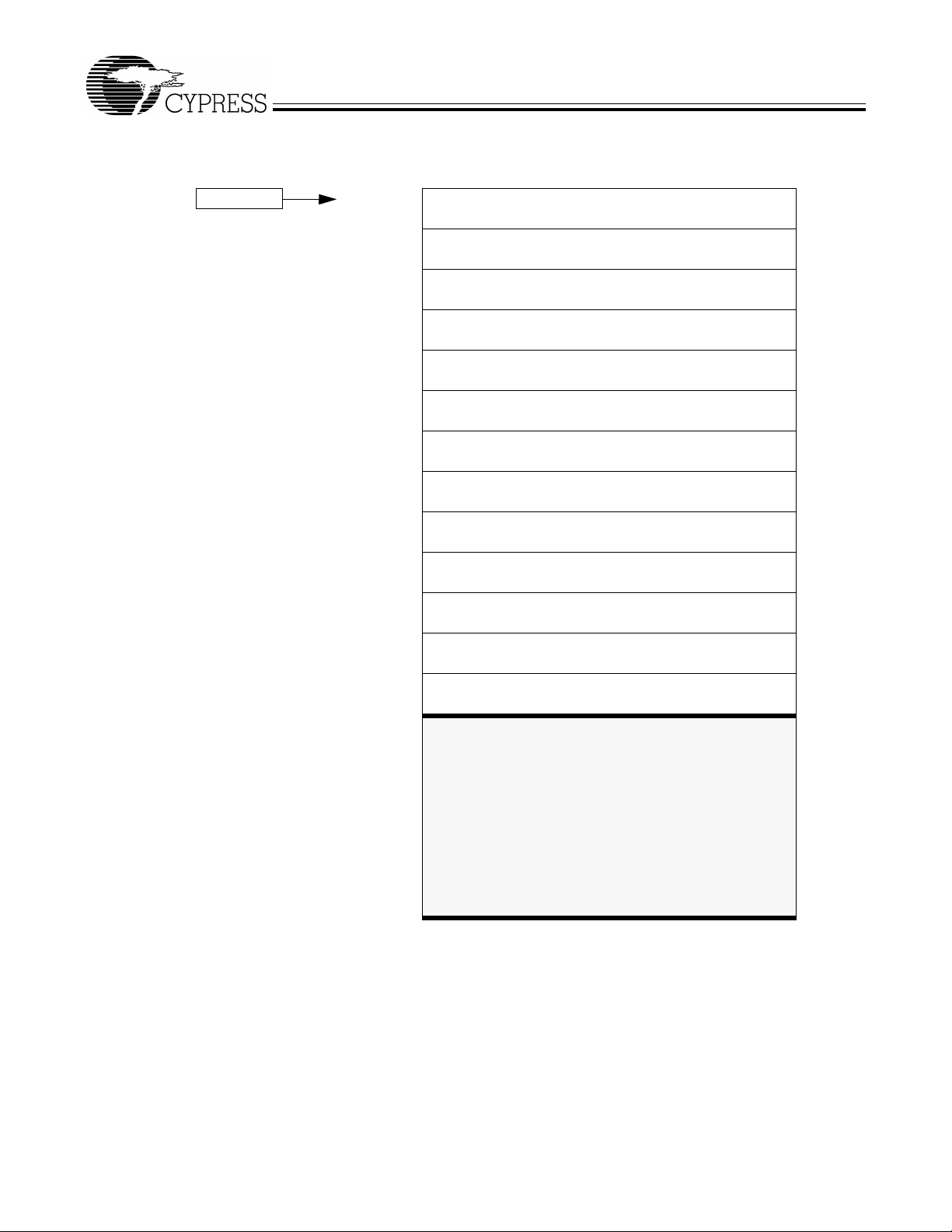

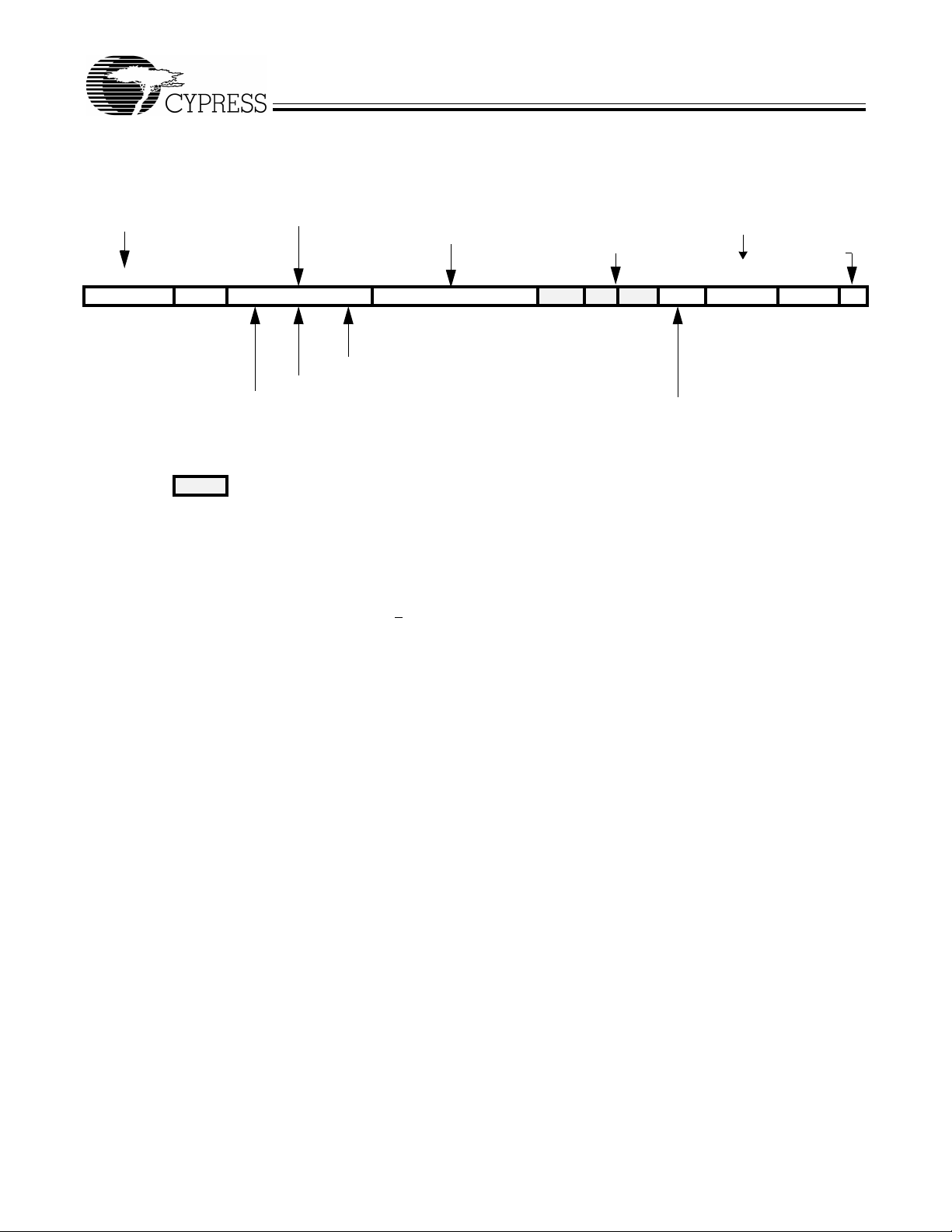

5.1.1 Program Memory Organization

after reset Address

14-bit PC 0x0000 Program execution begins here after a reset

CY7C66013

CY7C66113

0x0002 USB Bus Reset interrupt vector

0x0004 128-µs timer interrupt vector

0x0006 1.024-ms timer interrupt vector

0x0008 USB address A endpoint 0 interrupt vector

0x000A USB address A endpoint 1 interrupt vector

0x000C USB address A endpoint 2 interrupt vector

0x000E USB address B endpoint 0 interrupt vector

0x0010 USB address B endpoint 1 interrupt vector

0x0012 Hub interrupt vector

0x0014 DAC interrupt vector

0x0016 GPIO interrupt vector

0x0018

0x001A Program Memory begins here

0x1FDF 8 KB (-32) PROM ends here (CY7C66013, CY7C66113)

Figure 5-1. Program Memory Space with Interrupt Vector Table

I2C interrupt vector

5.2 8-Bit Accumulator (A)

The accumulator is the general-purpose register for the microcontroller.

5.3 8-Bit Temporary Register (X)

The “X” register is availa ble to the firmware for temporary storage of intermediate res ults. The microcontrol ler can perform inde xed

operations based on the value in X. Refer to Section 5.6.3 for additional information.

Document #: 38-08024 Rev. ** Page 14 of 53

Page 15

CY7C66013

CY7C66113

5.4 8-Bit Program Stack Pointer (PSP)

During a reset, the Program Stack Pointer (PSP) is set to 0x00 and “grows” upward from this address. The PSP may be set by

firmware, using the MOV PSP,A instruction. The PSP supports interrupt service under hardware control and CALL, RET, and

RETI instructions under firmware control. The PSP is not readable by the firmware.

During an interrupt acknowledge, interrupts are disabled and the 14-bit program counter, carry flag, and zero flag are written as

two bytes of data memory . The first byte is stored in the mem ory addressed by the PSP, then the PSP is incremented. The second

byte is stored in memory addressed by the PSP, and the PSP is incremented again. The overall effect is to store the program

counter and flags on the program “stack” and increment the PSP by two.

The Return From Interrup t (RETI) in struction decreme nts the PSP, then restores the second byte from memory a ddressed by the

PSP. The PSP is decrem ented again an d the first byte is restore d from memory addre ssed by the PSP. After the program counter

and flags have been res tored from stack, th e interrupts are enabled. The ov erall effe ct is to restore t he program counter a nd flags

from the program stack, decrement the PSP by two, and re-enable interrupts.

The Call Subroutine (CALL) instruction stores the program counter and flags on the program stack and increments the PSP by

two.

The Return From Subroutine (RET) instruction restores the program counter but not the flags from the program stack and

decrements the PSP by two.

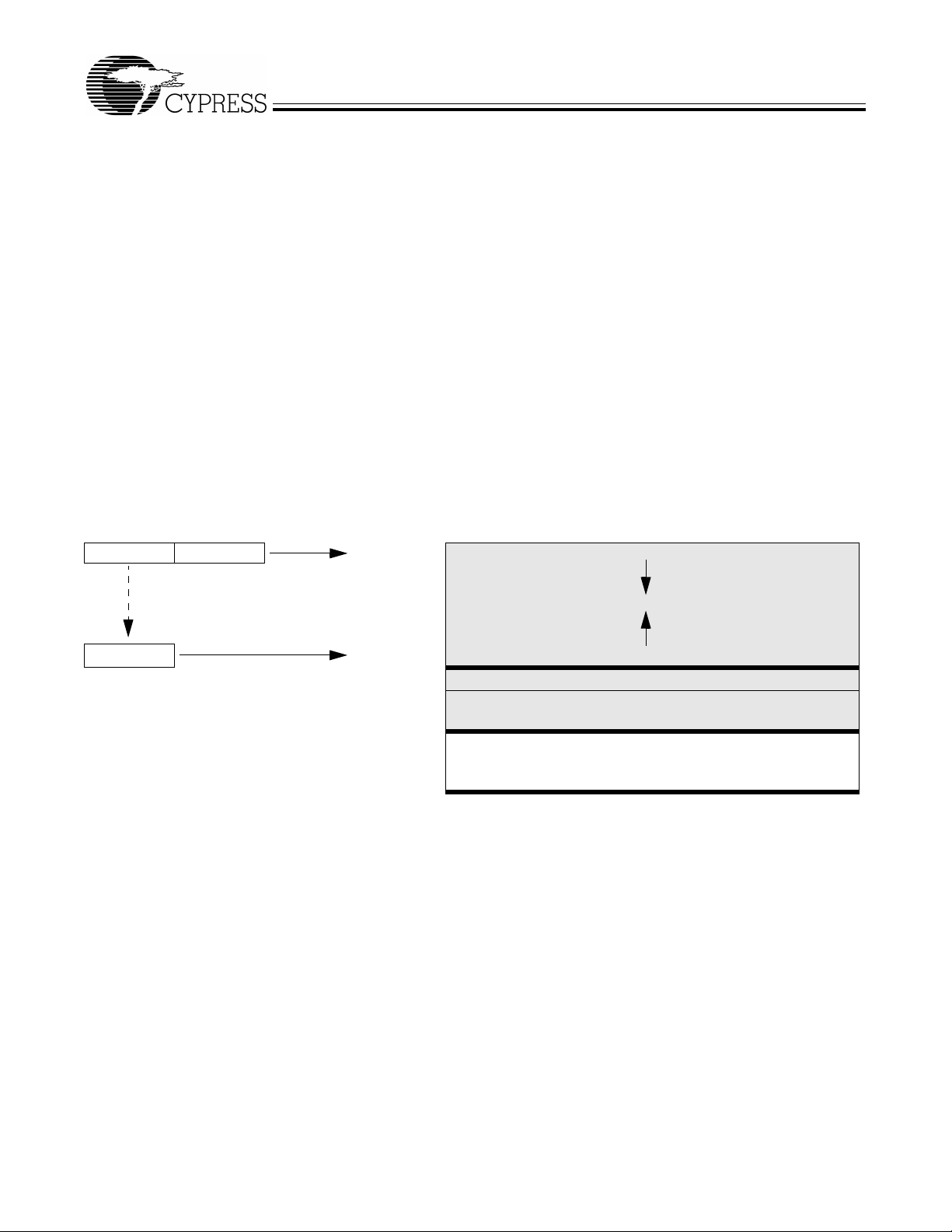

5.4.1 Data Memory Organization

The CY7C66x13 microcontrollers provide 256 bytes of data RAM. Normally, the SRAM is partitioned into four areas: program

stack, user variab les, data s tack, and U SB endpoint FIFOs. The foll owing is one example o f where the program stack , data stack ,

and user variables areas could be located.

After reset Address

8-bit DSP 8-bit PSP 0x00 Program Stack Growth

(Move DSP

8-bit DSP

[1]

)

user selected Data Stack Growth

User variables

USB FIFO space for up to two Addre sses and five endpo ints

0xFF

[2]

5.5 8-Bit Data Stack Pointer (DSP)

The Data Stack Pointer (DSP) supports PUSH and POP instructions that use the data stack for temporary storage. A PUSH

instruction pre-decrements the DSP, then writes data to the memory location addressed by the DSP. A POP instruction reads

data from the memory location addressed by the DSP, then post-increments the DSP.

During a reset, the DSP is reset to 0x00. A PUSH instruction when DSP equals 0x00 writes data at the top of the data RAM

(address 0xFF). This writes data to the memory area reserved for USB endpoint FIFOs. Therefore, the DSP should be indexed

at an appropriate memory location that does not compromise the Program Stack, user-defined memory (variables), or the USB

endpoint FIFOs.

For USB applications , the firmw are shou ld set the DSP to a n appropriate location to avoid a memo ry confli ct with RAM dedic ated

to USB FIFOs. The memory requirements for the USB endpoints are described in Section 19.2. Example assembly instructions

to do this with two device addresses (FIFOs begin at 0xD8) are shown below:

MOV A,20h ; Move 20 hex into Accumulator (must be D8h or less)

SWAP A,DSP ; swap accumulator value into DSP register

Notes:

1. Refer to Section 5.5 for a description of DSP.

2. Endpoint sizes are fixed by the Endpoint Size Bit (I/O register 0x1F, Bit 7), see Table 19-1.

Document #: 38-08024 Rev. ** Page 15 of 53

Page 16

CY7C66013

CY7C66113

5.6 Address Modes

The CY7C66013 and CY7C66113 microcontrollers support three addressing modes for instructions that require data operands:

data, direct, and indexed.

5.6.1 Data (Immediate)

“Data” address mode refers to a data operan d that is actually a con stant encoded in the instruct ion. As an example, co nsider the

instruction that loads A with the constant 0xD8:

• MOV A,0D8h

This instruction requires two bytes of code where the first byte identifies the “MOV A” instruction with a data operand as the

second byte. The second byte of the instruction is the constant “0xD8”. A constant may be refe r red to by na me if a pr ior “EQU”

statement assigns the constant value to the name. For example, the following code is equivalent to the example shown above:

• DSPINIT: EQU 0D8h

• MOV A,DSPINIT

5.6.2 Direct

“Direct” address mode is used when the data operand is a variable stored in SRAM. In that case, the one byte address of the

variable is encoded in the instruction. As an example, consider an instruction that loads A with the contents of memory address

location 0x10:

• MOV A,[10h]

Normally, variable names are assigned to variable addresses using “EQU” statements to imp rove the rea dability of the assembl er

source code. As an example, the following code is equivalent to the example shown above:

• buttons: EQU 10h

• MOV A,[buttons]

5.6.3 Indexed

“Indexed” address mode allows the firmware to manipulate arrays of data stored in SRAM. The address of the data operand is

the sum of a constant e ncoded in the instructio n and the c ontents of t he “X” registe r . Normal ly, the constant is the “base” address

of an array of data and the X register contains an index that indicates which element of the array is actually addressed:

• array: EQU 10h

• MOV X,3

• MOV A,[X+array]

This would have the effect of loading A with the fourth element of the SRAM “array” that begins at address 0x10. The fourth

element would be at address 0x13.

6.0 Clocking

XTALOUT

(pin 1)

XTALIN

(pin 2)

30 pF

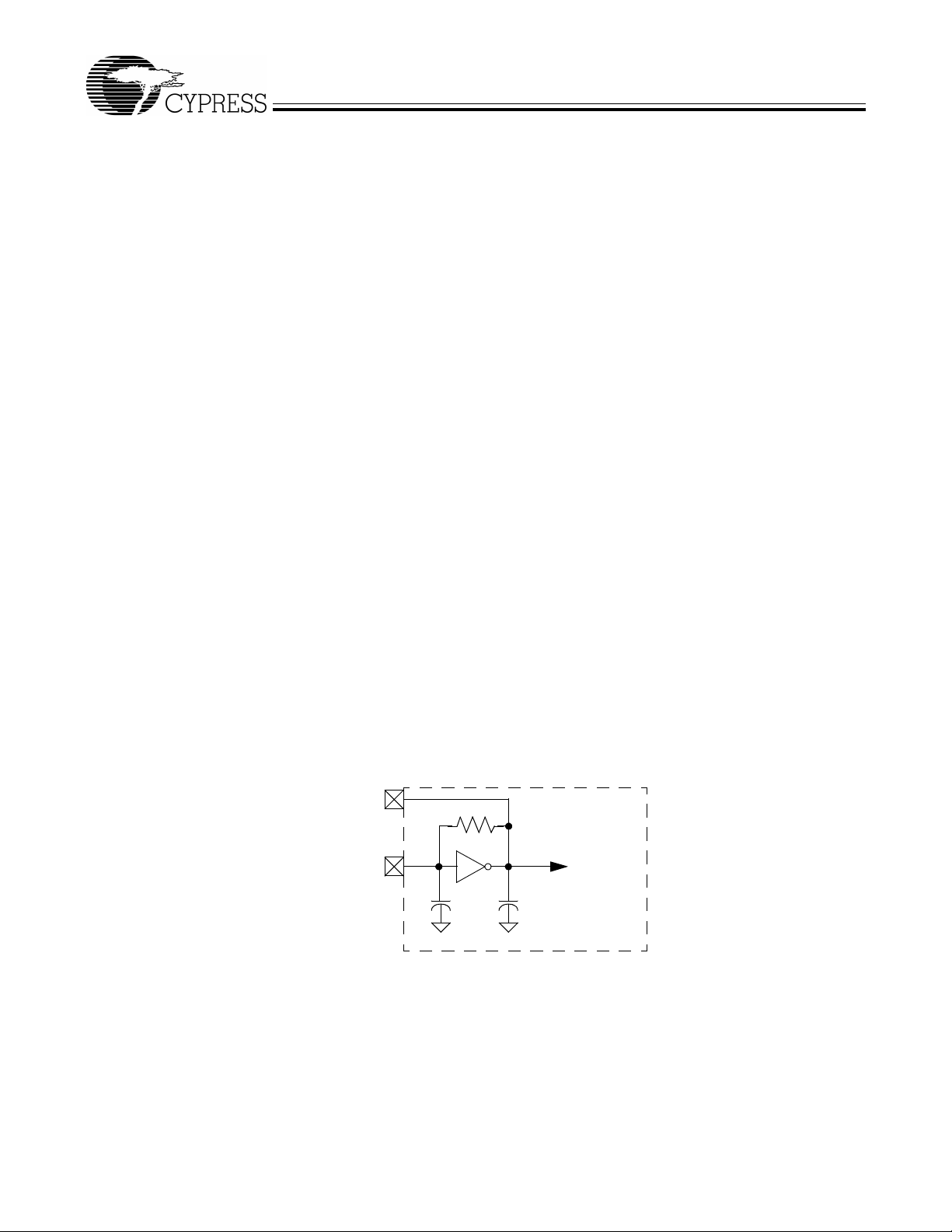

Figure 6-1. Clock Oscillator On-Chip Circuit

The XTALIN and XTALOUT are the clock pins to the microcontroller. The user can connect an external oscillator or a crystal to

these pins. When using an ex tern al c rys tal , kee p PC B traces be tw een the ch ip le ads and crys tal as sh ort as pos sible (less than

2 cm). A 6-MHz fundamenta l frequency p arallel resonant crystal can be connecte d to these pin s to provide a reference fre quency

for the internal PLL. Th e two inte rnal 30 -pF load caps appear i n series t o the ex ternal c rystal an d wou ld be e quiva lent to a 15-pF

load. Therefore, the crystal must have a required load capacitance of about 15–18 pF. A ceramic resonator does not allow the

microcontroller to meet the timing specifications of full speed USB and therefore a ceramic resonator is not recommended with

these parts.

An external 6-MHz clock can be applied to the XTALIN pin if the XTALOUT pin is left open. Grounding the XTALOUT pin when

driving XTALIN with an oscillator does not work because the internal clock is effectively shorted to ground.

to internal PLL

30 pF

Document #: 38-08024 Rev. ** Page 16 of 53

Page 17

CY7C66013

CY7C66113

7.0 Reset

The CY7C66x13 supports two resets: Power-On Reset (POR) and a Watch Dog Reset (WDR). Each of these resets causes:

• all registers to be restored to their default states,

• the USB Device Addresses to be set to 0,

• all interrupts to be disabled,

• the PSP and Data Stack Pointer (DSP) to be set to memory address 0x00.

The occurrence of a reset is recorded in the Processor Status and Control Register, as described in Section 15.0. Bits 4 and 6

are used to record the occurr ence of POR and WDR resp ectivel y. Firmware can int errogate these bit s to determ ine the ca use of

a reset.

Program execution starts at ROM address 0x0000 after a reset. Although this looks like interrupt vector 0, there is an important

difference. Reset processing does NOT push the program counter, carry flag, and zero flag onto program stack. The firmware

reset handler should configure the hardware before the “main” loop of code. Attem pting to execute a R ET or RETI in the firmwa re

reset handler causes unpredictable execution results.

7.1 Power-On Reset (POR)

When VCC is first applied to the chi p, the Power-On Reset (POR) signa l is asserted and th e CY7C66x13 e nters a “semi-suspend”

state. During the semi-suspend state, which is different from the suspend state defined in the USB specification, the oscillator

and all other block s o f th e part are functional, exc ept for the CPU. This semi-susp end tim e ens ure s that both a valid V

reached and tha t the inte rnal PLL has tim e to sta bilize befo re full o peratio n begins. When t he V

2.5V, and the oscillator is stable, the POR is deasserted and the on-chip timer starts counting. The first 1 ms of suspend time is

not interruptible, a nd the semi -suspend sta te continues fo r an additiona l 95 ms unl ess the coun t is bypassed by a USB Bus Res et

on the upstream port. The 95 ms provides time for V

If a USB Bus Reset occurs on the upstream port during the 95 ms semi-suspend time, the semi-suspend state is aborted and

program execution begins immediately from address 0x0000. In this case, the Bus Reset interrupt is pending but not serviced

until firmware sets the USB Bus Reset Interrupt Enable bit (bit 0 of register 0x20) and enables interrupts with the EI command.

The POR signal is asserte d whenever V

again. Behavior is the same as described above.

drops below approxim ately 2.5V , an d remains asserte d until VCC rises above this leve l

CC

to stabilize at a valid operating voltage before the chip executes code.

CC

has risen above approxi mately

CC

level is

CC

7.2 Watch Dog Reset (WDR)

The Watch Dog Timer Reset (WDR) occurs when the internal Watch Dog Timer rolls over. Writing any value to the write-only

Watch Dog Restart Register at address 0x26 clears the timer. The timer rolls over and WDR occurs if it is not cleared within

(8 ms minimum) of the la st clear . Bit 6 of th e Processor Statu s and Control Regis ter is set to reco rd this event (th e register

t

WATCH

contents are set to 010X0001 by the WDR). A Watch Dog Timer Reset lasts for 2 ms, after which the microcontroller begins

execution at ROM address 0x0000.

t

WATCH

Last write to

Watch Dog Timer

Register

The USB transmitter is disabled by a Watch Dog Reset because the USB Device Address Registers are cleared (see Section

19.1). Otherwise, the USB Controller would respond to all address 0 transactions.

It is possible for the WDR bit of the Proc ess or St atus an d Control Register (0xFF) to be se t foll owin g a PO R ev ent . If a fi rmw a re

interrogates the Processor Statu s and Cont rol Regis ter for a set condi tion on the WDR bit, the WDR bit should be ignored if the

POR (bit 3 of register 0xFF) bit is set.

No write to WDT

register, so WDR

goes HIGH

Figure 7-1. Watch Dog Reset (WDR)

2 ms

Execution begins at

Reset Vector 0x0000

Document #: 38-08024 Rev. ** Page 17 of 53

Page 18

CY7C66013

CY7C66113

8.0 Suspend Mode

The CY7C66x13 can be placed into a low-power state by setting the Suspend bit of the Processor Status and Control register.

All logic blocks in the device are turned off except the GPIO interrupt logic and the USB receiver. The clock oscillator and PLL,

as well as the free-running and watch dog timers, are shut down. Only the occurrence of an enabled GPIO interrupt or non-idle

bus activity at a USB upst ream or downstream p ort wakes the part from sus pend. The Run bit in th e Processor Status and Control

Register must be set to resume a part out of suspend.

The clock oscillator restarts immediately after exiting suspend mode. The microcontroller returns to a fully functional state 1 ms

after the oscillator is stable. The microcon troller executes the inst ruction following th e I/O write that placed the device into suspen d

mode before servicing any interrupt requests.

The GPIO interrupt allows the controller to wake-up periodic ally and poll system componen ts while maintaining a very low av erage

power consumption. To achieve the lowest possi ble current d uring suspend mode, all I/O shoul d be held at V

applies to internal port pins that may not be bonded in a particular package.

Typical code for entering suspend is shown below:

... ; All GPIO set to low-power state (no floating pins)

... ; Enable GPIO interrupts if desired for wake-up

mov a, 09h ; Set suspend and run bits

iowr FFh ; Write to Status and Control Register - Enter suspend, wait for USB activity (or GPIO Interrupt)

nop ; This executes before any ISR

... ; Remaining code for exiting suspend routine

or Gnd. This also

CC

9.0 General-Purpose I/O (GPIO) Ports

GPIO

CFG

OE

Internal

Data Bus

Port Write

Port Read

Reg_Bit

STRB

(Latch is Transparent

except in HAPI mode)

Interrupt

Enable

Interrupt

Controller

Data

Out

Latch

Data

In

Latch

Data

Interrupt

Latch

mode

2-bits

Control

Control

V

CC

Q1

14 kΩ

Q3*

Q2

*Port 0,1,2: Low I

Port 3: High I

sink

GPIO

PIN

sink

Figure 9-1. Block Diagram of a GPIO Pin

There are up to 31 GPIO pins (P0[7:0], P1[7:0], P2[7:0], and P3[6:0]) for the hardware interface. The number of GPIO pins

changes based on th e package type of the ch ip. Each port c an be confi gured as inp uts with intern al pull-up s, open drain outputs ,

or traditional CMOS outputs. Port 3 offers a higher current drive, with typical current sink capability of 12 mA. The data for each

GPIO port is accessible through the data registers. Port data registers are shown in Figure 9-2 through Figure 9-5, and are set

to 1 on reset.

Document #: 38-08024 Rev. ** Page 18 of 53

Page 19

CY7C66013

CY7C66113

7 6 5 4 3 2 1 0

P0[7] P0[6] P0[5] P0[4] P0[3] P0[2] P0[1] P0[0]

Figure 9-2. Port 0 Data 0x00 (read/write)

7 6 5 4 3 2 1 0

P1[7] P1[6] P1[5] P1[4] P1[3] P1[2] P1[1] P1[0]

Figure 9-3. Port 1 Data 0x01 (read/write)

7 6 5 4 3 2 1 0

P2[7] P2[6] P2[5] P2[4] P2[3] P2[2] P2[1] P2[0]

Figure 9-4. Port 2 Data 0x02 (read/write)

7 6 5 4 3 2 1 0

P3[7]

(see text)

P3[6] P3[5] P3[4] P3[3] P3[2] P3[1] P3[0]

Figure 9-5. Port 3 Data 0x03 (read/write)

Special care sho uld be ta ken w ith a ny un used GPIO data bits . An unu sed G PIO d ata bit , eithe r a pin on the c hip o r a port bit th at

is not bonded on a particular package, must not be left floating when the device enters the suspend state. If a GPIO data bit is

left floating, the leakage current caused by the floating bit may violate the suspend current limitation specified by the USB

specifications. If a ‘1’ is written to the unused data bit and the port is configured with open drain outputs, the unused data bit

remains in an indeterminate state. Therefore, if an unused port bit is programmed in open-drain mode, it must be written with a

‘0.’ Notice that the CY7C66 013 al ways req uires th at P3[7:5 ] be written with a ‘0.’ When the CY7C66113 is used the P3[7] should

be written with a ‘0.’

In normal non-HAPI mode, reads from a GPIO port always return the present state of the voltage at the pin, independent of the

settings in the Port Data Registers. If HAPI mode is activated for a port, reads of that port return latched data as controlled by

the HAPI signals (see Section 14.0). During reset, all of the GPIO pins are set to a high impedance input state (‘1’ in ope n drai n

mode). Writi ng a ‘0’ to a GPIO pin drives the pin LOW. In this state, a ‘0’ is always rea d on that GPI O pin unless an external

source overdrives the internal pull-down device.

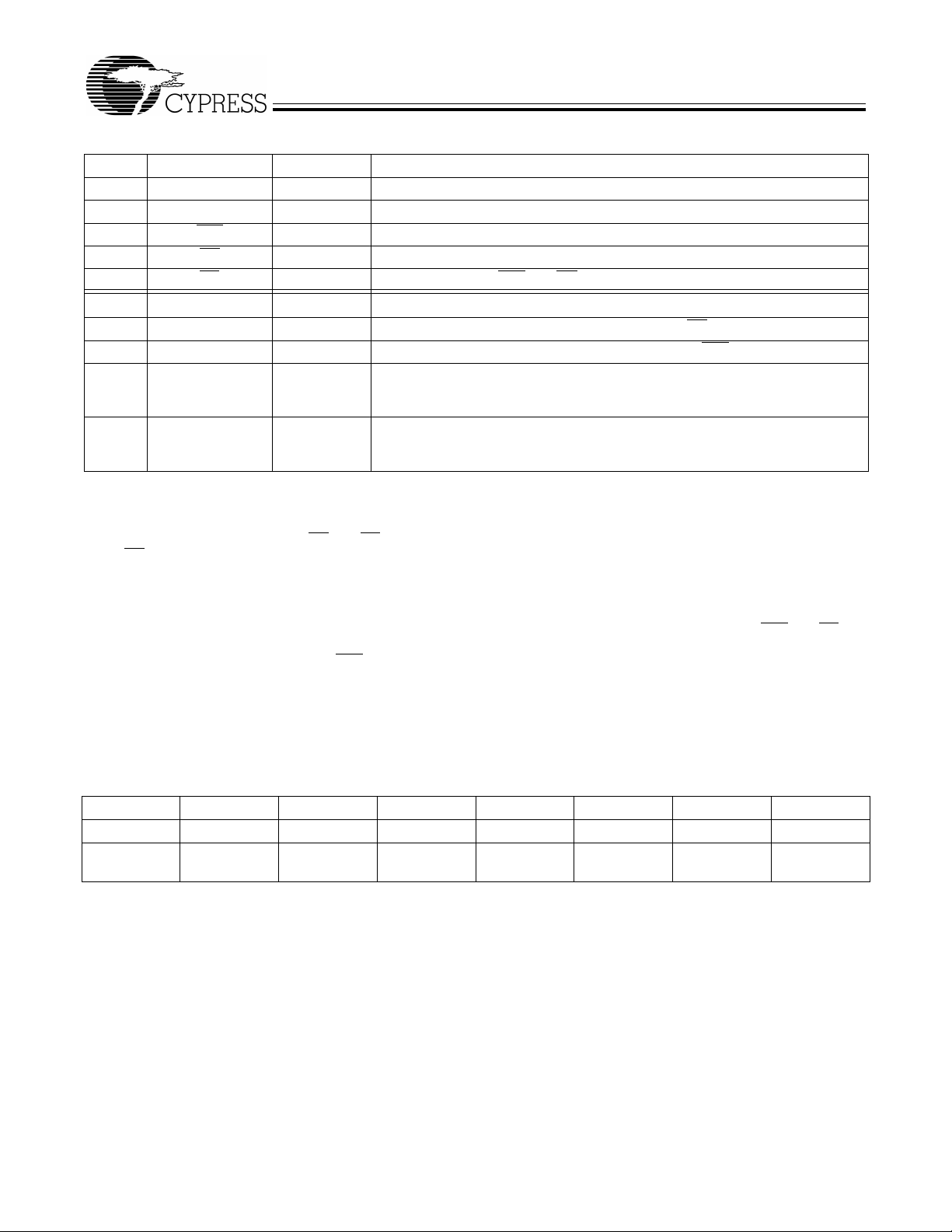

9.1 GPIO Configuration Port

Every GPIO port can be programmed as inputs with internal pull-ups, open drain outputs, and traditional CMOS outputs. In

addition, the interrupt polarity for each port can be programmed. With positive interrupt polarity, a rising edge (‘0’ to ‘1’) on an

input pin causes an interrup t. With n egativ e pola rity, a falli ng edge (‘1’ to ‘0’) on an inpu t pin c auses an int errupt. As sh own i n the

table below, when a GPIO po rt i s con figured with CMOS outputs, inte rrup ts from th at p ort are disabled. The GPIO Co nfi gura tio n

Port register provides two bits per port to program these features. The possible port configurations are detailed in Table 9-1:

Table 9-1. Port Configurations

Port Configuration bits Pin Interrupt Bit Driver Mode Interrupt Polarity

11 0 Resistive Disabled

1Resistive–

10 0 CMOS Output Disabled

1 Open Drain Disabled

01 0 Open Drain Disabled

1 Open Drain –

00

(Reset Stat e)

0 Open Drain Disabled (Default Condition)

1 Open Drain +

In “Resistive” mode, a 14-kΩ pull-up resistor is conditionally enable d for all pins of a GPIO port. An I/O pin is dri ven HIGH throug h

a 14-kΩ pull-up resistor when a ‘1’ ha s b een w rit ten to the pin. The output pin is driven LOW w ith the pu ll-up disabled when a ‘0’

has been written to the pi n. An I/O pin that has be en written as a ‘1’ can be used as an input pin with the integr ated 14-kΩ pull-u p

resistor. Resistive mode selects a negative (falling edge) interrupt polarity on all pins that have the GPIO interrupt enabled.

Document #: 38-08024 Rev. ** Page 19 of 53

Page 20

CY7C66013

CY7C66113

In “CMOS” mode, all pins of the GPIO port are outp uts that are ac tively driven. A C MOS port is no t a possible sou rce for interrupts .

In “Open Drain” mode, the internal pull-up resistor and CMOS driver (HIGH) are both disabled. An open drain I/O pin that has

been written as a ‘1’ can be used as an input or an open drain output. An I/O pin that has been written as a ‘0’ drives the output

low. The interrupt polarity for an open drain GPIO port can be selected as positive (rising edge) or negative (falling edge).

During reset, all of the bits in the GPIO Configuration Register are written with ‘0’ to select Open Drain output for all GPIO ports

as the default configuration.

7 6 5 4 3 2 1 0

Port 3

Config Bit 1

9.2 GPIO Interrupt Enable Ports

Each GPIO pin can be individually enabled or disabled as an interrupt source. The Port 0–3 Interrupt Enable registers provide

this feature with an interrupt enable bit for each GPIO pin. When HAPI mode (discussed in Section 14.0) is enabled the GPIO

interrupts are blocked, including ports not used by HAPI, so GPIO pins cannot be used as interrupt sources.

During a reset, GPIO interrupts are disabled by clearing all of the GPIO interrupt enable ports. Writing a ‘1’ to a GPIO Interrupt

Enable bit enables GPIO interrupts from the corresponding input pin. All GPIO pins share a common interrupt, as discussed in

Section 16.8.

Port 3

Config Bit 0

Port 2

Config Bit 1

Figure 9-6. GPIO Configuration Register 0x08 (read/write)

Port 2

Config Bit 0

Port 1

Config Bit 1

Port 1

Config Bit 0

Port 0

Config Bit 1

Port 0

Config Bit 0

7 6 5 4 3 2 1 0

P0[7] P0[6] P0[5] P0[4] P0[3] P0[2] P0[1] P0[0]

Figure 9-7. Port 0 Interrupt Enable 0x04 (write only)

7 6 5 4 3 2 1 0

P1[7] P1[6] P1[5] P1[4] P1[3] P1[2] P1[1] P1[0]

Figure 9-8. Port 1 Interrupt Enable 0x05 (write only)

7 6 5 4 3 2 1 0

P2[7] P2[6] P2[5] P2[4] P2[3] P2[2] P2[1] P2[0]

Figure 9-9. Port 2 Interrupt Enable 0x06 (write only)

7 6 5 4 3 2 1 0

reserved set to zero

P3[6] P3[5] P3[4] P3[3] P3[2] P3[1] P3[0]

Figure 9-10. Port 3 Interrupt Enable 0x07 (write only)

Document #: 38-08024 Rev. ** Page 20 of 53

Page 21

10.0 DAC Port

CY7C66013

CY7C66113

V

CC

Internal

Data Bus

Data

Out

Latch

DAC Write

Suspend

(Bit 3 of Register 0xFF)

Q1

14 kΩ

DAC

I/O Pin

4 bits

Isink

DAC

to Interrupt

Controller

Interrupt

Enable

Interrupt

Polarity

Internal

Buffer

DAC Read

Isink

Register

Interrupt Logic

Figure 10-1. Block Diagram of a DAC Pin

The CY7C661 13 feat ures a Digital to An alog Conversion (DAC) p ort which has prog rammable current sink on each I/O pin. Writing

a ‘1’ to a DAC I/O pin disables the output current sink (Isink DAC) and drives the I/O pin HIGH through an integrated 14-kΩ

resistor . When a ‘0’ is wr itten to a DAC I/O pin, th e Isink DAC is e nabled an d the pul l-up resi stor is d isabled. This ca uses the Isink

DAC to sink current to drive the output LOW. The amount of sink current for the DAC I/O pin is programmable over 16 values

based on the contents of the DAC Isink Register for that output pin. DAC[1:0] are high current outputs that are programmable

from 3.2 mA to 16 mA (typical). DAC[7:2] are low current outputs, programmable from 0.2 mA to 1.0 mA (typical).

When the suspend bit in Proces sor Status and Control Reg ister (0xFF) is set, the Isink D AC block of the DAC circuitry is disabled.

Special care should be t aken w he n the C Y7C 64 x1 3 dev ic e is pl ac ed in the sus pe nd. T he DA C Port D a ta R eg ist er(0 x30 ) sh oul d

normally be loaded with all ‘1’s (0xFF) before setting the suspend bit. If any of the DAC bits are set to ‘0’ when the device is

suspended, th at DAC input wil l float. The fl oating pin coul d result in exce ssive curre nt consumptio n by the device, unless an

external load places the pin in a deterministic state.

When a DAC I/O bit is writt en as a ‘1’, th e I/O pin is an outpu t pulle d HIGH through the 14-kΩ res istor or an input with an interna l

14-kΩ pull-up resistor. All DAC port data bits are set to ‘1’ during reset.

Low current outputs

0.2 mA to 1.0 mA typical

High current outputs

3.2 mA to 16 mA typical

7 6 5 4 3 2 1 0

DAC[7] DAC[6] DAC[5] DAC[4] DAC[3] DAC[2] DAC[1] DAC[0]

Figure 10-2. DAC Port Data 0x30 (read/write)

10.1 DAC Isink Registers

Each DAC I/O pin has an associated DAC Isink register to program the output sink current when the output is driven LOW. The

first Isink register (0x38 ) con trol s th e cu rrent for DA C[0], the second (0x39) for DAC[1], and so on unti l the Isi nk regis ter at 0x3 F

controls the current to D AC[7]. Writing all ‘0’s to the Isink register ca us es 1/5 of the max current to flow through the DAC I /O pin.

Writing all ‘1’s to the Isink register provide s the maximum current flow through the pin. The other 14 st ates of the DAC sink current

are evenly spaced between the se tw o val ues.

Isink Value

7 6 5 4 3 2 1 0

reserved reserved reserved reserved Isink[3] Isink[2] Isink[1] Isink[0]

Figure 10-3. DAC Port Isink 0x38 to 0x3F (write only)

Document #: 38-08024 Rev. ** Page 21 of 53

Page 22

CY7C66013

CY7C66113

10.2 DAC Port Interrupts

A DAC port interrupt can be enabled/disabled for each pin individually. The DAC Port Interrupt Enable register provides this

feature with an interrupt enable bit for each DAC I/O pin. Writing a ‘1’ to a bit in this register enables interrupts from the corresponding bit po sition . W riti ng a ‘0’ to a bit in the DAC Port Int errup t Enabl e regi ster di sable s int errupts from th e corre spond ing b it

position. All of th e DAC Port In terrupt Enable register bi ts are cleared to ‘0’ during a reset. Al l DAC pins share a com mon interrup t,

as explained in Section 16.7.

7 6 5 4 3 2 1 0

DAC[7] DAC[6] DAC[5] DAC[4] DAC[3] DAC[2] DAC[1] DAC[0]

Figure 10-4. DAC Port Interrupt Enable 0x31 (write only)

As an additional benefit, the interrupt polarity for each DAC pin is programmable with the DAC Port Interrupt Polarity register.

Writing a ‘0’ to a bit selects negative polarity (falling edge) that causes an interrupt (if enabled) if a falling edge transition occurs

on the correspond ing in put pin . Writing a ‘1’ to a bit i n th is reg is ter s el ec ts pos iti ve po lari ty (ris ing ed ge) that causes an interrupt

(if enabled) if a rising edge transition occurs on the corresponding input pin. All of the DAC Port Interrupt Polarity register bits

are cleared during a reset.

7 6 5 4 3 2 1 0

DAC[7] DAC[6] DAC[5] DAC[4] DAC[3] DAC[2] DAC[1] DAC[0]

Figure 10-5. DAC Port Interrupt Polarity 0x32 (write only)

11.0 12-Bit Free-Running Timer

The 12-bit timer provides two interrupts (128-µs and 1.024-ms) and allows the firmware to directly time events that are up to

4 ms in duration. The lower 8 bits of the timer can be read directly by the firmware. Reading the lower 8 bits latches the upper

4 bits into a temporary register. When the firmware reads the upper 4 bits of the timer, it is accessing the count stored in the

temporary register. The eff ect of this logic is to ensure a stable 12-bit tim er value can be re ad, even wh en the tw o reads ar e

separated in time.

11.1 Timer (LSB)

7 6 5 4 3 2 1 0

Timer

Bit 7

11.2 Timer (MSB)

7 6 5 4 3 2 1 0

Reserved Reserved Reserved Reserved Timer

Timer

Bit 6

Timer

Bit 5

Figure 11-1. Timer Register 0x24 (read only)

Figure 11-2. Timer Register 0x25 (read only)

Timer

Bit 4

Timer

Bit 3

Bit 11

Timer

Bit 2

Timer

Bit 10

Timer

Bit 1

Timer

Bit 9

Timer

Bit 0

Timer

Bit 8

Document #: 38-08024 Rev. ** Page 22 of 53

Page 23

CY7C66013

CY7C66113

1.024-ms Interrupt

128-

µs Interrupt

10 9 7856432

1 011

1-MHz Clock

L1 L0L2L3

D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

To Timer Register

8

Figure 11-3. Timer Block Diagram

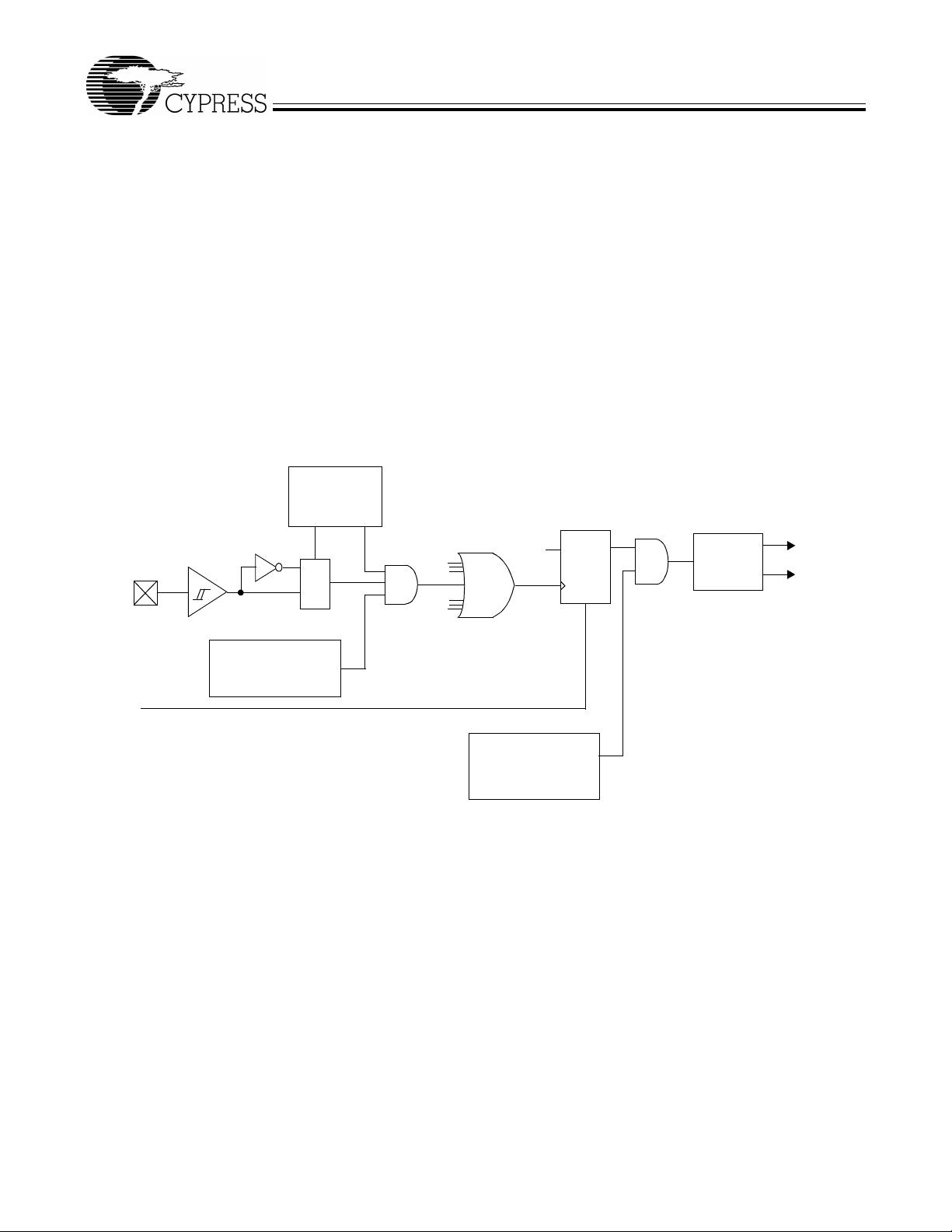

12.0 I2C and HAPI Configuration Register

Internal hardware suppo rts c om mu nic ati on with ex tern al de vi ce s through two interfaces: a two-wire I2C compatible, and a HAPI

for 1, 2, or 3 byte tra nsfers. The I

configuration registe r (see Figure 12-1 ). All bits of this register are cleared on reset.

7 6 5 4 3 2 1 0

R/W R/W R/W R R R/W R/W

I2C Position Reserved LEMPTY

Bits [7,1:0] of the HAPI/I

Bits [5:2] are used in HAPI mode only, and are described in Section 14.0. Table 12-1 shows the HAPI port configurations, and

Table 12-2 shows I

packages, and to allow simultaneous HAPI and I2C compatible operation.

HAPI operation is enabled whenever e ither HAP I Port W idth Bit ( Bit 1 or 0 ) is non -zero. Thi s af fects G PIO opera tion as describe d

in Section 14.0. The I

Table 12-1. HAPI Port Configuration

Table 12-2. I

I2C Position

2

C pin location configuration options. These I2C compatible options exist due to pin limitations in certain

2

C-compatible interface must be separately enabled as described in Section 13.0.

Port Width

Bits[1:0] HAPI Port Width

11 24 Bits: P3[7:0], P1[7:0], P0[7:0]

10 16 Bits: P1[7:0], P0[7:0]

01 8 Bits: P0[7:0]

00 No HAPI Interface

2

C Port Configuration

Bit[7]

X1I

00I

10I

2

C compatible and H API functions, dis cussed in detai l in Sections 13. 0 and 14.0, share a common

Polarity

Figure 12-1. HAPI/I2C Configuration Register 0x09 (read/write)

2

C Configuration Register control the pin out configuration of the HAPI and I2C compatible interfaces.

Port Width

DRDY

Polarity

Bit[1] I2C Positio n

Latch Empty Data Ready HAPI Port

2

C on P2[1:0], 0:SCL, 1:SDA

2

C on P1[1:0], 0:SCL, 1:SDA

2

C on P2[1:0], 0:SCL, 1:SDA

Width Bit 1

HAPI Port

Width Bit 0

Document #: 38-08024 Rev. ** Page 23 of 53

Page 24

13.0 I2C Compatible Controller

CY7C66013

CY7C66113

The I2C-compatible block provides a versatile two-wire communication with external devices, supporting master, slave, and

multi-master modes of operat ion. The I

interrupts as needed to allow firmware to take appropriate action during transactions. While waiting for firmware response, the

hardware keeps the I

2

C-compatible interface generates an interrupt to th e m ic roc ontr oll er at the end of each received or tra nsmi tted byte, when

The I

2

C-compatible bus idle if neces sar y.

2

C-compatible blo ck functio ns by handl ing the low- level sig naling in h ardware, and i ssuing

a stop bit is detected by the slave when in receive mode, or when arbitration is lost. Details of the interrupt responses are given

in Section 16.9.

2

C-compatible interfac e consists of two registers , an I2C Data Register (Figure 13-1) and an I2C Status and Control Register

The I

(Figure 13-2). The Data Register is implemented as separate read and write registers. Generally, the I

Register should only be monitored afte r the I

2

C interrupt, as all bits are valid at that time. Polling thi s register at oth er times could

2

C Status and Control

read misleading bit status if a transaction is underway.

2

C SCL clock is connected to bit 0 of GPIO port 1 or GPIO port 2, and the I2C SDA data is connected to bit 1 of GPIO port

The I

1 or GPIO port 2. Refer to Section 12.0 for the bit definitions and functionality of the HAPI/I2C Configuration Register, which is

used to set the locations of the co nfigurable I

Status & Control Register, the two LSB ([1:0]) of the corresponding GPIO port is placed in Open Drain mode, regardless of the

settings of the GPIO Configuration Register.The electrical characteristics of the I

GPIO ports 1 and 2. Note that the I

OL

2

C pins. Once the I2C-compatible func tio na lity is ena ble d by sett ing bit 0 of the I2C

(max) is 2 mA @ V

= 2.0V for ports 1 and 2.

OL

2

C-compatible interface is the same as that of

All control of the I2C clock and data lines is performed by the I2C compatible block.

7 6 5 4 3 2 1 0

I2C Data 7 I2C Data 6 I2C Data 5 I2C Data 4 I2C Data 3 I2C Data 2 I2C Data 1 I2C Data 0

Figure 13-1. I2C Data Register 0x29 (separate read/write registers)

7 6 5 4 3 2 1 0

R/W R/W R/W R/W R/W R/W R/W R/W

MSTR

Mode

Continue/

Busy

Xmit

Mode

ACK Addr ARB Lost/

Restart

Received

Stop

I2C

Enable

Figure 13-2. I2C Status and Control Register 0x28 (read/write)

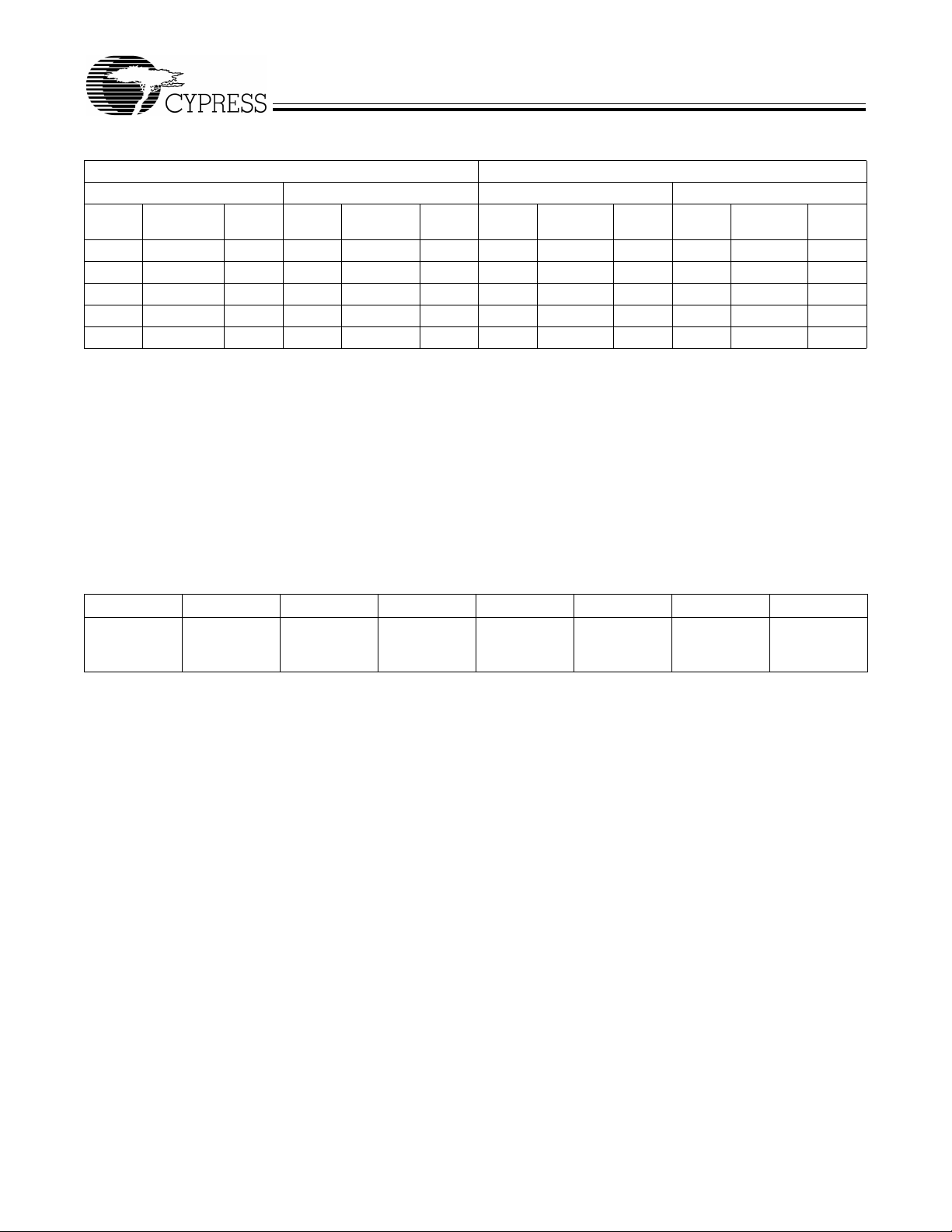

The I2C Status and Control register bits are defined in Table 13-1, with a more detailed description following.

Table 13-1. I

2

C Status and Control Register Bit Definitions

Bit Name Description

0I2C Enable Write to 1 to enable I2C-compatible function. When cleared, I2C GPIO pins operate

normally.

2

1 Received Stop Reads 1 only in slave re ceive mod e, when I

C Stop bit detected (unless firmw are did not

ACK the last transaction).

2 ARB Lost/Restart Reads 1 to indicate master has lost arbitration. Reads 0 otherwise.

Write to 1 in master mode to perform a restart sequence (also set Continue bit).

3 Addr Reads 1 during first byte after start/restart in slave mode, or if master loses arbitration.

Reads 0 otherwise. This bit should always be written as 0.

4 ACK In receive mode, write 1 to generate ACK, 0 for no ACK.

In transmit mode, reads 1 if ACK was received, 0 if no ACK received.

5 Xmit Mode Write to 1 for transmit mode, 0 for receive mode.

6 Continue/Busy Write 1 to indicate ready for next transaction.

Reads 1 when I

2

C-compatible block is busy with a transaction, 0 when transaction is

complete.

7 MSTR Mode Write to 1 for master mode, 0 for slave mo de. This bit is cleared if maste r loses arbitration.

Clearing from 1 to 0 generates Stop bit.

Document #: 38-08024 Rev. ** Page 24 of 53

Page 25

CY7C66013

CY7C66113

MSTR Mode: Setting this bit c au ses th e I2C to initiate a master m ode trans ac ti on b y s end ing a st art bit and transmitting the first

data byte from the data register (this typically holds the target address and R/W bit). Subsequent bytes are initiated by setting

the Continue bit, as described below.

2

In master mode, th e I

or receive sta te. The I2C-compatible block performs any required arbitration and clock synchronization. The loss of arbitration

results in the clearing of this bit, the setting of the ARB Lost bit, and the generation of an interrupt to the microcontroller. If the

chip is the target of an external master that wins arbitration, then the interrupt is held off until the transaction from the external

master is completed.

When MSTR Mode is cleared from 1 to 0 by a firmware write, an I

Continue/Busy: This bit i s wri tten by t he firm ware to indicate that the firmware is rea dy for the ne xt byte transaction to b egi n. In

other words, the bit has responded to an interrupt request and has completed the required update or read of the data register.

During a read this bit indicates if the hardware is busy and is locking out additional writes to the I

This locking allows the hardware to complete certain operations that may require an extended period of time. Following an I

interrupt, the I

2

to make one control register write without the need to check the Busy bit.

Xmit Mode: This bit is set by firmware to enter transmit mode and perform a data transmit in master or slave mode. Clear this

bit for receive mode. Firmware ge nerally determi nes the value of thi s bit from the R/W bit asso ciated with the I