Page 1

r

CY25818/19

Spread Spectrum Clock Generato

Features

• 8- to 32-MHz input frequency range

• CY25818: 8–16 MHz

• CY25819: 16–32 MHz

• Separate modulated and unmodulated clocks

• Accepts clock, crystal, and resonator inputs

• Down spread modulation

• Power-down function

• Low-power dissipation

— CY25818 = 33 mW-typ @ 8 MHz

— CY25818 = 56 mW-typ @ 16 MHz

— CY25819 = 36 mW-typ @ 16 MHz

Applications

• Printers and MFPs

• LCD panels and notebook PCs

• Digital copiers

•PDAs

• Automotive

• CD-ROM, VCD, and DVD

• Networking and LAN/WAN

•Scanners

•Modems

• Embedded digital systems

Benefits

— CY25819 = 63 mW-typ @ 32 MHz

• Low cycle-to-cycle jitter

— SSCLK = 250 ps-typ

— REFOUT = 275 ps-typ

• Peak electromagnetic interference (EMI) reduction by

8–16 dB

• Fast time to market

• Cost reduction

• Available in 8-pin (150-mil) SOIC package

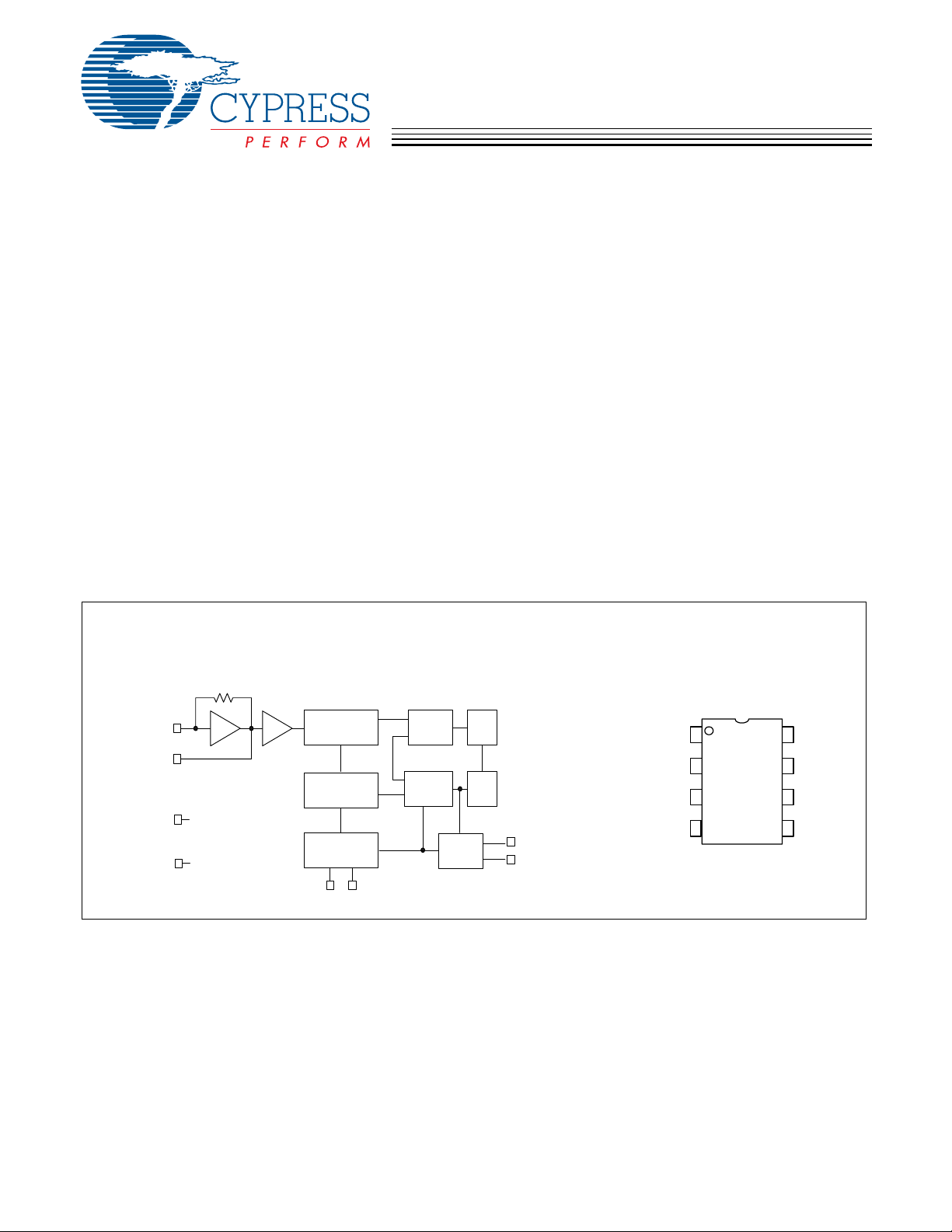

Block Diagram Pin Configuration

300K

XIN/CLKIN

XOUT

VDD

VSS

1

8

7

2

REFERENCE

DIVIDER

MODULATION

CONTROL

INPUT

DECODER

3 6

PD#

S0

PD and

CP

VCO

COUNTER

DIVIDER

and

MUX

LF

VCO

4

SSCLK

5

REFCLK

XIN/CLKIN

Vss

SSCLK

1

2

CY25818

CY25819

3

S0

4

8 Pin SOIC

8-pin SOIC

8

XOUT

7

Vdd

6

PD#

5

REFCLK

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document #: 38-07362 Rev. *B Revised April 11, 2006

[+] Feedback

Page 2

.

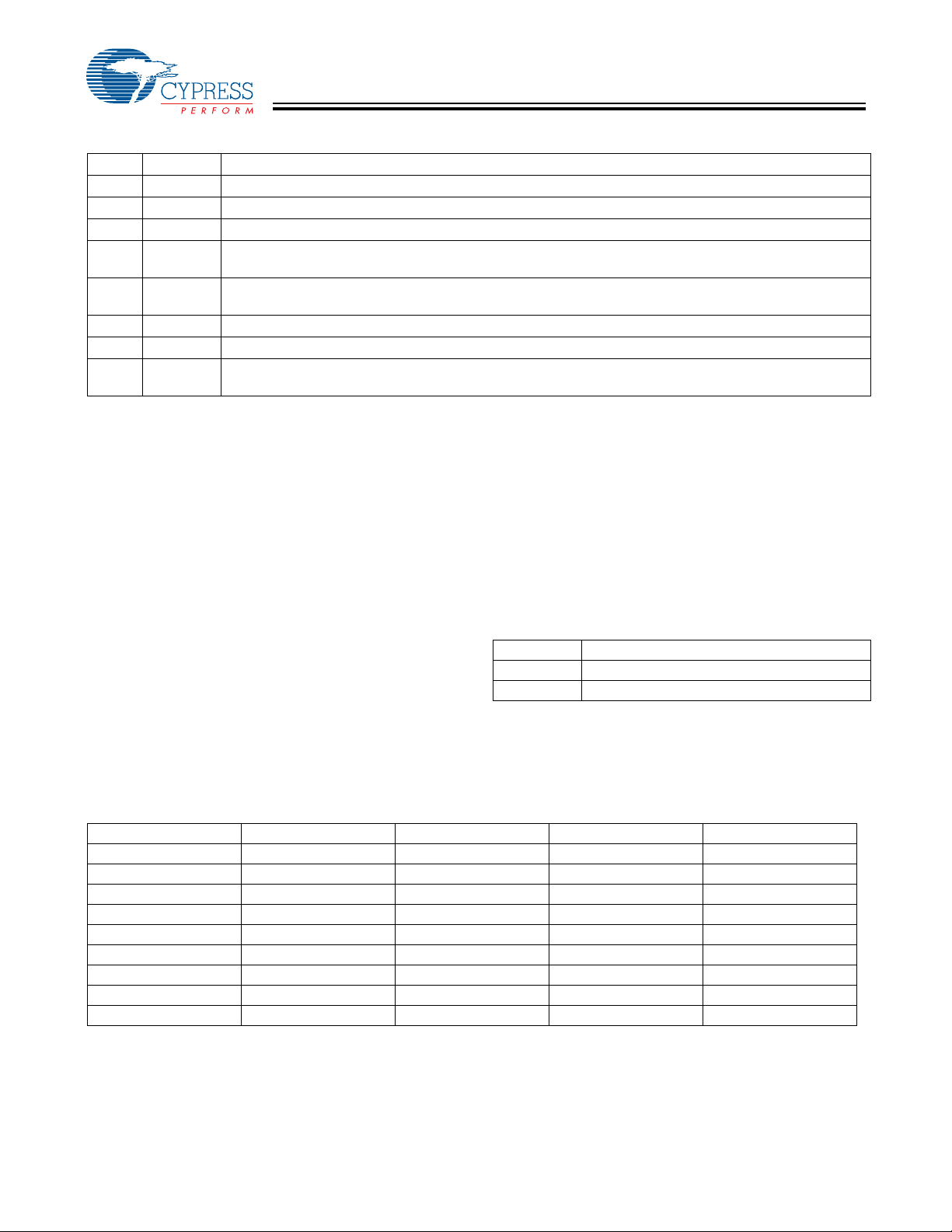

Pin Description

Pin Name Description

1 XIN/CLK Clock, Crystal, or Ceramic Resonator Input Pin.

2 Vss Power Supply Ground.

3 S0 Digital Spread% Control Pin. 3-Level input (H-M-L). Default = M.

4 SSCLK

5REFCLK

6 PD# Power-Down Control Pin. Default = H (Vdd).

7 Vdd Positive Power Supply.

8XOUT

Modulated Spread S pectrum Output Clock. The output frequency is referenced to input frequency . Refer

to Table 2 for the amount of modulation (Spread%).

Unmodulated Reference Clock Output. The unmodulate d output frequency is the same as the input

frequency.

Clock, Crystal, or Ceramic Resonator Output Pin. Leave this pin unconnected if an external clock is used

at X

pin.

IN

CY25818/19

Overview

The Cypress CY25818/19 products are Spread Spectrum

Clock Generator (SSCG) ICs used f or the purpose of re ducing

EMI found in today’s high-speed digital electronic systems.

The devices use a Cypress proprietary phase-locked loop

(PLL) and Spread Spectrum Clock (SSC) technology to

synthesize and modulate the frequency of the input clock. By

frequency modulating the clock, the measured EMI at the

fundamental and harmonic frequencies is greatly reduced.

This reduction in radiated energy can significantly reduce the

cost of complying with regulatory agency requirements and

improve time to market without degrading system performance.

The input frequency range is 8–16 MHz for the CY25818 and

16–32 MHz for the CY25819. Both products accept external

clock, crystal, or ceramic resonator inputs.

The CY25818/19 provide separate modulated (SSCLK) and

unmodulated reference (REFCLK) clock outputs which are the

same frequency as the input clock frequency. Down spread

frequency modulation can be selected by the user, based on

three discrete values of Spread%. A separate power down

function is also provided.

Table 2. Spread% Selection

XIN (MHz) Product S0 = 1 S0 = 0 S0 = M

Down (%) Down (%) Down (%)

8–10 CY25818 –3.0 –2.2 –0.7

10–12 CY25818 –2.7 –1.9 –0.6

12–14 CY25818 –2.5 –1.8 –0.6

14–16 CY25818 –2.3 –1.7 –0.5

16–20 CY25819 –3.0 –2.2 –0.7

20–24 CY25819 –2.7 –1.9 –0.6

24–28 CY25819 –2.5 –1.8 –0.6

28–32 CY25819 –2.3 –1.7 –0.5

The CY25818/19 products are available in an 8-pin SOIC

(150-mil) package with a commercial operating temperature

range of 0–70°C. Contact Cypress for availability of –40 to

+85°C industrial temperature range operation or TSSOP

package versions. Refer to the CY25568, CY25811,

CY25812, and CY25814 products for other functions such as

clock multiplication of 1×, 2×, or 4× to generate a wide range

of Spread Spectrum output clocks from 4 to 128 MHz.

Input Frequency Range and Selection

CY25818/19 input frequency range is 8–32 MHz. This range

is divided into two segments, as given in Table 1.

Table 1. Input and Output Frequency Selection

Product Input/Output Frequency Range

CY25818 8–16 MHz

CY25819 16–32 MHz

Spread% Selection

CY25818/19 SSCG products provide Down-Spread frequency

modulation. The amount of Spread% is selected by using

3-Level S0 digital input. Spread% values are given in Table 2.

Document #: 38-07362 Rev. *B Page 2 of 7

[+] Feedback

Page 3

CY25818/19

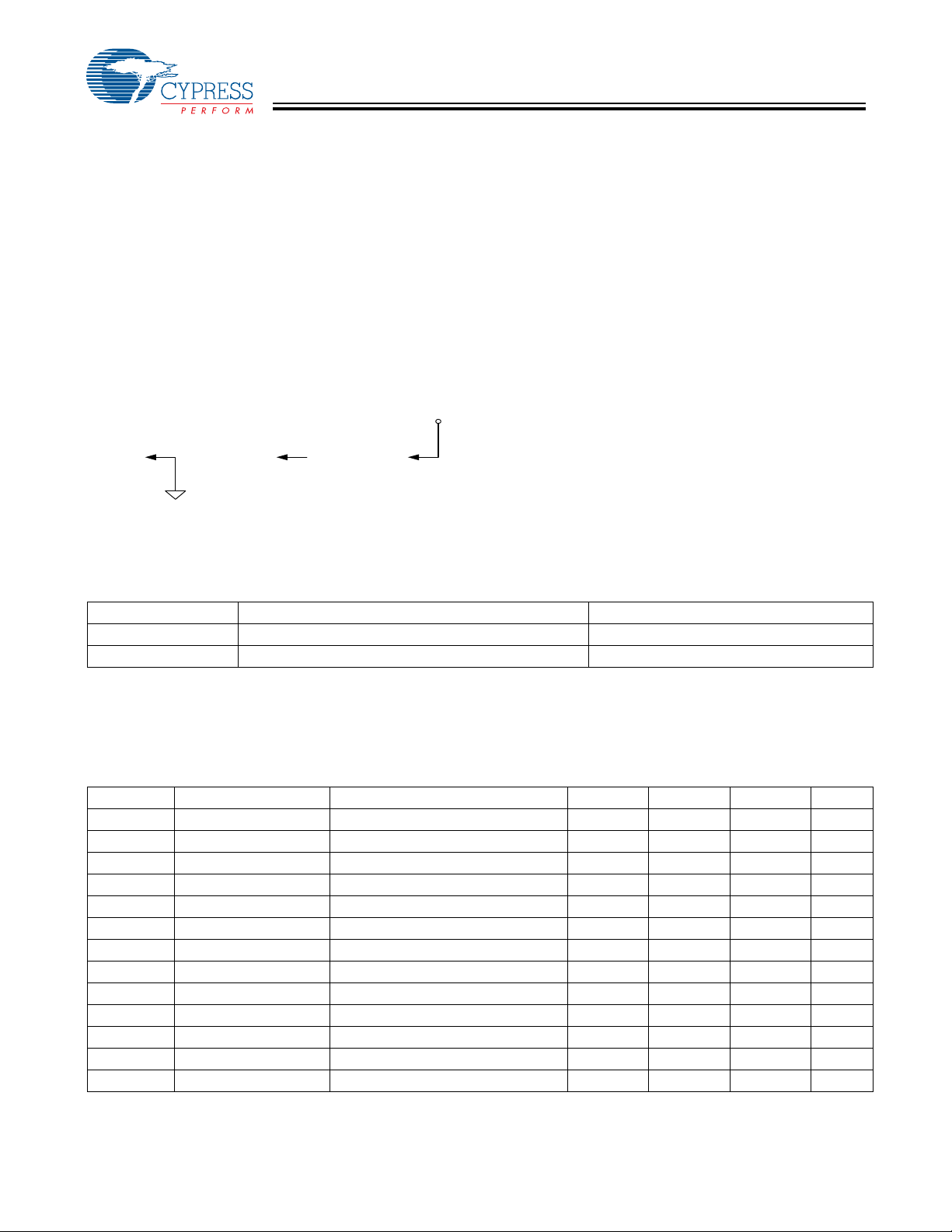

3-Level Digital Inputs

S0 digital input is designed to sense three logic levels desig nated as HIGH “1,” LOW “0,” and MIDDLE “M.” With this

3-Level digital input logic, the 3-Level logic is able to detect

three different logic levels .

The S0 pin includes an on-chip 20K (10K/10K) resistor divider.

No external application resistors are needed to implement

3-Level logic, as follows.

Logic Level “0”: 3-Level logic pin connected to GND.

Logic Level “M”: 3-Level logic pin left floating (no connection.)

Logic Level “1”: 3-Level logic pin connected to Vdd.

Figure 1 illustrates how to implement 3-Level Logic.

LOGIC

HIGH (H)

VDD

S0

to VDD

LOW (0)

S0

to V S S

LOGIC

LOGIC

MIDDLE (M)

S0

UNCONNECTED

VSS

Figure 1. 3-Level Logic

Modulation Rate

Spread Spectrum Clock Generators utilize frequency

modulation (FM) to distribute energy over a specific band of

frequencies. The maximum frequency of the clock (fmax) and

minimum frequency of the clock (fmin) determine this band of

frequencies. The time required to transition from fmin to fmax

and back to fmin is the period of the Modulation Rate, T mod.

The Modulation Rates of SSCG clocks are generally referred

to in terms of frequency, and fmod = 1/Tmod.

The input clock frequency, fin, and the internal divider

determine the Modulation Rate.

In the case of CY25818/19 devices, the (Spread Spectrum)

Modulation Rate, fmod, is given by the following formula:

fmod = f

where fmod is the Modulation Rate, fIN is the Input Frequency,

and DR is the Divider Ratio, as given in Table 3.

IN

/DR

Table 3. Modulation Rate Divider Ratios

Product Input Frequency Range Divider Ratio (DR)

CY25818 8–16 MHz 256

CY25819 16–32 MHz 512

Maximum Ratings

[1, 2]

Supply Voltage (Vdd):..................................................+ 5.5V

Input Voltage Relative to Vdd:..............................Vdd + 0.3V

Input Voltage Relati ve to Vss:............ ...................Vss + 0.3V

Operating Temperature:...................................0°C to + 70°C

Storage Temperature:................................ –65°C to + 150°C

Table 4. DC Electrical Characteristics Vdd = 3.3V ±10%, TA = 0°C to +70°C and CL = 15 pF (unless otherwise noted)

Parameter Description Conditions Min. Typ. Max. Unit

Vdd Power Supply Range 2.97 3.3 3.63 V

V

V

V

V

V

V

V

C

C

I

DD1

I

DD3

I

DD4

INH

INM

INL

OH1

OH2

OL1

OL2

IN1

IN2

Input HIGH Voltage S0 Input 0.85 Vdd Vdd Vdd V

Input MIDDLE Voltage S0 Input 0.40 Vdd 0.50 Vdd 0.60 Vdd V

Input LOW Voltage S0 Input 0.0 0.0 0.15 Vdd V

Output HIGH Voltage IOH = 4 ma, SSCLK and REFCLK 2.4 – – V

Output HIGH Voltage IOH = 6 ma, SSCLK and REFCLK 2.0 – – V

Output LOW Voltage IOL = 4 ma, SSCLK Output – – 0.4 V

Output LOW Voltage IOL = 10 ma, SSCLK Output – – 1.2 V

Input Capacitance XIN (Pin 1) and X

(Pin 8) 6.0 7.5 9.0 pF

OUT

Input Capacitance All Digital Inputs 3.5 4.5 6.0 pF

Power Supply Current FIN=8 MHz, no load – 10.0 12.5 mA

Power Supply Current FIN=32 MHz, no load – 19.0 23.0 mA

Power Supply Current PD# = Vss – 150 250 mA

Document #: 38-07362 Rev. *B Page 3 of 7

[+] Feedback

Page 4

)

CY25818/19

Table 5. Timing Electrical Characteristics Vdd = 3.3V ±10%, TA = 0°C to +70°C and CL = 15 pF (unless otherwise noted)

Parameter Description Conditions Min. Typ. Max. Unit

ICLKFR1 Input Frequency Range CY25818 8 – 16 MHz

ICLKFR2 Input Frequency Range CY25819 16 – 32 MHz

trise1 Clock Rise Time SSCLK and REFCLK, 0.4V to 2.4V 2.0 3.0 4.0 ns

tfall1 Clock Fall Time SSCLK and REFCLK, 0.4V to 2.4V 2.0 3 .0 4.0 ns

CDCin Input Clock Duty Cycle X

IN

CDCout Output Clock Duty Cycle SSCLK and REFCLK @ 1.5V 45 50 55 %

CCJss Cycle-to-Cycle Jitter SSCLK; F

CCJref Cycle-to-Cycle Jitter REFCLK; F

Characteristics Curves

The following curves demonstrate the characteristic behavior

of the CY25818/19 when tested over a number of environ mental and application specific parameters. These are typical

performance curves and are not meant to replace any

parameter specified in Table 4 and Table 5.

300

290

REFCLK CY25818

280

270

260

250

240

CCJ (ps)

230

SSCLK CY25818

220

210

200

8 121620242832

Frequency ( MHz )

Figure 2. CCJ (ps) vs. Frequency (MHz)

2.75

BW %

2.5

2.25

2

12 MHz

REFCLK CY25819

SSCLK CY25819

32 .0 MH z

IN

= F

IN

= 8–32 MHz 250 350 ps

OUT

= F

= 8–32 MHz 275 375 ps

OUT

20

19

CY25818

18

8 - 16 MH z

17

16

15

IDD(mA

14

13

12

11

10

8 1216 20242832

Figure 4. IDD (mA) vs. Frequency (MHz)

3.1

3

2.9

2.8

2.7

2.6

2.5

BW (%)

2.4

2.3

2.2

2.1

2

1.9

1.8

2.8 2.9 3 3.1 3.2 3 .3 3.4 3.5 3.6 3.7

20 50 80 %

CY25819

16 - 32 MH z

Frequency ( MHz )

CY25818@ 8.0 MHz

CY25819@ 32 M Hz

VDD (volts)

Figure 5. Bandwidth% vs. Vdd

1.75

-40 -25 -10 5 20 35 50 65 80 95 110 125

Temp (C)

Figure 3. Bandwidth% vs. Temperature

Notes:

1. Single Power Supply: The voltage on any input or I/O pin cannot exceed the power pin during power-up.

2. Operation at any Absolute Maximum Rating is not implied.

Document #: 38-07362 Rev. *B Page 4 of 7

[+] Feedback

Page 5

SSCG Profiles

CY25818/19 SSCG products use a non-linear “optimized”

frequency profile as shown in Figure 6 and Figure 7. The use

of Cypress proprietary “optimized” frequency profile maintains

flat energy distribution over the fundamental and higher order

harmonics. This results in additional EMI reduction in

electronic systems.

CY25818/19

Figure 6. CY25818 Spread Spectrum Profile

(Frequency vs. Time)

Application Schematic

C2

27 pF

C3

27 pF

14.3 MHz

or

27.0 MHz

[3]

1

8

XIN

XO UT

C3

7

Vdd

CY25818

CY25819

Figure 7. CY25819 Spread Spectrum Profile

(Frequency vs. Time)

Vdd

0.1 uF

SSCLK

REFCLK

4

14.3 MHz (CY25818)

5

27.0 MHz (CY25819)

[4]

6

PD#

3

S0

Vss

2

Figure 8. Typical Application Schematic

Notes:

3. X

= 16.0 MHz; S0 = 1; SSCLK = 16.0 MHz; BW = –2.14%.

IN

4. Xin = 32.0MHz; S0 = 1; SSCLK = 32.0 MHz; BW = -2.15%

Document #: 38-07362 Rev. *B Page 5 of 7

[+] Feedback

Page 6

Ordering Information

Part Number Package Type Product Flow

CY25818SC 8-pin SOIC Commercial, 0° to 70°C

CY25818SCT 8-pin SOIC–Tape and Reel Commercial, 0° to 70°C

CY25819SC 8-pin SOIC Commercial, 0° to 70°C

CY25819SCT 8-pin SOIC–Tape and Reel Commercial, 0° to 70°C

Lead-free

CY25818SXC 8-pin SOIC Commercial, 0° to 70°C

CY25818SXCT 8-pin SOIC–Tape and Reel Commercial, 0° to 70°C

CY25819SXC 8-pin SOIC Commercial, 0° to 70°C

CY25819SXCT 8-pin SOIC–Tape and Reel Commercial, 0° to 70°C

Package Drawing and Dimensions

8-lead (150-Mil) SOIC S8

8 Lead (150 Mil) SOIC - S08

PIN1ID

14

CY25818/19

0.050[1.270]

BSC

0.150[3.810]

0.157[3.987]

0.230[5.842]

0.244[6.197]

58

0.189[4.800]

0.196[4.978]

0.061[1.549]

0.068[1.727]

0.004[0.102]

0.0098[0.249]

0.0138[0.350]

0.0192[0.487]

0.004[0.102]

SEATING PLANE

0°~8°

1. DIMENSIONS IN INCHES[MM] MIN.

2. PIN1IDISOPTIONAL,

ROUND ON SINGLE LEADFRAME

RECTANGULAR ON MATRIX LEADFRAME

3. REFERENCE JEDEC MS-012

4. PACKAGE WEIGHT 0.07gms

S08.15 STANDARD PKG.

SZ08.15 LEAD FREE PKG.

PART #

0.016[0.406]

0.035[0.889]

MAX.

0.010[0.254]

0.016[0.406]

X 45°

0.0075[0.190]

0.0098[0.249]

All product and company names mentioned in this document may be the trademarks of their respective holders.

51-85066-*C

Document #: 38-07362 Rev. *B Page 6 of 7

© Cypress Semiconductor Corporation, 2006. The information contained herein is subject to ch an ge wi t hou t notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be

used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Fu rthermore, Cypre ss does not aut horize its

products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

[+] Feedback

Page 7

Document History Page

Document Title: CY25818/19 Spread Spectrum Clock Generator

Document Number: 38-07362

REV. ECN NO.

** 112462 03/21/02 OXC New Data Sheet

*A 122701 12/28/02 RBI Added power up requirements to maximum rating information.

*B 448097 See ECN RGL Add Lead-free devices

Issue

Date

Orig. of

Change Description of Change

CY25818/19

Document #: 38-07362 Rev. *B Page 7 of 7

[+] Feedback

Loading...

Loading...