Errata Revision: [**]

CY2305C

CY2309C

May 10, 2007

Errata Document for CY2305C, CY2309C Zero Delay Buffers

This document describes the errata for the Ze ro Delay Clock Buffers, CY2305C and CY2309C. Details include errat a

trigger conditions, scope of impact, available workarounds, and silicon revision applicability . Compare this document

to the device’s data sheet for a complete functional description.

Contact your local Cypress Sales Representative if you have questions.

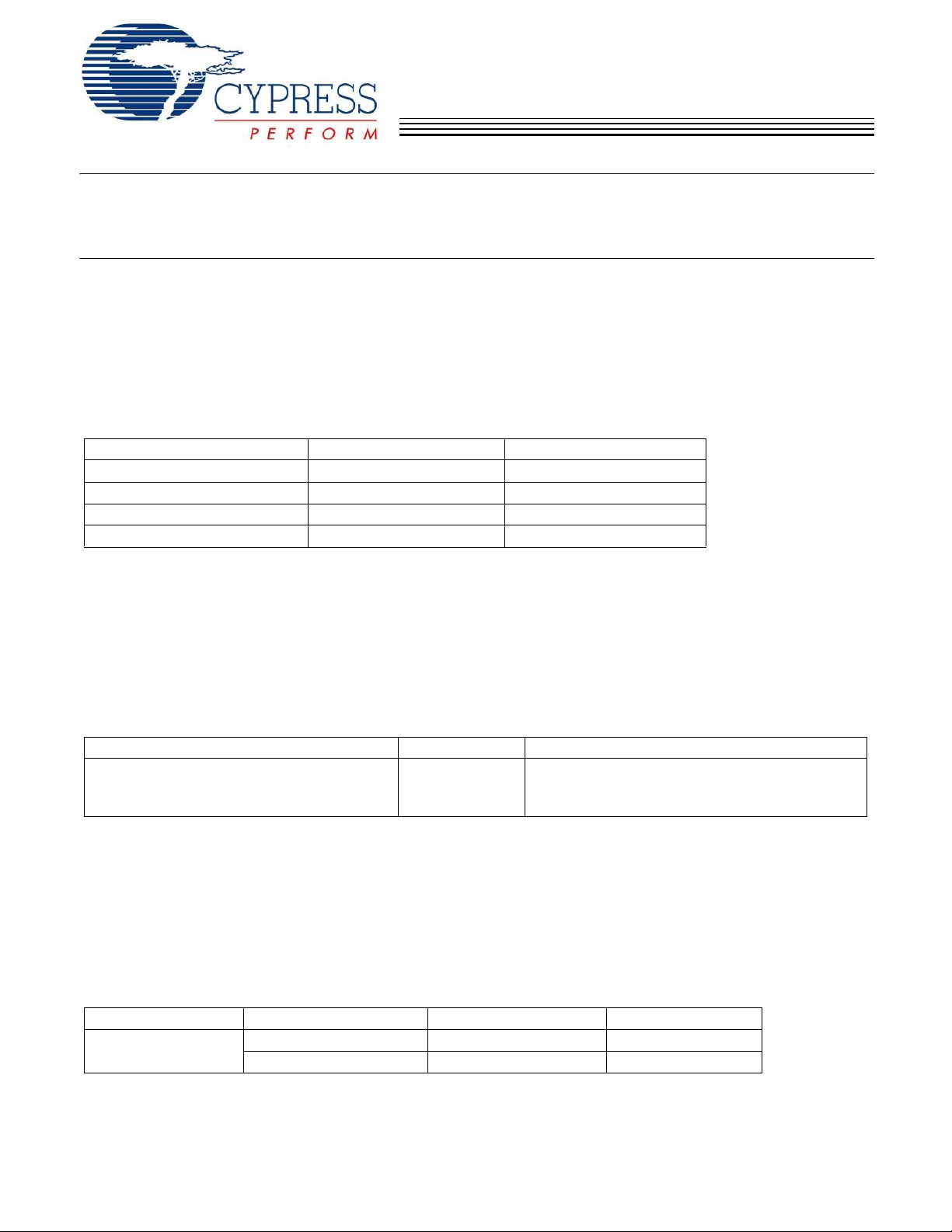

Part Numbers Affected

Part Number Temperature Grades Packages

CY2305C-1 all all

CY2305C-1H all all

CY2309C-1 all all

CY2309C-1H all all

Zero Delay Buffer Qualification Status

In Production

Zero Delay Buffer Errata Summary

The following table defines the errata applicability to available Zero Delay Buffer family devices.

Note Errata titles are hyperlinked. Click on the table item entry to jump to its description.

Items Part Numbers Fix Status

[1] Possible increased power down current All Will be corrected in the next silicon revision. The

errata is forecast to be corrected for all devices

dated October 2007 and later.

1. Possible increased power down current

• PROBLEM DEFINITION

When the device is in the power down state, an unbonded pad on the die is allowed to float. Because o f this,

power down current may exceed the data sheet limit.

While high current draw is theoretically possible any time d uring power down, it has only b een obse rved as a

transient occurrence shortly after the device enters power down. Steady-state current has always been ob

served to be within data sheet limits.

• PARAMETERS AFFECTED

Parameter Temperature Range Data Sheet Maximum Actual Maximum

IDD (PD Mode) Commercial 12 µA 3.5 mA

Industrial 25 µA 3.5 mA

• TRIGGER CONDITION(S)

None.

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134 • 408.943.2600

Document Number: 001-15585 Rev. ** Revised May 10, 2007

-

CY2305C

Errata Document

• SCOPE OF IMPACT

Possible increased power consum ption when in the power down s tate (that is, when the referenc e clock is

static).

• WORKAROUND

None.

• FIX STATUS

The silicon will be revised to correct this errata. The errata is forecast to be corrected for all devices dated

October 2007 and later.

References

[1] Document # 38-07672, CY2305C and CY2309C Zero Delay Buffer

Document Number: 001-15585 Rev. ** Page 2 of 3

© Cypress Semiconductor Corporation, 2007 . The i nf orma ti on con t a i ned he r ei n is subject to change without notice. Cypress Sem i conductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be

used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its

products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

CY2305C

Errata Document

Document History Page

Document Title: Errata Document for CY2305C, CY2309C Zero Delay Buffers

Document Number: 001-15585

REV. ECN NO.

** 1058882 See ECN KVM/

Issue

Date

Orig. of

Change Description of Change

Original release of spec.

KKVTMP

Document Number: 001-15585 Rev. ** Page 3 of 3

Loading...

Loading...