Three-PLL Serial-Programmable

Flash-Programmable Clock Generator

CY22395

CY22393

CY22394

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655

Features

• Three integrated phase-locked loops (PLLs)

• Ultra wide divide counters (8-bit Q, 11-bit P, and 7-bit post

divide)

• Improved linear crystal load capacitors

• Flash programmability with external programmer

• Field-programmable

• Low jitter, high accuracy outputs

• Power management options (Shutdown, OE, Suspend)

• Configurable crystal drive strength

• Frequency select via three external LVTTL inputs

• 3.3V operation

• 16-pin TSSOP package

• CyClocksRT™ software support

Advanced Features

•I2C serial interface for in-system configurability

• Configurable output buffer

• Digital VCXO

• High frequency LVPECL output (CY22394 only)

• 3.3/2.5V outputs (CY22395 only)

Benefits

• Generates up to three unique frequencies on up to six

outputs from an external source.

• Allows for 0 ppm frequency generation and frequency

conversion in the most demanding applications.

• Improves frequency accuracy over temperature, age,

process, and initial ppm offset.

• Nonvolatile programming enables easy customization,

ultra-fast turnaround, perfor mance tweaking, design timing

margin testing, inventory control, lower part count, and more

secure product supply. In addition, any part in the family can

be programmed multiple times, which reduces

programming errors and provides an easy upgrade path for

existing designs.

• In-house programming of samples and prototype quantities

is available using the CY3672 FTG Development Kit.

Production quantities are available through Cypress

Semiconductor’s value-added distribu tion partners or by

using third-party programmers from BP Microsystems, HiLo

Systems, and others.

• Performance suitable for high-end multimedia, communications, industrial, A/D converters, and consumer applications.

• Supports numerous low power application schemes and

reduces electromagnetic interference (EMI) by allowing

unused outputs to be turned off.

• Adjust crystal drive strength for compatibility with virtually

all crystals.

• 3-bit external frequency select options for PLL1, CLKA, and

CLKB.

• Industry standard packaging saves on board space.

• Easy to use software support for design entry.

2

•I

C interface allows in-system programming into volatile

configuration memory. All frequency settings can be

changed, providing literally millions of frequency options.

• Adjust output buffer strength to lower EMI or improve timing

margin.

• Fine tune crystal oscillator frequency by changing load

capacitance.

• Differential output up to 400 MHz.

• Provides interfacing option for low voltage parts.

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document #: 38-07186 Rev. *C Revised March 13, 2007

[+] Feedback [+] Feedback

CY22395

CY22394

CY22393

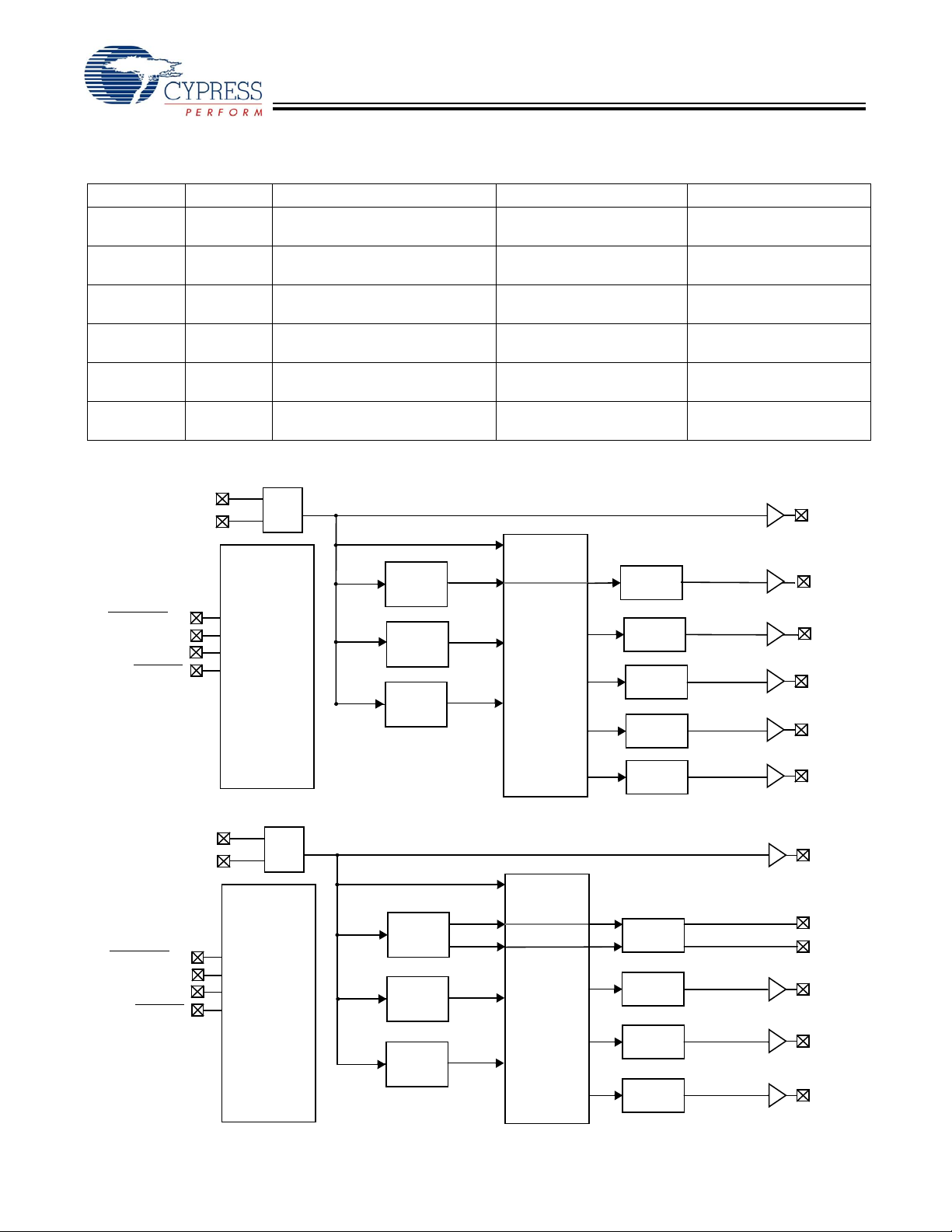

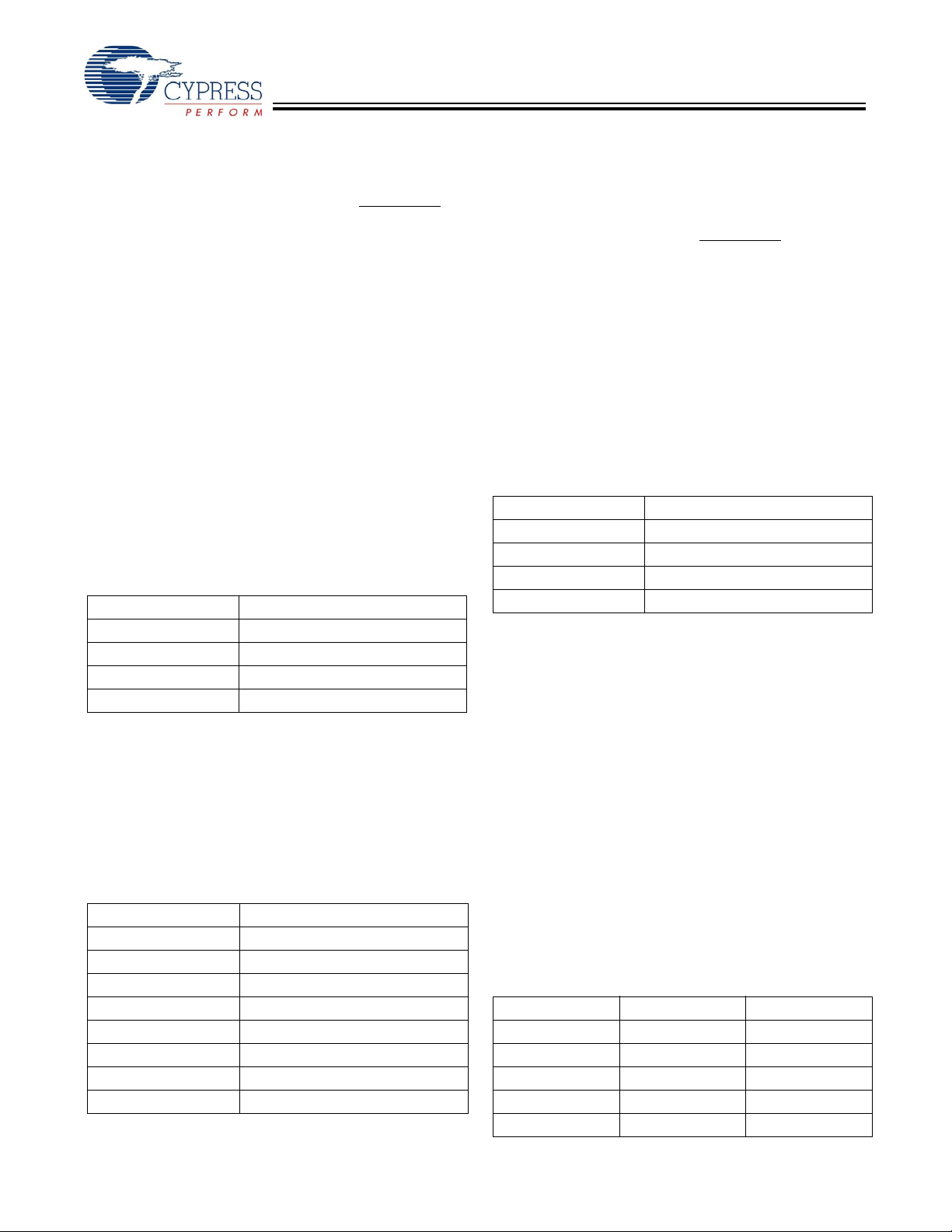

Logic Block Diagram — CY22393

XTALIN

XTALOUT

S2/SUSPEND

SDAT

SCLK

SHUTDOWN

/OE

CONFIGURATION

FLASH

OSC.

XBUF

PLL1

CLKE

11-Bit P

8-Bit Q

PLL2

11-Bit P

8-Bit Q

PLL3

11-Bit P

8-Bit Q

4x4

Switch

Crosspoint

Divider

/2, /3, or /4

Divider

7-Bit

Divider

7-Bit

Divider

7-Bit

Divider

7-Bit

CLKA

CLKB

CLKC

CLKD

Logic Block Diagram — CY22394

XTALIN

XTALOUT

S2/SUSPEND

SDAT

SCLK

SHUTDOWN

/OE

CONFIGURATION

FLASH

OSC.

XBUF

PLL1

P+CLK

11-Bit P

8-Bit Q

PLL2

11-Bit P

8-Bit Q

PLL3

11-Bit P

8-Bit Q

4x4

Switch

Crosspoint

Divider

7-Bit

Divider

7-Bit

Divider

7-Bit

PECL

OUTPUT

CLKA

CLKB

CLKC

P-CLK

0º

180º

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655

Selector Guide

Part Number Outputs Input Frequency Range Output Frequency Range Specifics

CY22393FC 6 CMOS 8 MHz–30 MHz (external crystal)

1 MHz–166 MHz (reference clock)

CY22393FI 6 CMOS 8 MHz–30 MHz (external crystal)

1 MHz–150 MHz (reference clock)

CY22394FC 1 PECL/

4 CMOS

CY22394FI 1 PECL/

4 CMOS

CY22395FC 4 LVCMOS/

1 CMOS

CY22395FI 4 LVCMOS/

1 CMOS

8 MHz–30 MHz (external crystal)

1 MHz–166 MHz (reference clock)

8 MHz–30 MHz (external crystal)

1 MHz–150 MHz (reference clock)

8 MHz–30 MHz (external crystal)

1 MHz–166 MHz (reference clock)

8 MHz–30 MHz (external crystal)

1 MHz–150 MHz (reference clock)

Up to 200 MHz Commercial Temperature

Up to 166 MHz Industrial Temperature

100 MHz–400 MHz (PECL)

Commercial Temperature

Up to 200 MHz (CMOS)

125 MHz–375 MHz (PECL)

Industrial Temperature

Up to 166 MHz (CMOS)

Up to 200 MHz (3.3V)

Commercial Temperature

Up to 133 MHz (2.5V)

Up to 166 MHz (3.3V)

Industrial Temperature

Up to 133 MHz (2.5V)

Document #: 38-07186 Rev. *C Page 2 of 17

[+] Feedback [+] Feedback

CY22395

CY22394

CY22393

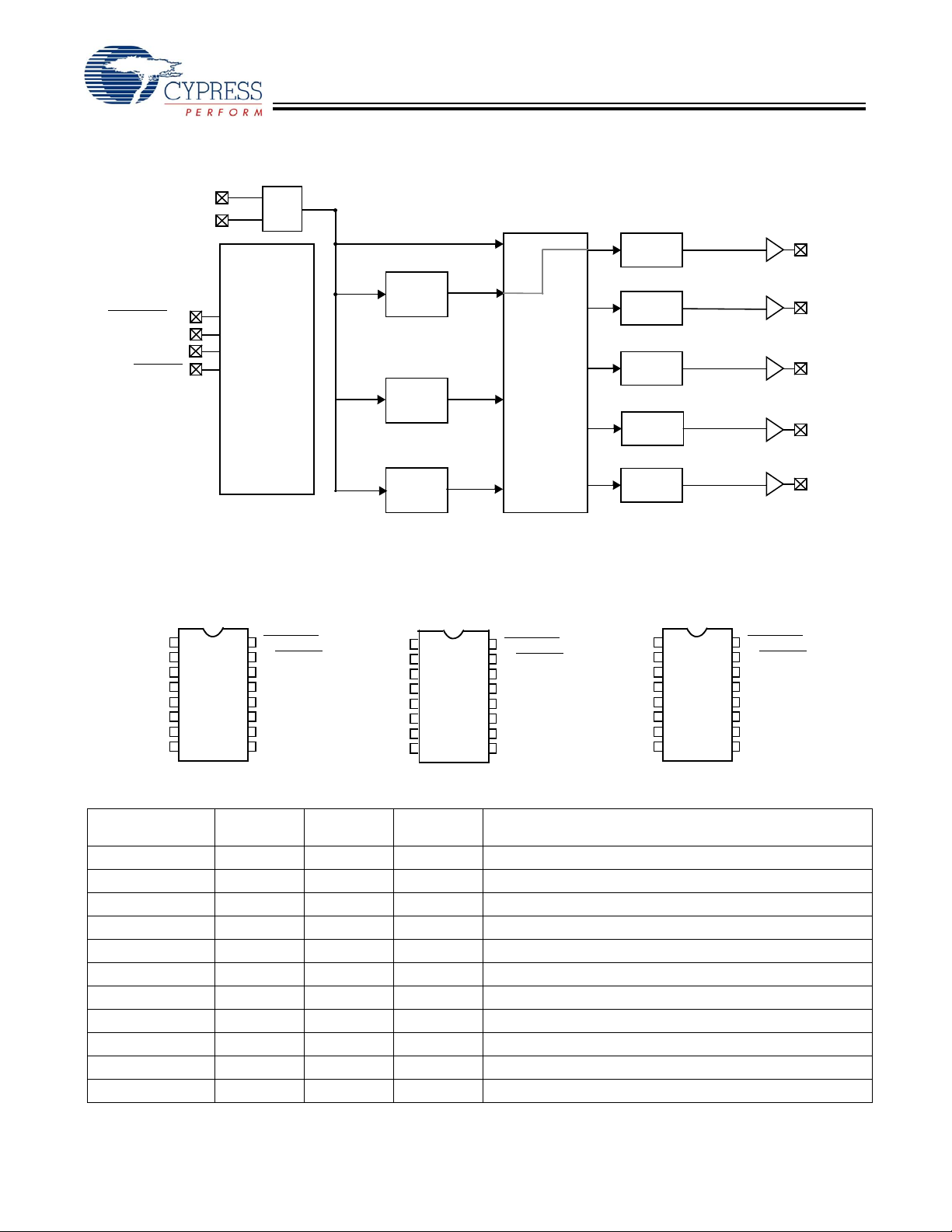

Logic Block Diagram — CY22395

XTALIN

XTALOUT

S2/SUSPEND

SDAT

SCLK

SHUTDOWN

/OE

CONFIGURATION

FLASH

OSC.

PLL1

LCLKE

11-Bit P

8-Bit Q

PLL2

11-Bit P

8-Bit Q

PLL3

11-Bit P

8-Bit Q

4x4

Switch

Crosspoint

Divider

7-Bit

Divider

7-Bit

Divider

7-Bit

Divider

7-Bit

Divider

/2, /3, or /4

LCLKA

LCLKB

CLKC

LCLKD

LCLKA, LCLKB, LCLKD, LCLKE referenced to LVDD

Pin Configurations

1

2

3

4

5

6

7

8

9

10

CLKC

V

DD

AGND

XTALIN

XTALOUT

XBUF

CLKD

CLKE

SHUTDOWN/OE

S2/SUSPEND

AV

DD

SCLK (S1)

SDAT (S0)

GND

CLKA

CLKB

16-pin TSSOP

11

12

13

14

15

16

CY22393

1

2

3

4

5

6

7

8

9

10

CLKC

V

DD

AGND

XTALIN

XTALOUT

XBUF

P–CLK

P+ CLK

SHUTDOWN/OE

S2/SUSPEND

AV

DD

SCLK (S1)

SDAT (S0)

GND

CLKA

CLKB

16-pin TSSOP

11

12

13

14

15

16

CY22394

1

2

3

4

5

6

7

8

9

10

CLKC

V

DD

AGND

XTALIN

XTALOUT

LCLKD

LCLKE

SHUTDOWN/OE

S2/SUSPEND

AV

DD

SCLK (S1)

SDAT (S0)

GND/LGND

LCLKA

LCLKB

16-pin TSSOP

11

12

13

14

15

16

CY22395

LV

DD

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655

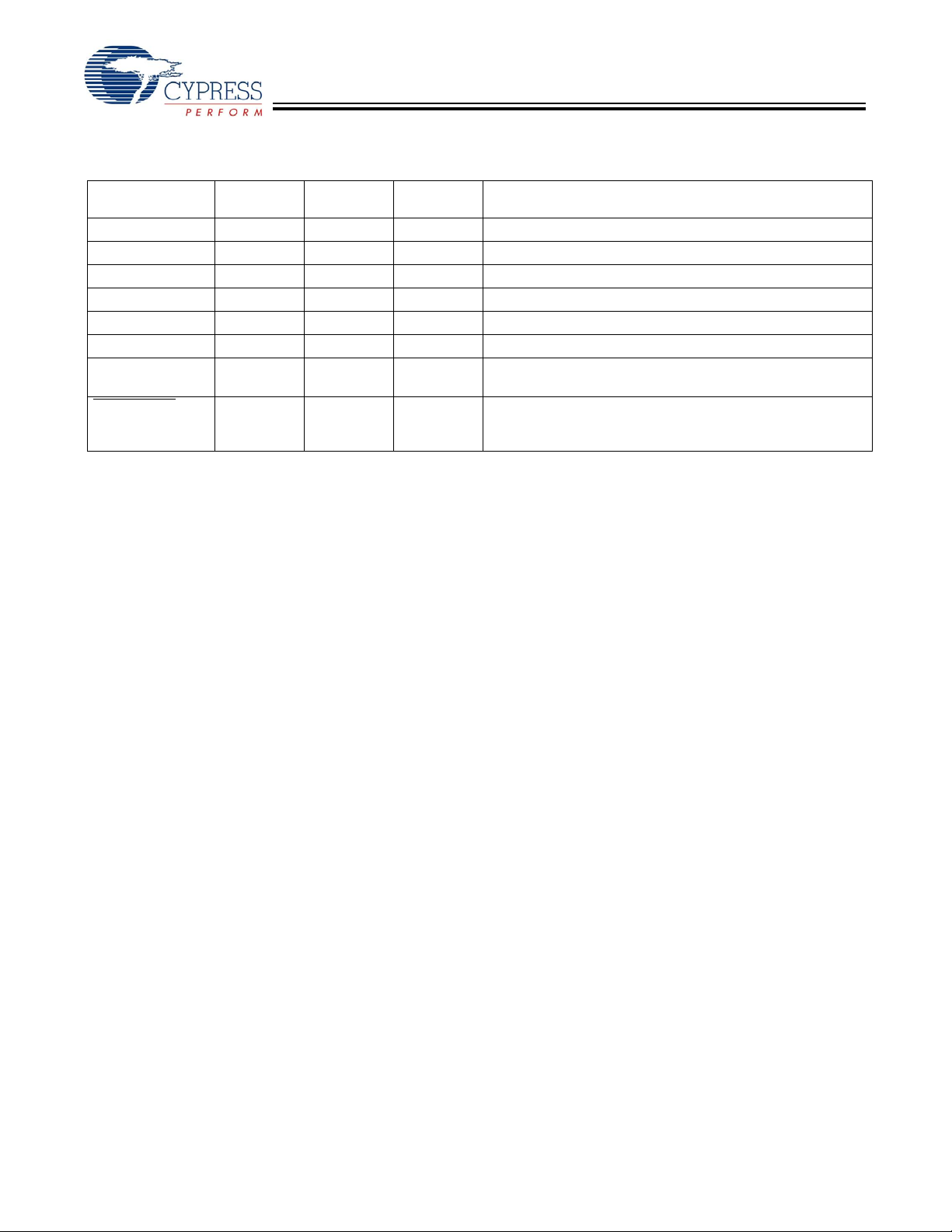

Pin Definitions

Name

CLKC 1 1 1 Configurable clock output C

V

DD

AGND 3 3 3 Analog Ground

XTALIN 4 4 4 Reference crystal input or external reference clock input

XTALOUT 5 5 5 Reference crystal feedback

XBUF 6 6 N/A Buffered reference clock output

LV

DD

CLKD or LCLKD 7 N/A 7 Configurable clock output D; LCLKD referenced to LVDD

P– CLK N/A 7 N/A LV PECL output

CLKE or LCLKE 8 N/A 8 Configurable clock output E; LCLKE referenced to LVDD

P+ CLK N/A 8 N/A LV PECL output

Note

Document #: 38-07186 Rev. *C Page 3 of 17

1. LVPECL outputs requir e an external termination network.

Pin Number

CY22393

2 2 2 Power supply

N/A N/A 6 Low voltage clock output power supply

Pin Number

CY22394

Pin Number

CY22395

Description

[1]

[1]

[+] Feedback [+] Feedback

CY22395

CY22394

Pin Definitions (continued)

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655

CY22393

Name

CLKB or LCLKB 9 9 9 Configurable clock output B; LCLKB referenced to LVDD

CLKA or LCLKA 10 10 10 Configurable clock output A; LCLKA referenced to LVDD

GND/LGND 11 11 11 Ground

SDAT (S0) 12 12 12 Serial Port (I2C) Data. S0 value latched during start up

SCLK (S1) 13 13 13 Serial Port (I2C) Clock. S1 value latched during start up

AV

DD

S2/

SUSPEND

SHUTDOWN/

OE

Pin Number

CY22393

14 14 14 Analog Power Supply

15 15 15 General purpose input for frequency control; bit 2. Optionally,

16 16 16 Places outputs in tri-state condition and shuts down chip when

Operation

The CY22393, CY22394, and CY22395 are a family of parts

designed as upgrades to the existing CY22392 device. These

parts have similar performance to the CY22392, but provide

advanced features to meet the needs of more demanding

applications.

The clock family has three PLLs which, when combi ned with

the reference, allow up to four independent frequencies to be

output on up to six pins. These three PLLs are completely

programmable.

Configurable PLLs

PLL1 generates a frequency that is equal to the reference

divided by an 8-bit divider (Q) and multiplied by an 11-bit

divider in the PLL feedback loop (P). The output of PLL1 is sent

to two locations: the cross point switch and the PECL output

(CY22394). The output of PLL1 is also sent to a /2, /3, or /4

synchronous post-divider that is output through CLKE. The

frequency of PLL1 can be changed using serial programming

or by external CMOS inputs, S0, S1, and S2. See the following

section on General Purpose Inputs for more detail.

PLL2 generates a frequency that is equal to the reference

divided by an 8-bit divider (Q) and multiplied by an 11-bit

divider in the PLL feedback loop (P). The output of PLL2 is sent

to the cross point switch. The frequency of PLL2 is changed

using serial programming.

PLL3 generates a frequency that is equal to the reference

divided by an 8-bit divider (Q) and multiplied by an 11-bit

divider in the PLL feedback loop (P). The output of PLL3 is sent

to the cross point switch. The frequency of PLL3 is changed

using serial programming.

General Purpose Inputs

S2 is a general purpose input that is programmed to allow for

two different frequency settings. Options that switches with

this general purpose input are as follows: the frequency of

PLL1, the output divider of CLKB, and the output divi der of

CLKA.

Pin Number

CY22394

Pin Number

CY22395

Description

Suspend mode control input

LOW. Optionally , only places outputs in tri-state condition and

does not shut down chip when LOW

The two frequency settings are contained within an eight-row

frequency table. The values of SCLK (S1) and SDAT (S0) pins

are latched during start up and used as the other two indexes

into this array.

CLKA and CLKB have seven-bit dividers that point to one of

the two programmable settings (register 0 and register 1). Both

clocks share a single register control and both must be set to

register 0, or both must be set to register 1.

For example, the part may be programmed to use S0, S1, and

S2 (0,0,0 to 1,1,1) to control eight different values of P and Q

on PLL1. For each PLL1 P and Q setting, one of the two CLKA

and CLKB divider registers can be chosen. Any divider change

as a result of switching S0, S1, or S2 is guaranteed to be glitch

free.

Crystal Input

The input crystal oscillator is an important feature of this family

of parts because of its flexibility and performance features.

The oscillator inverter has programmable drive strength. This

allows for maximum compatibility with crystals from various

manufacturers, process, performance, and quality.

The input load capacitors are placed on-die to reduce external

component cost. These capacitors are true parallel-plate

capacitors for ultra-linear performance. These were chosen to

reduce the frequency shift that occurs when nonlinear load

capacitance interacts with load, bias, supply, and temperature

changes. Nonlinear (FET gate) crystal load capacitors should

not be used for MPEG, POTS dial tone, co mmunications, or

other applications that are sensitive to absolute frequency

requirements.

The value of the load capacitors is determined by six bits in a

programmable register. The load capacitance can be set with

a resolution of 0.375 pF for a total crystal load range of 6 pF

to 30 pF.

For driven clock inputs, the input load capacitors can be

completely bypassed. This allows the clock chip to accept

driven frequency inputs up to 166 MHz. If the application

requires a driven input, leave XTALOUT floating.

Document #: 38-07186 Rev. *C Page 4 of 17

[+] Feedback [+] Feedback

CY22395

CY22394

CY22393

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655

Digital VCXO

The serial programming interface is used to dynamically

change the capacitor load value on the crystal. A change in

crystal load capacitance corresponds with a change in the

reference frequency.

For special pullable crystals specified by Cypress, the capacitance pull range is +150 ppm to –150 ppm from midrange.

Be aware that adjusting the frequency of the reference affects

all frequencies on all PLLs in a similar manner since all

frequencies are derived from the single refe re nce .

Output Configuration

Under normal operation there are four internal frequency

sources that are routed via a programmable cross point switch

to any of the four programmable 7-bit output dividers. The four

sources are: reference, PLL1, PLL2, and PLL3. The following

is a description of each output.

CLKA’ s output originates from the cross point switch and goes

through a programmable 7-bit post divider. The 7-bit post

divider derives its value from one of the two programmable

registers. See the section on “General Purpose Inputs” on

page 4 for more information.

CLKB’s output originates from the cross point switch and goes

through a programmable 7-bit post divider. The 7-bit post

divider derives its value from one of the two programmable

registers. See the section on “General Purpose Inputs” on

page 4 for more information.

CLKC’s output originates from the cross point switch and goes

through a programmable 7-bit post divider. The 7-bit post

divider derives its value from one programmable register.

CLKD’s output originates from the cross point switch and goes

through a programmable 7-bit post divider. The 7-bit post

divider derives its value from one programmable register. For

the CY22394, CLKD is brought out as the complimentary

version of a LV PECL Clock referenced to CLKE, bypassing

both the cross point switch and 7-bit post divider.

CLKE’s output originates from PLL1 and goes through a post

divider that may be programmed to /2, /3, or /4. For the

CY22394, CLKE is brought out as a low voltage PECL Clock,

bypassing the post divider.

XBUF is the buffered reference.

The Clock outputs have been designed to drive a single point

load with a total lumped load capacitance of 15 pF. While

driving multiple loads is possible with the proper termination it

is generally not recommended.

Power-Saving Features

The SHUTDOWN

LOW. If system shutdown is enabled, a LOW on this pin also

shuts off the PLLs, counters, reference oscillator, and all other

active components. The resulting current on the V

less than 5 mA (typical). Relock the PLLs after leaving

shutdown mode.

The S2/SUSPEND

izable set of outputs and/or PLLs, when LOW. All PLLs and

any of the outputs are shut off in nearly any combination. The

only limitation is that if a PLL is shut off, all outputs derived from

it must also be shut off. Suspending a PLL shuts off all

/OE input tri-states the outputs when pulled

pins is

DD

input is configured to shut down a custom-

associated logic, while suspending an output simply forces a

tri-state condition.

With the serial interface, each PLL and/or output is individually

disabled. This provides total control over the power savings.

Improving Jitter

Jitter Optimization Control is useful for mitigating problems

related to similar clocks switching at the same moment,

causing excess jitter. If one PLL is driving more than one

output, the negative phase of the PLL can be selected for one

of the outputs (CLKA–CLKD). This prevents the output edges

from aligning, allowing superior jitter performance.

Power Supply Sequencing

For parts with multiple V

sequencing requirements. The part is not fully operational until

all VDD pins have been brought up to the voltages specified in

the Operating Conditions[2] Table on page 12.

All grounds should be connected to the same ground plane.

pins, there are no power supply

DD

CyClocksRT Software

CyClocksRT is our second generation software application

that allows users to configure this family of devices. The

easy-to-use interface offers complete control of the many

features of this family including, but not limited to, input

frequency, PLL and output frequencies, and different

functional options. It checks data sheet frequency range limitations and automatically applies performance tuning.

CyClocksRT also has a power estimation feature that allows

the user to see the power consumption of a specific configuration. You can download a free copy of CyberClocks that

includes CyClocksRT for free on Cypress’s web site at

www.cypress.com.

CyClocksRT is used to generate P, Q, and divider values used

in serial programming. There are many internal frequency

rules that are not documented in this data sheet, but are

required for proper operation of the device. Check these rules

by using the latest version of CyClocksRT.

Junction Temperature Limitations

It is possible to program this family such that the maximum

Junction Temperature rating is exceeded. The package θ

115°C/W. Use the CyClocksRT power estimation feature to

verify that the programmed configuration meets the Junction

Temperature and Package Power Dissipation maximum

ratings.

Dynamic Updates

The output divider registers are not synchronized with the

output clocks. Changing the divider value of an active output

will likely cause a glitch on that output.

PLL P and Q data is spread between three bytes. Each byte

becomes active on the acknowledge for that byte, so changing

P and Q data for an active PLL will likely cause the PLL to try

to lock on an out-of-bounds condition. For this reason, turn off

the PLL being programmed during the update. Do this by

setting the PLL*_En bit LOW.

PLL1, CLKA, and CLKB each have multiple registers

supplying data. To program these resources safely, always

JA

is

Document #: 38-07186 Rev. *C Page 5 of 17

[+] Feedback [+] Feedback

CY22395

CY22394

CY22393

F

PLLFREF

P

T

Q

T

------ -

⎝⎠

⎛⎞

×=

P

T

2P3+()×()PO+=

Q

T

Q2+=

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655

program an inactive register, and then transition to that

register. This allows these resources to stay active during

programming.

The serial interface is active even with the SHUTDOWN

pin LOW as the serial interface logic uses static components

and is completely self timed. The part will not meet the I

current limit with transitioning inputs.

Memory Bitmap Definitions

Clk{A–D}_Div[6:0]

Each of the four main output clocks (CLKA–CLKD) features a

7-bit linear output divider. Any divider setting between 1 and

127 may be used by programming the value of the desired

divider into this register. Odd divide values are automatically

duty cycle corrected. Setting a divide value of zero powers

down the divider and forces the output to a tri-state condition.

CLKA and CLKB have two divider registers, selected by the

DivSel bit (which in turn is selected by S2, S1, and S0). This

allows the output divider value to change dynamically. For the

CY22394 device, ClkD_Div = 000001.

ClkE_Div[1:0]

CLKE has a simpler divider (see Table 1).

set ClkE_Div = 01.

Table 1.

ClkE_Div[1:0] ClkE Output

00 Off

01 PLL1 0° Phase/4

10 PLL1 0° Phase/2

11 PLL1 0° Phase/3

Clk*_FS[2:0]

Each of the four main output clocks (CLKA–CLKD) has a

three-bit code that determines the clock sources for the output

divider. The available clock sources are: Reference, PLL1,

PLL2, and PLL3. Each PLL provides both positive and

negative phased outputs, for a total of seven clock sources

(see Table 2). Note that the phase is a relative measure of the

PLL output phases. No absolute phase relation exists at the

outputs. )

Table 2.

Clk*_FS[2:0] Clock Source

000 Reference Clock

001 Reserved

010 PLL1 0° Phase

011 PLL1 18 0 ° Phase

100 PLL2 0° Phase

101 PLL2 180° Phase

110 PLL3 0° Phase

111 PLL3 18 0 ° Phase

Document #: 38-07186 Rev. *C Page 6 of 17

/OE

DDS

For the CY2239 4,

Xbuf_OE

This bit enables the XBUF output when HIGH. For the

CY22395, Xbuf_OE = 0.

PdnEn

This bit selects the function of the SHUTDOWN

this bit is HIGH, the pin is an active LOW shutdown contro l.

When this bit is LOW, this pin is an active HIGH output enable

control.

Clk*_ACAdj[1:0]

These bits modify the output predrivers, changing the duty

cycle through the pads. These are nominally set to 01, with a

higher value shifting the duty cycle higher. The performance of

the nominal setting is guaranteed.

Clk*_DCAdj[1:0]

These bits modify the DC drive of the outputs. The performance of the nominal setting is guaranteed.

Table 3.

Clk*_DCAdj[1:0] Output Drive Strength

00 –30% of nominal

01 Nominal

10 +15% of nominal

11 +50% of nominal

PLL*_Q[7:0]

PLL*_P[9:0]

PLL*_P0

These are the 8-bit Q value and 11-bit P values that determine

the PLL frequency. The formula is:

PLL*_LF[2:0]

These bits adjust the loop filter to optimize the stability of the

PLL. Table 4 can be used to guarantee stability. However,

CyClocksRT uses a more complicated algorithm to set the

loop filter for enhanced jitter performance. Use the Print

Preview function in CyClocksRT to determine the charge

pump settings for optimal jitter performance.

Table 4.

PLL*_LF[2:0] P

00016231

001 232 626

010 627 834

011 835 1043

100 1044 1600

Min PT Max

T

/OE pin. When

[+] Feedback [+] Feedback

Loading...

Loading...