Page 1

CY8C21x34/B

CapSense® Design Guide

Doc. No 001-66271 Rev. *B

Cypress Semiconductor

198 Champion Court

San Jose, CA 95134-1709

Phone (USA): 1.800.541.4736

Phone (Intnl): 408.943.2600

http://www.cypress.com

Page 2

Copyrights

Copyrights

© Cypress Semiconductor Corporation, 2010–2011. The information contained herein is subject to change without notice.

Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a

Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted

nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an

express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical

components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury

to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all

risk of such use and in doing so indemnifies Cypress against all charges.

Trademarks

PSoC Designer™, Programmable System-on-Chip™, PSoC Creator™, and SmartSense™ are trademarks and PSoC® and

CapSense® are registered trademarks of Cypress Semiconductor Corp. All other trademarks or registered trademarks

referenced herein are property of the respective corporations.

Source Code

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected

by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international

treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use,

modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of

creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress

integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or

representation of this Source Code except as specified above is prohibited without the express written permission of

Cypress.

Disclaimer

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL,

INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A

PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described

herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein.

Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure

may reasonably be expected to result in significant injury to the user. The inclusion of Cypress’ product in a life-support

systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against

all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

2 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense® Design Guide

Page 3

Contents

1. Introduction .................................................................................................................................................................... 7

1.1 Abstract ................................................................................................................................................................. 7

1.2 Cypress CapSense Documentation Ecosystem .................................................................................................... 7

1.3 CY8C21x34/B CapSense Plus Family Features.................................................................................................... 9

1.3.1 Advanced Touch Sensing Features .......................................................................................................... 9

1.3.2 Device Features........................................................................................................................................ 9

1.4 Document Conventions ....................................................................................................................................... 10

2. CapSense Technology ................................................................................................................................................ 11

2.1 CapSense Fundamentals .................................................................................................................................... 11

2.2 CapSense Methods in CY8C21x34/B .................................................................................................................. 13

2.2.1 CapSense with Sigma Delta Modulator (CSD) ....................................................................................... 13

2.2.2 CSD with ADC Functionality (CSDADC) ................................................................................................. 14

2.2.3 SmartSense™ Auto-tuning ..................................................................................................................... 14

3. CapSense Design Tools .............................................................................................................................................. 16

3.1 Overview of CapSense Design Tools .................................................................................................................. 16

3.1.1 PSoC Designer™ and User Modules ..................................................................................................... 16

3.1.2 Universal CapSense Controller Kit ......................................................................................................... 17

3.1.3 Universal CapSense Controller Module Board ....................................................................................... 18

3.1.4 CapSense Data Viewing Tools ............................................................................................................... 18

3.2 User Module Overview ........................................................................................................................................ 18

3.3 CapSense User Module Global Arrays ................................................................................................................ 18

3.3.1 Raw Count .............................................................................................................................................. 19

3.3.2 Baseline .................................................................................................................................................. 19

3.3.3 Difference Count (Signal) ....................................................................................................................... 19

3.3.4 Sensor State ........................................................................................................................................... 19

3.4 CSD User Module Configurations ........................................................................................................................ 20

3.4.1 CSD without Clock Prescaler .................................................................................................................. 20

3.4.2 CSD with Clock Prescaler ....................................................................................................................... 20

3.5 CSD User Module Parameters ............................................................................................................................ 20

3.6 CSD User Module High-Lev el Parame t ers .......................................................................................................... 21

3.6.1 Finger Threshold..................................................................................................................................... 21

3.6.2 Noise Threshold...................................................................................................................................... 21

3.6.3 Baseline Update Threshold .................................................................................................................... 21

3.6.4 Sensors Autoreset .................................................................................................................................. 21

3.6.5 Hysteresis ............................................................................................................................................... 21

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 3

Page 4

Debounce ............................................................................................................................................... 22

3.6.6

3.6.7 Negative Noise Threshold ...................................................................................................................... 22

3.6.8 Low Baseline Reset ................................................................................................................................ 22

3.6.9 High Level Parameter Recommendations .............................................................................................. 22

3.7 CSD User Module Low-Lev el Parame ter s ........................................................................................................... 23

3.7.1 Scanning Speed ..................................................................................................................................... 23

3.7.2 Resolution ............................................................................................................................................... 23

3.7.3 Reference ............................................................................................................................................... 24

3.7.4 Ref Value ................................................................................................................................................ 24

3.7.5 Prescaler Period ..................................................................................................................................... 24

3.7.6 Shield Electrode Out ............................................................................................................................... 24

3.8 CSDADC User Module Configurations ................................................................................................................ 24

3.8.1 CSDADC with PRS16 Clock Source....................................................................................................... 24

3.8.2 CSDADC with PRS8 Clock Source......................................................................................................... 24

3.8.3 CSDADC with PWM8 Clock Source ....................................................................................................... 25

3.8.4 CSDADC with VC2 Clock Source ........................................................................................................... 25

3.9 CSDADC User Module Parameters ..................................................................................................................... 25

3.10 Low-Level Parameters ......................................................................................................................................... 25

3.10.1 Scanning Speed ..................................................................................................................................... 25

3.10.2 Resolution ............................................................................................................................................... 25

3.10.3 Reference ............................................................................................................................................... 26

3.10.4 Ref Value ................................................................................................................................................ 26

3.10.5 Prescaler Period ..................................................................................................................................... 26

3.10.6 Shield Electrode Out ............................................................................................................................... 26

3.10.7 ADC Enabled .......................................................................................................................................... 26

3.11 SmartSense User Module Parameters ................................................................................................................ 27

3.12 Low-Level Parameters ......................................................................................................................................... 27

3.12.1 Shield Electrode Out ............................................................................................................................... 27

3.12.2 Modulator Capacitor Pin ......................................................................................................................... 27

3.12.3 Feedback Resistor Pin ............................................................................................................................ 27

3.12.4 Threshold Setting Mode .......................................................................................................................... 27

3.12.5 Sensitivity Level ...................................................................................................................................... 27

3.12.6 Finger Threshold..................................................................................................................................... 28

4. CapSense Performance Tuning with User Modules ................................................................................................. 29

4.1 General Considerations ....................................................................................................................................... 29

4.1.1 Signal, Noise, and SNR .......................................................................................................................... 29

4.1.2 Charge/Discharge Rate .......................................................................................................................... 30

4.1.3 Importance of Baseline Update Threshold Verification ........................................................................... 31

4.2 Tuning the CSD and CSDADC User Modules ..................................................................................................... 32

4.2.1 Set Up Hardware and Software for Tuning ............................................................................................. 33

4.2.2 Select Prescaler...................................................................................................................................... 33

4.2.3 Set Raw Count Range with Rb ................................................................................................................ 33

4.2.4 Set High-Level Parameters ..................................................................................................................... 34

4.3 Configuring SmartSense User Module ................................................................................................................ 34

5. Design Considerations ............................................................................................................................................... 37

4 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 5

Overlay Selection ................................................................................................................................................ 37

5.1

5.2 ESD Protection .................................................................................................................................................... 38

5.2.1 Prevent ................................................................................................................................................... 38

5.2.2 Redirect .................................................................................................................................................. 38

5.2.3 Clamp ..................................................................................................................................................... 38

5.3 Electromagnetic Compatibility (EMC) Considerations ......................................................................................... 38

5.3.1 Radiated Interference ............................................................................................................................. 38

5.3.2 Radiated Emissions ................................................................................................................................ 39

5.3.3 Conducted Immunity and Emissions ....................................................................................................... 39

5.4 Software Filtering ................................................................................................................................................. 39

5.5 Power Consumption ............................................................................................................................................ 40

5.5.1 System Design Recommendations ......................................................................................................... 40

5.5.2 Sleep-Scan Method ................................................................................................................................ 40

5.5.3 Response Time versus Power Consumption .......................................................................................... 41

5.5.4 Measuring Average Power Consumption ............................................................................................... 41

5.6 Pin Assignments .................................................................................................................................................. 42

5.7 PCB Layout Guidelines ....................................................................................................................................... 42

6. Water Tolerance ........................................................................................................................................................... 43

6.1 Shield Electrode and Guard Sensor .................................................................................................................... 43

6.1.1 Shield ...................................................................................................................................................... 43

6.1.2 Guard Sensor ......................................................................................................................................... 46

6.2 Design Recommendations .................................................................................................................................. 48

7. Proximity Sensing ....................................................................................................................................................... 49

7.1 Types of Proximity Sensors ................................................................................................................................. 49

7.1.1 Button ..................................................................................................................................................... 49

7.1.2 Wire ........................................................................................................................................................ 49

7.1.3 PCB Trace .............................................................................................................................................. 49

7.1.4 Sensor Ganging ...................................................................................................................................... 49

7.2 Design Recommendations .................................................................................................................................. 50

8. Low Power Design Considerations ............................................................................................................................ 51

8.1 Additional Power Saving Techniques .................................................................................................................. 51

8.1.1 Set Drive Modes to Analog HI-Z ............................................................................................................. 51

8.1.2 Putting it All Together ............................................................................................................................. 52

8.1.3 Sleep Mode Complications ..................................................................................................................... 52

8.1.4 Pending Interrupts .................................................................................................................................. 52

8.1.5 Global Interrupt Enable ........................................................................................................................... 52

8.2 Post Wakeup Execution Sequence ..................................................................................................................... 53

8.2.1 PLL Mode Enabled ................................................................................................................................. 53

8.2.2 Execution of Global Interrupt Enable ...................................................................................................... 53

8.2.3 I2C Slave with Sleep Mode ..................................................................................................................... 53

8.2.4 Sleep Timer ............................................................................................................................................ 53

9. Resources .................................................................................................................................................................... 55

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 5

Page 6

Website ............................................................................................................................................................... 55

9.1

9.2 Datasheet ............................................................................................................................................................ 55

9.3 Technical Reference Manual ............................................................................................................................... 55

9.4 Development Kits ................................................................................................................................................ 55

9.4.1 Universal CapSense Controller Kit ......................................................................................................... 55

9.4.2 Universal CapSense Module Boards ...................................................................................................... 55

9.4.3 In-Circuit Emulation (ICE) Kit .................................................................................................................. 56

9.5 PSoC Programmer .............................................................................................................................................. 56

9.6 MultiChart ............................................................................................................................................................ 56

9.7 PSoC Designer .................................................................................................................................................... 56

9.8 Code Examples ................................................................................................................................................... 56

9.9 Design Support .................................................................................................................................................... 57

9.10 Document Revision History ................................................................................................................................. 57

6 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 7

1. Introduction

1.1 Abstract

This document gives design guidance for using capacitive touch sensing (CapSense®) functionality with the

CY8C21x34/B family of CapSense Plus Controllers. The following topics are covered in thi s guide:

Features of the CY8C21x34/B family of CapSense Plus Controllers

CapSense principl es of oper ati on

Introduction to CapSense design tools

In depth guide to tuning the CapSense touch sensing system for optimal performance

Advanced features such as water tolerance and proximity detection

Electrical and mechanical system design consid erations

Additional resources and support for designing CapSense into your system

1.2 Cypress CapSense Documentation Ecosystem

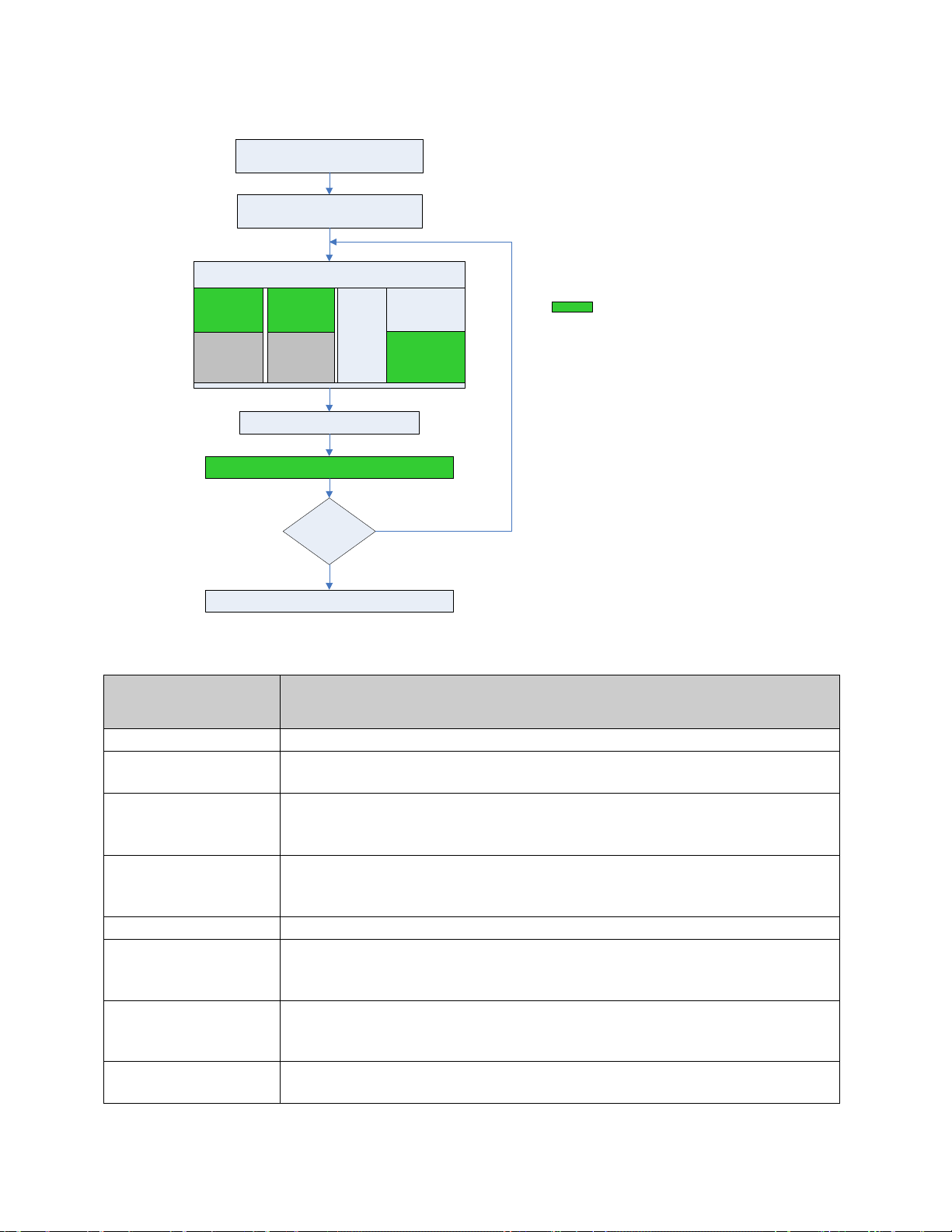

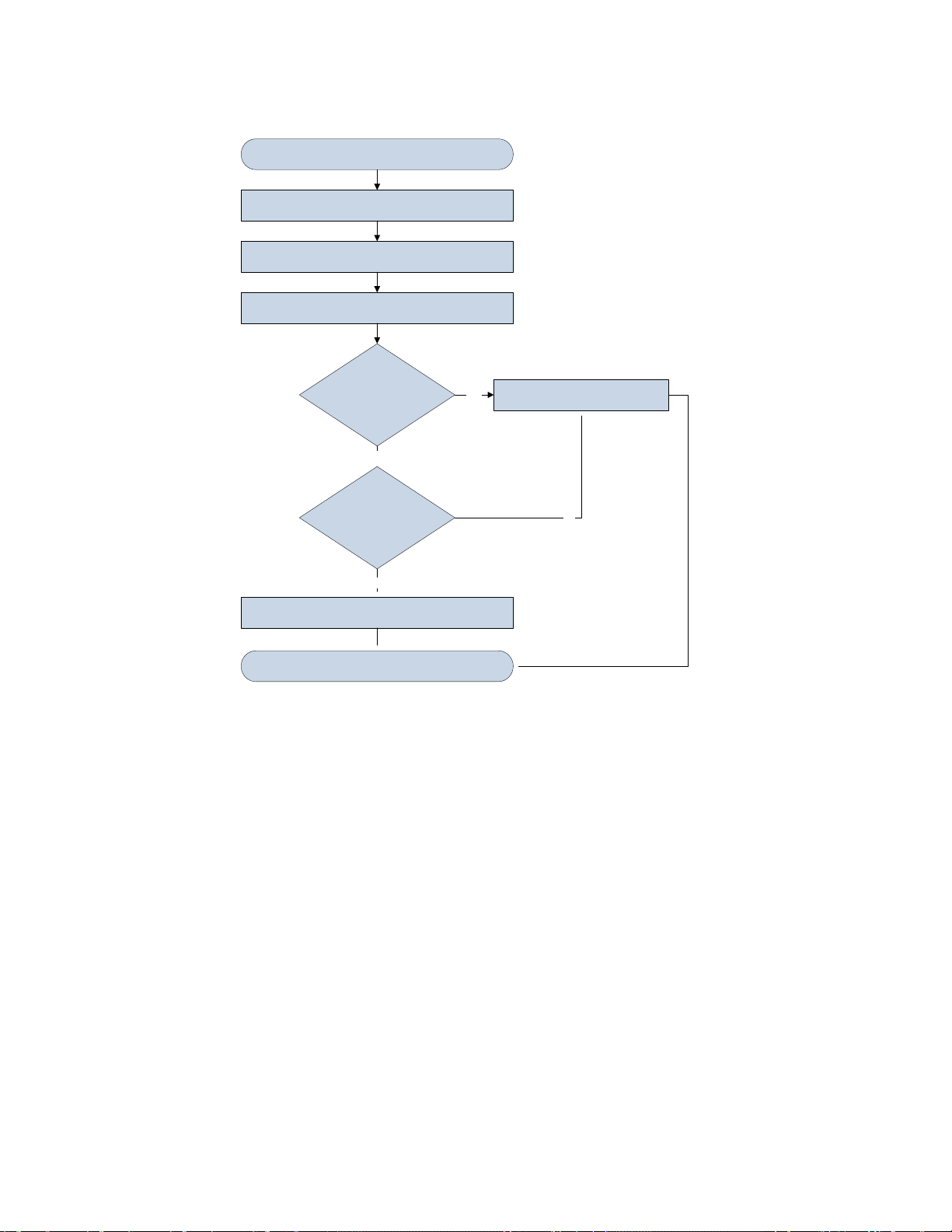

Figure 1-1 and Table 1-1 summarize the Cypress CapSense documentation ecosystem. These resources allow

implementers to quickly access the information needed to successfully complete a CapSense product design.

Figure 1-1 shows the typical flow of a product design cycle with capacitive sensing; the information in this guide is

most pertinent to the topics highlighted in green. Table 1-1 includes links to the supporting documents for each of the

numbered tasks in Figure 1-1.

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 7

Page 8

2. CapSense device selection based

on needed functionality

3. Mechanical

Design

4. Schematic

capture and

PCB layout

1. Specify system requirements and

characteristics

5. PSoC

Designer

project

creation

Preproduction build (prototype)

6. Firmware

development

7. CapSense

configuration

and tuning

8. Test and evaluate system functionality and

CapSense performance

Design for CapSense

Performance

satisfactory

Production

Yes

No

= Topics covered in this document

Figure 1-1. Typical CapSense Product Design Flow

Numbered Design Task of

Figure 1-1

1 Getting Started with CapSense

2

3

4

5 PSoC Designer User Guides

6

7

8

Table 1-1. Cypress Documents Supporting Numbered Design Tasks of Figure 1-1

Supporting Cypress CapSense Documentation

Getting Started with CapSense

CY8C21x34/B CapSense Device Datasheets

Getting Started with CapSense

PSoC Family Specific CapSense

CapSense Application Notes

Getting Started with CapSense

PSoC Family Specific CapSense

CapSense Application Notes

CapSense Application Notes

CapSense Code Examples

PSoC Family Specific Technical Reference Manual (for CY8C21x34/B)

PSoC Family Specific CapSense Design Guide (this document)

PSoC Family Specific CapSense User Module Datasheets (CSD, CSDADC, and SmartSense)

PSoC Family Specific Technical Reference Manual (for CY8C21x34/B)

PSoC Family Specific CapSense Design Guide (this document)

CapSense Code Examples

Design Guide (this document)

Design Guide (this document)

8 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 9

1.3 CY8C21x34/B CapSense Plus Family Features

Cypress’s CY8C21x34/B is a low-power, high-perfor ma nce, progr a mm able CapSense controller family that features:

1.3.1 Advanced Touch Sensing Features

Programmable capacitive sensing elements

Supports a combination of CapSense buttons, sliders, and proximity sensors with CSD and CSDADC

capacitive sensing technology

SmartSense™ Auto-tuning (CY8C21x34B)

Contains an integrated API to implement buttons and sliders

Supports up to 24 capacitive buttons and 4 sliders

Supports proximity sensing up to 5 cm (with on-board PCB trace)

Water-tolerant performance with shield electrode

1.3.2 Device Features

High-performance, low-power M8C Harvard-architec tur e pro ces sor

M8C processor speeds up to 24 MHz

Flexible on-chip memory

Up to 8 KB of flash and 512 B of SRAM

Emulated EEPROM supported

Precision, progra mma ble cloc king

Internal main oscillator (IMO): 24/48 MHz ± 2.5%

Internal low-speed oscillator (ILO) at 32 kHz for watchdog and sleep

Enhanced general-purpose input/output (GPIO) features

Up to 28 general-purpose I/Os (GPIOs) with programmable pin configuration

25-mA sink current on all GPIOs

Internal resistive pull-up, HI-Z, open-drain, and strong drive modes on all GPIOs

Peripheral features

Counter, timer, PWM, Pulse Width Discriminator (PWD), and hardware 7-segment drive

2

I

C communication with Master, Slave, and Multi-Master configurations

SPI, UART, IRDA, and one-wire communication protocols

Operating Conditions

Operating Voltage: 2.4 V to 5.25 V with operation down to 1.0 V by using on-chip switch mode pump

Temperature Range: –40

Packaging

16-pin SOIC (150-MIL) to 32-pin QFN (5 x 5 mm)

AEC qualified automotive grade parts – CY8C21334 and CY8C21534

o

C to +85 oC

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 9

Page 10

1.4 Document Conventions

Convention Usage

Courier New

Italics

[Bracketed, Bold]

File > Open

Bold

Times New Roman

Text in gray boxes Describes Cautions or unique functionality of the product.

Displays file locations, user entered text, and source code:

C:\ ...cd\icc\

Displays file names and reference documentation:

Read about the sourcefile.hex file in the PSoC Designer User Guide.

Displays keyboard commands in procedures:

[Enter] or [Ctrl] [C]

Represents menu paths:

File > Open > New Project

Displays commands, menu paths, and icon names in procedures:

Click the File icon and then click Open.

Displays an equation:

2 + 2 = 4

10 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 11

2. CapSense Technology

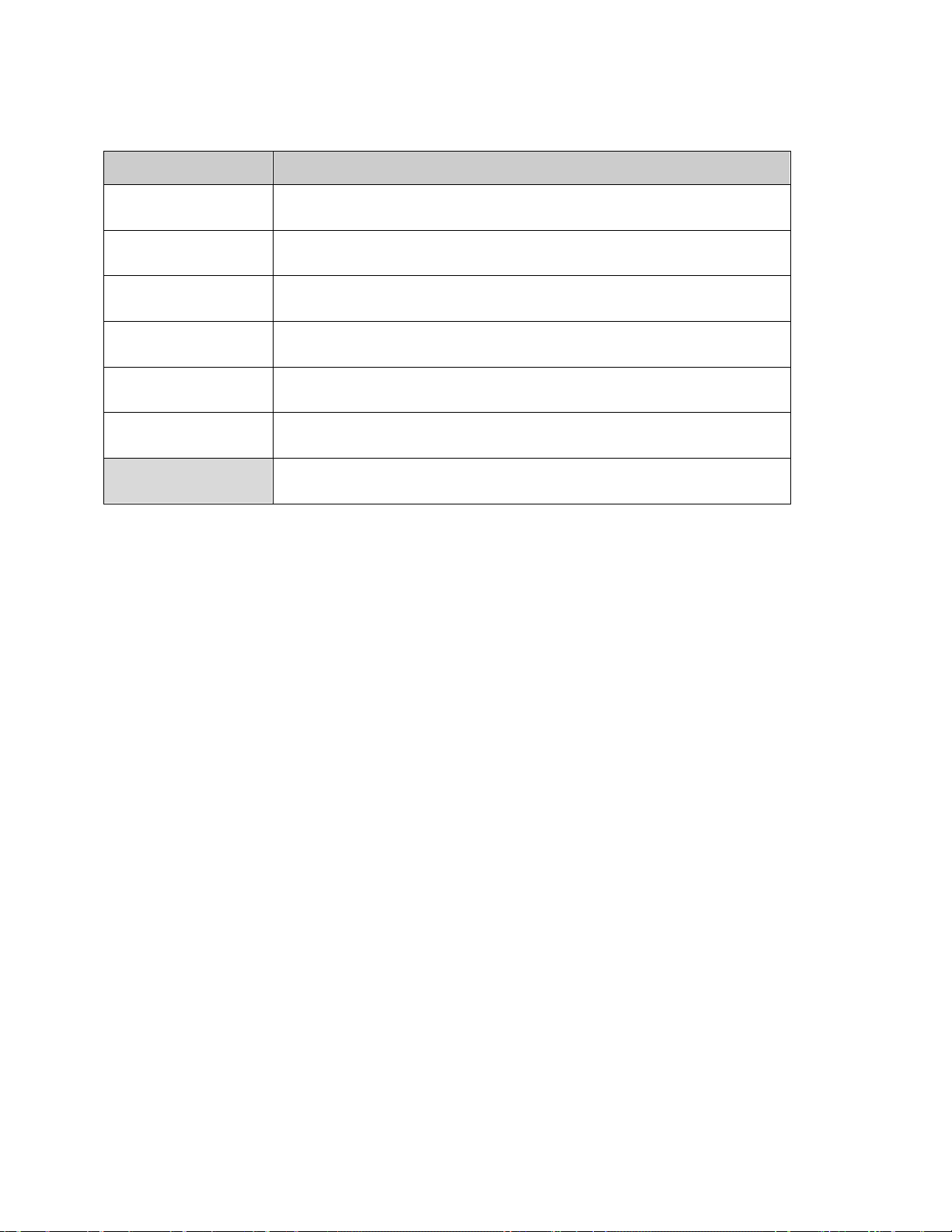

CY8C21x34/B Rb

Cmod

Cx,n

Cx,2

Cx,1

Sensor Equivalent

Capacitors

P1[1] or P1[5]

P0[1] or P0[3]

2.1 CapSense Fundamentals

CapSense is a touch-sensing technology that works by measuring the capacitance of each I/O pin on the CapSense

controller that has been designated as a sensor. As shown in Figure 2-1, the total capacitance on each of the sensor

pins can be modeled as equivalent lumped capacitors with values of C

Circuitry internal to the CY8C21x34/B device converts the magnitude of each C

post processing. The other components, namely Rb and C

circuitry.

Figure 2-1. CapSense Implementation in a CY8C21x34/B PSoC Device

, are used by the CapSense controller’s internal

MOD

through C

X,1

X

for a design with n sensors.

X,n

into a digital code that is stored for

As shown in Figure 2-2, each sensor I/O pin is connected to a sensor pad by traces, vias, or both as necessary. The

overlay is a nonconductive cover over the sensor pad that constitutes the product’s touch interface. When a f inger

comes into contact with the overlay, the conductivity and mass of the body effectively introduces a grounded

conductive plane parallel to the sensor pad. This is represented in Figure 2-2. This arrangement constitutes a pa r all e l

plate capacitor whose capacitance is given by Equation 1.

.

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 11

Page 12

D

A

C

r

F

εε

0

=

PX

CC =

FPX

CCC +=

Figure 2-2. Cross Section of Typical CapSense PCB with the Sensor Being Activated by a Finger

Equation 1

Where:

CF = The capacitance affected by a finger in contact with the overlay over a sensor

ε

= Free space permittivity

0

= Dielectric constant (relative permittivity) of overlay

ε

r

A = Area of finger and sensor pad overlap

D = Overlay thickness

In addition to the parallel plate capacitance, a finger in contact with the overlay causes electric field fringing between

itself and other conductors in the immediate vicinity. The effect of these fringing fields is typically minor compared to

that of the parallel plate capacitor and can usually be ignored.

Even without a finger touching the overlay, the sensor I/O pin has some parasitic capacitance (C

). CP results f rom

P

the combination of the CapSense controller internal parasitics and electric field coupling between the sensor pad,

traces, and vias, and other conductors in the system such as ground plane, other traces, any metal in the product’s

chassis or enclosure, and so on. The CapSense controller measures the total capacitance (C

) connected to a

X

sensor pin.

When a finger is not touching a sensor:

Equation 2

When a finger is touching the sensor:

Equation 3

In general CP is an order of magnitude greater than CF. CP usually ranges from 6 pF to 15 pF, but in extreme cases

can be as high as 50 pF. CF usually ranges from 0.1 pF to 0.4 pF. The magnitude of C

is of critical importance when

P

tuning a CapSense system and will be discussed in CapSense Performance Tuning with User Modules.

12 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 13

Cx

Vdd

i

sensor

Sigma-Delta

Converter

Precharge

Clock

Cmod

Rb

High-Z

input

Sw1

Sw2

CY8C21x34/B

Gnd

i

bleed

= External Connection

AMUX Bus

Vref

Rbus

R

inline

2.2 CapSense Methods in CY8C21x34/B

CY8C21x34/B devices support several CapSense methods for converting sensor capacitance (CX) into a digi t al co de.

These are CapSense Sigma Delta (CSD), CSD with ADC (CSDADC), and SmartSense. These methods are

implemented in the form of PSoC Designer User Modules and are described in Section 3 of this design guide.

2.2.1 CapSense with Sigma Delta Modulator (CSD)

The CapSense Sigma-Delta (CSD) method in CY8C21x34/B devices incorporates CX into a switched-capacitor circuit

as shown in Figure 2-3. The sensor (C

underlapped switches Sw1 and Sw2, respectively. Sw1 and Sw2 are driven by a Precharge clock to generate a

current (I

) into the AMUX bus. The magnitude of I

SENSOR

Sigma-Delta converter samples AMUX bus voltage and generates a modulating bit stream that controls the constant

current source (I

sensor bleeds off the charge I

), which charges AMUX such that the average AMUX bus voltage is maintained at V

DAC

SENSOR

low-pass filter that attenuates Precharge switching transients at the Sigma-Delta converter input.

) is alternately connected to VDD and the Analog MUX (AMUX) bus by the

X

is directly proportional to the magnitude of CX. The

SENSOR

from the modulating capacitor (C

MOD

). C

in combination with Rbus forms a

MOD

Figure 2-3. CSD Block Diagram

REF

. The

In maintaining the average AMUX voltage at a steady state value (V

average bleed current (I

BLEED

) to I

by controlling the bit stream duty cycle. The Sigma-Delta converter stores

SENSOR

), the Sigma-Delta converter matches the

REF

the bit stream over the duration of a sensor scan and the accumulated result is a digital output value, known as raw

counts, that is directly proportional to C

state. Figure 2-4 plots the CSD raw counts from a number of consecutive scans during which the sensor is touched

and then released by a finger. As explained in CapSense Fundamentals, the fing er touch caus es C

which in turn causes raw counts to increase proportionally. By comparing the shift in steady state raw count level

C

F,

. This raw count is interpreted by high-level algorithms to resolve sensor

x

to increase by

x

to a predetermined threshold, the high-level algorithms can determine whether the sensor is in an On (Touch) or Off

(No Touch) state.

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 13

Page 14

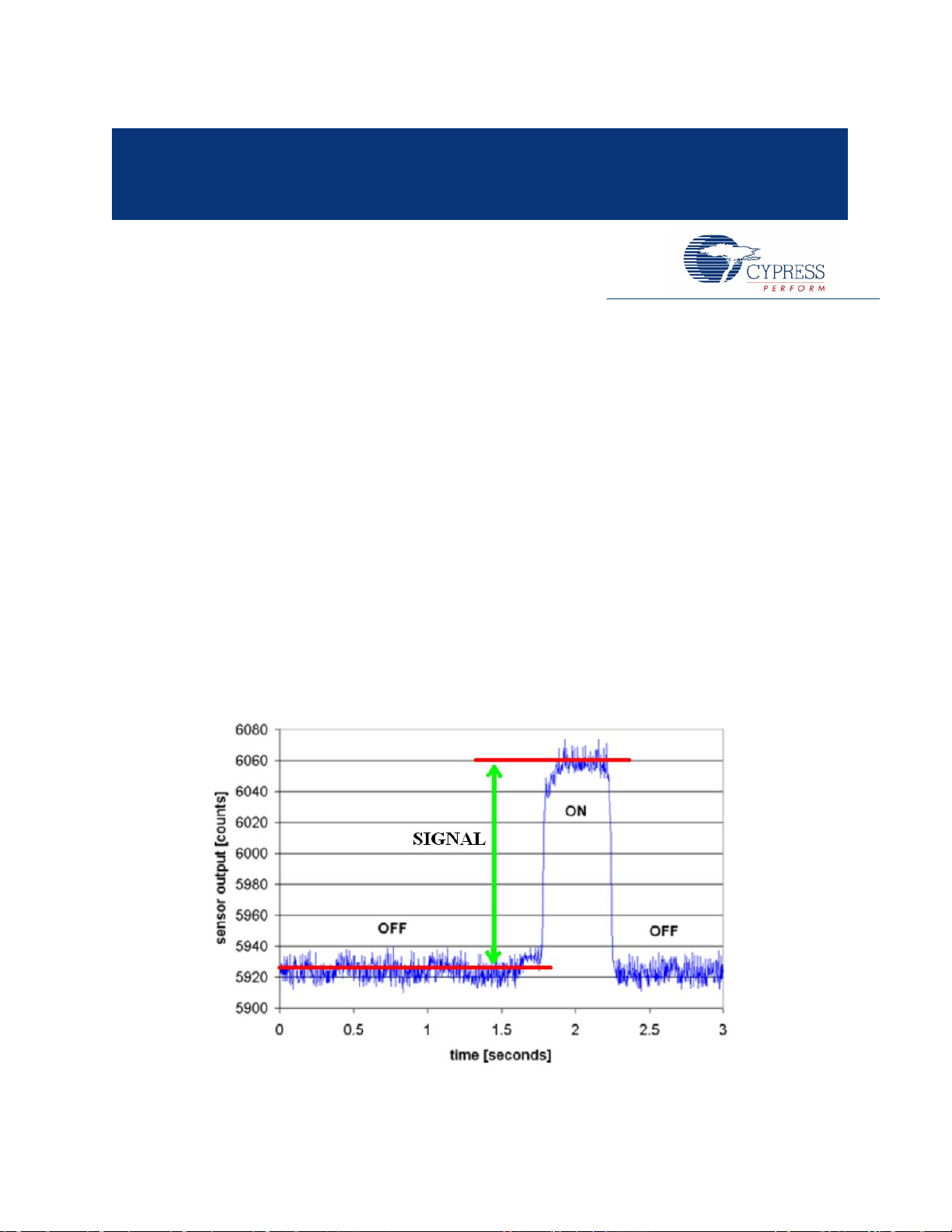

Figure 2-4. CSD Raw Counts during a Finger Touch

2.2.2 CSD with ADC Functionality (CSDADC)

The CSDADC CapSense method functions in an identical manner as CSD except that it is augmented with the ADC

functionality in addition to capacitance measurement.

2.2.2.1 ADC Features

Absolute and ratiometric ADC input modes with run-time mode switching, which allows you to easily scan

different sensor types

Single-slope ADC for absolute voltage input mode

Built-in calibration mechanism for the single-slope ADC

Integrating incremental ADC for ratiometric input mode

2.2.3 SmartSense™ Auto-tuning

Tuning the touch-sensing user interface is a critical step in ensuring proper system operation and a pleasant user

experience. The typical design flow entails tuning the sensor interface in the initial design phase, during system

integration, and finally production fine-tuning before the production ramp. Tuning is an iterative process and can be

time consuming. SmartSense Auto-tuning was developed to simplify the user interface development cycle. It is easy

to use and significantly reduces the design cycle time by eliminating the tuning process throughout the entire product

development cycle, from prototype to mass production. SmartSense tunes each CapSense sensor automatically at

power up and then monitors and maintains optimum sensor performance during run time. This technology adapts for

manufacturing variation in PCBs, overlays, and noise generators such as LCD inverters, AC line noise, and switchmode power supplies, and automatically tunes them out. SmartSense Auto-tuning requires between 2.1 KB -3.7 KB

of flash depending on configuration and 29B of RAM per sensor.

2.2.3.1 Process Variation

The SmartSense User Module (UM) for the CY8C21x34B is designed to work with sensor parasitic capacitance in the

range of 5 pF to 45 pF (typical sensor CP values are in the range of 10 pF to 20 pF). The sensitivity parameter for

each sensor is set automatically, based on the characteristics of that particular sensor. This improves the yield in

mass production, as consistent response is maintained from every sensor regardless of C

within the specified range of 5 to 41 pF. Parasitic capacitance of the individual sensors can vary due to PCB layout,

PCB manufacturing process variation, or with vendor-to-vendor PCB variation within a multisourced supply chain.

The sensitivity of a sensor depends on its parasitic capacitance; higher C

result in decreased finger touch signal amplitude. In some cases, the change in C

resulting in less than optimum sensor performance (either too sensitive or not sensitive enough) or, wor st case, a

nonoperational sensor. In either situation, you must retune the system, and in some cases requalify the UI

subsystem. SmartSense Auto-tuning solves these issues.

values decrease the sensor sensitivity and

P

variation between sensors

P

value detunes the system,

P

14 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 15

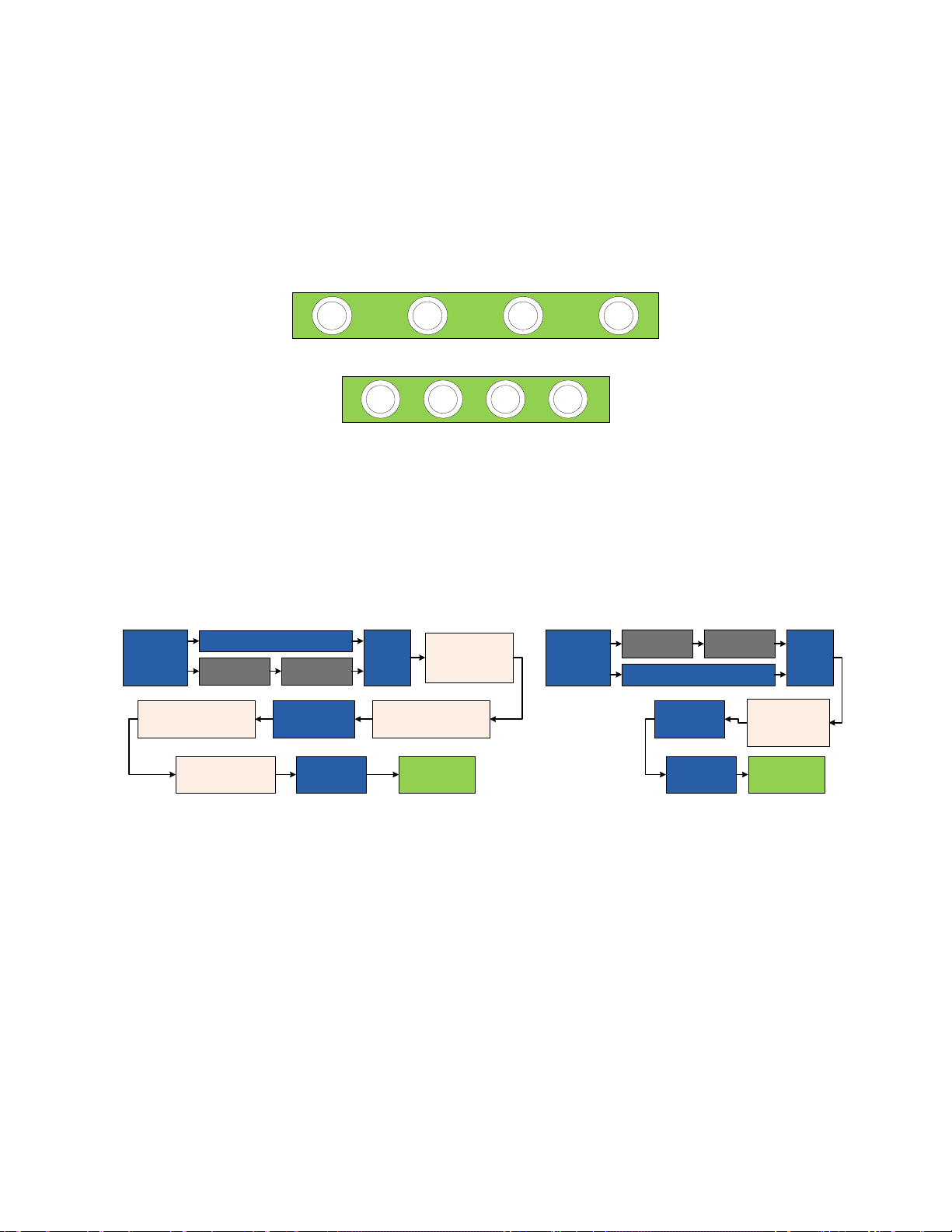

Feasibility

Study

Schematics

Design

PCB Layout

Design

Mechanical Design

Review

System

Integration

Re-tuning for any

changes

Tuning process

Production Fine

Tuning

Design

Validation

Production

Typical capacitive user interface Design Cycle

Firmware

Development

Feasibility

Study

Schematics

Design

PCB Layout

Design

Mechanical Design

Review

System

Integration

Design

Validation

Production

SmartSense based capacitive user interface Design Cycle

Firmware

Development

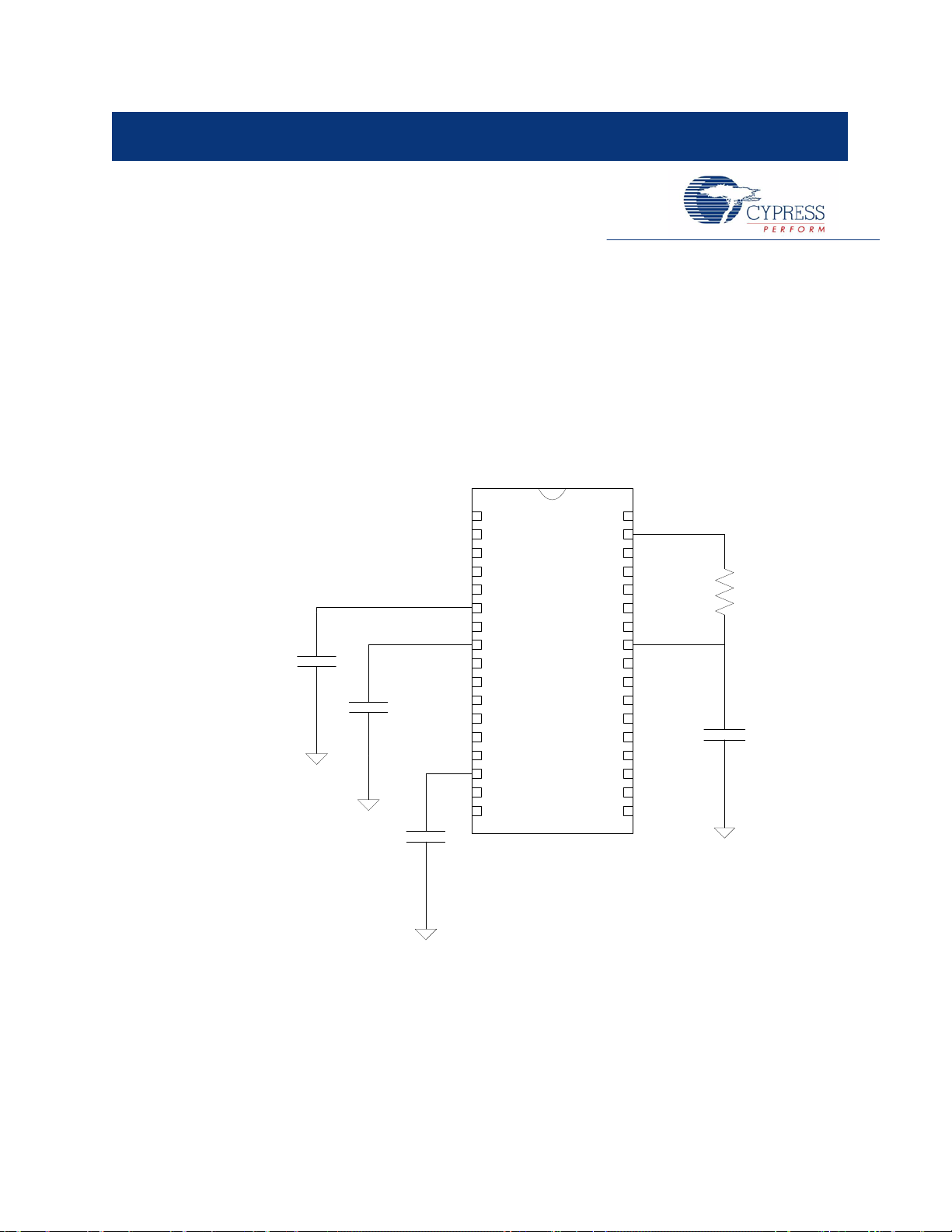

SmartSense Auto-tuning makes platform designs possible. Imagine the capacitive touch sensing multimedia keys in a

laptop computer; the spacing between the buttons depends on the size of the laptop and keyboard layout. In this

example, the wide-screen machine has larger spaces between the buttons than a standard-screen model. More

space between buttons means increased trace length between the sensor and the CapSense controller, which leads

to higher parasitic capacitance of the sensor. This means that the parasitic capacitance of the CapSense buttons can

be different in different models of the same platform design. Though the functionality of these buttons is the same for

all of the laptop models, the sensors must be tuned for each model. SmartSense enables you to do platform designs

using the recommended best practices shown in the PCB Layout in Getting Started with CapSense, knowing the

tuning will be done efficiently and automatically.

Figure 2-5. Design of Laptop Multimedia Keys for a 21-inchModel

Figure 2-6. Design of Laptop Multimedia Keys for a 15-inchModel with Identical Functionality and Button Size

2.2.3.2 Reduced Design Cycle Time

Usually the most time-consuming task for a capacitive sensor interface design is firmware development and sensor

tuning. With a typical touch-sensing controller, the sensor must be retuned when the same design is ported to

different models or when there are changes in the mechanical dimensions of the PCB or the sensor PCB layout. A

design with SmartSense solves these challenges because it needs less firmware development effort, no tuning, and

no retuning. This makes a typical design cycle much faster. Figure 2-7 compares the design cycles of a t ypi c al t ouc h sensing controller and a SmartSense-based design.

Figure 2-7. Typical Capacitive Inter fa ce Design Cycle Comparison

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 15

Page 16

3. CapSense Design Tools

3.1 Overview of CapSense Design Tools

Cypress offers a full line of hardware and software tools for developing your CapSense capacitive touch-sense

application. A basic development system for the CY8C21x34/B family includes the components discussed in this

chapter. See Resources for ordering information.

3.1.1 PSoC Designer™ and User Modules

Cypress’s exclusive integrated design environment, PSoC Designer, allows you to configure analog and digital

blocks, develop firmware, tune, and debug your design. Applications are developed in a drag-and-drop design

environment using a library of user modules. User modules are configured either through the Device Editor GUI or by

writing into specific registers with firmware. PSoC Designer comes with a built-in C compiler and an embedded

programmer. A pro compiler is available for complex designs.

CSD, CSDADC, and SmartSense User Modules implement capacitive touch sensors using switched-capacitor

circuitry, an analog multiplexer, a comparator, digital counting functions, and high-level software routines (APIs). User

modules for other analog and digital peripherals are available to implement additional functionality such as I

TX8, Timers, and PWMs.

Figure 3-1. PSoC Designer Device Editor

2

C, SPI,

3.1.1.1 Gett ing Started with CapSense User Modules

To create a new CY8C21x34/B project in PSoC Designer:

1. Create a new CY8C21x34/B PSoC Designer proje ct.

2. Select and place any user modules requiring dedicated pins (such as I

3. Select and place the CSD, CSDADC, or SmartSense User Module.

4. Right-click the user module to access the User Module wizard.

5. Set button sensor count, slider configuration, pin assignments, and associations.

6. Set pins and global user mod u le parame ter s .

16 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

2

C or LCD) and assign ports and pins.

®

Design Guide

Page 17

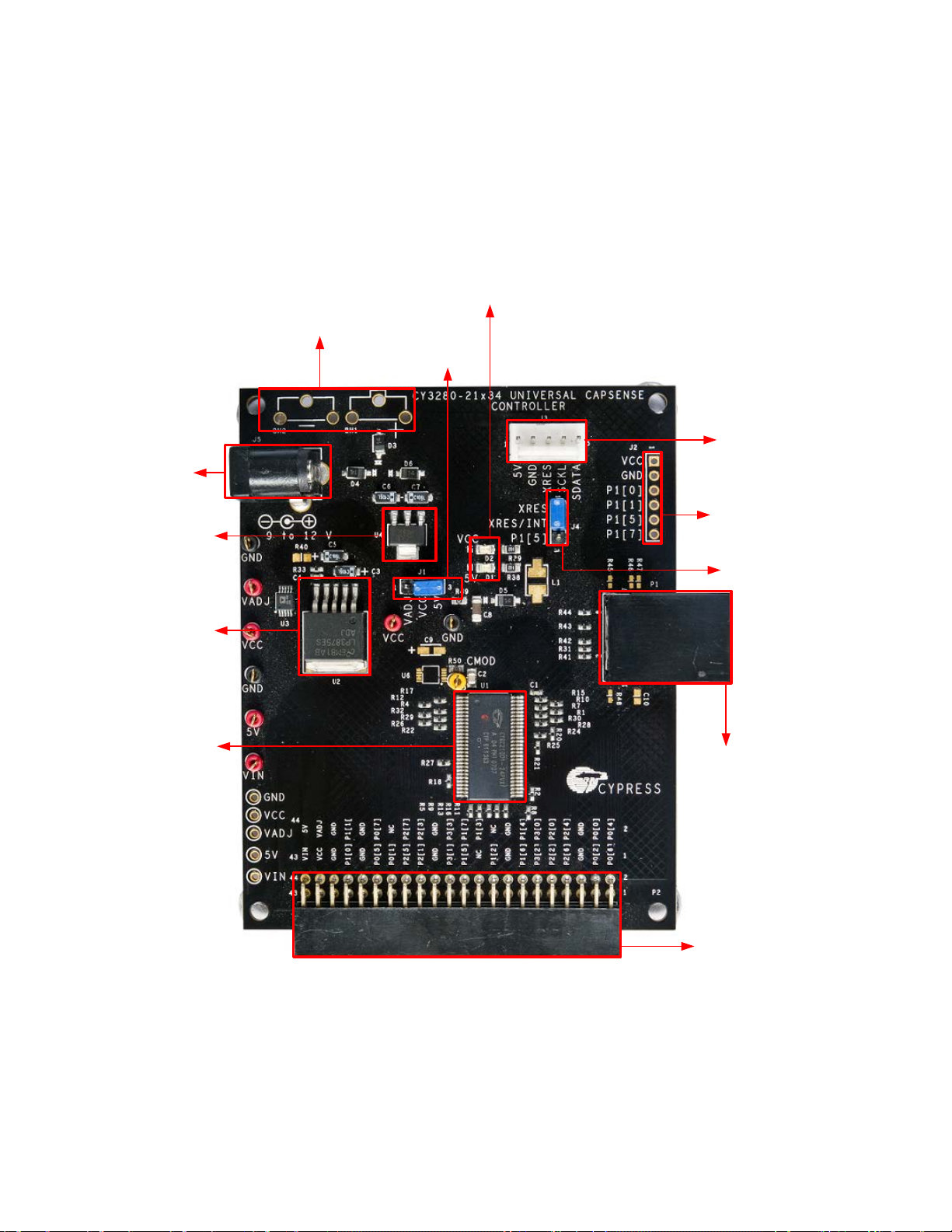

DC Supply

Jack

5-V Voltage

Regulator IC

SPI / I2C

Expansion Header

ISSP Header

LEDs D1 and D2

Adjustable

Voltage

Regulator IC

CapSense

Controller

CY8C21001

Jumper for

XRES Selection

CapSense Module

Connector

ICE Cube

Connector

Jumper to Select

Power Option

9-V Battery

Terminal

7. Generate the application and switch to Application Editor.

8. Adapt sample code from U ser Module Datasheet: (CY8C21x34) to implement buttons or sliders.

3.1.2 Universal CapSense Controller Kit

The Universal CY3280-BK1 CapSense Controller Kit features predefined control circuitry and plug-in hardware to

make prototyping and debugging easy. Programming and I2C-to-USB Bridge hardware are included for tuning and

data acquisition.

Figure 3-2. CY3280-21x34 CapSense Controller Kit

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 17

Page 18

3.1.3 Universal CapSense Controller Module Board

Cypress’s module boards feature a variety of sensors, LEDs, and interfaces to meet your application’s needs.

CY3280-BSM Simple Butto n Module

CY3280-BMM Matrix Button Module

CY3280-SLM Linear Slider Module

CY3280-SRM Radial Slider Module

CY3280-BBM Universal CapSense Prototyping Module

3.1.4 CapSense Data Viewing Tools

Many times during the CapSens e design process, you will want to monitor CapSense data (raw counts, baseline,

difference counts, and so on) for tuning and debugging purposes. There are two CapSense Data Viewing Tools,

MultiChart, and Bridge Control Panel. These tools are explained in more detail in the application note

AN2397 – CapSense Data Viewing Tools.

3.2 User Module Overview

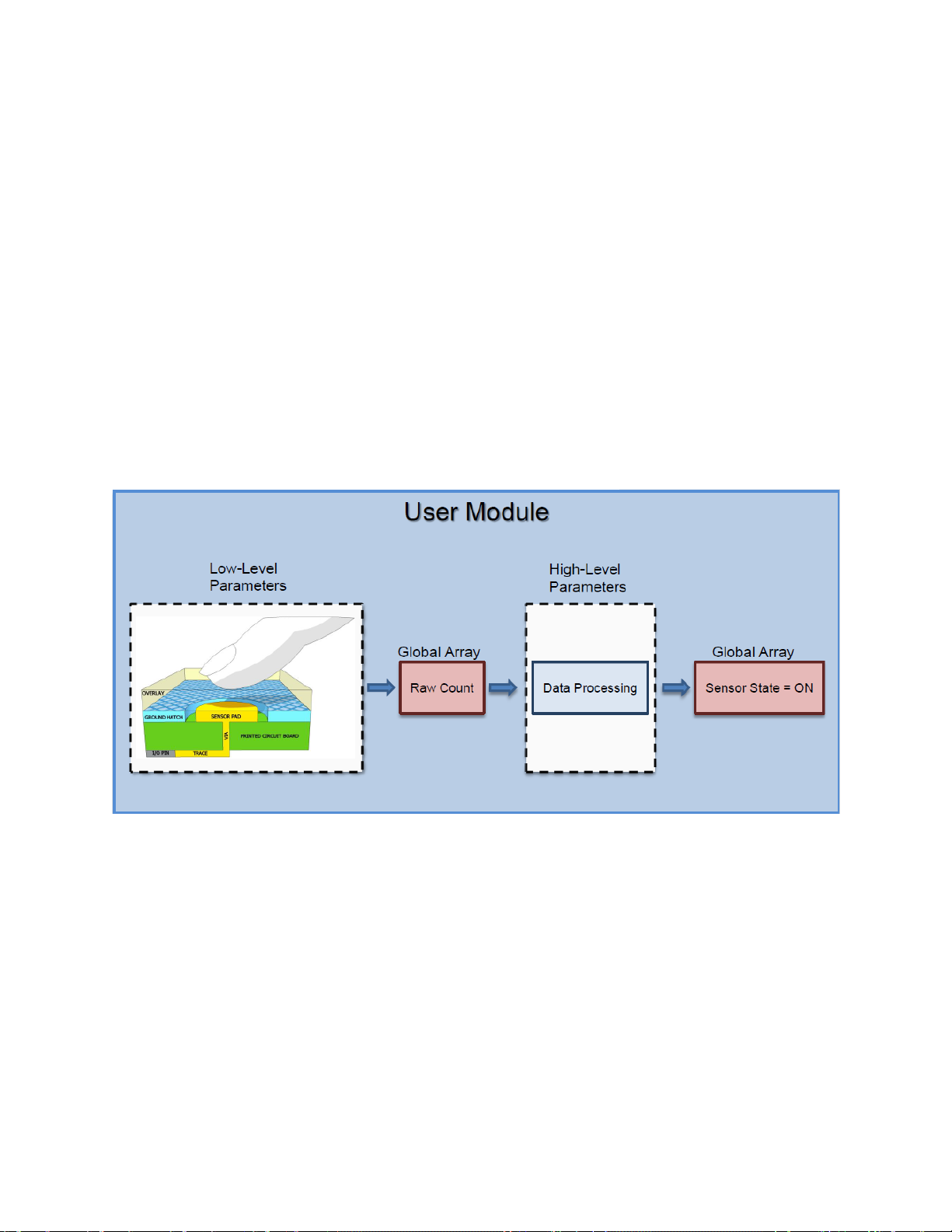

Figure 3-3. User Module Block Diagram

User modules contain an entire CapSense system from physical sensing to data processing. The behavior of the user

module is defined using several parameters. These parameters affect different parts of the sensing system and can

be separated into low-level and high-level parameters that communicate with one another using global arrays.

Low-level parameters, such as the speed and resolutions for scanning sensors, define the behavior of the sensing

method at the physical layer, and relate to the conversion from capacitance to raw count. Low-level parameters are

unique to each type of sensing method and are described in CSDADC User Module Configurations, CSDADC Use r

Module Parameters, and SmartSense User Module Parameters.

High-level parameters, such as debounce counts and noise thresholds, define how the raw counts are processed to

produce information such as the sensor ON/OFF state and the estimated finger position on a slider. These

parameters are the same for all sensing methods and are described in CSD User Module High-Level Parameters.

3.3 CapSens e Us e r Module Global Arrays

Before learning CapSense User Module parameters, you must be familiar with certain global arrays used by the

CapSense system. These arrays should not be altered manually, but may be inspected for debugging purposes.

18 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 19

Difference Count

(Signal)

Raw Count

Figure 3-4. Raw Count, Baseline, Difference Count, and Sensor State

3.3.1 Raw Count

The hardware circuit in the CapSense controller measures the sensor capacitance. It stores the result in a digital form

called raw count upon calling the user module API UMname_ScanSensor(), where UMname can be CSD, CSDADC,

or SmartSense.

The raw count of a sensor is proportional to its sensor capacitance. Raw count increases as the sensor capacitance

value increases.

The raw count values of sensors are stored in the UMname_waSnsResult[] integer array. This array is defined in the

header file UMname.h.

3.3.2 Baseline

Gradual environmental changes such as temperature and humidity affect the sensor raw count, which results in

variations in the counts.

The user module uses a complex baselining algorithm is to compensate for these variations. The algorithm uses

baseline variables to accomplish this. The baseline variables keep track of any gradual variations in raw count values.

Essentially, the baseline variables hold the output of a digital low pass filter to which input raw count values are fed.

The baselining algorithm is executed by the user module API UMname_UpdateSensorBaseline, where UMname can

be CSD, CSDADC, or SmartSense.

The baseline values of sensors are stored in UMname_waSnsBaseline[] integer array. This array is defined in the

header file UMname.h.

3.3.3 Difference Count (Signal)

The Difference Count, which is also known as the signal of a sensor, is defined as the difference in counts between a

sensor’s raw count and baseline values. When the sensor is inactive, the Difference Count is zero. Activating sensors

(by touching) results in a positive Difference Count value.

The Difference Count values of sensors are stored in the UMname_waSnsDiff[] integer array, where UMname can be

CSD, SmartSense, or CSA_EMC. This array is defined in the header file UMname.h.

Difference count variables are updated by the user module API UMname_UpdateSensorBaseline()..

3.3.4 Sensor State

Sensor state represents the active/inactive status of the physical sensors. The state of the s ensor changes from 0 to

1 upon finger touch and returns to 0 upon finger release.

Sensor states are stored in a byte array named UMname_baSnsOnMask[]array, where UMname can be CSD,

CSDADC, or SmartSense. Each array element stores the sensor state of eight consecutive sensors.

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 19

Page 20

High-Level

Low-Level

Sensor states are updated by the user module API UMname_bIsAnySensorActive()

3.4 CSD User Module Configurations

The CSD User Module has two selectable clock configurations. These configurations use different signal sources for

the switched-capacitor circuit on the front end of the CSD, as shown in Fi gure 2-3 on page 13.

You should select the clock configuration when you first place the CSD Us er Module in your PSoC Designer project.

You can change this selection later by right-clicking the CSD User Module and selecting User Module Selection

Options.

3.4.1 CSD without Clock Prescaler

In this configuration, a 16-bit pseudo-random sequence (PRS) is used as the signal source for the switched-capacitor

circuit on the front end of the CSD. System Clock (IMO) is the clock source for the PRS. The PRS spreads the clock’s

frequency spectrum and provi des good noise immunity. This configuration requires three digital blocks.

3.4.2 CSD with Clock Prescaler

In this configuration, an 8-bit PRS is used as the signal source for the switched capacitor circuit on the front end of

the CSD. IMO is divided by an adjustable prescaler divider and is used as the clock source for the PRS. The PRS

spreads the clock’s frequency spectrum to provide noise immunity. Note that the 16-bit PRS used in the CSD without

the Clock Prescaler configuration provides better noise immunity. This configuration requires three digital blocks.

Because it needs a lower switching frequency, use this configuration when operating in an environment with high C

The relationship between CP and switching frequency is discussed in Select Prescaler.

P.

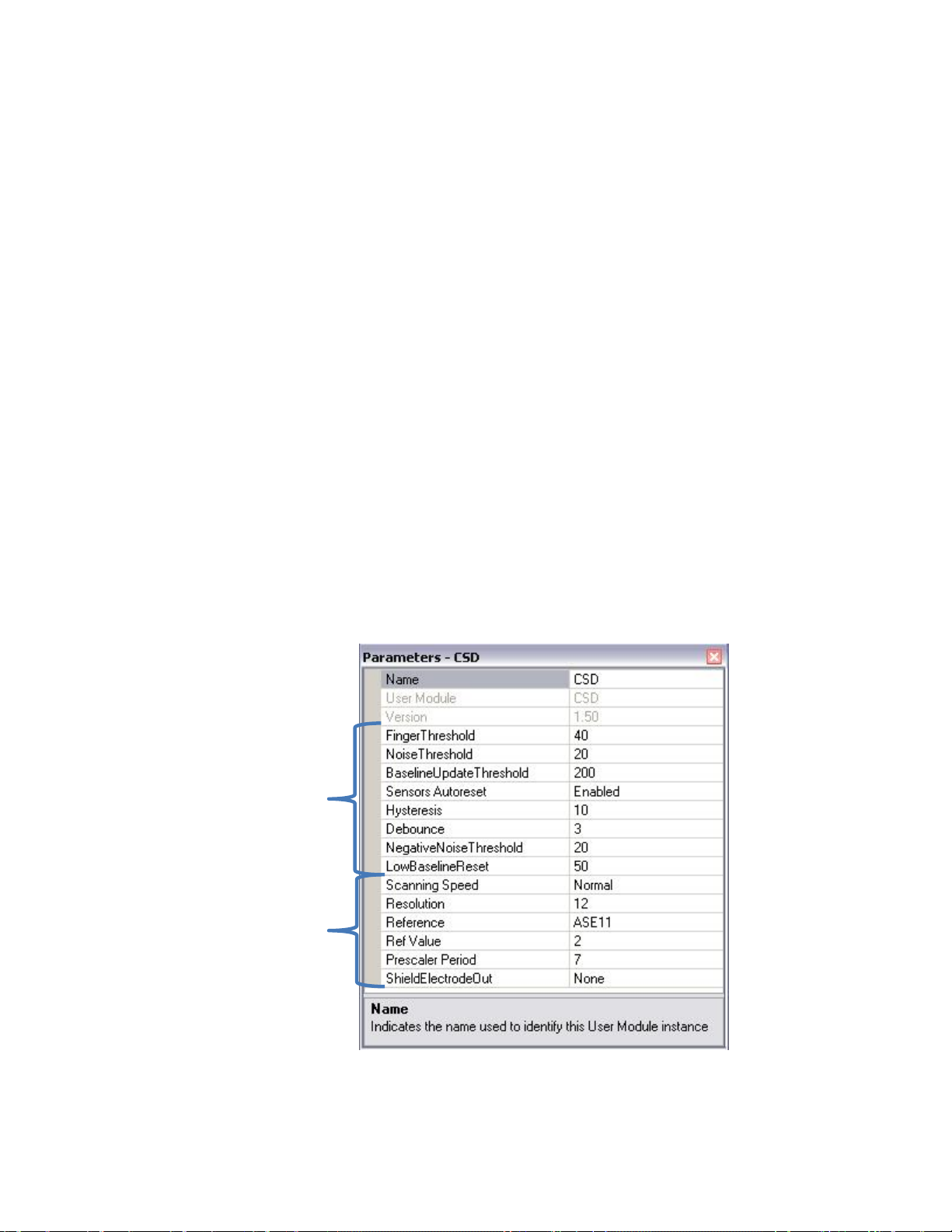

3.5 CSD User Module Parameters

The CSD User Module parameters are classified into high-level and low-level parameters. See Figure 3-5 for a list of

CSD user module parameters and how they are classified.

Figure 3-5. PSoC Designer - CSD Parameters Window

20 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 21

3.6 CSD User Module High-Level Parameters

3.6.1 Finger Threshold

The Finger Threshold parameter is used by the user module to judge the active/inactive state of a sensor. If the

Difference Count value of a sensor is greater than the Finger Threshold value, the sensor is judged as active. This

definition assumes that Hysteresis is set to zero and Debounce is set to 1.

Possible values are 5 to 255.

3.6.2 Noise Threshold

The user module uses the Noise Threshold value to interpret the upper limit of noise counts in the raw count. For

individual sensors, the baselining update algorithm is paused when the raw count is greater than the baseline and the

difference between them is greater than this threshold.

For slider sensors, the centroid calculation is paused when the difference count is greater than the Noise Threshold

value.

Possible values are 3 to 255. For proper user module operation, the Noise Threshold value should never be set

higher than Finger Threshold value minus the Hysteresis setting.

3.6.3 Baseline Update T hr eshold

When the raw count value is above the current baseline and the difference count is below the noise Threshold, the

difference between the current baseline and the raw count is accumulated into a "bucket." When the bucket fills

completely, the baseline increments and the bucket is emptied. The Baseline Update Threshold parameter sets the

threshold that the bucket must reach for the baseline to increment.

Possible values are 0 to 255.

3.6.4 Sensors Autor eset

The Sensors Autoreset parameter determines whether the baseline is updated at all times, or only when the

difference counts are less than the Noise Threshold value.

When Sensors Autoreset is enabled, the baseline is updated constantly. This limits the maximum time duration of the

sensor but prevents the sensors from permanently turning on when the raw count accidentally rises without anything

touching the sensor. This sudden rise can be caused by a large voltage fluctuation in the power supply, a high-energy

RF noise source, or a very quick temperature change.

When Sensors Autoreset is disabled, the baseline is updated only when the difference counts are less than the Noise

Threshold parameter.

Possible values are Enabled and Disabled.

3.6.5 Hysteresis

The Hysteresis setting prevents the sensor ON state from chattering because to system noise. The function of

Hysteresis is given in Equation 4. The equation assumes that Debounce is set to 1.

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 21

Page 22

Figure 3-6. Sensor State Versus Difference Count with Hysteresis Set to Zero

Equation 4

3.6.6 Debounce

The Debounce parameter prevents spikes in raw counts from changing the sensor state from OFF to ON. For the

sensor state to transition from OFF to ON, the Difference Count value must remain greater than the Finger Threshold

value plus the hysteresis level for the number of samples specified.

Possible values are 1 to 255. A setting of 1 provides no debouncing.

3.6.7 Negative Noise Threshold

The Negative Noise Threshold parameter acts as a negative difference count threshold. If the raw count is less than

the baseline minus the negative noise threshold for the number of samples specified by the Low Baseline Reset

parameter, the baseline is set to the new raw count value.

Possible values are 0 to 255.

3.6.8 Low Baseline Reset

The Low Baseline Reset parameter works in conjunction with the Negative Noise Threshold parameter. It counts the

number of abnormally low samples required to reset the baseline. It is used to correct the finger-on-at-startup

condition.

Possible values are 0 to 255.

3.6.9 High Level Parameter Recommendations

The following recommendations are a starting place for selecting the optimal parameter settings.

Finger Threshold: Set to 75 percent of Difference Counts with sensor ON

Noise Threshold: Set to 40 percent of Difference Counts with sensor OFF

Baseline Update Threshold: Set to two times Noise Threshold

Sensors Autoreset: Based on design requirements

Hysteresis: Set to 15 percent of Difference Counts with sensor ON

Debounce: Based on design requirements

22 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 23

Scanning Speed (µs)

Ultra Fast

Fast

Normal

Slow

Scanning Speed (µs)

Ultra Fast

Fast

Normal

Slow

Negative Noise Thresh old: Set equal to Noise Threshold

Low Baseline Reset: Set to 10

3.7 CSD User Module Low-Level Parameters

The CSD User Module has several low-level parameters in addition to the high-level parameters. These parameters

are specific to the CSD sensing method and determine how raw count data is acquired from the sensor.

3.7.1 Scanning Speed

This parameter sets the sensor scanning speed. Although a faster scanning speed provides a good response time,

slower scanning speeds give the following advantages:

Improved SNR

Better immunity to power supply and temperature changes

Less demand for system interrupt latency; you can handle longer interrupts

See Table 3-1 and Table 3-2 for scanning speed and resolution performance.

Possible values are Ultra Fast, Fast, Normal, and Slow.

3.7.2 Resolution

This parameter determines the scanning resolution in bits. The maximum raw count for scanning resolution of N bits

N-1

. Increasing the resolution improves sensitivity and SNR, but reduces scan time. See Table 3-1 and Table 3-2

is 2

for scanning speed and resolution performance. Possible values are 9 to 16 bits.

Table 3-1. Scanning Speed and Resolution for 24-MHz IMO Operation, without Clock Prescaler (PRS16

Configuration)

Resolution

(bits)

9 75 110 170 300

10 110 170 300 510

11 170 300 510 1010

12 300 510 1010 2030

13 510 1010 2030 4060

14 850 1690 3380 6760

15 1520 3040 6080 12200

16 2880 5720 11500 23200

Table 3-2. Scanning Speed and Resolution for 24- MHz IMO Operation, with Prescaler (PRS8 Configuration)

Resolution

(bits)

9 60 85 150 255

10 85 150 255 510

11 150 255 510 1020

12 255 510 1020 2040

13 510 1020 2010 4080

14 845 1700 3380 6760

15 1530 3060 6120 12100

16 2880 5800 11500 23000

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 23

Page 24

3.7.3 Reference

A voltage reference to the input of the comparator is required for the proper operation of CSD.

Possible values are:

VBG: Internal voltage reference of 1.3 V derived from a fixed bandgap reference.

ASE11: Internal variable voltage reference derived from a PWM.

AnalogColumn_InputSelect_1: External voltage reference such as a resistor divider network or externally filtered

PWM/PRSPWM signal. This reference can be connected to a CapSense controller pin and used as the

comparator reference source.

3.7.4 Ref Value

The effect of this parameter depends on the Reference parameter selection. This value has no effect when the

reference comes from the VBG or from AnalogColumn_InputSelect_1. When the reference comes from ASE11, this

parameter sets the reference value.

Possible values are: 0 (minimum ¼V

) to 8 (maximum ¾ VDD).

DD

3.7.5 Prescaler Period

The sensor capacitance is switched continuously between two potentials while scanning. This parameter sets the

prescaler period register and determines the precharge switch output frequency. This parameter is available only for

CSD with the clock prescaler configuration.

Possible values are1 to 255.

3.7.6 Shield Electrod e O ut

Shield Electrode Out should be enabled for applications requiring water-tolerant performance. The shield electrode

signal source can be selected from one of the free digital row buses (Row_0_Output_1 to Row_0_Output_3). Each

row output can be routed to one of three pins. Set the Row LUT Function to A.

Possible values are Enabled and Disabled.

3.8 CSDADC User Module Configurations

The CSDADC combines capacitance sensing with ADC functionality. It saves code space by reusing modules

common to both the CSD and ADC. You should use the CSDADC when your design requires both capacitance

sensing and ADC functionality. Applications that need one or the other should use the CSD User Module or the ADC8

or ADC10 User Modules.

There are four selectable clock configurations for the CSDADC User Module: PRS16, PWM8, PRS8, and VC2. These

configurations use different signal sources for the switched capacitor circuit on the front end of the CSD

You should select the clock configuration when you first place the CSDADC User Module into your PSoC Designer

project. You can change this selection later by right-clicking the CSD ADC User Module and selecting User Module

Selection Options.

3.8.1 CSDADC with PRS16 Clock Source

In this configuration, a 16-bit pseudo-random sequence (PRS) is used as the signal source for the switched-capacitor

circuit on the front end of the CSD. System Clock (IMO) is the clock source for the PRS. The PRS spreads the clock’s

frequency spectrum and provi des good noise immunity. This configuration requires three digital blocks.

3.8.2 CSDADC with PRS8 Clock Source

In this configuration, an 8-bit PRS is used as the signal source for the switc hed-capacitor circuit on the front end of

the CSD. System Clock (IMO) is the clock source for the PRS. The PRS spreads the clock’s frequency spectrum to

give noise immunity. Note that the 16-bit PRS used in the CSD without the Clock Prescaler configuration provides

better noise immunity. This configuration requires three digital blocks.

24 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 25

Because it needs a lower switching frequency, you should use configuration when operating in an environment with

high C

User Modules.

, The relationship between CP and switching frequency is discussed in CapSense Performance Tuning with

P

3.8.3 CSDADC with PWM8 Clock Source

In this configuration, IMO is divided by an adjustable prescaler divider and used for the switched capacitor circuit on

the front end of the CSD. This configuration is more sensitive to noise at the frequency of operation and its

harmonics. This configuration requires two digital blocks.

This configuration is suitable for sensing through high-resistance materials (such as ITO) or when you want low

operation frequency because of emission problems.

3.8.4 CSDADC with VC2 Clock Source

In this configuration, the system clock is divided using an adjustable divider, VC2, and used for the switchedcapacitor circuit on the front end of the CSD. This configuration is more sensitive to noise signals at the frequency of

operation and its harmonics. This configuration requires one digital block.

This configuration is suitable for sensing through high-resistance materials (such as ITO) or when you want low

operation frequency because of emission problems.

3.9 CSDADC User Module Parameters

Figure 3-7. PSoC Designer - C SDAD C Parameters Windows

3.10 Low-Level Parameters

3.10.1 Scanning Speed

This parameter sets sensor scanning speed. Although faster scanning speed provides good response time, slower

scanning speeds provide the following advantages:

Improved SNR

Better immunity to power supply and temperature changes

Less demand for system interrupt latency; you can handle longer interrupts

See Table 3-1 and Table 3-2 for scanning speed and resolution performance. Possible values are Ultra Fast, Fast,

Normal, and Slow.

3.10.2 Resolution

This parameter determines the scanning resolution in bits. The maximum raw count for scanning resolution of N bits

N-1

is 2

. Increasing the resolution improves sensitivity and SNR, but reduces scan time. See Table 3-1 and Table 3-2

for scanning speed and resolution performance.

Possible values are 9 to 16 bits.

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 25

Page 26

3.10.3 Reference

A voltage reference to the input of the comparator is required for the proper operation of CSD.

Possible values are:

VBG: Internal voltage reference of 1.3 V derived from a fixed band-gap reference.

ASE11: Internal variable voltage reference derived from a PWM.

AnalogColumn_InputSelect_1: External voltage reference such as a resistor divider network or externally filtered

PWM/PRSPWM signal. This reference can be connected to a CapSense controller pin and used as the

comparator reference source.

3.10.4 Ref Value

The effect of Ref Value depends on the Reference parameter. When Reference is set to ASE11, Ref Value sets the

reference value.

Possible values are 0 (minimum ¼ VDD) to 8 (maximum ¾ VDD).

Increasing Ref Value decreases sensitivity, but increases the influence on the shield electrode. If the design has

sensors with noticeable capacitance differences (sensor pads of different sizes), you can use an API function to

balance raw counts by setting a higher Ref Value for the sensors with larger capacitance.

Ref Value has no effect when Reference is set to VBG or AnalogColumn_InputSelect_1. Ref Value is not available in

CSDADC with the VC2 clock source configuration.

3.10.5 Prescaler Period

Prescaler Period determines the precharge switch output frequency.

Possible values are 1 to 255. The recommended values are 2

15, 31, 63, 127, or 255). Other values can result in more noise, especially at low resolution and high scan speed.

Prescaler Period is available only for configurations with prescaler.

n – 1

to obtain the maximum signal-to-noise rati o (1 , 3, 7,

3.10.6 Shield E lec tr od e Out

The shield electrode signal source can be selected from one of the free digital row buses (Row_0_Output_1 to

Row_0_Output_3). Each row output can be routed to one of three pins. Set the Row LUT Function to A.

Possible values are Enabled and Disabled.

This parameter is available only in CSDADC with the PRS8/PRS16 clock source configurations. In CSDADC with the

PWM8 clock source configuration, the shield electrode signal is permanently connected to Row_0_Output_0.

3.10.7 ADC Enabled

When this parameter is set to Enabled, the ADC routines are included in the compliable code and can be called from

user code. When this parameter is set to Disabled, the ADC routines are not included. Setting this parameter to

Disabled can be useful in saving the flash memory if the ADC is no longer required by your design. When this

parameter is set to Disabled, the CSDADC User Module behaves the same as the CSD User Module.

26 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 27

High-Level

Low-Level

Low-Level

Low-Level

High-Level

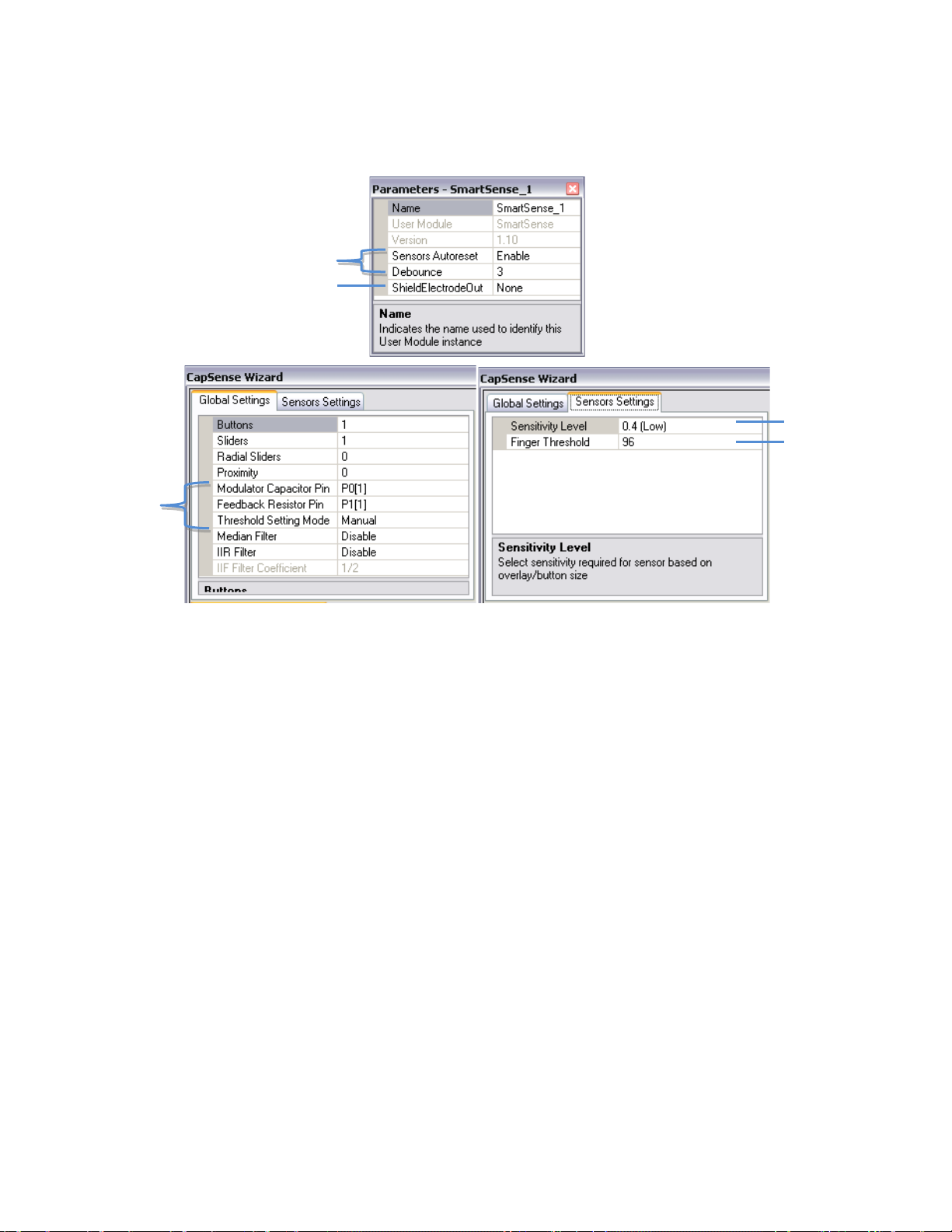

3.11 SmartSense User Module Parameters

Figure 3-8. PSoC Designer SmartSense Parameters

3.12 Low-Level Parameters

3.12.1 Shield E lec tr od e Out

A shield electrode is used to reduce parasitic capacitance. The shield electrode signal can be routed to one of the

free digital row buses (Row_0_Output_1 – Row_0_Output_3). Each row output can then be routed to one of the

allowed pins. Set the Row LUT Function to A.

3.12.2 Modulator Capacitor Pin

This parameter sets the pin to connect the external modulator capacitor (C

P0[3].

3.12.3 Feedback Resistor Pin

This parameter sets the pin to connect the external feedback resistor (Rb). Choose from the available pins: P1[1],

P1[5], P3[1]. Some pins are not available on some device packages. Use pins P1[5] or P3[1] to avoid programming

problems.

3.12.4 Threshold Setting Mode

Use this parameter to select between Automatic and Manual threshold settings.

3.12.5 Sensitivity Level

This parameter is used to increase and decrease the sensitivity of a sensor. Possible values are 0.1 pF (highest

sensitivity), 0.2 pF, and 0.4 pF (lowest sensitivity). Use a higher sensitivity setting for thicker overlay on capacitive

sensors.

). Choose from the available pins P0[1],

MOD

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 27

Page 28

3.12.6 Finger Threshold

This parameter is applicable only when threshold setting mode is set to Manual mode. It is recommended that you set

this value to 80 percent of the sensor signal stored in the SmartSense_baSnSSignal[] array. This array can be easily

monitored using I

2

C or UART communication protocols.

28 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 29

4. CapSense Performance Tuning with User Modules

Optimal user module parameter settings depend on board layout, button dimensions, overlay material, and

application requirements. These factors are discussed in Design Considerat ions. Tuning is the process of identifying

the optimal parameter settings for robust and reliable sensor operation.

4.1 General Considerations

4.1.1 Signal, Noise, and SNR

A well-tuned CapSense system reliably discriminates between ON and OFF sensor states. To achieve this level of

performance, the CapSense signal must be significantly larger than the CapSense noise. The measure that

compares signal to noise is the signal-to-noise ratio (SNR). Before discussing the meaning of SNR for CapSense, it is

first necessary to define signal and noise in the context of touch sensing.

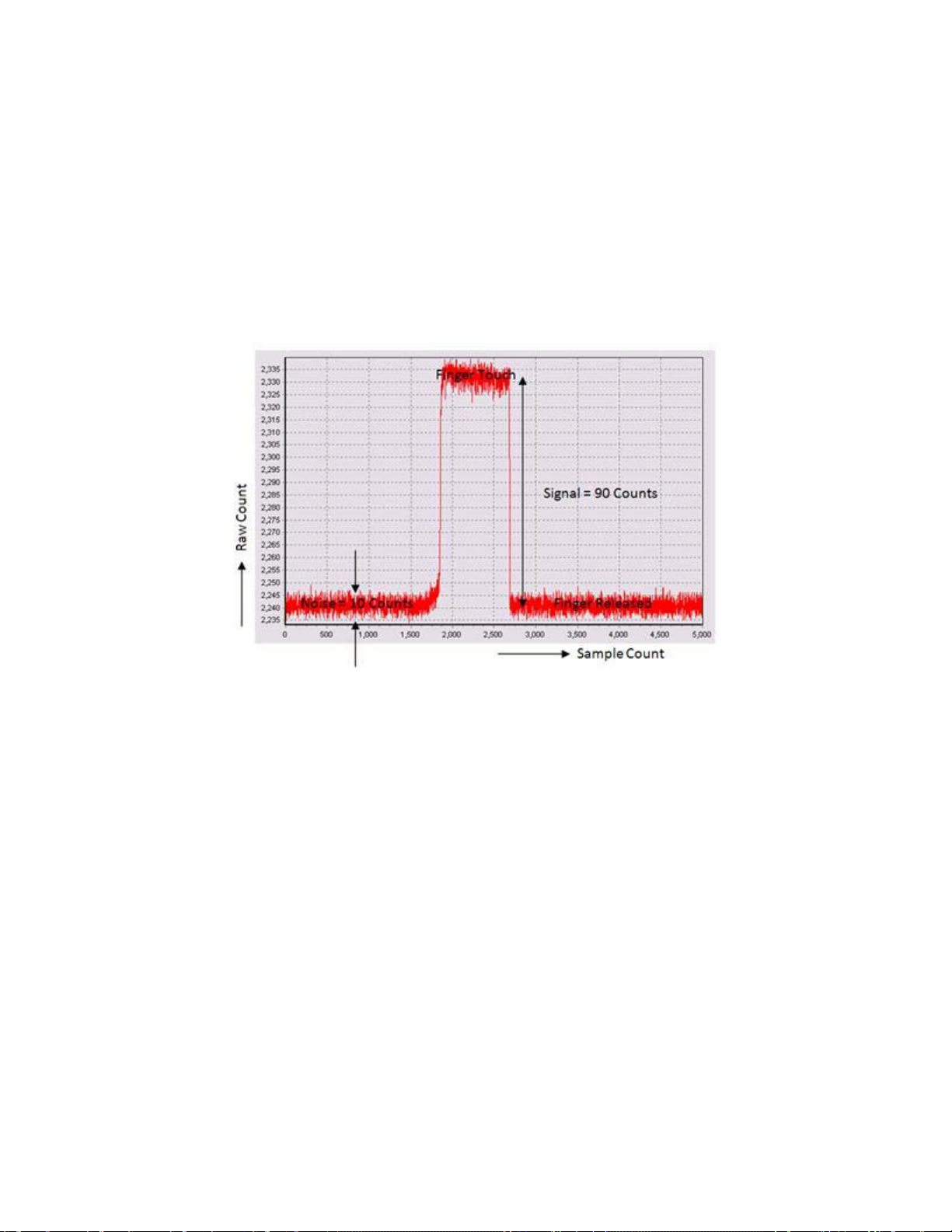

4.1.1.1 CapSense Signal

The CapSense signal is the change in the sensor response when a finger is placed on the sensor, as demonstrated

in Figure 4-1. The output of the sensor is a digital counter with a value that tracks the sensor capacitance. In this

example, the average level without a finger on the sensor is 5925 counts. When a finger is placed on the sensor, the

average output increases to 6060 counts. Because the CapSense signal tracks the change in counts due to the

finger, Signal = 6060 – 5925 = 135 counts.

Figure 4-1. Example of CapSense Signal

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 29

Page 30

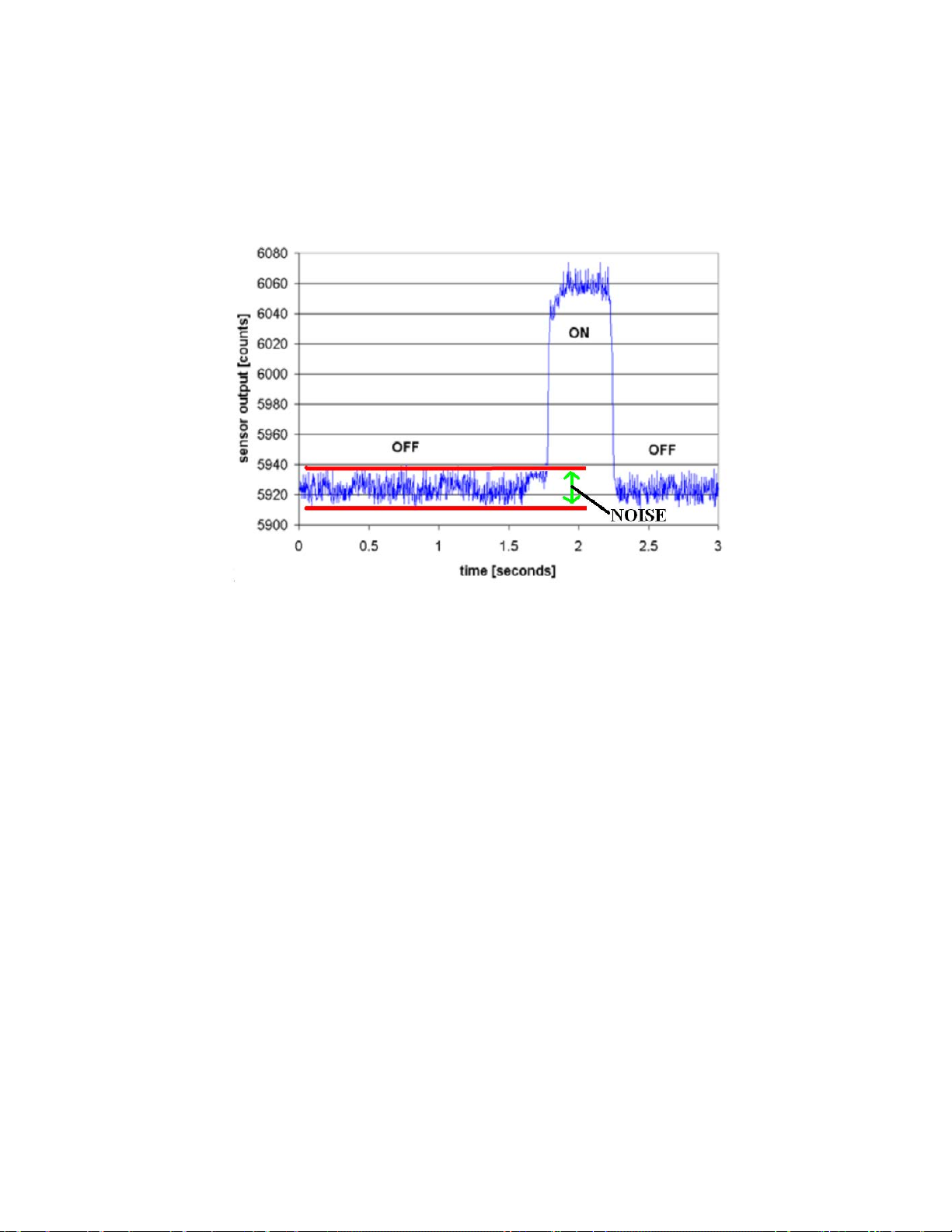

4.1.1.2 CapSense Noise

CapSense noise is the peak-to-peak variation in sensor response when a finger is not present, as shown in

Figure 4-2. In this example, the output waveform without a finger is bounded by a minimum of 5912 counts and a

maximum of 5938 counts. Because the noise is the difference between the minimum and the maximum values of this

waveform, Noise = 5938 – 5912 = 26 counts.

Figure 4-2. Example of CapSense Noise

4.1.1.3 CapSense SNR

CapSense SNR is the simple ratio of signal and noise. Continuing with the example, if the signal is 135 counts and

noise is 26 counts, and then SNR is 135:26, which reduces to an SNR of 5.2:1. The minimum recommended SNR for

CapSense is 5:1, which means the signal is five times larger than the noise. Filters are commonly implemented in

firmware to reduce noise. See Software Filtering for more informat ion.

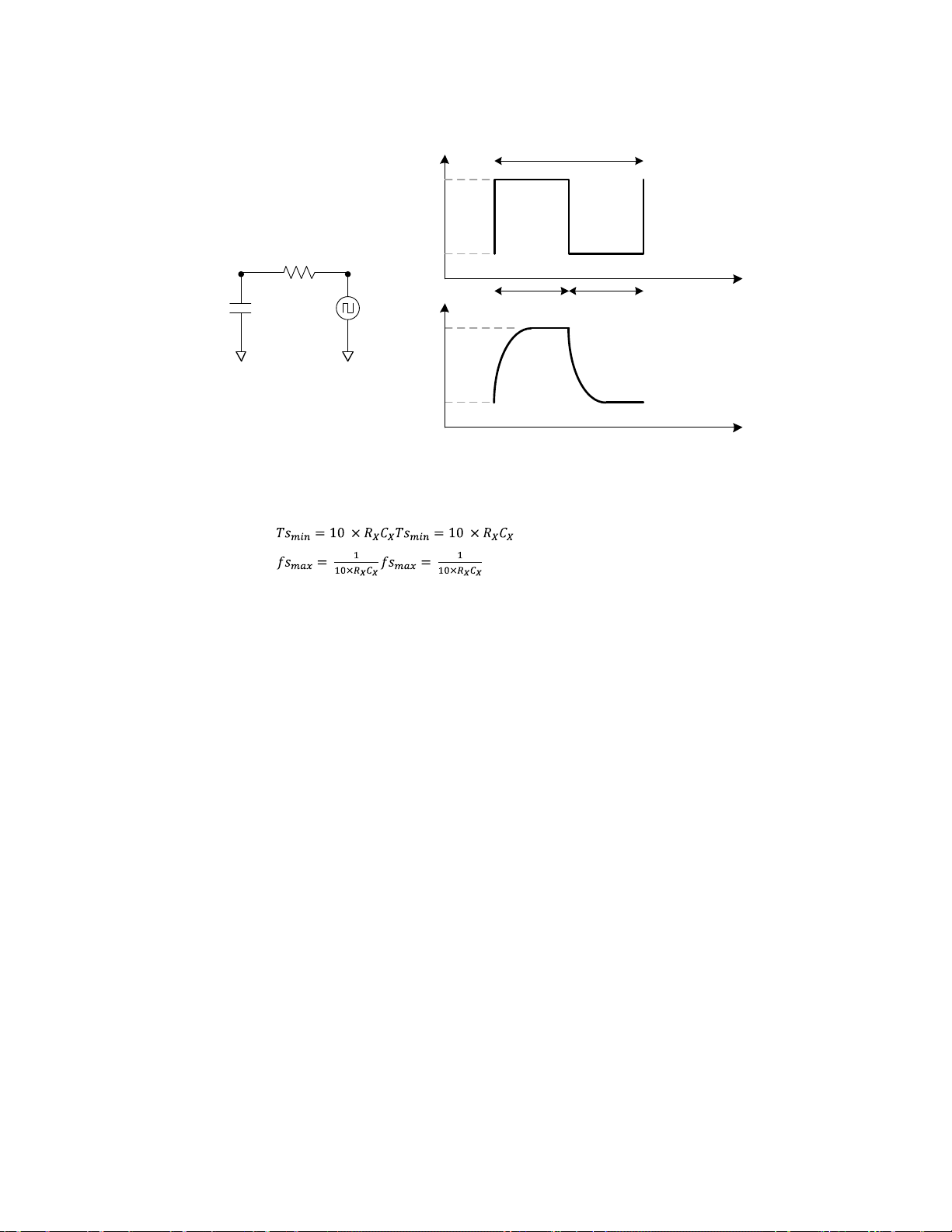

4.1.2 Charge/Discharge Rate

To achieve maximum sensitivity in the tuning process, the sensor capacitor must be charged and discharged fully

during each cycle. The charge/discharge path switches between two states at a rate set by the Clock parameter in

the User Module.

The charge/discharge path includes series resistance that slows down the transfer of charge. The rate of change for

this charge transfer is characterized by an RC time constant involving the sensor capacitor and series resistance, as

shown in Figure 4-3.

30 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 31

V

s

V

x

Vdd

Vref

Vdd

Vref

t

t

R

x

C

x

V

s

V

x

5*R

x

*C

x

5*R

x

*C

x

Ts

min

>= 10*R

x

*C

x

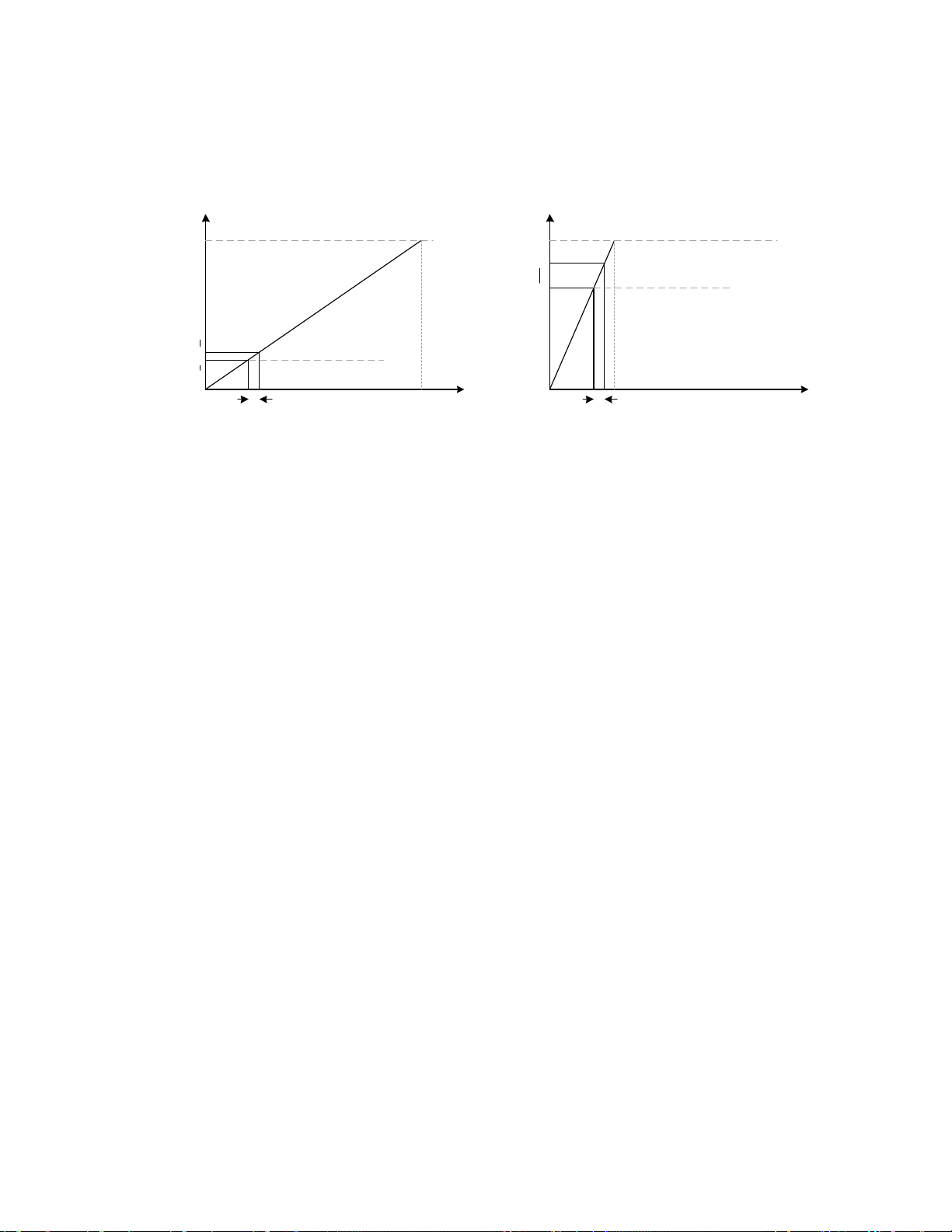

Figure 4-3. Charge/Discharge Waveforms

Make sure to set the charge/discharge rate to a level that is compatible with this RC time constant. The rule of thumb

is to allow a period of 5RC for each transition, with two transitions per period (one charge, one discharge).The

equations for minimum time period and maximum freq uen cy are:

Equation 5

Equation 6

For example, assume the series resistor includes a 560-Ω external resistor and up to 800 Ω of internal resistance and

the sensor capacitance is typical:

RX = 1.4 kΩ

C

= 24 pF

X

The value of the time constant and maximum front-end switching frequency in this example would be:

Ts

= 0.34 µs

min

fs

= 3 MHz

max

4.1.3 Importance of Baseline Update Threshold Verification

Temperature and humidity both cause the average number of counts to drift over time. The baseline is a reference

count level for CapSense measurements that is an important part of compensating for environmental effects. Highlevel decisions, such as Finger Present and Finger Absent states, are based on the reference level established by the

baseline. Because each sensor has unique parasitic capacitance associated with it, each capacitive sensor has its

own baseline.

Baseline tracks the change in counts at a rate set by the Baseline Update Threshold parameter. Make sure to match

the update rate to the intended application. If the update rate is too fast, the baseline will compensate for any

changes introduced by a finger, and the moving finger will not be detected. If the update rate is too slow, relatively

slow environmental changes may be mistaken for fingers. During development, you should verify the Baseline

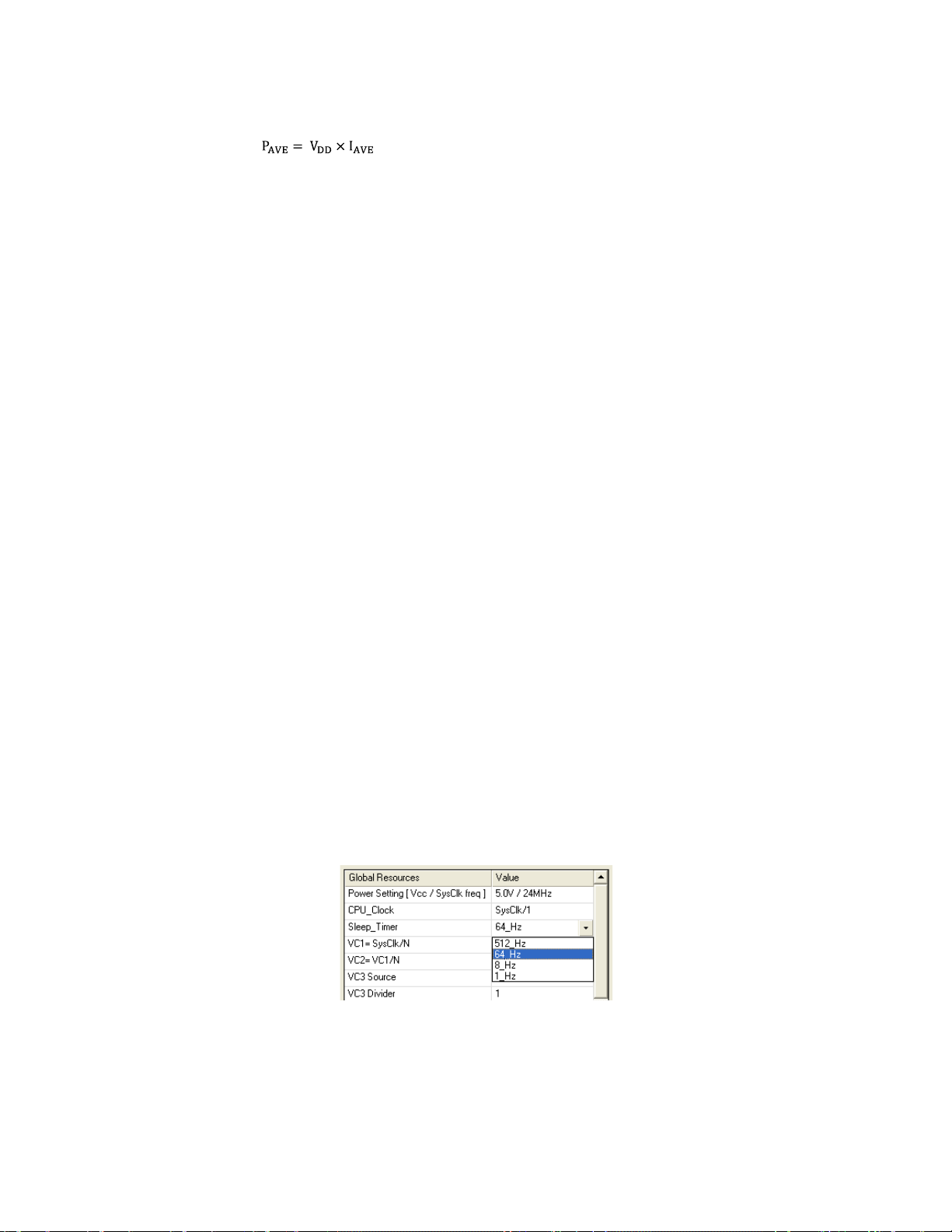

Update Threshold settings.

CY8C21x34/B CapSense® Design Guide Document No. 001-66271 Rev. *B 31

Page 32

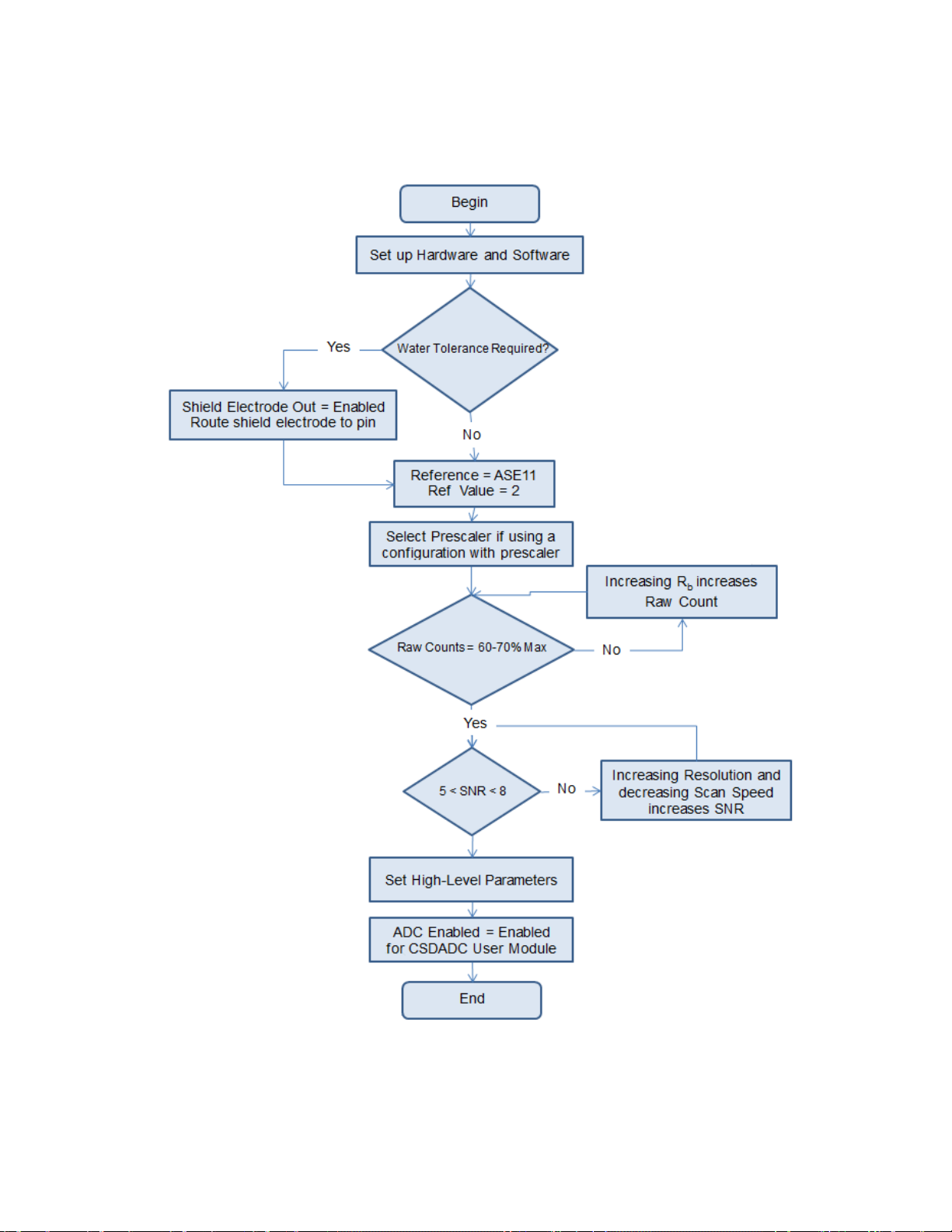

4.2 Tuning the CSD and CSDADC User Modules

Figure 4-4. Tuning CSD and CSDADC User Modules

32 Document No. 001-66271 Rev. *B CY8C21x34/B CapSense

®

Design Guide

Page 33

4.2.1 Set Up Hardware and S o ftw ar e for Tuni ng

Before starting the tuning process, certain hardware and software tools are required. They are listed in the Overview

of CapSense Design Tools. Tuning requires monitoring the raw counts, baseline, and difference counts of the

sensors through a communication interface. A code example that uses an I

communicate with the PC can be downloaded here. After do wnloading the example project:

1. Open the code example using PSoC Designer. In Workspace Explorer, right-click CSD User M odule and select

CSD Wizard. You are shown four CapSense buttons assigned to the pins. Change the number of buttons and

pin assignments according to your application requirements.

2. Change Modulator Capacitor Pin and Feedback Resistor Pin, if required.

3. Generate and build the project.

4. Program the CapSense controller with the hex file.

5. Refer to “Instructions to use USB-I2C Tool to Monitoring CapSense Data” found in the code example’s

documentation for instructions on how to monitor raw count, baseline, and difference count.

2

C communication protocol to

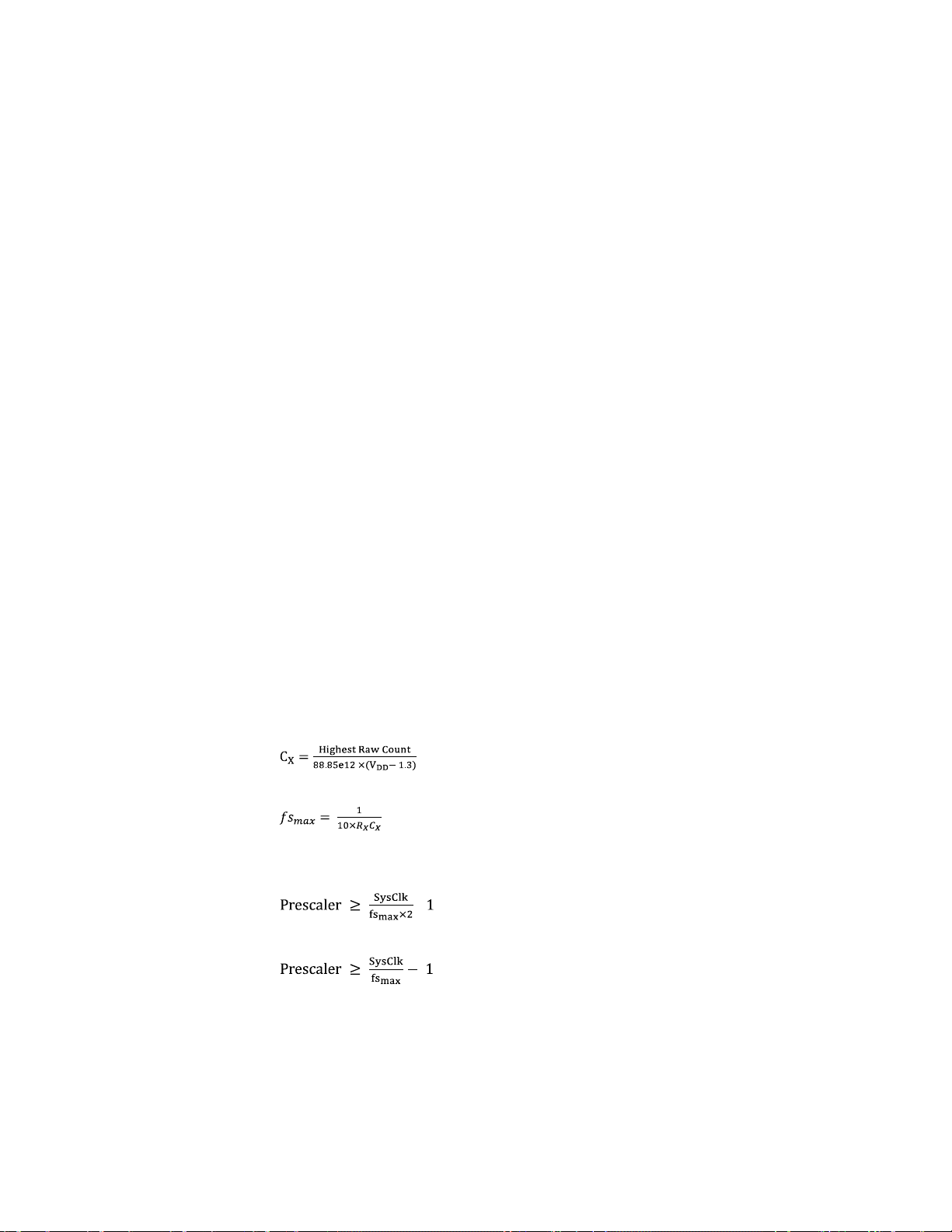

4.2.2 Select Prescaler

To select the Prescaler value, use the following process:

1. Measure the maximum sensor parasitic capacitance using an LCR meter or the CapSense controller. If you are

using an LCR meter, skip to Step 5.