CYGNL C8051F206 Datasheet

C8051F206

C8051F206

C8051F206 C8051F206

Mixed-Signal 8KB ISP

FLASH MCU

PRELIMINARY

ANALOG PERIPHERALS

12-bit, 32-Channel ADC

- 32 External Inputs (Each Port I/O can be configured

as an ADC Input on the Fly!)

- Programmable Throughput up to 100ksps

- Programmable Amplifier Gains of 16,8,4,2,1, and 0.5

- No Missing Codes

- VREF from External Pin or VDD

Two Comparators

- Programmable Hysteresis

- Configurable to Generate Interrupts or Reset

VDD Monitor and Brown-out Detector

ON-CHIP JTAG DEBUG

- On-Chip Debug Circuitry Facilitates Full Speed, NonIntrusive In-System Debug (No Emulator Required!)

- Provides Breakpoints, Single Stepping, Watchpoints,

Stack Monitor

- Inspect/Modify Memory and Registers

- Superior Performance to Emulation Systems Using

ICE-Chips, Target Pods, and Sock ets

- Low Cost, Complete Development Kit: $99

SUPPLY VOLTAGE .....................2.7V to 3.6V

- Typical Operating Current: 9mA @ 25MHz

0.1uA (sleep mode)

8051-COMPATIBLE µµµµC Core

- Pipelined Instruction Architecture; Executes 70%

of Instructions in 1 or 2 System Clocks

- Up to 25MIPS Throughput with 25MHz Clock

- Expanded Interrupt Handler; Up to 21 Interrupt

Sources

MEMORY

- 1280 Bytes Data RAM (256 + 1k)

- 8k Bytes FLASH; In-System Programmable in 512

byte Sectors

DIGITAL PERIPHERALS

- 32 Port I/O; All are 5V tolerant

- Hardware SPI

TM

and UART Serial Ports Available

Concurrently

- Three 16-bit Counter/Timers

- Dedicated Watch-Dog Timer

- Bi-directional Reset

CLOCK SOURCES

- Internal Programmable Oscil lator: 2-to- 1 6MH z

- External Oscillator: Crystal, RC, C, or Clock

- Can Switch Between Clock Sources on-the-fly;

Useful in Power Saving Modes

Temperature Range: –40°°°°C to +85°°°°C

48-Pin TQFP Package

SPI is a trademark of Motorola, Inc.

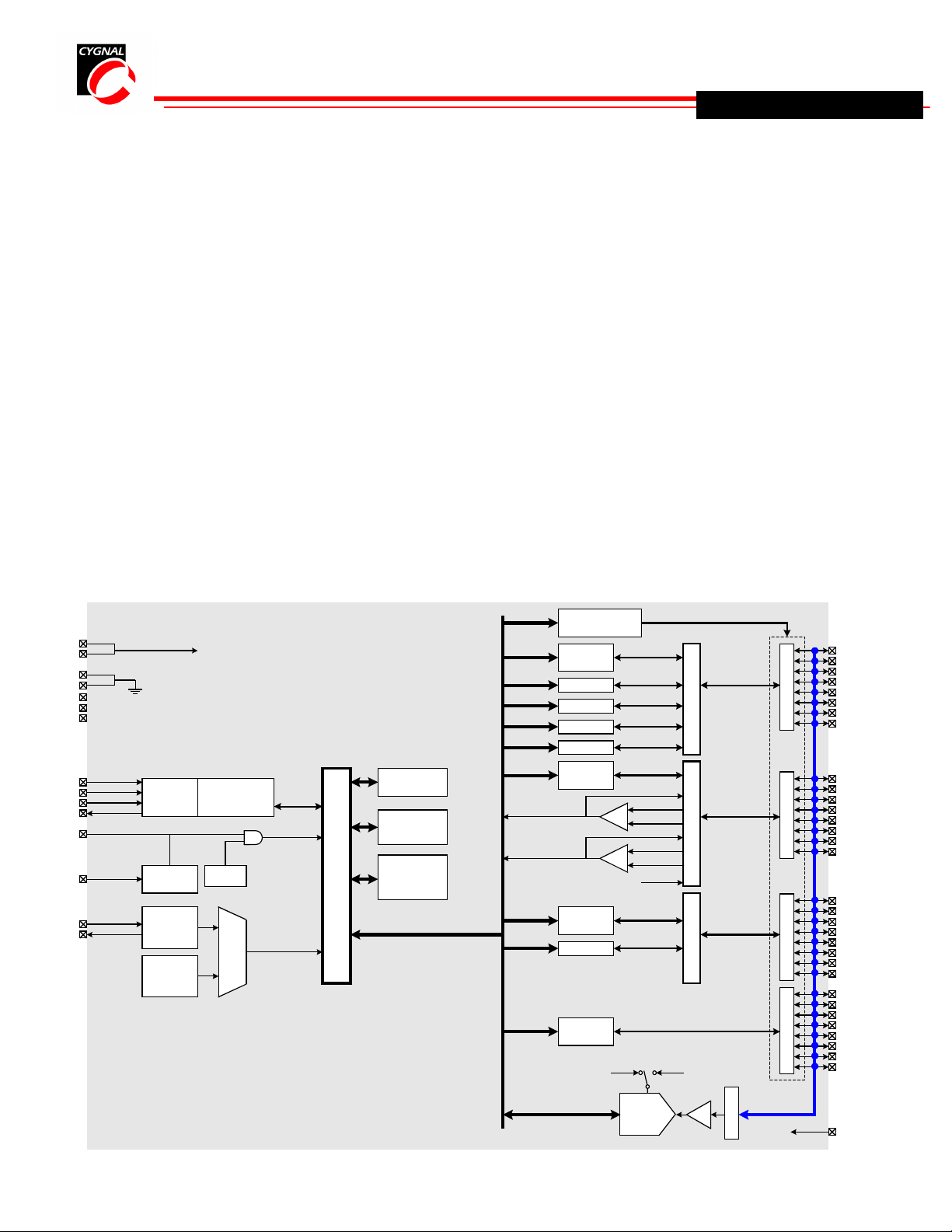

VDD

VDD

GND

GND

TCK

TMS

TDI

TDO

/RST

MONEN

XTAL1

XTAL2

Port I/O Mode

Analog/Digital

Power

NC

NC

NC

8kbyte

JTAG

Logic

Debug HW

Reset

8

0

5

FLASH

256 byte

RAM

1

VDD

Monitor

WDT

1024 byte

XRAM

C

External

Oscillator

Circuit

Internal

Oscillator

System Clock

o

SFR Bus

r

e

& Config.

Port 0

Latch

UART

Timer 0

Timer 1

Timer 2

Port 1

Latch

CP0

CP1

Port 2

Latch

SPI

Port 3

Latch

CP0

CP1

VDD

CP0+

CP0-

CP1+

CP1-

SYSCLK

VREF

P

0

M

U

X

P

1

M

U

X

P

2

M

U

X

P

0

D

r

v

P

1

D

r

v

P

2

D

r

v

P

3

D

r

v

P0.0/TX

P0.1/RX

P0.2//INT0

P0.3//INT1

P0.4/T0

P0.5/T1

P0.6/T2

P0.7/T2EX

P1.0/CP0+

P1.1/CP0P1.2/CP0

P1.3/CP1+

P1.4/CP1P1.5/CP1

P1.6/SYSCLK

P1.7

P2.0/NSS

P2.1/MISO

P2.2/MOSI

P2.3/SCK

P2.4

P2.5

P2.6

P2.7

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

12-bit

100ksps

ADC

PGA

A

M

U

X

AIN0-AIN31

VREF

5.23.2001

C8051F206

C8051F206

C8051F206 C8051F206

Mixed-Signal 8KB ISP

FLASH MCU

PRELIMINARY

SELECTED ELECTRICAL SPECIFICATIONS TA = -40°C to +85°C unless otherwise specified.

PARAMETER CONDITIONS MIN TYP MAX UNITS

GLOBAL CHARACTERISTICS

Digital Supply Voltage 2.7 3.6 V

Digital Supply Current with

CPU active (VDD=2.7V)

Digital Supply Current

(shutdown)

Clock=25MHz

Clock=1MHz

Clock=32kHz; VDD Monitor Disabled

Oscillator not running; VDD Monitor

Enabled

Oscillator not running; VDD Monitor

9

0.7

20

10

0.1

mA

mA

µA

µA

µA

Disabled

Digital Supply RAM Data

1.5 V

Retention Voltage

CPU & DIGITAL I/O PORTS

Clock Freque ncy Range DC 25 MHz

Port Output High Voltage IOH = -3mA, Port I/O push-pull VDD – 0.7 V

Port Output Low Voltage IOL = 8.5mA 0.6 V

Input High Voltage 0.7 x VDD V

Input Low Voltage 0.3 x VDD V

SPI Bus Clock Frequency fCLK=MCU Clock; SPI in M aster Mode fCLK/2 MHz

A/D CONVERTER

Resolution 12 bits

Integral Nonlinearity

Differential Nonlinearity Guaranteed Monotonic

Signal-to-Noise Plus

± 1 ± 2

± 1

64 dB

LSB

LSB

Distortion

Throughput Rate 100 ksps

Input Voltage Range 0 VREF V

COMPARATORS

Response Time | CP+ – CP- | = 100mV 4

µs

Input Voltage Range -0.25 VDD + 0.25 V

Input Bias Current -5 0.001 +5 nA

Input Offset Voltage -10 +10 mV

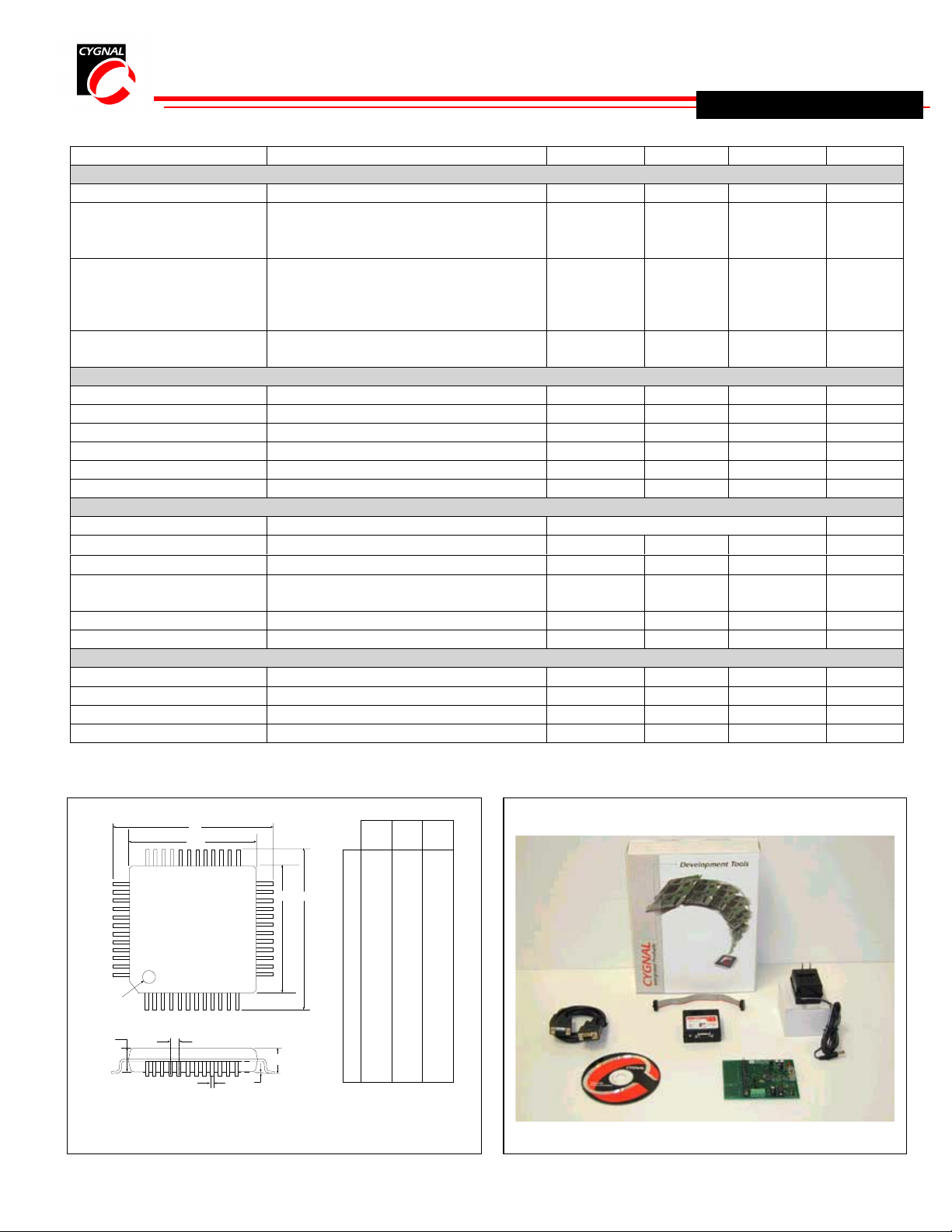

PACKAGE INFORMATION

D

D1

48

PIN 1

IDENTIFIER

1

A2

e

b

MIN

C8051F206DK DEVELOPMENT KIT ($99)

NOM

(mm)

-

-

1.00

0.22

9.00

7.00

0.50

9.00

7.00

MAX

(mm)

1.20

0.15

1.05

0.27

-

-

-

-

-

(mm)

A

-

A1

A2

D1

E1

0.05

0.95

b

0.17

D

-

-

e

-

E

-

-

E1

E

A

A1

Loading...

Loading...