CRD4201-2

CrystalClear™ AC '97 Six Channel Primary ACR Audio Reference Design

Features

l Six Channel Analog Audio Output

l Built-in Headphone Amplifier

l CS4201 audio codec and CS4334 DACs

l 20-bit D to A conversion (DAC)

l 18-bit A to D conversion (ADC)

l S/PDIF (IEC-958) optical digital output

l Complete suite of Analog I/O connections:

– Line, Mic, CD, Video and Aux Inputs

– Line Front, and Line Rear Outputs

l 2-layer low cost PC board

l Meets Intel

l Exceeds Microsoft’s

audio performance requirements.

®

AC ‘97 version 2.1 specification

®

PC 99 and PC-2001

Description

The CRD4201-2 Advanced Communications Riser

(ACR) reference design features six channel analog audio outputs and a optical S/PDIF digital output. This

board uses the CS4201 audio codec which has several

advanced features such as a built-in headphone amplifier, up to 30 dB of microphone boost, and serial digital

audio outputs.

The CRD4201-2 reference design is available by ordering the CMK4201-2 manufacturing kit. This kit includes

a full set of schematic design files (OrCAD

®

CAD

9.1 formats), PCB job files (PADS® ASCII), PCB

artwork files, and bill of materials. This reference design

offers significant cost savings over competing solutions

and can be easily modified to meet your specific design

goals.

ORDERING INFO

CMK4201-2 (Manufacturing Kit)

®

7.2 and Or-

Microphone Input

Front Channel Outputs

Front Channel Outputs

Headphone Output

Rear Channel Outputs

Center Channel and

Sub-Woofer Outputs

S/PDIF Digital

Optical Output

Preliminary Product Information

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

MIC

IN

AUX INVIDEO INCD ININT MODEM

LINE

IN

LINE

OUT

HEADPH

OUT

SURR

OUT

CNT/LFE

OUT

S/PDIF

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

Copyright Cirrus Logic, Inc. 2001

Cirrus Logic

CRD4201-2

CS4201

OUT

(All Rights Reserved)

DS483RD2A2

JUN ‘01

1

TABLE OF CONTENTS

1. GENERAL INFORMATION ...................................................................................3

2. SCHEMATIC DESCRIPTION ................................................................................3

2.1 CS4201 Audio Codec .................................................................................3

2.2 Analog Inputs ..............................................................................................3

2.3 Rear, Center and Sub-Woofer Outputs ......................................................4

2.4 Front Channel and Headphone Outputs ....................................................4

2.5 S/PDIF Optical Output ...............................................................................4

2.6 ACR Connector and EEPROM ...................................................................4

2.7 Component Selection .................................................................................4

2.8 EMI Components ........................................................................................5

3. GROUNDING AND LAYOUT ................................................................................5

3.1 Partitioned Voltage and Ground Planes .....................................................5

3.2 CS4201 Layout Notes .................................................................................5

4. REFERENCES .......................................................................................................6

4.1 ADDENDUM ...............................................................................................6

5. BILL OF MATERIALS .........................................................................................19

LIST OF FIGURES

CRD4201-2

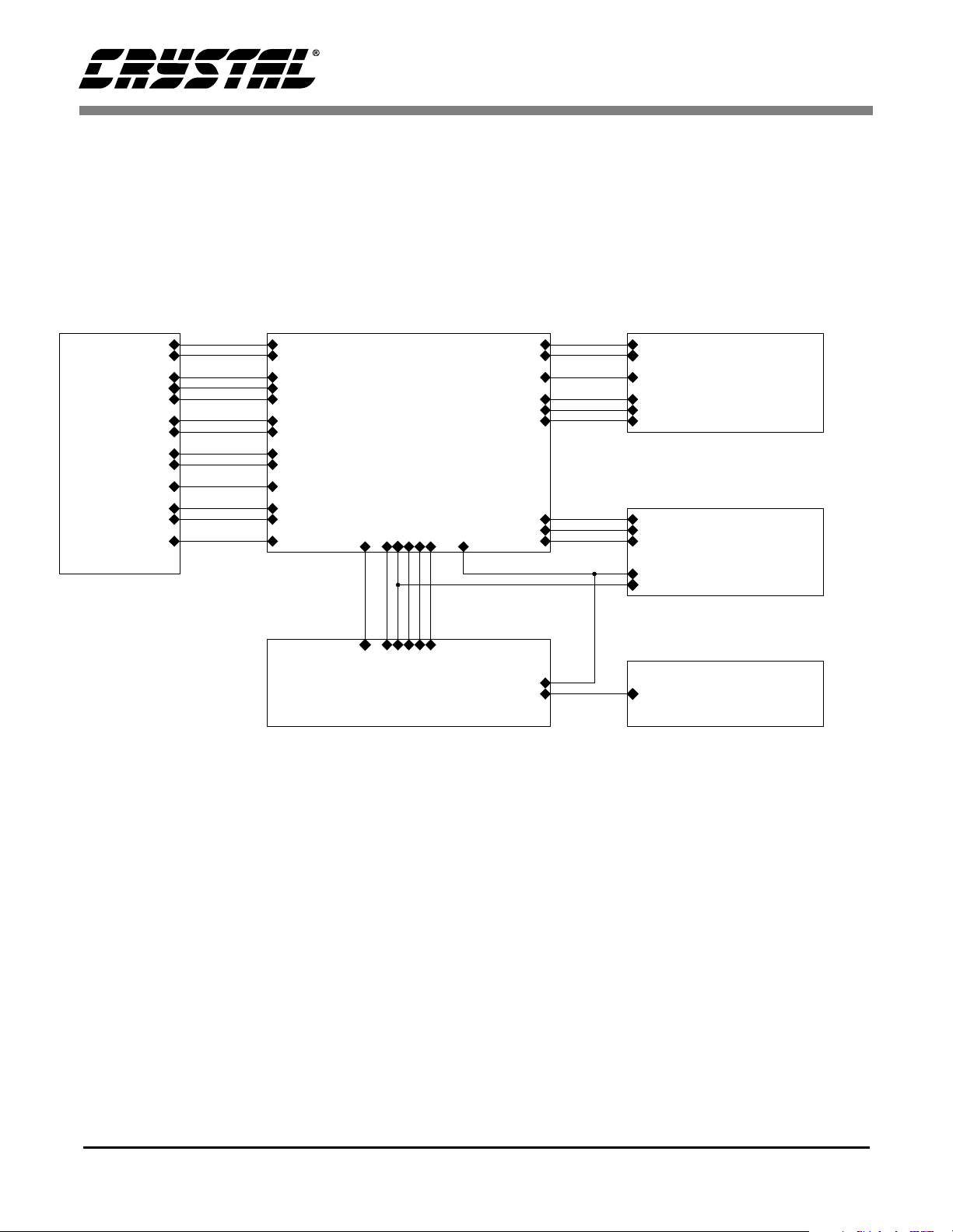

Figure 1. Block Diagram ....................................................................................................7

Figure 2. CS4201 Audio Codec .........................................................................................8

Figure 3. Analog Inputs ......................................................................................................9

Figure 4. Rear, Center, and Sub-Woofer Outputs ...........................................................10

Figure 5. Front Channel and Headphone Outputs ..........................................................11

Figure 6. S/PDIF Optical Output ......................................................................................12

Figure 7. ACR Connector .................................................................................................13

Figure 8. PCB Layout: Top Assembly Drawing ................................................................14

Figure 9. PCB Layout: Top Layer ....................................................................................15

Figure 10. PCB Layout: Bottom Layer .............................................................................16

Figure 11. PCB Layout: Drill Drawing ..............................................................................17

Figure 12. PCB Layout: Top Silkscreen ..........................................................................18

Contacting Cirrus Logic Support

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at:

http://www.cirrus.com/corporate/contacts/

Microsoft , Windows 95, Windows 98 and Windows Millennium and WHQL is registered trademark of Microsoft.

CrystalClear is a trademark of Cirrus Logic, Inc.

Intel is a registered trademark of Intel Corporation.

OrCAD is a registered trademark of OrCAD, Inc.

PADS is a registered trademark of, PADS Software, Inc.

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information

describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained

in this document is accurate and reliable. However, the information is subject to change without notice and is provided “AS IS” without warranty of any kind (express

or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This

document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be

copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior

written consent of Cirrus Logic, Inc. Items from any Cirrus Logic website or disk may be printed for use by the user. However, no part of the printout or electronic

files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc.Furthermore, no part of this publication may be used as a basis for manufacture or sale of any items without the

prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks

or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found

at http://www.cirrus.com.

2 DS483RD2A2

CRD4201-2

1. GENERAL INFORMATION

The CRD4201-2 reference design is an ACR card

that features six channel CD quality analog audio

outputs. The card includes a CS4201 AC ’97 audio

codec and two CS4334 24-bit serial stereo DACs.

This combination gives the CRD4201-2 a rich feature set and industry leading audio performance.

The CS4201 on this card is configured as the primary AC ‘97 audio codec. If there is an AC ‘97 audio codec on the motherboard, it must be disabled.

The CS4201 audio codec has a stereo 20-bit DAC,

a stereo 18-bit ADC, and a very flexible analog audio mixer. The serial data outputs are paired with

two CS4334 DACs to provide four additional channels of analog audio. The CS4201 also features

three stereo pairs of line level analog inputs, a microphone input, and a stereo pseudo-differential

CD input. The input signals can be routed to the

ADC for recording or mixed together for recording

and direct playback. The CS4201 has internal registers that are used to control its various features

such as volume levels, audio muting, and signal

routing. The CS4201 maintains high audio quality

®

and exceeds the Microsoft

audio performance specification.

The CS4201 audio codec communicates to the audio controller across the ACR interface through the

AC-Link. The AC-Link is a 5-wire serial digital interface that transfers digital audio between the two

devices and also sends commands from the audio

controller to the CS4201’s registers. For more information on the AC-Link, see the Intel® AC’97

version 2.1 specification.

PC-99 and PC-2001

2. SCHEMATIC DESCRIPTION

The block diagram in Figure 1 illustrates the interconnections between the schematic pages found at

the end of this document. Sections 2.1 through 2.8

describe the circuitry contained in these schematics.

2.1 CS4201 Audio Codec

The CS4201 audio codec is shown in Figure 2. The

input signals to the CS4201 originate from the analog inputs in Figure 3, and the analog outputs are

shown in Figure 5. AFLT1 and AFLT2 (pins 29,

30) require 1000 pF NPO/COG capacitors connected to analog ground. These capacitors provide

a single pole lowpass filter at the inputs of the

ADC. No other input filtering is required.

FLT3D, FLTI, and FLTO (pins 32, 33, 34) form the

internal analog 3D enhancement filter. The FLT3D

pin requires a 0.01 µF capacitor to analog ground.

The FLT0 and FLT1 pins require a NPO/COG

1000 pF series capacitor.

The AC-Link may require series termination resistors to prevent reflections. These are normally

placed as close as possible to the transmitting end

of a particular AC-Link signal. Both SDATA_IN

(pin 8) and BIT_CLK (pin 6) are outputs of the

CS4201 and each have a 47 Ω series termination

resistor.

The CS4201 is powered by separate analog and

digital power supplies, each with their own respective grounds. The AGND symbols refer to analog

ground, and DGND symbols refer to digital

ground. The analog and digital grounds must be

connected together. For best results, connect them

together at a single point with a 0.050 inch trace underneath the CS4205. Each power pin needs separate decoupling capacitors. The CS4201 audio

codec uses a 0.1 uF ceramic capacitor for each of

the 3.3 V digital and 5 V analog supply pins. These

decoupling capacitors are placed as close as possible to their respective pins.

2.2 Analog Inputs

The LINE_IN, VIDEO, and AUX_IN stereo input

jacks in Figure 3 are connected to a 6 dB voltage

divider and AC coupled to the CS4201. The voltage divider allows input signal levels of up to

DS483RD2A2 3

CRD4201-2

2 Vrms. The 2.2 µF AC coupling capacitor values

are used to minimize low frequency roll-off.

The microphone circuit is AC coupled by a 1 µF capacitor to minimize low frequency roll-off. The

microphone circuit provides low voltage phantom

power for electret microphones. Phantom power is

derived from the +5 V analog supply and provides

a maximum of 4.2 V under no load and a minimum

of 2.0 V under a 0.8 mA load. These parameters are

required by PC-99 and PC-2001.

The CS4201 features a pseudo-differential CD input that minimizes common mode noise and interference. Each CD signals acts as one side of the

differential input and CD_COM acts as the other

side. CD_COM is used as the common return path

for both the left and right channels.

2.3 Rear, Center, and Sub-Woofer Outputs

The outputs in Figure 4 drive the rear speakers

(surround), center speaker (CNT), and sub-woofer

(LFE) in a six channel audio application. These

four outputs are driven digitally from the CS4201

through two serial output ports and converted to analog audio through two high-performance CS4334

24-bit stereo DACs.

2.4 Front Channel and Headphone Outputs

Figure 5 details the Headphone Output and Line

Output circuits. The Line Outputs are the main analog outputs in a two channel system or the Front

Outputs in a six channel audio system.

The Line Outputs of the CS4201 (pins 35 and 36)

are buffered by a Motorola MC34072 dual opamp. The MC34072 is a high performance low

noise op-amp well suited for audio applications.

Line Out is designed to drive high impedance loads

of 10 KΩ or higher.

The CS4201 has a built in headphone amplifier on

pins 39 and 41. These outputs are capable of driv-

ing headphones with impedances as low as 32 Ω.

The headphone outputs are AC coupled through

220 µF capacitors. These large capacitor values

create excellent low frequency response even under

32 Ω loads.

2.5 S/PDIF Optical Output

The S/PDIF (IEC-958) digital output shown in

Figure 6, is compatible with digital outputs on consumer devices such as Mini Disk recorders and

consumer stereo receivers. The S/PDIF output operates at a fixed sampling frequency of 48 kHz. It

uses an industry standard TOSLINK digital optical

transmitter, the Toshiba TOTX-173.

2.6 ACR Connector and EEPROM

The ACR connector is shown in Figure 7. ACR is a

motherboard interface that supports audio, modem,

LAN, and DSL subsystems. ACR applications are

targeted at OEMs, system manufacturers, and system integrators who wish take advantage of physically separating their audio, modem, or LAN

circuitry from the PC motherboard. ACR accomplishes this without the additional cost associated

with the interface circuitry required for a PCI bus

add-in card.

The CRD4201-2 uses a 24LC09 EEPROM to store

configuration data for plug-and-play enumeration.

The 24LC09 is designed specifically for ACR applications. The base address of the device is internally wired to 0xB0. The EEPROM holds the

Subsystem Vendor ID and Subsystem ID. For ACR

design specifications, programming utilities, and

information on programming the EEPROM see the

Advanced Communication Riser Special Interest

Group (ACR SIG) homepage at http://www.acrsig.org/.

Note: an ACR signal called PRIMARY_DN# is

normally tied to ID0# on the CS4201. This signal is

used to set the AC ’97 codec on the ACR card as either the primary or secondary audio codec. The

CRD4201-2 is designed to have the only audio co-

4 DS483RD2A2

CRD4201-2

dec in the system so the PRIMARY_DN# signal

trace has been removed.

2.7 Component Selection

Great attention was given to the particular components used on the CRD4201-2 board with cost, performance, and package selection as the most

important factors. Listed are some of the guidelines

used in the selection of components:

• No components smaller than 0805 SMT package.

• Only single package passive components. No

resistor packs. This reduces the risk of crosstalk

between analog audio signals.

• All components except connectors, jumpers

and the 24.576 MHz crystal are in surface

mount packages.

• Dual footprints are used for the 24.576 MHz

crystal.

2.8 EMI Components

Optional capacitors and inductors are included to

help the board meet EMI compliance tests, such as

FCC Part 15. Choose these component values according to individual requirements.

3. GROUNDING AND LAYOUT

The component layout and signal routing of the

CRD4201-2 provides a good model for laying out

your own ACR add-in card.

3.1 Partitioned Voltage and Ground

Planes

It is critical for good audio performance to separate

digital and analog sections to prevent digital noise

from effecting the performance of the analog circuits. The analog section of the CRD4201-2 is

completely isolated from the digital section with a

100 mil partition. Partitioning is defined as the absence of copper on all signal layers. The analog and

digital sections each have their own separate

ground planes. All analog components, power traces, and signal traces are routed over the analog

ground plane. Digital components, power traces

and signal traces are not allowed to crossover into

the analog section.

The CS4201 audio codec is placed at the transition

point between the analog and digital ground planes.

The pins are arranged on the CS4201 so that the analog and digital signals are separated from each

other. The analog and digital ground planes must

be tied together for the CS4201 to maintain proper

voltage references. For best results, the two ground

planes are tied together with a single 50 mil trace

under the CS4201 near its digital ground pins.

Data converters are generally susceptible to noise

on the crystal pins. In order reduce noise from coupling onto these pins, the area around the 24.576

MHz crystal and its signal traces is filled with copper on the top and bottom of the PCB and attached

to digital ground.

A separate chassis ground provides a noise-free

reference point for all of the EMI suppression components. The chassis ground plane is connected to

the analog ground plane at the external jacks.

3.2 CS4201 Layout Notes

Refer to the CS4201 Data Sheet for analog and digital partitioning guidelines and bypass capacitors

placement. Pay special attention to the bypass capacitors on REFFLT, AFLT1, AFLT2 and the

power supply capacitors.

DS483RD2A2 5

4. REFERENCES

1) Intel®, Audio Codec ‘97 Component Specification, Revision 2.1, May 22, 1998.

http://developer.intel.com/ial/scalableplatforms/audio/

CRD4201-2

2) ACR Special Interest Group, ACR Specification 1.0

http://www.acrsig.org/

3) Cirrus Logic, CS4201 Audio Codec ‘97 Data Sheet

http://www.cirrus.com/products

4) Steve Harris, Clif Sanchez, Personal Computer Audio Quality Measurements

http://www.cirrus.com/pubs/meas100.pdf

5) Microsoft, PC Design Guidelines

http://www.microsoft.com/hwdev/desguid/

6) M. Montrose, Printed Circuit Board Design Techniques for EMC Compliance (2nd edition), IEEE

Press, New York: 2000.

,

, Version 1.0

4.1 ADDENDUM

• Schematic drawings

• Layout drawings

• Bill of materials

6 DS483RD2A2

CRD4201-2

ANALOG_IN

ANALOG_IN

LINE_IN_L

LINE_IN_R

CD_IN_L

CD_IN_R

CD_COM

VIDEO_IN_L

VIDEO_IN_R

AUX_IN_L

AUX_IN_R

MIC_IN

PHONE_IN

MONO_OUT

PC_BEEP

CS4201

LINE_IN_L

LINE_IN_R

CD_IN_L

CD_IN_R

CD_COM

VIDEO_IN_L

VIDEO_IN_R

AUX_IN_L

AUX_IN_R

MIC_IN

PHONE_IN

MONO_OUT

PC_BEEP

CS4201

ACR_BUS

ACR_BUS

PRIM_DN#

PRIM_DN#

ANALOG_OUT

LINE_OUT_L

LINE_OUT_R

VREFOUT

HP_OUT_L

HP_OUT_R

HP_OUT_C

SDOUT

ABITCLK

ASDOUT

ASYNC

ARST#

ARST#

ASYNC

ABITCLK

SPDIF/SDO2

ASDIN

ASDIN

ASDOUT

SCLK

LRCLK

SPDIF/SDO2

SPDIF_TX

LINE_OUT_L

LINE_OUT_R

VREFOUT

HP_OUT_L

HP_OUT_R

HP_OUT_C

ANALOG_OUT

SERIAL PORT

SDOUT

SCLK

LRCLK

SPDIF/SDO2

ABITCLK

SERIAL PORT

SPDIF_OUT

SPDIF_TX

SPDIF_OUT

Figure 1. Block Diagram

DS483RD2A2 7

CRD4201-2

DGND AGND

LINE_OUT_L

ASDOUT

ASYNC

ASDIN

ABITCLK

R1 47

ARST#

R2 47

HP_OUT_L

LINE_OUT_R

MONO_OUT

SPDIF/SDO2

HP_OUT_R

PRIM_DN#

SCLK

LRCLK

SDOUT

HP_OUT_C

NOTE: In order to be

compatible with a wider

range of motherboards, the

PRIMARY_DN# trace has been

physically cut on the

CRD4201-2.

10

5

42

26

AVss2

AVss1

U1 CS4201

AVdd2

AVdd1

38

25

+5VA

+3.3VD

6

4

7

8

11

DVss1

DVss2

DVdd1

DVdd2

1

9

SYNC

BIT_CLK

PC_BEEP12PHONE13AUX_L14AUX_R15VIDEO_L16VIDEO_R17CD_L18CD_GND19CD_R20MIC121MIC222LINE_IN_L23LINE_IN_R

RESET#

SDATA_IN

SDATA_OUT

37

39

41

36

35

MONO_OUT

HP_OUT_L

HP_OUT_R

LINE_OUT_R

LINE_OUT_L

24

SPDO/SDO248EAPD/SCLK

47

REFFLT27Vrefout28AFLT129AFLT2

45

31

40

44

43

DGND

ID1#46ID0#

HPCFG

HP_OUT_C

GPIO1/SDOUT

GPIO0/LRCLK

GND TIE 0.050 inches

FLTO34FLTI33FLT3D

XTL_IN2XTL_OUT

C10

C9

3

1000pF

NPO

0.01uF

X7R

32

30

AGND

C15

22pF

NPO

Y1

24.576 MHz

C14

22pF

NPO

DGND DGND

Figure 2. CS4201 Audio Codec

MIC_IN

CD_IN_L

PC_BEEP

PHONE_IN

C4

0.1uF

X7R

C3

0.1uF

X7R

+5VA

C2

0.1uF

X7R

C1

0.1uF

X7R

+3.3VD

AGNDDGND

VIDEO_IN_R

AUX_IN_L

VIDEO_IN_L

AUX_IN_R

LINE_IN_L

CD_COM

LINE_IN_R

CD_IN_R

VREFOUT

C8

1000pF

NPO

C13

1000pF

C7

C6

C5

1000pF

NPO

0.1uF

X7R

2.2uF

Y5V

AGND

NPO

MONO_OUT

C12

1000pF

NPO

LINE_OUT_R

C11

1000pF

NPO

LINE_OUT_L

AGND

8 DS483RD2A2

CRD4201-2

CD

IN

LINE IN

LINE_IN_R

+

ELEC

C17 2.2uF

R4 6.8K

43521

J1

R6 6.8K

AGND

LINE_IN_L

+

ELEC

C21 2.2uF

R8 6.8K

R10 6.8K

AGND

C20

100pF

NPO

C19

100pF

NPO

CGND

AGND

Connect CGND

to AGND at

the jack

MIC IN

+5VA

R15 1.5K

R14 2.2K

J3

452

MIC_IN

PC_BEEP

Y5V

C24 1uF

C29

NO POP

AGNDAGND

-3 dB corners at 60 Hz

and 13.8 kHz

(Ri >= 28 kOhm)

R17 100

C28

10uF

ELEC

+

C27

100pF

NPO

C26

100pF

NPO

CGND

AGND

1

Connect CGND

to AGND at

the jack

X7R

C31 0.1uF

C32

2700pF

X7R

R23

4.7K

AGND AGND

R21 47K

L7

31@100MHz

DGND

1

2

J6

PC SPEAKER IN

Figure 3. Analog Inputs

CD_IN_L

+

ELEC

C22 2.2uF

R12 47K

R11 100

L3

31@100MHz

VIDEO_IN_R

+

ELEC

C23 2.2uF

R13 6.8K

L4

4

R5 47K

AGND

31@100MHz

CD_COM

+

ELEC

C18 4.7uF

R7 100

L2

123

R9 47K

AGND AGND

31@100MHz

CD_IN_R

+

ELEC

C16 2.2uF

R3 100

L1

4

R16 6.8K

AGND

31@100MHz

VIDEO_IN_L

+

ELEC

C25 2.2uF

R19 6.8K

R18 6.8K

AGND

L5

31@100MHz

AGND

123

AUX_IN_R

+

ELEC

C30 2.2uF

R22 6.8K

R20 6.8K

AGND AGND

L6

31@100MHz

4

AUX_IN_L

+

ELEC

C33 2.2uF

R25 6.8K

R24 6.8K

L8

31@100MHz

AGND

123

PHONE_IN

+

ELEC

C34 2.2uF

R26 6.8K

L9

R27 6.8K

AGND

31@100MHz

4

MONO_OUT

+

ELEC

C35 2.2uF

R29

47K

R28 0

L10

31@100MHz

AGND AGND

123

J2

J4

VIDEO IN

J5

AUX IN

J7

INTERNAL MODEM CONNECTION

DS483RD2A2 9

SURROUND JACK

(REAR CHANNEL OUTPUT)

CRD4201-2

Connect CGND

to AGND at

2700pF

X7R

the jack

AGND

CNT/LFE JACK

J9

4

2

1

J8

4

2

1

C39

C46

Connect CGND

2700pF

X7R

to AGND at

the jack

AGND

C42

C41

0.1uF

0.1uF

CGND

AGND

AGND

X7R

X7R

C38

2700pF

X7R

R30 560

R31 560

ELEC

ELEC

+

+

C36 10uF

C37 10uF

+5VA

7

6

5

8

VA+

AGND

AOUTR

R35

47K

R34

47K

R33

270K

R32

270K

AOUTL

(CENTER CHANNEL AND SUB-WOOFER)

R36 560

C43 10uF

ELEC

+

5

AOUTR

C45

2700pF

X7R

R37 560

ELEC

+

C44 10uF

7

6

8

VA+

AGND

R41

47K

47K

R40

R39

270K

R38

270K

AOUTL

CGND

AGND

AGND

AGND

Figure 4. Rear, Center, and Sub-Woofer Outputs

U2 CS4334

SDATA1DEM#/SCLK2LRCK3MCLK

SDOUT

C40

10uF

ELEC

+

4

+5VA

U3 CS4334

SDATA1DEM#/SCLK2LRCK3MCLK

AGND

4

LRCLK

SCLK

SPDIF/SDO2

ABITCLK

10 DS483RD2A2

CRD4201-2

J10

4

2

LINE OUT JACK

1

Connect CGND

to AGND at

the jack

AGND

J11

4

2

HEADPHONE JACK

1

Connect CGND

to AGND at

the jack

AGNDAGND

(FRONT CHANNEL OUTPUTS)

C58

100pF

NPO

C57

100pF

NPO

R49

10K

R48

10K

CGND

C48 10uF

C51

100pF

NPO

C50

100pF

NPO

R45

220K

R44

220K

ELEC

ELEC

+

+

C49 10uF

+5VA

C52

0.1uF

CGND

AGND

C55 220uF

ELEC

ELEC

+

+

C56 1uF

ELEC

+

X7R

Vee Vcc

AGND

C54 220uF

+5VA

1

U4A

84

MC34072D

+

-

3

2

22pF

NPO

AGND

R42 33K

C47

7

U4B

MC34072D

NPO

+

C53 22pF

5

6

R46 33K

Figure 5. Front Channel and Headphone Outputs

R43 27K

VREFOUT

R47 27K

HP_OUT_R

HP_OUT_L

LINE_OUT_R

LINE_OUT_L

HP_OUT_C

DS483RD2A2 11

CRD4201-2

SPDIF_TX

+5VD

R50 8.2K

C59

0.1uF

X7R

DGND

Figure 6. S/PDIF Optical Output

J12

4

3

2

1

TOTX-173

5

DGND

6

DGND

12 DS483RD2A2

CRD4201-2

C61

10uF

ELEC

+

C60

0.1uF

X7R

+5VD

+3.3VD

DGND

SPDIF/SDO2

C63

10uF

ELEC

+

+3.3VD

C62

0.1uF

X7R

DGND

4.7K

R56

+3.3VDASYNC

R55

4.7K

SPDIF_TX

ASDIN

ABITCLK

R57

NO POP

8

Vcc

R58

0

C64

0.1uF

X7R

DGND DGND

SDA

SCL

5

7

WP

SCL6SDA

A1

P1

A6

A2

A5

A7

GND

RSVD(1)A3RSVD(2)A4RSVD(3)

MONO_PHONE

AUDIO_PWRDN

AUDIO_MUTE#B1AGNDB2MONO_OUT/PC_BEEPB3RSVD(4)B4RSVD(5)B5PRIMARY_DN#B6-12VB7GNDB8+12VB9GND

NC11NC22NC33Vss

U5

R51 0

+3.3VD

R52 NO POP

populate only one

resistor

A9

A8

USB_OC#

+5Vdual/+5Vsb

GND

A10

A11

USB+

USB-

A12

A14

A13

GND

S/PDIF_IN

GND

R53 NO POP

R54 47

populate R54 for primary codec

populate R53 for secondary codec

DGND

A16

A18

A20

A22

A19

A15

A17

GND

GND

SYNC

+3.3Vdual/+3.3Vsb

A24

A21

A23

GND

GND

SDA

BITCLK

SDATA_IN1

SDATA_IN0

24LC09

4

DGND

C67

+C66

EEPROM address "0xB0"

10uF

ELEC

AGNDDGND

Figure 7. ACR Connector

+5VD

GND

RSVD(6)

RSVD(7)

+3.3VD

GND

SDATA_OUT

RESET#

SDATA_IN3

GND

SDATA_IN2

GND

MSTRCLK

SCL

ACR Connector

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

DGND

+12VD

+5VD

+3.3VD

3

OUT

U6

+12VD +5VA

MC78M05C

GND

2

IN

1

10uF

ELEC

+

ASDOUT

NOTE: In order to be

compatible with a wider

range of motherboards, the

PRIMARY_DN# trace has been

PRIM_DN#

physically cut on the

CRD4201-2.

ARST#

C65

0.1uF

X7R

DS483RD2A2 13

CRD4201-2

Figure 8. PCB Layout: Top Assembly Drawing

14 DS483RD2A2

CRD4201-2

Figure 9. PCB Layout: Top Layer

DS483RD2A2 15

CRD4201-2

Figure 10. PCB Layout: Bottom Layer

16 DS483RD2A2

CRD4201-2

Figure 11. PCB Layout: Drill Drawing

DS483RD2A2 17

CRD4201-2

Figure 12. PCB Layout: Top Silkscreen

18 DS483RD2A2

CRD4201-2

C42,C52,C59,C60,C62,C64,

5. BILL OF MATERIALS

C65

Item Quantity Reference Manufacturer Part Number Description

1 14 C1,C2,C3,C4,C6,C31,C41, KEMET C0805C104K5RAC CAP, 0805, X7R, .1uF, 10%, 50V

2 1 C5 KEMET C1206C225M8VAC CAP, 1206, Y5V, 2.2uF, 20%, 10V

3 6 C7,C8,C10,C11,C12,C13 KEMET C0805C102K5GAC CAP, 0805, C0G, 1000pF, 10%, 50V

4 1 C9 KEMET C0805C103K5RAC CAP, 0805, X7R, .01uF, 10%, 50V

5 4 C14,C15,C47,C53 KEMET C0805C220K5GAC CAP, 0805, C0G, 22pF, 10%, 50V

6 10 C16,C17,C21,C22,C23,C25, PANASONIC ECE-V1VS2R2SR CAP, SMT A, ELEC, 2.2uF, 20%, 35V

C30,C33,C34,C35

7 1 C18 PANASONIC ECE-V1ES4R7SR CAP, SMT A, ELEC, 4.7uF, 20%, 25V

8 4 C19,C20,C26,C27 KEMET C0805C101J5GAC CAP, 0805, COG, 100pF, 5%, 50V

9 1 C24 KEMET C0805C105M8VAC CAP, 0805, Y5V, 1uF, 20%, 10V

10 12 C28,C36,C37,C40,C43,C44, PANASONIC ECE-V1CA100R CAP, SMT B, ELEC, 10uF, 20%, 16V

C48,C49,C61,C63,C66,C67

11 1 C29 NO POP NO POP NO POP

12 5 C32,C38,C39,C45,C46 KEMET C0805C272K5RAC CAP, 0805, X7R, 2700pF, 10%, 50V

13 4 C50,C51,C57,C58 KEMET C0805C101J5GAC CAP, 0805, C0G, 100pF, 5%, 50V

14 2 C54,C55 PANASONIC ECE-V0GA221P CAP, SMT D, ELEC, 220uF, 20%, 4V

15 1 C56 PANASONIC ECE-V1HA010R CAP, SMT B, ELEC, 1uF, 20%, 50V

16 1 J1 LZR ELECTRONICS SJ372 CONN, 1/8" DOUBLE SW. STEREO PHONE JACK

17 4 J2,J4,J5,J7 MOLEX 70553-0003 HDR, 4X1, 0.025" PIN, 0.1" CTR, 15u" AU

18 1 J3 LZR ELECTRONICS SJ374 CONN, 1/8" SINGLE SW. STEREO PHONE JACK

19 1 J6 MOLEX 70553-0036 HDR, 2X1, 0.025" PIN, 0.1" CTR, 150u" SN/PB

20 4 J8,J9,J10,J11 LZR ELECTRONICS SJ373 CONN, 1/8" NON-SW. STEREO PHONE JACK

DS483RD2A2 19

CRD4201-2

L9,L10

21 1 J12 TOSHIBA TOTX173 CONN, OPTICAL TOSLINK TRANSMITTER

22 10 L1,L2,L3,L4,L5,L6,L7,L8, TDK HF50ACB321611-T IND, FBEAD, 1206, 31@100MHz, 25%

23 1 P1 NONE EDGE CONNECTOR ACR BUS CONNECTOR

24 3 R1,R2,R54 PHILIPS 9C08052A47R0J RES, SO, 0805, 47, 5%, 1/10W, METAL FILM

25 4 R3,R7,R11,R17 PHILIPS 9C08052A1000J RES, SO, 0805, 100, 5%, 1/10W, METAL FILM

26 14 R4,R6,R8,R10,R13,R16,R18, PHILIPS 9C08052A6801F RES, SO, 0805, 6.8K, 1%, 1/10W, METAL FILM

R19,R20,R22,R24,R25,R26,

R27

27 9 R5,R9,R12,R21,R29,R34, PHILIPS 9C08052A4702J RES, SO, 0805, 47K, 5%, 1/10W, METAL FILM

R35,R40,R41

28 1 R14 PHILIPS 9C08052A2201J RES, SO, 0805, 2.2K, 5%, 1/10W, METAL FILM

29 1 R15 PHILIPS 9C08052A1501J RES, SO, 0805, 1.5K, 5%, 1/10W, METAL FILM

30 3 R23,R55,R56 PHILIPS 9C08052A4701J RES, SO, 0805, 4.7K, 5%, 1/10W, METAL FILM

31 3 R28,R51,R58 PHILIPS 9C08052A0R00J RES, SO, 0805, 0, 5%, 1/10W, METAL FILM

32 4 R30,R31,R36,R37 PHILIPS 9C08052A5600J RES, SO, 0805, 560, 5%, 1/10W, METAL FILM

33 4 R32,R33,R38,R39 PHILIPS 9C08052A2703J RES, SO, 0805, 270K, 5%, 1/10W, METAL FILM

34 2 R42,R46 PHILIPS 9C08052A3302F RES, SO, 0805, 33K, 1%, 1/10W, METAL FILM

35 2 R43,R47 PHILIPS 9C08052A2702F RES, SO, 0805, 27K, 1%, 1/10W, METAL FILM

36 2 R45,R44 PHILIPS 9C08052A2203J RES, SO, 0805, 220K, 5%, 1/10W, METAL FILM

37 2 R48,R49 PHILIPS 9C08052A1002J RES, SO, 0805, 10K, 5%, 1/10W, METAL FILM

38 1 R50 PHILIPS 9C08052A8201J RES, SO, 0805, 8.2K, 5%, 1/10W, METAL FILM

39 2 R52,R57 NO POP NO POP NO POP

40 1 R53 NO POP NO POP NO POP

41 1 U1 CIRRUS LOGIC CS4201-JQ IC, TQFP, AC ’97 2.1 SERIAL CODEC W/ HP AMP + SRC

20 DS483RD2A2

CRD4201-2

42 2 U2,U3 CIRRUS LOGIC CS4334-KS IC, SO, SOIC8, DAC, STEREO

43 1 U4 MOTOROLA MC34072D IC, SO, SOIC8, 34072, SINGLE SUPPLY DUAL OP AMP

44 1 U5 Microchip 24LC09-I/SN IC, SO, SOIC8, SERIAL EEPROM, 4 x 256 x 8

45 1 U6 MOTOROLA MC78M05CDT IC, SO, +5V REGULATOR, DPAK, 4%, 500mA

46 1 Y1 FOX FS24.576 XTAL, 24.576MHz, HC49S, Fund Mode, Par Res

DS483RD2A2 21

Loading...

Loading...