Page 1

PC10420

ARCNET® Network Interface Modules for PC/104 Bus Computers

INST ALLA TION GUIDE

INTRODUCTION

The PC10420 series of ARCNET network interface modules (NIMs) links

PC/104 compatible computers with the ARCNET local area network (LAN).

ARCNET is classified as a token-bus LAN operating at a nominal 2.5 Mbps

while supporting 255 nodes. Interfacing ARCNET to a host computer

usually requires a NIM which plugs into the host computer’s bus.

The PC10420 incorporates the newer COM20020 ARCNET controller chip

with enhanced features over the earlier generation ARCNET chips. New

performance and integration enhancements include command chaining

operation and an internal 2K x 8 RAM buffer. There is no requirement for

wait-state arbitration.

Each PC10420 module has two LEDs on the board. The green LED

indicates that the module is receiving data on the network and the yellow

LED indicates bus access to the module. The PC10420 also has a piano

style DIP switch so that node addresses can be easily reassigned without

removing the module.

There are several versions of the PC10420 ARCNET NIM. The

PC10420-CXS supports coaxial star configurations requiring external

active or passive hubs. The PC10420-CXB supports coaxial bus

configuration usually requiring no hubs. Other versions include the

PC10420-FOG which supports fiber optic cable with either ST or SMA

connectors. The PC10420-TPB supports twisted-pair bus cabling using

RJ-11 and screw terminal connectors. There are various versions that

support EIA-485 communication each using RJ-11 and screw terminal

connectors.

On some models, operation up to 5.0 Mbps is possible. These models are

identified with a /5 designation.

Page 2

SPECIFICATIONS

Environmental

Operating temperature: 0°C to +60°C

Storage temperature: –40°C to +85°C

Data Rates

PC10420* 2.5 Mbps, 1.25 Mbps, 625 kbps, 312.5 kbps, 156.25 kbps

PC10420/5* 5.0 Mbps, 2.5 Mbps, 1.25 Mbps, 625 kbps, 312.5 kbps

* The -CXS, -CXB and -TPB models can only operate at 2.5 Mbps.

The -485X model can only operate at 1.25, 2.5 or 5.0 Mbps.

Dimensions

3.550" x 3.775"

(90 mm x 95 mm)

Shipping Weight

1 lb. (.45 kg)

I/O Mapping

Supports I/O Mapping on any 16-byte boundary

Interrupt Lines

Supports strapping of IRQ 2/9, 3, 4, 5, 6, or 7

Compatibility

PC10420 series NIMs are compliant with ANSI/ATA 878.1 and PC/104

Specification 2.3.

Regulatory Compliance

FCC Part 15 Class A

Power Requirements

Model +5V –12V

PC10420-CXS 200 mA 20 mA

PC10420-CXB 200 mA 50 mA

PC10420-FOG-SMA 300 mA N/A

PC10420-FOG-ST 300 mA N/A

PC10420-TPB 200 mA 50 mA

PC10420-485 200 mA N/A

PC10420-485D 200 mA N/A

PC10420-485X 200 mA N/A

PC10420/5-485 200 mA N/A

PC10420/5-485D 200 mA N/A

PC10420/5-485X 200 mA N/A

PC10420/5-FG-ST 300 mA N/A

TD874100-0IH

2

Page 3

INSTALLATION

Passive P2 Connector

Although the PC10420 is an eight-bit module, the PC10420 does provide a

P2 connector used for 16-bit applications. The advantage of the P2

connector is that 8-bit modules, such as the PC10420, can be located in the

middle of the PC/104 stack without compromising the integrity of the 16-bit

bus. Signals from the PC10420 are not connected to the passive P2

connector.

Mounting the PC10420

The PC10420 incorporates stack-through connectors and is shipped with

four 0.6" standoffs to facilitate mounting of the PC10420 onto the PC/104

stack. The PC10420 should be mounted below the 8-bit modules if any are

present in the system. If another eight-bit module is to be mounted above

the PC10420, use the enclosed standoffs. On some older eight-bit modules,

only two mounting holes are provided so only two standoffs are used. If

the PC10420 is the last module on the stack, use either two or four

M3x0.5-5MM panhead screws (not provided) to complete the mounting

onto the stack. Once mounted, field connections can be made.

Since the PC/104 stack does not make provision for a chassis (earth)

connection, a metal screw terminal has been provided for this purpose.

Simply connect one end of a green earthing wire to the screw terminal and

the other end to a suitable chassis ground.

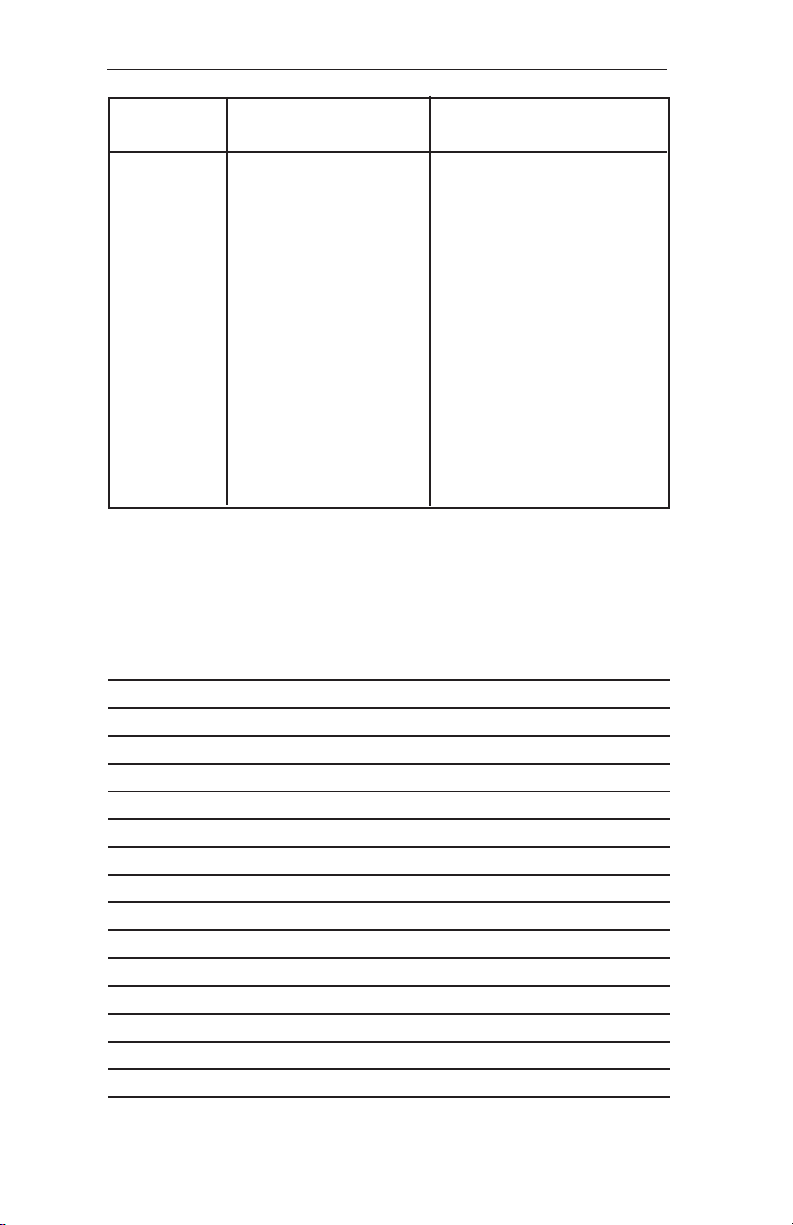

Register Map

The PC10420 requires 16 contiguous I/O address locations in order to

access the COM20020 register and node ID switch. Because several

locations are reserved, it is important not to address another device to these

locations. The register map is shown in Table 1.

TD874100-0IH

3

Page 4

I/O Read Write

Address Register Register

Base + 0 Status Interrupt Mark

Base + 1 Diagnostic Status Command

Base + 2 Address Pointer High Address Pointer High

Base + 3 Address Pointer Low Address Pointer Low

Base + 4 Data Data

Base + 5 Reserved Reserved

Base + 6 Configuration Configuration

Base + 7 Test ID/..../Next ID Test ID/..../Next ID

Base + 8 Node ID Switch Reserved

Base + 9 Node ID Switch Reserved

Base + A Reserved Reserved

Base + B Reserved Reserved

Base + C Reserved Reserved

Base + D Reserved Reserved

Base + E Reserved Reserved

Base + F Reserved Reserved

Table 1—Register Map

I/O Base Addressing

The I/O base address for the register map can be set with jumpers. The

PC10420 does not require any memory address space—simplifying

installation. See Table 2 for details.

A9 A8 A7 A6 A 5 A4 I/O ADDRESS

n nnnn 100

nnnn 110

nnn n 120

nnn 130

nn nn 140

nn n 150

nn n 160

nn 170

n nnn 180

nnn 190

nnn1A0

nn 1B0

nnn1C0

nn1D0

nn1E0

TD874100-0IH

4

Page 5

A9 A8 A7 A6 A5 A4 I/O ADDRESS

n 1F0

nnnnn 200

nn n n 210

nn n n 220

nn n 230

nn n n 240

nn n 250

nn n 260

nn 270

n nnn 280

nnn 290

nn n 2A0

nn 2B0

nnn2C0

nn 2D0

nn2E0

n 2F0

nnnn 300* Default

nn n 310

nn n 320

nn 330

nnn 340

nn 350

nn360

n 370

nnn 380

nn 390

nn 3A0

n 3B0

nn 3C0

n 3D0

n 3E0

3F0

Key: n = Install Jumper

Table 2—I/O Base Address

TD874100-0IH

5

Page 6

Interrupts

Interrupts can be invoked at jumper location E1 which consists of a series of

rows of two posts each. Each row is labeled with an interrupt line

corresponding to one of the PC bus interrupt designators. To enable an

interrupt, insert a jumper across a pair of posts corresponding to the desired

interrupt. Only one interrupt can be selected; therefore, only one jumper is

supplied. If no interrupts are desired, remove all jumpers at E1. The default

interrupt setting is INT 2.

Indicator Lights

There is a dual LED located at the PC10420 front plane. The yellow LED

indicates that the PC10420 is being accessed via its I/O address. The green

LED indicates that the PC10420 is receiving ARCNET traffic from the

network.

Node ID Switch

Although not always necessary with the COM20020, the PC10420 provides

a separate input port that reads an 8-bit DIP switch (SW1) located near the

board edge. This switch is intended to serve as a node ID switch, although it

can serve as a general purpose switch if desired. The node ID switch has no

connection to the COM20020 ARCNET controller chip.

The most significant bit (MSB) is switch position 1, and the least significant

bit (LSB) is switch position 8. A switch in the open position (off position or

away from the printed circuit board) introduces a logic “1.” Figure 1 shows

the node ID switch. In this example, the switch is set to hexadecimal

address F5.

MSB LSB

Figure 1—Node ID Switch

FIELD CONNECTIONS

The PC10420 is available in several transceiver options. Each transceiver,

which is matched to a particular cable type, is identified by a three-character

suffix appended to the model numbers. The capabilities of each transceiver

differs.

TD874100-0IH

6

Page 7

-CXS Coaxial Star

In a coaxial star system, NIMs and hubs are interconnected in a point-topoint fashion using coaxial cable. A NIM can connect to one other NIM or

can connect to an unused port on a hub. Hub-to-hub connections are

allowed.

In a two-node system, simply connect the two -CXS NIMs together using

RG-62/u coaxial cable. The length of cable cannot exceed 2000 feet.

If more than two NIMs are used on a network, either an active or passive

hub is required. With passive hubs, a maximum of four NIMs can be

interconnected. Unused ports on the passive hub must be terminated with a

93-ohm (nominal) resistor. The maximum length between a passive hub port

and a NIM is 100 feet.

Active hubs provide overall better performance than passive hubs since

greater distances can be achieved along with a degree of isolation. Connect

each NIM to a port on the hub using RG-62/u coaxial cable. This length of

cable cannot exceed 2000 feet nor can the length of cable between two

cascaded hubs exceed 2000 feet. However, up to ten hubs can be cascaded

thereby providing an overall cable length of 22,000 feet. Unused ports on

active hubs need not be terminated.

Figure 2—Active hubs can be cascaded

for greater distances.

-CXB Coaxial Bus

For hubless systems, the -CXB transceiver can be used. NIMs are

interconnected with RG-62/u cables and BNC Tee connectors. Each -CXB

NIM represents a high impedance connection in both the powered and

unpowered states. Therefore, passive termination must be applied to both

ends of a bus segment. Use BNC style 93-ohm (nominal) resistors at each

end. The maximum segment length is 1000 feet and the maximum number

of NIMs that can be connected to a segment is eight.

To extend a bus segment beyond 1000 feet, an active hub is required. If the

hub port is of the -CXS type, connection can be made if a few simple rules

are followed. Only connect this bus segment at the end of a segment. Do not

connect the hub to the middle of a segment since the hub port is not of the

TD874100-0IH

7

Page 8

high impedance type. Do not terminate the end which attaches to the hub

port since a -CXS port effectively terminates the end of a bus segment.

Simply remove the BNC Tee connector and terminator from the segment end

and attach the cable directly to the hub port. The opposite segment end still

requires termination if no hub connection is being made.

Figure 3—Bus segments can be extended

through active hubs.

-FOG Fiber Optic (-ST, -SMA)

The fiber optic option is designated -FOG; however, a further designation is

required in order to specify the type of

connector. The -FOG-ST uses the ST

style connector while the -FOG-SMA

uses the SMA style connector. Cable

sizes of 50, 62.5 or 100 micron duplex

cable can be used with either

connector.

Fiber optic connections require a

duplex cable arrangement. Only star

and distributed star topologies are

supported. Two unidirectional cable

paths provide the duplex link. There

are two devices on each NIM. One

device, colored light gray, is the

transmitter and the other, dark gray, is the receiver. Remember that “light

goes out of the light (gray).” To establish a working link between a NIM and

another NIM or a hub to a NIM, the transmitter of point A must be

connected to a receiver at

point B. Correspondingly,

the receiver at point A must

be connected to a transmitter

at point B. This establishes

the duplex link.

Figure 4—Fiber Optic

Option (-FOG)

Optical Power Budget

The optical power budget is

the ratio of the light source

Table 3—The power budget varies with

the fiber core size.

TD874100-0IH

8

Page 9

strength divided by the light receiver sensitivity expressed in dB. The link

loss budget, which includes losses due to cable and connectors, must be less

than the power budget. Assuming cable attenuation of 3.5 dB/km, up to

2 km of 62.5 µm fiber optic cable can be used per segment.

-TPB Twisted-Pair Bus

The -CXB transceiver can be modified to drive a balanced cable system

with the addition of some parts. This configuration is called -TPB and it

supports shielded or unshielded twisted-pair cable such as Category 5. Dual

RJ-11 connectors replace the single BNC connector in order to support the

popular modular plug connectors. For convenience, a three-position screw

terminal connector is also provided (see Figure 7). Follow the connector pin

assignments in Tables 4 and 5 when using these connectors or when mixing

cable types. Wiring between NIMs is accomplished in a daisy-chain fashion

with point-to-point cables connecting the various NIMs to create a bus

segment. The end NIMs will have one vacant RJ-11 socket which is to hold

the RJ-11 style 100-ohm terminator required to terminate the end points of

the bus segment. When terminating the screw terminal connector, install a

100 ohm, 1/4 watt resistor across terminals 1 and 2. Use twisted-pair cable

and observe polarity. Modular plugs must be installed on this cable so that

they do not invert the signals. Most satin cable does not twist the pairs nor

maintain signal polarity. Do not use this cable. To test for the proper cable

connections, hold both ends of the cable side by side with the retaining clips

facing the same direction. The color of the wire in the right-most position of

each plug must be the same if there is no inversion of the cable. If this is not

the case, the cable is inverted. Up to eight -TPB NIMs can be connected to

one segment which cannot exceed 400 feet in length.

The overall distance of a twisted-pair network can be expanded beyond 400

feet if hubs are used. Use a hub port that supports the same -TPB interface.

Figure 5—TPB NIMs are connected in a daisy-chain fashion

with terminators inserted at both end NIMs.

-485D DC Coupled EIA-485 (Non Backplane Mode)

The PC10420-485D supports DC coupled EIA-485 communication via a

daughter board which replaces the coaxial hybrid transceiver. This daughter

board receives the conventional P1 and P2 pulses intended for the coaxial

hybrid transceiver and converts them to an elongated P1 pulse (the width is

equal to P1 and P2) suitable for the EIA-485 differential driver. Therefore,

TD874100-0IH

9

Page 10

do not set the COM20020 to backplane mode for EIA485 communication as recommended in SMSC’s

application note and data sheet since Contemporary

Controls (CC) implements the same signaling on this

daughter board. With our approach, the same software

driver used for coaxial networks will function

with the EIA-485 version of the PC10420 without

modification.

Figure 6—Modular Jack

Numbering Orientation

Modular Connector Pin

Assignments

6-Contacts

Pin Usage

1 Not Available

2 Not Used

3 Line+

4 Line

5 Not Used

6 Not Available

–

Table 4—Modular

Connector Pin

Assignments for -TPB

Figure 7) and two RJ-11 connectors are

supplied on each NIM and are bussed together

to provide a convenient daisy-chain method for

connecting multiple nodes onto one segment.

This segment can be up to 900 feet long of

Category 5 unshielded twisted-pair cable, and

as many as 17 nodes can occupy the segment.

Make sure that the phase integrity of the wiring

remains intact. Pin 3 of the modular jack on

each NIM must be connected together. The same

applies to pin 4. Most modular (satin cable)

telephone wiring inverts the phase of the wiring,

thereby reversing the connections to pins 3 and 4

at each end. Do not use this type of cable. Some

modular cable is not even twisted. Be sure to use the proper cable. Refer to

Tables 4 and 5 for connector pin assignments.

Termination

Each end of the segment must be terminated in the characteristic impedance

of the cable. A 120-ohm resistor can be invoked with a jumper which resides

on the EIA-485 daughter board. With the middle jumper inserted at location

E1 on the daughter board, 120 ohms of resistance is applied across the

twisted-pair. With the jumper removed, no termination is applied. If it is

desired to apply external termination instead, remove this jumper and insert

an RJ-11 style terminator in the unused RJ-11 modular jack or install a 120

ohm, 1/4 watt resistor across pins 1 and 2 on the screw terminal connector.

One three-position screw terminal (see

Table 5—Screw Terminal Connector

Pin Assignments for -485, -485D -485X and -TPB

TD874100-0IH

10

Page 11

Incorporating a resistance value less than 120 ohms is not recommended

since it may excessively load the EIA-485 transceivers.

Bias

In addition to the termination, it is also necessary to apply bias to the

twisted-pair network so that when the line is floated, differential receivers

will not assume an invalid logic state. There are two precision bias resistors

(Rb) of equal value on each daughter board. One resistor is tied to the +5 V

line while the other is tied to ground. Each resistor has a jumper associated

with it. If the two jumpers are installed, the resistor tied to +5 V is

connected to the (+) signal line while the grounded resistor is connected to

the (–) line. This voltage drop will bias the differential receivers into the

“1” state when no differential drivers are

enabled. Differential receivers typically switch at

or near zero volts differential and are guaranteed

to switch at +/–200 mV. Through the transition

point, 70 mV of hysteresis will be experienced.

Therefore, a positive bias of 200 mV or greater

will ensure a defined state. We recommend that

bias be applied to both ends of the wiring

segment by installing the two end jumpers

located at position E1 on the daughter board.

This is to be done for only the two NIMs

located at the end of the segment. All other

NIMs will have their jumpers removed.

The termination and bias rules are simple. If the NIM is located at the

extreme ends of the segment, install all three jumpers at location E1 on the

daughterboard. If the NIM is located between the two end NIMs, remove all

three jumpers. If external termination is desired, remove the middle jumper

at E1.

Figure 7—Screw

Terminal Connector

Numbering Orientation

For EIA-485 DC operation, it is very important that all devices on the

wiring segment be referenced to the same ground potential in order that the

common mode voltage requirement (+/–7 Vdc) of the EIA-485 specification

is achieved. This can be accomplished by running a separate ground wire

between all PC computers or by relying upon the third wire ground of the

power connector assuming that the DC power return is connected to chassis

ground on the PC computer. Another approach would be to connect the DC

common of each PC computer to a cold water pipe. Connected systems, each

with different elevated grounds, can cause unreliable communications or

damage to the EIA-485 differential drivers. Therefore, it is important that an

adequate grounding method be implemented. A ground connection can be

found at pin 3 of the screw terminal connector.

TD874100-0IH

11

Page 12

Segments of -485D connected NIMs can be extended through the use of

active hubs. Select a MOD HUB expansion module with a -485D

compatible port. Connect one end of the segment to this port following the

same termination rules as used for a NIM. This hub port counts as one NIM

when cable loading is being calculated. The NIM electrically closest to the

hub port should not have any termination or bias applied. Follow the same

rules for other segments attached to different hub ports. Each hub effectively

extends the segment another 900 feet. Maintain the same cabling polarity as

the NIMs by using cable connections that do not invert the signals.

-485 DC Coupled EIA-485 (Backplane Mode)

If the software driver you intend to use sets the COM20020 into backplane

mode, you will need the PC10420-485

Jumper

E3/E4 # of Nodes

1-2, 3-4, 5-6 2-5

3-4, 5-6 6-15

5-6 16-30

Table 6—Backplane Mode,

DC Coupled EIA-485

Option (-485)

place a jumper at E5 on pins 1 and 2. If termination is not required, simply

move the E5 jumper to pins 2 and 3. Cabling and expansion rules are the

same for the -485 and -485D options.

version. This version does not utilize the

daughter-board approach. Instead you

will find three sets of jumpers labeled

E3, E4 and E5 which replace the three

jumper functionality of E1 found in the

-485D model. Operation is similar to

that of the -485D version but the bias is

distributed among all the nodes. If bias

is required, place jumpers in locations

E3 and E4 according to Table 6. The

jumper configuration of E3 must match

that of E4. If termination is required,

Note: When all jumpers are left open, minimal bias is provided by a pair of

10K-ohm resistors.

-485X AC Coupled EIA-485

The AC coupled EIA-485 transceiver offers advantages over DC coupled

EIA-485. No bias adjustments need to be made since each transceiver has

its own fixed bias network isolated by a pulse transformer. Unlike the DC

coupled EIA-485, wiring polarity is unimportant. Either inverted or straight

through cable can be used or even mixed within one AC coupled network.

Much higher common mode voltage levels can be achieved with AC

coupling due to the transformer coupling which has a 1000 Vdc breakdown

rating.

There are disadvantages to the AC coupled transceiver as compared to the

DC coupled technology. The DC coupled distances are longer (900 feet)

compared to the AC coupled distance (700 feet). The AC coupled

transceiver will operate at 1.25, 2.5 and 5.0 Mbps while the DC coupled

transceiver will operate over all six data rates.

TD874100-0IH

12

Page 13

The cabling rules of the -485X are similar to the -485D. Dual RJ-11

connectors and one three-position screw terminal connector are used in each

NIM. Wire a maximum of 13 NIMs in a daisy-chain fashion leaving the end

NIMs with vacant RJ-11 connections. On these NIMs insert a jumper at E1

on both -485X daughter boards to invoke 120-ohm termination resistors or

leave the jumpers open and insert RJ-11 style passive terminators in each of

the two vacant RJ-11 jacks. Termination can also be accomplished by

installing a 120-ohm, ¼ watt resistor across pins 1 and 2 of the screw

terminals at each end of the bus segment. Refer to Tables 4 and 5 for

connector pin assignments. Termination should not be applied to any of the

NIMs located between the two end NIMs of the segment. Do not mix -485D

and -485X NIMs together on one segment; however, bridging of the

technologies is possible using active hubs with the appropriate transceivers.

To extend -485X segments, use a hub as discussed under the -485D section.

Make sure that the active hub transceivers are of the -485X type. Cable

inversion is not of any consequence.

Figure 8—Jumper settings for EIA-485 models.

Electromagnetic Compatibility

The PC10420 series complies with Class A radiated and conducted

emissions as defined by FCC Part 15 and EN55022. This equipment is

intended for use in non-residential areas.

Warning

This is a Class A product as defined in EN55022. In a domestic

environment this product may cause radio interference in which case

the user may be required to take adequate measures.

TD874100-0IH

13

Page 14

NEED MORE HELP INSTALLING THIS PRODUCT?

More information can be found on our web site at www.ccontrols.com. When

contacting one of our offices, just ask for Technical Support.

Warranty

Contemporary Controls (CC) warrants its new product to the original purchaser for two years from the product shipping date. Product returned to CC

for repair is warranted for one year from the date that the repaired product is

shipped back to the purchaser or for the remainder of the original warranty

period, whichever is longer.

If a CC product fails to operate in compliance with its specification during the

warranty period, CC will, at its option, repair or replace the product at no

charge. The customer is, however, responsible for shipping the product; CC

assumes no responsibility for the product until it is received.

CC’s limited warranty covers products only as delivered and does not cover

repair of products that have been damaged by abuse, accident, disaster, misuse, or incorrect installation. User modification may void the warranty if the

product is damaged by the modification, in which case this warranty does not

cover repair or replacement.

This warranty in no way warrants suitability of the product for any specific

application. IN NO EVENT WILL CC BE LIABLE FOR ANY DAMAGES

INCLUDING LOST PROFITS, LOST SAVINGS, OR OTHER INCIDENTAL

OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OR

INABILITY TO USE THE PRODUCT EVEN IF CC HAS BEEN ADVISED

OF THE POSSIBILITY OF SUCH DAMAGES, OR FOR ANY CLAIM BY

ANY PARTY OTHER THAN THE PURCHASER.

THE ABOVE WARRANTY IS IN LIEU OF ANY AND ALL OTHER

WARRANTIES, EXPRESSED OR IMPLIED OR STATUTORY, INCLUDING THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR

PARTICULAR PURPOSE OR USE, TITLE AND NONINFRINGEMENT.

Returning Products for Repair

Return the product to the location from which it was purchased by following

the instructions at the URL below:

www.ccontrols.com/rma.htm

DECLARATION OF CONFORMITY

Information about the regulatory compliance of this product can be found at the

URL below:

www.ccontrols.com/compliance.htm

TD874100-0IH

14

Page 15

[This page was deliberately left blank.]

TD874100-0IH

15

Page 16

[This page was deliberately left blank.]

TD874100-0IH

16

Loading...

Loading...