Consumer Microcircuits Limited FX839P4, FX839D5, FX839D2 Datasheet

CML Semiconductor Products

Analogue Control Interface

FX839

1.0 Features

• Three DACs

8 or 10-Bit Resolution

• Custom IRQ Generator with Variable

8-Bit Reference Settings

• Multiplexed 4 Input ADC

10-Bit Resolution

• Scalable ADC Clock Frequencies

from Xtal/Clock

• Two Variable Attenuators • Serial Interface to Host µC

• Low Power (3.0V Operation) • 24-Pin SSOP Package

September 1997

D/839/4

Advance Information

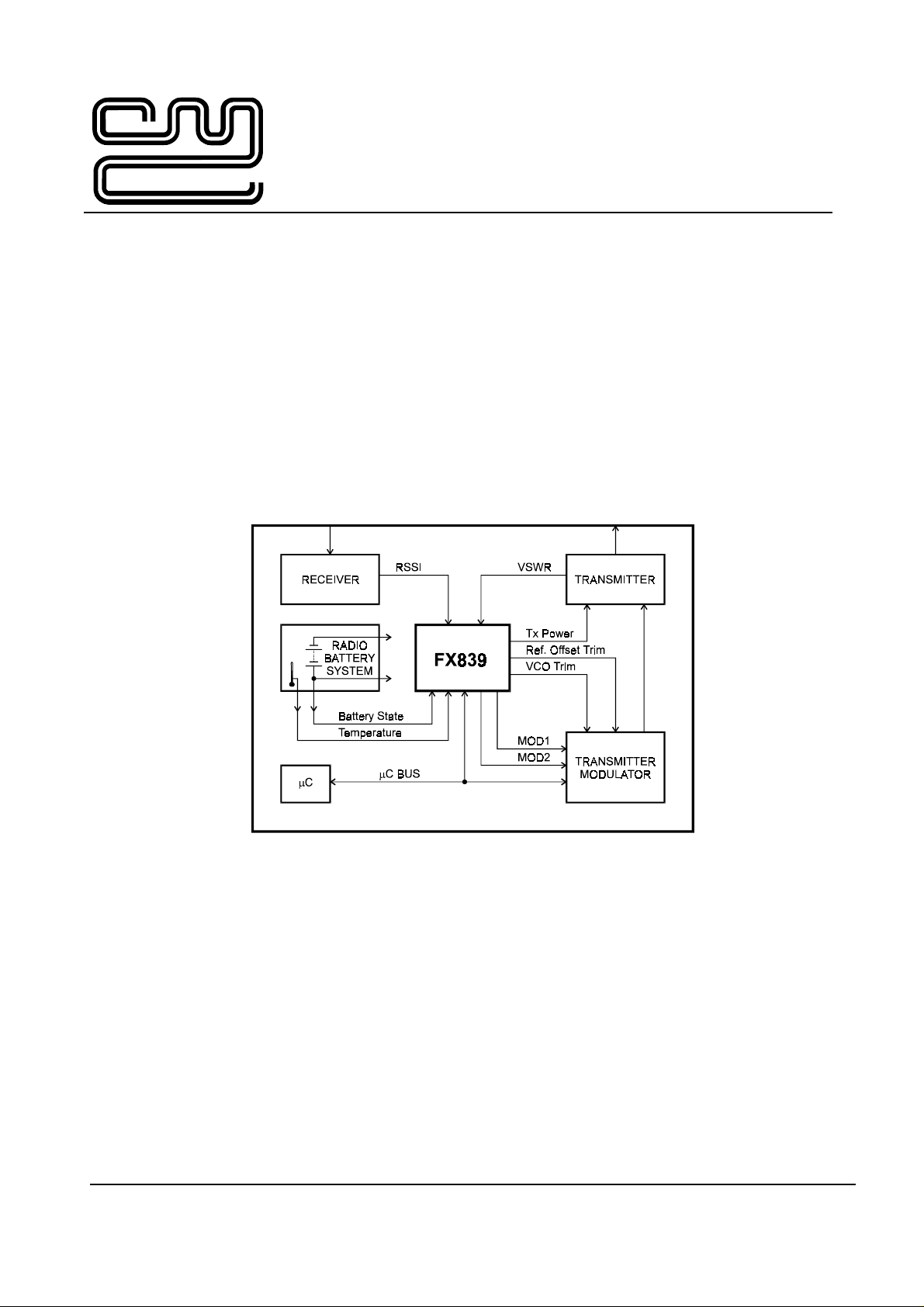

1.1 Brief Description

This product comprises a selection of independent functional blocks vital to modern microcomputer controlled

radio-frequency communications equipment. Examples of possible uses are as follows:

The four-way multiplexed ADC with magnitude comparator may be used for monitoring RSSI, battery

•

voltage, temperatures, reflected signals or error voltages.

The three DACs may be used to adjust VCOs, reference oscillators, power output, bias current or IF gain.

•

The two variable attenuators may be used to adjust deviation, modulation depth or baseband gain.

•

The FX839 is controlled via the standard serial 'C-BUS'. This is complementary to, and c ompatible with, many

standard microcomputers and other baseband processing blocks.

Consumer Microcircuits Limited

1997

Analogue Control Interface

Section

1.0 Features..........................................................................................................1

1.1 Brief Description............................................................................................1

1.2 Block Diagram................................................................................................3

1.3 Signal List.......................................................................................................4

1.4 External Components.................................................................................... 6

1.5 General Description....................................................................................... 7

1.5.1 Software Description

1.6 Application Notes.........................................................................................15

1.6.1 General

1.7 Performance Specification.......................................................................... 16

1.7.1 Electrical Performance

1.7.2 Packaging

FX839

CONTENTS

Page

.....................................................................8

..........................................................................................15

................................................................16

.....................................................................................21

Note:

As this product is still in development, it is likely that a number of changes and additions will be made to

this specification. Items marked TBD or left blank will be included in later issues. Information in this

data sheet should not be relied upon for final product design.

Consumer Microcircuits Limited 2

1997

D/839/4

Analogue Control Interface

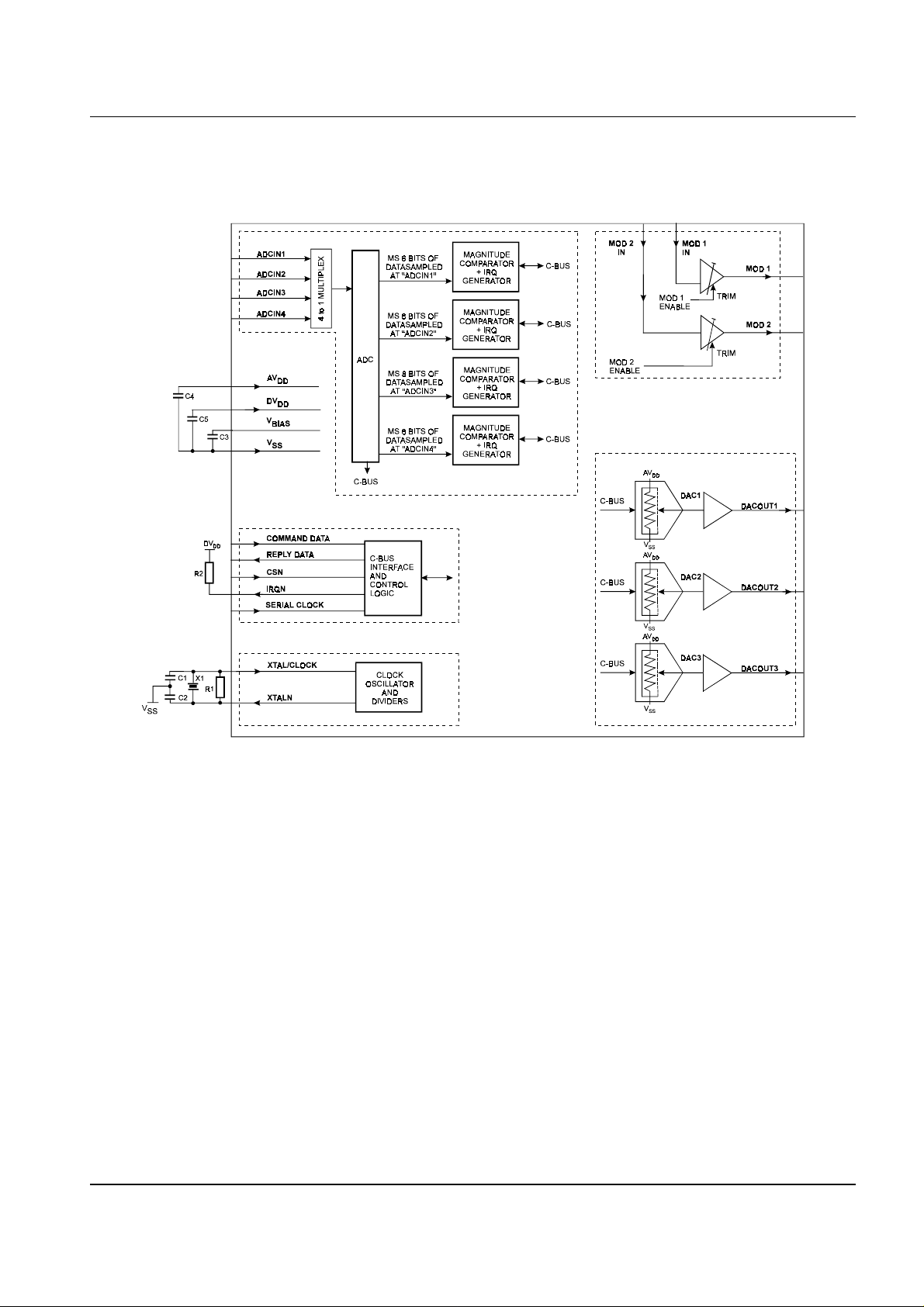

1.2 Block Diagram

FX839

Consumer Microcircuits Limited 3

1997

Figure 1: Block Diagram

D/839/4

Analogue Control Interface

1.3 Signal List

FX839

Package

P4/D2/D5

Signal Description

Pin No. Name Type

1 XTALN O/P The inverter output of the on-chip oscillator.

2 XTAL/CLOCK I/P The input to the on-chip oscillator, for external Xtal circuit

or clock.

3 SERIAL

CLOCK

I/P The 'C-BUS' serial clock input. This clock, produced by

the µController, is used for transfer timing of commands

and data to and from the device.

See 'C-BUS' Timing Diagram (Figure 4).

4 COMMAND

DATA

I/P The 'C-BUS' serial data input from the µController. Data is

loaded into this device in 8-bit bytes, MSB (B7) first, and

LSB (B0) last, synchronised to the SERIAL CLOCK.

See 'C-BUS' Timing Diagram (Figure 4).

5 REPLY DATA O/P The 'C-BUS' serial data output to the µController. The

transmission of REPLY DATA bytes is synchronised to the

SERIAL CLOCK under the control of the CSN input.

This 3-state output is held at high impedance when not

sending data to the µController. See 'C-BUS' Timing

Diagram (Figure 4).

6 CSN I/P The 'C-BUS' data loading control function: this input is

provided by the µController. Data transfer sequences are

initiated, completed or aborted by the CSN signal.

See 'C-BUS' Timing Diagram (Figure 4).

7 IRQN O/P This output indicates an interrupt condition to the

µController by going to a logic '0'. This is a 'wire-ORable'

output, enabling the connection of up to 8 peripherals to 1

interrupt port on the µController. This pin has a low

impedance pulldown to logic '0' when active and a highimpedance when inactive. An external pullup resistor is

required.

The conditions that cause interrupts are indicated in the

IRQ FLAG register and are effective if not disabled.

8 ADCIN1 I/P Analogue to digital converter input 1 (ADC1)

9 ADCIN2 I/P Analogue to digital converter input 2 (ADC2)

Consumer Microcircuits Limited 4

1997

D/839/4

Analogue Control Interface

FX839

1.3 Signal List

Package

P4/D2/D5

(continued)

Signal Description

Pin No. Name Type

10 ADCIN3 I/P Analogue to digital converter input 3 (ADC3)

11 ADCIN4 I/P Analogue to digital converter input 4 (ADC4)

12 V

SS

P

OWER

The negative supply rail (ground) for both analogue and

digital supplies.

13 V

BIAS

O/P An analogue bias line for the internal circuitry, held at ½

. This pin must be decoupled by a capacitor mounted

AV

DD

close to the device pins.

14 N/C No internal connection. Do not make any connection to

this pin.

15 DACOUT1 O/P Digital to analogue converter No. 1 output (DAC1)

16 DACOUT2 O/P Digital to analogue converter No. 2 output (DAC2)

17 DACOUT3 O/P Digital to analogue converter No. 3 output (DAC3)

18 N/C No internal connection. Do not make any connection to

this pin.

19 AV

DD

P

OWER

The positive analogue supply rail. Analogue levels and

voltages are dependent upon this supply. This pin should

be decoupled to V

by a capacitor.

SS

20 MOD1 IN I/P Input to MOD1 variable attenuator.

21 MOD2 IN I/P Input to MOD2 variable attenuator.

22 MOD1 O/P Output of MOD1 variable attenuator.

23 MOD2 O/P Output of MOD2 variable attenuator.

24 DV

DD

P

OWER

The positive digital supply rail. Digital levels and voltages

are dependent upon this supply. This pin should be

by a capacitor.

SS

Notes:

decoupled to V

I/P = Input

O/P = Output

Consumer Microcircuits Limited 5

1997

D/839/4

Analogue Control Interface

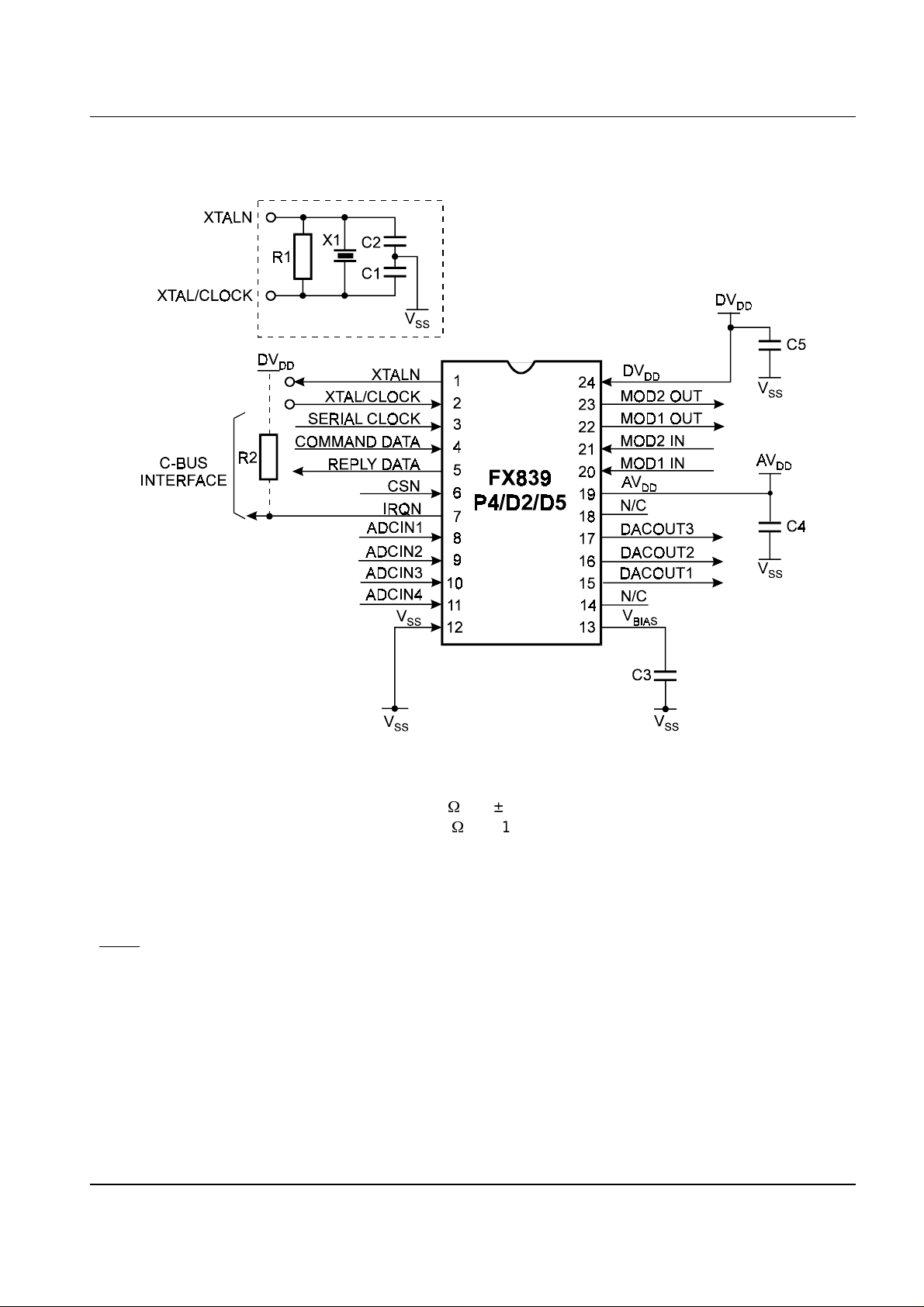

1.4 External Components

FX839

C1 22pF ±20% R1 1M

C2 22pF ±20% R2 22k

C3 0.1µF ±20%

C4 0.1µF ±20%

C5 0.1µF ±20%

Notes

: 1. If an external clock is to be used, it should be connected to Pin 2 and the components C1, C2,

R1 and X1 omitted. The ADC clock frequency is derived from the cryst al or external clock by

means of internal programmable dividers. Refer to Section 1.7 for details of cry stal or external

clock frequency range.

Figure 2: Recommended External Components

Consumer Microcircuits Limited 6

1997

±5% X1 Note 1

:

±10%

:

D/839/4

Analogue Control Interface

FX839

1.5 General Description

The device comprises four groups of r elated functions: variable attenuators, digital to analogue converters, a

multiplexed analogue to digital converter with multiplexer, clock generator and four 8-bit magnitude

comparators with variable reference lev els. These functions are all controlled by the 'C-BUS' serial interface

and are described below:

Variable Attenuators

The two variable attenuators have a range of 0 to -12dB and 0 to -6dB respectively and may be c ontrolled

independently.

Digital to Analogue Converters

Three DACs are provided with default resolutions of 8 bits, which are defined at the initial chip reset. In this

mode the 'C-BUS' data is transferred in a single byte. An option is provided to define any one or more of the

DAC resolutions to be 10 bits, then the DAC requires the transfer of two 'C-BUS' data bytes.

The upper and lower DAC reference voltages are defined internally as AV

and VSS respectively. The output

DD

voltage is expressed as:

= AVDD x (DATA / 2n) [Volts]

V

OUT

Where, n is the DAC resolution (8 or 10 bits) and DATA is the dec imal v alue of the input code. For ex ample: n

= 8 and binary code = 11111111 therefore DATA = 255

= AVDD x (255 / 256) [Volts]

V

OUT

Any one of the three DAC input latches may be loaded by sending an address/command byte followed by one

or two data bytes to the 'C-BUS' interface. The data is then latc hed and the static voltage is updated at the

appropriate output.

When a DAC is disabled its output is defined as open-circuit.

Analogue to Digital Converter and ADC Clock Generator

A single successive approximation ADC is provided with four multiplexed inputs. In order to minimise the

sampling time of each input channel, a Sample and Hold circuit has not been included at the input of the ADC.

For the sampling to be accurate the input signal should not change significantly during the conver sion time.

Since the typical application is for the monitoring of slowly changing control voltages this should not present

any problems. The maximum signal 'linear rate of change', 'S', can be quantified by the following expres sion

(for a maximum 1 bit error):

Where f

S = AV

is the internal ADC clock frequency.

adc_clk

DD

x f

/ (210 x 1000 x (10 + 2)) [mV/µs]

adc_clk

The programmable clock generator is intended to be flexible, making use of an external system clock signal or

a dedicated crystal. This clock signal is scaled to provide the internal ADC cloc k frequency ( f

adc_clk

). The user

has full control of the frequency scaling fac tor and this s hould be chos en s uc h that the input cloc k frequenc y , at

the XTAL/CLOCK pin, divided by this factor is no more than 1MHz.

Consumer Microcircuits Limited 7

1997

D/839/4

Loading...

Loading...