Consumer Microcircuits Limited FX806ALS, FX806ALG, FX806AJ Datasheet

FX806A

A

UDIO PROCESSOR

SERIAL

CLOCK

MAIN

PROCESS

OUT

XTAL/CLOCK

CLOCK

GENERATOR

DE-EMPHASIS

FILTER

(RX)

AUDIO IN

INPUT

PROCESS

MAIN PROCESS

OUTPUT DRIVES

To EXTERNAL AUDIO

PROCESSES

EXTERNAL AUDIO

PROCESS IN

CALIBRATION INPUT

ATTENUATOR

CHIP

SELECT

PRIMARY

and

SECONDARY

AUDIO

INPUTS

———

Voice.

Sub-/Audio

Tone.

FFSK.

etc.

SUM

OUT

MOD.

IN

COMMAND

DATA

#

# #

(TX)

MIC. IN

ATTENUATOR

MODULATION 2

OUT

MODULATION 1

OUT

LOUDSPEAKER

AUDIO

TRANSMITTER

MODULATION

DRIVES

C-BUS INTERFACE

VOGAD SENSE

ATTENUATOR

MODULATION

SUMMING

AMP

POWER

SUPPLY

PRE-EMPHASIS

LIMITING

FILTERING

GAIN SETTING

# indicates logic control

#

#

#

# # #

#

#

#

MIC. & VOGAD

AMPS

LOW &

HIGHPASS

FILTERS

GAIN

SET

VOGAD

SENSE

#

#

BUFFER

VOGAD

SENSE

XTAL

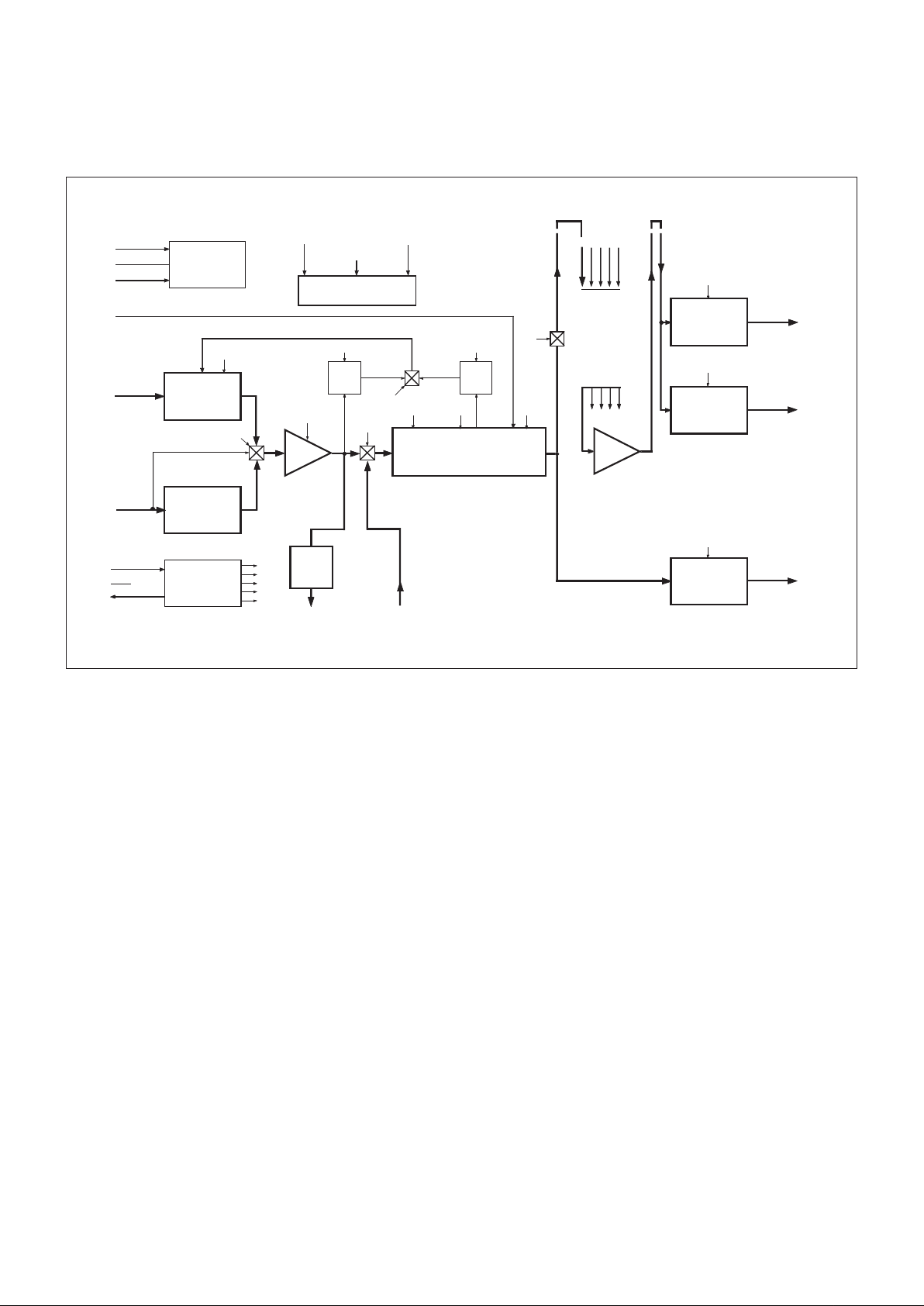

Fig.1 FX806A Audio Processor

● Main Process

Conditioning for Input or External Process signals with

gain/pre-emphasis, high and lowpass switched capacitor

filters and a transmitter deviation limiter. The Main Process

Output may be switched to V

BIAS

.

● Summation and Output Drives

Main “voice audio” from the Main Process is combined

with signalling and data from other DBS 800 facilities, to

provide the composite (in and outband) signal for the digitally

adjustable Transmitter Modulation Drives.

Received audio is level (volume) adjusted for output to

loudspeaker circuitry.

Signal-level stability and therefore output accuracy, of

the FX806A is maintained by a voltage-controlled gain

system (VOGAD) with specific gain sensors that are selected

automatically by the Internal/External Mode Command. The

VOGAD system permits high deviation with low distortion.

This is achieved by reducing the path gain (and so reducing

the distortion introduced by the Peak Deviation limiter) when

the input signal is large.

Signal levels can be controlled to provide ‘dynamiccompensation’ for such factors as temperature drift, VCO

non-linearity, etc.

FX806A audio output stages can be completely disabled

or the whole microcircuit placed into a “Powersave” mode,

leaving only clock and “C-BUS” circuitry active.

The FX806A is a low-power, 5-volt CMOS integrated

circuit and is available in 24-pin DIL cerdip and 24-pin/lead

plastic SMD packages.

Brief Description

Intended primarily to operate as the “Audio Terminal” of

Radio Systems using the DBS 800 Digitally-integrated

Baseband System, the FX806A is a PMR Audio Processor

which meets EIA and CEPT audio specifications.

Using a unique filter line-up, the FX806A offers lower

distortion versus modulation level figures than conventional

filter/limiter configurations.

The FX806A is a half-duplex device whose signal paths

and level-setting elements are dynamically configured and

adjusted by digital information sent from the Radio

µController using “C-BUS” hardware and software protocol.

Figure 5 shows a complete functional block diagram of

the FX806A signal paths which can be viewed as 3 sections:

● Input Process

Selectable transmit or receive input paths.

The transmit path with low-noise input and VOGAD

amplifiers and bandpass filtered stages provides good signalto-noise performance at low input levels and minimum

distortion for high-drive modulation signals.

De-emphasis is software selectable at the Rx Audio Input

for FM or PM radio configurations.

This initial audio, after in-line gain adjustment, is

available for switching to either external audio processes

(such as scrambling) or internally to the Main Process

stages.

Publication D/806A/3 July 1994

2

Pin Number Function

FX806A

J/LG/LS

1

2

3

4

5

6

7

8

9

10

11

12

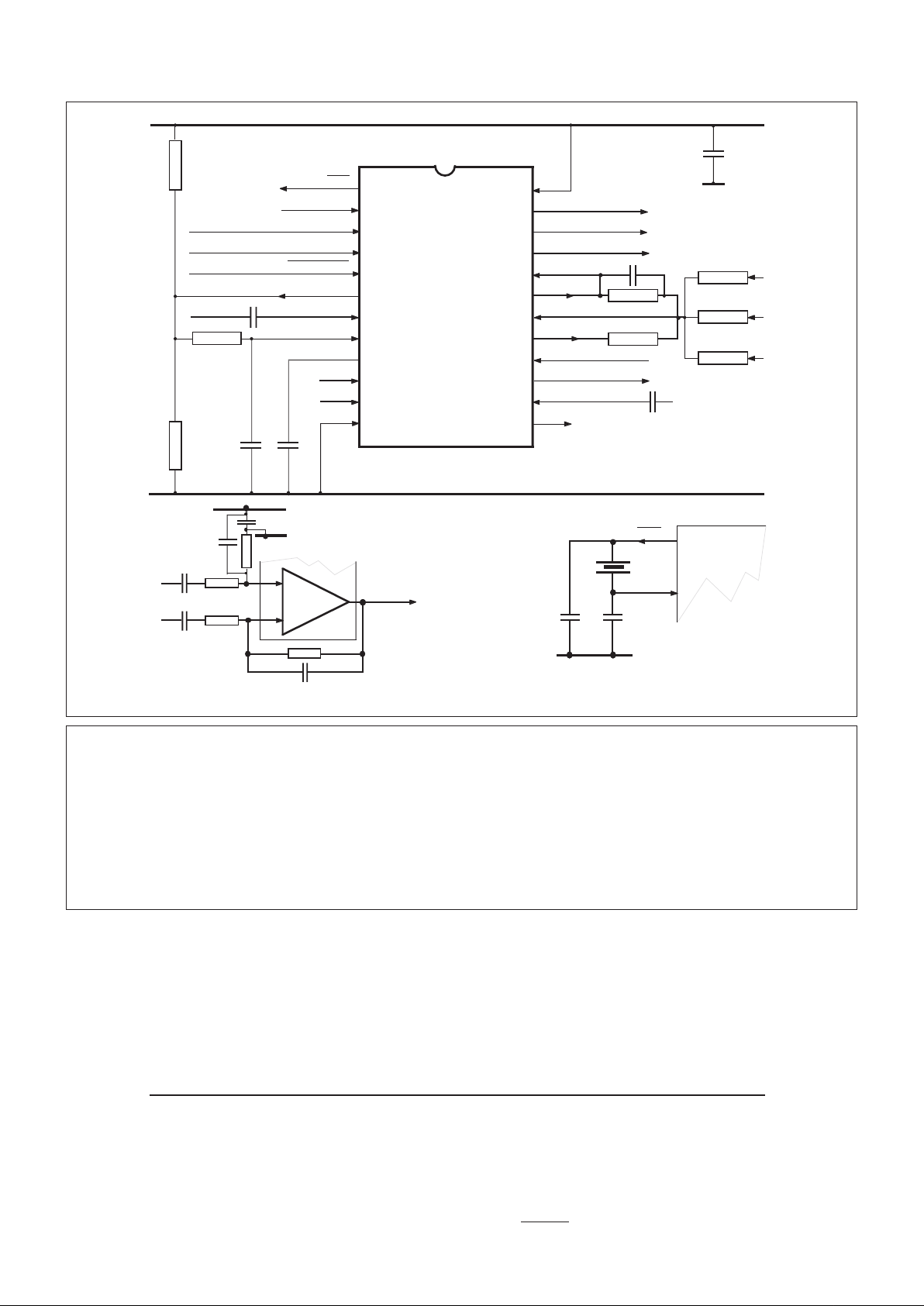

Xtal: The output of the on-chip clock oscillator. External components are required at this output when

a Xtal circuit is employed. See Figure 2, INSET 2.

Xtal/clock: The input to the on-chip clock oscillator inverter. A Xtal or externally derived clock should

be connected here. See Figure 2, INSET 2. This clock provides timing for on-chip elements, filters etc.

Serial Clock: The “C-BUS,” serial data loading clock input. This clock, produced by the µController, is

used for transfer timing of Command Data to the Audio Processor. See Timing diagrams and System

Support Document.

Command Data: The “C-BUS,” serial data input from the µController. Command Data is loaded to

this device in 8-bit bytes, MSB (B7) first, and LSB (B0) last, synchronized to the Serial Clock. The

Command/Data instruction is acted upon at the end of loading the whole instruction. Command

information is detailed in Tables 1, 2, 3, 4 and 5. See Timing diagrams and System Support

Document.

Chip Select (CS): The “C-BUS,” data loading control function. This input is provided by the

µController. Command Data transfer sequences are initiated, completed or aborted by the CS signal.

See Timing diagrams and System Support Document.

VOGAD Out: The output of the relevant VOGAD sensor. This output, with external attack and decay

setting components, should be connected as in Figures 2 and 3, to the VOGAD In pin.

Rx Audio In: The audio input to the FX806A from the radio receiver's demodulator circuits. This

input, which requires to be a.c. coupled with capacitor C

12

, is selected by a Control Command bit.

VOGAD In: The gain control signal from the selected VOGAD sensor (VOGAD Out) to the “Input

Process” Voltage Controlled Amplifier. VOGAD operation is enabled via a Mode Command (Bit5).

Individual sensors, automatically selected, permit gain control from either the Input Process or an

external process. External attack and decay setting components should be applied as recommended

in Figures 2 and 3.

V

BIAS

: The output of the on-chip analogue circuitry bias system, held internally at VDD/2. This pin

should be decoupled to VSS by a capacitor C10, See Figure 2.

Mic In (+): The non-inverting input to the microphone Op-Amp. This input requires external

components for Op-Amp gain/attenuation setting as shown in Figure 2, INSET 1.

Mic In (–): The inverting input to the microphone Op-Amp. This input requires external components

for Op-Amp gain/attenuation setting as shown in Figure 2, INSET 1.

V

SS

: Negative supply rail (GND).

3

Pin Number Function

FX806A

J/LG/LS

13

14

15

16

17

18

19

20

21

22

23

24

Mic Out: The output of the microphone Op-Amp, used with the Mic In (–) input to provide the required

gain/attenuation using external components as shown in Figure 2. The external components shown are

to assist in the use of this amplifier with either inverting or non-inverting inputs. During Powersave

(Volume Command) this output is placed at V

SS

.

Processed Audio In: The input to the device from such external audio processes as Voice Store and

Retrieve or Frequency Domain Scrambling. This input, which requires to be a.c. coupled with a

capacitor, C

13

, is selected by a Mode Command bit.

External Audio Process: The buffered output of the Input Processing stage. For further external

audio processing prior to re-introduction at the Processed Audio In pin.

CALibration Input: A unique input, intended to be used for dynamic balancing of the modulator drives

and for measuring Deviation Limiter levels. A CUE (beep) input from the FX803 Audio Tone Processor

can be entered on this line. This input is selected via a Mode Command bit (11

H

) and is self-biased.

Main Process Out: The output of the Main Process stage. This output is summed with additional

system inputs as required (Audio, Sub-Audio Signalling, FFSK – See System Overview) in the on-chip

Modulation Summing Amplifier. External components as shown in Figure 2 should be used as required.

Sum In:

The input and output terminals of the on-chip Modulation Summing Amplifier. External components

are required for input signals, with gain/attenuation setting as shown in Figure 2. For single-signal,

no-gain requirements, Main Process Out may be linked directly to Modulation In.

Sum Out:

Modulation In: The final, composite modulating signal to VCO (Mod 1) and Reference (Mod 2) Output

Drives.

Audio Output: The processed audio signal output intended as a received audio (volume) output.

Though normally used in the Rx mode, operation in Tx is permitted. The output level of this attenuator is

controlled via a Volume Set command. During Powersave this output is placed at V

SS

.

Modulation 1 Drive: The drive to the radio modulator Voltage Controlled Oscillator (VCO), from the

composite audio summing stage.

Modulation 2 Drive: The drive to the radio modulator Reference Oscillator, from the composite audio

summing stage.

NOTE: These VCO output attenuators are individually adjustable using the Modulator Levels command.

During Powersave these outputs are placed at V

SS

.

V

DD

: Positive supply rail. A single, stable +5 volt supply is required. Levels and voltages within the

Audio Processor are dependant upon this supply.

4

Analogue Application Information

External Components

MAIN

PROCESSOUT

XTAL/CLOCK

C

9

VOGAD OUT

VOGAD IN

MIC. IN (+)

MIC. IN (-)

SERIAL CLOCK

COMMAND DATA

CHIP SELECT

RX AUDIO IN

MIC. OUT

PROCESSED AUDIO IN

EXTERNAL AUDIO PROCESS

CALIBRATION IN

SUM IN

SUM OUT

MOD IN

AUDIO OUT

MODULATION 1 DRIVE

MODULATION 2 DRIVE

EXTERNAL SIGNAL

AND

DATA INPUTS

C

8

C

10

R

5

C

12

SEE INSET 2

SEE INSET 1

R

8

R

7

R

9

R

10

C

13

INSET 2

XTAL/CLOCK

C

7

X

1

1

2

FX806A J

INSET 1

MIC. IN (+)

MIC. IN (-)

MIC. OUT

10

11

13

+

-

R

3

C

3

C

1

R

1

C

2

R

2

C

4

C

5

R

4

FX806A J

XTAL

R

12

V

SS

V

DD

XTAL

V

BIAS

V

SS

V

SS

R

11

V

SS

V

SS

C

6

V

BIAS

C

11

V

DD

13

14

15

16

17

18

19

20

21

22

23

24

1

2

3

4

5

6

7

8

9

10

11

12

FX806A J

R

6

Fig.2 Recommended External Components

Component Value

R

1

= 10.0kΩ

R

2

10.0kΩ

R

3

20.0kΩ

R

4

20.0kΩ

R

5

10.0kΩ

R

6

2.2MΩ

R

7

100kΩ

R

8

100kΩ

R

9

100kΩ

R

10

= 100kΩ

R

11

100kΩ

R

12

2.2MΩ

C

1

470nF

C

2

470nF

C

3

270pF

C

4

270pF

C

5

0.1µF

C

6

33pF

C

7

= 5 – 65pF

C

8

1.0µF

C

9

1.0µF

C

10

1.0µF

C

11

22pF

C

12

100nF

C

13

10.0nF

X

13

4.0MHz

Tolerance: R = ±10%. C = ± 20%

Notes

To demonstrate the versatility of the Mic. inputs, Input

Op-Amp gain/attenuation components for a voltage gain of

6.0dB are shown (INSET 1) in a differential configuration.

Components for a single (+ or -) input may be employed.

Resistor values R7 to R11 (summation components) are

dependant upon application and configuration requirements.

Xtal circuit capacitors C6 (CD) and C7 (CG) shown (INSET

2) are recommended in accordance with

CML Application

Note D/XT/2 December 1991

. Circuit drive and drain resistors

are incorporated on-chip.

Operation of any CML microcircuit without a Xtal or clock

input may cause device damage. To minimise damage in the

event of a Xtal/drive failure, it is recommended that the power

rail (VDD) is fitted with a current limiting device (resistor or fast

reaction fuse).

VOGAD Components Calculations – Figures 2 and 3

Provided R

5

>>1.0kΩ and R6 = R12 >>R

5

Then:

Attack Time (TA) = R5 x C

8

Decay Time (TD) = R6 x C

8

2

Loading...

Loading...