Consumer Microcircuits Limited FX805LS, FX805LG, FX805J Datasheet

FX805 Sub-Audio

Signalling Processor

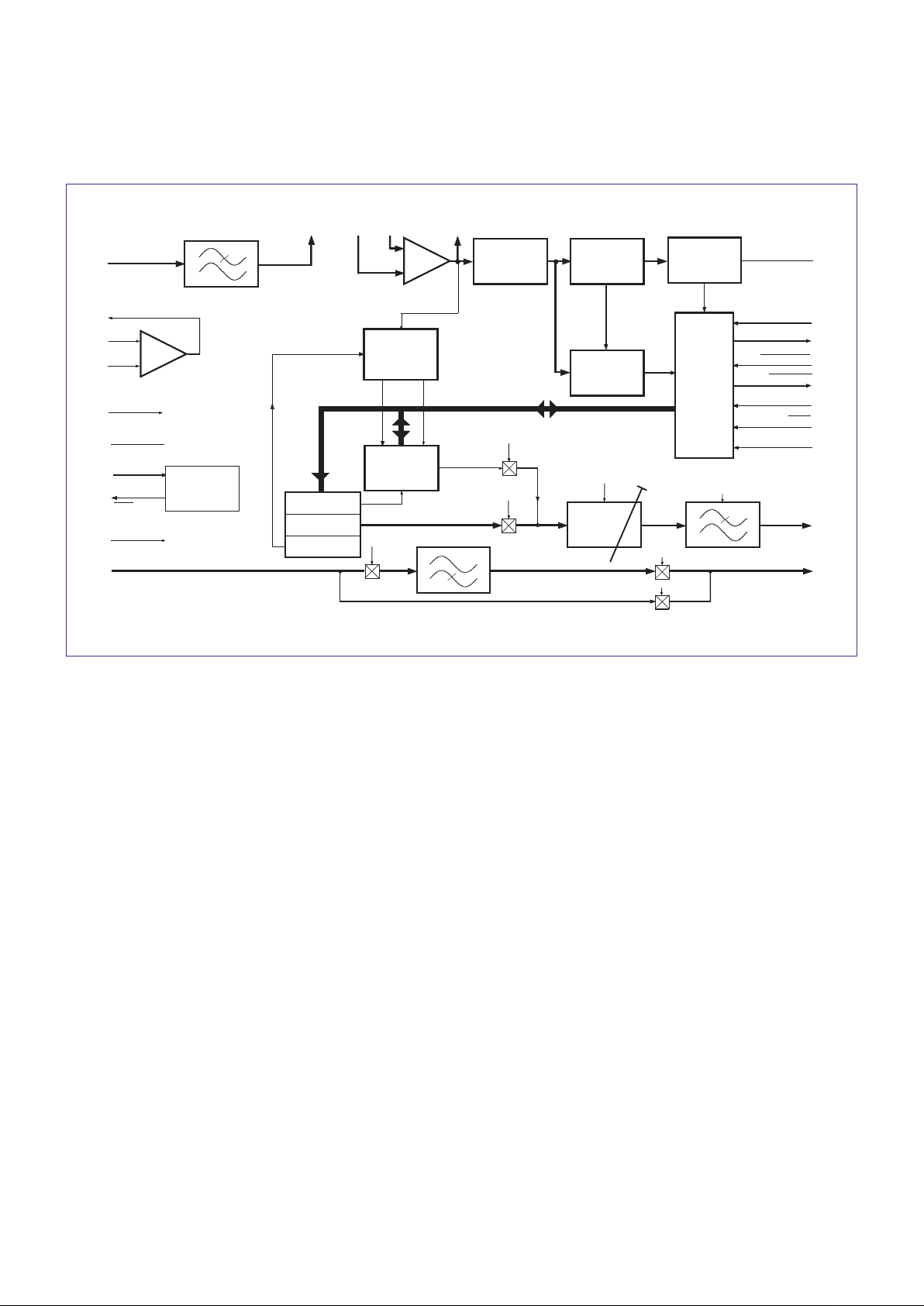

AUDIO IN

COMMAND DATA

C-BUS

INTERFACE

AND

CONTROL

LOGIC

REPLY DATA

SERIAL CLOCK

XTAL/CLOCK

NOTONE

ADDRESS SELECT

Tx LEVEL

ADJUST

Rx SUB-AUDIO

OUT

+

–

Rx AMP

COMPARATOR

AMP

Tx

SUB-AUDIO

OUT

AUDIO OUT

Rx SUB-AUDIO

IN

NOTONE

TIMER

DIGITAL

NOISE

FILTER

CLOCK

GENERATOR

DATA BUFFER

and

SHIFT REGISTER

SUB-AUDIO BANDSTOP

Variable

Bandwidth

NRZ Tx BAUD

RATE

V

DD

V

BIAS

V

SS

180Hz/260Hz

COMPARATOR

IN OUT

CHIP SELECT

WAKE

FREQUENCY

ASSESMENT

IN

OUT

NRZ

Rx Data

NRZ

Rx Baud Rate

CTCSS

Tx TONE

NRZ Rx

CLOCK RATE

NRZ Rx

DATA and

BAUD RATE

EXTRACTOR

+

–

Raw NRZ “Data”

CTCSS “Sub-Audio” Frequency

INTERRUPT

XTAL

Rx

Tx

NRZ Tx Data

Audio Signal Path

Audio By-Pass

Rx LOWPASS

Tx SUB-AUDIO LOWPASS

FREQUENCY

MEASUREMENT

(COUNTER)

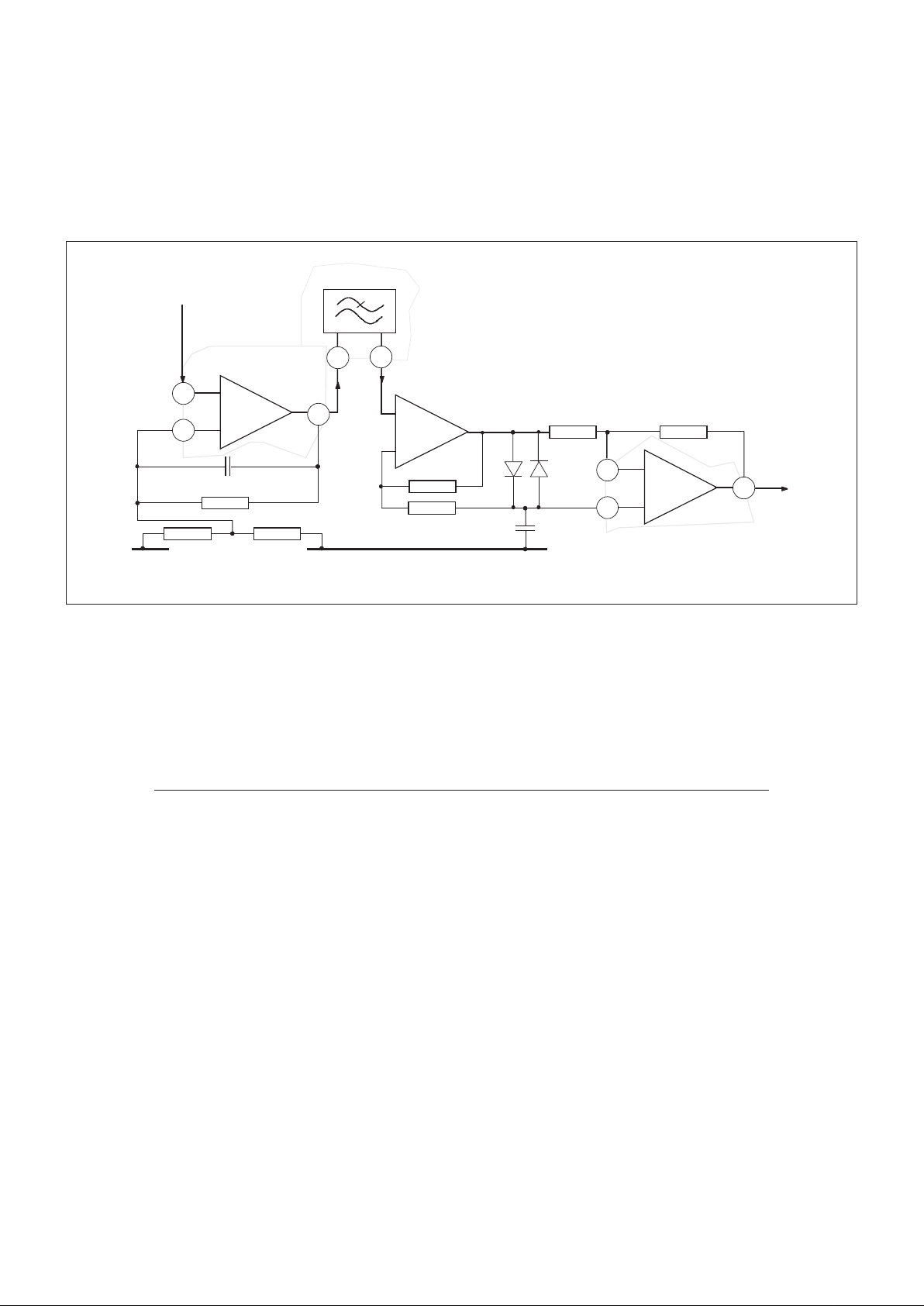

Fig.1 FX805 Sub-Audio Signalling Processor

FX805 Sub-Audio Signalling Processor

A µProcessor controlled, sub-audio frequency signalling

processor to provide an outband audio and digital signalling

facility for PMR radio systems.

This device caters for the transmission and non-predictive

reception of:

●

Continuous Tone Controlled Squelch (CTCSS) tones

and other non-standard sub-audio frequencies.

●

Non-Return-to-Zero (NRZ) data to facilitate Continuous

Digitally Coded Squelch (CDCS/DPL

) system

operations.

To achieve these functions, the FX805 has on-chip:

●

A non-predictive CTCSS Tone Decoder and CDCS subaudio signal demodulator.

●

A CTCSS/NRZ Encoder with Tx level adjustment and

lowpass filter output stage with optional NRZ

pre-emphasis.

●

A selectable sub-audio bandstop filter.

●

A Notone (CTCSS Rx) period timer.

Setting of the FX805 functions and modes is by data

loaded from the µController to the controlling registers within

the device. Reply Data and Interrupt protocol keep the

µController up to date on the operational status of the

circuitry –– all via the “C-BUS” interface.

CTCSS tone data for transmission is generated within the

µController, loaded to CTCSS Tx Frequency Register,

encoded and output as a tone via the Tx Sub-Audio Lowpass

Filter.

Received non-predicted CTCSS tone frequencies are

measured and the resulting data, in the form of a 2-byte

data-word, is presented via the CTCSS Rx Frequency

Register to the µController for matching against a ‘look-up’

table. Noise filtering is provided to improve the signal quality

prior to measurement.

NRZ coded data streams for transmission, when

generated within a µController, are loaded to the NRZ Tx

Data Buffer and output, in 8-bit bytes, through the Lowpass

Filter circuitry as sub-audio signals. CDCS turn-off tones can

be added to the data signals by switching the FX805 to the

CTCSS transmit mode at the appropriate time.

NRZ coding is produced by the µController and translated

into sub-audio signals by the FX805.

Received NRZ data is filtered, detected and placed into

the NRZ Rx Data Register which is then available for transfer

one byte at a time, to the µController, for decoding by

software. Clock extraction circuitry is provided on chip and

Rx and Tx baud rates are selectable.

Provision is made in both hardware and system software

allocations to address two FX805 Sub-Audio Signalling

Processors consecutively to achieve multi-mode, duplex

operation.

The FX805 has a powersaving function which may be

controlled by software or a dedicated (Wake) input.

The FX805 is a low-power, 5-volt CMOS integrated circuit

and is available in 24-pin DIL cerdip and 24-pin/lead plastic

SMD packages.

DPL is a registered trademark of Motorola Inc.

Publication D/805/3 July 1994

2

Pin Number Function

FX805

J/LG/LS

1

2

3

4

5

6

7

8

9

10

11

12

Xtal: The output of the on-chip clock oscillator. External components are required at this input when a

Xtal (f

XTAL

) input is used. See Figure 2.

Xtal/Clock: The input to the on-chip clock oscillator inverter. A Xtal or externally derived clock (f

XTAL

)

should be connected here. See Figure 2.

Address Select: This pin enables two FX805 devices to be used on the same “C-BUS,” providing fullduplex operation. See Tables 1 and 2.

Interrupt Request (IRQ): The output of this pin indicates an interrupt condition to the µController, by

going to a logic “0.” This is a “wire-or able” output, allowing the connection of up to 8 peripherals to 1

interrupt port on the µController. This pin has a low impedance pulldown to logic “0” when active and a

high impedance when inactive. The System IRQ line requires 1 pullup resistor to VDD. The conditions

that cause interrupts are indicated in the Status Register (Table 4) and are shown below:

Rx CTCSS Tone Measurement Complete CTCSS N

OTONE

Timer Expired

1 NRZ Rx Data Byte Received New NRZ Rx Data Received Before Last Byte Read

NRZ Tx Buffer Ready NRZ Data Transmission Complete

Serial Clock: The “C-BUS” serial clock input. This clock, produced by the µController, is used for

transfer timing of commands and data to and from the Sub-Audio Signalling Processor. See Timing

Diagrams.

Command Data: The “C-BUS” serial data input from the µController. Data is loaded to this device in

8-bit bytes, MSB (B7) first, and LSB (B0) last, synchronized to the Serial Clock. See Timing Diagrams.

Chip Select (CS): The “C-BUS” data loading control function. This input is provided by the

µController. Data transfer sequences are initiated, completed or aborted by the CS signal. See Timing

Diagrams.

Reply Data: The “C-BUS” serial data output to the µController. The transmission of Reply Data bytes

is synchronized to the Serial Clock under the control of the Chip Select input. This 3-state output is held

at high impedance when not sending data to the µController. See Timing Diagrams.

Tx Sub-Audio Out: The sub-audio output (pure or NRZ derived). Signals are band-limited, the Tx

Output Filter has a variable bandwidth, see Table 6. This output is at V

BIAS

(a) when the NRZ Encoder

is enabled but no data is being transmitted, (b) when the FX805 is placed in the Powersave All

condition.

Audio In: The input to the switched sub-audio bandstop (highpass) filter. This input is internally biased

and requires to be a.c. coupled by capacitor C

7

.

Audio Out: The output of the ‘audio signal path’ (filter or by-pass). This output is controlled by the

Control Register and when disabled is held at V

DD

/2.

V

SS

: Negative Supply (Signal Ground).

3

Pin Number Function

FX805

J/LG/LS

13

14

15

16

17

18

19

20

21

22

23

24

“C-BUS” is CML’s proprietry standard for the transmission of commands and data between a

µ

Controller and DBS 800 microcircuits. It may be used with any µController, and can, if

desired, take advantage of the hardware serial I/O functions embodied into many types of

µ

Controller. The “C-BUS” data rate is determined soley by the µController.

Rx Amp (-) In: The inverting input to the on-chip Rx Input Amp. See Figures 2, 3 and 4.

Rx Amp (+) In: The non-inverting input to the on-chip Rx Input Amp.

Rx Amp Out: The output of the on-chip Rx Input Op-Amp. This circuit may be used, with external

components, as a signal amplifier and an anti-aliasing filter prior to the Rx Lowpass Filter, or for other

purposes. See Figure 2 for component details.

Rx Sub-Audio In: The received sub-audio (CTCSS/NRZ) input. This input is internally biased to V

DD

/2

and requires to be a.c. coupled or biased. See Figure 2 for component details.

Rx Sub-Audio Out: The output of the Rx Lowpass Filter. This output may be coupled into the on-chip

amplifier or comparator as required.

V

BIAS

: The internal circuitry bias line, held at VDD/2 this pin must be decoupled to VSS by capacitor C

8

(see Figure 2).

Comparator In (-): The inverting input to the on-chip “comparator” amplifier. See Figures 2, 3 and 4.

Comparator (+): The non-inverting input to the on-chip “comparator” amplifier. See Figures 2, 3 and 4.

Comparator Out: The output of the “comparator” amplifier. This node is also internally connected to

the input of the Digital Noise Filter (see Figure 1). When both decoders are Powersaved, this output is

at a logic “0.”

N

OTONE Timing: External RC components connected to this pin form the timing mechanism of a

NOTONE period timer. The external network determines the ‘charge-rate’ of the timer to VDD/2. Expiry of

the timer will cause an interrupt. This facility is only used in the CTCSS Rx mode.

Wake: This ‘real-time ’ input can be used to reactivate the FX805 from the ‘Powersave All’ condition

using an externally derived signal. The FX805 will be in a ‘Powersave All’ condition when both this pin

and Bit 0 of the Control Register are set to a logic “1.” Recovery from “Powersave All” is achieved by

putting either the Wake pin or the ‘Powersave All’ bit to logic “0,” thus allowing FX805 activation by the

µController or an external signal, such as R.S.S.I. or Carrier Detect.

V

DD

: Positive supply rail. A single +5-volt power supply is required. Levels and voltages within the Sub-

Audio Signalling Processor are dependant upon this supply.

NOTE: (i) Further information on external components and DBS 800 system integration of this

microcircuit are contained in the System Support Document.

(ii) A glossary of abbreviations used in this document is supplied.

(iii) Guidance upon the generation and manipulation of NRZ Rx and Tx data is given in DBS

800 Application Support Document.

4

Application Information

External Components

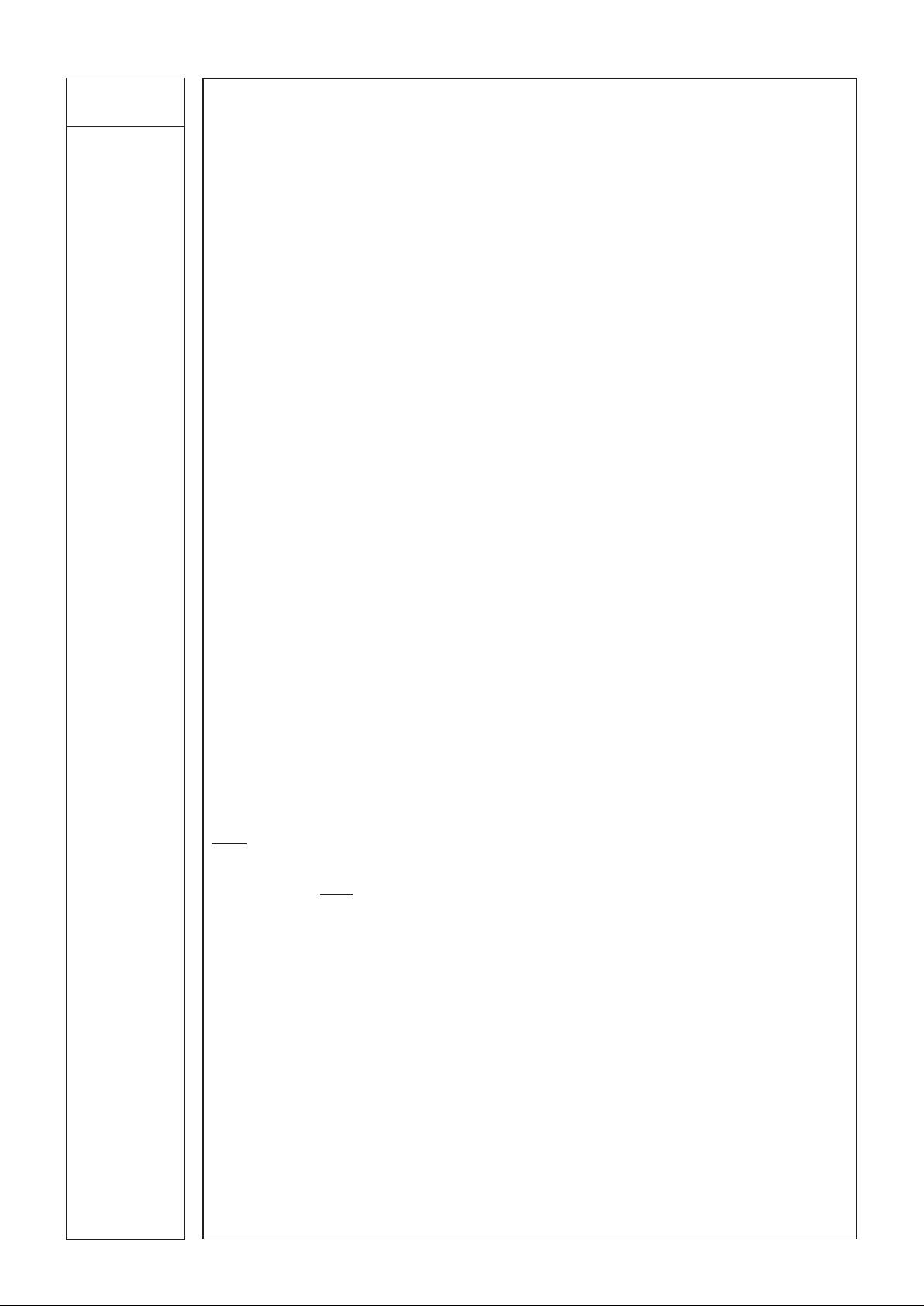

XTAL/CLOCK

V

DD

SEE INSET

V

SS

NOTONEADDRESS SELECT

13

14

15

16

17

18

19

20

21

22

23

24

1

2

3

4

5

6

7

8

9

10

11

12

FX805J

SERIAL CLOCK

COMMAND DATA

REPLY DATA

Tx SUB-AUDIO OUT

AUDIO IN

AUDIO OUT

V

SS

COMPARATOR OUT

COMPARATOR IN (+)

COMPARATOR IN (-)

Rx AMP IN (-)

Rx SUB-AUDIO OUT

Rx AMP IN (+)

Rx SUB-AUDIO IN

Rx AMP OUT

V

SS

*

WAKE

XTAL

CS

V

DD

C

8

C

7

R

8

R

7

R

6

C

5

C

6

R

4

V

BIAS

C

3

R

3

D1D

2

R

5

C

4

R

2

IRQ

2

1

XTAL/CLOCK

V

SS

FX805J

INSET

XTAL

R

1

X

1

C

2

C

1

C6= 1.0µF

C

7

0.1µF

C

8

1.0µF

C

9

Fig.4

D

1

silicon small sig

D

2

silicon small sig

X1f

XTAL

4.00MHz

R9= Fig.4

R

10

Fig.4

R

11

Fig.4

C

1

33.0pF

C

2

33.0pF

C

3

1.5µF

C

4

15.0µF

C

5

1.0µF

Component Value

R1= 1.0MΩ

R

2

360kΩ

R

3

10.0kΩ

R

4

150kΩ

R

5

100kΩ

R

6

150kΩ

R

7

22.0kΩ

R

8

360kΩ

Fig.2 Recommended External Components

Notes

on external components and connections

1. Xtal/clock circuitry components shown INSET are

recommended in accordance with CML Application Note

D/XT/2 December 1991. The DBS 800 System

Information Document contains additional notes on Xtal/

clock distribution and frequencies.

2. R

8

is a System Component. Its value is chosen, for

example, with the FX806 Modulation Summing

Amplifier, to provide a sub-audio signal level of -11.0dB

to the system modulator.

3. Components R

6

and C6 are NOTONE timing components.

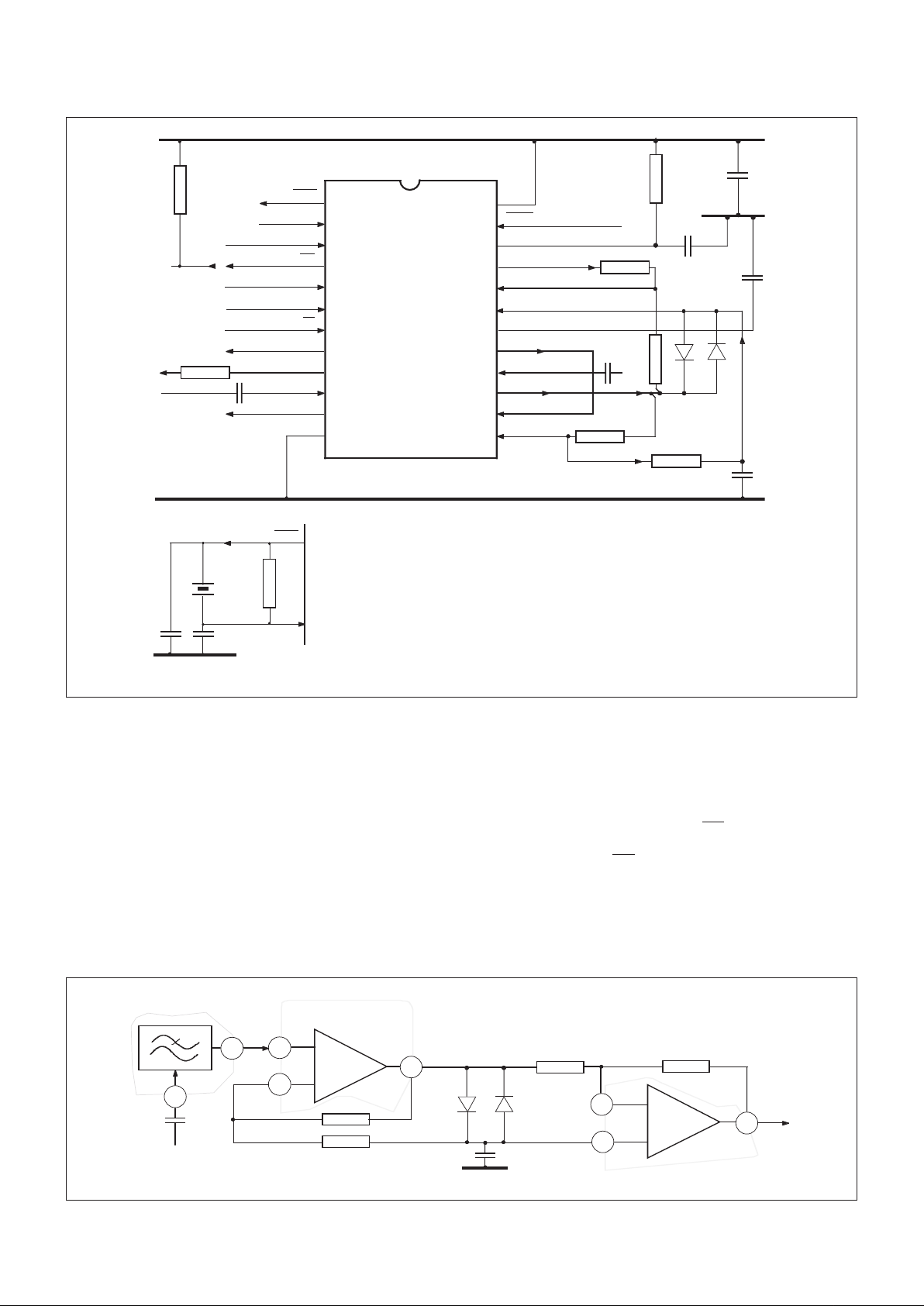

With reference to Figure 2, Figures 3 and 4 show in detail recommended alternative component configurations for the FX805.

14

+

13

–

17

Rx AMP IN

COMPARATOR IN

COMPARATOR OUT

FX805

Rx AMP

FX805

COMPARATOR

20

21

19

D.C. RESTORATION

+

–

HYSTERESIS

R

2

R

5

C

4

V

SS

D

2

D

1

R

3

R

4

FX805 Rx LPF

16

C

3

Rx Sub-Audio Input

15

Fig.3 Employment of FX805 Input Components

4. R2 and R5 are dependant upon the input signal level.

Values given are for the specified composite signal.

5. R7 is used as the DBS 800 system common-pullup for

the “C-BUS” Interrupt Request (IRQ) line, the optimum

value of this component will depend upon the circuitry

connected to the IRQ line.

5

Application Information ......

External Components ......

COMPARATOR IN

14

+

13

–

Rx AMP IN

From

Rx Discriminator

15

COMPARATOR OUT

FX805

Rx AMP

20

21

19

D.C. RESTORATION

HYSTERESIS

R

2

R

5

C

4

V

SS

D

2

D

1

R

3

R

4

+

–

+

–

17

V

DD

C

9

R

9

R

10

R

11

FX805

COMPARATOR

EXTERNAL

OP-AMP

16

FX805 Rx LPF

Fig.4 FX805 Input Components Using an External Op-Amp

Using an External Op-Amp

For d.c. coupling the FX805 to the receiver’s discriminator

output when using NRZ communication, it is recommended

that an additional, external Op-Amp is employed as

configured in Figure 4. This configuration will allow long

sequences of logic “1

s

” or “0s” to be successfully decoded

(eg. LTR trunking systems).

Figure 3 shows an input component configuration for use

generally for CTCSS signal and NRZ data reception.

Input coupling capacitor C

3

is required because the Rx

Sub-Audio Input is held at V

BIAS

during all powered conditions

of the FX805. Diodes D1 and D2 can be any silicon smallsignal diode.

FX805 Operational Modes

NRZ Tx (Encoding)

The NRZ Encoder is formed by a shift register and the Tx

Sub-Audio Lowpass Filter. Data loaded from the Command

Data line is output one 8-bit byte at a time from the NRZ Tx

Data Register. The output data-signal level may be adjusted

and filtered. Data may be pre-emphasized via a “C-BUS”

command. The Tx baud rate is programmed as the NRZ Tx

Baud Rate (R

NRZ Tx

) (Table 5).

CTCSS Tx (Encoding)

The CTCSS Tone Encoder comprises a clock-divider

programmed by an 11-bit binary number (Q) loaded to the

CTCSS Tx Frequency Register (Table 5) via the “C-BUS”

Command Data line.

The square-wave output of the encoder is fed through the

Tx Level Adjust variable gain block to the Tx Sub-Audio

Lowpass Filter, a variable bandwidth circuit controlled by

4-bits (P) of the CTCSS Tx Frequency Register. The Tx SubAudio output is a sine-wave. Standard and non-standard

sub-audio tones are available, a ‘CDCS’ turn-off tone may be

generated.

NRZ Rx (Decoding)

Input (NRZ type) sub-audio signals are filtered and the

data clock extracted. Decoded data is serially loaded into a

shift register buffer. This data is output one 8-bit byte at a

time as Reply Data from the NRZ Rx Data Register (Page

14) to the µController. The expected Rx baud rate is

programmed as the NRZ Rx Baud Rate (R

NRZ Rx

) (Table 5).

Any codeword recognition can be carried out by software.

CTCSS Rx ( Decoding)

Received CTCSS signals are filtered, coherence is

increased by the digital noise filter. The quality of the signal

is assessed by measurement of the cycle-to-cycle period

variance and, provided it is sufficiently good, the frequency is

measured over a period of 122.64 milliseconds.

If the average signal quality is consistently too low, NOTONE

is indicated, if not, the input frequency is precisely indicated

in the CTCSS Rx Frequency Register in a binary form as

shown in Figure 6.

As any single sub-audio tone within the specified range

may be selected, this would enable a ‘CDCS’ turn-off tone

(of 134Hz) to be decoded whilst operating in the NRZ Rx

mode.

The output resistance (open loop) of the on-chip Rx Amp

is ≈ 6kΩ. In the configuration shown in Figure 3, the (Rx

Amp) RC time-constant is therefore 90ms. If this period is

too long for some systems, ie. those employing half-duplex,

short data bursts, an external amplifier should be considered

in place of the FX805 on-chip Rx Amp.

LTR is a registered trademark of E.F. Johnson Company

Components R9, R

10

and R11 should be calculated to

provide an accurate potential of 2.5V d.c. (equal to V

BIAS

) at

pin-junction 15/16 when using a discriminator input. C9 is an

optional component which, if additional filtering is required,

should be calculated, with R9 to provide a lowpass cut-off

frequency (fCO) of 500Hz.

Loading...

Loading...