Consumer Microcircuits Limited FX631P, FX631DW, FX631D5 Datasheet

CML Semiconductor Products

PRODUCT INFORMATION

FX631

Features

Detects 12kHz and 16kHz SPM

Frequencies

Low Power (3.0 Volt

Operation

High Speechband Rejection

Properties

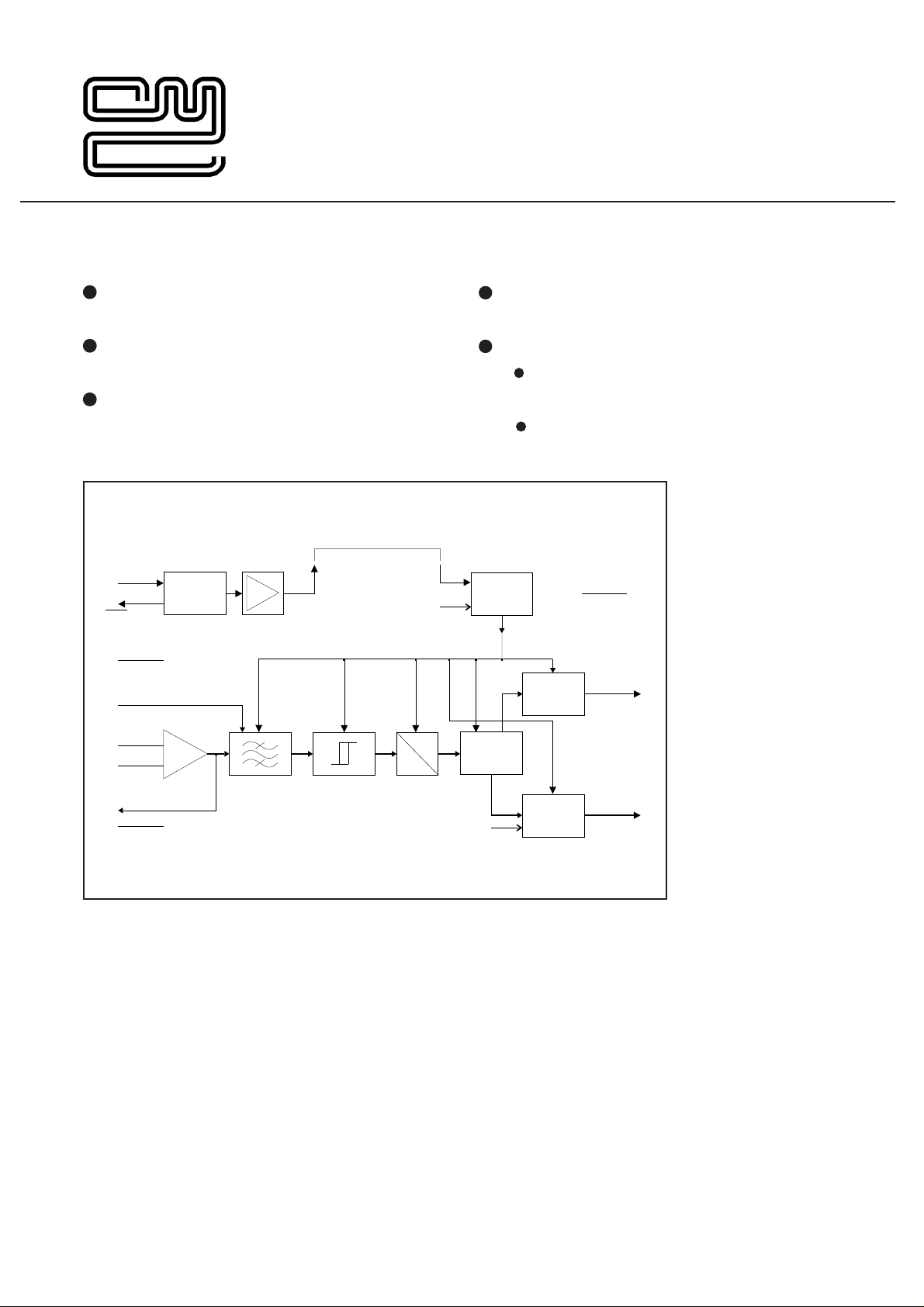

XTAL/CLOCK

XTAL/CLOCK

OSCILLATOR

XTAL

<1.0mA)

MIN

CLOCK

OUT

Low-Voltage SPM Detector

Publication D/631/6 June 1997

Tone-Follower and P ac ket Mode

Outputs

Applications

Complex and/or Simple

T elephone Systems

Call-Charge/-Logging

Systems

CLOCK IN

SYSTEM

CLOCK

DIVIDERS

V

SS

V

DD

SYSTEM

(12kHz/16kHz)

SIGNAL

IN (-)

SIGNAL

IN (+)

AMP OUT

V

BIAS

INPUT AMP

-

+

12kHz/16kHz

+20dB

LEVEL DETECTOR

1

DIVIDER

Fig.1 Functional Block Diagram

Brief Description

The FX631 is a low-power, system-selectable

Subscriber Pulse Metering (SPM) detector to indicate

the presence, on a telephone line, of both 12kHz and

16kHz telephone call-charge frequencies.

Deriving its input directly from the telephone line,

input amplitude/sensitivities are component adjustable

to the user's national ‘Must/Must-Not Decode’

specifications via an on-chip input amplifier, whilst the

12kHz and 16kHz frequency limits are accurately

defined by the use of an external 3.579545MHz

telephone-system Xtal or clock-pulse input.

The FX631, which demonstrates high 12kHz and

16kHz performance in the presence of both voice and

noise, can operate from either a single or differential

analogue signal input from which it will produce two

individual logic outputs.

32

TONE FOLLOWER

OUTPUT

PACKET MODE

OUTPUT

FX631

MEASURE

SYSTEM

PERIOD

TONE

FOLL OW ER

LOGIC

PACKET

TONE

LOGIC

1. Tone Follower Output - A 'tone-following' logic

output producing a “Low” level for the period of a

correct decode and a “High” level for a bad

decode or N

OTONE.

2. Packet (Cumulative Tone) Mode Output - To

respond and de-respond after a cumulative 40ms

of good tone (or N

OTONE) in any 48ms period.

This process will ignore small fluctuations or

fades of a valid frequency input and is available

for µProcessor ‘Wake-Up’, Minimum tone

detection, N

OTONE indication or transient

avoidance.

This system (12kHz/16kHz) selectable microcircuit,

which may be line-powered, is available in 16-pin plastic

DIL and surface mount SOIC and 24-pin plastic SSOP

packages.

1

Pin Number Function

FX631

D5

1

4

5

6

8

12

FX631

DW/P

1

2

3

4

7

8

Xtal/Clock: The input to the on-chip clock oscillator; for use with a 3.579545MHz Xtal in

conjunction with the Xtal output (see Figure 2); circuit components are on chip. Using this

mode of clock operation, the Clock Out pin should be connected directly to the Clock In pin. If

2.3 Pin Function Description

a clock pulse input is employed to the Clock In pin, this pin must be connected directly to V

(see Figure 2).

XTAL The input of the oscillator inverter.

XTALN The output of the oscillator inverter

Xtal: The output of the on-chip clock oscillator inverter.

CLKIN The input to the internal clock divider circuitry.

When a 3.579545MHz crystal is used, it should be connected across XTAL &

Clock Out: The buffered output of the on-chip clock oscillator inverter. If a Xtal input is

should be directly connected to CLKIN. No other external components are necessary because

employed this output should be connected directly to the Clock In pin.

the other oscillator components (capacitor, resistor) are on chip.

When an externally available clock signal is used, it should be inserted at CLKIN. XTAL should

be tied to VDD or Vss and

Clock In: The 3.579545MHz clock pulse input to the internal clock-dividers. If a clock pulse

XTAL should be left open circuit.

input is employed, the Xtal/Clock input (Pin 1) should be connected to V

SYSTEM A logic input pin which controls whether the device detects 12Khz SPM tones (logic 1)

or 16Khz SPM tones (logic 0). It has an internal 1 Mohm pull- up resistor (l 2Khz).

V

: The output of the on-chip analogue bias circuitry. Held internally at VDD/2, this pin should

BIAS

NEGIP The negative input, positive input and output respectively of the gain adjusting POSIP

be decoupled to V

amplifier.

V

: Negative supply rail (GND).

External components are used in conjunction with the op -amp according to the required level

SS

sensitivity and depending on whether the incoming signal is differential or common mode.

SS

AMPOP

(see Figure 2).

XTAL and XTAL

. See Figure 2.

DD

DD

13

17

18

19

20

21

24

10

11

13

14

15

16

9

Signal In (+):

Signal In (-):

The positive and negative signal inputs to, and the output from, the input gain

VDD The power supply, ground and filter bias pins respectively.

adjusting signal amplifier. Refer to the graph in Figure 4 for guidance on

VSS

setting level sensitivities to national specifications, and the selection of gain

BIAS Voo and bias should each be de- coupled, via a 1 .0@F capacitor, to VSS.

adjusting components.

Amp Out:

Tone Follower Output: This output provides a logic “0” (Low) for the period of a detected

tone, and a logic “1” (High) for N

TTFOP TRUE TONE FOLLOWER OUTPUT. This is the pin that responds and de-

responds within 4ms of a good tone appearing or disappearing.

It is thus like an envelope of the SPM tone.

· logic 0 represents ‘detect’ and logic 1 represents ‘not detect’.

OTONE detection. See Figure 7.

Packet Mode Output: A logic output that will be available after a cumulation of 40ms of 'good'

tone has been received. This packet mode tone follower will only respond when a tone

DTFOP This is the output of the ‘delayed tone follower’ block.

frequency of sufficient quality has been received for sufficient time, i.e. a cumulation of 40ms in

any 48ms, short tone bursts or breaks will be ignored. This output provides a logic “0” (Low)

It will respond when 40ms of good tone has been received within any 48ms window. The 48ms

is divided into 24 ‘packets’ of 2ms each (16Khz mode) or 15 ‘packets’ of 2.667ms each (12Khz

for a detected tone and a logic “1” (High) for N

mode). Each packet represents 32 cycles of SPM frequency. The window is a shifting window,

ie. the 48ms window is assessed every 2ms (16Khz mode) or 2.667ms (12Khz). If the

System: The logic input to select device operation to either 12kHz (logic “1” - High) or 16kHz

necessary number of good packets are consecutive, the output will respond in the minimum

(logic “0” - Low) SPM systems. This input has an internal 1MΩ pullup resistor (12kHz).

time of 40ms.

V

: Positive supply rail. A single, stable power supply is required. Critical levels and voltages

DD

· logic 0 represents ‘detect’ and logic 1 represents ‘not detect’.

OTONE detection. See Figure 7.

within the FX631 are dependant upon this supply. This pin should be decoupled to V

by a capacitor mounted close to the pin.

Note that if this device is ‘line’ powered, the resulting supply must be stable. See notes on

Microcircuit Protection from high and spurious line voltages.

SS

2, 3,

7, 9,

10, 11,

14,

15, 16,

22, 23

5, 6,

12

No internal connection, leave open circuit.

2

Application Information

External Components

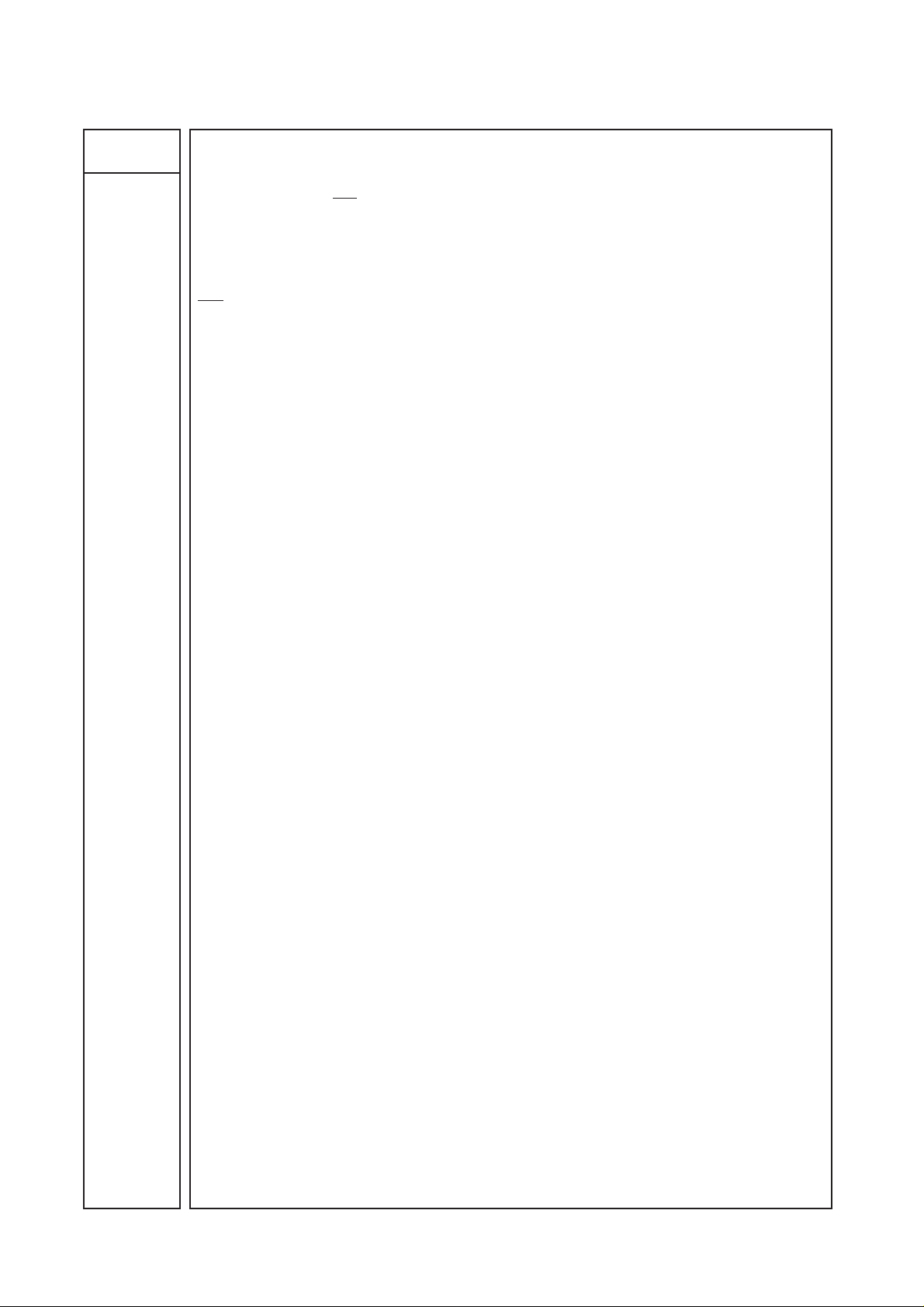

XTAL/CLOCK

X

For use with a Clock Pulse input

- Remove Xtal (X

- Connect Pin 1 to V

- Remove link (Pins 3/4)

- Input clock pulses to CLOCK IN

CLOCK IN

)

1

DD

1

CLOCK OUT

C

2

XTAL/CLOCK

XTAL

CLOCK IN

V

BIAS

V

V

DD

C

1

V

V

1

2

3

4

FX631DW

5

6

7

SS

8

V

16

15

14

13

12

11

10

9

SS

DD

SYSTEM

PACKET MODE OUTPUT

TONE FOLLOWER OUTPUT

AMP OUT

SIGNAL IN (-)

SIGNAL IN (+)

R

4

SS

R

1

C

3

R

2

C

R

3

4

Fig.2 Recommended External Components - Differential Input Mode

Component Value

R

1

R

2

R

3

R

4

C

1

C

2

C

3

C

4

X

1

R

FEEDBACK

R

IN (-)

R

IN (+)

R

BIAS

1.0µF ±20%

1.0µF ±20%

C

IN (-)

C

IN (+)

3.579545MHz

External Components

1. The values of the Input Amp gain components

illustrated are calculated using the Input Gain

Calculation Graphs (Figures 4 and 5).

Whilst calculating input gain components, for

correct operation, it is recommended that the

values of resistors R

than, or equal to, 33kΩ.

2. Refer to following pages for advice on Microcircuit

Protection from high and spurious line voltages.

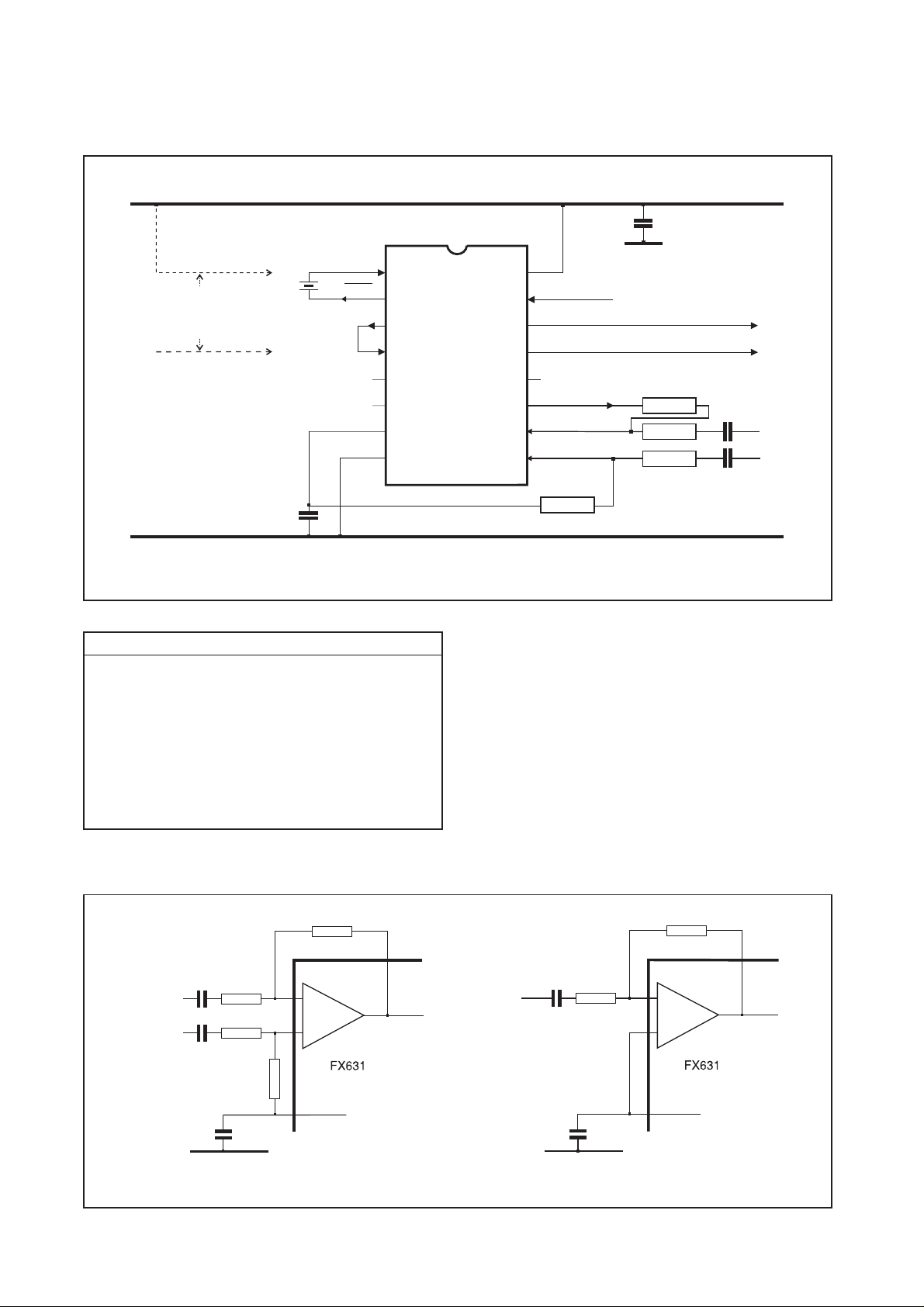

Differential Input Common Mode Input

INPUT AMP

Tip (a)

Ring (b)

-

+

and R4 are always greater

1

INPUT AMP

-

+

V

BIAS

V

SS

Fig.3 Example Input Configurations

V

BIAS

V

SS

3

Loading...

Loading...