Consumer Microcircuits Limited FX613P, FX613DW Datasheet

Publication D/613/3 December 1995

CML Semiconductor Products

FX613

PRODUCT INFORMATION

The FX613 is a wide-band, ‘N-Tone’, non-predictive

tone decoder to measure telephone system call progress

tones in PABX, Pay/Feature-Phone, Fax and Modem

systems.

Adhering to Must/Must-Not Decode limits and able to

measure inband frequencies in outband modulation, this

decoder measures the frequency of input signals in the

range 300Hz to 2,150Hz; the result of each

measurement is presented to a system µProcessor, as a

6-bit serial word.

The decode frequency range, which covers the

World's call progress application spectrum, is processed

internally as two bands: LO = 300Hz to 660Hz and HI =

900Hz to 2150Hz. Frequency measurement is achieved

by counting the number of cycles in a set time period

(LO = 39.47ms or HI = 13.16ms). Bad signal/level quality

or NOTONE results in a count-abort, timing-reset and no

output from the decoder.

Current frequency information is output for the

µProcessor using a Serial Data, Clock and Interrupt

interface.

Data from the FX613 should be processed by a

µProcessor whose algorithms are able to recognize the

frequency, sequence and/or cadence of input signals as

national call progress information; e.g.: ‘Dial’, ‘Busy’,

‘Number-Unobtainable’, ‘Ringing’ and automatic tones

employed by Fax, Modem systems. Software can be

simply configured to reject speech frequencies.

Due to its ‘N-Tone’, non-predictive decoding capability,

units employing the FX613 can be redeployed under a

new national standard by a simple software amendment.

Available in 16-pin plastic S.O.I.C. SMD and 14-pin

plastic DIL packages, this low-cost, mixed analogue/digital

microcircuit has a typical power requirement of less than

1mA at 3 volts and utilizes a telecom-system clock input

of 3.579545MHz to maintain frequency accuracy.

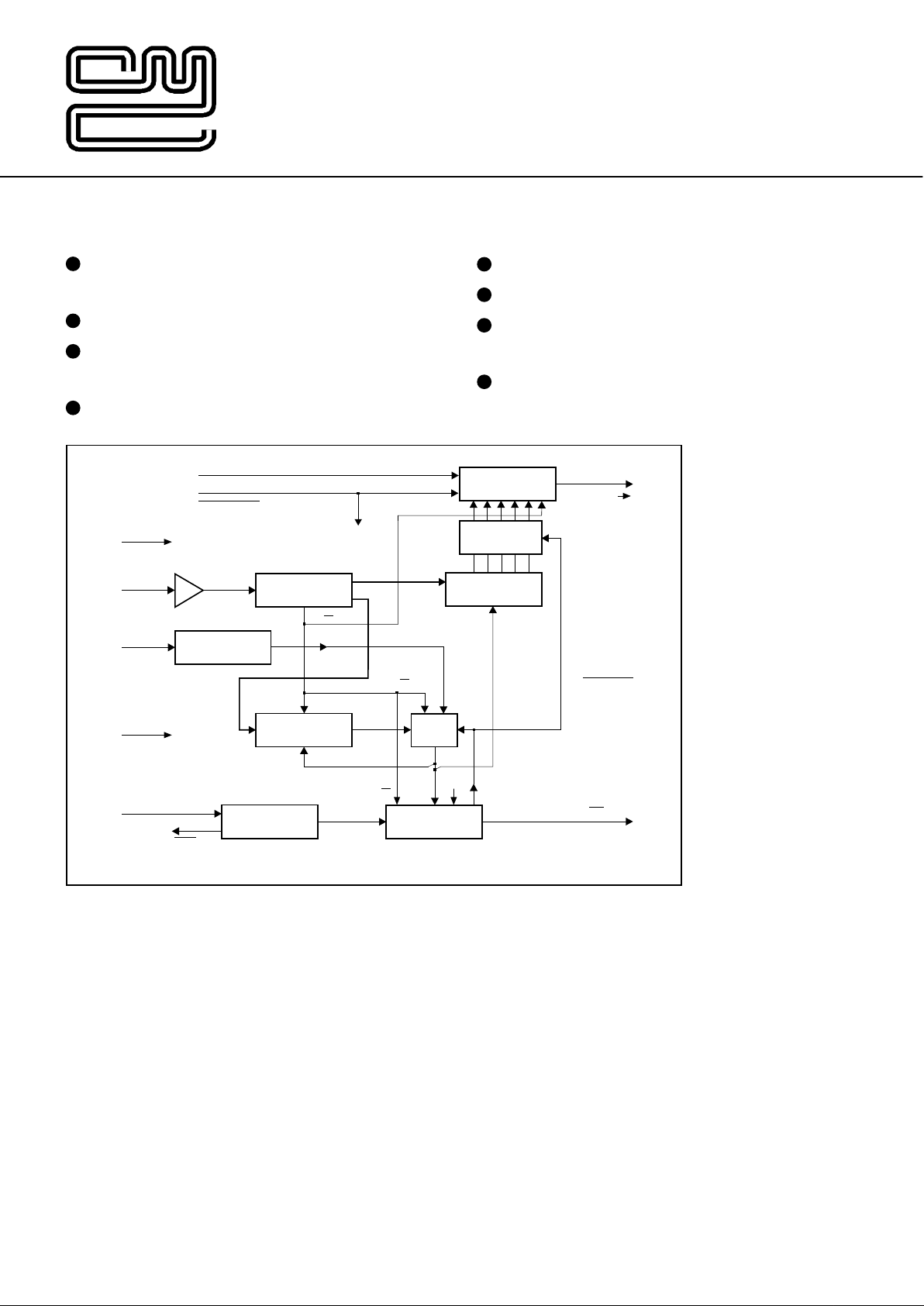

Fig.1 Functional Block Diagram

Brief Description

Universal Call Progress Decoder

CLOCK

GENERATOR

LOGIC

SERIAL CLOCK

SIGNAL IN

V

SS

V

DD

V

BIAS

LEVEL IN

DATA OUT

XTAL/CLOCK

3.579545MHz

TIME

CS

CS

GOOD/BAD

TIME

RESET

RESET

RESET

COUNT

DECODE

ON / OFF

f

f/4

f/4

IRQ

XTAL

CHIP SELECT

HI/LO

HI/LO

HI / LO BAND

FREQUENCY

COUNTER

LATCH

SERIAL OUTPUT

PORT (6-BITS)

TIMER

LO = 39.4ms

HI = 13.16ms

012345

SIGNAL QUALITY

ASSESSOR

LEVEL

DETECTOR

FILTER &

BAND SELECTOR

FX613

Features

Covers Worldwide Call Progress

Frequencies (300Hz to 2,150Hz)

3 Volt <1mA Requirement

Decodes Single or Modulated

T ones

Analogue In/Serial Data Out

Speech Discrimination Ability

µProcessor Compatible Outputs

Telephone/Telecoms, Radio and

Fax/Modem Applications

Mixed Analogue/Digital

Technology

2

FX613DW

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

FX613P

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Pin Number Function

Xtal/Clock: The input to the on-chip clock oscillator inverter. A 3.579545MHz Xtal or

externally derived telephone system clock (f

XTAL

) should be connected here.

Note - The operation of the FX613 without a suitable Xtal/Clock input may cause

device damage.

Xtal: The output of the on-chip clock oscillator inverter. See Figure 2.

No internal connection.

V

BIAS

: The internal circuitry bias line, held at VDD/2 this pin must be decoupled to VSS.

Level In: The input for level discrimination. This input is internally biased to V

BIAS

,

signals must be a.c. coupled. The audio signal must be fed to both this pin and the

Signal In pin. Correct level detection determines the operation of this device (see

Principles of Decoder Operation), however to disregard the amplitude of the input

levels the FX613 may be permanently enabled by pulling this pin to VDD and disabled

by pulling to VSS.

Signal In: The input for frequency discrimination and decoding. This input is internally

biased to V

BIAS

, signals must be a.c. coupled. The audio signal must be fed to both this

pin and the Level In pin.

No internal connection.

VSS: Negative supply rail. Signal ground.

No internal connection.

No internal connection.

IRQ: This Interrupt Request output from the FX613 is ‘wire-OR able’ allowing the

interrupt outputs of other peripherals to be combined and connected to the Interrupt

input of a µProcessor. This input has a low-impedance pulldown to V

SS

when active and

a high-impedance when inactive. An interrupt is produced on completion of a HI or LO

frequency measurement.

Serial Clock: The serial clock from the µProcessor. Data Out is clocked into the

µProcessor on the rising edge of the Serial Clock. See Data-Read Timing diagram.

Chip Select: A logic “0” at this input will select this device.

Data Out: The serial data output. Under the control of the Chip Select and Serial

Clock inputs, data should be read from this output in 6-bit blocks MSB (Bit-5) first.

If 8 serial clock pulses are applied, two additional logic “0s” will be output after Bit-0.

No internal connection.

VDD: Positive supply rail. A single, stable supply is required. Levels and voltages within

the FX613 are dependent upon this supply. This pin should be decoupled to VSS by a

capacitor located close to the FX613 pins.

3

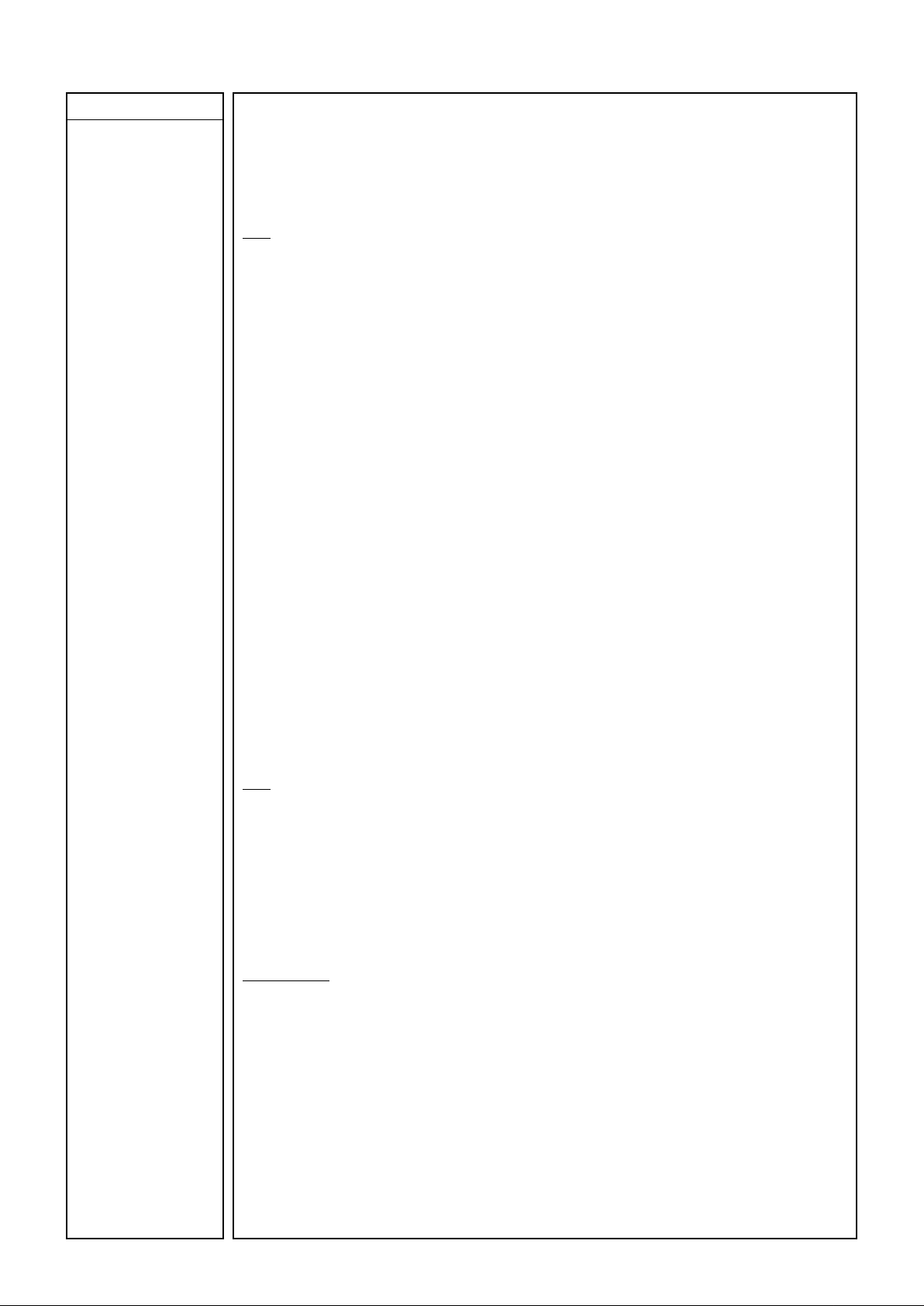

Application Information

V

DD

V

SS

V

SS

V

SS

C

1

C

4

C

2

C

3

R

1

V

BIAS

1

2

3

4

5

6

7

8

14

15

16

13

12

11

10

9

FX613DW

SERIAL CLOCK INPUT

DAT A OUT

LEVEL IN

SIGNAL IN

AUDIO SIGNAL

XTAL/CLOCK

V

DD

XTAL

IRQ

CHIP SELECT

C

5

C

6

R

2

X

1

1

2

V

SS

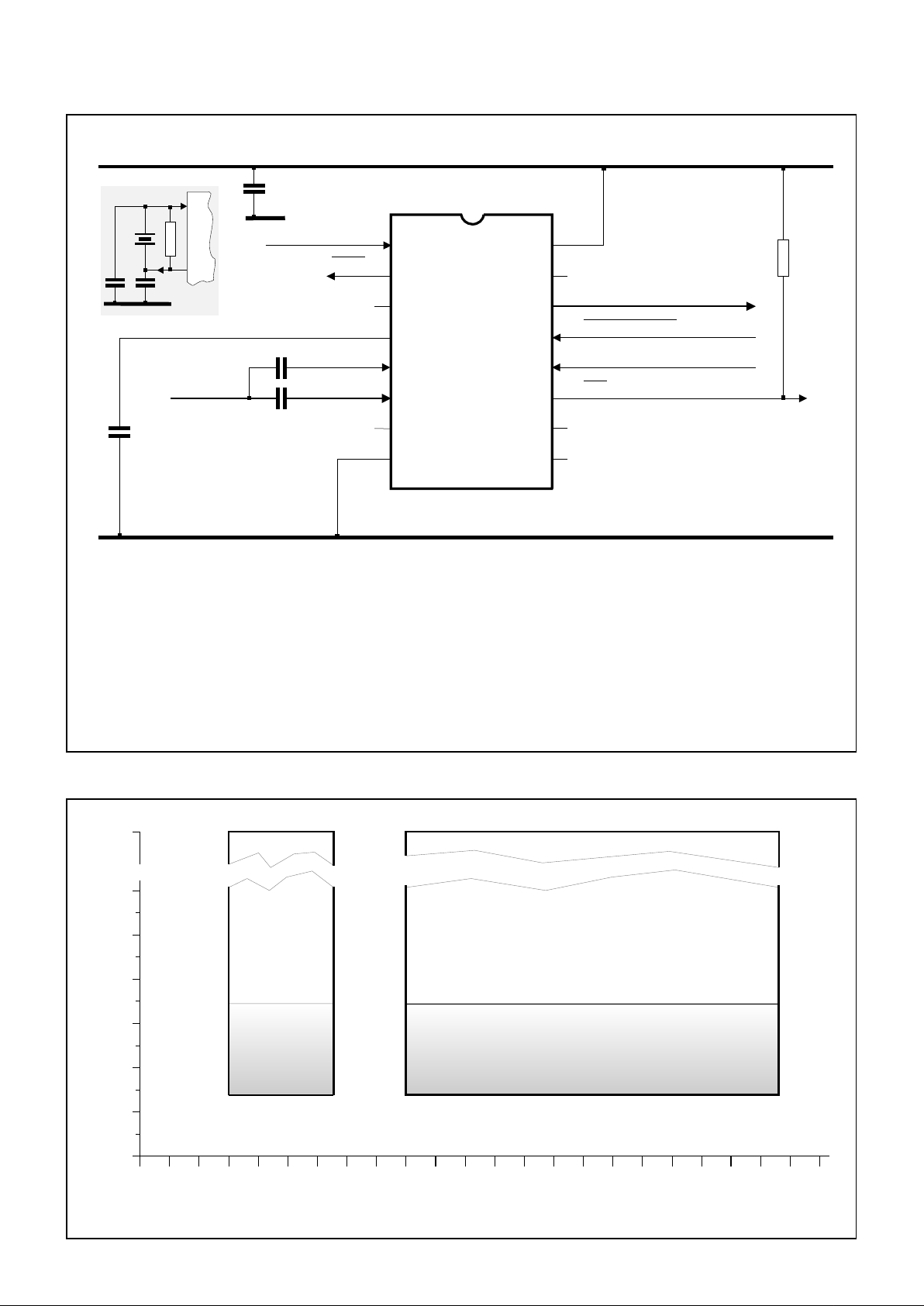

0

0

200 400 600 800 1000 1200 1400 1600 1800 2000 2200

-50

-40

-30

-20

-10

V

DD

775mVrms

Must

Decode

Level (dB)

Frequency (Hz)

Must-Not

Decode

Low Band

(LO)

High Band

(HI)

Fig.3 HI/LO Decode Bands

Fig.2 External Component Connections

Component Value

R

1

22.0kΩ

R

2

1.0MΩ

C

1

0.01µF

C

2

0.1µF

C

3

1.0µF

C

4

1.0µF

C

5

33.0pF

C

6

33.0pF

X

1

3.579545MHz

Tolerances: C = ± 20% R = ± 10%

Notes

(1) The Xtal/Clock input may be driven from the host telephone

system's 3.579545MHz clock; if a Xtal drive is required, the

configuration shown INSET is recommended.

(2) The audio signal should be input to both Signal In and Level In pins

via separate coupling capacitors. If it is wished to operate the

device with disregard to on-chip level thresholds and permanently

enable the FX613, the Level In pin should be held at VDD.

To disable the FX613 the Level In pin should be held at VSS. Level

thresholds are preset internally.

Loading...

Loading...