Consumer Microcircuits Limited FX589P, FX589D5 Datasheet

CML Semiconductor Products

PRODUCT INFORMATION

Low-Volta ge/High-Speed

FX589

GMSK Modem

Publication D/589/7 January 1998

Features

Full-Duplex Gaussian Minimum

Shift Keying (GMSK)

Operating from 3 Volts to 5.5 Volts

Data Rates 4kb/s to 64kb/s

Selectable BT (0.3 or 0.5)

Low-Current Analogue/Digital

Non-DSP Solution

Meets RCR STD-18

Tx ENABLE

Tx PS

Tx DAT A

XTAL/CLOCK

XTAL

ClkDIVA

ClkDIVB

BT

RxHold

PLLacq

RxDCacq

Rx PS

Rx SIGNAL IN

Rx FEEDBACK

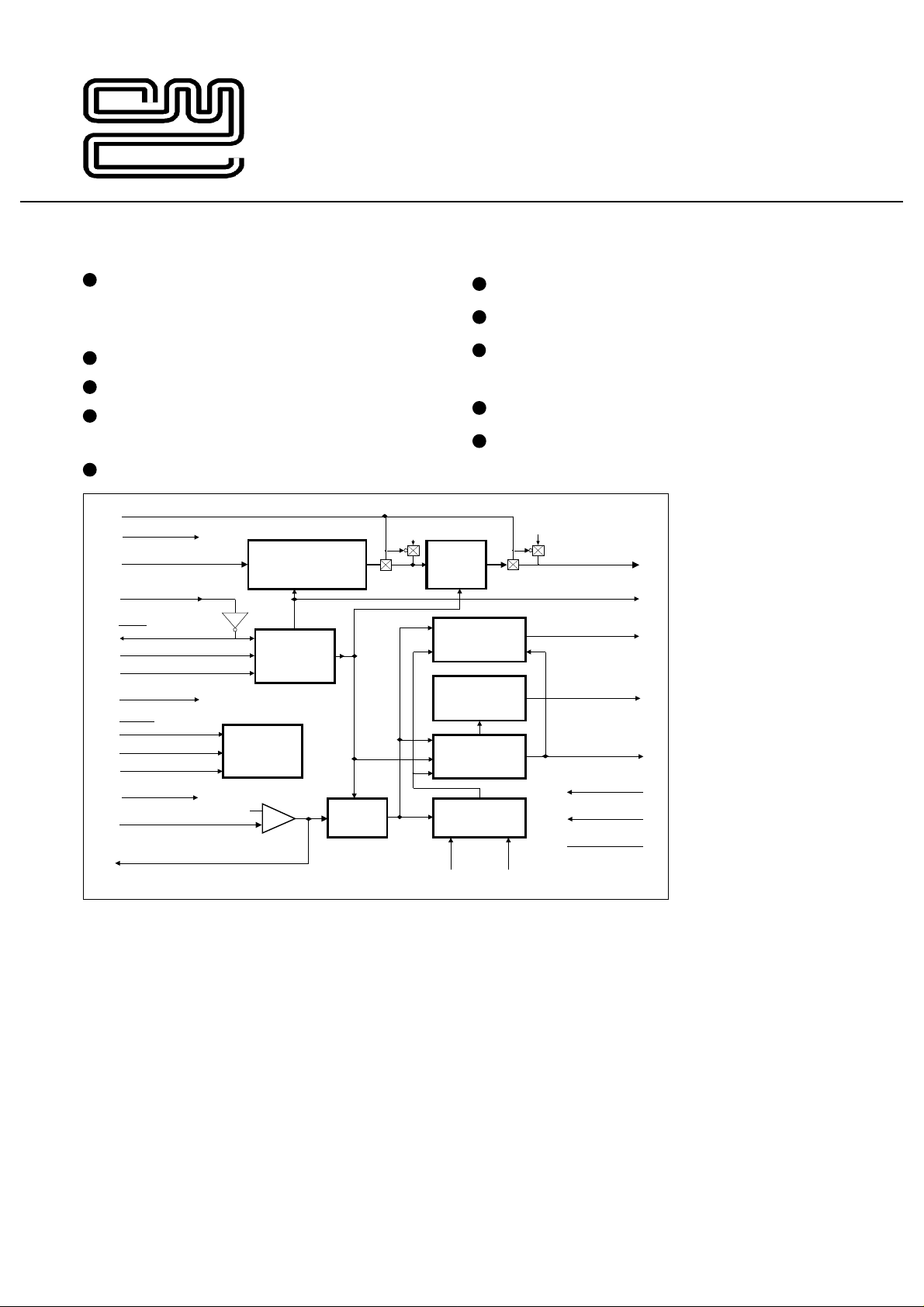

Fig.1 Functional Block Diagram

DATA RETIME

LEVEL SHIFT

DIVIDER

Rx CIRCUIT

CONTROL

V

BIAS

+

-

&

CLOCK

FILTER

Rx

V

BIAS

FILTER

DOC1

Applications

Wireless LAN/Modems

Handy Data Terminals

Low-Power Wireless Data Link

for PCs, Laptops and Printers

Point-Of-Sale Terminals

Wireless Bar-Code Readers

and Stock Controllers

V

Tx

Rx DATA

EXTRACT

Rx S/N

DETECTION

Rx CLOCK

EXTRACT

Rx LEVEL

MEASURE

DOC2

BIAS

Tx OUT

Tx CLOCK

Rx DAT A

Rx S/N

Rx CLOCK

V

DD

V

SS

V

BIAS

FX589

Brief Description

The FX589 is a single-chip modem employing

Gaussian Minimum Shift Keying (GMSK) modulation.

Data rates of 4kb/s to 64kb/s and the choice of BT

to 0.3 or 0.5 are pin-programmable functions to suit

radio data channel bandwidth requirements.

The Rx and Tx digital data interfaces are bit-serial

and synchronised to Rx and Tx data clocks generated

by the modem. Separate Rx and Tx Powersave/Enable

inputs allow for full- or half-duplex operation.

Rx input levels can be set by a suitable ac and dc

level adjusting circuit built, with external components,

around an on-chip Rx input amplifier.

Acquisition, lock and hold of Rx data signals is made

easier and faster by the use of Rx Control Inputs to clamp,

detect and/or hold input data levels and can be set by the

system µProcessor as required.

Indication is available, from the Rx S/N output, as to the

quality of the received signal.

The FX589 design features a low-current analogue/digital

ASIC process offering significantly lower current

consumption than DSP technology. For data rates up to

32kb/s the FX589 draws typically 1.5mA at 3.0 volts V

for data rates up to 64kb/s at 5.0 volts, typically 4.0mA.

This low-power CMOS microcircuit is available in both

24-pin plastic DIL and Small Outline (SOIC and SSOP)

packages.

1

DD

and

Pin Number Function

FX589DW

FX589D5

FX589P

1

2

Xtal: The output of the on-chip clock oscillator.

Xtal/Clock: The input to the on-chip Xtal oscillator. A Xtal, or externally derived clock (f

XTAL

) pulse

input should be connected here. If an externally generated clock is to be used, it should be

connected to this pin and the Xtal pin left unconnected.

Note that operation of the FX589 without a suitable Xtal or clock input may cause device damage.

3

ClkDivA:

Two logic level inputs that control the internal clock divider and hence the transmit and

receive data rate. See Table 1.

4

5

ClkDivB:

Rx Hold: A logic “0” applied to this input will ‘freeze’ the Clock Extraction and Level Measurement

circuits unless they are in ‘acquire’ mode.

6

RXDCacq: A logic “1” applied to this input will set the Rx Level Measurement circuitry to the

‘acquire’ mode.

7

8

9

10

11

PLLacq: A logic “1” applied to this input will set the Rx Clock Extraction circuitry to ‘acquire’ mode

(see Table 2).

Rx PS: A logic “1” applied to this input will powersave all receive circuits except for “Rx Clock”

output (which will continue at the set bit-rate) and cause the “Rx Data” and “Rx S/N” outputs to go

to a logic “0”.

V

: The internal circuitry bias line, held at VDD/2, this pin must be decoupled to VSS by a

BIAS

capacitor mounted close to the pin.

Rx Feedback: The output of the Rx Input Amplifier/the input to the Rx Filter.

Rx Signal In: The input to Rx Input Amplifier.

12

V

: Negative supply rail. Signal ground.

SS

2

Pin Number Function

FX589DW

FX589D5

FX589P

13

14

15

16

17

18

Doc1:

Connections to the Rx Level Measurement Circuitry. A capacitor should be connected

from each pin to V

. See Figure 2.

SS

Doc2:

BT: A logic level to select the modem ‘BT’ (the ratio of the Tx Filter's -3dB frequency to the Bit-

Rate). A logic “1” sets the modem to a BT of 0.5, a logic “0” to a BT of 0.3.

Tx Out: The Tx signal output from the FX589 GMSK Modem.

Tx Enable: A logic “1” applied to this input enables the transmit data path through the Tx Filter to

the “Tx Out” pin. A logic “0” will put the “Tx Out” pin to V

via a high impedance.

BIAS

Tx PS: A logic “1” applied to this input will powersave all transmit circuits except for the “Tx

Clock”.

19

20

21

22

23

24

Tx Data: The logic level input for the data to be transmitted. This data should be synchronous

with the “Tx Clock”.

Rx Data: A logic level output carrying the received data, synchronous with the “Rx Clock”.

Rx Clock: A logic level clock output at the received data bit-rate.

Tx Clock: A logic level clock output at the transmit-data rate.

Rx S/N: A logic level output which may be used as an indication of the quality of the received

signal.

V

: Positive supply rail. A single, stable power supply is required. Levels and voltages within this

DD

modem are dependent upon this supply. This pin should be decoupled to V

by a capacitor

SS

mounted close to the pin.

3

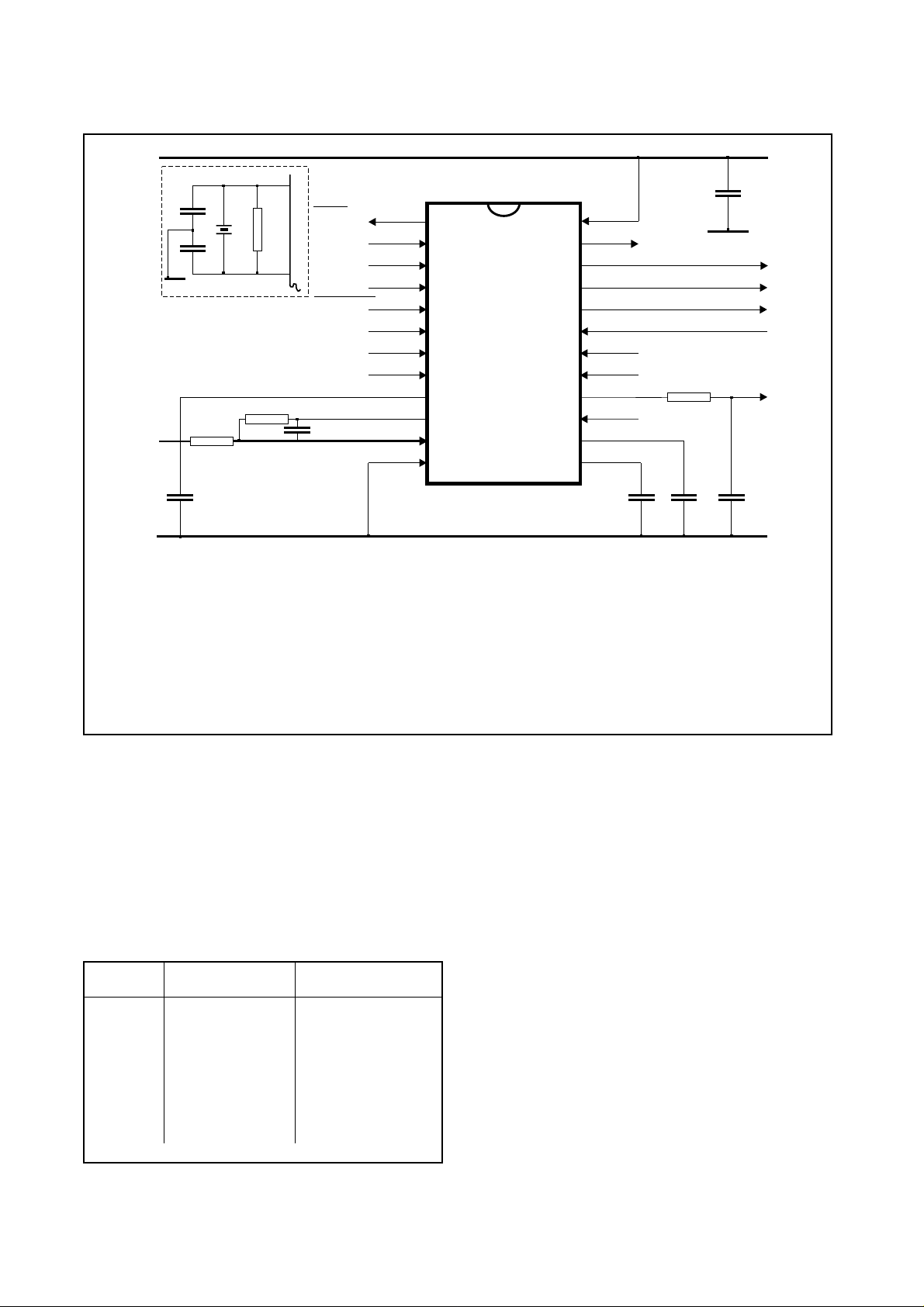

Application Information

XTAL

1

C

3

X

1

R

2

C

2

V

SS

R

C

XTAL/CLOCK

3

5

2

R

4

C

6

XTAL

XTAL/CLOCK

ClkDivA

ClkDivB

Rx HOLD

RxDCacq

PLLacq

Rx PS

V

BIAS

Rx FEEDBACK

Rx SIGNAL IN

V

V

DD

C

4

V

1

2

3

4

5

6

FX589P

7

8

9

10

11

12

SS

V

SS

24

23

22

21

20

19

18

17

16

15

14

13

DD

Rx S/N

Tx CLOCK

Rx CLOCK

Rx DATA

Tx DATA

Tx PS

Tx ENABLE

Tx OUT

BT

Doc2

Doc1

C

7

V

SS

R

1

C

C

8

1

External Components

Component Value Tolerance

R

1

R

2

R

3

R

4

C

1

C

2

Note 1 ±5%

1.0MΩ ±10%

Note 2 ±10%

100kΩ ±10%

Note 1 ±10%

Note 5

Fig.2 Recommended External Components

Notes

1. The RC network formed by R

between the Tx Out pin and the input to the

and C1 is required

1

modulator. This network, which can form part of any

dc level shifting and gain adjustment circuitry, forms

an important part of the transmit signal filtering.

The ground connection to the capacitor C

positioned to give maximum attenuation of high-

should be

1

frequency noise into the modulator.

The component values should be chosen so that the

product of the resistance (Ohms) and the capacitance

(Farads) is: BT of 0.3 = 0.34/bit rate (bits/second)

Data Rate BT = 0.3 BT = 0.5

(b/s) R1 (kΩ) C1 (pF) R1 (kΩ) C1 (pF)

4000 120 680 120 470

4800 100 680 100 470

8000 91 470 120 220

9600 91 390 47 470

16000 47 470 91 150

19200 100 180 91 120

32000 47 220 47 150

38400* 47 180 47 120

64000* 56 100 51 68

* VDD >= 4.5V

BT of 0.5 = 0.22/bit rate (bits/second).

Note that in all cases, the value of R1 should be not less

than 47.0kΩ and that the calculated value of C

calculated parasitic (circuit) capacitances.

includes

1

C

3

C

4

C

5

C

6

C

7

C

8

X

1

Note 5

100nF ±20%

1.0µF ±20%

22.0pF ±20%

Note 4

Note 4

Note 3

2. R3, R4 and C6 form the gain components for the Rx

Input signal. R

should be chosen as required by the

3

signal input level.

3. The FX589 can operate correctly with Xtal/Clock

frequencies of 1.0MHz to 8.2MHz (V

1.0MHz to 5.0MHz (V

= 3.0V); see Table 1 for

DD

= 5.0V) and

DD

examples. Operation of this device without a Xtal or

Clock input may cause device damage.

4. C

and C8 should both be 15.0nF for a data rate of

7

8kb/s, and inversely proportional to the data rate for

other data rates, e.g. 30.0nF at 4kb/s, 1.8nF at

64kb/s.

5. The value chosen for C

and C3 (including stray

2

capacitances) should be suitable for the applied V

and the frequency of X1.

As a guide: C

= C3 = 33.0pF at 1.0MHz falling to

2

18pF at the maximum frequency.

At 3 volts, C

The equivalent series resistance of X

= C3 = 33.0pF falling to 18pF at 5.0MHz.

2

should be less

1

than 2.0kΩ falling to 150Ω at the maximum frequency.

Stray capacitance on the Xtal/clock circuit pins must

be minimised.

4

DD

Application Information ......

Rx FREQUENCY

DISCRIMINATOR

SIGNAL AND

DC LEVEL

ADJUSTMENT

Rx SIGNAL IN Rx FEEDBACK

CIRCUITS

µCONTROLLER

or UART

RxD

RxC

TxD

TxC

Rx DATA

Rx CLOCK

Tx DATA

Tx CLOCK

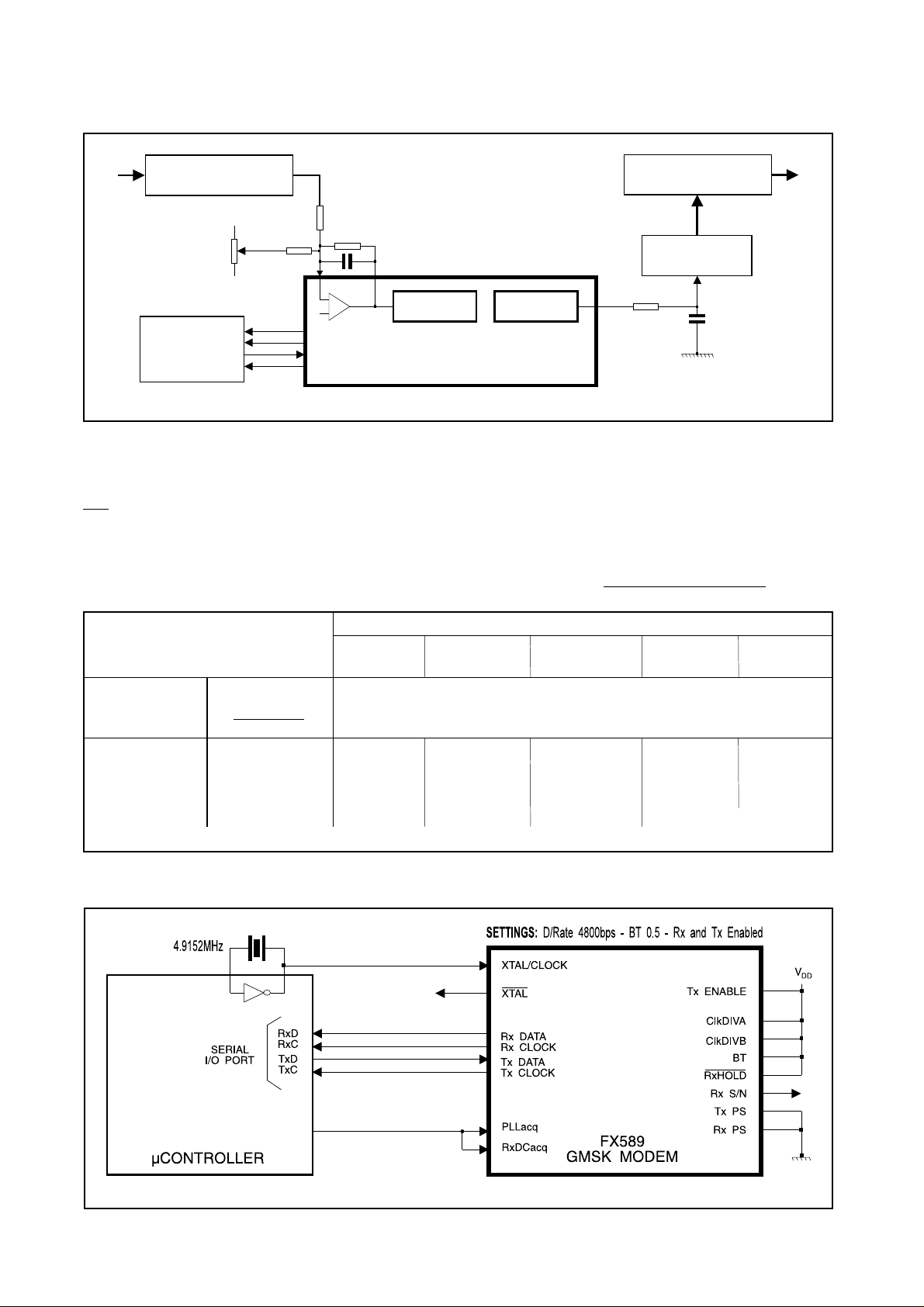

Fig.3 External Signal Paths

Clock Oscillator and Dividers

The Tx and (nominal) Rx data rates are determined

by division of the frequency present at the Xtal pin,

which may be generated by the on-chip Xtal oscillator

or be derived from an external source. Any Xtal/clock

frequency in the range 1.0MHz to 5.0MHz (V

or 1.0MHz to 8.2MHz (V

= 5.0V) may be employed,

DD

depending upon the desired data rate.

= 3.0V)

DD

FREQUENCY

MODULATOR

SIGNAL AND

DC LEVEL

ADJUSTMENT

Rx

Tx

CIRCUITS

Tx OUT

FX589

GMSK MODEM

A division ratio to facilitate data-rate setting is

controlled by the logic level inputs on the ClkDivA/B

pins, and is shown in Table 1 (below) - together with

examples of how various ‘standard’ data-rates may be

derived from common µP or Xtal frequencies.

Data Rate = Xtal/Clock Frequency

Division Ratio (ClkDivA/B)

Note the device operation is not guaranteed

above 64,000 bits/s or below 4,000 bits/s at

the relevant supply voltage

8.192 4.9152 4.096 2.4576 2.048

Xtal/Clock Frequency (MHz)

[12.288/3] [12.288/5] [6.144/3]

Inputs Division Ratio:

ClkDiv ClkDiv Xtal Freq Data Rate (b/s)

A B Data Rate

0 0 128 64000* 38400* 32000 19200 16000

0 1 256 32000 19200 16000 9600 8000

1 0 512 16000 9600 8000 4800 4000

1 1 1024 8000 4800 4000

Table 1 Clock/Data Rates

* VDD >= 4.5V

Fig.4 Minimum µController System Connections

5

Application Information ......

Rx Signal Path Description

The function of the Rx circuitry is to:

1. Set the incoming signal to a usable level.

2. Clean the signal by filtering.

3. Provide dc level thresholds for clock and data

extraction.

4. Provide clock timing information for data

extraction and external circuits.

5. Provide Rx data in a binary form.

6. Assess signal quality and provide Signal-to-Noise

information.

The output of the radio receiver's Frequency

Discriminator should be fed to the FX589's Rx Filter via

a suitable gain and dc level adjusting circuit. This gain

circuit can be built, with external components, around

the on-chip Rx Input Amplifier, with the gain set so that

the signal level at the Rx Feedback pin is nominally 1

Volt peak-to-peak (for V

V

when receiving a continuous “1111000011110... ”

BIAS

data pattern.

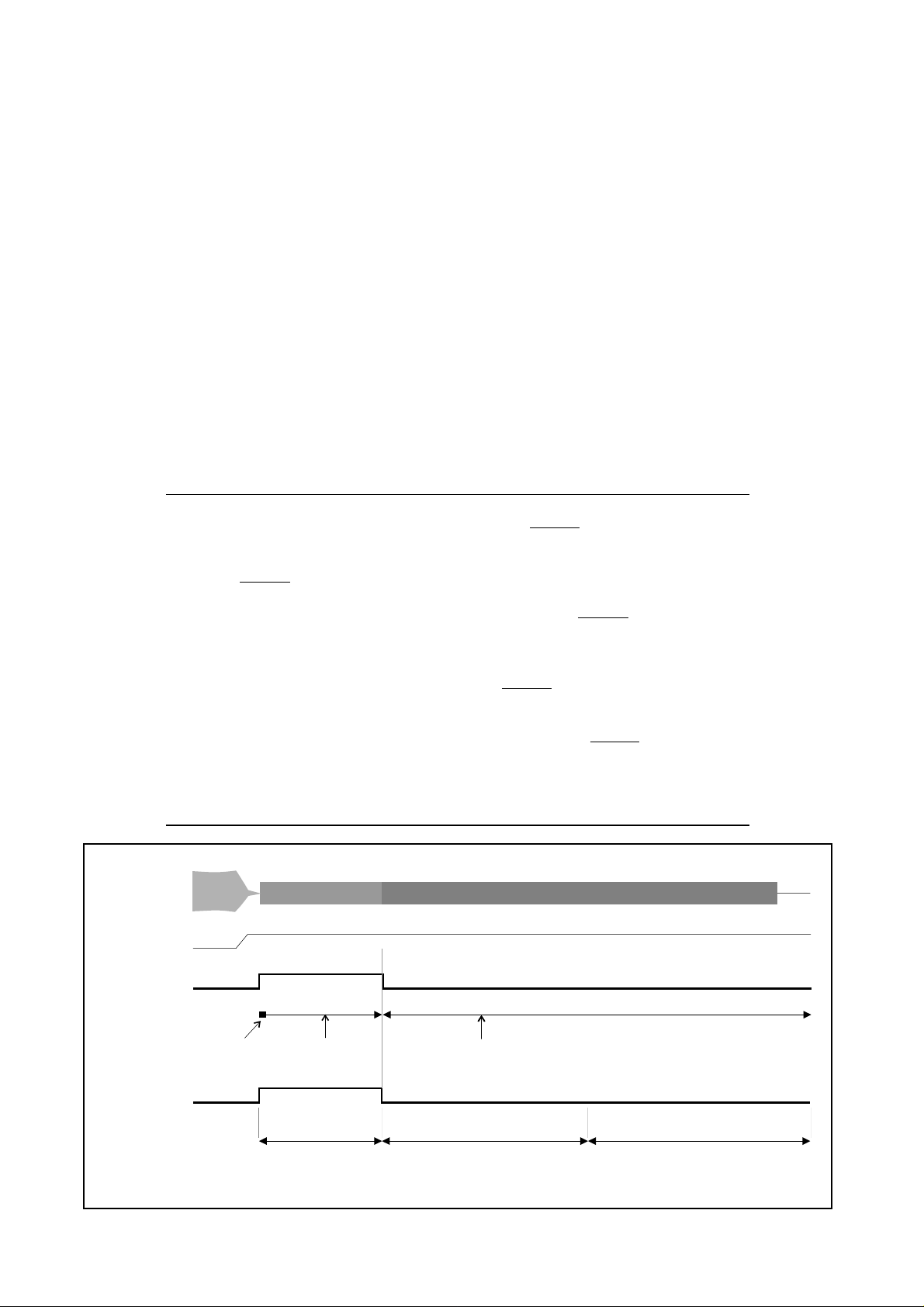

Rx Circuit Control Modes

The operating characteristics of the Rx Level

Measurement and Clock Extraction circuits are

controlled, as shown in Table 2, by logic level inputs

applied to the ‘PLLacq,’ ‘Rx Hold’ and ‘RxDCacq’ pins to

suit a particular application, or to cope with changing

reception conditions.

With reference to Figure 5, the Rx Mode Control

diagram: In general, a data transmission will begin with a

preamble of, for example, “1100110011001100,” to allow

the receive modem to establish timing -and level-lock- as

quickly as possible. After the Rx carrier has been

detected, and during the time that the preamble is

expected, the ‘RxDCacq’ and ‘PLLacq’ inputs should be

switched from a logic “0 to 1” so that the Level Measuring

and Clock Extraction modes are operated and

sequenced as shown.

= 5.0 V) centred around

DD

Positive going signal excursions at Rx Feedback

pin will produce a logic “0” at the Rx Data Output.

Negative going excursions will produce a logic “1.”

The received signal is fed through the lowpass Rx

Filter, which has a -3dB corner frequency of 0.56 times

the data bit-rate, before being applied to the Level

Measure and Clock and Data extraction blocks.

The Level Measuring block consists of two voltage

detectors. One of which measures the amplitude of the

‘positive’ parts of the received signal; the other

measures the amplitude of the ‘negative’ portions.

External capacitors are used by these detectors, via

the Doc 1/2 pins, to form voltage- ‘hold’ or ‘integrator’

circuits. Results of the two measurements are then

processed to establish the optimum dc level decisionthresholds for the Clock and Data extraction,

depending upon the Rx signal amplitude, BT and any

dc offset present.

The ‘Rx Hold’ input should normally be held at a logic

“1” while data is being received, but may be driven to a

logic “0” to freeze the Level Measuring and Clock

Extraction circuits during a fade. If the fade lasts for less

than 200 bit periods, normal operation can be resumed

by returning the ‘Rx Hold’ input to a logic “1” at the end of

the fade. For longer fades, it may be better to reset the

Level Measuring circuits by placing the ‘RxDCacq’ to a

logic “1” for 10 to 20 bit periods.

‘Rx Hold’ has no effect on the Level Measuring

circuits while ‘RxDCacq’ is at a logic “1”, and has no

effect on the PLL while ‘PLLacq’ is at a logic “1”.

A logic “0” on ‘Rx Hold’ does not disable the ‘Rx

Clock’ output, and the Rx Data Extraction and S/N

Detector circuits will continue to operate.

Rx SIGNAL

INPUT

Rx CAR DET

(RSSI) INPUT

RxDCacq

Rx LEVEL

MEASURE

MODE

PLLacq

CLOCK

EXTRACTION

CCT MODE

’CLAMP’

’FAST PEAK

Fig.5 Rx Mode Control Diagram

PREAMBLE

DETECT’

’ACQUIRE’

’AVERAGI N G PEAK

DETECT’

30 BITS

’MEDIUM BW’

6

DAT A

’NARROW BW’

Loading...

Loading...