Consumer Microcircuits Limited FX469LG, FX469J, FX469DW, FX469PG, FX469LS Datasheet

1

Features

Selectable Data Rates

1200, 2400 and 4800 Baud

Full-Duplex FFSK

Rx and Tx Bandpass Filters

Clock Recovery and Carrier

Detect Facilities

Rx and Tx Enable Functions

Publication D/469/6 April 1998

Pin Selected Xtal/Clock Inputs

1.008MHz or 4.032MHz

Radio and General Applications

Data-Over-Radio

PMR and Cellular Signalling

Portable Data Terminals

Personal/Cordless Telephone

CML Semiconductor Products

PRODUCT INFORMATION

FX469

Brief DescriptionBrief Description

Brief DescriptionBrief Description

Brief Description

Rx, Tx and Carrier Detect paths each contain a

bandpass filter to ensure the provision of optimum

signal conditions both in the modem and for the Tx

modulation circuitry.

The FX469 demonstrates a high sensitivity and

good bit-error-rate under adverse signal conditions;

the carrier detect time constant is set by an external

capacitor, whose value should be arranged as

required to further enhance this product's performance

in high noise environments.

This low-power device requires few external

components and is available in small outline plastic

(S.O.I.C) and cerdip DIL packages.

The FX469 is a single-chip CMOS LSI circuit which

operates as a full-duplex pin-selectable 1200, 2400 or

4800 baud FFSK Modem. The mark and space

frequencies are 1200/1800, 1200/2400 and 2400/4800

Hz respectively. Tone frequencies are phase

continuous; transitions occur at the zero crossing point.

Employing a common Xtal oscillator with a choice of

two clock frequencies (1.008MHz or 4.032MHz) to

provide baud-rate, transmit frequencies, and Rx and Tx

synchronization, the transmitter and receiver operate

entirely independently including individual section

powersave functions.

The FX469 includes on chip circuitry for Carrier Detect

and Rx Clock recovery, both of which are made

available as output pins.

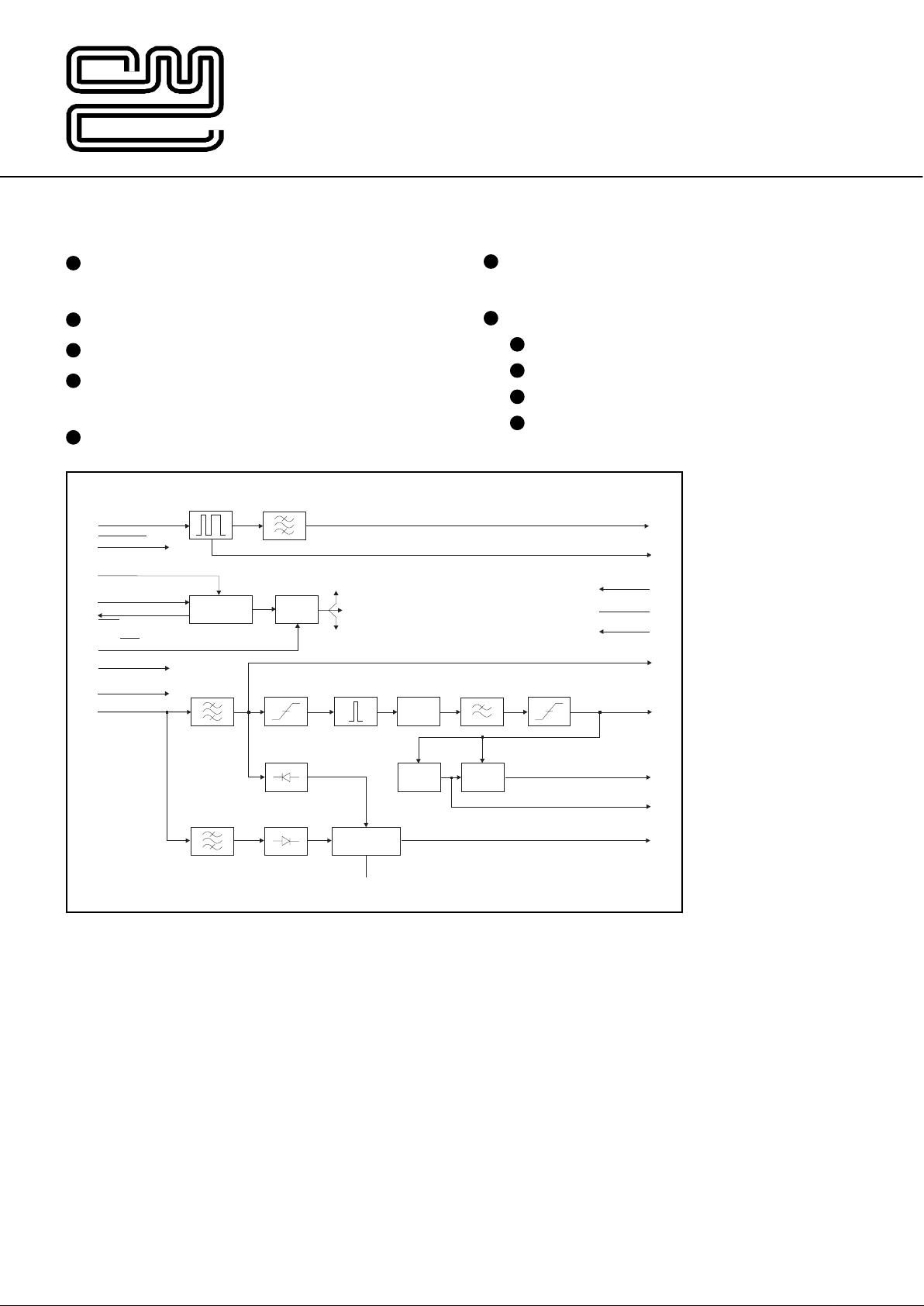

Fig.1 Functional Block Diagram

CLOCK

OSCILLATOR

DIVIDER

DATA

LATCH

DIGITAL

PLL

RECTIFIER

S/N

COMPARATOR

NOISEFILTER

RECTIFIER

RxFILTER

RxENABLE

4800BAUDSELECT

DATA

FILTER

DIGITAL

FILTER

LIMITER LIMITER

RETRIGGERABLE

MONOSTABLE

TxGENERATOR

XTAL/CLOCK

CLOCKRATE

TxDATAI/P

RxSIGNALI/P

TxSIGNALO/P

UNCLOCKED

DATAO/P

CLOCKED

DATAO/P

RxSYNCO/P

BANDPASSO/P

CARRIERDETECTO/P

CARRIERDETECTTIMECONSTANT

TxSYNCO/P

TxFILTER

XTAL

f

..n

V

DD

V

SS

V

BIAS

1200/2400BAUDSELECT

TxENABLE

FX469

1200/2400/4800 Baud

FFSK Modem

2

Pin Number Function

DW

1

2

3

4

5

6

7

8

9

10

Xtal/Clock : The input to the on-chip inverter, for use with either a 1.008MHz or a 4.032MHz

Xtal or external clock. Clock frequency selection is by the “Clock Rate” input pin. The

selection of this frequency will affect the operational Data Rate of this device. Refer to Baud

Selection information on the next page. Operation of any CML microcircuit without a Xtal or

clock input may cause device damage. To minimise damage in the event of a Xtal/drive

failure. it is recommended that the power rail (VDD) is fitted with a current limiting device

(resistor or fast-reaction fuse).

XtalN : Output of the on-chip inverter.

Tx Sync O/P : A squarewave, produced on-chip, to synchronize the input of logic data and

transmission of the FFSK signal (See Figure 4).

Tx Signal O/P : When the transmitter is enabled, this pin outputs the (140-step pseudo

sinewave) FFSK signal (See Figure 4).

With the transmitter disabled, this output is set to a high-impedance state.

Tx Data I/P : Serial logic data to be transmitted is input to this pin.

Tx EnableN : A logic ‘0’ will enable the transmitter (See Figure 4). A logic ‘1’ at this input will

put the transmitter into powersave whilst forcing “Tx Sync Out” to a logic ‘1’ and “Tx Signal

Out” to a high-impedance state. This pin is internally pulled to VDD.

Bandpass O/P : The output of the Rx Bandpass Filter. This output impedance is typically

10kW and may require buffering prior to use.

Rx Enable : The control of the Rx function. The control of other outputs is given below.

Rx Enable = Rx Function Clock Data O/P Carrier Detect Rx Sync Out

“1” = Enabled Enabled Enabled Enabled

“0” = Powersave “0” “0” 1” or “0”

V

BIAS

: The output of the on-chip analogue bias circuitry. Held internally at VDD/2, this pin

should be decoupled to VSS by a capacitor (C2). (See Figure 2.

This bias voltage is maintained under all powersave conditions.

VSS: Negative supply rail (GND).

J/P6

1

2

3

5

6

7

8

9

10

11

LG/LS

1

2

3

5

7

8

9

10

11

12

FX469

3

Pin Number Function

DW

11

12

13

14

15

16

17

18

19

20

Unclocked Data O/P: The recovered asynchronous serial data output from the receiver.

Clocked Data O/P: The recovered synchronous serial data output from the receiver.

Data is latched out by the recovered clock, available at the “Rx Sync O/P,” (See Figure 5).

Carrier Detect O/P: When an FFSK signal is being received this output is a logic ‘1.’

Rx Signal I/P: The FFSK signal input for the receiver. This input should be coupled via a

capacitor, C3.

Rx Sync O/P: A flywheel squarewave output. This clock will synchronize to incoming Rx

FFSK data (See Figure 5).

1200/2400 Baud Select: A logic ‘1’ on this pin selects the 1200 baud option.

Tone frequencies are: one cycle of 1200Hz represents a logic ‘1,’ one-and-a-half cycles of

1800Hz represents a logic ‘0.’ A logic ‘0’ on this pin selects the 2400 baud option.

Tone frequencies are: one-half cycle of 1200Hz represents a logic ‘1,’ one cycle of 2400Hz

represents a logic ‘0.’ This function is also used, in part, to select the 4800 baud option. This

pin has an internal 1MW pullup resistor.

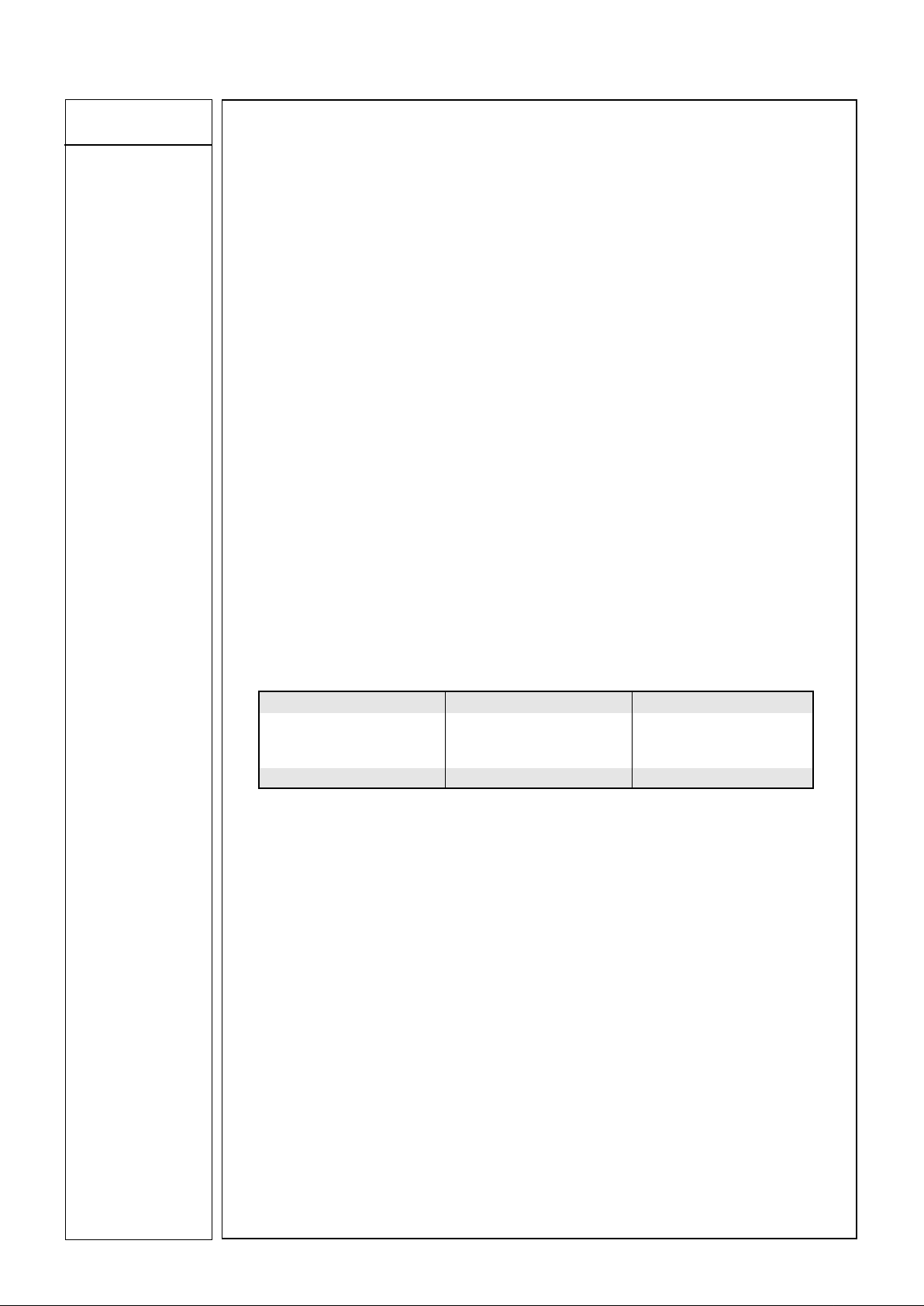

Operational Data Rate Configurations are illustrated in the table below.

Xtal/Clock Frequency 1.008MHz 4.032MHz

Clock Rate pin 0 0 1 1 1

1200/2400 Select pin 1 0 1 0 0

4800 Select pin 0 0 0 0 1

Baud Rate 1200 2400 1200 2400 4800

4800 Baud Select: A logic ‘1’ on this pin combined with a logic ‘0’ on the 1200/2400 Baud

Select pin will select the 4800 option (1MW pulldown resistor).

Tone frequencies are: one-half cycle of 2400Hz represents a logic ‘1,’ one cycle of 4800Hz

represents a logic ‘0.’ This state can only be achieved using a 4.032MHz Xtal input.

Clock Rate: A logic input to select and allow the use of either a 1.008MHz or 4.032MHz

Xtal/clock. Logic ‘1’ = 4.032MHz, logic ‘0’ = 1.008MHz. This input has an internal pulldown

resistor (1.008MHz).

Carrier Detect Time Constant : Part of the carrier detect integration function. The value of

C4 connected to this pin will affect the carrier detect response time and hence noise

performance (See Figure 2, Note 3).

VDD: Positive supply rail. A single 5-volt supply is required.

No internal connection, do not use.

J/P6

12

13

14

15

17

16

18

19

20

22

4,

21

LG/LS

13

14

15

16

18

19

20

21

22

24

4, 6, 17,

23

FX469

Loading...

Loading...