Consumer Microcircuits Limited FX029J, FX029DW, FX029D5 Datasheet

1

PRODUCT INFORMATION

CML Semiconductor Products

FX029

Features

2 Digitally Controlled Amplifiers

Gain/Attenuation Range of ±48dB

+ Output Mute, in 2dB Steps

Gain/Attenuation Levels Set by

Serial Interface

Separate Fixed-Gain Uncommitted

Amplifier

5 Volt Low-P ower Operation

Applications

Cellular and PMR

Communications Systems

Automatic and Manual Test

Equipment

Remote Gain Adjustments

T elephone Audio Settings

Medical Equipment

Audio and Data Gain Setting

Applications

Brief Description

The FX029 single-chip Dual Digitally Controlled

Amplifier Array can replace manual audio-level

controls in most electronic applications including radio

and line communications systems.

The FX029 comprises two digitally controlled gain

and attenuation stages, with each stage having 48

distinct gain steps (range; between -48dB and +48dB

in 2dB steps) plus a MUTE state to powersave the

addressed section. Minimum current drain results from

muting both sections.

Both gain stages have selectable inputs. This

switching allows for selection of three different input

signals to stage 1 and two to stage 2.

Dual Digitally Controlled

Amplifier Array

Publication D/029/3 April 1997

Provisional Issue

FX029

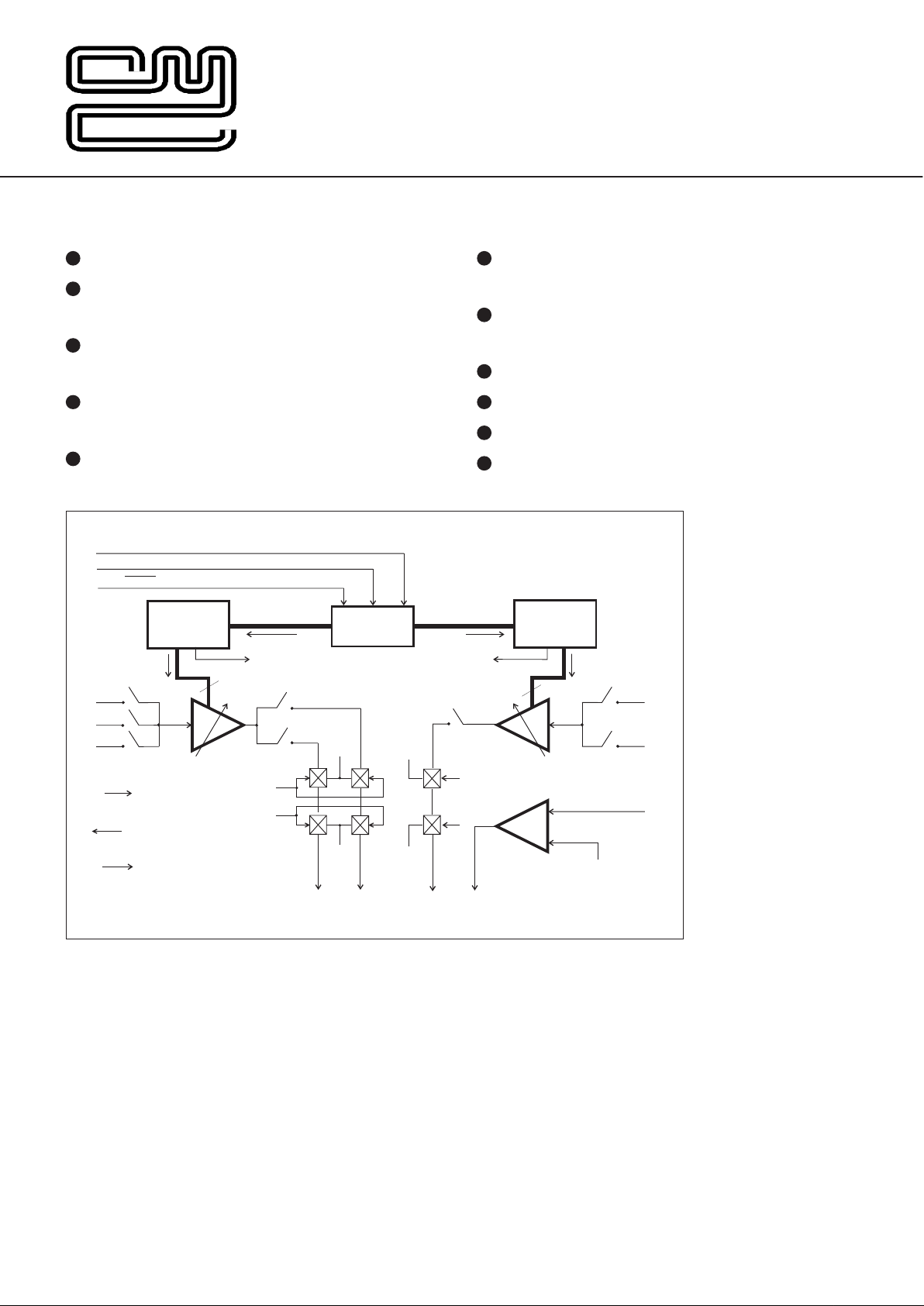

Fig.1 Functional Block Diagram

Stage 1 also provides output switching.

In addition to the two digitally controlled gain stages,

there is a general purpose, uncommitted inverting

amplifier; the gain of this particular amplifier is

component controlled externally using negative

feedback.

Control of each gain stage section is accomplished

through the serial interface. All switching is

accomplished using controlled rise and fall times,

thereby ensuring no annoying transients (clicks or

pops).

The FX029 requires a single 5 volt supply and is

available in compact cerdip and small outline packages.

3

21B1A

V

DD

V

BIAS

V

SS

Stage 1

Stage 1 Inputs

Stage 2 Inputs

Stage 3 Input

OUTPUTS

Control 1

Control 1

Gain

V

BIAS

V

BIAS

V

SS

V

SS

Gain

SERIAL CLOCK

SERIAL DATA

Control 2

Control 2

V

BIAS

6

6

Stage 2

-

+

IN 2A

IN 1A

IN 2B

IN 1B

IN 3

IN 1C

(UNCOMMITTED)

Stage 3

SERIAL

INTERFACE

STAGE 1

CONTROL

REGISTER

STAGE 2

CONTROL

REGISTER

LOAD/LATCH

2

Serial Clock: This external clock input is used to “clock in” the control data. See Figure 4 for

timing information. This input has an internal 1MΩ pullup resistor.

Serial Data: Operation of the two amplifier stages (1 and 2) is controlled by the data entered

serially at this pin. The data is entered (bit 13 to bit 0) on the rising edge of the external Serial

Clock. The data format is described in Tables 1-3 and Figure 4.

This input has an internal 1MΩ pullup resistor.

Load/Latch: Governs the loading and execution of the serial control data. During serial data

loading this input should be kept at a logical “1” to ensure that data rippling past the latches

has no effect. When all 14 bits have been loaded this input should be strobed “1” to “0” to “1” to

latch the new data in. Data is executed on the rising edge of this strobe.

IN 1A (Stage 1 Input 1): Analogue Input.

IN 1B (Stage 1 Input 2): Analogue Input.

IN 2A (Stage 2 Input 1): Analogue Input.

IN 2B (Stage 2 Input 2): Analogue Input.

VSS: Negative supply rail (GND).

V

BIAS

: The output of the on-chip bias circuitry, held at VDD/2.

IN 1C (Stage 1 Input 3): Analogue Input. Normally used for FSK data.

OUT 2 (Stage 2 Output): Analogue Output.

OUT 1B (Stage 1 Output 2): Analogue Output.

OUT 1A (Stage 1 Output 1): Analogue Output.

OUT 3 (Uncommitted Amplifier Output): Output from the general purpose uncommitted

amplifier.

IN 3 (Uncommitted Amplifier Input): Inverting input to general purpose uncommitted amplifier.

VDD: Positive supply rail. A single +5-volt power supply is required.

Pin Number Function

DW/J

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

D5

1

4

5

6

7

8

9

12

13

16

17

18

20

21

23

24

FX029

Loading...

Loading...