Consumer Microcircuits Limited FX002J, FX002DW Datasheet

CML Semiconductor Products

PRODUCT INFORMATION

FX002

Features

Up to 8.5dB Signal-to-Noise

Improvement

Input Frequency Range: 17Hz to 13kHz

[Sub-Audio and Audio Frequencies]

Low-Voltage Operation: 2.5 Volts

10mVrms Minimum Signal Input

Digital Output Signal (fIN x 4)

‘Divided-Down’ Clock Outputs

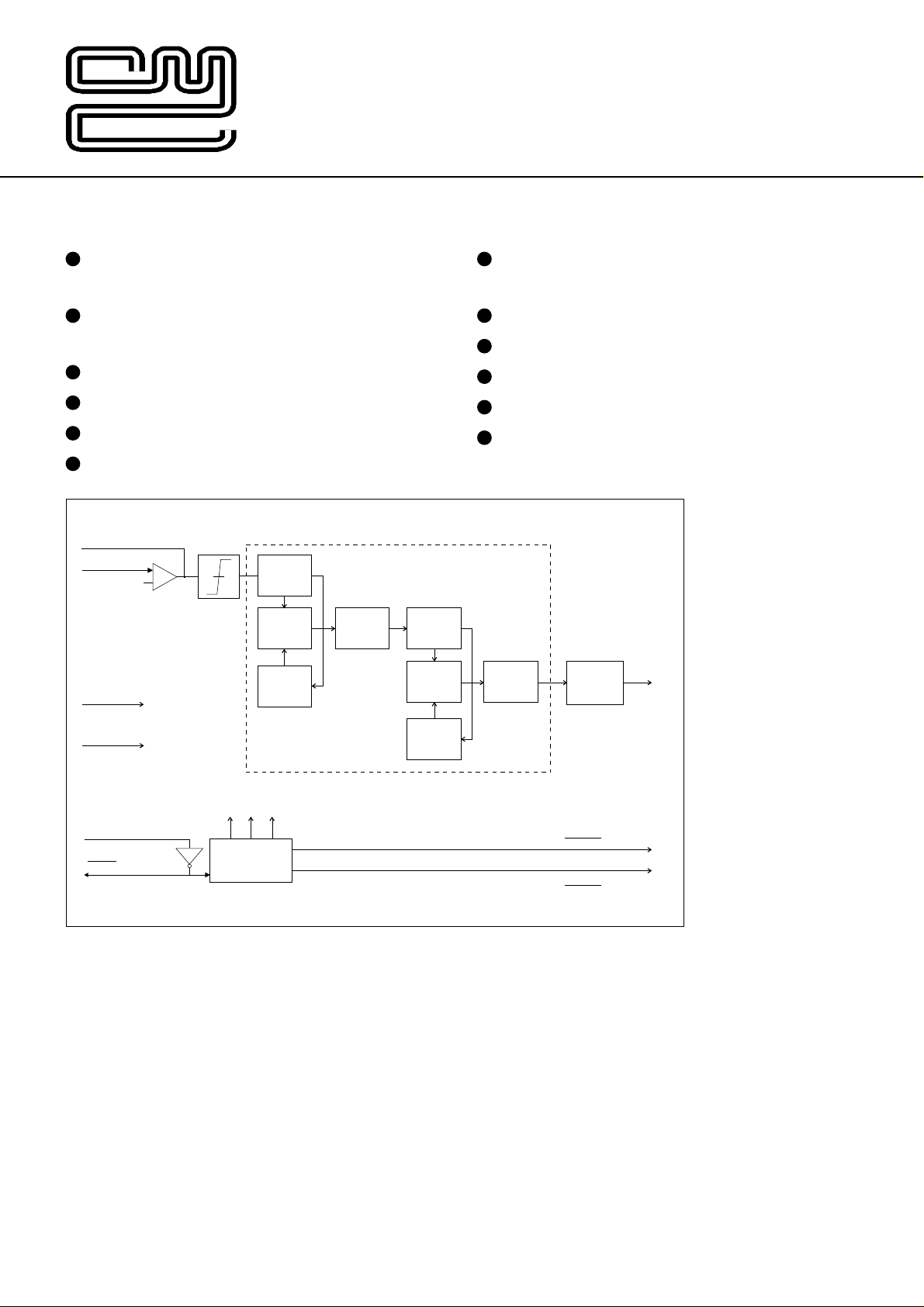

SIGNAL BIAS

SIGNAL IN

-

+

DELAY

48-BIT

Signal to Noise Enhancer

Publication D/002/2 July 1994

Applications

Radio Communications and

Paging Systems

Tone Detection

Sonar Detection and Analysis

Slow Data-Rate Communications

Medical Equipment

Interference Investigation

DELAY

24-BIT

COMPARE

LOGIC

DELAY

24-BIT

V

DD

V

SS

XTAL/CLOCK

XTAL

COMPARE

LOGIC

DELAY

48-BIT

AUTOCORRELATION

PROCESS

CLOCKS

XTAL/CLOCK

GENERATOR/

DIVIDER

INTERPOLATE

Fig.1 Functional Block Diagram

Brief Description

The FX002 is a single-chip device to extract single

periodic signals from very high random-noise

environments.

Using patented autocorrelation techniques the

FX002 will enhance the input signal's signal-to-noise

ratio by as much as 8.5dB and provide a digital output

signal centred at four times (x4) the input frequency.

The amplitude of non-periodic components of the

signal is substantially reduced. The patented

autocorrelator compares the incoming signal to itself;

the more elements of the waveform that are seen as

periodic, the higher the energy at the microcircuit

output.

The FX002 cascades two autocorrelators, each one

improving the signal-to-noise ratio.

OUTPUT

[4 x SIGNAL IN]

INTERPOLATE

OUTPUT

LOGIC

FX002

CLOCK

OUTPUT

6

CLOCK

OUTPUT

24

With a random noise input the output will swing

rail-to-rail at random (peak-limited). The input/output

signal delay is fixed by the choice of clock frequency

and the length of the internal register. The FX002 will

operate at supply voltages of between 2.5 volts and

5.5 volts and with Xtal/clock frequencies from 20kHz to

2.5MHz. Using various Xtal/clock inputs the device can

be set to accept input signal frequencies, in bands,

from 17.0Hz to 13.0kHz.

Two uncommited clock outputs are available to

supply 'divided-down' Xtal/clock frequencies for use in

external and peripheral functions.

This low-power signal processing device is

available in 16-pin cerdip dual-in-line (DIL) and plastic

small outline (S.O.I.C.) surface mount packages.

1

Pin Number Function

FX002DW

1

3

4

5

6

8

FX002J

1

3

4

5

6

7

Signal In: The inverting input to the analogue amplifier/comparator. Used with the Signal Bias

pin; external coupling components are required (see Figure 2).

Signal Bias: The output of the analogue amplifier/comparator. Do not load this pin with

peripheral circuitry; there is no drive capacity for off-chip signalling. The feedback resistor

should be not less than 200kΩ. See Figure 2.

VDD: Positive supply rail. A single, stable power supply is required. Note that this device has

two VDD pins; this input is positioned to prevent cross-talk, either or both may be connected to

the host circuit's supply line. Do not attempt to draw current from either VDD pin.

Clock/24: A squarewave output clock signal at the rate of

Xtal/clock

/24; provided for peripheral

and test purposes.

Xtal: The output of the on-chip clock oscillator inverter.

Xtal/Clock: The input to the on-chip clock oscillator inverter; this may be a Xtal, resonator or

clock pulse input. The selection of this frequency will affect the operational input signal

bandwidth (and output frequency) of this device; refer to Table 2. Note that the choice of V

DD

will determine the maximum Xtal/clock frequency and hence the maximum useable signal

input frequency. Operation of any CML microcircuit without an active Xtal or clock input may

cause device damage. A clock pulse input is fed directly into this pin; Xtal/clock components

are not required.

Table 1 provides a guide to maximum usable Xtal/clock frequencies at pre-determined V

DD

values.

V

(V) Max. Xtal/Clock

DD

Freq. (MHz)

2.5 0.625

Table 1

3.0 1.0

5.0 2.5

9

11

13

16

2, 7, 10,

12, 14, 15

9

11

13

16

2, 8,

10, 12,

14, 15

VSS: Negative supply rail (GND).

Clock/6: A squarewave output clock signal at the rate of

Xtal/clock

/6; provided for peripheral

and test purposes.

Output: (f

OUT

= 4 x f

). The auto-correlated output signal at four times (x 4) the input

SIGNAL IN

signal (see Figure 4).

There is a time delay between input and output signals (see Specifications).

VDD: Positive supply rail. A single, stable power supply is required.

Note that this device has two VDD pins; either or both may be connected to the host circuit's

supply line. Do not attempt to draw current from either VDD pin.

The choice of VDD will determine the maximum Xtal/clock frequency and hence the maximum

useable signal input frequency (see Figure 3).

No internal connection. Leave open-circuit.

2

Loading...

Loading...