Consumer Microcircuits Limited CMX639P6, CMX639E2, CMX639D4 Datasheet

CMX639

Consumer / Commercial

CVSD Digital Voice Codec

2000 Consumer Microcircuits Limited

D/639/2 November 2000 Provisional Issue

Features Applications

•• Single Chip Full Duplex CVSD codec

•• Integrated Input and Output Filters

•• Consumer and Business Handheld

Devices

•• Robust Coding for Wireless Links •• Digital Voice Appliances

•• Programmable Sampling Clocks •• Spread Spectrum Wireless

•• 3 and 4 bit Companding Algorithms •• Cordless Phones

•• Low Power/Small Size for Portable Devices •• Voice Recording and Storage

•• 1.9mA/2.75mA typ. @ 3.0V/5.0V •• Delay Lines

•• 3.0V to 5.5V Operation •• Time Domain Scramblers

•• Powersave Mode •• Multiplexers and Switches

1.1 Brief Description

The CMX639 is a Continuously Variable Slope Delta Modulation (CVSD) full duplex CODEC for use in

consumer and commercial digital voice communication systems. With its robust and selectable coding

algorithms, low cost, very low power, and small size, the CMX639 is ideal for use in a wide variety of

consumer and business digital voice applications. Its completely integrated CODEC simplifies design and

eliminates the costs, complexity and risk of external filters and software algorithms.

8kbps to 128kbps data/sampling clock rates are supported both via external clock signals or internally

generated, programmable clocks. Internal data/sampling clocks are derived from an on-chip reference

oscillator that uses an external clock crystal. An internal data/sampling clock output signal is provided to

synchronize external circuits, if desired. Multiplexer applications are also well supported by the encoder

output’s three-state/high impedance enable feature.

The CMX639 operates from 2.7V to 5.5V supplies and is available in the following packages: 24-pin TSSOP

(CMX639E2), 16-pin SOIC (CMX639D4) and 22-pin PDIP (CMX639P6).

CVSD Codec CMX639

2000 Consumer Microcircuits Limited 2 CMX639/2

CONTENTS

Section

Page

1.0

Features and Applications ..................................................................1

1.1 Brief Description..................................................................................1

1.2 Block Diagram......................................................................................3

1.3 Signal List ............................................................................................4

1.4 External Components..........................................................................6

1.5 General Description.............................................................................7

1.6 Application Notes ................................................................................7

1.7 Performance Specification..................................................................8

1.7.1 Electrical Performance...............................................................8

1.7.2 Packaging ............................................................................... 15

CVSD Codec CMX639

2000 Consumer Microcircuits Limited 3 CMX639/2

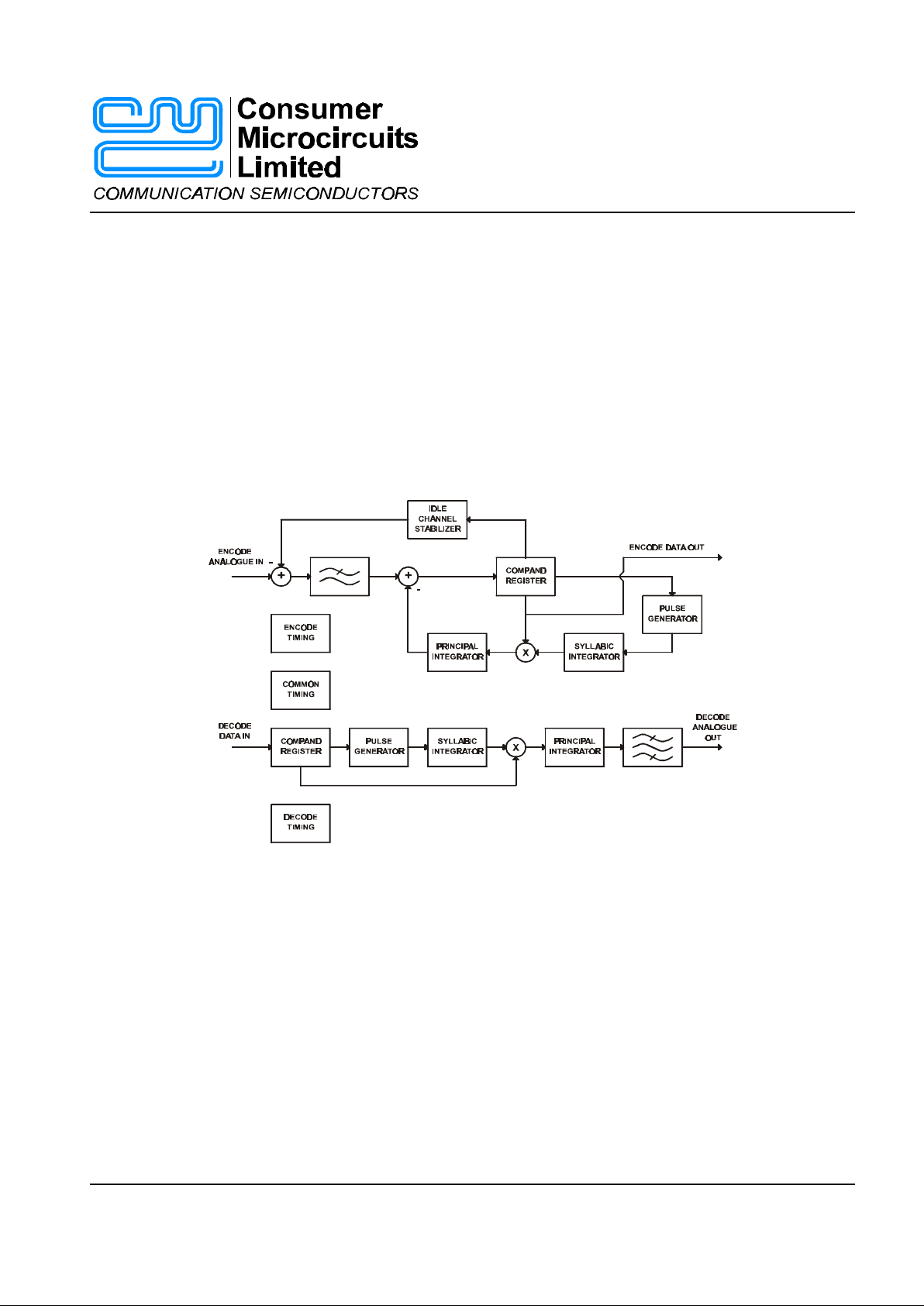

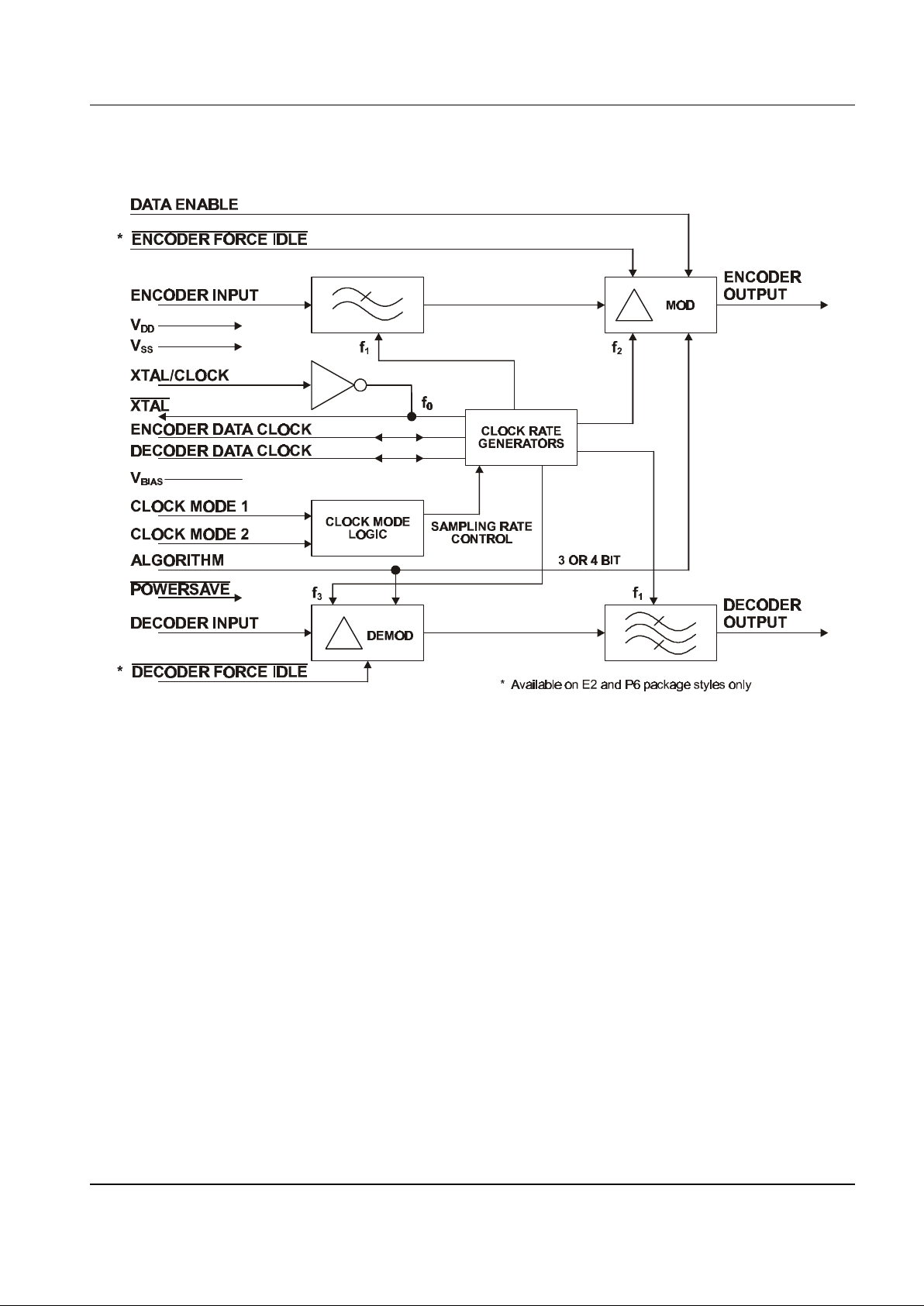

1.2 Block Diagram

Figure 1 Block Diagram

CVSD Codec CMX639

2000 Consumer Microcircuits Limited 4 CMX639/2

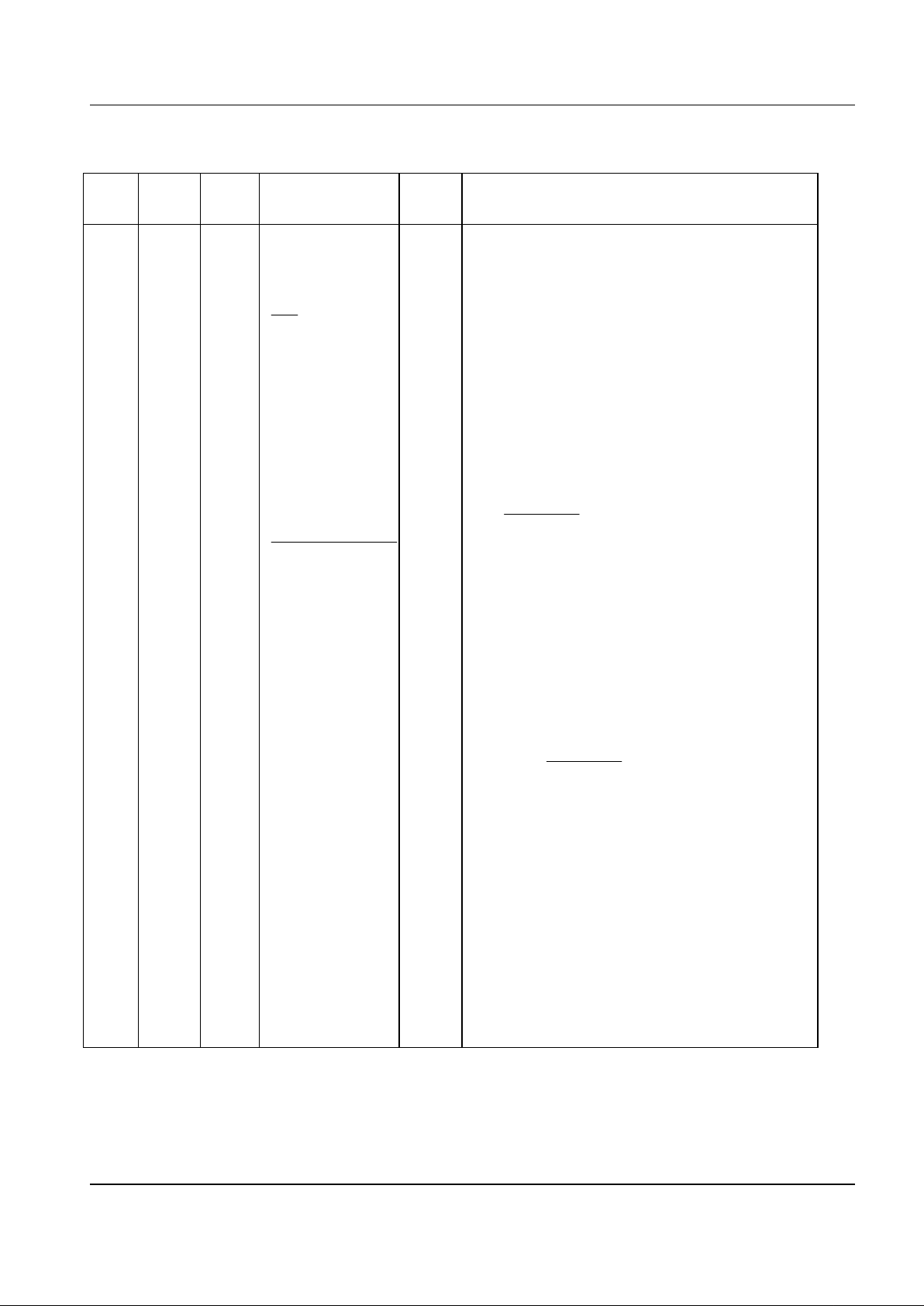

1.3 Signal List

P6

22-pin

PDIP

E2

24-pin

TSSOP

D4

16-pin

SOIC

Signal Name Type

Description

1 1 1 Xtal/Clock input Input to the clock oscillator inverter. A

1.024MHz Xtal input or externally derived clock

is injected here.

2 N/C No Connection

2 3 2

Xtal

output The 1.024 MHz output of the clock oscillator

inverter.

3 4 N/C No Connection

4 5 3 Encoder Data

Clock

input/

output

A logic I/O port. External encode clock input or

internal data clock output. Clock frequency is

dependent upon Clock Mode 1 and 2 inputs and

Xtal frequency. Note: No internal pull-up is

provided. See Table 3.

5 6 4 Encoder Output output The encoder digital output. This is a three-state

output whose condition is set by the Data Enable

and

Powersave inputs. See Table 2.

6 7

Not

present

Idle Force Encoder

input When this pin is at a logical '0' the encoder is

forced to an idle state and the encoder digital

output is ‘0101…’, a perfect idle pattern. When

this pin is a logical '1' the encoder encodes as

normal. Internal 1M

Ω pull-up.

7 8 5 Data Enable input Data is made available at the encoder output pin

by control of this input. See Encoder Output pin.

Internal 1 M

Ω pull-up.

8 9 N/C No Connection

9 10 6 V

BIAS

Normally at V

DD

/2, this pin should be externally

decoupled by capacitor C4. Internally pulled to

V

SS

when Powersave is a logical '0'.

10 11 7 Encoder Input input The analog signal input. Internally biased at

V

DD

/2, this input requires an external coupling

capacitor. The source impedance driving the

coupling capacitor should be less than 1k

Ω. A

lower driving source impedance will reduce

encoder output channel noise levels.

11 12 8 VSS power Negative Supply

12 13 N/C No Connection

13 14 9 Decoder Output output The recovered analog signal is output at this pin.

It is the buffered output of a lowpass filter and

requires external components. During

‘Powersave’ this output is open circuit.

14 15 N/C No Connection

CVSD Codec CMX639

2000 Consumer Microcircuits Limited 5 CMX639/2

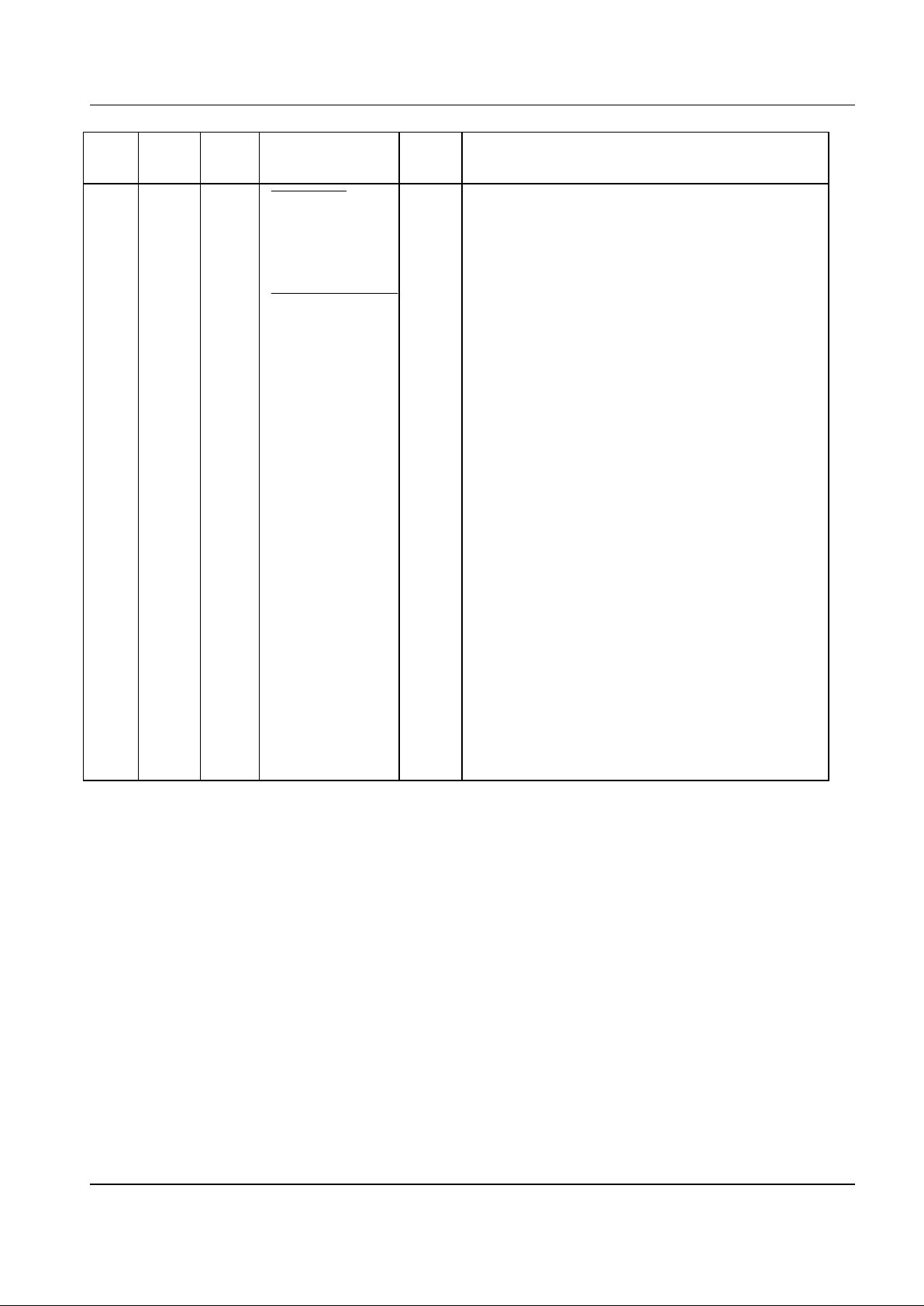

P6

22-pin

PDIP

E2

24-pin

TSSOP

D4

16-pin

SOIC

Signal Name Type

Description

15 16 10

Powersave

Input A logic '0' at this pin puts most parts of the codec

into a quiescent, non-operational state. When at a

logical '1', the codec operates normally. Internal 1

M

Ω pull-up.

17 N/C No Connection

16 18

Not

present

Idle

Force Decoder

input A logic '0' at this pin gates a ‘0101...’ pattern

internally to the decoder so that the Decoder

Output goes to V

DD

/2. When this pin is a logical

'1' the decoder operates as normal. Internal 1M

Ω

pull-up.

17 19 11 Decoder Input input

The received digital signal input. Internal 1 M

Ω

pull-up.

18 20 12 Decoder Data

Clock

input/

output

A logic I/O port. External decode clock input or

internal data clock output. Clock frequency is

dependent upon Clock Mode 1 and 2 inputs and

Xtal frequency. Note: No internal pull-up is

provided. See Table 3.

19 21 13 Algorithm input A logic '1' at this pin sets this device for a 3-bit

companding algorithm. A logical '0' sets a 4-bit

companding algorithm. Internal 1 M

Ω pull-up.

20

21

22

23

14

15

Clock Mode 2

Clock Mode 1

input

input

Clock rates refer to f = 1.024MHz Xtal/Clock input.

During internal operation the data clock

frequencies are available at these ports for

external circuit synchronization. Independent or

common data rate inputs to Encode and Decode

data clock ports may be employed in the External

Clocks mode. Internal 1M

Ω pull-ups. See Table 3.

22 24 16 VDD power Positive Supply. A single 3.0V to 5.5V supply is

required. This pin should be externally decoupled

to V

SS

by capacitor C5.

Loading...

Loading...