CONEX Fusion878A Datasheet

Data Sheet 100600B

December 3, 1999

Fusion™ 878A

PCI Video Decoder

The Fusion 878A is a complete, low cost, single-chip solution for analog

broadcast signal capture on the PCI bus. The Fusion 878A takes advantage

of the PCI-based system’s high bandwidth and inherent multimedia

capability. It is designed to be interoperable with any other PCI multimedia

device at the component or board level.

The Fusion 878A has all the video and audio capture features of the

Bt878, plus a whole lot more. Designed to address the demanding

requirements of the Personal Computing and digital video industry, Fusion

878A meets PC98/PC99 requirements as well as being fully PCI 2.2

compliant. Fusion 878A addresses the current analog PC TV requirements

since it is pin for pin compatible and software compatible with the current

Bt878. But, Fusion 878A can also be used in an array of MPEG digital

transport stream products as well. The world is turning digital, with new

standards in Television – ATSC and COFDM – and Television recording

technologies using MPEG compression. Fusion 878A can be used as the hub

into the PC connecting the multiple analog and digital video formats in the

PC via a single PCI connection.

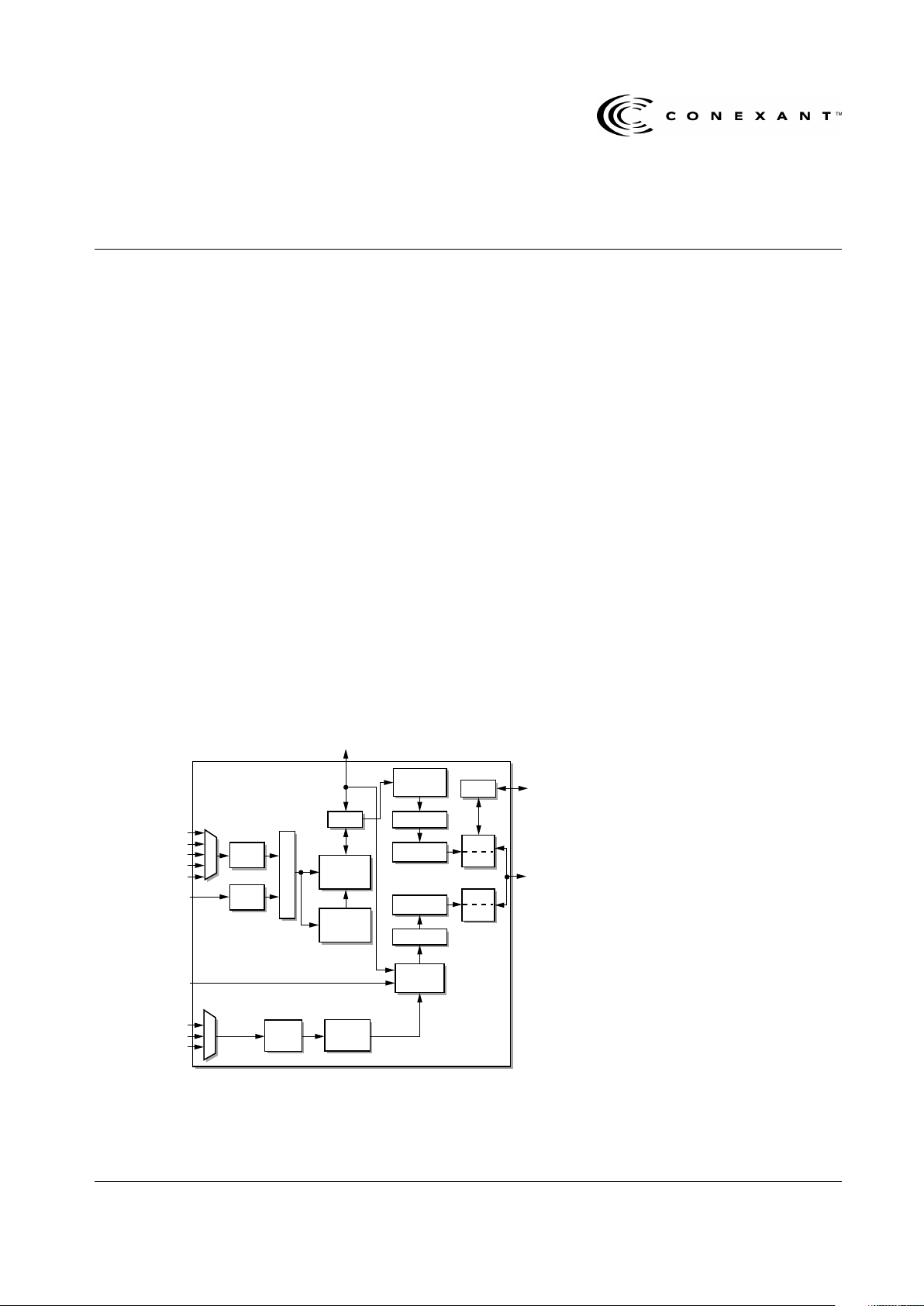

Functional Block Diagram

40 MHz

ADC

40 MHz

ADC

PCI I/F

Composite 1

PCI

Bus

S-Video (C)

TV

FM

Composite 2

Composite S-Video (Y)

Mic

High BW

Audio

ADC

Input

Gain

Control

Ultralock™

and Clock

Generation

Video

Decode

and Scaling

I

2

C

GPIO

Composite 3

Composite 4

GPIO and Digital/Video Port

3:1 MUX

Target

Initiator

Target

Initiator

Audio

Stream

Format

Audio FIFO

DMA

Controller

DMA

Controller

Video FIFO

Pixel

Format

Conversion

879A_001

I2S (dig. audio)

Decimation LPF

Distinguishing Features

• NTSC/PAL/SECAM video decoding

• Supports capture resolutions up to 768 x 576 (full

PAL)

• On-chip PCI bus mastering and bridge

functionality

• Supports HDTV/audio/MPEG2 transport data

across PCI bus

• High-speed serial port support MPEG transport

stream up to rates of 40 Mbps

• High-speed parallel port supports MPEG transport

streams up to 20 Mbps

• Flexible 24-bit wide GPIO

• CCIR656 interface

• Interfaces to a Digital TV data stream from a VSB

or OFDM demodulator

• Multiple YCrCb and RGB pixel formats and YUV

planar formats supported on output

• Selectable pixel density: 8, 16, 24, and 32 bits per

pixel

• Performs complex clipping of video source and

VGA video overlay

• Permits different program control and color

space/scaling for even and odd fields

• Executes Windows 98 “Scatter and Gather”

• Integrates advanced chroma and luma comb

filters/scalers

• Image scaleable in X and Y direction

• Y/C, 6-tap luma/2-tap chroma polyphase filter

• Receives Digital audio via I2S serial port

• Includes VBI data capture (closed captioning,

teletext, and Intercast data decoding)

• 100% PCI Rev. 2.2 compliant

• PC 98/PC 99 compliant

• WHQL-certifiable

• Accepts Mono audio input

• Packaged in compact 128-pin plastic QFP

Fusion 878A Specific Features

• Full stereo decoding for both TV audio (BTSC) and

FM radio

• Enhanced GPIO/I

2

S

• ACPI support

• Byte alignment

• Vital product data

• High speed serial port

• High speed parallel port

Applications

• PC television

• Digital television

• Digital VCR

• Desktop video phone

• Still frame capture

• VBI data service capture

100600B Conexant

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is

assumed by Conexant for its use, nor any infringement of patents, copyrights, or other rights of third parties which may result from its

use. No license is granted by implication or otherwise under any patent rights or copyrights of Conexant other than for circuitry

embodied in Conexant products. Conexant reserves the right to change circuitry at any time without notice. This document is subject

to change without notice.

Conexant products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a

Conexant product can reasonably be expected to result in personal injury or death. Conexant customers using or selling Conexant

products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from

such improper use or sale.

Conexant, the Conexant symbol and “What’s Next in Communications Technologies” are trademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered

trademarks of third parties. All other marks mentioned herein are the property of their respective owners.

© 1999 Conexant Systems, Inc.

Printed in U.S.A.

All Rights Reserved

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send

comments and suggestions to conexant.tech.pubs@conexant.com. For technical questions, contact your local

Conexant sales office or field applications engineer.

Ordering Information

Related Documents

Fusion Technical Reference Manual

Fusion Programmers Guide

Model Number Package Operating Temperature

Fusion 878A 128-pin PQFP 0 °C to + 70 °C

100600B Conexant iii

Table of Contents

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xiii

1.0 Product Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1 Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2 Detailed Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2.1 Video Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2.2 Audio Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2.3 Analog Video and Digital Camera Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2.4 Intel Intercast™ Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2.5 Video DMA Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.2.6 Audio DMA Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.2.7 Data Transport Engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.2.8 PCI Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.2.9 UltraLock™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.2.10 Scaling and Cropping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.2.11 Input Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.2.12 GPIO Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.2.13 Vertical Blanking Interval Data Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.2.14 I2C Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.2.15 HDTV Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.3 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

2.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

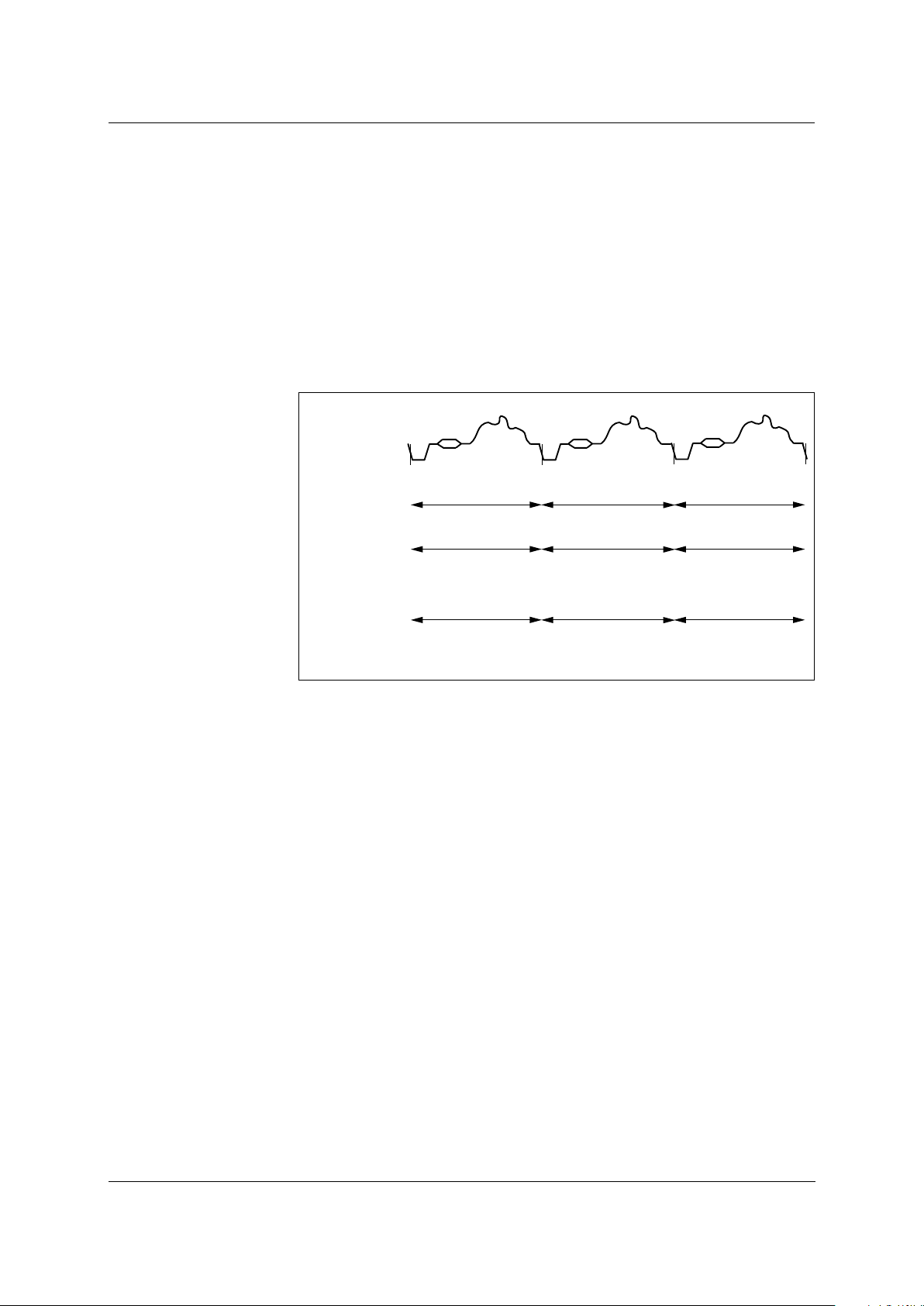

2.1 UltraLockTM Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1.1 The Challenge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1.2 Operating Principles of UltraLock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.2 Composite Video Input Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

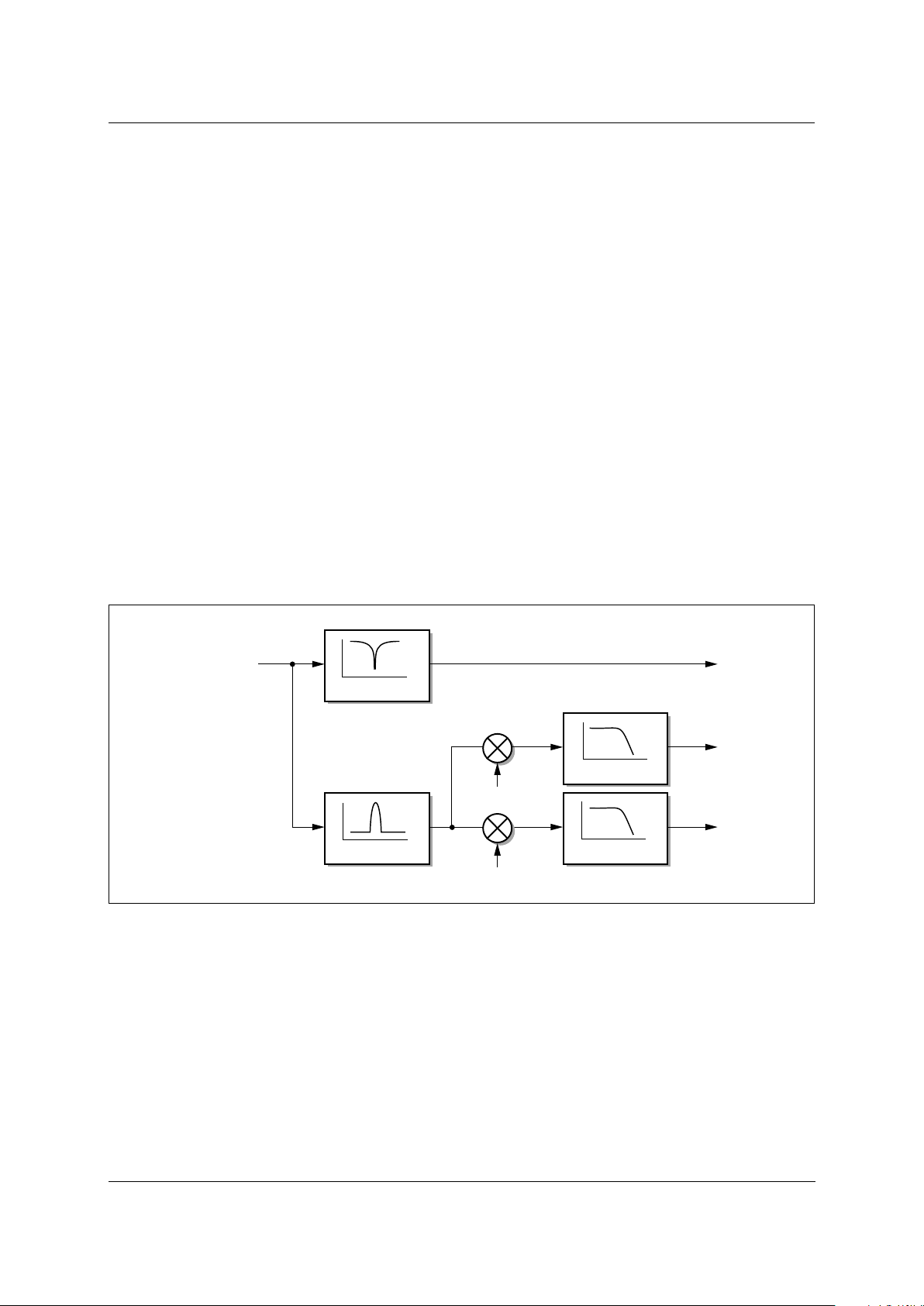

2.3 Y/C Separation and Chroma Demodulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Table of Contents Fusion 878A

PCI Video Decoder

iv Conexant 100600B

2.4 Video Scaling, Cropping, and Temporal Decimation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.4.1 Down-Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.4.1.1 Horizontal and Vertical Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.4.1.2 Field Aligned Vertical Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.4.1.3 Luminance Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.4.1.4 Peaking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.4.1.5 Chrominance Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.4.1.6 Scaling Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.4.2 Image Cropping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2.4.2.1 Cropping Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2.4.3 Temporal Decimation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

2.5 Video Adjustments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.5.1 The Hue Adjust Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.5.2 The Contrast Adjust Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.5.3 The Saturation Adjust Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.5.4 The Brightness Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.6 Automatic Chrominance Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.7 Low Color Detection and Removal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.8 Coring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

2.9 VBI Data Output Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

2.9.1 VBI Line Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2.10 Video Data Format Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

2.10.1 Pixel Data Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

2.10.2 Video Control Code Status Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

2.10.3 YCrCb to RGB Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.10.4 Gamma Correction Removal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.10.5 YCrCb Sub-sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.10.6 Byte Swapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31

2.11 Video and Control Data FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

2.11.1 Logical Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

2.11.2 FIFO Data Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

2.11.3 Physical Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

2.11.4 FIFO Input/Output Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

2.12 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

2.12.1 Target Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

2.12.2 RISC Program Setup and Synchronization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

2.12.3 RISC Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-38

2.12.4 Complex Clipping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-43

2.12.5 Executing Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-44

2.12.6 FIFO Overrun Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-45

2.12.7 FIFO Data Stream Resynchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-46

2.13 Byte Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-47

Fusion 878A Table of Contents

PCI Video Decoder

100600B Conexant v

2.14 Multifunction Arbiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48

2.14.1 Normal PCI Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48

2.14.2 430FX Compatibility Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48

2.14.3 Interfacing with Non-PCI 2.1 Compliant Core Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-49

2.15 Audio A/D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-50

2.15.1 Muxing and Anti-aliasing Filtering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-50

2.15.2 Input Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-50

2.16 High Speed Serial Interface Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-52

2.17 Asynchronous Data Parallel Mode: Raw Data Capture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-53

2.18 Digital Audio Packetizer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-54

2.18.1 Audio FIFO Memory and Status Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-54

2.18.2 PCI Bus Latency Tolerance for Audio Buffer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-54

2.18.3 FIFO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-55

2.18.4 Audio Packets and Data Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-56

2.18.5 Digital Audio Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-57

2.18.5.1 Digital Audio Input Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-57

2.18.6 Data Packet Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-58

2.18.7 Audio Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-59

2.18.8 Audio Dropout Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-59

2.19 Digital Television Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-60

3.0 Electrical Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1 Input Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1 Analog Signal Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.2 Multiplexer Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.3 Flash A/D Converters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.4 A/D Clamping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.5 Power-up Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.6 Automatic Gain Controls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.7 Crystal Inputs and Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.8 2X Oversampling and Input Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.2 PCI Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.3 General Purpose I/O Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.3.1 GPIO Pin Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.3.2 GPIO Modes in Fusion 878A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.3.3 GPIO Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.3.4 SPI Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

3.3.5 SPI Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

3.3.6 GPIO SPI Mode Timing Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

3.3.7 Digital Video Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

3.3.7.1 CCIR656 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

3.3.7.2 Modified SMPTE-125 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

3.3.8 GPIO Timing Diagram for SPI and Digital Video Input Modes . . . . . . . . . . . . . . . . . . . . . 3-20

3.4 I2C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

Table of Contents Fusion 878A

PCI Video Decoder

vi Conexant 100600B

3.5 I2C Serial EEPROM Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

3.5.1 EEPROM Address Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

3.5.2 Subsystem Vendor ID. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

3.5.2.1 EEPROM Upload at PCI Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

3.5.2.2 Register Load from BIOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

3.5.2.3 Programming and Write-Protect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

3.5.3 Vital Product Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

3.5.3.1 Vital Product Data EEPROM Addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

3.5.3.2 Vital Product Data Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

3.5.3.3 Vital Product Data Write Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

3.6 Power Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

3.6.1 PME# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

3.6.2 D3 Power States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

3.7 JTAG Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

3.7.1 Need for Functional Verification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

3.7.2 JTAG Approach to Testability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

3.7.3 Optional Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-30

3.7.4 Verification with the TAP Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-30

4.0 PC Board Layout Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1 Layout Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1.1 Capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1.2 Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.2 Split Planes and Voltage Regulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.3 Latchup Avoidance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

5.0 Control Register Definitions-Function 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1 PCI Configuration Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2 PCI Configuration Registers (Header) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

0x00—Vendor and Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

0x04—Command and Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

0x08—Revision ID and Class Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

0x0C—Header Type, Latency Timer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

0x10—Base Address 0 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

0x2C—Subsystem ID and Subsystem Vendor ID Register . . . . . . . . . . . . . . . . . . . . 5-4

0x3C—Interrupt Line, Interrupt Pin, Min_Gnt, Max_Lat Register. . . . . . . . . . . . . . . . 5-5

0x34—Capabilities Pointer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

0x40—Device Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

0x44—VPD Capability Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

0x48—VPD Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

0x4C—Power Management Capability Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

0x50—Power Management Support Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.3 Local Registers (Memory Mapped) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

0x000—Device Status Register (DSTATUS). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

0x004—Input Format Register (IFORM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

0x008—Temporal Decimation Register (TDEC) . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

Fusion 878A Table of Contents

PCI Video Decoder

100600B Conexant vii

MSB Cropping Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

0x00C—Even Field (E_CROP)

0x08C—Odd Field (O_CROP)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

Vertical Delay Register, Lower Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

0x090—Even Field (E_VDELAY_LO)

0x010—Odd Field (O_VDELAY_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

Vertical Active Register, Lower Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

0x014—Even Field (E_VACTIVE_LO)

0x094—Odd Field (O_VACTIVE_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

Horizontal Delay Register, Lower Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

0x018—Even Field (E_DELAY_LO)

0x098—Odd Field (O_DELAY_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Horizontal Active Register, Lower Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

0x01C—Even Field (E_HACTIVE_LO)

0x09C—Odd Field (O_HACTIVE_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Horizontal Scaling Register, Upper Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

0x020—Even Field (E_HSCALE_HI)

0x0A0—Odd Field (O_HSCALE_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Horizontal Scaling Register, Lower Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

0x024—Even Field (E_HSCALE_LO)

0x0A4—Odd Field (O_HSCALE_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

0x028—Brightness Control Register (BRIGHT). . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

Miscellaneous Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

0x02C—Even Field (E_CONTROL)

0x0AC—Odd Field (O_CONTROL)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

0x030—Luma Gain Register, Lower Byte (CONTRAST_LO) . . . . . . . . . . . . . . . . . . 5-15

0x034—Chroma (U) Gain Register, Lower Byte (SAT_U_LO) . . . . . . . . . . . . . . . . . 5-16

0x038—Chroma (V) Gain Register, Lower Byte (SAT_V_LO) . . . . . . . . . . . . . . . . . 5-17

0x03C—Hue Control Register (HUE). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

SC Loop Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

0x040—Even Field (E_SCLOOP)

0x0C0—Odd Field (O_SCLOOP)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

0x044—White Crush Up Register (WC_UP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

0x048—Output Format Register (OFORM). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

Vertical Scaling Register, Upper Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

0x04C—Even Field (E_VSCALE_HI)

0x0CC—Odd Field (O_VSCALE_HI)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

Vertical Scaling Register, Lower Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

0x050—Even Field (E_VSCALE_LO)

0x0D0—Odd Field (O_VSCALE_LO)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

0x054—Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

0x5B—Audio Reset Register (ARESET) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

0x060—AGC Delay Register (ADELAY) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

0x064—Burst Delay Register (BDELAY) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

0x068—ADC Interface Register (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

Video Timing Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24

0x6C—Even Field (E_VTC)

0xEC—Odd Field (O_VTC)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24

0x07C—Software Reset Register (SRESET). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24

0x078—White Crush Down Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

0x080—Timing Generator Load Byte (TGLB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

0x084—Timing Generator Control (TGCTRL) Register . . . . . . . . . . . . . . . . . . . . . . 5-26

0x0B0—Total Line Count Register (VTOTAL_LO) . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

Table of Contents Fusion 878A

PCI Video Decoder

viii Conexant 100600B

0x0B4—Total Line Count Register (VTOTAL_HI). . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

0x0D4—Color Format Register (COLOR_FMT). . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28

0x0D8—Color Control Register (COLOR_CTL). . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

0x0DC—Capture Control Register (CAP_CTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

0x0E0—VBI Packet Size Register (VBI_PACK_SIZE) . . . . . . . . . . . . . . . . . . . . . . . 5-30

0x0E4—VBI Packet Size / Delay Register (VBI_PACK_DEL). . . . . . . . . . . . . . . . . . 5-30

0x0E8—Field Capture Counter Register (FCAP) . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

0x0F0—PLL Reference Multiplier Register (PLL_F_LO) . . . . . . . . . . . . . . . . . . . . . 5-30

0x0F4—PLL Reference Multiplier Register (PLL_F_HI). . . . . . . . . . . . . . . . . . . . . . 5-30

0x0F8—Integer Register (PLL-XCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

0x0FC—Digital Video Signal Interface Format (DVSIF) Register . . . . . . . . . . . . . . . 5-31

0x100—Interrupt Status Register (INT_STAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32

0x104—Interrupt Mask Register (INT_MASK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-33

0x10C—GPIO and DMA Control Register (GPIO_DMA_CTL) . . . . . . . . . . . . . . . . . 5-34

0x110—I2C Data/Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35

0x114—RISC Program Start Address Register (RISC_STRT_ADD) . . . . . . . . . . . . 5-36

0x118—GPIO Output Enable Control Register (GPIO_OUT_EN) . . . . . . . . . . . . . . . 5-36

0x120—RISC Program Counter Register (RISC_COUNT) . . . . . . . . . . . . . . . . . . . 5-36

0x200–0x2FF—GPIO Data I/O Register (GPIO_DATA) . . . . . . . . . . . . . . . . . . . . . . 5-36

6.0 Control Register Definitions–Function 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1 PCI Configuration Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.2 PCI Configuration Registers (Header) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

0x00—Vendor and Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

0x04—Command and Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

0x08—Revision ID and Class Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

0x0C—Header Type Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

0x0C—Latency Timer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

0x10—Base Address 0 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

0x2C—Subsystem ID and Subsystem Vendor ID Register . . . . . . . . . . . . . . . . . . . . 6-5

0x34—Capabilities Pointer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

0x3C—Interrupt Line, Interrupt Pin, Min_Gnt, Max_Lat Register. . . . . . . . . . . . . . . . 6-5

0x40—Device Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

0x44—VPD Capability Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

0x48—VPD Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

0x4C—Power Management Capability Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

0x50—Power Management Support Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.3 Local Registers (Memory Mapped) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

0x100—Interrupt Status Register (INT_STAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

0x104—Interrupt Mask Register (INT_MASK). . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

0x10C—Audio Control Register (GPIO_DMA_CTL) . . . . . . . . . . . . . . . . . . . . . . . . 6-11

0x110—Audio Packet Lengths Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

0x114—RISC Program Start Address Register (RISC_STRT_ADD). . . . . . . . . . . . . 6-13

0x120—RISC Program Counter Register (RISC_COUNT) . . . . . . . . . . . . . . . . . . . . 6-13

7.0 Parametric Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1 DC Electrical Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.2 AC Electrical Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.3 Package Mechanical Drawing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Appendix A. Acronym List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Fusion 878A List of Figures

PCI Video Decoder

100600B Conexant xi

List of Figures

Figure 1-1. Fusion 878A Detailed Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-2

Figure 1-2. Fusion 878A Audio/Video Decoder and Scaler Block Diagram . . . . . . . . . . . . . . . . . . . . . . 1-3

Figure 1-3. Fusion 878A Pinout Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

Figure 2-1. UltraLock Behavior for NTSC Square Pixel Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 2-2. Y/C Separation and Chroma Demodulation for Composite Video . . . . . . . . . . . . . . . . . . . . 2-4

Figure 2-3. Y/C Separation Filter Responses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Figure 2-4. Filtering and Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

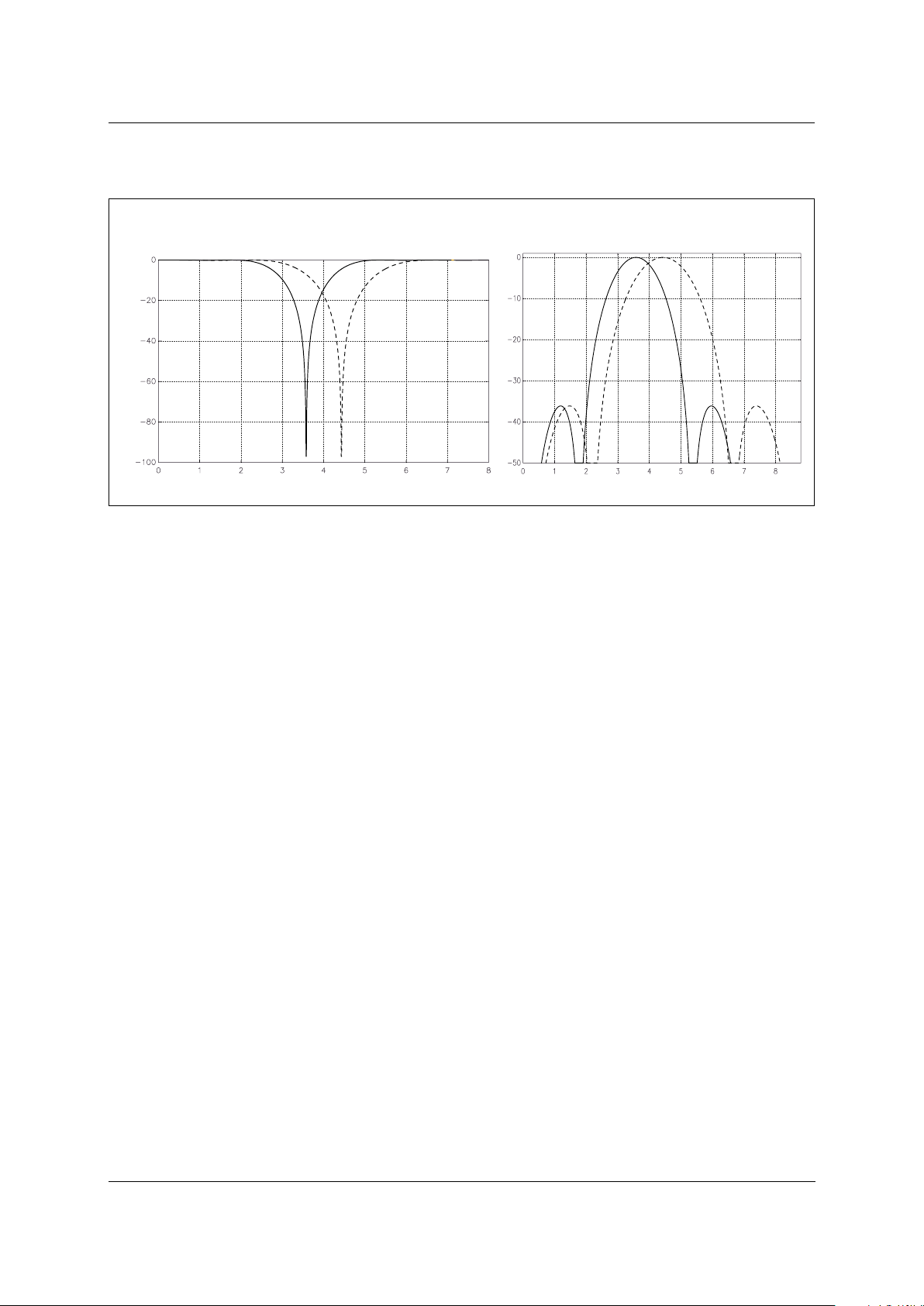

Figure 2-5. Optional Horizontal Luma Low-Pass Filter Responses . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Figure 2-6. Combined Luma Notch, 2x Oversampling and Optional

Low-Pass Filter Response (NTSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Figure 2-7. Combined Luma Notch, 2x Oversampling and Optional

Low-Pass Filter Response (PAL/SECAM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Figure 2-8. Combined Luma Notch and 2x Oversampling Filter Response . . . . . . . . . . . . . . . . . . . . . . 2-9

Figure 2-9. Frequency Responses for the Four Optional Vertical Luma Low-Pass Filters . . . . . . . . . . 2-10

Figure 2-10. Peaking Filters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Figure 2-11. Luma Peaking Filters with 2x Oversampling Filter and Luma Notch . . . . . . . . . . . . . . . . . 2-12

Figure 2-12. Effect of the Cropping and Active Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

Figure 2-13. Regions of the Video Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

Figure 2-14. Coring Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

Figure 2-15. Regions of the NTSC Video Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

Figure 2-16. Regions of the PAL Video Frame (Fields 1, 2, 5, and 6) . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

Figure 2-17. VBI Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

Figure 2-18. VBI Section Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

Figure 2-19. Video Data Format Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

Figure 2-20. Data FIFO Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

Figure 2-21. Audio/Video RISC Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-37

Figure 2-22. Example of Complex Clipping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-44

Figure 2-23. Asynchronous Data Parallel Input Multiplexer Block. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-53

Figure 2-24. FIFO Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-55

Figure 2-25. Audio Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-57

Figure 2-26. Data Packet Mode Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-58

Figure 2-27. Audio Data Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-59

Figure 3-1. Typical External Circuitry. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Figure 3-2. Clock Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Figure 3-3. Luma and Chroma 2x Oversampling Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Figure 3-4. PCI Video Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

Figure 3-5. PCI Audio Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

Figure 3-6. GPIO Pin Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Figure 3-7. GPIO Normal Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

List of Figures Fusion 878A

PCI Video Decoder

xii Conexant 100600B

Figure 3-8. GPIO SPI Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

Figure 3-9. GPIO SPI Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

Figure 3-10. Basic Timing Relationships for SPI Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

Figure 3-11. Video Timing in SPI Output Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-16

Figure 3-12. CCIR 656 Interface to Digital Input Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-19

Figure 3-13. GPIO Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20

Figure 3-14. The Relationship Between SCL and SDA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

Figure 3-15. I

2

C Typical Protocol Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

Figure 3-16. Instruction Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-30

Figure 4-1. Optional Regulatory Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Figure 5-1. Function 0 PCI Configuration Space Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Figure 6-1. Function 1 PCI Configuration Space Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Figure 7-1. Clock Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Figure 7-2. JTAG Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Figure 7-3. 128-pin PQFP Package Mechanical Drawing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Fusion 878A List of Tables

PCI Video Decoder

100600B Conexant xiii

List of Tables

Table 1-1. Audio/Video Capture Product Family. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

Table 1-2. Pin Descriptions Grouped by Pin Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

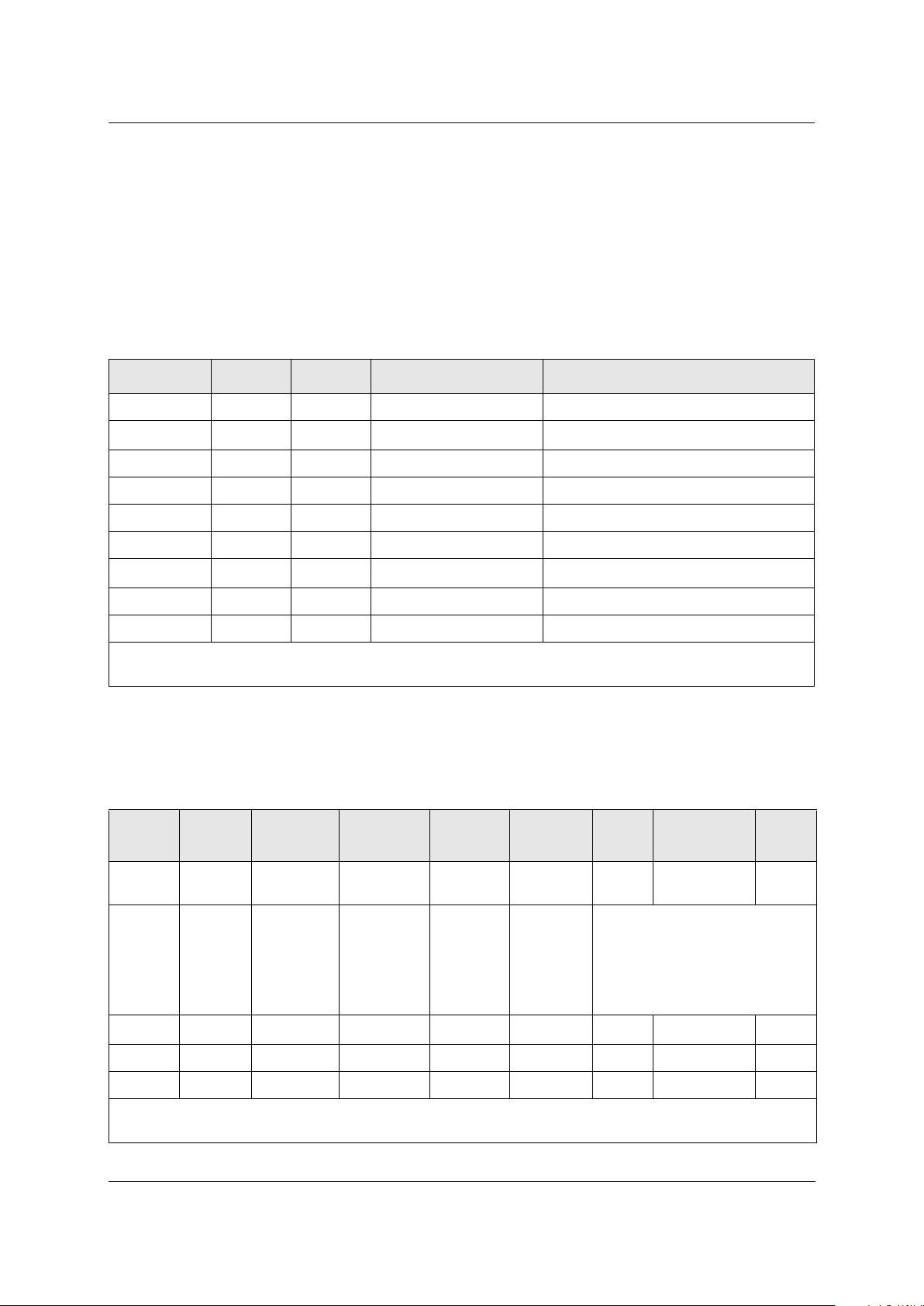

Table 2-1. Video Input Formats Supported by the Fusion 878A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Table 2-2. Register Values for Square Pixel Video Input Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Table 2-3. Scaling Ratios for Popular Formats Using Frequency Values . . . . . . . . . . . . . . . . . . . . . . . 2-16

Table 2-4. Square Pixel Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

Table 2-5. Color Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

Table 2-6. Byte Swapping Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31

Table 2-7. Status Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

Table 2-8. FIFO Full/Almost Full Counts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

Table 2-9. Table of PCI Bus Access Latencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-35

Table 2-10. RISC Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-38

Table 2-11. Write 640 Pixels in RGB8 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-47

Table 2-12. Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-50

Table 2-13. Digital Audio Packetizer Programming Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-54

Table 2-14. Audio Data Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-59

Table 3-1. Recommended Crystals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

Table 3-2. SPI Input GPIO Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

Table 3-3. SPI GPIO Output Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Table 3-4. GPIO SPI Mode Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

Table 3-5. Pin Definition of GPIO Port When Using Digital Video-In Mode . . . . . . . . . . . . . . . . . . . . . 3-18

Table 3-6. External EEPROM Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

Table 3-7. EEPROM Upload Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-24

Table 3-8. VPD Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

Table 3-9. VPD Write Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

Table 3-10. Device Identification Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-30

Table 4-1. Capacitor Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Table 5-1. BRIGHT Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

Table 5-2. CONTRAST Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

Table 5-3. (SAT_U_MSB + SAT_U_LO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

Table 5-4. SAT_V (SAT_V_MSB + SAT_V_LO). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

Table 5-5. HUE Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

Table 7-1. Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

Table 7-2. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Table 7-3. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Table 7-4. Clock Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Table 7-5. Power Supply Current Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-4

Table 7-6. JTAG Timing Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Table 7-7. Decoder Performance Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-5

List of Tables Fusion 878A

PCI Video Decoder

xiv Conexant 100600B

100600B Conexant 1-1

1

1.0 Product Overview

1.1 Functional Overview

The Fusion 878A video and audio capture chip is a multi-function peripheral

component interconnect (PCI) device intended for +5 V only operation. The

video function features a direct memory access (DMA)/PCI bus master for analog

NTSC/PAL/SECAM composite, S-Video, and digital CCIR 656 video capture.

The audio function features a completely independent DMA/PCI bus master for

FM radio or TV sound capture.

The Fusion 878A is based on the Bt848A video capture chip. The Fusion

878A is a Bt848A upgraded to include various audio capture capabilities. The

main features of the Bt848A are: NTSC/PAL/SECAM video decoding, multiple

YCrCb and RGB pixel formats supported on the output, vertical blanking interval

(VBI) data capture for closed captioning, teletext, and intercast data decoding.

The complete set of video and audio capture features are documented in this data

sheet.

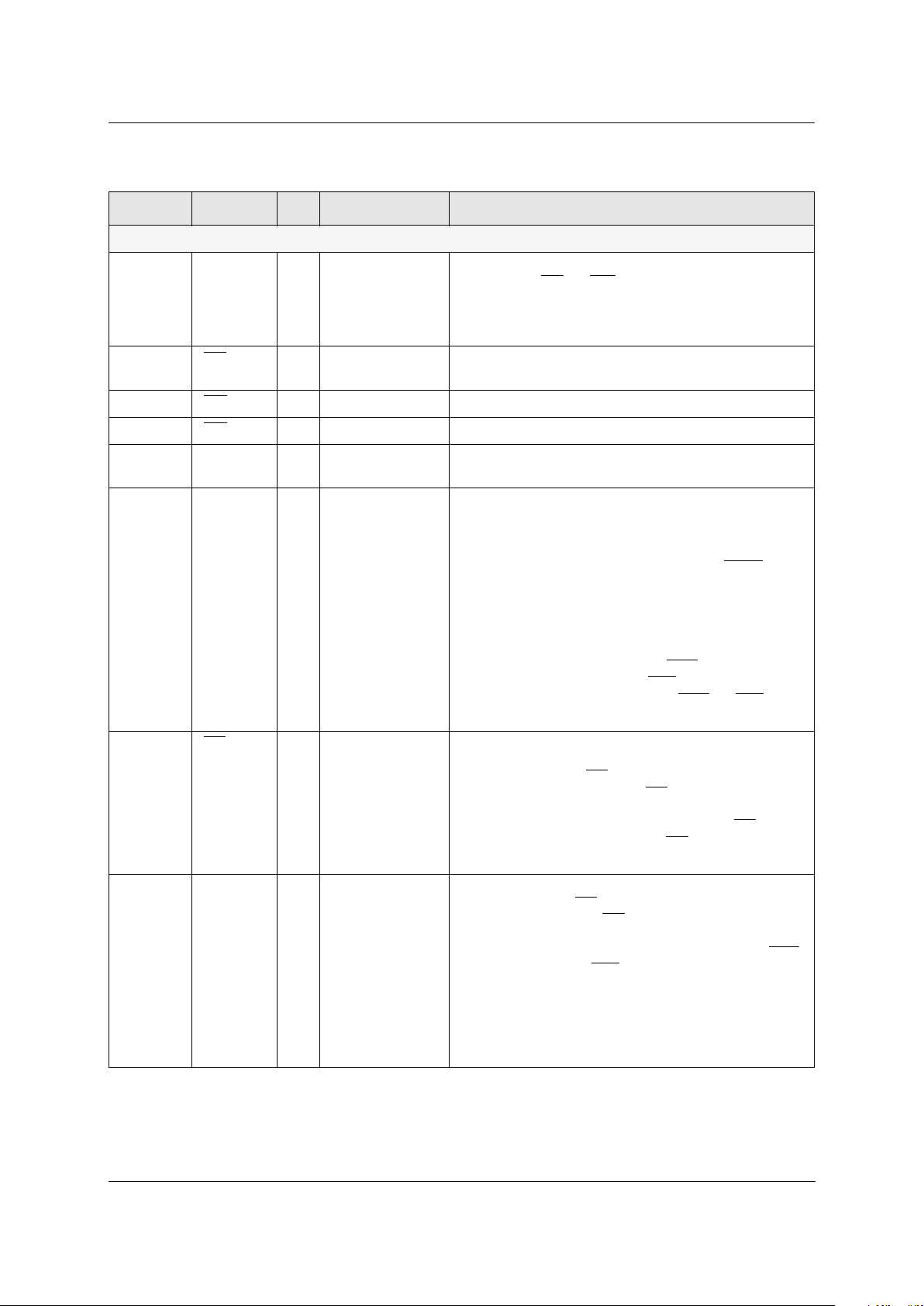

Table 1 -1 indicates which audio capture features are added to the Bt848A to

produce the Fusion 878A.

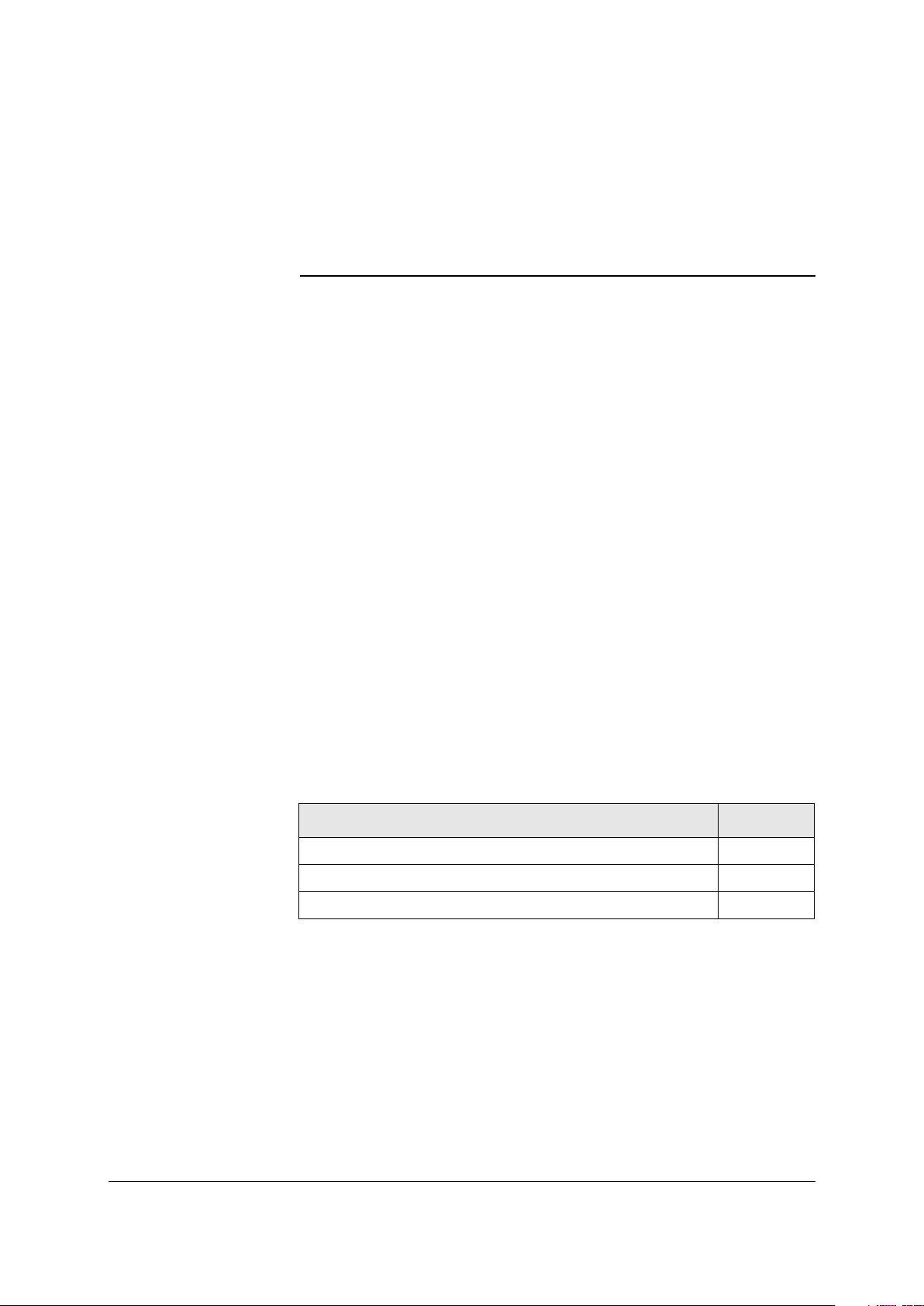

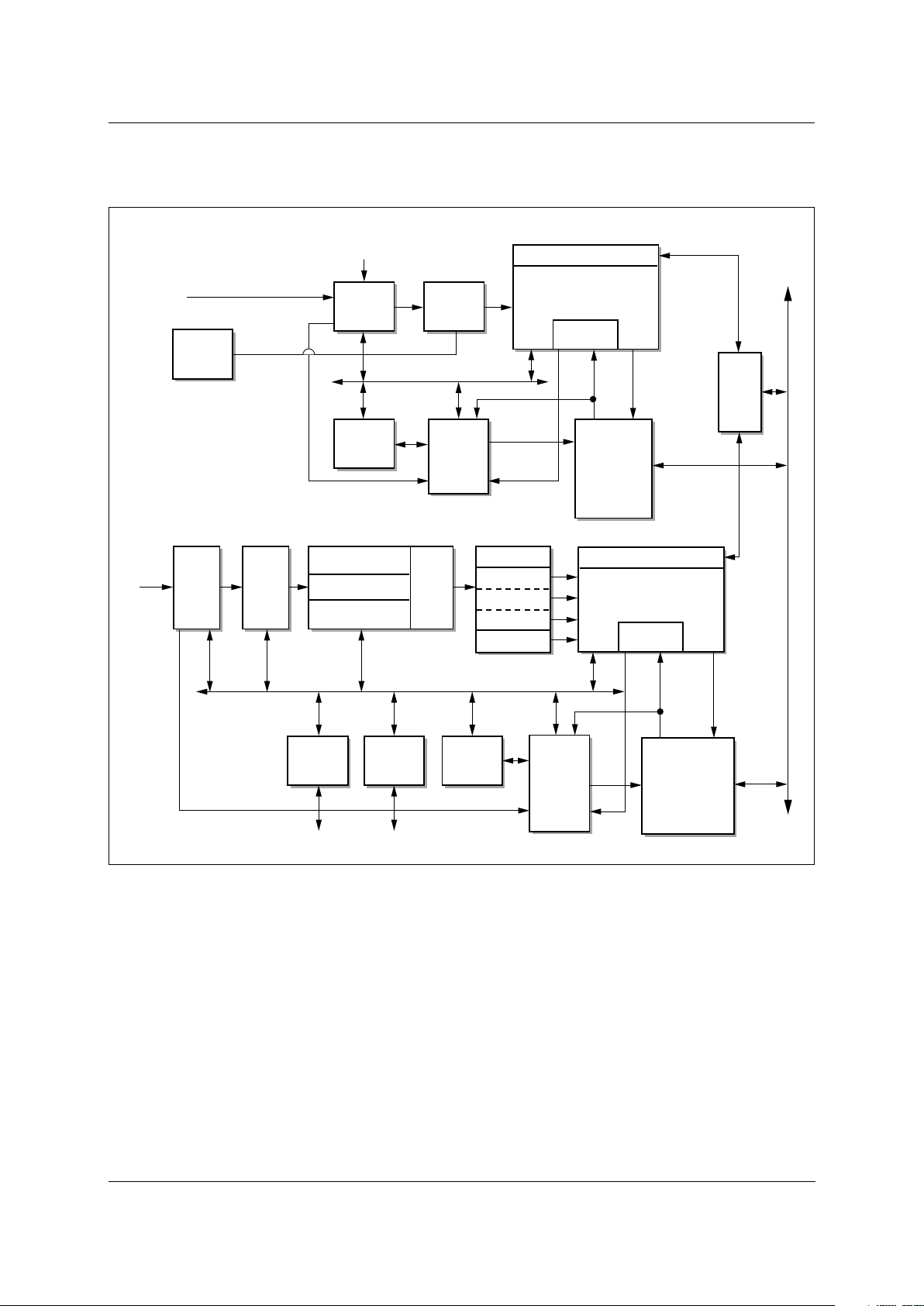

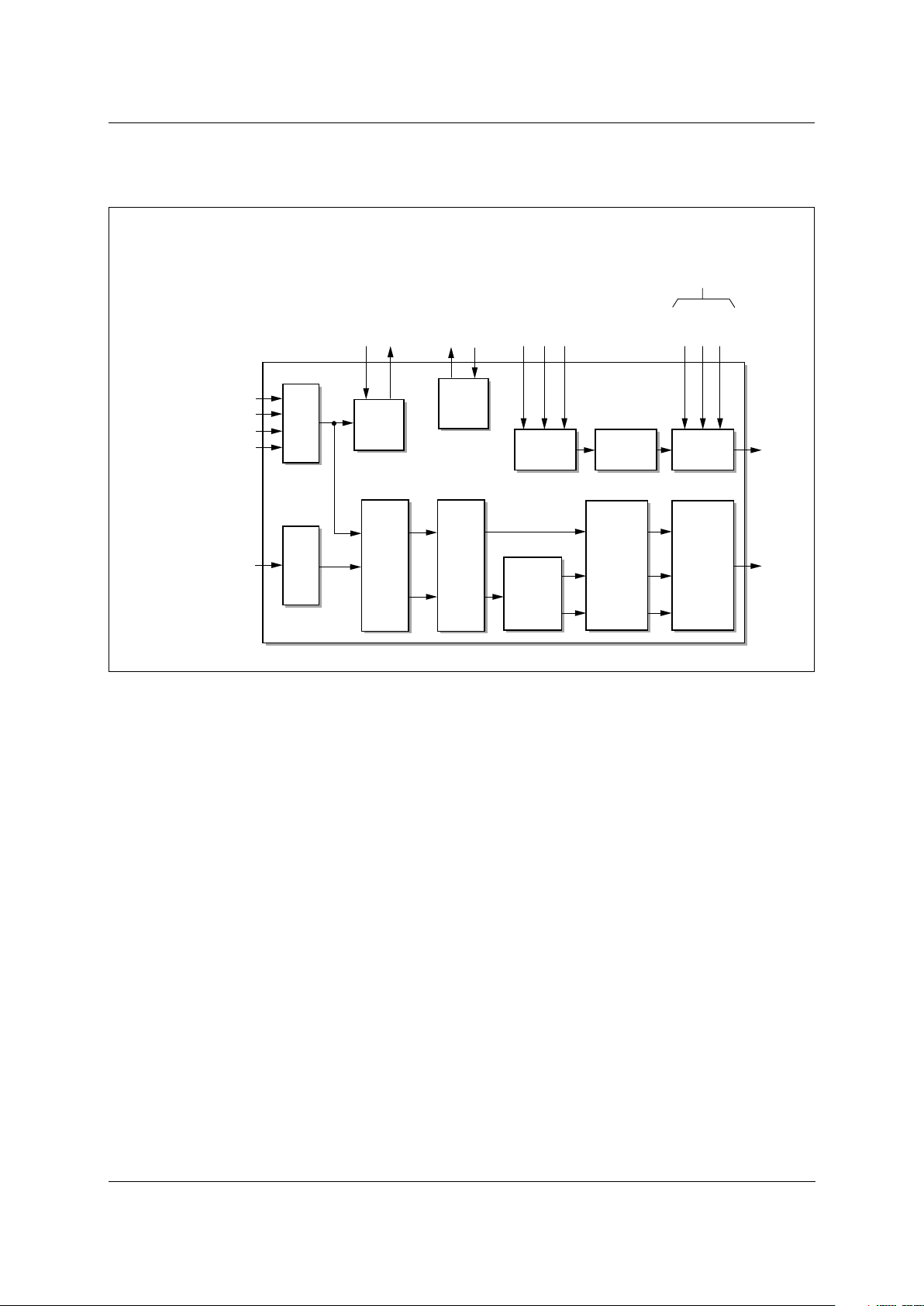

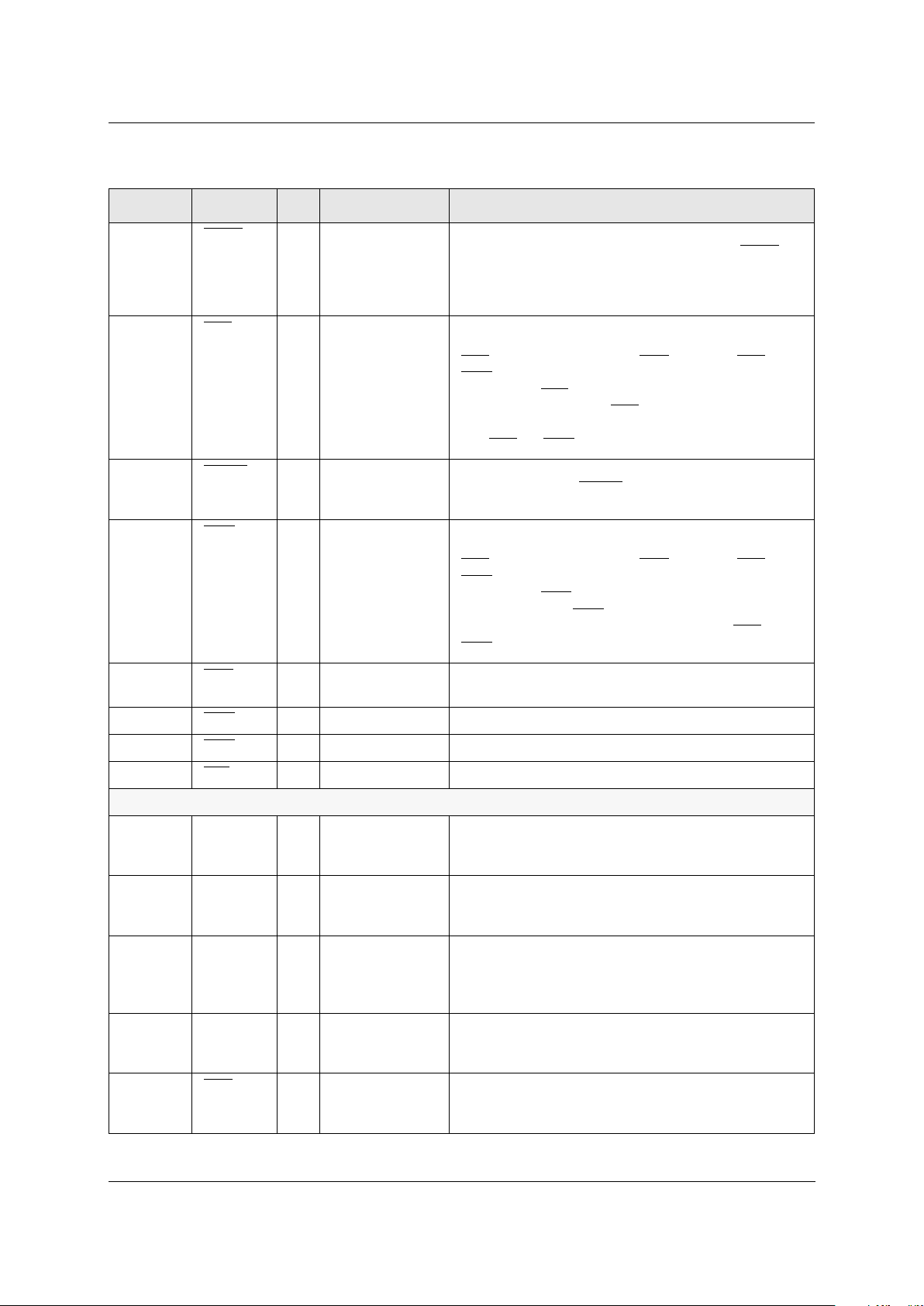

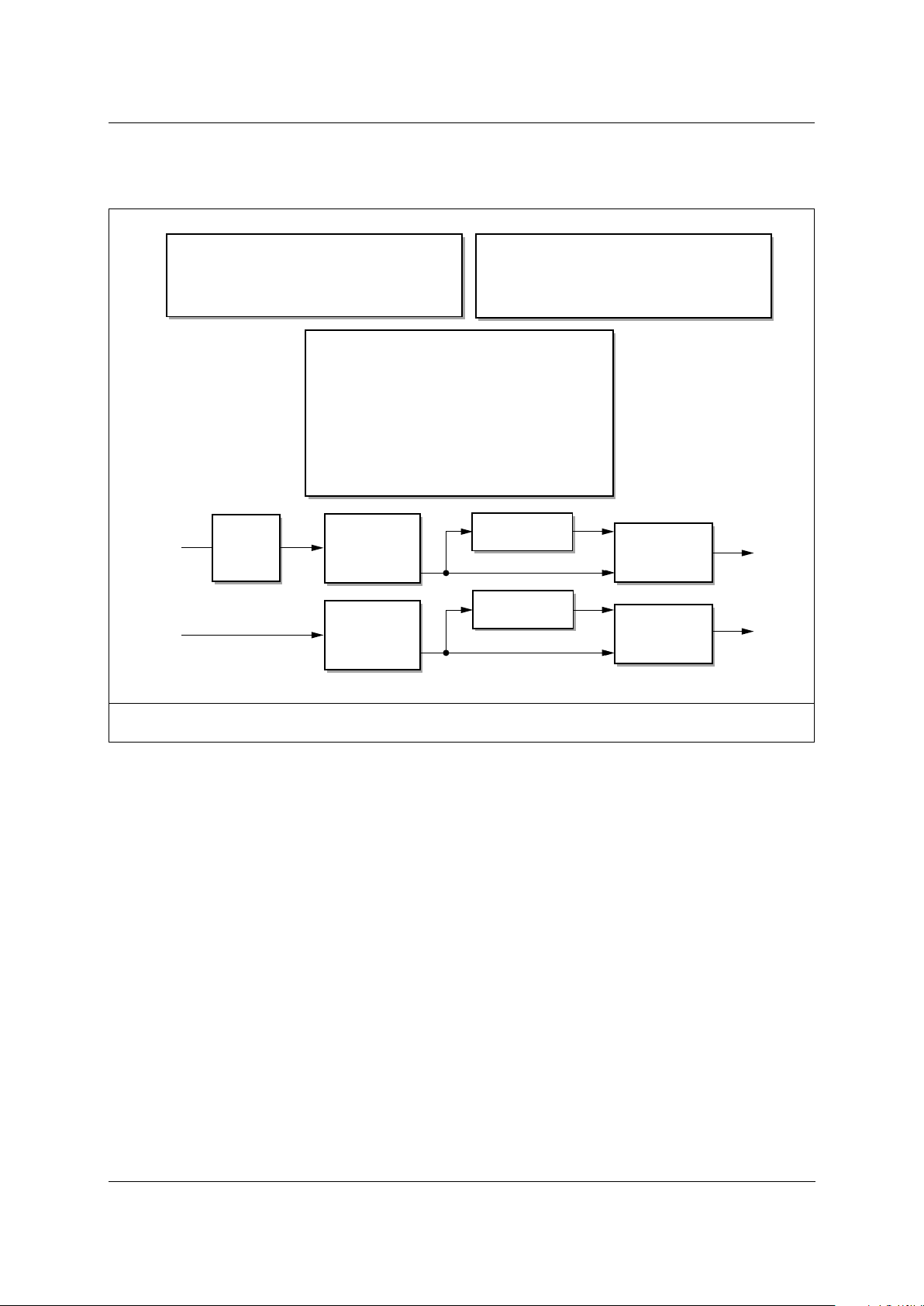

Figure 1-1 illustrates a block diagram of the Fusion 878A, and Figure 1-2

illustrates a detailed block diagram of the decoder and scaler sections of the

Fusion 878A.

Table 1-1. Audio/Video Capture Product Family

All Features of the Bt848A, Plus: CN878A

Mono line level and MIC level audio capture x

Mono TV audio x

ACPI Support x

1.0 Product Overview Fusion 878A

1.1 Functional Overview PCI Video Decoder

1-2 Conexant 100600B

Figure 1-1. Fusion 878A Detailed Block Diagram

I2S

Video

Decoder

Video

Scaler

YCrCb 4:2:2, 4:1:1

CSC/Gamma

8-Bit Dither

MUX

FIFOs

:

Y 70x36

Cb: 35x36

:

Cr 35x36

# DWORDs

DMA Controller

PCI Initiator

GPIO

I

2

C Master

Analog

Video

Video Data Format Converter

Local Registers

Wr

Instr Data

Rd

PCI

Bus

DMA Controller PCI Initiator

Instruction

Queue

Address Generator

FIFO Data MUX

PCI

Arbiter

Audio

Decoder

FIFO

35x36

Analog

Audio

Digital

Audio

AD MUX

PCI Target

Controller

Local Registers

Wr

Instr Data

Rd

Interrupts

PCI Target

Controller

Interrupts

Digital Video I2C

879A_002

Parity

Generator

AD MUX

Parity

Generator

PCI

Config

Registers

PCI

Config

Registers

Format

Address Generator

FIFO Data MUX

Instruction

Queue

Fusion 878A 1.0 Product Overview

PCI Video Decoder

1.1 Functional Overview

100600B Conexant 1-3

Figure 1-2. Fusion 878A Audio/Video Decoder and Scaler Block Diagram

Composite 1

Composite 2

Composite 3

Composite/S-Video (Y)

S-Video (C)

CIN

AGCCAP

REFP

XTO

XTI

STV TV-Audio

SFM Radio-Audio

SML Mic or Line-Level

Audio

ADATA

ALRCK

ASCLK

Digital

Audio (I

2

S)

Y

A/D

C

A/D

AGC

Clocking

Audio

A/D

Audio

Processing

Digital

Audio

Packetizer

Oversampling

Low-Pass Filter

Y/C

Separation

Chroma

Demod

Hue, Saturation,

and Brightness

Adjust

Horizontal and

Vertical Filtering

and Scaling

Video Data

Format Converter

Audio FIFO

879A_003

1.0 Product Overview Fusion 878A

1.2 Detailed Features PCI Video Decoder

1-4 Conexant 100600B

1.2 Detailed Features

1.2.1 Video Capture

The Fusion 878A integrates an NTSC/PAL/SECAM composite and S-Video

decoder, scaler, DMA controller, and PCI Bus master on a single device. The

Fusion 878A can place video data directly into host memory for video capture

applications and into a target video display frame buffer for video overlay

applications. As a PCI initiator, the Fusion 878A can take control of the PCI bus

as soon as it is available, thereby avoiding the need for on-board frame buffers.

The Fusion 878A contains a pixel data FIFO to decouple the high speed PCI bus

from the continuous video data stream.

The video data input may be scaled, color translated, and burst-transferred to a

target location on a field basis. This allows for simultaneous preview of one field

and capture of the other field. Alternatively, the Fusion 878A is able to capture

both fields simultaneously or preview both fields simultaneously. The fields may

be interlaced into memory or sent to separate field buffers.

1.2.2 Audio Capture

The Fusion 878A can also capture the broadcast audio spectrum over the PCI bus.

This enables system solutions without the use of an analog audio cable. In

addition, the audio capture can be used to implement microphone audio capture

for complete videoconferencing applications.

1.2.3 Analog Video and Digital Camera Capture

The Fusion 878A includes a digital camera port to support digital video capture.

This specification defines the registers and functionality required for

implementing analog video capture support. Most of the analog and digital video

register settings are identical.

In addition to the standard CCIR 656 digital interface, the Fusion 878A can

accept digital video from digital cameras such as the Conexant Quartsight™,

Silicon Vision™, and Logitech™. Internally the digital stream is routed to the

high-quality down-scaler and color adjustment processing. It is then bus-mastered

into system memory or displayed via the graphics frame buffer.

1.2.4 Intel Intercast™ Support

The Fusion 878A fully supports the Intel Intercast technology. Intel Intercast

technology combines the programming of television and the Internet on the PC.

Fusion 878A 1.0 Product Overview

PCI Video Decoder

1.2 Detailed Features

100600B Conexant 1-5

1.2.5 Video DMA Channels

The Fusion 878A enables separate destinations for the odd and even fields, each

controlled by a pixel RISC instruction list. This instruction list is created by the

Fusion 878A device driver and placed in the host memory. The instructions

control the transfer of pixels to target memory locations on a byte resolution

basis. Complex clipping can be accomplished by the instruction list, blocking the

generation of PCI bus cycles for pixels that are not to be seen on the display.

The DMA channels can be programmed on a field basis to deliver the video

data in packed or planar format. In packed mode, YCrCb data is stored in a single

continuous block of memory. In planar mode, the YCrCb data is separated into

three streams which are burst to different target memory blocks. Having the video

data in planar format is useful for applications where the data compression is

accomplished via software and the CPU.

1.2.6 Audio DMA Channels

The audio channel delivers 8-bit or 16-bit digital samples of a digital

frequency-multiplexed analog signal to system memory in packets of DWORDs.

A RISC program controls the audio DMA Program Initiator. The flow of audio

data and audio RISC instructions is completely independent and asynchronous to

the flow of video data and video RISC instructions.

Since the audio data path operates in continuous transfer mode (no sync gaps),

both the analog and the digital audio inputs can be used for other data capture

applications. The analog input offers 360 kHz usable BW at 8 effective bits or 100

kHz usable BW at 12 effective bits. The digital input offers up to 20 Mbps for the

parallel mode and 40 Mbps for the serial mode.

The audio DMA channel controller is similar to the video DMA controller in

that it supports packed mode RISC instructions. It also only interfaces to one

35 x 36 FIFO and its associated 6-bit DWORD counter.

The audio PCI initiator is identical to the video PCI initiator; they have the

same DMA controller interface and the same support for interrupts and

configuration space. Since the video and audio initiators are independent, each

can handle retries without inhibiting the other. Thus, the audio function can

initiate transfers to the host bridge even when a GFX target is retrying the video

function.

The audio PCI target is similar to the video PCI target with respect to

interrupts, configuration space, memory-mapped registers, and parity error

checking. The main difference in audio is that all of the memory-mapped

registers remain within the PCI clock and 32-bit interface domain. There is no

register interface to the audio clock domain. Thus, this target never issues a

disconnect or a retry.

1.2.7 Data Transport Engine

The Fusion 878A data transport engine operates in instruction mode. Video data

and audio data are delivered over the PCI bus under independent control.

1.0 Product Overview Fusion 878A

1.2 Detailed Features PCI Video Decoder

1-6 Conexant 100600B

1.2.8 PCI Bus Interface

The Fusion 878A is designed to efficiently utilize the available 132 Mbps PCI

bus. The 32-bit DWORDs are output on the PCI bus with the appropriate image

data under the control of the DMA channels. The video stream consumes bus

bandwidth with average data rates varying from 44 Mbps for full size 768 x 576

PAL RGB32, to 4.6 Mbps for NTSC CIF 320 x 240 RGB16, to 0.14 Mbps for

NTSC ICON 80 x 60 8-bit mode.

The pixel instruction stream for the DMA channels consumes a minimum of

0.1 Mbps. The Fusion 878A provides the means for handling the bandwidth

bottlenecks caused by slow targets and long bus access latencies that can occur in

some system configurations. To overcome these system bottlenecks, the Fusion

878A gracefully degrades and recovers from FIFO overruns to the nearest pixel in

real time.

1.2.9 UltraLock™

The Fusion 878A employs a proprietary technique known as UltraLock to lock to

the incoming analog video signal. It always generates the required number of

pixels per line from an analog source in which line length can vary by as much as

a few microseconds. UltraLock’s digital locking circuitry enables the

VideoStream decoders to lock on to video signals quickly and accurately,

regardless of their source. Since the technique is completely digital, UltraLock

can recognize unstable signals caused by VCR head switches or any other

deviation and adapt the locking mechanism to accommodate the source.

UltraLock uses nonlinear techniques that are difficult, if not impossible, to

implement in genlock systems. And unlike linear techniques, it adapts the locking

mechanism automatically.

1.2.10 Scaling and Cropping

The Fusion 878A can reduce the video image size in both horizontal and vertical

directions independently, using arbitrarily selected scaling ratios. The X and Y

dimensions can be scaled down to one-sixteenth of the full resolution. Horizontal

scaling is implemented with a 6-tap interpolation f ilter, while up to 5-tap

interpolation is used for vertical scaling with a line store.

The video image can be arbitrarily cropped by reducing the number of active

scan lines and active horizontal pixels per line.

The Fusion 878A supports a temporal decimation feature that reduces video

bandwidth. This is accomplished by allowing frames or fields to be dropped from

a video sequence at fixed but arbitrarily selected intervals.

1.2.11 Input Interface

Analog video signals are input to the Fusion 878A via a four-input multiplexer.

The multiplexer can select between four composite source inputs or between three

composite and a single S-Video input source. When an S-Video source is input to

the Fusion 878A, the luma component is fed through the input analog multiplexer,

and the chroma component feeds directly into the C input pin. An AGC circuit

enables the Fusion 878A to compensate for non-standard amplitudes in the analog

signal input.

Fusion 878A 1.0 Product Overview

PCI Video Decoder

1.2 Detailed Features

100600B Conexant 1-7

The clock signal interface consists of a pair of pins that connect to a 28.63636

MHz (8 × NTSC Fsc) crystal. Either fundamental or third harmonic crystals may

be used. Alternatively, CMOS oscillators may be used.

1.2.12 GPIO Port

The Fusion 878A provides a 24-bit GPIO bus. This interface can be used to input

or output up to 24 general purpose I/O signals. Alternatively, the GPIO port can

be used as a means to input video data. For example, the Fusion 878A can input

the video data from an external digital camera and bypass the Fusion 878A’s

internal video decoder block.

1.2.13 Vertical Blanking Interval Data Capture

The Fusion 878A provides a complete solution for capturing and decoding VBI

data. The Fusion 878A can operate in a VBI Line Output Mode, in which the VBI

data is only captured during select lines. This mode of operation enables

concurrent capture of VBI lines containing ancillary data and normal video image

data.

In addition, the Fusion 878A supports a VBI Frame Output Mode in which

every line in the video frame istreated as if it were a VBI line. This mode of

operation is designed for use with still frame capture/processing applications.

1.2.14 I2C Interface

The Fusion 878As I2C interface supports both 99.2 kHz timing transactions and

396.8 kHz, repeated start, multi-byte sequential transactions. As an I

2

C master,

Fusion 878A can program other devices on the video card, such as a TV tuner as

long as the device address is known. The Fusion 878A supports multi-byte

sequential reads (more than one transaction) and multi-byte write transactions

(greater than three transactions), which enable communication to devices that

support auto-incremental internal addressing.

1.2.15 HDTV Support

Fusion 878A has the ability to accept either serial or parellel HDTV data and

deliver that data to the host. Serial and parellel inputs both use the audio DMA

channel to transfer the HDTV MPEG packets to the host.

Serial HDTV streams may be input to the high speed serial port, which shares

pins with the digital audio (I

2

S) port. Fusion 878A will accept serial HDTV

streams at up to 40 Mbps.

Parellel HDTV data may be input to the GPIO port in asychronous parallel

mode at up to 20 Mbps.

1.0 Product Overview Fusion 878A

1.3 Pin Descriptions PCI Video Decoder

1-8 Conexant 100600B

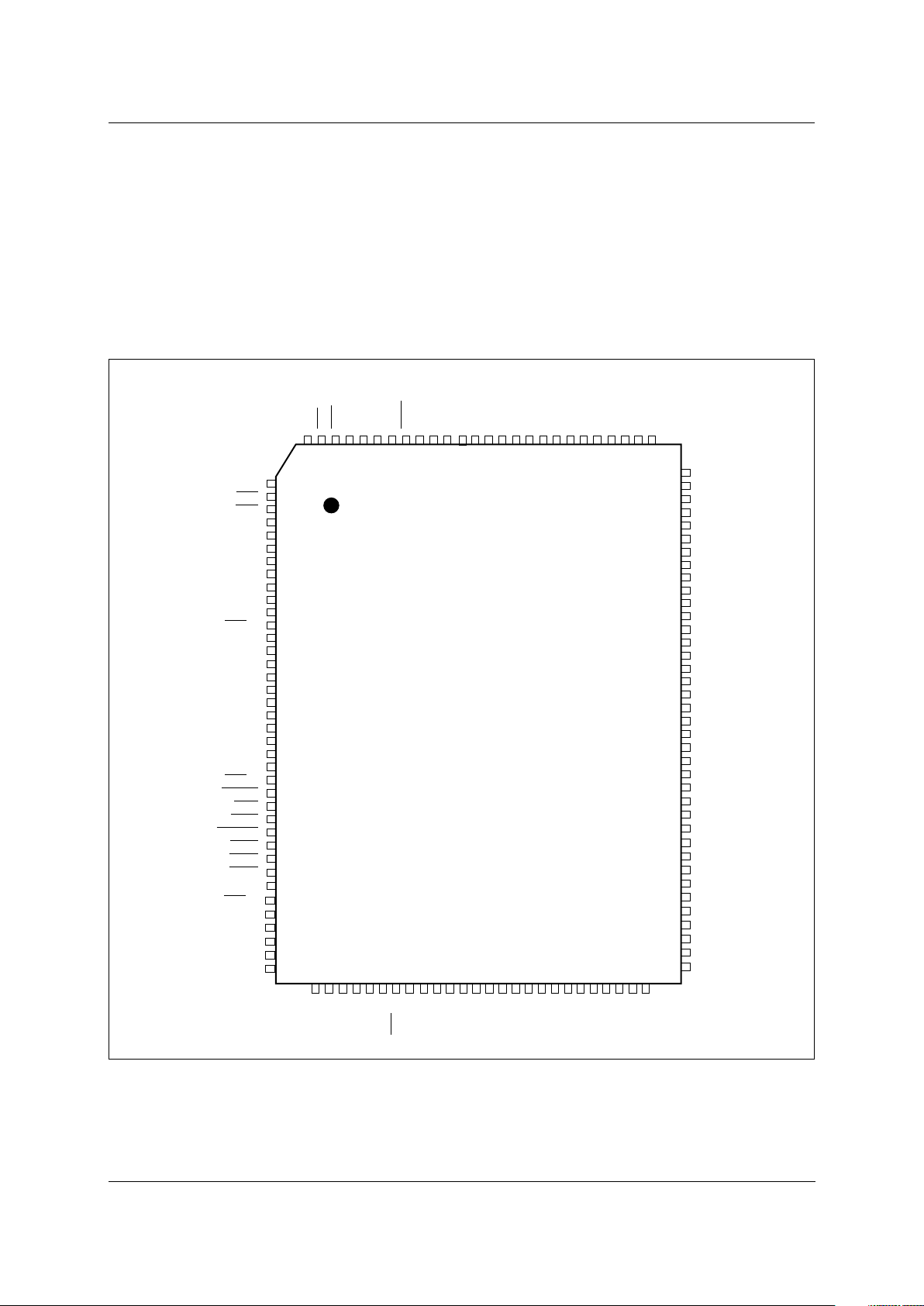

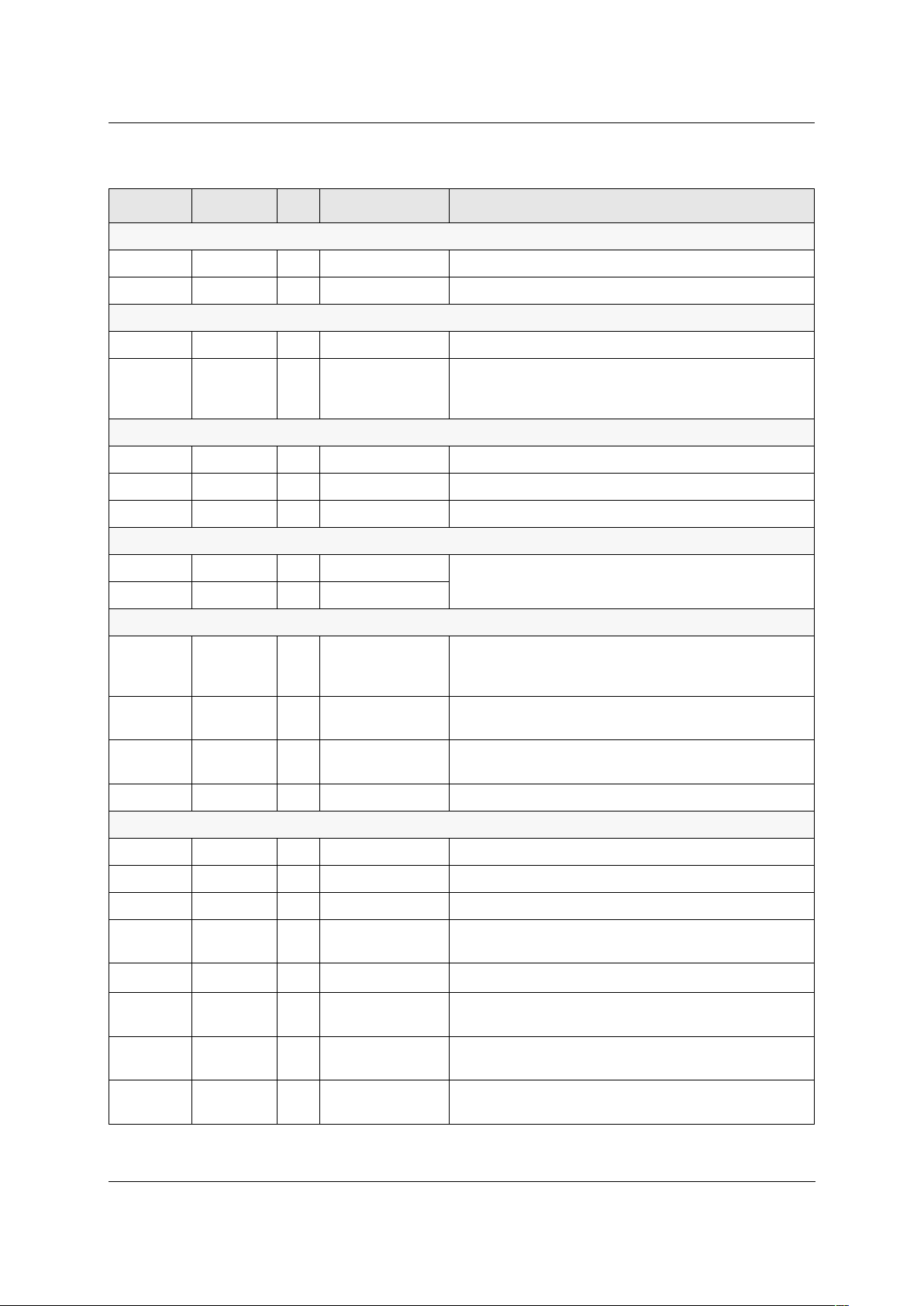

1.3 Pin Descriptions

Figure 1-3 displays the pinout diagram. Tabl e 1- 2 provides a description of pin

functions grouped by common function.

Figure 1-3. Fusion 878A Pinout Diagram

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

118

119

120

121

122

123

124

125

126

127

128

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

VDD

GNT

REQ

AD[31]

AD[30]

AD[29]

AD[28]

AD[27]

AD[26]

AD[25]

AD[24]

C

BE[3]

IDSEL

AD[23]

AD[22]

AD[21]

AD[20]

AD[19]

VDD

GND

AD[18]

AD[17]

AD[16]

C

BE[2]

FRAME

IRDY

TRDY

DEVSEL

STOP

PERR

SERR

PA R

GND

RST

INTA

TDI

TDO

TMS

TCK

TRST

MUX3

AGND

MUX2

MUX1

VAA

MUX0

AGND

REFP

AGCCAP

VAA

CIN

AGND

VCCAP

RBIAS

VCOMO

VCOMI

VRXP

VRXN

VBB

STV

BGND

SFM

BGND

C

BE[1]

AD[15]

AD[14]

AD[13]

AD[12]

VDD

GND

CLK

AD[11]

AD[10]

AD[09]

AD[08]

C

BE[0]

AD[07]

AD[06]

AD[05]

AD[04]

AD[03]

AD[02]

AD[01]

AD[00]

VDD

GND

GPIO[23]

GPIO[22]

GPIO[21]

GPIO[20]

GPIO[19]

GPIO[18]

XTI

XTO

GND

SMXC

VBB

SML

GND

VDD

SDA

SCL

ASCLK

GPIO[01]

GPIO[02]

GPIO[03]

GPIO[04]

GPIO[05]

GPIO[06]

GPIO[07]

GPIO[08]

GPIO[09]

GPIO[10]

GPIO[11]

GND

VDD

GPIO[12]

GPIO[13]

GPIO[14]

GPIO[15]

GPIO[16]

GPIO[17]

GPCLK

VDD

ALRCK

A DATA

GPIO[00]

Fusion 878A

117

VAA

879A_004

Fusion 878A 1.0 Product Overview

PCI Video Decoder

1.3 Pin Descriptions

100600B Conexant 1-9

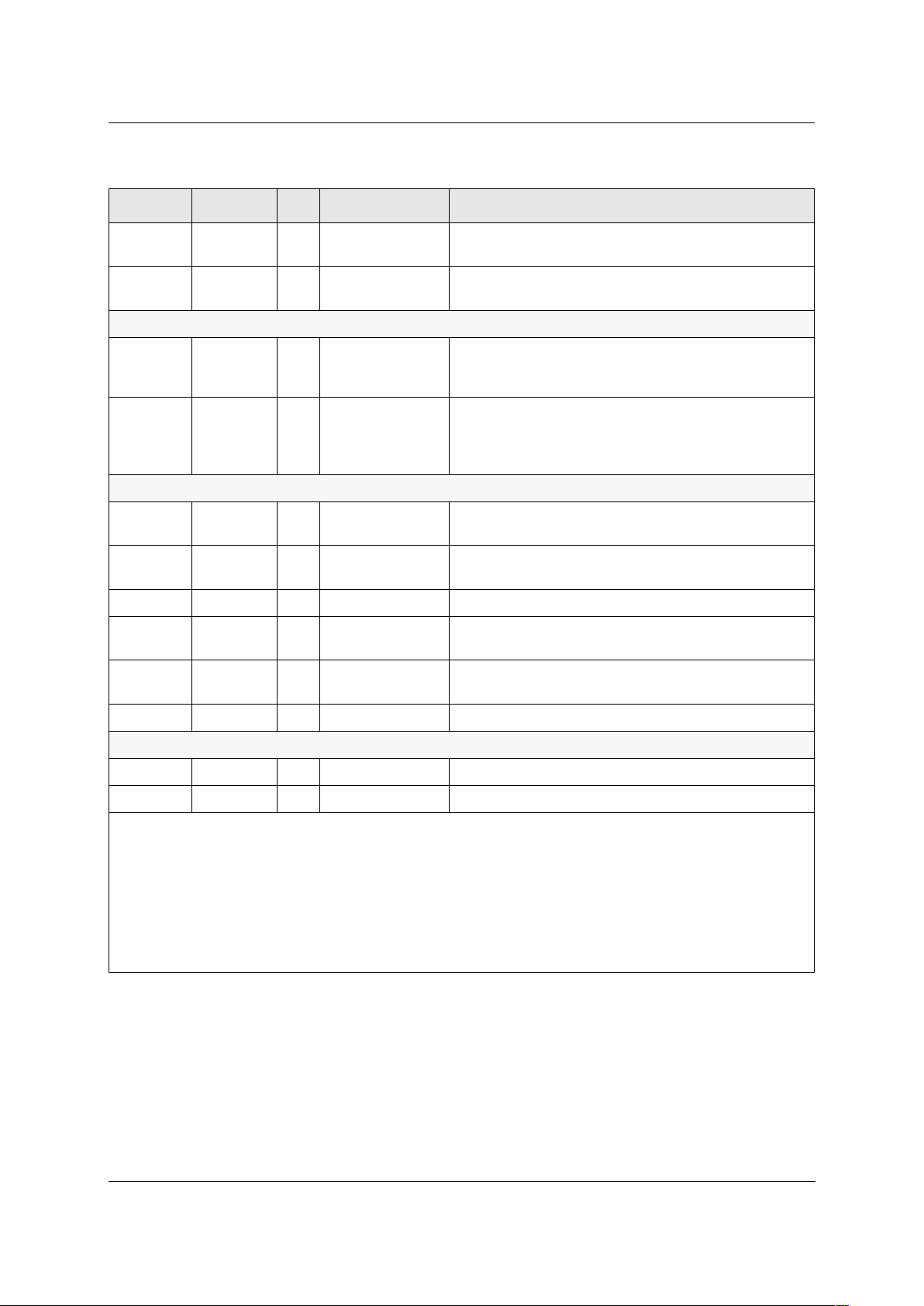

Table 1-2. Pin Descriptions Grouped by Pin Function (1 of 4)

Pin # Pin Name I/O Signal Description

PCI Interface (50 Pins)

(1)

40 CLK I Clock This input provides timing for all PCI transactions. All PCI

signals except RST

and INTA are sampled on the rising edge of

CLK, and all other timing parameters are defined with respect to

this edge. The Fusion 878A supports a PCI clock of up to

33.3333 MHz.

127 RST

I Reset This input three-states all PCI signals asynchronous to the CLK

signal.

3REQ

O Request Agent desires bus.

2GNTI Grant Agent granted bus.

13 IDSEL I Initialization

Device Select

This input is used to select the Fusion 878A during

configuration read and write transactions.

4–11,

14–18,

21–23,

34–37,

41–44,

46–53

AD[31:0] I/O Address/Data These three-state, bidirectional I/O pins transfer both address

and data information. A bus transaction consists of an address

phase followed by one or more data phases for either read or

write operations.

The address phase is the clock cycle in which FRAME

is first

asserted. During the address phase, AD[31:0] contains a byte

address for I/O operations and a DWORD address for

configuration and memory operations. During data phases,

AD[7:0] contains the least significant byte and AD[31:24]

contains the most significant byte.

Read data is stable and valid when TRDY

is asserted and

write data is stable and valid when IRDY

is asserted. Data is

transferred during the clocks when both TRDY

and IRDY are

asserted.

12, 24,

33, 45

CBE

[3:0] I/O Bus

Command/Byte

Enable

These three-state, bidirectional I/O pins transfer both bus

command and byte enable information. During the address

phase of a transaction, CBE

[3:0] signals contain the bus

command. During the data phase, CBE

[3:0] are used as byte

enables. The byte enables are valid for the entire data phase and

determine which byte lanes carry meaningful data. CBE

[3]

refers to the most significant byte and CBE

[0] refers to the least

significant byte.

32 PAR I/O Parity This three-state, bidirectional I/O pin provides even parity

across AD[31:0] and CBE

[3:0]. This means that the number of

1s on PAR, AD[31:0], and CBE

[3:0] equals an even number.

PAR is stable and valid one clock after the address phase. For

data phases, PAR is stable and valid one clock after either TRDY

is asserted on a read, or IRDY

is asserted on a write. Once valid,

PAR remains valid until one clock after the completion of the

current data phase. PAR and AD[31:0] have the same timing,

but PAR is delayed by one clock. The target drives PAR for read

data phases; the master drives PAR for address and write data

phases.

1.0 Product Overview Fusion 878A

1.3 Pin Descriptions PCI Video Decoder

1-10 Conexant 100600B

25 FRAME I/O Cycle Frame This sustained, three-state signal is driven by the current master

to indicate the beginning and duration of an access. FRAME

is

asserted to signal the beginning of a bus transaction. Data

transfer continues throughout assertion. At de-assertion, the

transaction is in the final data phase.

26 IRDY

I/O Initiator Ready This sustained, three-state signal indicates the bus master’s

readiness to complete the current data phase.

IRDY

is used in conjunction with TRDY. When both IRDY and

TRDY

are asserted, a data phase is completed on that clock.

During a read, IRDY

indicates when the initiator is ready to

accept data. During a write, IRDY

indicates when the initiator

has placed valid data on AD[31:0]. Wait cycles are inserted until

both IRDY

and TRDY are asserted together.

28 DEVSEL

I/O Device Select This sustained, three-state signal indicates device selection.

When actively driven, DEVSEL

indicates the driving device has

decoded its address as the target of the current access.

27 TRDY

I/O Target Ready This sustained, three-state signal indicates the target’s

readiness to complete the current data phase.

IRDY is used in conjunction with TRDY. When both IRDY and

TRDY

are asserted, a data phase is completed on that clock.

During a read, TRDY

indicates when the target is presenting

data. During a write, TRDY

indicates when the target is ready to

accept the data. Wait cycles are inserted until both IRDY

and

TRDY

are asserted together.

29 STOP I/O Stop This sustained, three-state signal indicates the target is

requesting the master to stop the current transaction.

30 PERR

I/O Parity Error Report data parity error.

31 SERR O System Error Report address parity error. Open drain.

126 INTA O Interrupt A This signal is an open drain interrupt output.

JTAG (5 Pins)

122 TCK I Test Clock Used to synchronize all JTAG test structures. When JTAG

operations are not being performed, this pin must be driven to a

logical low.

123 TMS I Test Mode Select JTAG input pin whose transitions drive the JTAG state machine

through its sequences. When JTAG operations are not being

performed, this pin must be left floating or tied high.

125 TDI I Test Data Input JTAG pin used for loading instructions to the TAP controller or

for loading test vector data for boundary-scan operation. When

JTAG operations are not being performed, this pin must be left

floating or tied high.

124 TDO O Test Data Output JTAG pin used for verifying test results of all JTAG sampling

operations. This output pin is active for certain JTAG operations

and will be three-stated at all other times.

121 TRST

I Test Reset JTAG pin used to initialize the JTAG controller. When JTAG

operations are not being performed, this pin must be driven to a

logical low.

Table 1-2. Pin Descriptions Grouped by Pin Function (2 of 4)

Pin # Pin Name I/O Signal Description

Fusion 878A 1.0 Product Overview

PCI Video Decoder

1.3 Pin Descriptions

100600B Conexant 1-11

I2C Interface (2 Pins)

90 SCL I/O Serial Clock Bus clock, output open drain.

91 SDA I/O Serial Data Bit Data or Acknowledge, output open drain.

General Purpose I/O (25 Pins)

66 GPCLK I/O GP Clock Video clock. Internally pulled up to VDD.

56–61,

67–72,

75–86

GPIO[23:0] I/O General Purpose

I/O

Fusion 878A pin decoding in normal mode. Pins pulled up to

VDD. For additional information, see Tables 3-3 and 3-5.

Digital Audio Input/Audio Test Signals (3 Pins)

87 ADATA I/O Audio Data Bit serial data.

88 ALRCK I/O Audio Clock Left/right framing clock.

89 ASCLK I/O Audio Serial Clock Bit serial clock.

Reference Timing Interface Signals (2 Pins)

62 XTI I A 28.63636 MHz crystal can be tied directly to these pins, or a

single-ended oscillator can be connected to XTI.

63 XTO O

Video Input Signals (7 Pins)

114, 116,

118, 120

MUX[0:3] I Analog composite video inputs to the on-chip 4:1 analog

multiplexer. Unused inputs should be tied to AGND. The output

of the MUX is direct-coupled to Y-A/D.

112 REFP A The top of the reference ladder for the video A/Ds. Connect to a

0.1 µF decoupling capacitor to AGND.

111 AGCCAP A The AGC time-constant control capacitor node. Must be

connected to a 0.1µF capacitor to AGND.

109 CIN I Analog chroma input to the C-A/D.

TV/Radio Audio Input Signals (10 Pins)

100 STV I TV sound input from TV tuner.

98 SFM I FM sound input from FM tuner.

94 SML I MIC/line input.

96 SMXC A Audio MUX anti-alias filter RC node. Connect through 68 pF

capacitor to BGND.

106 RBIAS A

Connection point for external bias 9.53 k

Ω 1% resistor.

105 VCOMO A Common mode voltage for the audio analog circuitry. This pin

should be connected to an external filtering 0.1 µF capacitor.

104 VCOMI A Common mode voltage for the audio analog circuitry. This pin

should be connected to an external filtering 0.1 µF capacitor.

107 VCCAP A Audio analog voltage compensation capacitor. This pin should

be connected to an external filtering 0.1 µF capacitor.

Table 1-2. Pin Descriptions Grouped by Pin Function (3 of 4)

Pin # Pin Name I/O Signal Description

1.0 Product Overview Fusion 878A

1.3 Pin Descriptions PCI Video Decoder

1-12 Conexant 100600B

103 VRXP A Audio input circuitry reference voltage. This pin should be

connected to an external filtering 0.1 µF capacitor.

102 VRXN A Audio input circuitry reference voltage. This pin should be

connected to an external filtering 0.1 µF capacitor.

I/O and Core Power and Ground (14 Pins)

1, 19, 38,

54, 65 73,

92

VDD P Digital outputs power supply.

20, 39,

55, 64,

74, 93,

128