CONEX CX74036 Datasheet

CX74036

IS-136 Receive RF IC for TDMA and AMPS Applications

Conexant’s CX74036 receive RF IC is an advanced, highly integrated and high

performance, triple-mode, dual-band IC for IS-136 compliant cellular radio

applications and is designed in an advanced 28 GHz Ft BiCMOS process. In the

800 MHz cellular band, the CX74036 is designed to operate in both the Time

Division Multiple Access (TDMA) mode and Advanced Mobile Phone System

(AMPS) mode. In the 1900 MHz Personal Communications System (PCS) band,

the device operates in the TDMA mode.

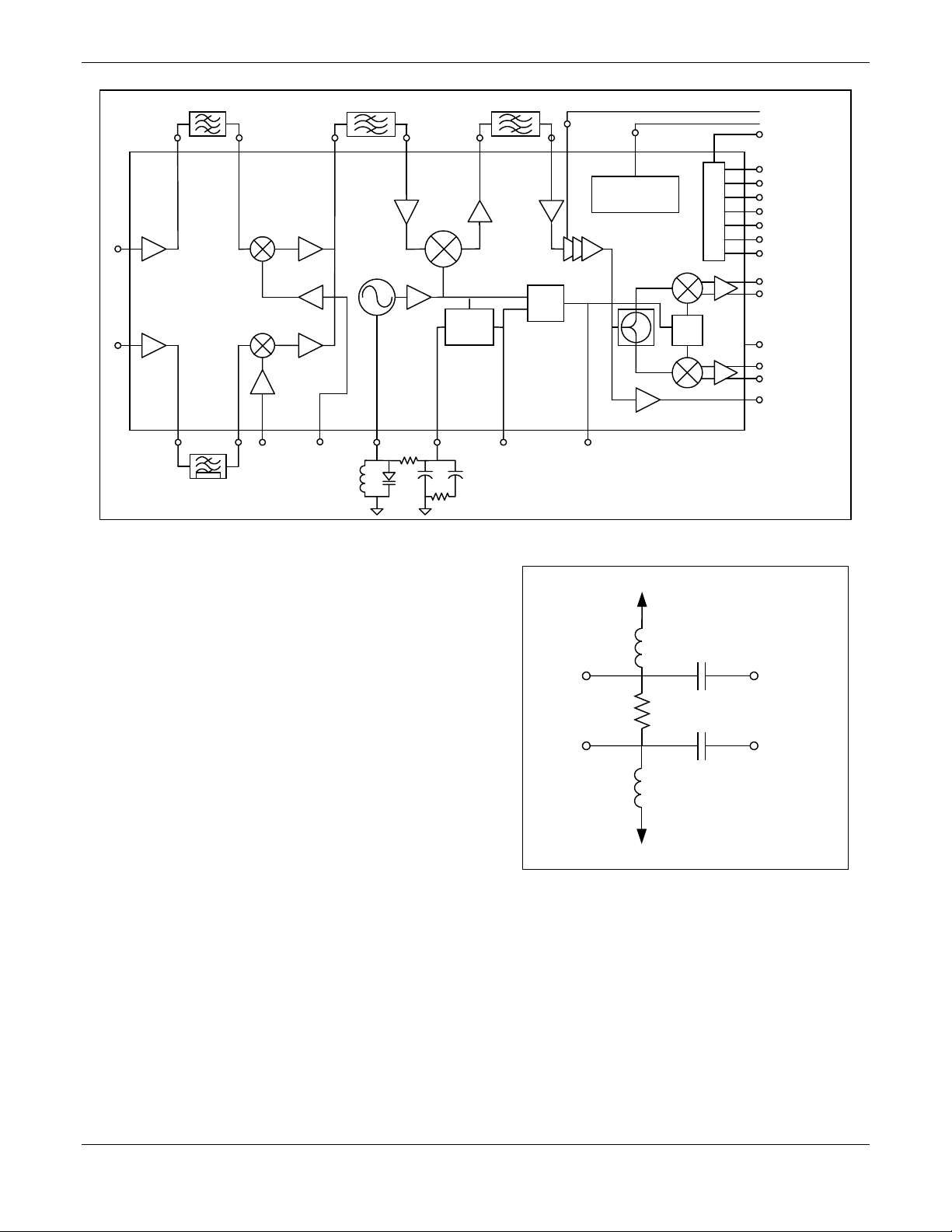

The CX74036 embodies all the necessary functions for a radio receiver system

except for the RF and Intermediate Frequency (IF) filters and RF Local Oscillator

(LO) sources. The device front-end section has two Low Noise Amplifier (LNA) and

mixer pairs, one for the 800 MHz band and the other for the 1900 MHz band. A

common path is taken from the first IF mixer output to the demodulator output.

The CX74036 48-pin, 7x7 Land Grid Array (LGA) package pin configuration is

shown in Figure 1. A block diagram of the CX74036 is shown in Figure 2.

LNA_OH

LNA_OL

VCC2_LNAH

VCC2_LNAL

VCC1_LNA

NC2

LNA_INL

LNA_INH

NC1

Features

• Front-end to baseband in one IC

• Inphase and Quadrature (I/Q) demodulator

• 3 V supply operation

• Low current consumption

• LNA gain switch with current reduction

• IF LO synthesizer with Voltage Controlled

Oscillator (VCO) (requires external tank)

• 70 dB Variable Gain Amplifier (VGA) dynamic

range

• Low Noise Figure (NF) and high 3rd order Input

Intercept Point (IIP3) mixers

Applications

• Cellular and/or PCS band phones

• TDMA and/or AMPS mode phones

• Portable battery powered radio equipment

EXT_LO

IF_O +

Data Sheet

LNA_G

MXIH

MIXIL

BAND

CHIP_EN

LOIH

LOIL

VCC_MX

STANDBY

IQ/IF

MXOUT+

MXOUT-

MX2I+

1

2

3

4

5

6

7

8

9

10

11

12

13

MX2I-

45464748 44 43 42 41 40 39 38

17161514 18 19 20 21 22 23 24

Vvga

VCC_IF

MX2OUT

IFBYPASS

VGAI-

VCC_VGA

VGAI+

FB_CAP

37

36

35

34

33

32

31

30

29

28

27

26

25

CLK

LATCH_EN

101105A-1_082500

Figure 1. CX74036 48-Pin, 7x7 LGA Package Pin Configuration

Conexant – Proprietary

Data Subject to Change October 17, 2000

IF_O Q-

Q+

I-

I+

EXT_LOIN

VCC_VCO

VCO-

VCO+

VCC_SYN

LP_FIL

REFIN

DATA

Doc. No. 101105A

CX74036 Receive RF IC

Image Rejection Filter

PCS RF InCell RF In

CX74036

RX RFIC

Cell LO

Image Rejection Filter

1st IF S A W

PCS LO

450 KHz

1st IF L O

÷P

VHF

Synth

19.44 MHz Ext.1.8 MHz

Power

Management

÷ 4

IF Bu ffe r

Vvga

Vcc

Standby

CLK

DATA

EN

LNA Gain

Interface

101105A-2_101200

Band Select

Power Down

VCO/REFIN

I

IQ/

IF

Q

IF Ou t

Figure 2. CX74036 Functional Block Diagram

Technical Description

Low Noise Amplifiers:

independent LNAs for the cellular and PCS bands. The gain of

both LNAs can be switched off to a loss mode via one command

line interface. Only one LNA is powered at any given time.

Control is done by an external band-select control signal. The

input and output matches are external to the chip. The LNAs’

parameters, Noise Figure (NF), and gain are chosen to provide

an excellent balance between system sensitivity and IIP3

requirements to achieve maximum dynamic range. Both LNA

outputs are ported off-chip to allow for image filtering before

being fed to the RF mixer inputs.

RF Mixers:

The mixers are designed to operate with a low LO

input power level of –10 dBm. This eliminates the requirement of

buffer amplifiers for the external VCO. Cellular band mixer high

gain and low NF performance allow for the cellular LNA gain to

be lower, which saves current consumption. Both mixers are

designed to provide high suppression of one-half IF response.

The outputs of both mixers share a common interface path to

the external IF Surface Acoustic Wave (SAW) filter, which

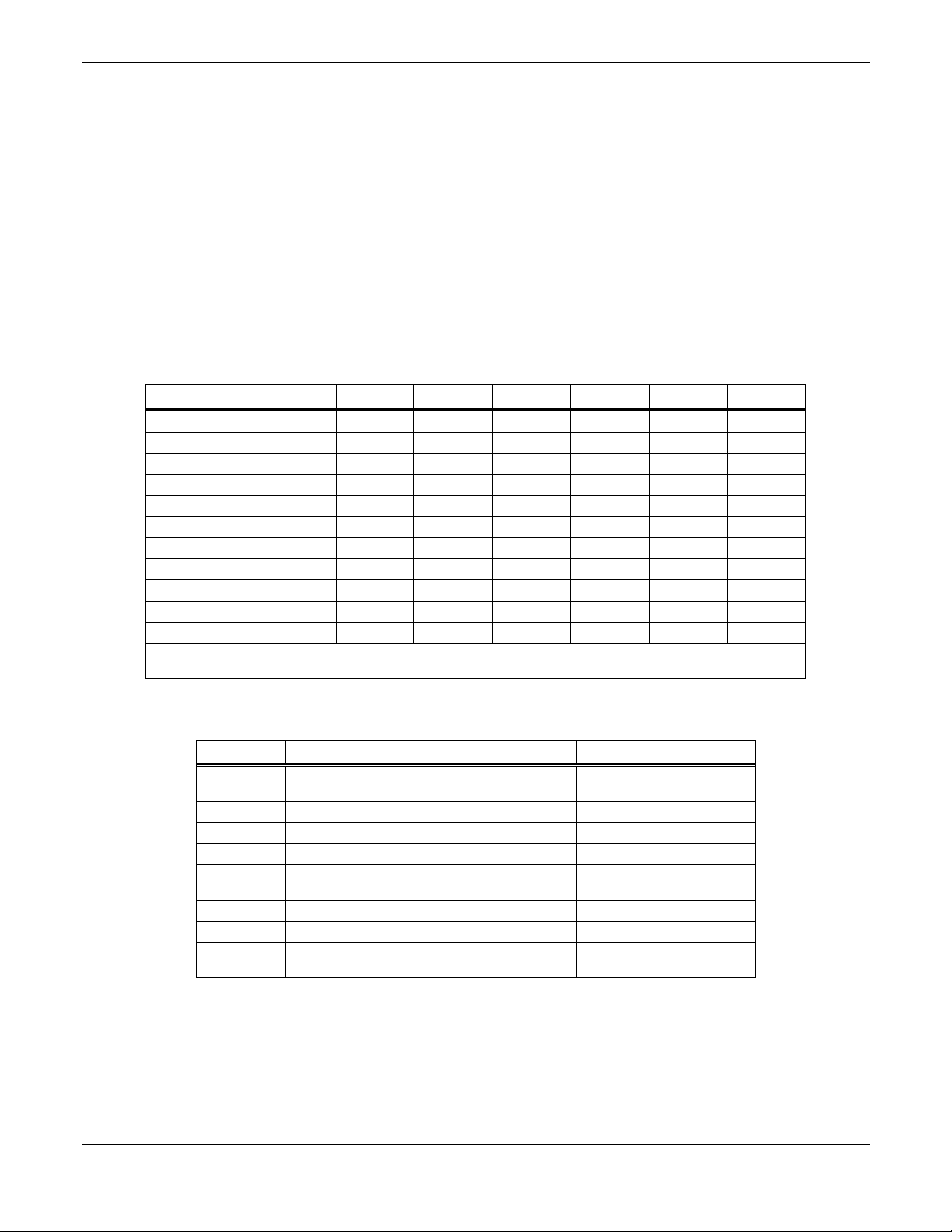

reduces complexity and cost. The RF mixer load configuration is

shown in Figure 3. Inductors can be Surface Mount Multilayer

Chip (SMMC) components.

First IF Mixer

: This mixer begins the common signal path for

both cellular and PCS band modes. Input and output impedance

are set to values that are close to the most commonly available

SAW and ceramic filters.

The CX74036 contains two

Vcc

330 nH

1200 pF

+

RF Mixers

Output

10 K

Ω

to IF S A W

Filter

-

330 nH

Vcc

Figure 3. RF Mixer Load Configuration

Variable Gain Amplifier:

dynamic range to satisfy the high system dynamic range

requirement. With the inclusion of the LNA gain switch, the

system dynamic range is extended to more than 95 dB.

I/Q Demodulator:

Using digital circuitry generates a stable

quadrature LO signal, on-chip direct connection to the VGA

output, on-chip LO source, and lowpass filtering for each

channel. This, in turn, provides a high performance I/Q

demodulator with very low amplitude and phase offsets. The

output signal quality is compatible with many baseband interface

requirements.

1200 pF

101105A-3_101100

The VGA itself provides 70 dB of

2

Conexant – Proprietary

101105A

Data Subject to Change October 17, 2000

Receive RF IC CX74036

VHF Synthesizer and Oscillator:

The on-chip VHF synthesizer

and an oscillator with an added external tank circuit generate

the required second IF LO signal for conversion down to the

standard second IF signal. A programmable divide circuit is also

included to generate the LO for the I/Q demodulator. Depending

on the frequency plan used, an option is provided to inject an

external LO source for the I/Q demodulator.

Control Logic Truth Table.

The Control Logic Truth Table is

shown in Table 1.

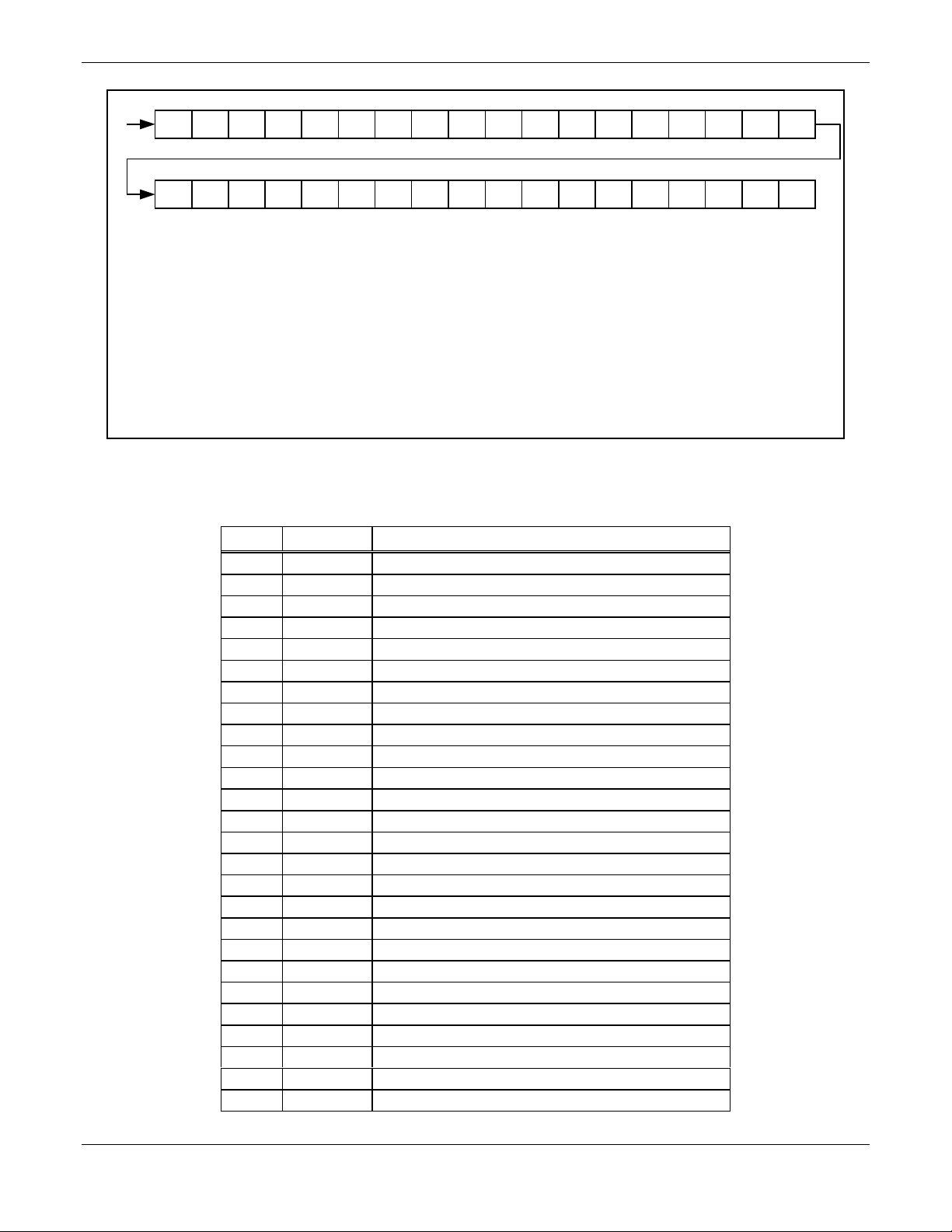

3-Wire Bus Programming.

The 3-wire bus programming data

is included in Table 2. The 3-wire programming data pattern

diagram is shown in Figure 4.

Table 1. Control Logic Truth Table

Mode LNA_G BAND CHIP_EN STANDBY IQ/IF LO_EXT

Active, Low Band, LNA High Gain, IQ101101

Active, High Band, LNA High Gain, IQ111101

Active, Low Band, LNA Low Gain, IQ001101

Active, High Band, LNA Low Gain, IQ011101

Active, Low Band, LNA High Gain, IF101111

Active, High Band, LNA High Gain, IF111111

Active, Low Band, LNA Low Gain, IF001111

Active, High Band, LNA Low Gain, IF011111

Standby --- --- 0 1 --- 1

External LO Mode --- --- 1 --- --- 0

Sleep --- --- 0 0 --- 0

Note.

Synthesizer prescaler and charge pump can be turned off via programming from the 3-wire bus. This mode can be used when driv i ng

the IF Mixer with an external synthesizer.

Electrical and Mechanical Specifications ________________

The signal pin assignments, names, and descriptions are found

in Table 3. Absolute maximum ratings are provided in Table 4,

the recommended operating conditions are specified in Table 5.

Electrical characteristics are shown in Table 6.

Figure 6 provides the 48-Pin, 7x7 LGA package dimensions.

ESD Sensitivity

The CX74036 is a static-sensitive electronic device. Do not

operate or store near strong electrostatic fields. Take proper

ESD precautions.

Table 2. 3-Wire Bus Programming Data

Bit Number Function Programming

00 Select VCO or Reference Input to Programming Counter “0” = Reference Input

01 – 08 Synthesizer M Counter Programming, MB0 – MB7

09 – 12 Synthesizer A Counter Programming, AB0 – AB3

13 – 23 Synthesizer Reference C ounter Programming, RB0 – RB10

24 Charge Pump P olarity “0” = Ground Referenced Varactor

25 – 32 Programmable M Counter Programming, M2B0 – M2B1

33 – 34 Programmable A Counter Programming, A2B0 – A2B1

35 Synthesizer Power down (For External Synt hesizer Mode) “0” = Internal Synthesizer

101075A

October 17, 2000 Data Subject to Change

Conexant – Proprietary

“1” = VCO Input

“1” = VCC Referenced Varactor

“1” = External Synthesizer

3

CX74036 Receive RF IC

MSB

SPD

35

34

A2B033M2B732M2B631M2B5

A2B1

30

M2B4

29

28

M2B227M2B126M2B025CPP

M2B3

24

RB10

23

22

RB821RB720RB619RB5

RB9

18

RB4

17

16

RB215RB114RB013AB3

RB3

12

AB2

11

10

AB009MB708MB607MB5

AB1

06

05

MB4

04

MB203MB102MB001VRS

MB3

00 = First bit shifted in (LSB)

35 = Last bit shifted in (MSB)

VRS = Select VCO or Reference Input to Programmable Counter

"0" = Reference Input

"1" = VCO Input

MB0 - MB 7: Programming for Synthesizer M Counter: MB0 (LSB), MB7 = (MSB)

AB0 - AB3: Programming for Synthesizer A Counter: AB0 (LSB), AB7 = (MS B)

RB0 - RB10: Programming for Synthesizer R Counter: RB0 (LSB), RB10 = (MSB ). CPP = Change P um p Polarity,

"0" = G rou nd R efe ren ce

M2B0 - M2B7: Programming for LO Divider M Counter: M2B0 (LSB), M2B7 = (MSB)

A2B0 - A2B7: Programming for LO Divider A Counter: A2B0 (LSB), A2B1 = (MSB)

SPD = Sy nthesizer Power Down (for External Synthesizer Mode)

"1" = Inte rnal S y n the siz er,

"0"= E x terna l S yn the s ize r

101105A-4_101200

Figure 4. 3-Wire Programming Data Pattern

Table 3. Signal Pin Names and Definitions (1 of 2)

Pin No. Signal Name Description

1 LN A_G LNAs gain control command

2 MXIH 1900 MHz band mixer Input

3 MIXIL 800 MHz band mix er Input

4 BAND 800 MHz/1900 MHz band select command

5 CHIP_EN Chip power down select command

6 LOIH 1900 MHz RF mixer LO input

7 LOIL 800 MHz RF mixer LO input

8VCC_MX RF mixer VCC

9 ST ANDBY Control signal to enable RF LO buffers and VHF synthesi zer

10 IQ/IF I/Q or IF output select command

11 MXOUT+ RF mixer output. Open Collector.

12 MXOUT- RF mixer output. Open Collector.

13 MX2I+ IF mixer input

14 MX2I- IF mixer input

15 VCC_IF IF section VCC

16 IFBYPASS IF mixer bias decoupling

17 MX2OUT IF mixer output

18 Vvga Analog volta ge input for VGA gain control

19 VCC_VGA VGA section VCC

20 VGAI- VGA input

21 VGAI+ VGA input

22 FB_CAP VGA DC feedback fil ter capacitor c onnection

23 LATCH_EN Enable input lin e for internal synthesizer programming

24 CLK Serial clock input line for internal synthesizer programming

25 DATA Serial data input line for internal synt hesizer programming

26 REFIN 19.44 MHz reference oscillator input. Requires VCC/2 DC bias.

LSB

00

4

Conexant – Proprietary

101105A

Data Subject to Change October 17, 2000

Loading...

Loading...