CONEX CN8478EPF, CN8478EBG, CN8474AEPF, CN8474AEBG, CN8472AEPF Datasheet

...

Advance Information

This document contains information on a product under development. The parametric information

contains target parameters that are subject to change.

CN8478/CN8474A/CN8472A/CN8471A

Multichannel Synchronous Communications Controller (MUSYCC™)

Product Description

The CN8478, CN8474A, CN8472A, and CN8471A are advanced Multichannel

Synchronous Communication Controllers (MUSYCCs) that format and deformat up

to 256 (CN8478), 128 (CN8474A), 64 (CN8472A), or 32 (CN8471A) HDLC

channels in a single CMOS integrated circuit. MUSYCC operates at Layer 2 of the

Open Systems Interconnection (OSI) protocol reference model. MUSYCC provides

a comprehensive, high-density solution for processing HDLC channels for

internetworking applications such as Frame Relay, ISDN D-channel signaling,

X.25, Signaling System 7 (SS7), DXI, ISUP, and LAN/WAN data transport. Under

minimal host supervision, MUSYCC manages a linked list of channel data buffers

in host memory by performing Direct Memory Access (DMA) of the HDLC

channels.

MUSYCC interfaces with eight independent serial data streams, such as T1/E1

signals, and then transfers data across the popular 32-bit Peripheral Component

Interface (PCI) bus to system memory at a rate of up to 66 MHz. Each serial

interface can be operated at up to 8.192 MHz. Logical channels can be mapped as

any combination of DS0 time slots to support ISDN hyperchannels (Nx64 kbps) or

as any number of bits in a DS0 for subchanneling applications (Nx8 kbps).

MUSYCC also includes a 32-bit expansion port for bridging the PCI bus to local

microprocessors or peripherals. A JTAG port enables boundary-scan testing to

replace bed-of-nails board testing.

®

Device drivers for Linux, VxWorks

, and pSOS™ operating systems are

available under a no-fee license agreement from Conexant. The device drivers

include C source code and supporting software documents.

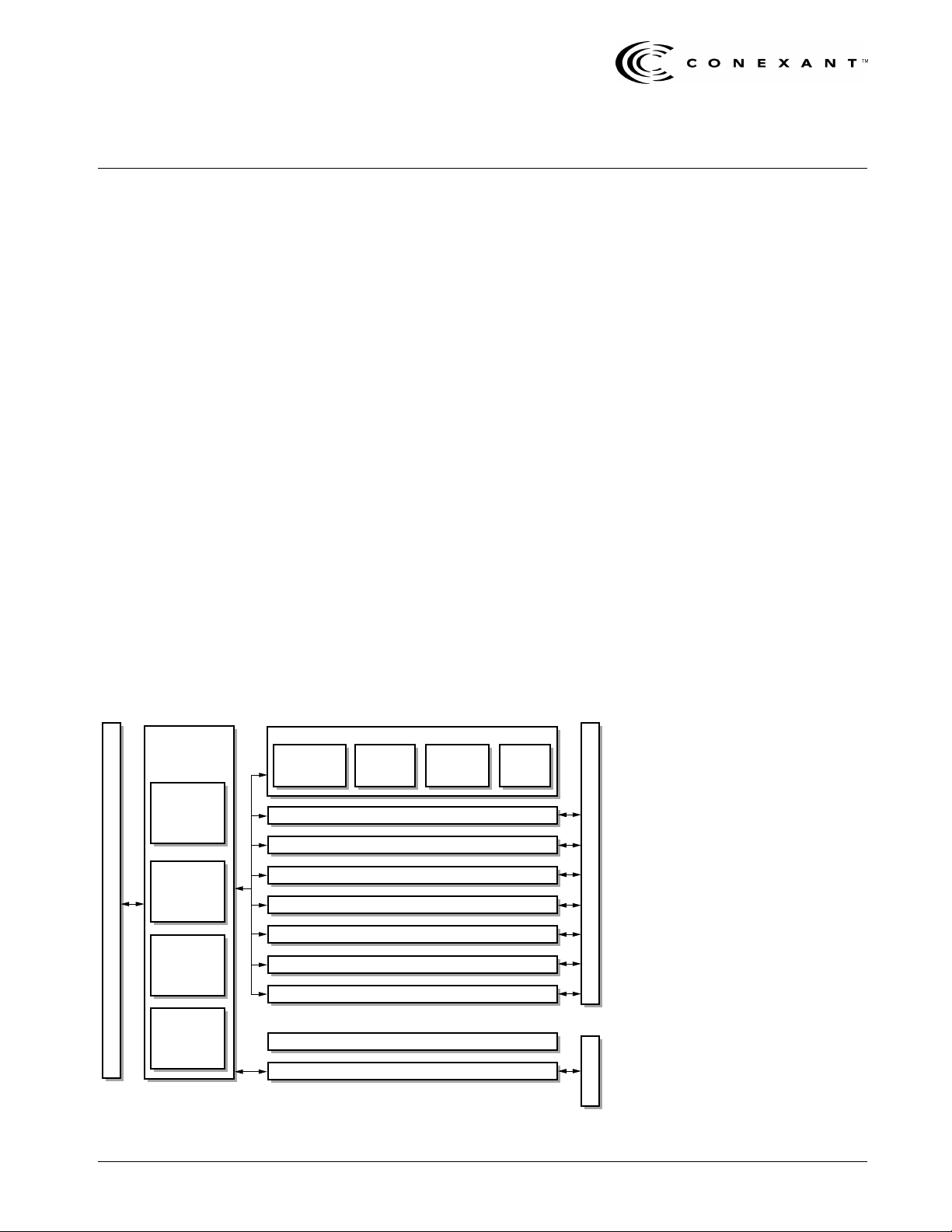

Functional Block Diagram

Channel Group 0 – Serial Interface

DMA

Controller

Interrupt

Controller

Channel Group 1 – Serial Interface

Channel Group 2 – Serial Interface

Channel Group 3 – Serial Interface

Channel Group 4 – Serial Interface

Channel Group 5 – Serial Interface

Channel Group 6 – Serial Interface

Channel Group 7 – Serial Interface

Boundary Scan and Test Access

Expanion Bus Interface

Bit-Level

Processor

Tx/Rx-BLP

Port

Interface

Tx/Rx

PCI Bus

Host

Interface

Device

Configuration

Registers

PCI

Interface

PCI

Configuration

Space

(Function 0)

PCI

Configuration

Space

(Function 1)

Tx/Rx-DMAC

Note: Number of serial interfaces is device-dependent.

Distinguishing Features

• 256-, 128-, 64-, or 32-channel HDLC

controller

• OSI Layer 2 protocol support

• General purpose HDLC (ISO 3309)

– X.25 (LAPB)

– Frame relay (LAPF/ANSI T1.618)

– ISDN D-channel (LAPD/Q.921)

– SS7 support

• 8, 4, 2, or 1 independent serial interfaces

which support

– T1/E1 data streams

– DC to 8.192 Mbps TDM busses

• Configurable logical channels

– Standard DS0 (56, 64 kbps)

– Hyperchannel (Nx64)

– Subchannel (Nx8)

• Per-channel protocol mode selection

– 16-bit FCS mode

– 32-bit FCS mode

– SS7 mode (16-bit FCS)

– Transparent mode (unformatted data)

• Per-channel DMA buffer management

– Linked list data structures

– Variable size transmit/receive FIFO

• Per-channel message length check

– Select no length checking

– Select from two 12-bit registers to

compare message length

– Maximum length 16,384 Bytes

• Direct PCI bus interface

– 32-bit, 66 or 33 MHz operation

– Bus master and slave operation

– PCI Version 2.1

• Local Expansion Bus interface (EBUS)

– 32-bit multiplexed address/data bus

– Burst access up to 64 Bytes

• Low power, 3.3/2.5 V CMOS operation

• JTAG boundary scan access port

• 208-pin PQFP/surface-mount package

•BGA

Serial Data Bus

Applications

• ISDN basic-rate or primary-rate interfaces

• ISDN D-channel controller

•Routers

• Cellular base station switch controller

• CSU/DSU

• Protocol converter

• Packet data switch

• Frame relay switches/Frame Relay Access

Devices (FRAD)

• DXI network interface

Local Bus

• Distributed packet-based communications

system

• Access multiplexer/concentrator

100660E Conexant

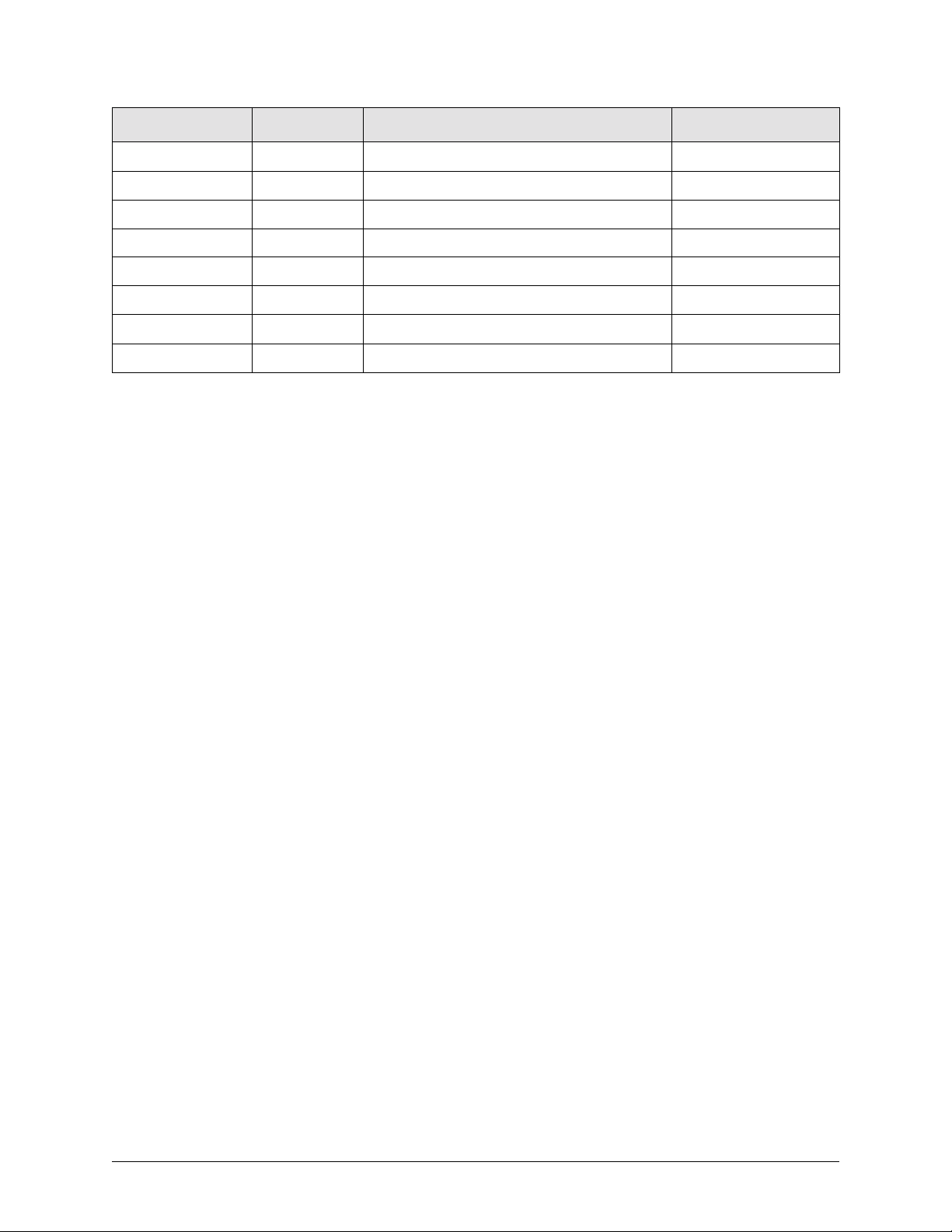

Ordering Information

Model Number Version Package Temperature Range

CN8471AEPF 32-Channel 208-Pin Plastic Quad Flat Pack (PQFP) –40 °C to +85 °C

CN8472AEPF 64-Channel 208-Pin Plastic Quad Flat Pack (PQFP) –40 °C to +85 °C

CN8474AEPF 128-Channel 208-Pin Plastic Quad Flat Pack (PQFP) –40 °C to +85 °C

CN8478EPF 256-Channel 208-Pin Plastic Quad Flat Pack (PQFP) –40 °C to +85 °C

CN8471AEBG 32-Channel 208-Pin Plastic Ball Grid Array –40 °C to +85 °C

CN8472AEBG 64-Channel 208-Pin Plastic Ball Grid Array –40 °C to +85 °C

CN8474AEBG 128-Channel 208-Pin Plastic Ball Grid Array –40 °C to +85 °C

CN8478EBG 256-Channel 208-Pin Plastic Ball Grid Array –40 °C to +85 °C

© 2000, Conexant Systems,Inc.

All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. (“Conexant”) products. These materials are

provided by Conexant as a service to its customers and may b e used for informational purposes only. Conexant assumes no

responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at

any time, without not ice. Conexant makes no commitment to update the information and sha ll have no responsibility whatsoever for

conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as

provided in Conexant’s Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALSARE PROVIDED “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED,RELATING

TO SALE AND/OR USE OF CONEXANT P RODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A

PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF A NY

PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.CONEXANT FURTHER DOES NOT WARRANT THE

ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT,GRAPHICS OR OTHER ITEMS CONTAINED W ITHIN THESE

MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT,INCIDENTAL, OR CONSEQUENTIAL

DAMAGES,INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULTFROM THE USE

OF THESE MATERIALS.

Conexant products are not intended for us e in medical, lifesaving or life sustaining applications. Conexant customers us i ng or selling

Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages

resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant™, the Conexant C symbol, and “What’s Next in Communications

Technologies”™. Product names or services listed in this publication are for identification purposes only, and may be trademarks of

third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant’s Legal Information posted at www.conexant.com,whichis

incorporated by reference.

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and

suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications

engineer.

100660E Conexant

Table of Contents

List of Figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

List of Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

1.0 System Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

2.0 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1 PCI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.1.1 PCI Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.1.2 PCI Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1.3 PCI Configuration Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2 PCI Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.2.1 Function 0 Network Controller—PCI Master and Slave. . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.2.2 Function 1 Expansion Bus Bridge, PCI Slave . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.2.3 PCI Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

2.2.4 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

2.2.5 PCI Bus Parity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2.2.6 PCI Throughput and Latency Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2.2.6.1 PCI Bus Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

2.2.6.2 Latency Computation—Single Dword Access. . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.2.6.3 Latency Computation—Burst Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

3.0 Expansion Bus (EBUS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.1 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.2 Address and Data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.3 Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.4 Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.1.5 Address Duration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.1.6 Data Duration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.1.7 Bus Access Interval . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.1.8 PCI to EBUS Interaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.1.9 Microprocessor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.1.10 Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.1.11 Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

100660E Conexant iii

Table of Contents CN8478/CN8474A/CN8472A/CN8471A

Multichannel Synchronous Communications Controller (MUSYCC™)

4.0 Serial Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

4.1 Serial Port Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.2 Bit Level Processor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.3 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.4 Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.5 Channelized Port Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.5.1 Hyperchannels (Nx64) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.5.2 Subchannels (Nx8). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.5.3 Frame Synchronization Flywheel. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.5.4 Change-of-Frame Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.5.5 Out-of-Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.6 Serial Port Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4.7 Tx and Rx FIFO Buffer Allocation and Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

4.7.1 Example Channel BUFFLOC and BUFFLEN Specification. . . . . . . . . . . . . . . . . . . . . . . . . 4-13

4.7.2 Receiving Bit Stream . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

4.7.3 Transmitting Bit Stream . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

4.7.3.1 Transmit Data Bit Output Value Determination . . . . . . . . . . . . . . . . . . . . . . . 4-16

5.0 Memory Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1 Memory Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1.1 Register Map Access and Shared Memory Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.1.2 Memory Access Illustration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5.2 Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5.2.1 Host Interface Level Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

5.2.1.1 Global Configuration Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

5.2.1.2 Dual Address Cycle Base Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5.2.2 Channel Group Level Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5.2.2.1 Group Base Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5.2.2.2 Service Request . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

5.2.2.3 Group Configuration Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

5.2.2.4 Memory Protection Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

5.2.2.5 Port Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

5.2.2.6 Message Length Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

5.2.2.7 Time Slot Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

5.2.2.8 Subchannel Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24

5.2.3 Channel Level Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

5.2.3.1 Channel Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

5.2.4 Message Level Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

5.2.4.1 Using Message Descriptors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

5.2.4.2 Note for Interrupt Driven Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

5.2.4.3 Head Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

5.2.4.4 Message Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

5.2.4.5 Message Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32

5.2.4.6 Buffer Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32

iv Conexant 100660E

CN8478/CN8474A/CN8472A/CN8471A Table of Contents

Multichannel Synchronous Communications Controller (MUSYCC™)

5.2.4.7 Buffer Status Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

5.2.4.8 Next Message Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

5.2.4.9 Data Buffer Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

5.2.4.10 Message Descriptor Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

5.2.5 Interrupt Level Descriptors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-38

5.2.5.1 Interrupt Queue Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-38

5.2.5.2 Interrupt Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-39

5.2.5.3 Interrupt Status Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-44

5.2.6 Interrupt Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-45

5.2.6.1 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-45

5.2.6.2 Interrupt Descriptor Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-45

5.2.6.3 INTA* Signal Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-46

5.2.6.4 INTB* Signal Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-46

6.0 Basic Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-1

6.1 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1.1 Hard PCI Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1.2 Soft Chip Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.1.3 Soft Group Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.1.4 Initialization Sequence Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.2 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2.1 PCI Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2.2 Global Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.2.3 Interrupt Queue Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.2.4 Channel Group(s) Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.2.5 Service Request Mechanism. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.2.6 MUSYCC Internal Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.2.6.1 Memory Operations—Inactive Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.2.6.2 Memory Operations—Active Channels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.3 Channel Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.3.1 Group Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.3.2 Group Base Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

6.3.3 Global Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.3.4 Interrupt Queue Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-12

6.3.5 Group Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.3.6 Memory Protection Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

6.3.7 Port Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

6.3.8 Message Length Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-15

6.3.9 Transmit Time Slot Map—Channel 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-15

6.3.10 Transmit Subchannel Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-16

6.3.11 Transmit Channel Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

6.3.12 Receive Time Slot Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

6.3.13 Receive Subchannel Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

6.3.14 Receive Channel Configuration Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

6.3.15 Message Lists . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

100660E Conexant v

Preliminary Information

Table of Contents CN8478/CN8474A/CN8472A/CN8471A

Multichannel Synchronous Communications Controller (MUSYCC™)

6.3.16 Channel Activation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-21

6.3.16.1 Transmit Channel Activation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-21

6.3.16.2 Receive Channel Activation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-22

6.3.17 Channel Deactivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-23

6.3.17.1 Transmit Channel Deactivation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-23

6.3.17.2 Receive Channel Deactivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-23

6.3.18 Channel Jump . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-24

6.3.19 Frame Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-24

6.3.20 Descriptor Polling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25

6.3.21 Repeat Message Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-26

6.4 Protocol Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

6.4.1 Frame Check Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

6.4.2 Opening/Closing Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

6.4.3 Abort Codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

6.4.4 Zero-Bit Insertion/Deletion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

6.4.5 Message Configuration Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

6.4.5.1 Idle Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

6.4.5.2 Inter-message Pad Fill. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

6.4.5.3 Repeat Message Transmission. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

6.4.6 Message Configuration Bits Copy Enable/Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

6.4.7 Bit-Level Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-31

6.4.7.1 Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

6.4.7.2 Receive. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

6.4.8 HDLC Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-33

6.4.8.1 Transmit Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-33

6.4.8.2 Receive Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-34

6.4.8.3 Transmit Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-36

6.4.8.4 Receive Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-37

6.4.9 Transparent Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-43

6.4.9.1 Transmit Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-44

6.4.9.2 Receive Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-44

6.4.9.3 Transmit Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-45

6.4.9.4 Receive Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-46

6.4.10 Intersystem Link Protocol (ISLP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-48

6.5 Signaling System 7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-49

6.5.1 SS7 Repeat Message Transmission. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-49

6.5.2 Message Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-49

6.5.3 Signal Unit Error Rate Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-50

6.5.4 SUERM Counter Incrementing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-50

6.5.5 SUERM Octet Counting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-50

6.5.6 SUERM Counter Decrementing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-50

6.6 Self-Servicing Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-51

vi Conexant 100660E

CN8478/CN8474A/CN8472A/CN8471A Table of Contents

Multichannel Synchronous Communications Controller (MUSYCC™)

7.0 Electrical and Mechanical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1 Electrical and Environmental Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1.2 Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.1.3 Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.2 Timing and Switching Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.2.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.2.2 Host Interface (PCI) Timing and Switching Characteristic. . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.2.3 Expansion Bus (EBUS) Timing and Switching Characteristic . . . . . . . . . . . . . . . . . . . . . 7-11

7.2.4 EBUS Arbitration Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

7.2.5 Serial Interface Timing and Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

7.2.6 Package Thermal Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

7.2.7 Mechanical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

8.0 Terms, Definitions, and Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.1 Applicable Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.2 Numeric Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

8.3 Bit Stream Transmission Convention. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.4 Bit Stream Storage Convention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

8.5 Acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-5

8.6 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.7 Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-9

Appendix A JTAG Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.1 Instruction Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.2 BYPASS Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

100660E Conexant vii

Preliminary Information

Table of Contents CN8478/CN8474A/CN8472A/CN8471A

Multichannel Synchronous Communications Controller (MUSYCC™)

viii Conexant 100660E

CN8478/CN8474A/CN8472A/CN8471A List of Figures

Multichannel Synchronous Communications Controller (MUSYCC™)

List of Figures

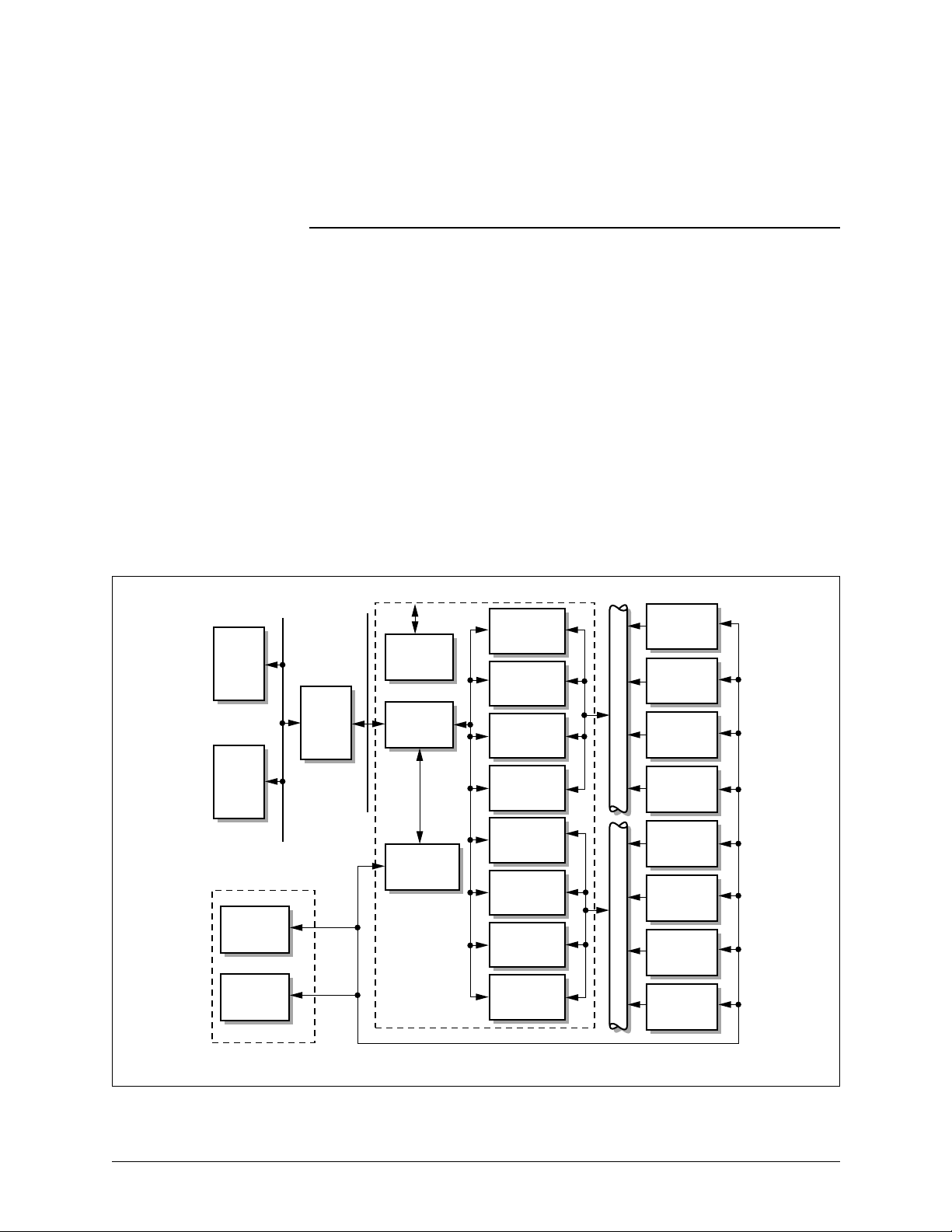

Figure 1-1. System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

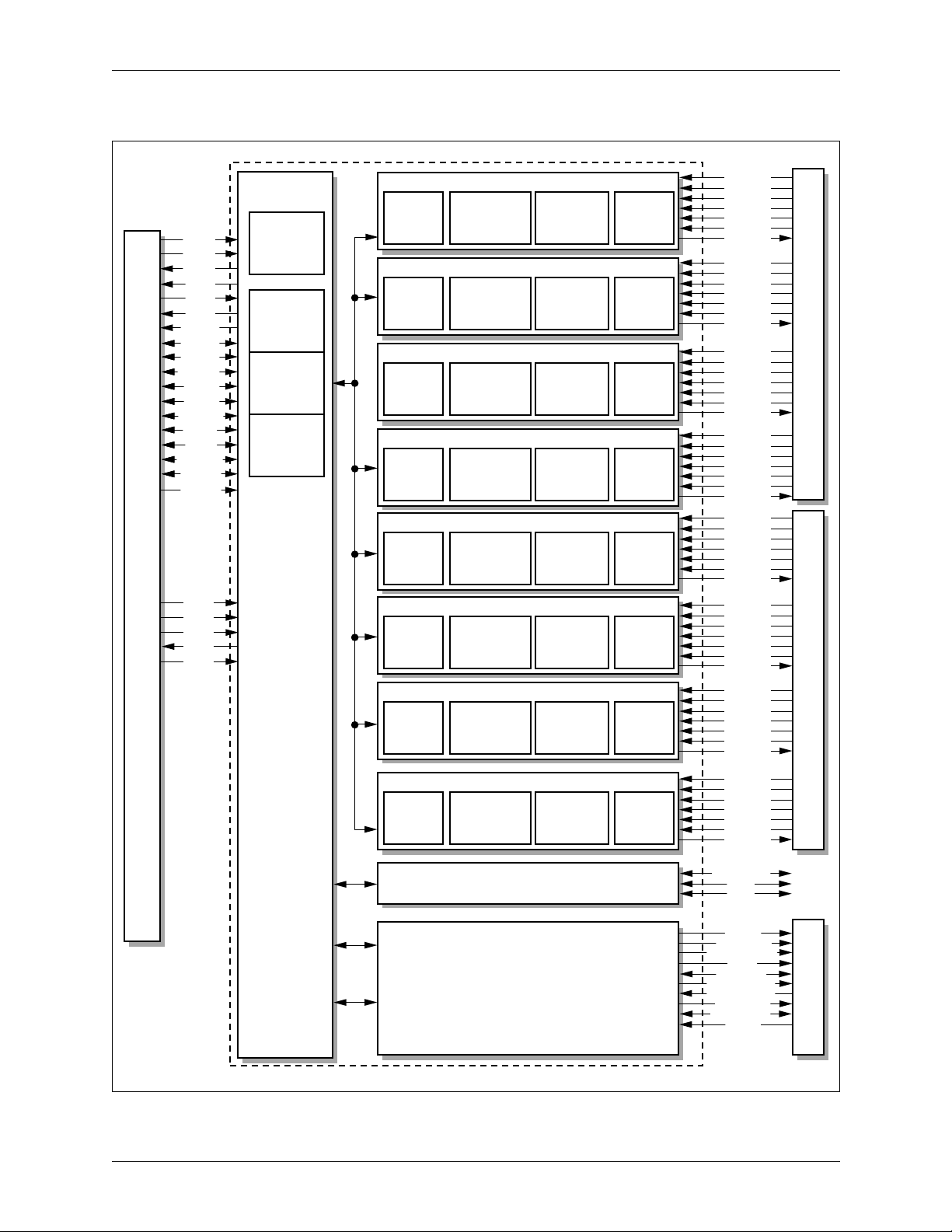

Figure 1-2. Detailed System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

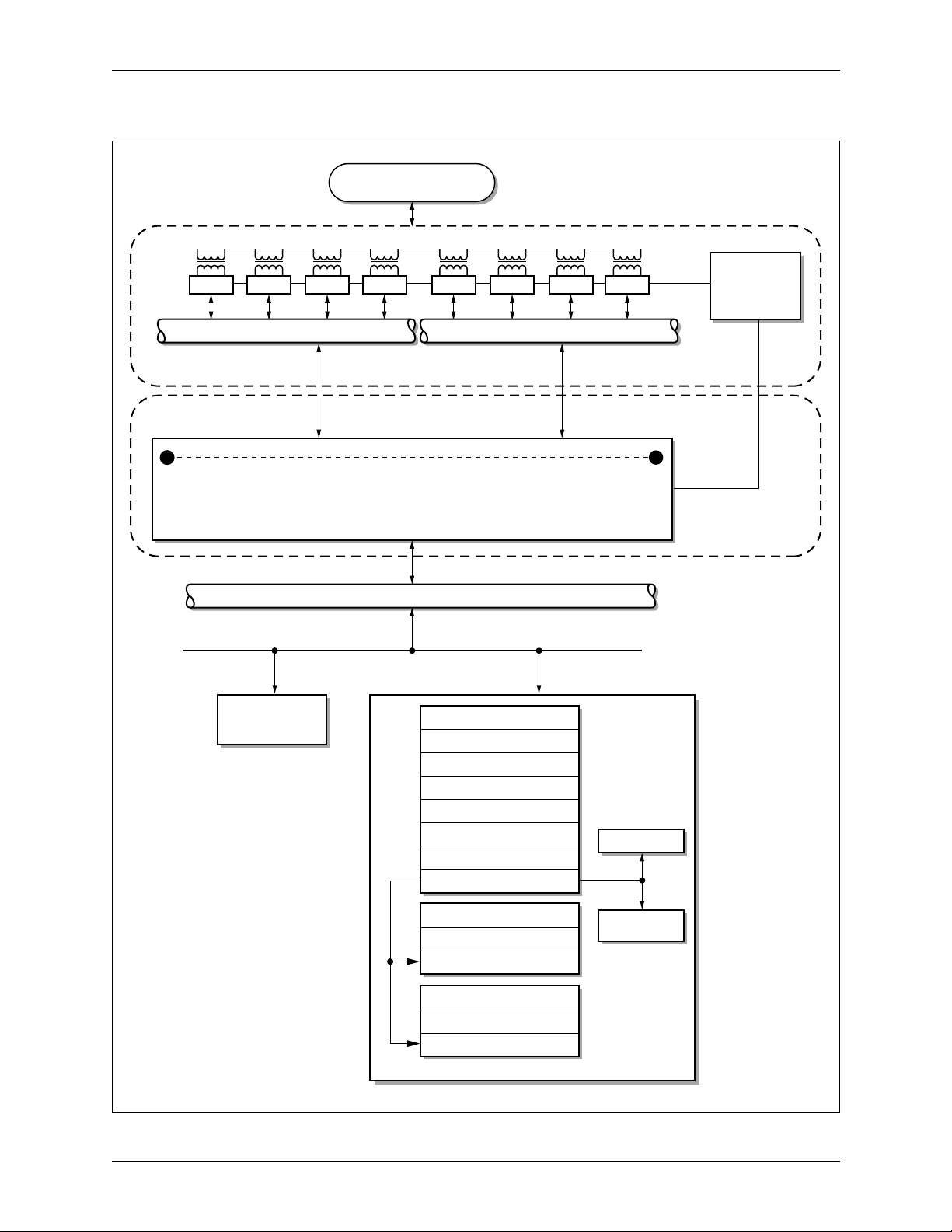

Figure 1-3. MUSYCC Application Example—Frame Relay Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

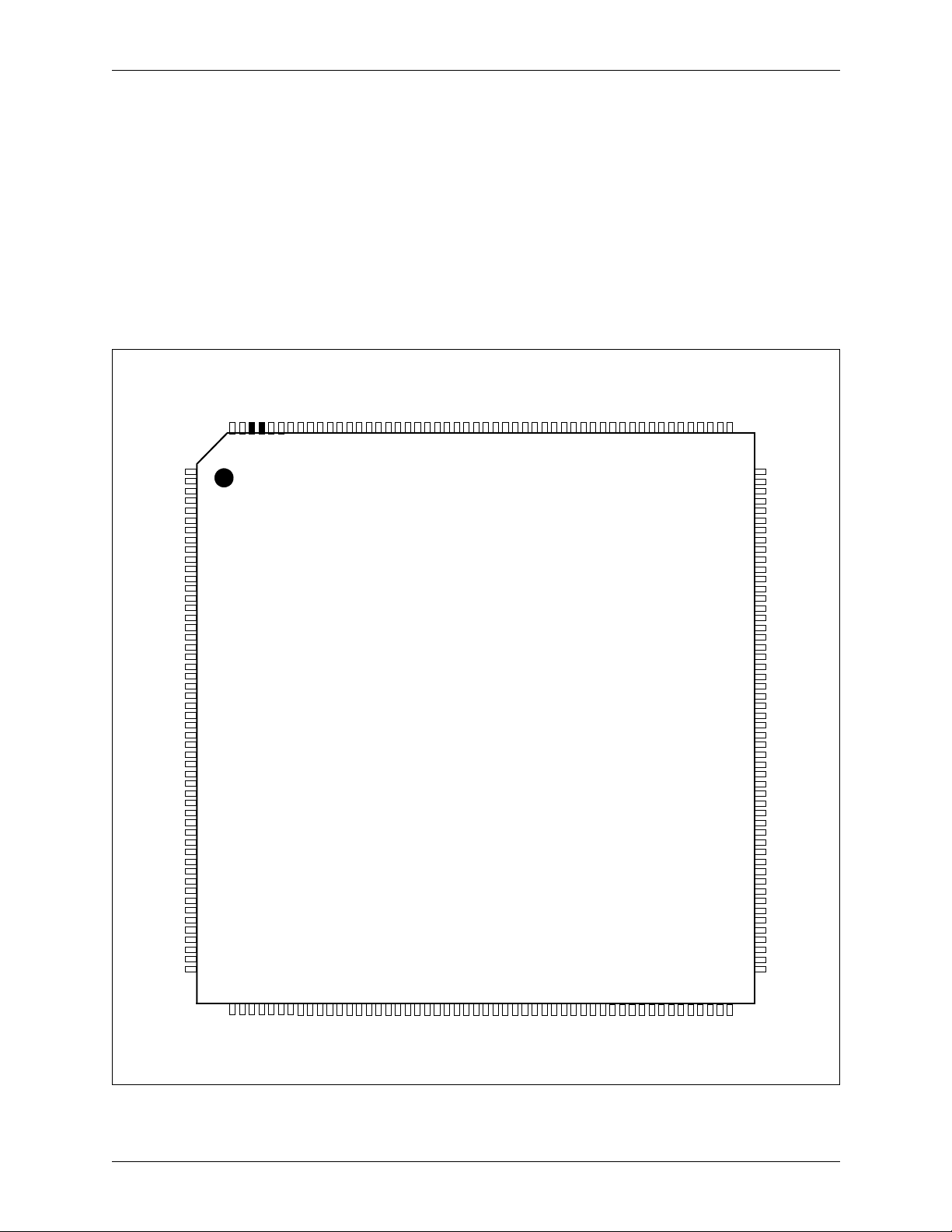

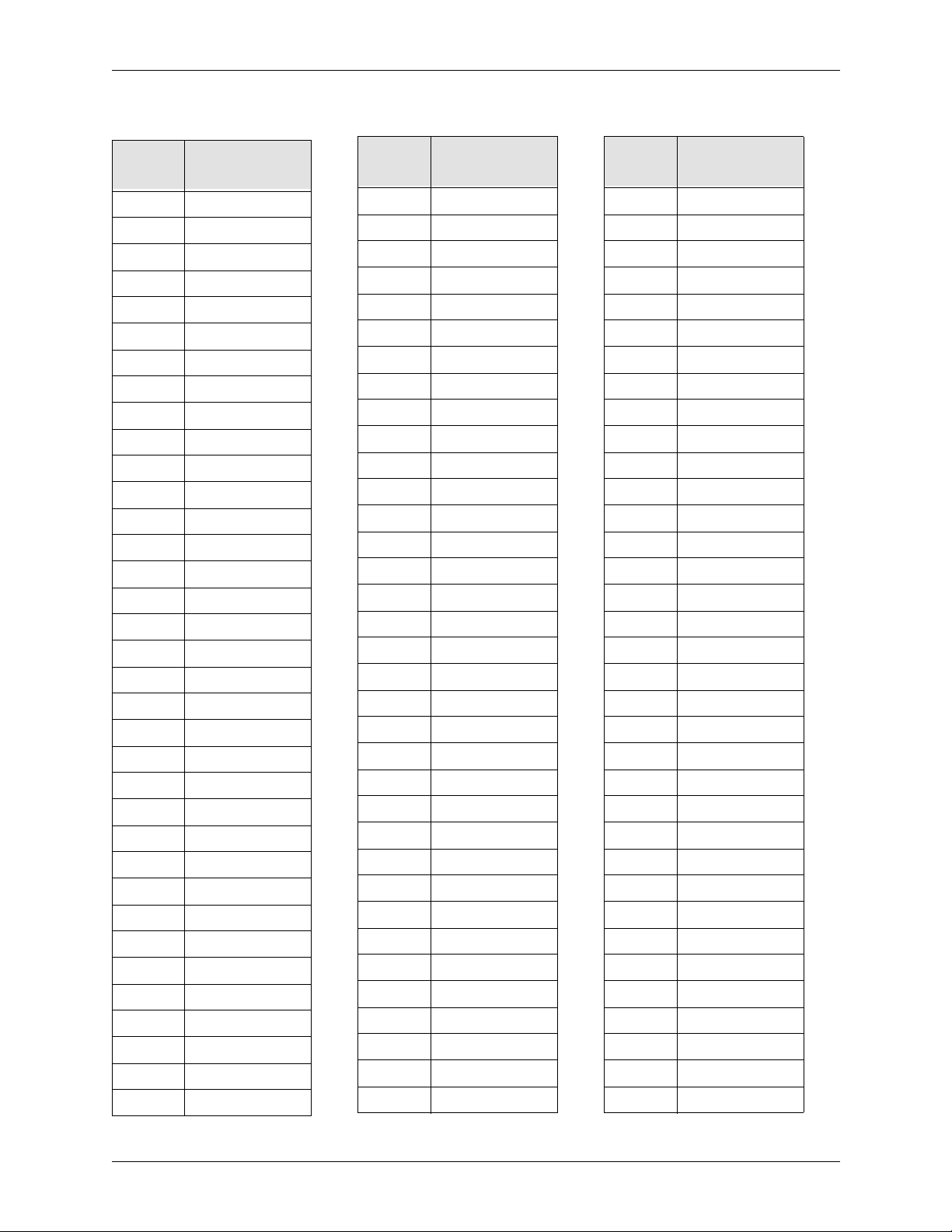

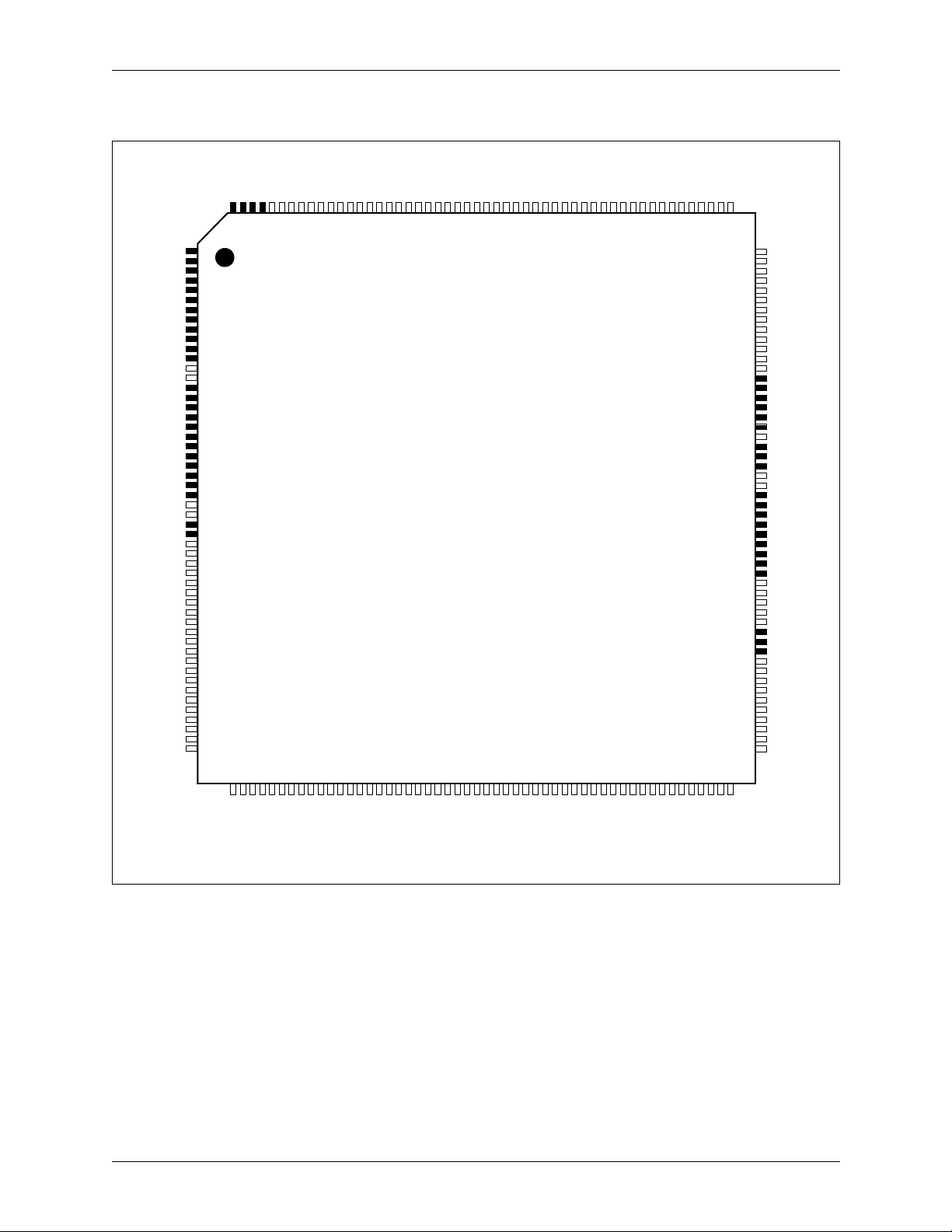

Figure 1-4. CN8478 MQFP Pinout Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

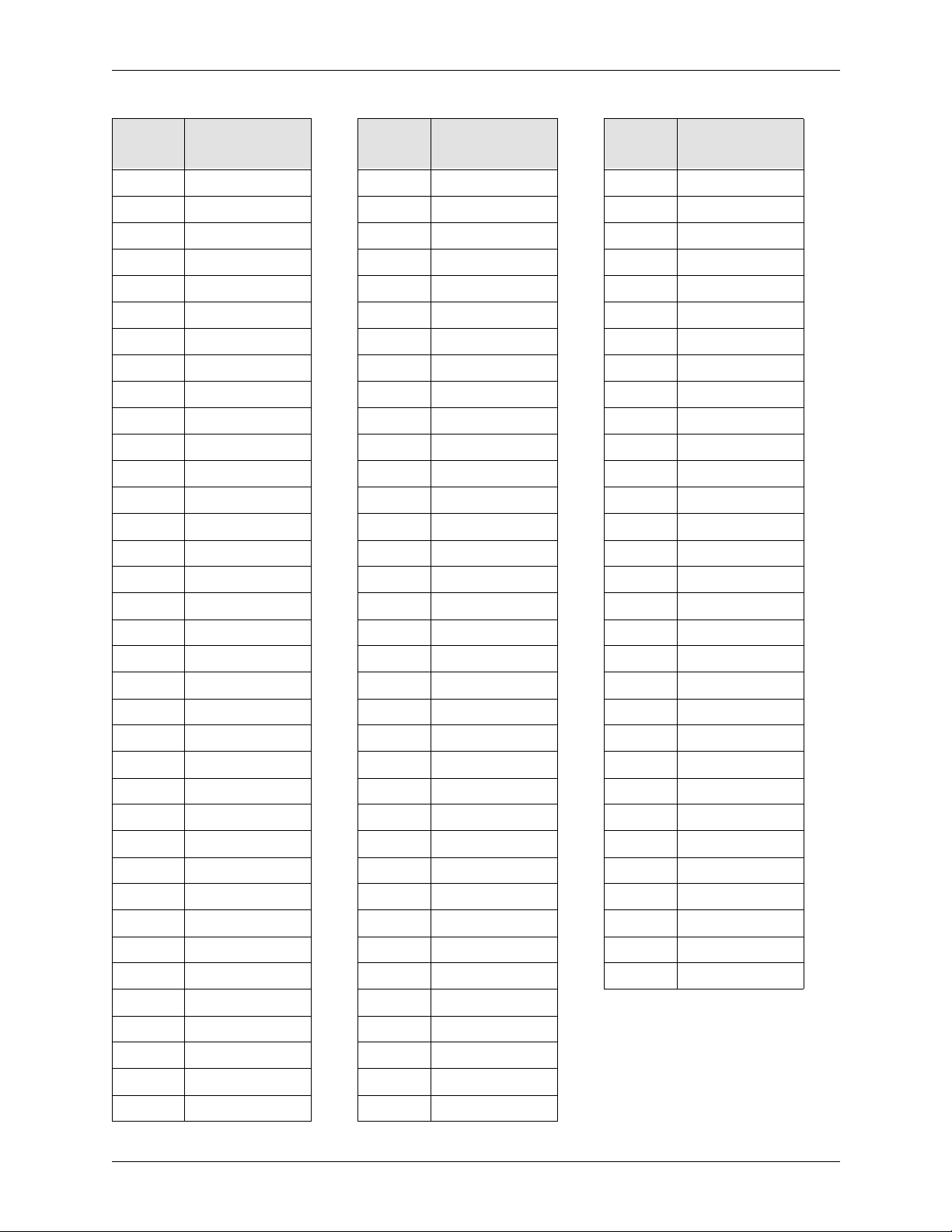

Figure 1-5. CN8474A MPQF Pinout Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

Figure 1-6. CN8472A MQFP Pinout Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

Figure 1-7. CN8471A MQFP Pinout Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

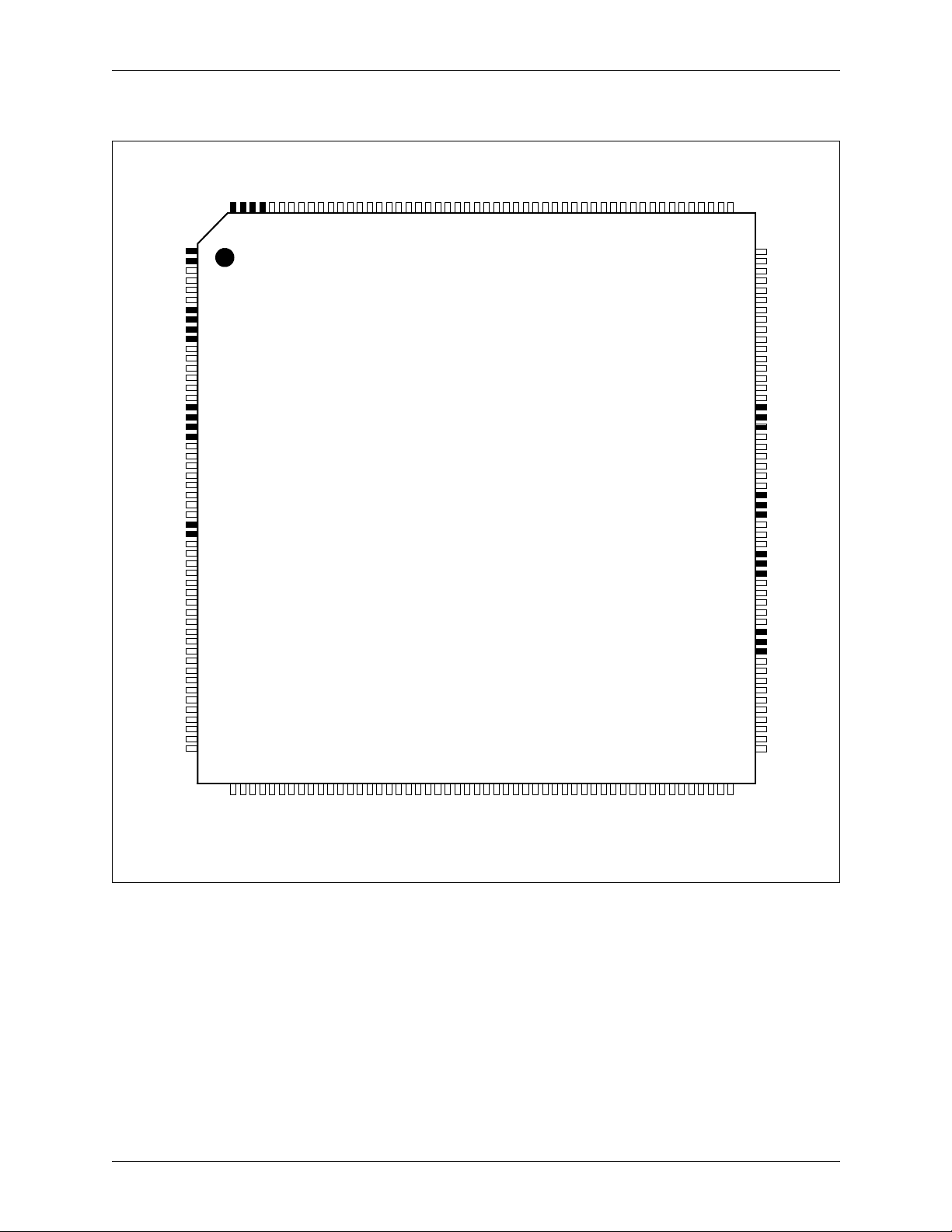

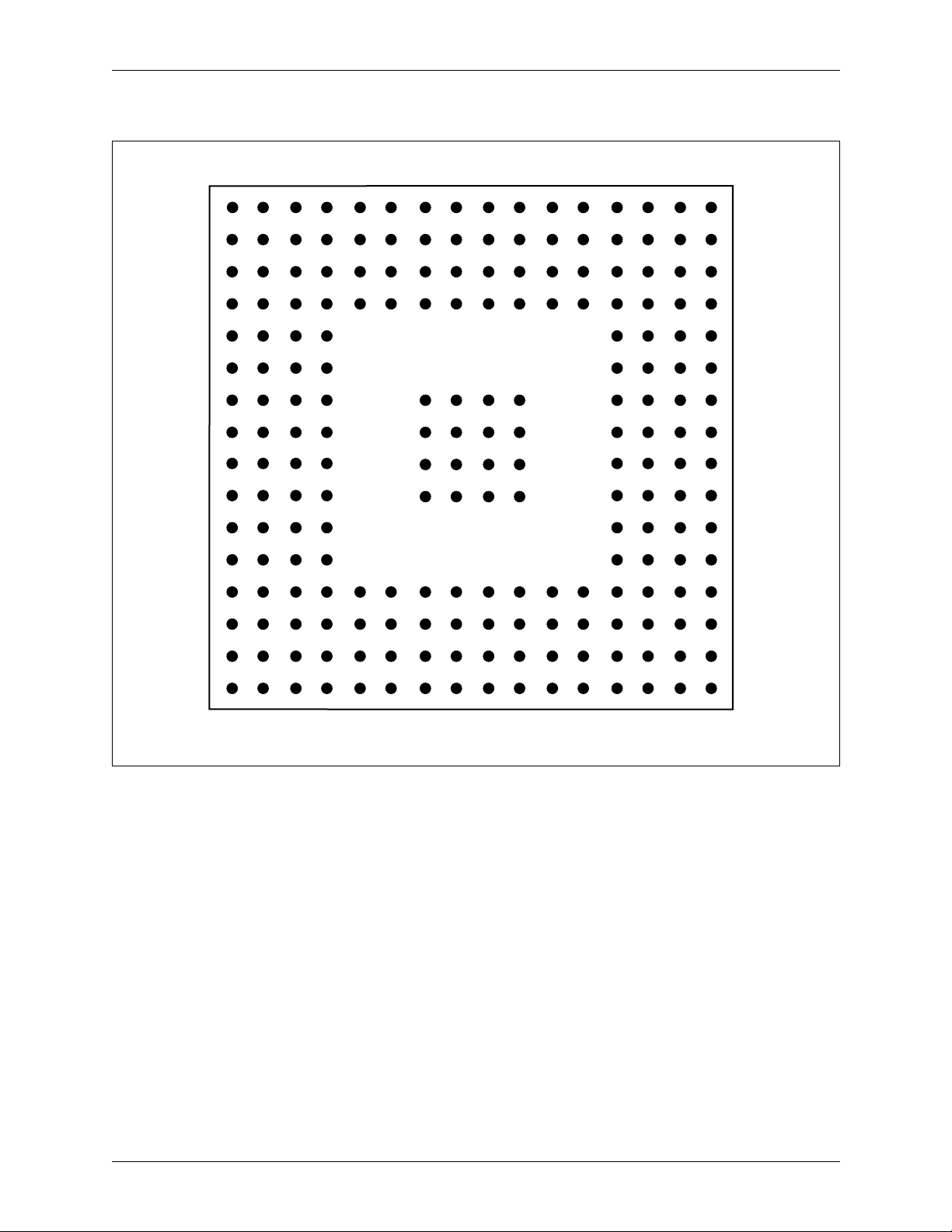

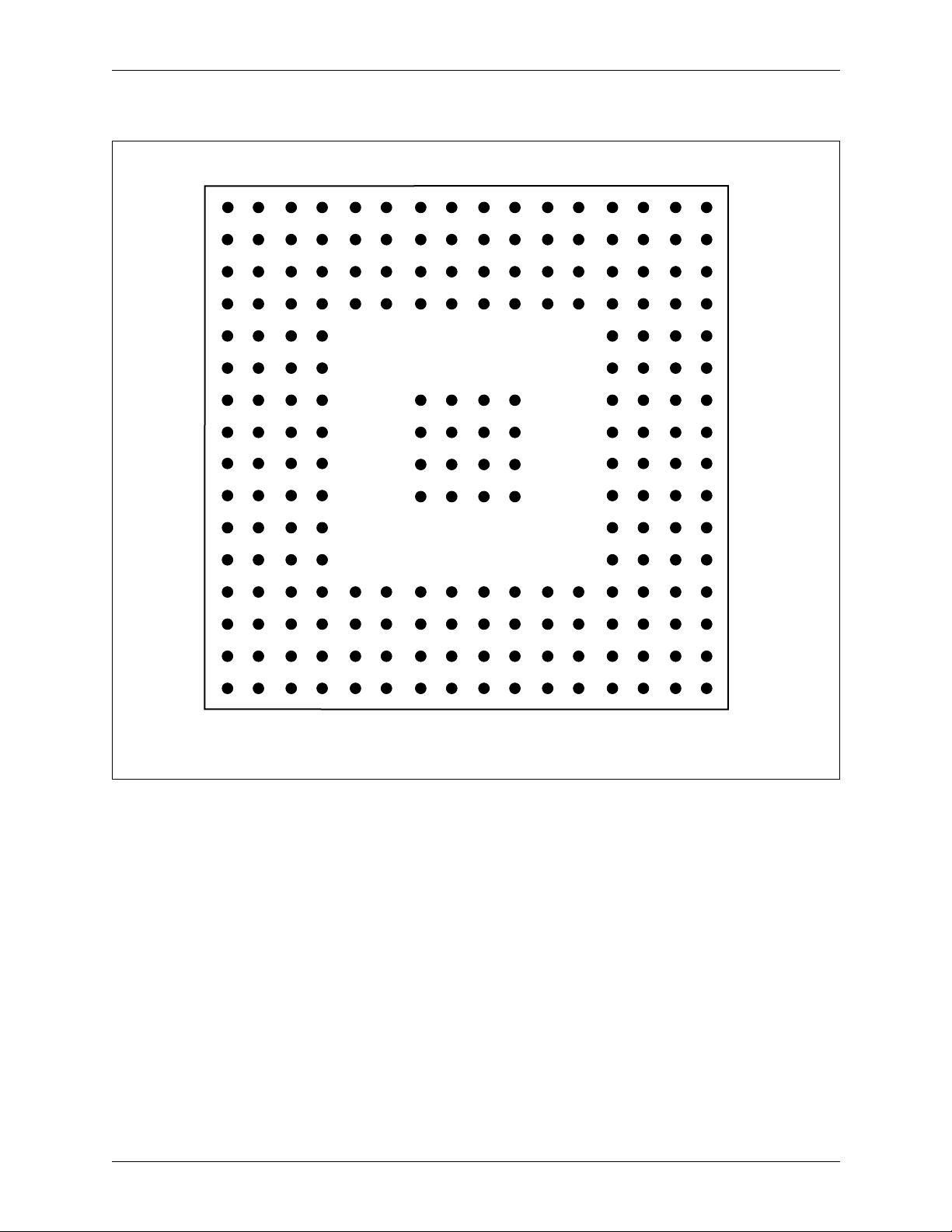

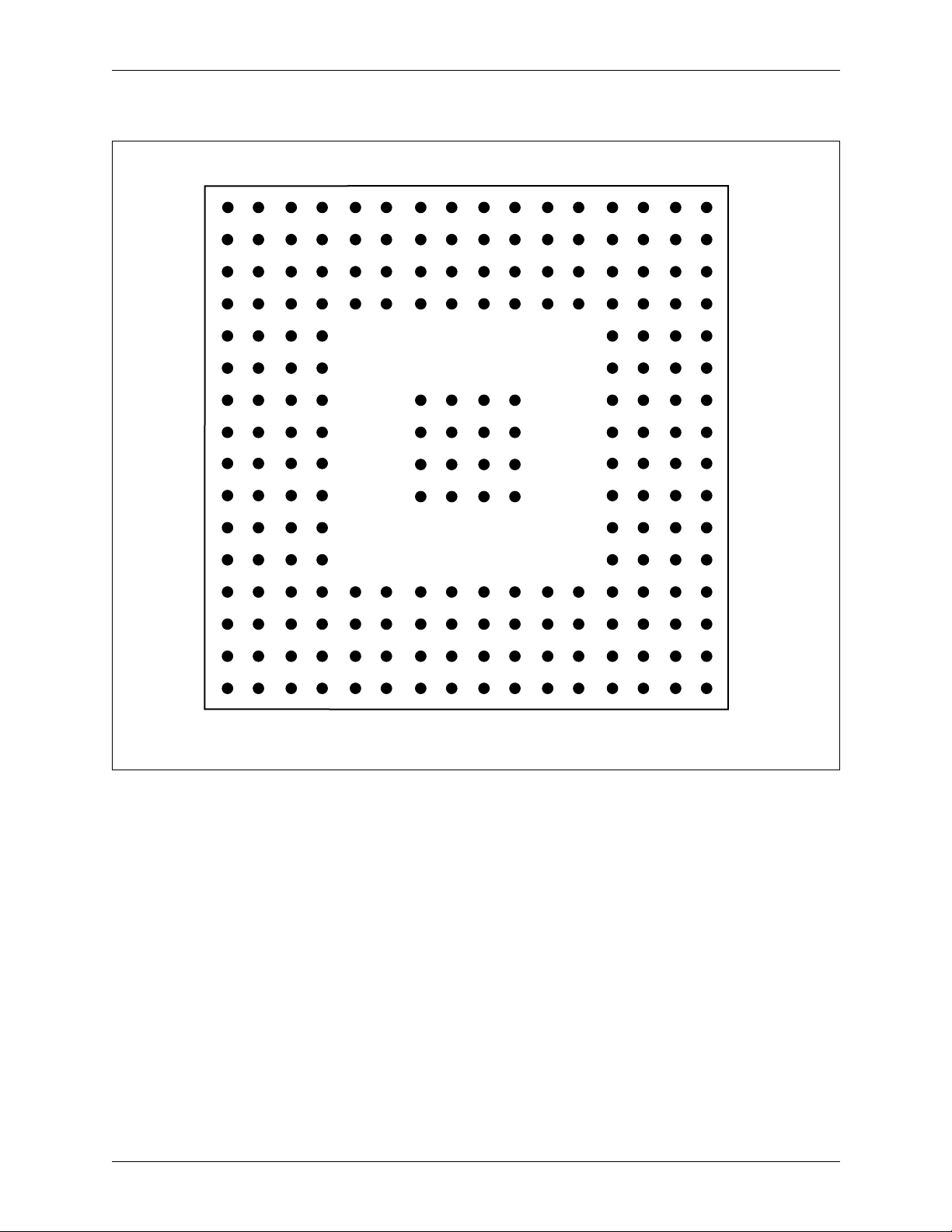

Figure 1-8. CN8478 PBGA Pinout Configuration (Top View) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

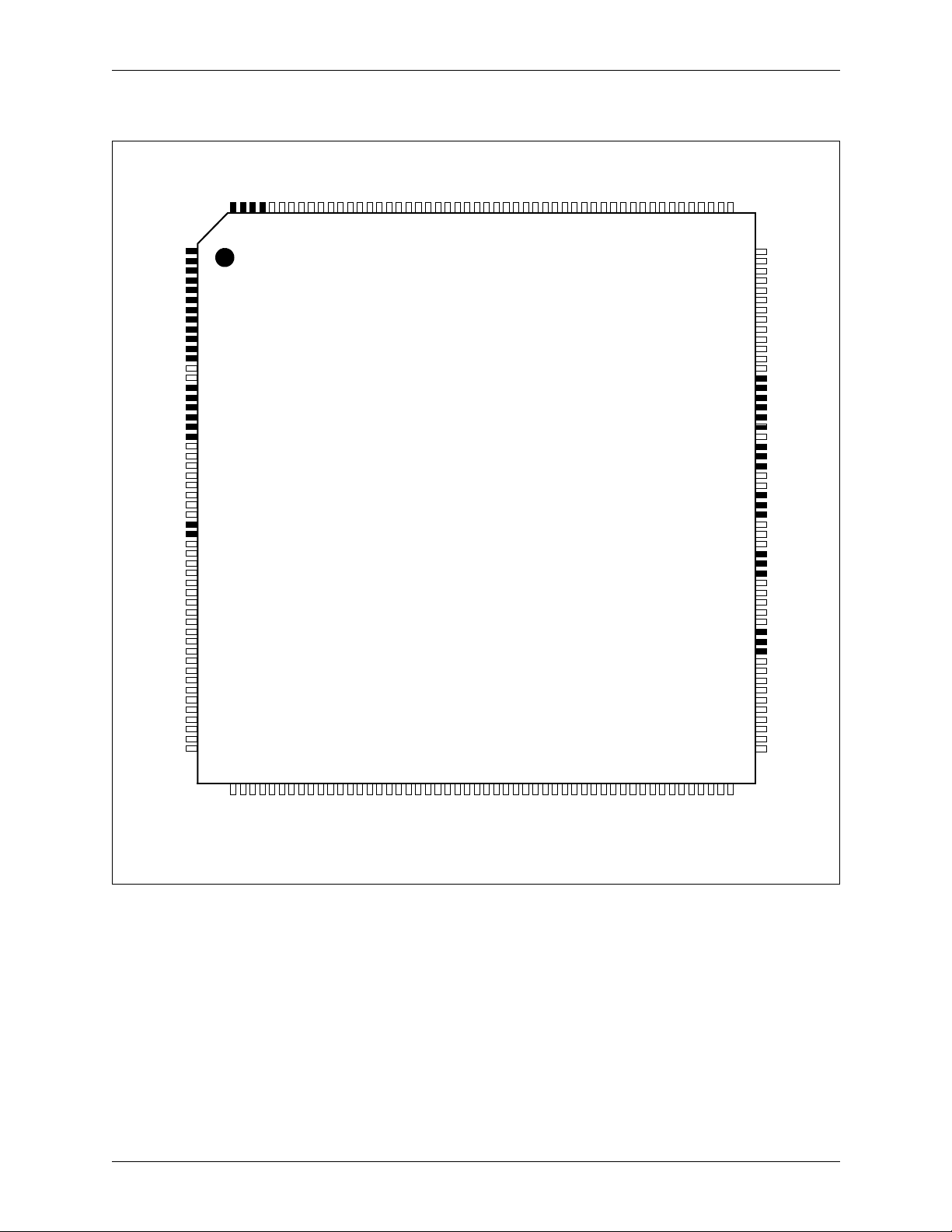

Figure 1-9. CN8474A PBGA Pinout Configuration (Top View) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

Figure 1-10. CN8472A PBGA Pinout Configuration (Top View) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-15

Figure 1-11. CN8471A PBGA Pinout Configuration (Top View) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

Figure 1-12. CN8478 Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

Figure 2-1. Host Interface Functional Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Figure 2-2. Address Lines During Configuration Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Figure 3-1. EBUS Functional Block Diagram with Local MPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Figure 3-2. EBUS Functional Block Diagram without Local MPU. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Figure 3-3. EBUS Address/Data Line Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

Figure 3-4. EBUS Connection, Non-multiplexed Address/Data, 8 Framers, No MPU. . . . . . . . . . . . . . . 3-8

Figure 3-5. EBUS Connection, Non-multiplexed Address/Data, 61 Framers, No MPU. . . . . . . . . . . . . . 3-9

Figure 3-6. EBUS Connection, Multiplexed Address/Data, 8 Framers, No MPU. . . . . . . . . . . . . . . . . . 3-10

Figure 4-1. Serial Interface Functional Block Diagram, Channel Group 0. . . . . . . . . . . . . . . . . . . . . . . . 4-1

Figure 4-2. Transmit and Receive T1 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Figure 4-3. Transmit and Receive E1 (also 2xE1, 4xE1) Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Figure 4-4. Transmit and Receive Nx64 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-7

Figure 4-5. Serial Port Mapping Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Figure 4-6. Receive Data Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

Figure 4-7. Transmit Data Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

Figure 4-8. Transmit Data Bit Output Value Determination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

Figure 5-1. Shared Memory Model Per Channel Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Figure 5-2. Interrupt Notification To Host . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-47

Figure 7-1. PCI Clock (PCLK) Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Figure 7-2. PCI Reset Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Figure 7-3. PCI Output Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

Figure 7-4. PCI Input Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Figure 7-5. PCI Read Multiple Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Figure 7-6. PCI Write Multiple Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

Figure 7-7. PCI Write Single Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

Figure 7-8. ECLK to PCLK Relationship (M66EN = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

Figure 7-9. ECLK to PCKL Relationship (M66EN = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

100660E Conexant ix

List of Figures CN8478/CN8474A/CN8472A/CN8471A

Multichannel Synchronous Communications Controller (MUSYCC™)

Figure 7-10. EBUS Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

Figure 7-11. EBUS Output Timing Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

Figure 7-12. EBUS Input Timing Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-13

Figure 7-13. EBUS Write/Read Transactions, Intel-Style . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

Figure 7-14. EBUS Write/Read Transactions, Motorola-Style . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-15

Figure 7-15. Serial Interface Clock (RCLK,TCLK) Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

Figure 7-16. Serial Interface Clock (RCLK,TCLK) Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-17

Figure 7-17. Serial Interface Data Input Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-17

Figure 7-18. Serial Interface Data Delay Output Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

Figure 7-19. 208-Pin Metric Quad Flatpack (MQFP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

Figure 7-20. 208-Pin Plastic Ball Grid Array (PBGA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-20

Figure A-1. JTAG Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

x Conexant 100660E

CN8478/CN8474A/CN8472A/CN8471A List of Tables

Multichannel Synchronous Communications Controller (MUSYCC™)

List of Tables

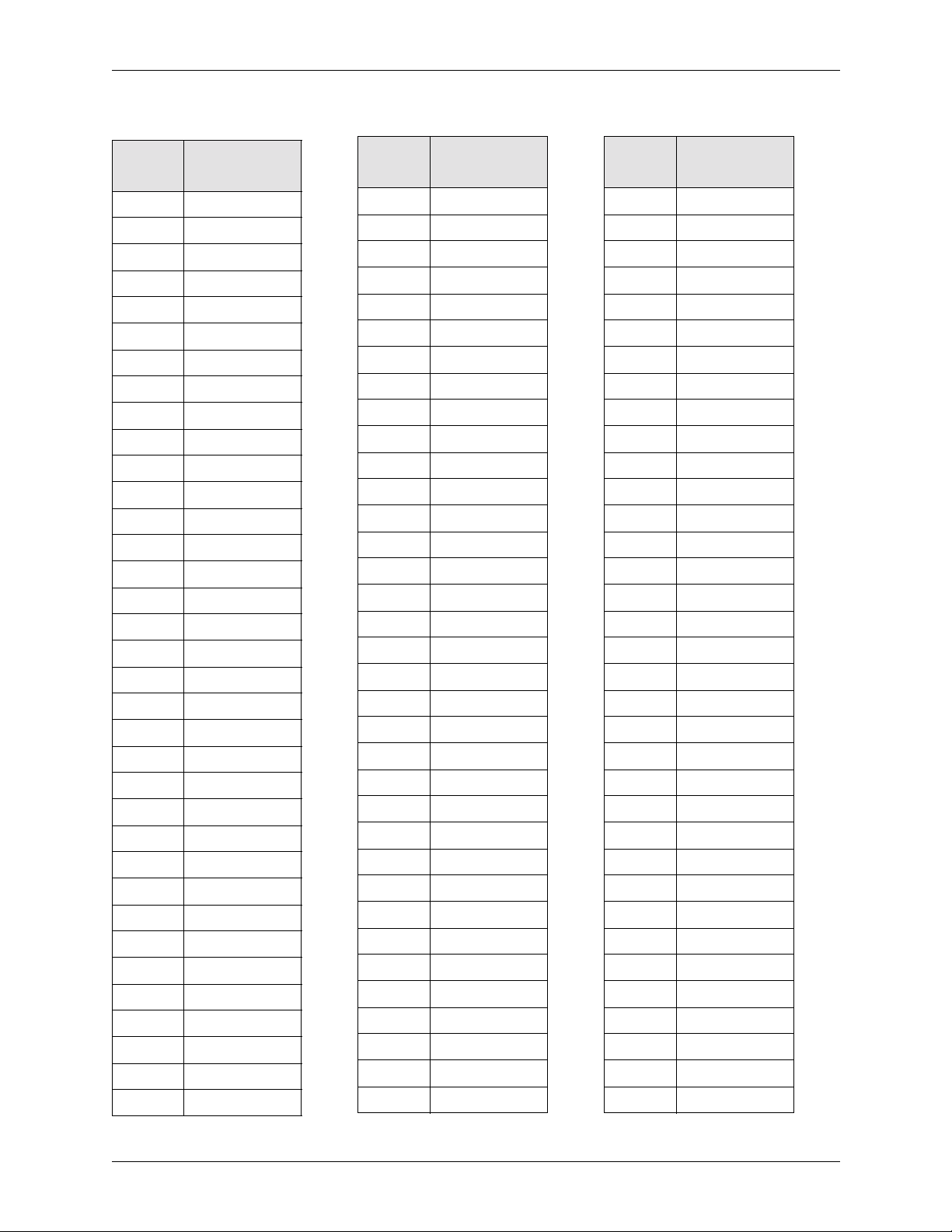

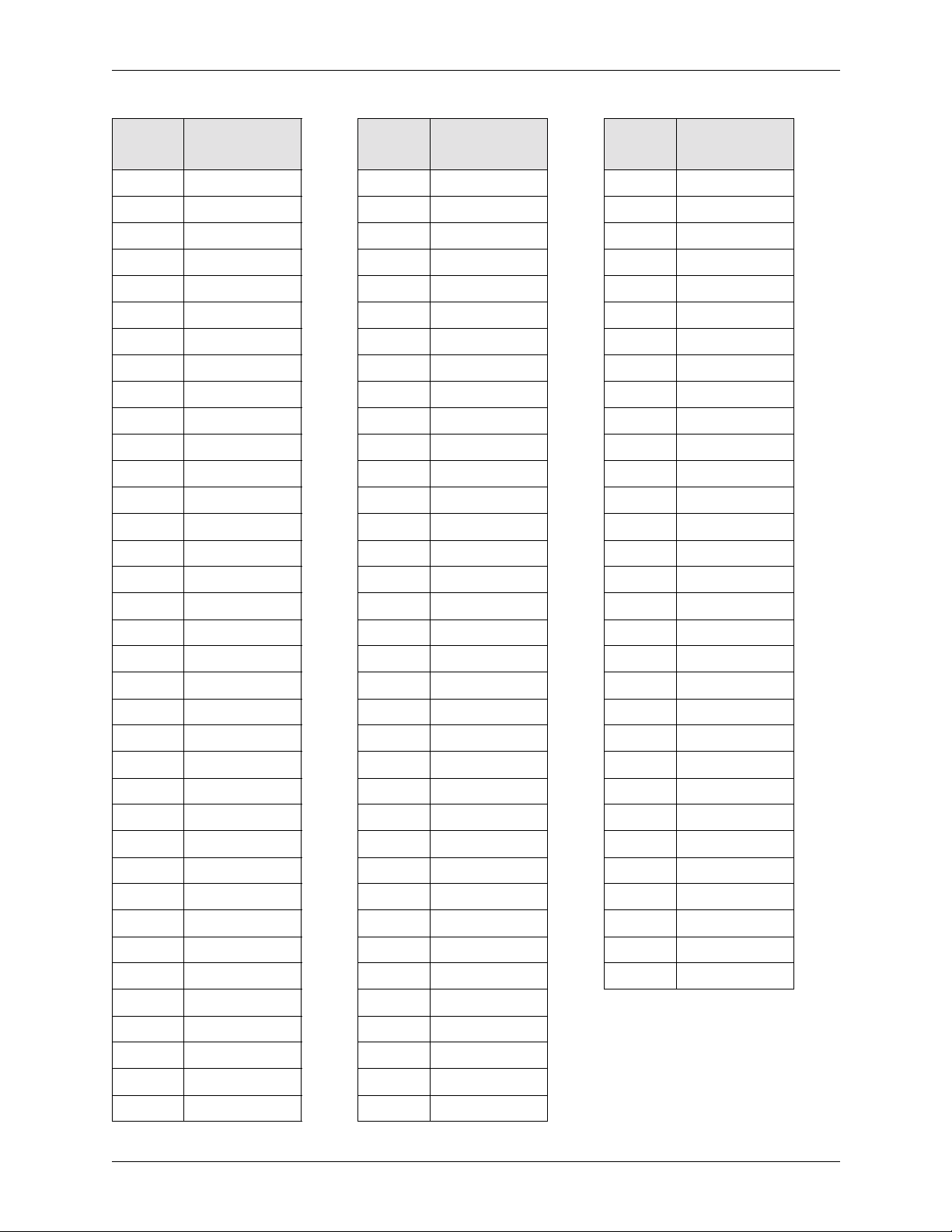

Table 1-1. CN8478 MQFP Pin List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Table 1-2. CN8478 PBGA Pin List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

Table 1-3. I/O Pin Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

Table 1-4. CN8478 Hardware Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

Table 2-1. Function 0 Configuration Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Table 2-2. Function 1 Configuration Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Table 2-3. Register 0, Address 00h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Table 2-4. Register 1, Address 04h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Table 2-5. Register 2, Address 08h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Table 2-6. Register 3, Address 0Ch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Table 2-7. Register 4, Address 10h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

Table 2-8. Registers 5–14, Addresses 14h–38h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

Table 2-9. Register 15, Address 3Ch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

Table 2-10. Register 0, Address 00h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Table 2-11. Register 1, Address 04h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Table 2-12. Register 2, Address 08h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

Table 2-13. Register 3, Address 0Ch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

Table 2-14. Register 4, Address 10h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

Table 2-15. Registers 5 through 14–Addresses 14h through 38h . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

Table 2-16. Register 15, Address 3Ch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

Table 2-17. PCI Latency Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

Table 3-1. Intel Protocol Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Table 3-2. Motorola Protocol Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Table 4-1. Channelized Serial Port Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Table 4-2. Internal Buffer Memory Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

Table 4-3. Example of 32-Channel with Subchanneling Buffer Allocation (Receive or Transmit) . . . . . 4-13

Table 4-4. Example of 32-Channel without Subchanneling Buffer Allocation (Receive or Transmit) . . 4-14

Table 4-5. Example of 16-Channel without Subchanneling Buffer Allocation (Receive or Transmit) . . 4-14

Table 5-1. MUSYCC Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Table 5-2. Group Structure Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Table 5-3. MUSYCC PCI Function Memory Allocation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Table 5-4. Shared Memory Allocation—Group Descriptors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Table 5-5. Host Assigns Group Base Pointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Table 5-6. Global Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

Table 5-7. Dual Address Cycle Base Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-12

Table 5-8. Group Base Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Table 5-9. Service Request Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

Table 5-10. Group Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

Table 5-11. Memory Protection Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

100660E Conexant xi

List of Tables CN8478/CN8474A/CN8472A/CN8471A

Multichannel Synchronous Communications Controller (MUSYCC™)

Table 5-12. Port Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

Table 5-13. Message Length Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

Table 5-14. Transmit or Receive Time Slot Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-22

Table 5-15. Time Slot Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

Table 5-16. Transmit or Receive Subchannel Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

Table 5-17. Subchannel Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

Table 5-18. Channel Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

Table 5-19. Message Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

Table 5-20. Head Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

Table 5-21. Message Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

Table 5-22. Transmit Buffer Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-33

Table 5-23. Receive Buffer Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

Table 5-24. Transmit Buffer Status Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35

Table 5-25. Receive Buffer Status Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-36

Table 5-26. Next Descriptor Pointer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

Table 5-27. Data Buffer Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

Table 5-28. Interrupt Queue Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-38

Table 5-29. Interrupt Queue Pointer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-38

Table 5-30. Interrupt Queue Length. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-38

Table 5-31. Interrupt Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-41

Table 5-32. Interrupt Status Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-44

Table 6-1. Example—Components of Group Base Pointer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

Table 6-2. Example—Components of Global Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . 6-11

Table 6-3. Example—Components of Interrupt Queue Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-12

Table 6-4. Example—Components of Group Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . 6-13

Table 6-5. Example—Components of Memory Protection Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

Table 6-6. Example—Components of Port Configuration Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

Table 6-7. Example—Components of Message Length Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-15

Table 6-8. Example—Components of Transmit Time Slot Map – Channel 0 . . . . . . . . . . . . . . . . . . . . 6-16

Table 6-9. Example—Components of Transmit Subchannel Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

Table 6-10. Example—Components of Channel Configuration Descriptor. . . . . . . . . . . . . . . . . . . . . . . 6-18

Table 6-11. Polling Frequency Using a Time Slot Counter Method . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-26

Table 6-12. Memory Map for Message Configuration Descriptor Table . . . . . . . . . . . . . . . . . . . . . . . . . 6-30

Table 6-13. Message Configuration Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-30

Table 7-1. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

Table 7-2. Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Table 7-3. Electrical Operating Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Table 7-4. PCI Interface DC Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

Table 7-5. PCI Clock (PCLK) Waveform Parameters, 33 MHz PCI Clock . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Table 7-6. PCI Clock (PCLK) Waveform Parameters, 66 MHz PCI Clock . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Table 7-7. PCI Reset Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

Table 7-8. PCI I/O Timing Parameters, 33 MHz PCI Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

Table 7-9. PCI I/O Timing Parameters, 66 MHz PCI Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

Table 7-10. PCI I/O Measure Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

Table 7-11. EBUS Reset Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

Table 7-12. EBUS I/O Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

xii Conexant 100660E

CN8478/CN8474A/CN8472A/CN8471A List of Tables

Multichannel Synchronous Communications Controller (MUSYCC™)

Table 7-13. EBUS I/O Measure Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

Table 7-14. Serial Interface Clock (RCLK, TCLK) Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

Table 7-15. Serial Interface I/O Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-16

Table 7-16. Serial Interface Clock Hysteresis (RCLK, TCLK, with Schmitt Trigger) . . . . . . . . . . . . . . . . 7-16

Table 7-17. Serial Interface I/O Measure Conditions for 3.3 V Signaling . . . . . . . . . . . . . . . . . . . . . . . . 7-17

Table 7-18. MUSYCC Package Thermal Resistance Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

Table 8-1. Number Representation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

Table 8-2. Digitized Voice Transmission Convention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

Table 8-3. Digital Data Transmission Convention. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-3

Table 8-4. MUSYCC Byte Transmission Convention. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

Table 8-5. Little-Endian Storage Convention (Intel-style). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

Table 8-6. Big-Endian Storage Convention (Motorola-style) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

Table 8-7. CN8478 Data Sheet Revisions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-9

Table A-1. IEEE Std. 1149.1 Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Table A-2. JTAG Timing Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

100660E Conexant xiii

List of Tables CN8478/CN8474A/CN8472A/CN8471A

Multichannel Synchronous Communications Controller (MUSYCC™)

xiv Conexant 100660E

1

1.0 System Description

The Conexant MUSYCC is a high-throughput communications controller for synchronous, link-layer

applications that multiplexes and demultiplexes up to 256 data channels. Each channel can be configured to

support HDLC, Transparent, or SS7 applications. MUSYCC operates at the Layer 2 (the data link protocol

level) reference of the International Organization for Standardization (ISO) Open Systems Interconnection

(OSI). MUSYCC is installed between the multiple serial interface devices and the shared buffer memory of one

or more host processors.

MUSYCC’s serial ports interface to a standard Pulse Code Modulation (PCM) highway, which operates at

T1, E1, 2xE1, or 4xE1 rates. Data can be formatted in the HDLC protocol or left unformatted. The protocol is

specified on a per-channel and direction basis.

An on-device Peripheral Components Interface (PCI) controller, known as the host interface, is provided.

Access to MUSYCC is available through PCI read, write, and configuration cycles (see Figure 1-1).

Figure 1-1. System Block Diagram

System

Host

System

Memory

Optional

Components

Local

Host

Local

Memory

8478_001

Local Bus

Local

Bridge

Bus

PCI

PCI Bus

EBUS

JTAG

Host

Interface

(PCI)

Expansion

Bus

Interface

MUSYCC

Serial

Interface 0

Serial

Interface 1

Serial

Interface 2

Serial

Interface 3

Serial

Interface 4

Serial

Interface 5

Serial

Interface 6

Serial

Interface 7

Physical

Interface 0

Physical

Interface 1

Physical

Interface 2

PCM Highway(s)

Physical

Interface 3

Physical

Interface 4

Physical

Interface 5

Physical

Interface 6

PCM Highway( s)

Physical

Interface 7

100660E Conexant 1-1

1.0 System Description CN8478/CN8474A/CN8472A/CN8471A

Multichannel Synchronous Communications Controller (MUSYCC™)

MUSYCC also provides an on-device, 32-bit local expansion bus (EBUS) controller which allows a host

processor to access local memory and physical interface devices directly through MUSYCC over the PCI using

configurable memory mapping features.

MUSYCC manages buffer memory for each active data channel with common list-processing structures.

The on-device features allow data transmission between buffer memory and the serial interfaces with minimum

host processor intervention. This allows the host processor to concentrate on managing the higher layers of the

protocol stack.

Figures 1-2 and 1-3 illustrate detailed system block diagrams and a sample application.

1-2 Conexant 100660E

CN8478/CN8474A/CN8472A/CN8471A 1.0 System Description

Multichannel Synchronous Communications Controller (MUSYCC™)

Figure 1-2. Detailed System Block Diagram

PCLK

PRST*

INTB*

INTA*

GNT*

REQ*

SERR*

PERR*

IDSEL*

FRAME*

IRDY*

TRDY*

DEVSEL*

STOP*

PAR*

CBE[3:0]*

AD[31:0]

M66EN

PCI Bus

TCK

TEN*

3.3/5.0 Volt, 33/66 MHz

TMS

TDO

TDI

Host Interface

Device

Configuration

Registers

PCI

Interface

PCI

Configuration

Space

[Function 0]

PCI

Configuration

Space

[Function 1]

Interrupt

Controller

Interrupt

Controller

Interrupt

Controller

Interrupt

Controller

Interrupt

Controller

Interrupt

Controller

Interrupt

Controller

Serial Interface Channel Group 0

DMA

Controller

Tx/Rx-DMAC

Serial Interface Channel Group 1

DMA

Controller

Tx/Rx-DMAC

Serial Interface Channel Group 2

DMA

Controller

Tx/Rx-DMAC

Serial Interface Channel Group 3

DMA

Controller

Tx/Rx-DMAC

Serial Interface Channel Group 4

DMA

Controller

Tx/Rx-DMAC

Serial Interface Channel Group 5

DMA

Controller

Tx/Rx-DMAC

Serial Interface Channel Group 6

DMA

Controller

Tx/Rx-DMAC

Bit-Level

Processor

Tx/Rx-BLP

Bit-Level

Processor

Tx/Rx-BLP

Bit-Level

Processor

Tx/Rx-BLP

Bit-Level

Processor

Tx/Rx-BLP

Bit-Level

Processor

Tx/Rx-BLP

Bit-Level

Processor

Tx/Rx-BLP

Bit-Level

Processor

Tx/Rx-BLP

Port

Interface

Tx/Rx

Port

Interface

Tx/Rx

Port

Interface

Tx/Rx

Port

Interface

Tx/Rx

Port

Interface

Tx/Rx

Port

Interface

Tx/Rx

Port

Interface

Tx/Rx

RCLK0

RSYNC0

RDAT0

ROOF0

TCLK0

TSYNC0

TDAT0

RCLK1

RSYNC1

RDAT1

ROOF1

TCLK1

TSYNC1

TDAT1

RCLK2

RSYNC2

RDAT2

ROOF2

TCLK2

TSYNC2

TDAT2

RCLK3

RSYNC3

RDAT3

ROOF3

TCLK3

TSYNC3

TDAT3

RCLK4

RSYNC4

RDAT4

ROOF4

TCLK4

TSYNC4

TDAT4

RCLK5

RSYNC5

RDAT5

ROOF5

TCLK5

TSYNC5

TDAT5

RCLK6

RSYNC6

RDAT6

ROOF6

TCLK6

TSYNC6

TDAT6

Serial Interface System BusSerial Interface System Bus

RCLK7

RSYNC7

RDAT7

ROOF7

TCLK7

TSYNC7

TDAT7

SCAN_EN

TM0

TM1

ECLK

RD* (DS*)

WR* (R/WR*)

ALE*

BGACK*

HOLD (BR*)

HLDA (BG*)

EBE[3:0]*

EAD[31:0]*

EINT*

Bus

Microprocessor

8478_002

Scan

Data

Control

Interrupt

Controller

Serial Interface Channel Group 7

DMA

Controller

Tx/Rx-DMAC

Boundary Scan and Test Access

Expansion Bus Interface

Bit-Level

Processor

Tx/Rx-BLP

Port

Interface

Tx/Rx

100660E Conexant 1-3

1.0 System Description CN8478/CN8474A/CN8472A/CN8471A

Multichannel Synchronous Communications Controller (MUSYCC™)

Figure 1-3. MUSYCC Application Example—Frame Relay Switch

Frame Relay Network

Control

PHY

PHY PHY PHY

PHY PHY

PHY

PHY

Data

MPU

(Optional)

System Bus – PCM Highway

Tx

Clk, Data,

Sync

Port 0

Ch Grp 0

Por t 1

Ch Grp 1

System Host

Clk, Data,

Sync, OOF

Port 2

Ch Grp 2

Rx

Physical Layer

Data Link Layer

Port 3

Ch Grp 3

Port 4

Ch Grp 4

Serial Port Interface

CN8478

Host Interface (PCI)

PCI Bus

PCI Local Bus Bridge

Channel Group 7 Descriptor

Channel Group 6 Descriptor

Channel Group 5 Descriptor

Channel Group 4 Descriptor

Channel Group 3 Descriptor

Channel Group 2 Descriptor

Channel Group 1 Descriptor

Channel Group 0 Descriptor

System Bus – PCM Highway

Tx

Clk, Data,

Sync

Port 5

Ch Grp 5

Ch Grp 6

Port 6

Rx

Clk, Data,

Sync, OOF

Por t 7

Ch Grp 7

Interface

Configuration

EBUS

32-Bit

Address

and Data

Multiplexed

EBUS

8478_003

Tx Channel 31 Message List

Tx Channel ... Message List

Tx Channel 0 Message List

Rx Channel 31 Message List

Rx Channel ... Message List

Rx Channel 0 Message List

System Memory

Interrupt

Queue

1-4 Conexant 100660E

CN8478/CN8474A/CN8472A/CN8471A 1.0 System Description

Multichannel Synchronous Communications Controller (MUSYCC™)

1.1 Pin Descriptions

1.1 Pin Descriptions

Figures 1-4 through 1-7 illustrate the pinouts for CN8478, CN8474A, CN8472A, and CN8471A. Signals

marked with black are NCs. Tables 1-1 and 1-2 summarize the pin assignments for the CN8478 in the MQFP

and PBGA packages, respectively. Ta ble 1 -3 lists the pin input and output functions. Table 1 -4 lists the hardware

signal definitions.

Figure 1-4. CN8478 MQFP Pinout Configuration

VDDc

EAD[30]

EAD[31]

189

VSS

EAD[29]

186

187

188

VDDo

VSSo

EAD[24]

EAD[25]

EAD[26]

EAD[27]

EAD[28]

181

182

183

184

185

EAD[22]

EAD[23]

176

177

178

179

180

Preliminary

CN8478

EAD[21]

VSSo

174

175

EAD[18]

169

EAD[17]

168

EAD[16]

167

EAD[15]

166

VSSo

165

VDDo

164

EAD[14]

163

EAD[13]

162

EAD[12]

161

EAD[11]

160

EAD[10]

159

VSS

EAD[9]

157

158

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

VGG

EAD[8]

EAD[7]

VSSo

EAD[6]

EAD[5]

EAD[4]

EAD[3]

VSSo

VDDo

EAD[2]

EAD[1]

EAD[0]

TCLK[3]

TSYNC[3]

TDAT[3]

TCLK[7]

TSYNC[7]

TDAT[7]

VSSo

TCLK[2]

TSYNC[2]

TDAT[2]

VSS

VDDc

TCLK[6]

TSYNC[6]

TDAT[6]

TCLK[1]

TSYNC[1]

TDAT[1]

TCLK[5]

TSYNC[5]

TDAT[5]

TCLK[0]

TSYNC[0]

TDAT[0]

VSS

VDDp

TCLK[4]

TSYNC[4]

TDAT[4]

TM[0]

TM[1]

TM[2]

VSSo

VDDo

AD[0]

AD[1]

AD[2]

AD[3]

AD[4]

EAD[19]

VDDp

EAD[20]

VSS

170

171

172

173

RSYNC[7]

RDAT[7]

ROOF[3]

RCLK[3]

RSYNC[3]

RDAT[3]

ROOF[6]

RCLK[6]

RSYNC[6]

RDAT[6]

ROOF[2]

RCLK[2]

VDDp

VSS

RSYNC[2]

RDAT[2]

ROOF[5]

RCLK[5]

RSYNC[5]

RDAT[5]

ROOF[1]

RCLK[1]

RSYNC[1]

RDAT[1]

ROOF[4]

RCLK[4]

VDDc

VSS

RSYNC[4]

RDAT[4]

ROOF[0]

RCLK[0]

RSYNC[0]

RDAT[0]

TCK

TRST*

TMS

TDO

TDI

INTB*

INTA*

VDDo

PCLK

VSSo

PRST

GNT*

REQ*

AD[31]

AD[30]

AD[29]

AD[28]

VGG

VDDo

VSSo

EBE[2]*

EBE[1]*

EBE[0]*NCNC

ROOF[7]

RCLK[7]

200

201

202

203

204

205

206

207

208

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

EINT*

HOLD(BR*)

HLDA(BG*)

BGACK*

EBE[3]*

195

196

197

198

199

ALE*(AS*)

194

ECLK

R*(R/WR*)

RD*(DS*)

VSSo

190

191

192

193

104

103

102

101

100

VSS

AD[27]

555453

VSSo

AD[26]

AD[25]

AD[24]

IDSEL

CBE[3]*

AD[23]

AD[22]

VSSo

VDDo

AD[21]

AD[20]

VSS

VDDp

AD[19]

AD[18]

AD[17]

AD[16]

VSSo

CBE[2]*

FRAME*

IRDY*

VDDc

VSS

TRDY*

DEVSEL*

VDDo

VSSo

STOP*

SERR*

PERR*

PAR

86858483828180797877767574737271706968676665646362616059585756

AD[15]

CBE[1]*

VSSo

AD[14]

AD[13]

AD[12]

AD[11]

AD[10]

VDDo

VSSo

AD[9]

99989796959493929190898887

AD[8]

M66EN

AD[7]

CBE[0]*

AD[5]

AD[6]

VSSo

100660E Conexant 1-5

1.0 System Description CN8478/CN8474A/CN8472A/CN8471A

1.1 Pin Descriptions Multichannel Synchronous Communications Controller (MUSYCC™)

Table 1-1. CN8478 MQFP Pin List

Pin

Number

1 RSYNC[7]

2 RDAT[7]

3 ROOF[3]

4 RCLK[3]

5 RSYNC[3]

6 RDAT[3]

7 ROOF[6]

8 RCLK[6]

9 RSYNC[6]

10 RDAT[6]

11 ROOF[2]

12 RCLK[2]

13 VDDi

14 VSS

15 RSYNC[2]

16 RDAT[2]

17 ROOF[5]

18 RCLK[5]

19 RSYNC[5]

20 RDAT[5]

21 ROOF[1]

22 RCLK[1]

23 RSYNC[1]

24 RDAT[1]

25 ROOF[4]

26 RCLK[4]

27 VDDc

28 VSS

29 RSYNC[4]

30 RDAT[4]

31 ROOF[0]

32 RCLK[0]

33 RSYNC[0]

34 RDAT[0]

35 TCK

Pin Label

Pin

Number

36 TRST*

37 TMS

38 TDO

39 TDI

40 INTB*

41 INTA*

42 VDDo

43 PCLK

44 VSSo

45 PRST*

46 GNT*

47 REQ*

48 AD[31]

49 AD[30]

50 AD[29]

51 AD[28]

52 VGG

53 VSS

54 AD[27]

55 VSSo

56 AD[26]

57 AD[25]

58 AD[24]

59 CBE[3]*

60 IDSEL

61 AD[23]

62 AD[22]

63 VDDo

64 VSSo

65 AD[21]

66 AD[20]

67 VDDi

68 VSS

69 AD[19]

70 AD[18]

Pin Label

Pin

Number

71 AD[17]

72 AD[16]

73 VSSo

74 CBE[2]*

75 FRAME*

76 IRDY*

77 VDDc

78 VSS

79 TRDY*

80 DEVSEL*

81 VDDo

82 VSSo

83 STOP*

84 PERR*

85 SERR*

86 PAR

87 CBE[1]

88 AD[15]

89 VSSo

90 AD[14]

91 AD[13]

92 AD[12]

93 AD[11]

94 AD[10]

95 VDDo

96 VSSo

97 AD[9]

98 M66EN

99 AD[8]

100 CBE[0]*

101 AD[7]

102 AD[6]

103 AD[5]

104 VSSo

105 AD[4]

Pin Label

1-6 Conexant 100660E

CN8478/CN8474A/CN8472A/CN8471A 1.0 System Description

Multichannel Synchronous Communications Controller (MUSYCC™)

Pin

Number

106 AD[3]

107 AD[2]

108 AD[1]

109 AD[0]

110 VDDo

111 VSSo

112 TM[2]

113 TM[1]

114 TM[0]

115 TDAT[4]

116 TSYNC[4]

117 TCLK[4]

118 VDDi

119 VSS

Pin Label

Pin

Number

142 TSYNC[3]

143 TCLK[3]

144 EAD[0]

145 EAD[1]

146 EAD[2]

147 VDDo

148 VSSo

149 EAD[3]

150 EAD[4]

151 EAD[5]

152 EAD[6]

153 VSSo

154 EAD[7]

155 EAD[8]

Pin Label

1.1 Pin Descriptions

Pin

Number

178 EAD[24]

179 EAD[25]

180 EAD[26]

181 VDDo

182 VSSo

183 EAD[27]

184 EAD[28]

185 VDDc

186 VSS

187 EAD[29]

188 EAD[30]

189 EAD[31]

190 ECLK

191 VSSo

Pin Label

120 TDAT[0]

121 TSYNC[0]

122 TCLK[0]

123 TDAT[5]

124 TSYNC[5]

125 TCLK[5]

126 TDAT[1]

127 TSYNC[1]

128 TCLK[1]

129 TDAT[6]

130 TSYNC[6]

131 TCLK[6]

132 VDDc

133 VSS

134 TDAT[2]

135 TSYNC[2]

136 TCLK[2]

137 VSSo

156 VGG

157 VSS

158 EAD[9]

159 EAD[10]

160 EAD[11]

161 EAD[12]

162 EAD[13]

163 EAD[14]

164 VDDo

165 VSSo

166 EAD[15]

167 EAD[16]

168 EAD[17]

169 EAD[18]

170 EAD[19]

171 VDDi

172 VSS

173 EAD[20]

192 WR*(R/ WR*)

193 RD*(DS*)

194 ALE*(AS*)

195 EINT*

196 HOLD(BR*)

197 HLDA(BG*)

198 BGACK*

199 EBE[3]*

200 EBE[2]*

201 VDDo

202 VSSo

203 EBE[1]*

204 EBE[0]*

205 NC

206 NC

207 ROOF[7]

208 RCLK[7]

138 TDAT[7]

139 TSYNC[7]

140 TCLK[7]

141 TDAT[3]

174 EAD[21]

175 VSSo

176 EAD[22]

177 EAD[23]

100660E Conexant 1-7

1.0 System Description CN8478/CN8474A/CN8472A/CN8471A

1.1 Pin Descriptions Multichannel Synchronous Communications Controller (MUSYCC™)

Figure 1-5. CN8474A MPQF Pinout Configuration

ROOF[3]

RCLK[3]

RSYNC[3]

RDAT[3]

ROOF[2]

RCLK[2]

VDDp

VSS

RSYNC[2]

RDAT[2]

ROOF[1]

RCLK[1]

RSYNC[1]

RDAT[1]

VDDc

VSS

ROOF[0]

RCLK[0]

RSYNC[0]

RDAT[0]

TCK

TRST*

TMS

TDO

TDI

INTB*

INTA*

VDDo

PCLK

VSSo

PRST

GNT*

REQ*

AD[31]

AD[30]

AD[29]

AD[28]

VGG

161

EAD[12]

VSS

EAD[9]

EAD[10]

EAD[11]

157

158

159

160

156

VGG

155

EAD[8]

154

EAD[7]

153

VSSo

152

EAD[6]

151

EAD[5]

150

EAD[4]

149

EAD[3]

148

VSSo

147

VDDo

146

EAD[2]

145

EAD[1]

144

EAD[0]

143

TCLK[3]

142

TSYNC[3]

141

TDAT[3]

140

NC

139

NC

138

NC

137

VSSo

136

TCLK[2]

135

TSYNC[2]

134

TDAT[2]

133

VSS

132

VDDc

131

NC

130

NC

129

NC

TCLK[1]

128

TSYNC[1]

127

126

TDAT[1]

125

NC

124

NC

123

NC

122

TCLK[0]

121

TSYNC[0]

120

TDAT[0]

119

VSS

118

VDDp

117

NC

116

NC

115

NC

114

TM[0]

113

TM[1]

112

TM[2]

111

VSSo

110

VDDo

109

AD[0]

AD[1]

108

AD[2]

107

AD[3]

106

AD[4]

105

VDDc

VDDo

EBE[1]*

EBE[0]*NCNC

NC

NC

207

208

NC

1

NC

2

3

4

5

6

NC

7

NC

8

9

NC

NC

10

11

12

13

14

15

16

17

NC

NC

18

NC

19

NC

20

21

22

23

24

NC

25

NC

26

27

28

NC

29

NC

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

VSSo

201

202

203

204

205

206

HOLD(BR*)

HLDA(BG*)

BGACK*

EBE[3]*

EBE[2]*

196

197

198

199

200

VSSo

EAD[29]

EAD[30]

EAD[31]

ECLK

R*(R/WR*)

RD*(DS*)

ALE*(AS*)

EINT*

191

192

193

194

195

VSS

186

187

188

189

190

Preliminary

CN8474A

VDDo

VSSo

EAD[26]

EAD[27]

EAD[28]

180

181

182

183

184

185

EAD[25]

179

EAD[24]

178

EAD[23]

177

176

EAD[22]

VSSo

174

175

EAD[21]

EAD[19]

EAD[20]

VDDp

VSS

170

171

172

173

VSSo

EAD[13]

EAD[14]

EAD[15]

EAD[16]

EAD[17]

EAD[18]

169

VDDo

162

163

164

165

166

167

168

104

103

102

101

100

VSSo

VDDo

AD[9]

99989796959493929190898887

AD[8]

M66EN

AD[7]

CBE[0]*

AD[5]

AD[6]

VSSo

53

VSS

AD[27]

VSSo

AD[26]

AD[25]

AD[24]

IDSEL

CBE[3]*

AD[23]

AD[22]

VSSo

VDDo

AD[21]

AD[20]

VSS

VDDp

AD[19]

AD[18]

AD[17]

AD[16]

VSSo

CBE[2]*

FRAME*

IRDY*

VSS

VDDc

TRDY*

DEVSEL*

VSSo

VDDo

STOP*

SERR*

PERR*

PAR

868584838281807978777675747372717069686766656463626160595857565554

AD[15]

CBE[1]*

VSSo

AD[14]

AD[13]

AD[12]

AD[11]

AD[10]

NOTE(S): An active low signal is denoted by a trailing asterisk (*).

1-8 Conexant 100660E

CN8478/CN8474A/CN8472A/CN8471A 1.0 System Description

Multichannel Synchronous Communications Controller (MUSYCC™)

Figure 1-6. CN8472A MQFP Pinout Configuration

VDDc

VDDo

VSSo

EAD[24]

EAD[25]

EAD[26]

EAD[27]

EAD[28]

178

179

180

181

182

183

184

185

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

VDDp

VSS

NC

NC

NC

NC

NC

NC

ROOF[1]

RCLK[1]

RSYNC[1]

RDAT[1]

NC

NC

VDDc

VSS

NC

NC

ROOF[0]

RCLK[0]

RSYNC[0]

RDAT[0]

TCK

TRST*

TMS

TDO

TDI

INTB*

INTA*

VDDo

PCLK

VSSo

PRST

GNT*

REQ*

AD[31]

AD[30]

AD[29]

AD[28]

VGG

VDDo

EBE[1]*

EBE[0]*NCNC

NC

NC

207

208

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29