CONEX CN8380EPF Datasheet

Advance Information

This document contains information on a product under development. The parametric information

contains target para meters that are subject to c h ange.

CN8380

Quad T1/E1 Line Interface

The CN8380 is a fully integrated quad line interface unit for both 1.544 Mbps (T1) and

2.048 Mbps (E1) app lications . It is de signed to complement T1/E1 f ramers or oper ate as

a stand-alone line interface to synchronous or plesiochronous mappers and

multiplexers. The device can be controlled through a host mode serial port or by

hardware mode operation, where device control and status are obtained through

non-multiplexed dedicated pins. Many of these pins are also dedicated to individual

channels for maximum flexibility and for use in redundant systems. Integrated in the

CN8380 device is a clock rate adapter (CLAD), which provides various low-jitter

programmable system clock outputs. The receive section of the CN8380 is designed to

recover encoded signals from lines having up to 12 dB of attenuation. The transmit

section consists of a programmable, precision pulse shaper.

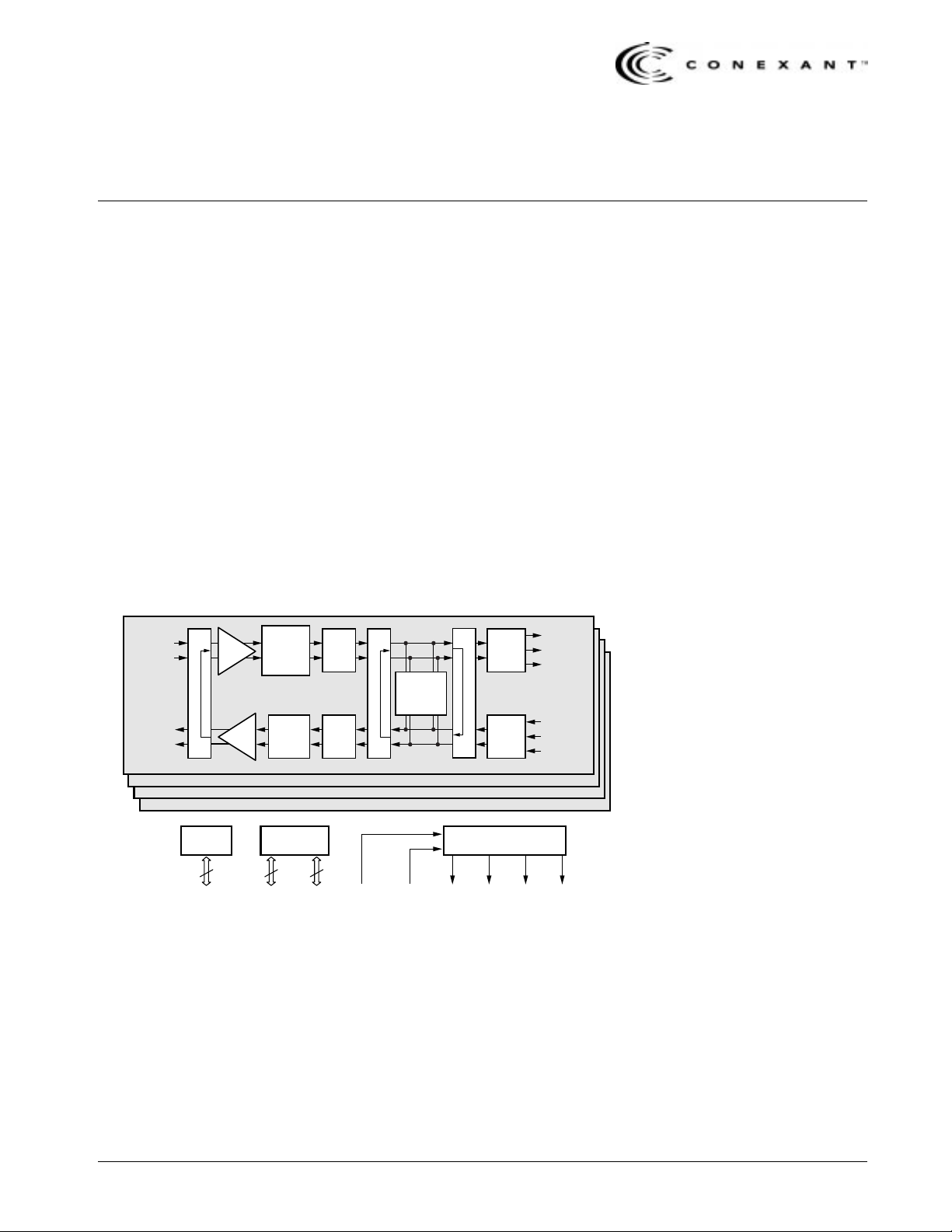

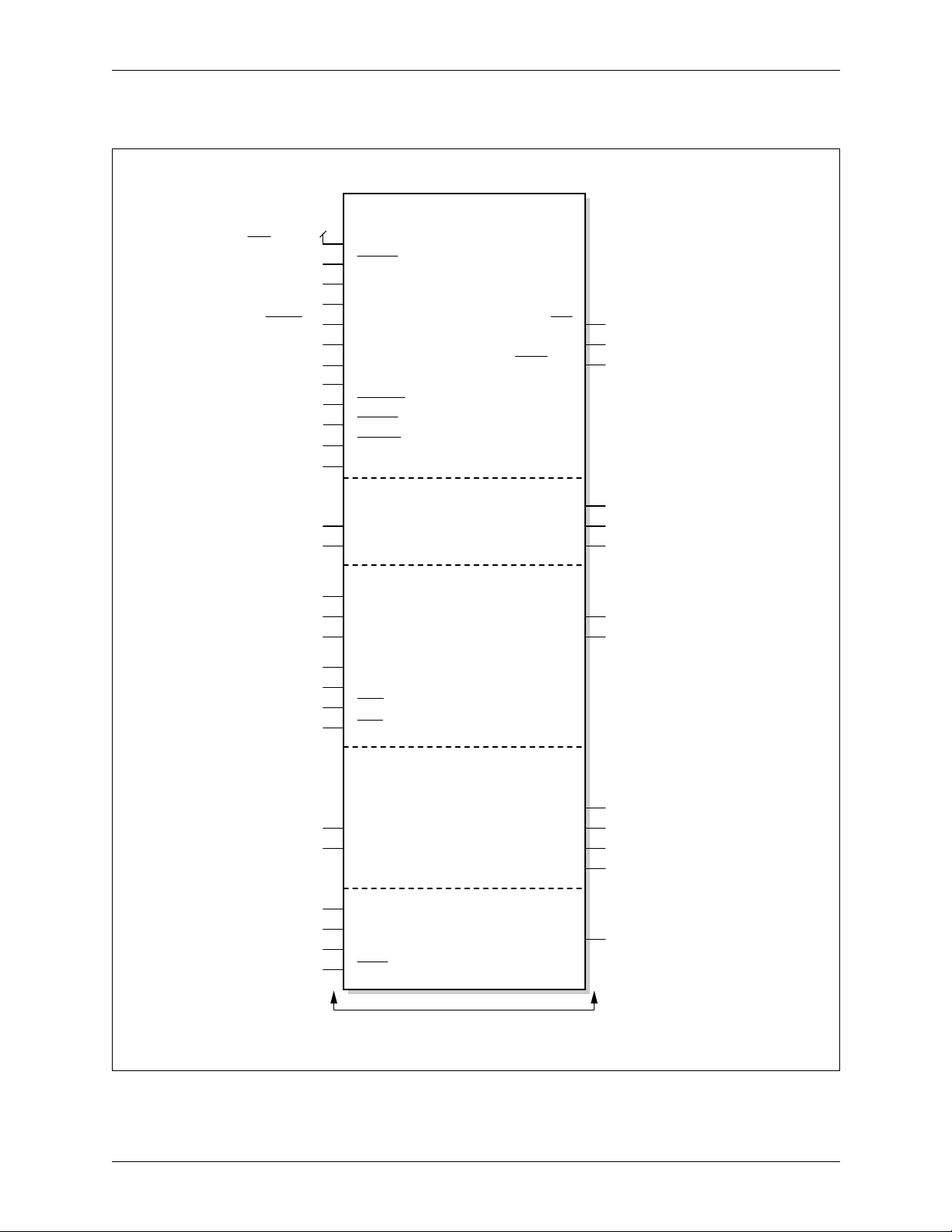

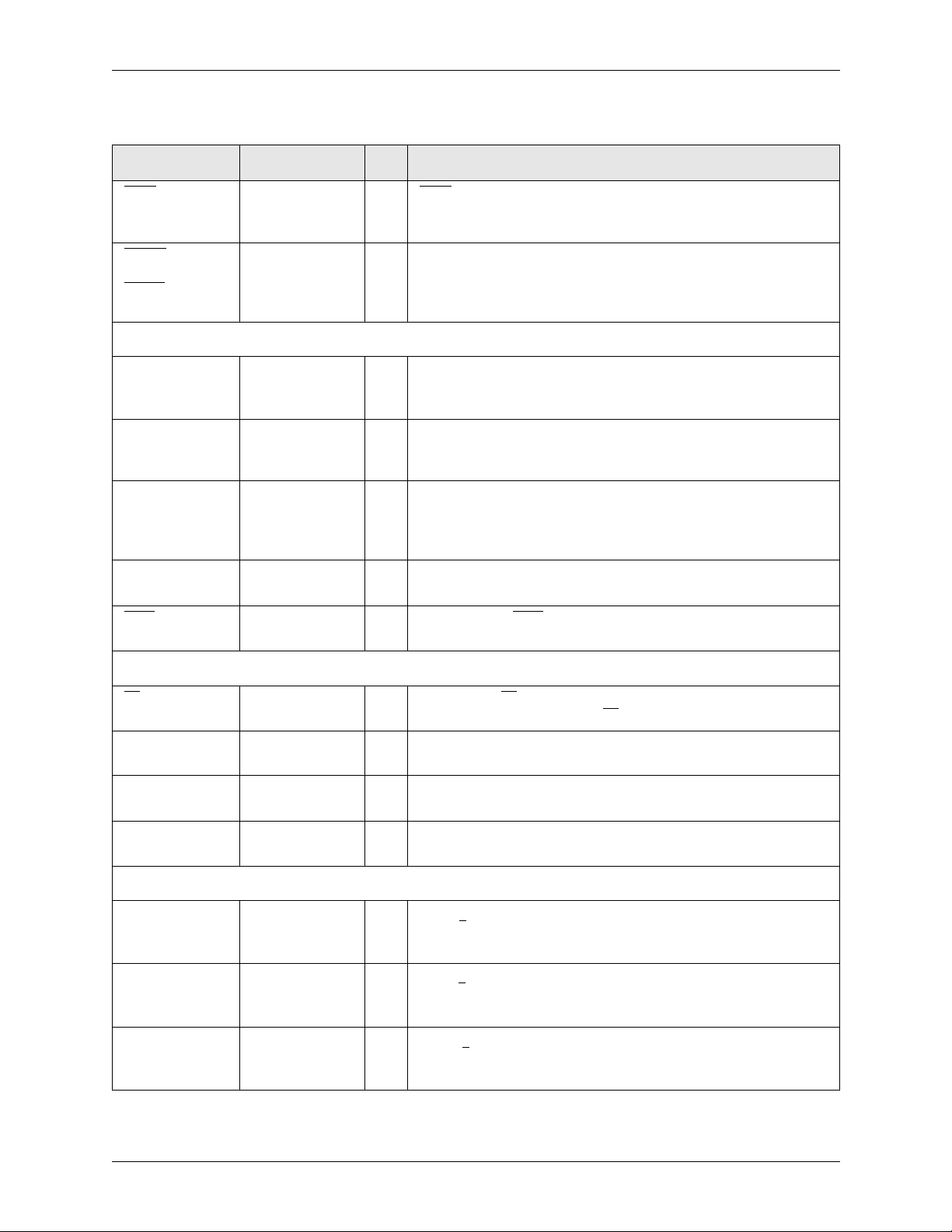

Functional Block Diagram

RTIP[1]

RRING[1]

XTIP[1]

XRING[1]

8380_001

Receiver

Driver

Local Analog Loopback

JTAG

Test Port

5

JTAG

Signals

Test

Control and

Alarm Signals

Clock

and

Data

Recovery

Pulse

Shaping

Control

47 4

Host

Serial

Port

RLOS

Detect

TAIS

10 MHz

Reference

Attenuator

Local Digital Loopback

Variable

Fixed

Reference

Jitter

1.544

MHz

Decode

Remote Line Loopback

Decode

Clock Rate Adapter

2.048

MHz

ZCS

ZCS

32.768

MHz

RPOSO[1]

RNEGO[1]

RCKO[1]

TPOSI[1]

TNEGI[1]

TCLK[1]

LIU #1

LIU #2

LIU #3

LIU #4

8 kHz–32 MHz

Selectable

Distinguishing Features

• Four T1/E1 short haul line interface s

in a single chip

• On-chip CLAD /system synchronizer

• Digital (crystal-less) jitter attenuators

selectable for transmitter/receiver on

each line interface

• Meets AT&T pub 62411 jitter spec s

• Meets ITU G.703, ETS 300 011

(PSTNX) Conn ections

• AMI/B8ZS/ HDB3 line codes

• Host serial port or hardware only

control modes

• On-chip receive clock recovery

• Common transformers for 120/75

E1 and 100

Ω

T1

Ω

• Low-power 3.3 V power supply

• Transmitter performance monitor

• Compatible with latest ANSI, ITU-T,

and ETSI standards

• 128-pin MQFP packa ge

• Remote and local loopbacks

Applications

• SONET/SDH multipl exers

• T3 and E3/E4 (PDH) multiplexers

• ATM multiplexers

• Voice compression and vo ice

processing equipment

• WAN routers and bridges

• Digital loop carrier terminals (DLC)

• HDSL terminal units

• Remote concentrators

• Central office equip ment

• PBXs and rural switches

• PCM/voice channel banks

• Digital access and cross-connect

systems (DACS)

Data Sheet Advance Information N8380DSA

April 26, 1999

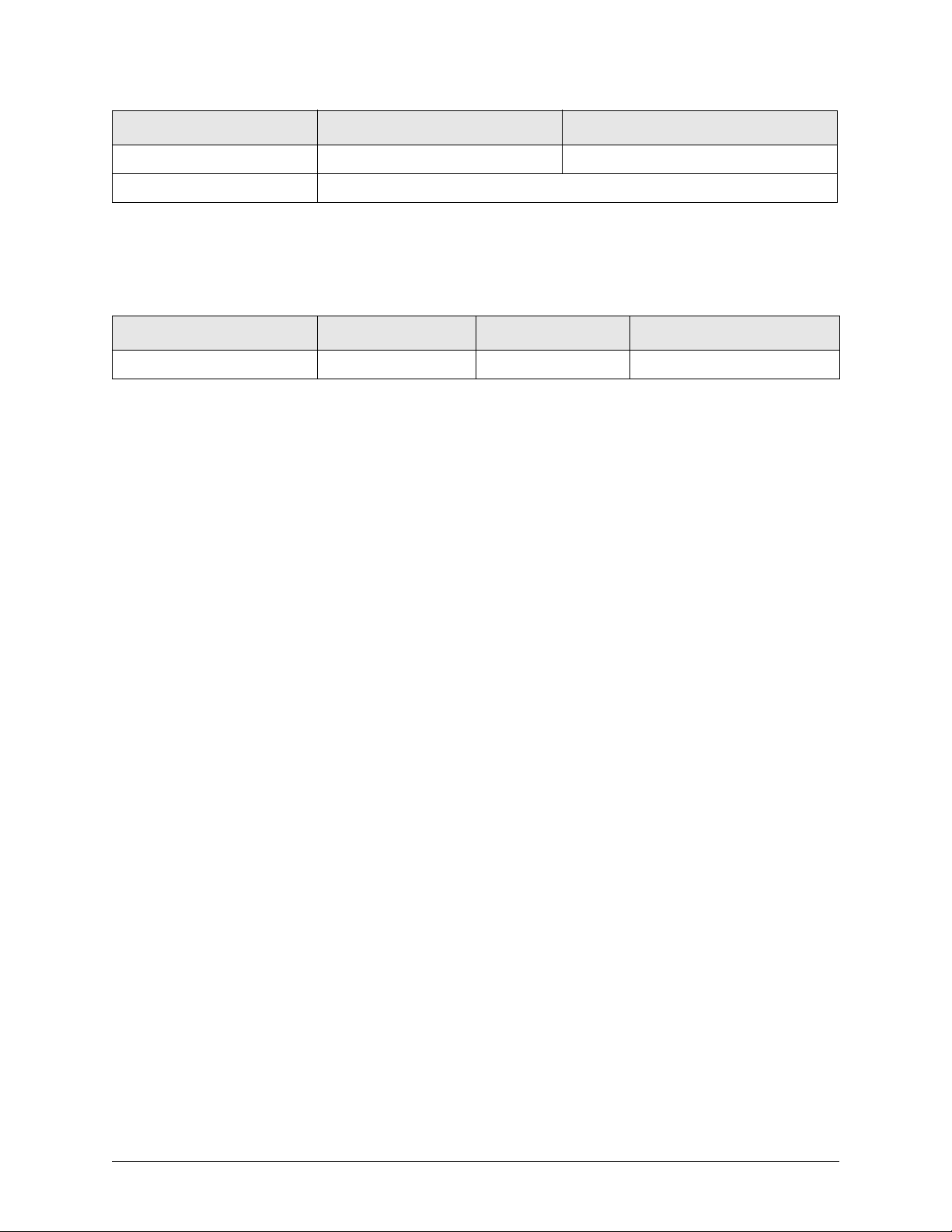

Ordering Information

Model Number Package Operating Temperature

CN8380EPF 128-pin MQFP –40 °C to +85 °C

CN8398EVM BT00–D660–001

Revision History

Revision Level Date Description

A Advance April 26, 1999 Created

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is

assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent rights of Conexant other than for circuitry embodied in Conexant

products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without

notice.

Conexant and “What’s Next in Communications Technologies” are trademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered

trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc.

Print e d in U.S.A.

All Rights Reserved

Reader Response:

suggestions via e-mail to Conexant Reader Response@conexant.com. Sorry, we can't answer your technical

questions at this address. Please contact your local Conexant sales office or local field applications engineer if you

have technical questions.

To im prove the qu ali ty of our publica tio ns, we welco me your fe edb ack. Please send com me nts or

N8380DSA Conexant

Advance Information

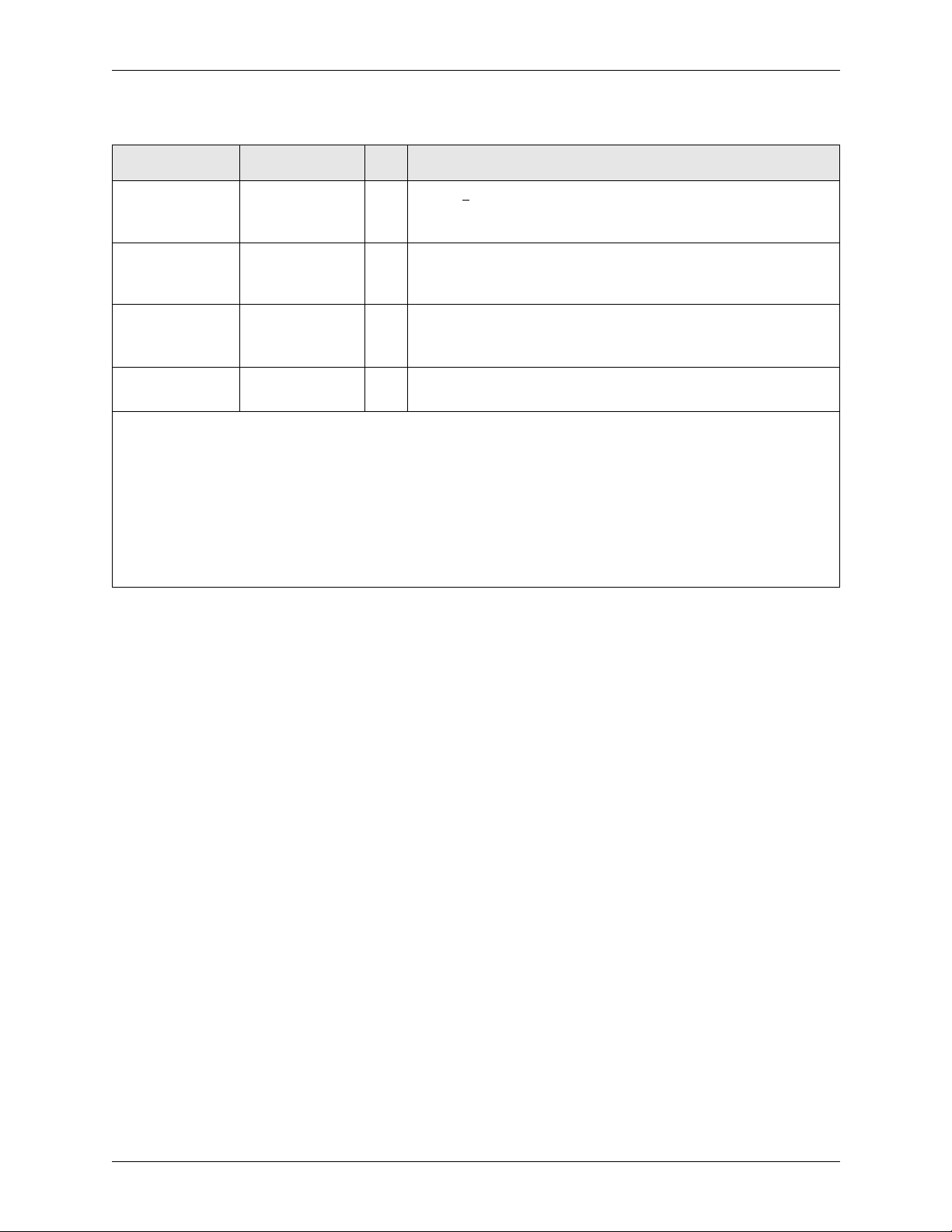

CN8398EVM Octal T1/E1 Evaluation Module

CN8380 Quad T1/E1 LIU CN8380 Quad T1/E1 LIU

Eight RJ48C T1 or E1 Line Connections

Microprocessor

Control

8380_002

Local PCM Highway (i.e., 2 @ 8192 kbps)

Contact a Conexant representative for EVM avail a bility and price.

Detailed Feature Summary

Interface Compatibility

• T1.102–1993

• G.703 at 1.544 or 2.048 Mbps

• ITU-T Recommendation I.431

Receive Line Interface

• External Termination

• Equalizer compensation for – 20 dB

bridged monitor levels

• + 3 dB to –12 dB receiver sensitivity

Transmit Line Interface

• Pulse shapes for 0–655 ft., in 133 ft.

steps (T1 DSX–1)

• External termination for improved

return loss

• Line driver enable/disable for

protection switching

• Output short circuit protection (for

BABT applications)

Jitter Atten uator Elastic Store

• Receive or transmit direction

• 8-, 16-, 32-, 64- , or 128-bit depth

• Automatic and manual centering

Line Codes

• Bipolar alternate mark inversi on line

coding

• Optional zero code suppression:

– Independent tra nsmit and receive

– T1: B8ZS

– E1: HDB3

Loopbacks

• Remote loopback towards line

– With or without JAT

– Retains BPV transparency

• Local loopback towards system

– Analog line loopback

– Local digital loopback

• Simultaneous local and remote line

loopbacks

Clock Rate Adapter

• Outputs jitter attenuated line rate

clock

– CLK1544 = 1544 k (T1)

– CLK2048 = 2048 k (E1)

• CLAD output supports 14 output

clock frequencies: 8 kHz to

32,768 kHz

CN8398 Octal T1/E1 Framer

• Programma ble input timing

reference:

– Receive recovered clock from any

channel

– Internal clock (REFCKI)

–CLADI

• Subrate CLADI timing reference:

– Line rate

N

÷2

, N = 0 to 7

– References as low as 8 kHz

Host Serial Interface

• Compatible with existing framers

• Compatible with microprocessor

serial ports

• Bit rates up to 8 Mbps

In-Service Performance Monitoring

• Transmit alarm detectors:

– Loss of Transmit Clock (TLOC)

– Transmit Short Circuit (TSHORT)

• Receive alarm detectors:

– Loss of Signal (RLOS)

– Loss of Analog Input (RALOS)

– Bipolar/Line Code Violations

• Automatic and on-demand transmit

alarms:

– AIS following TLOC

– Automatic AIS clock switching

N8380DSA Conexant

Advance Information

N8380DSA Conexant

Advance Information

Table of Contents

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .xi

1.0 Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

2.0 Circuit Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.1 Overview

2.2 Configuration and Control

2.2.1 Hardware Mode

2.2.2 Host Mode

2.2.3 Host Serial Control Interface

2.2.4 Reset

2.3 Receiver

2.3.1 Data Recovery

2.3.2 Clock Recovery

2.3.3 Receive Jitter Attenuator

2.3.4 RZCS Decoder

2.3.5 Receive Digital Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.2.4.1 Power-on Reset

2.2.4.2 Hard Reset

2.2.4.3 Soft Reset

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.3.1.1 Raw Receive Mode

2.3.1.2 Sensitivity

2.3.1.3 Bridge Mode

2.3.1.4 Loss Of Signal Detector

2.3.2.1 Phase Lock Loop

2.3.2.2 Jitter Tolera nce

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

2.3.5.1 Bipolar Mode

2.3.5.2 Unipolar Mode

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

N8380DSA Conexant v

Advance Information

Table of Contents CN8380

Quad T1/E1 Line Interface

2.4 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.4.1 Transmit Digital Interface

2.4.1.1 Bipolar Mode

2.4.1.2 Unipolar Mode

2.4.2 TZCS Encoder

2.4.3 Transmit Jitter Attenuator

2.4.4 All 1s AIS Generator

2.4.5 Pulse Shaper

2.4.6 Driver

2.4.7 Transmitter Ou tput Monitoring

2.5 Loopbacks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

2.5.1 Local An alo g Loop back

2.5.2 Local Dig ital Loopback

2.5.3 Remote Line Loopback

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.4.6.1 Transmit Termination Options

2.4.6.2 Output Disable

2.4.7.1 S hort Circuit Detect

2.4.7.2 Driver Performance Monitor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.6 Jitter Attenuator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.7 Clock Rate Adapter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2.7.1 Inputs

2.7.2 Outputs

2.7.3 Configuration Options

2.8 Test Access Port (JTAG). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

2.8.1 Instructions

2.8.2 Device Identification Register

3.0 Registers

3.1 Address Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.2 Global Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

00—Device Identification (DID)

01—Global Configurat i on (GC R)

02—CLAD Configuration (CLAD_C R)

03—CLAD Frequency Select (CSEL)

04—CLAD Phase Detector Scale Factor (CPHASE)

05—CLAD Test (CTEST)

06—CLAD Status (CSTAT)

07—(FREG)

08—(TESTA1)

09—(TESTA2)

0A—(FUSE_CH1)

0B—(FUSE_CH2)

0C—(FUSE_CH3)

0D—(FUSE_CH4)

0E—(FUSE_RES)

0F—(TESTD)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 -3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 -3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

vi Conexant N8380DSA

Advance Information

CN8380 Table of Contents

Quad T1/E1 Line Interface

3.3 Per Channel Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

10, 20, 30, 40—Jitter Attenuator Configuration (JAT_CR)

11, 21, 31, 41—Receiver Configuration (RLIU_CR)

12, 22, 32, 42 —Tr ansmitter Configuration (TLIU_CR)

13, 23, 33, 43—LIU Control (LIU_CTL)

15, 25, 35, 45—Alarm Status (ALARM)

16, 26, 36, 46—Interrupt Status Register (ISR)

17, 27, 37, 47—Interrupt Enable Register (IER)

3.4 Transm itter Shape Registers

18 - 1F—Transmit PULSE Shape CONFIGURATION (SHAPE1)

28 - 2F—Transmit PULSE Shape CONFIGURATION (SHAPE2)

38 - 3F—Transmit PULSE Shape CONFIGURATION (SHAPE3)

48 - 4F—Transmit PULSE Shape CONFIGURATION (SHAPE4)

50—(TESTA3)

51—(TESTA4)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

4.0 Electrical/Mechanical Specifications

4.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

. . . . . . . . . . . . . . . . . . . . . . . 3-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

. . . . . . . . . . . . . . . . . . . . . . . . . 3-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

. . . . . . . . . . . . . . . . . . . . 3-17

. . . . . . . . . . . . . . . . . . . . 3-17

. . . . . . . . . . . . . . . . . . . . 3-17

. . . . . . . . . . . . . . . . . . . . 3-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2 Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.3 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.4 Performan ce Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.5 AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4.6 Packaging. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

Appendix A: Applicable Standards

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Appendix B: External Component Specifications

Appendix C: Acronym List

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

N8380DSA Conexant vii

Advance Information

Table of Contents CN8380

Quad T1/E1 Line Interface

viii Conexant N8380DSA

Advance Information

CN8380 List of Figures

Quad T1/E1 Line Interface

List of Figures

Figure 1-1. CN8380 Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-2

Figure 1-2. CN8380 Logic Diagram (Host Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

Figure 1-3. CN8380 Logic Diagram (Hardware Mode). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4

Figure 2-1. Detailed Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

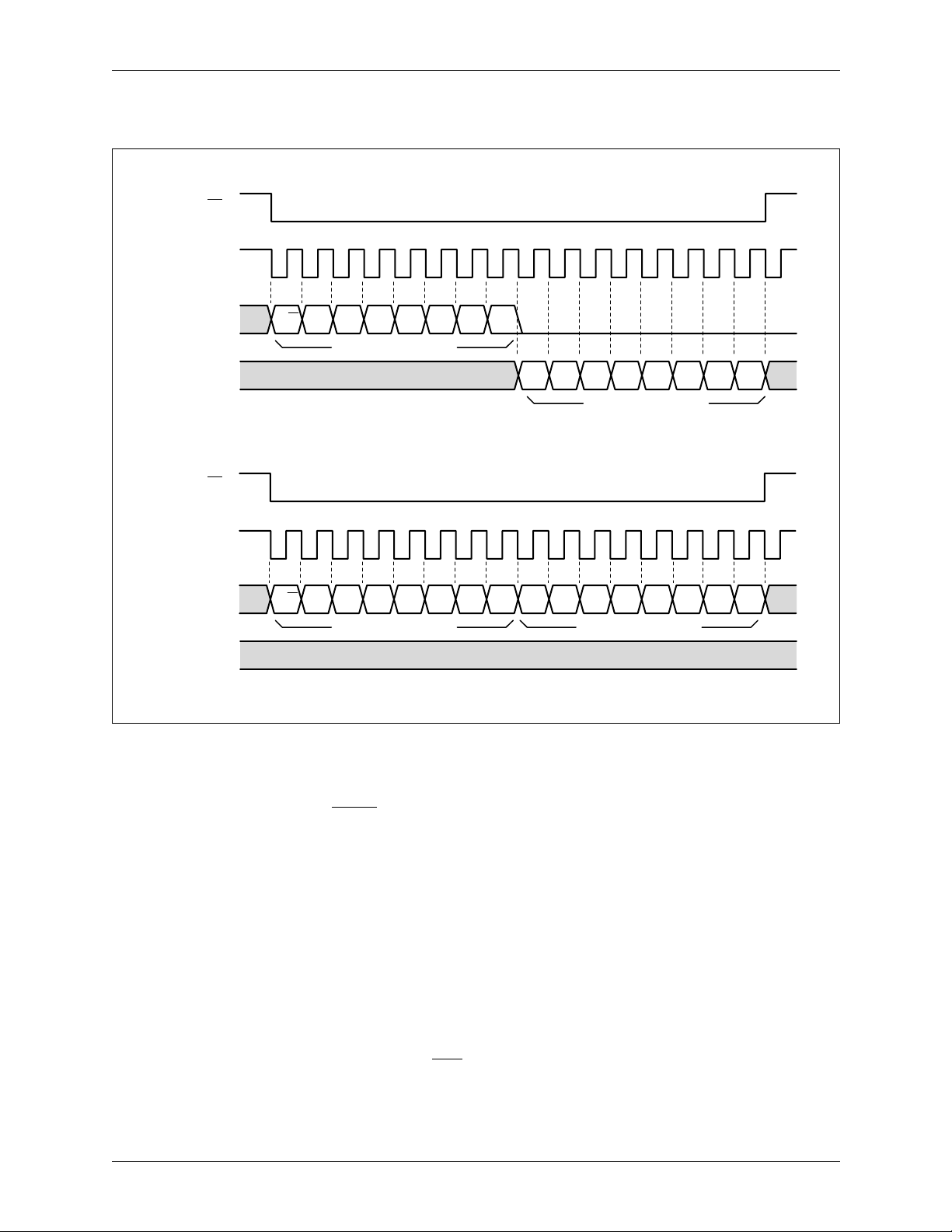

Figure 2-2. Host Serial Port Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

Figure 2-3. Receiver Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

Figure 2-4. Raw Mode Receiver Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

Figure 2-5. Transmitter Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

Figure 2-6. Transmit Pulse Shape. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

Figure 2-7. Transmit Termination Components. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-15

Figure 2-8. Receiver Input Jitter Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-23

Figure 2-9. Typical JAT Transfer Characteristics with Various JAT Sizes . . . . . . . . . . . . . . . . . . . . . .2-24

Figure 2-10. CLAD Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-25

Figure 4-1. XOE

Figure 4-2. RESET

Figure 4-3. CLAD Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-7

Figure 4-4. Receiver Signals Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8

Figure 4-5. Transmitter Signals Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-9

Figure 4-6. Host Serial Port Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-10

Figure 4-7. Host Serial Port Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-11

Figure 4-8. Host Serial Port Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-11

Figure 4-9. JTAG Interface Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-12

Figure 4-10. 128-Pin MQFP Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-13

Figure B-1. Minimum Hardware Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-2

Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5

Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-6

N8380DSA Conexant ix

Advance Information

List of Figures CN8380

Quad T1/E1 Line Interface

x Conexant N8380DSA

Advance Information

CN8380 List of Tables

Quad T1/E1 Line Interface

List of Tables

Table 1-1. Hardware Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5

Table 2-1. Line Compatible Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

Table 2-2. Transmitter Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

Table 2-3. Transmit Pulse Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

Table 2-4. Transmit Termination Option A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-16

Table 2-5. Transmit Termination Option B. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-16

Table 2-6. Transmit Termination Option C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-17

Table 2-7. Transmit Termination Option D. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-17

Table 2-8. Transmit Termination Option E. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-18

Table 2-9. Loopback Controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-20

Table 2-10. CLAD Outputs and Frequencies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26

Table 2-11. CLAD Reference Frequencies and Configuration Examples. . . . . . . . . . . . . . . . . . . . . . . . .2-27

Table 2-12. Sample Alternate Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-28

Table 2-13. JTAG Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-29

Table 2-14. Device Identification JTAG Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-29

Table 3-1. Address Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

Table 3-2. Transmitter Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-14

Table 4-1. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

Table 4-2. Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

Table 4-3. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

Table 4-4. Performance Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

Table 4-5. XOE

Table 4-6. RESET

Table 4-7. CLAD Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-7

Table 4-8. Receiver Signals Timing Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8

Table 4-9. Transmitter Signals Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-9

Table 4-10. Host Serial Port Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-10

Table 4-11. JTAG Interface Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-12

Table A-1. Applicable Standards. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-1

Table B-1. Transformer Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-1

Table B-2. REFCKI (10 MHz) Crystal Oscillator Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-1

Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5

Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-6

N8380DSA Conexant ix

Advance Information

List of Tables CN8380

Quad T1/E1 Line Interface

xii Conexant N8380DSA

Advance Information

1

1.0 Pin Descriptions

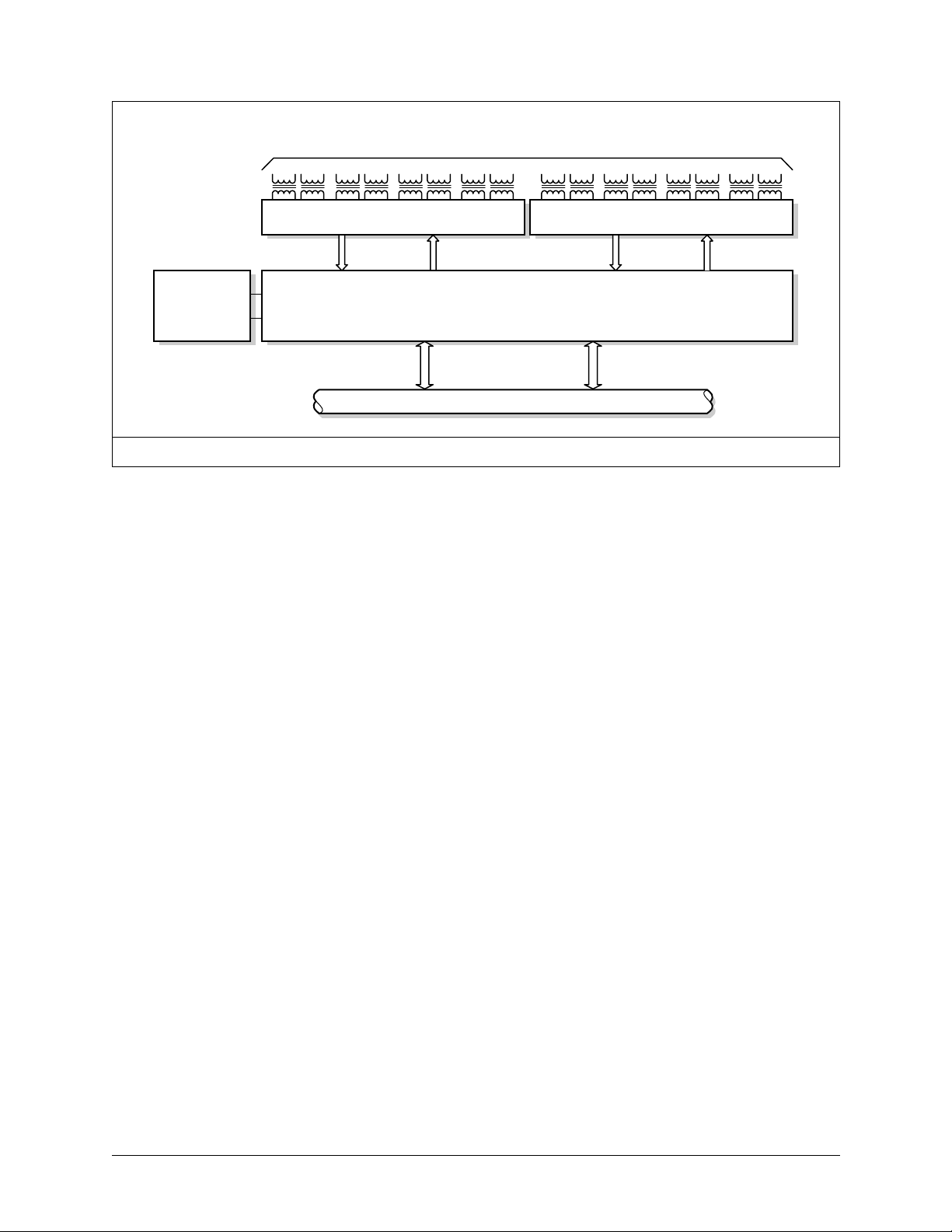

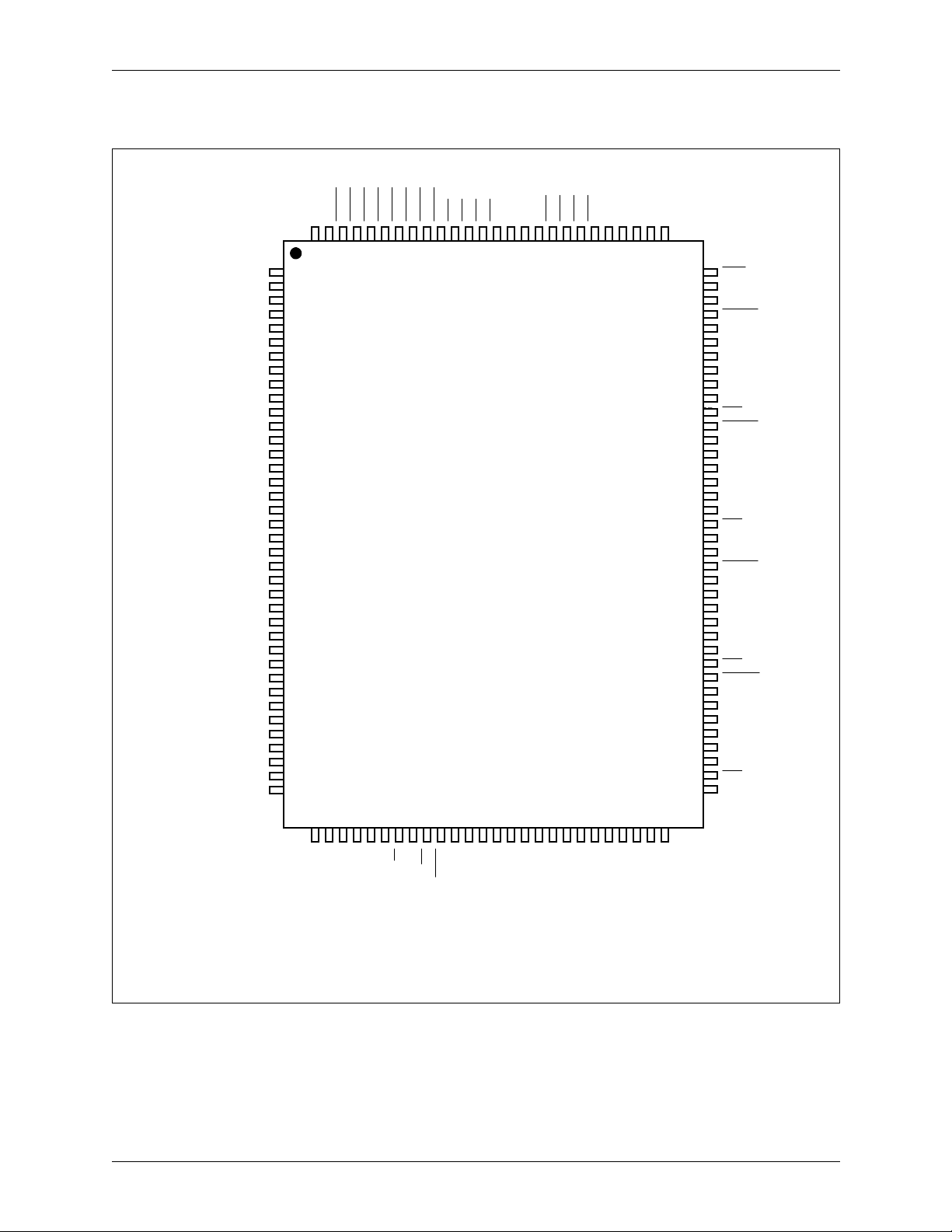

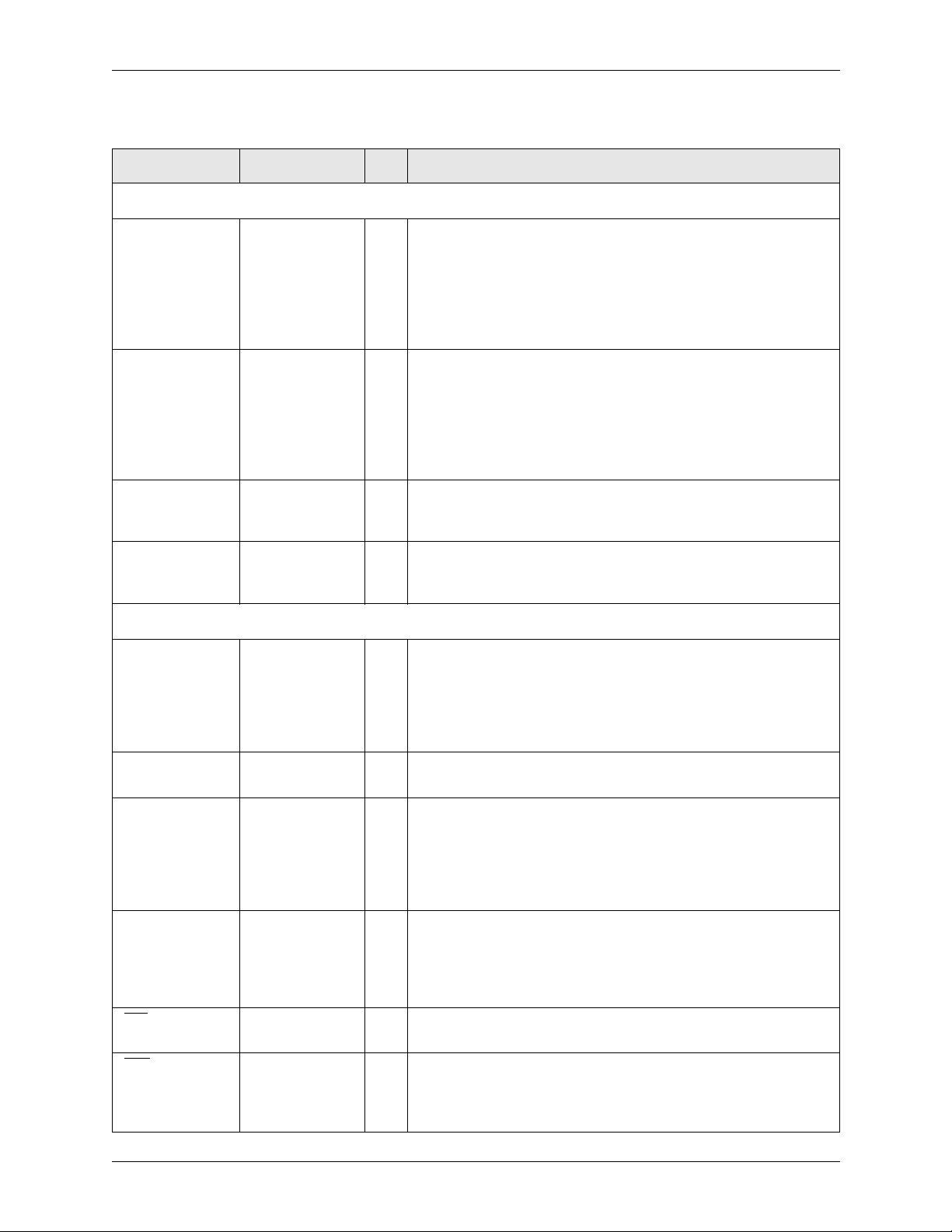

The CN8380 is packaged in a 128-pin metric quad flat pack (MQFP). A pinout

diagram is illustrated in Figure 1-1. Logic diagrams are illustrated in Figure 1-2

and Figure 1-3. Pin labels and numbers, input/output functions, and descriptions

are provided in Table 1-1.

The following input pins contain an internal pull-up resistor (> 50 kΩ) and

may remain unconnected if unused or if the active high input state is desired:

XOE

[1:4]

TAIS

[1:4]

RAWMD

RLOOP

LLOOP

HM

UNIPOLAR

JDIR/SCLK

JSEL(2)/SDI

JSEL(1)/CS

JSEL(0)

RESET

HTERM

CLK_POL

PTS(2:0)

TDI (Unused if JTAG not connected)

TMS (Disables JTAG if not connected)

TCK (Unused if JTAG not connected)

TRST

[1:4]

[1:4]

[1:4]

(Unused if JTAG not connected)

N8380DSA Conexant 1-1

Advance Information

1.0 Pin Descriptions CN8380

Figure 1-1. CN 8380 Pinout Diagram

CLADI

VAACL

GNDCL

REFCKI

VSS

VDD

CLK32

CLK1544

CLK2048

CLADO

VSS

RNEGO/BPV [4]

RPOSO/RDATO [4]

TPOSI/TDATI [4]

RNEGO/BPV [3]

RPOSO/RDATO [3]

TPOSI/TDATI [3]

RNEGO/BPV [2]

RPOSO/RDATO [2]

TPOSI/TDATI [2]

RNEGO/BPV [1]

RPOSO/RDATO [1]

TPOSI/TDATI [1]

VDD

RCKO [4]

TNEGI [4]

TCLK [4]

RCKO [3]

TNEGI [3]

TCLK [3]

VSS

VDD

RCKO [2]

TNEGI [2]

TCLK [2]

RCKO [1]

TNEGI [1]

TCLK [1]

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

EACKI

TACKI

128

127

RLOOP [2]

RLOOP [3]

RLOOP [4]

126

125

124

LLOOP [3]

LLOOP [4]

RLOOP [1]

123

122

121

TAIS [4]

LLOOP [1]

LLOOP [2]

120

119

118

128-Pin MQFP

TAIS [1]

TAIS [2]

TAIS [3]

117

116

115

CN8380

VSS

VDD

UNIPOLAR

114

113

112

RLOS [3]

RLOS [4]

111

110

RLOS [1]

RLOS [2]

109

108

VGG

107

Quad T1/E1 Line Interface

TDO

TDI

TMS

TCK

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

85

TRST

VAA

GND

RAWMD [4]

RRING [4]

RTIP [4]

VAAT [4]

GNDT [4]

XRING [4]

XTIP [4]

XOE [4]

RAWMD [3]

RRING [3]

RTIP [3]

VAAT [3]

GNDT [3]

XRING [3]

XTIP [3]

XOE [3]

GNDR

VAAR

RAWMD [2]

RRING [2]

RTIP [2]

VAAT [2]

GNDT [2]

XRING [2]

XTIP [2]

XOE [2]

RAWMD [1]

RRING [1]

RTIP [1]

VAAT [1]

GNDT [1]

XRING [1]

XTIP [1]

XOE [1]

HM

616263

N.C.

PTS(2)

PTS(1)

64

PTS(0)

LEGEND:

39404142434445464748495051

IRQ

RESET

HTERM

JATERR [4]

JATERR [3]

JATERR [2]

JSEL(0)

JDIR / SCLK

JSEL(1) / CS

JSEL(2) / SDI

JATERR [1] / SDO

CLK_POL

52

53545556575859

VSS

ZCS

N.C.

N.C.

VDD

N.C.

N.C.

N.C.

N.C.

60

N.C.

[#] - Port Number

(#) - Bit Number

8380_003

1-2 Conexant N8380DSA

Advance Information

CN8380 1.0 Pin Descriptions

Quad T1/E1 Line Interface

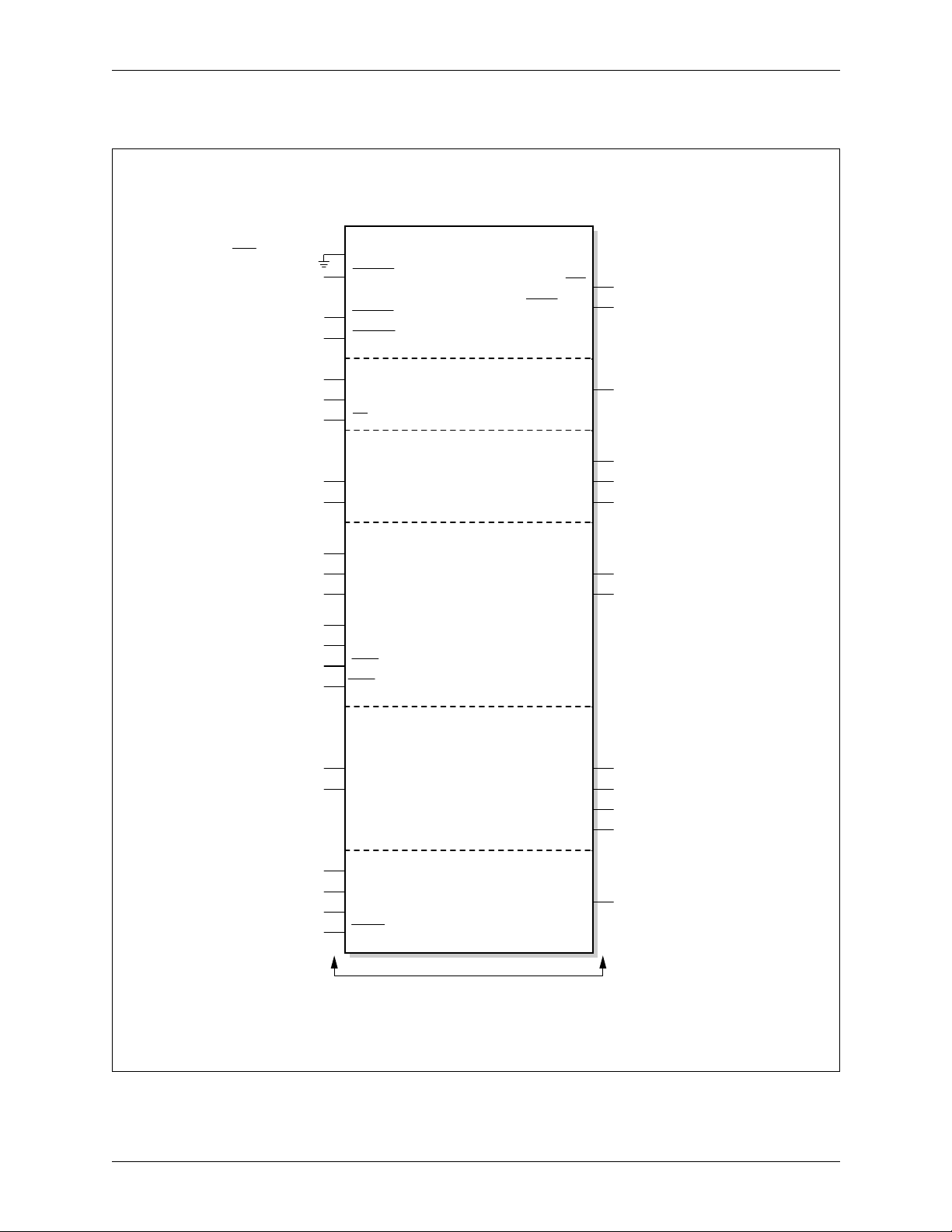

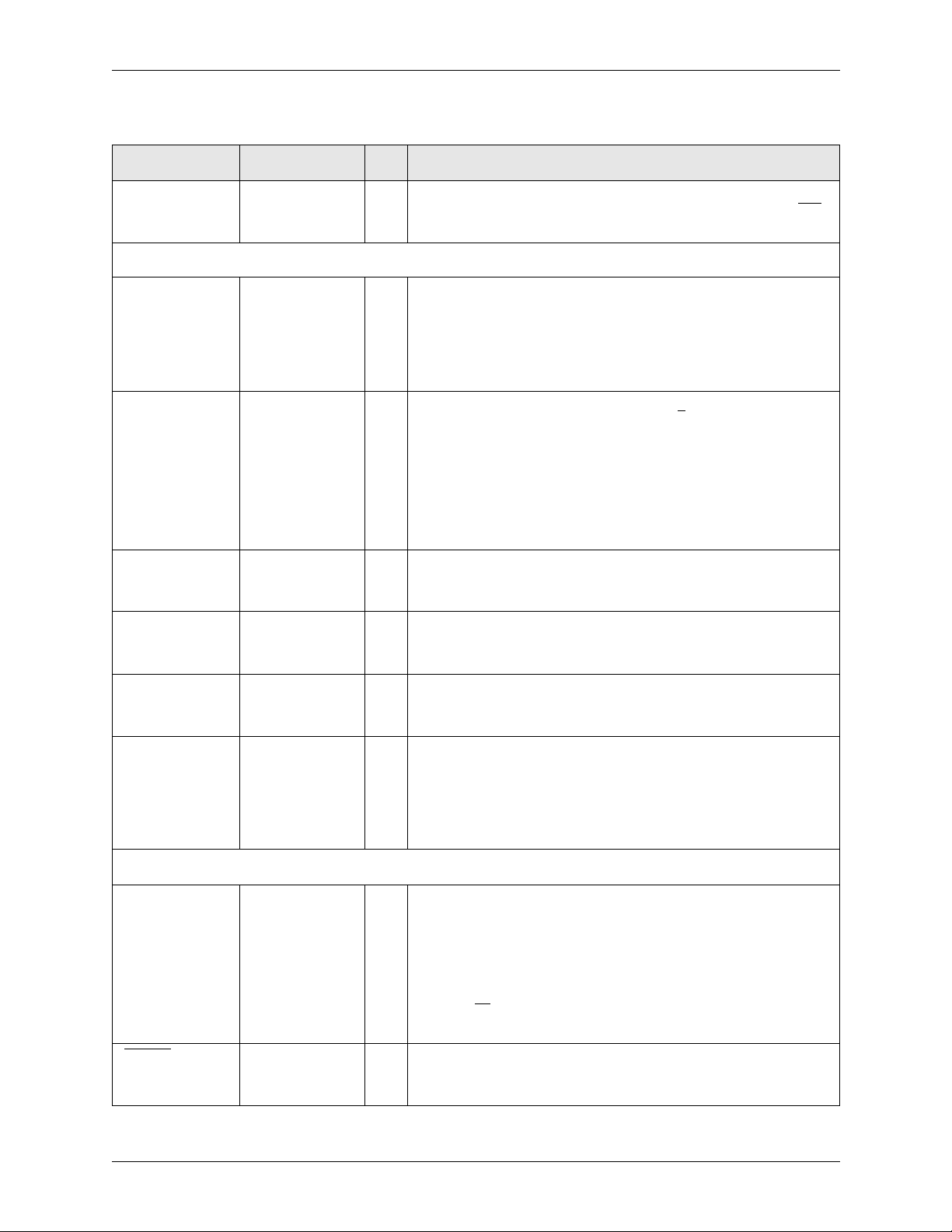

Figure 1-2. CN83 80 Logic Diagram (Ho s t Mode)

Hardware/Host Mode

Hardware/Host Mode

Local Loopback

Local Loopback

Remote Loopback

Remote Loopback

Serial Data In

Serial Data In

Serial Clock In SCLK

Serial Chip Select

Transmit Positive Rail

Transmit Negative Rail

Serial Clock In SCLK

Serial Chip Select

Receive Tip

Receive Tip

Receive Ring

Receive Ring

Transmit Clock

Transmit Clock

Transmit Positive Rail

Transmit Negative Rail

PIO

I

I

I

I

I

I

I

I

PIO

I

I

I

I

I

I

I

I

I

I

I

I

HM

HM

RESETHardware Reset

RESETHardware Reset

LLOOP[1:4]

LLOOP[1:4]

RLOOP[1:4]

RLOOP[1:4]

SDI

SDI

CS

CS

RTIP[1:4]

RTIP[1:4]

RRING[1:4]

RRING[1:4]

TCLK[1:4]

TCLK[1:4]

TPOSI[1:4]

TPOSI[1:4]

TNEGI[1:4]

TNEGI[1:4]

Host Mode

Host Mode

Hardware

Control

Hardware

Interface

Control

Interface

Serial Port

Serial Port

Interface

Interface

(SERIO)

RLOS[1:4]

RLOS[1:4]

(SERIO)

Receiver

Receiver

(RCVR)

(RCVR)

Transmitter

Transmitter

(XMTR)

(XMTR)

RCKO[1:4]

RCKO[1:4] Receive Clock

RPOSO[1:4] Receive Positive Rail

RPOSO[1:4] Receive Positive Rail

RNEGO[1:4]

RNEGO[1:4]

XTIP[1:4]

XRING[1:4]

XRING[1:4] Transmit Ring

IRQ

IRQ

SDO

SD O Serial Data Out

XTIP[1:4] Transmit Tip

Interrupt Request

O

Interrupt Request

O

Receive Loss of Signal Status

O

Receive Loss of Signal Status

O

Serial Data Out

O

O

O

Receive Clock

O

O

O

Receive Negative Rail

O

Receive Negative Rail

O

Transmit Tip

O

O

Transmit Ring

O

O

1544 kHz All 1s Clock

1544 KHz All Ones Clock

2048 kHz All 1s Clock

2048 KHz All Ones Clock

Transmit Output Enable

Transmit Output Enable

Transmit All 1s

Transmit All Ones TAIS[1:4]

CLAD Input CLK32 32.768 MHz Clock Out

CLAD Input CLK32 32.768 MHz Clock Out

Test Mode Select

Test Mode Select

Test Data In

Test Data In

Test Reset In

Test Reset In

8380_004

I

I

I

I

I

I

I

I

I

I

TACKI

I

EACKI

I

XOE[1:4]

I

TAIS[1:4]

I

CLADI

I

I

REFCKIReference Clock

I

TCKTest Clock In

I

TMS

I

TDI

I

TRST

TACKI

EACKI

XOE[1:4]

Clock Rate

Clock Rate

Adapter (CLAD)

Adapter (CLAD)

CLADI

REFCKIReference Clock

Boundary Scan

TCKTest Clock In

TMS

TDI

TRST

PIO = Programmable I/O

Boundary Scan

(JTAG)

(JTAG)

I = Input, O = Output

I = Input, O = Output

PIO = Programmable I/O

O

O

CLK1544

CLK1544

CLK2048 E1 Line Rate Clock Out

CLK2048 E1 Line Rate Clock Out

CLADO

CLADO

TDO

TDO

T1 Line Rate Clock Out

O

T1 Line Rate Clock Out

O

O

O

CLAD Output

O

O

CLAD Output

Test Data Out

O

Test Data Out

O

N8380DSA Conexant 1-3

Advance Information

1.0 Pin Descriptions CN8380

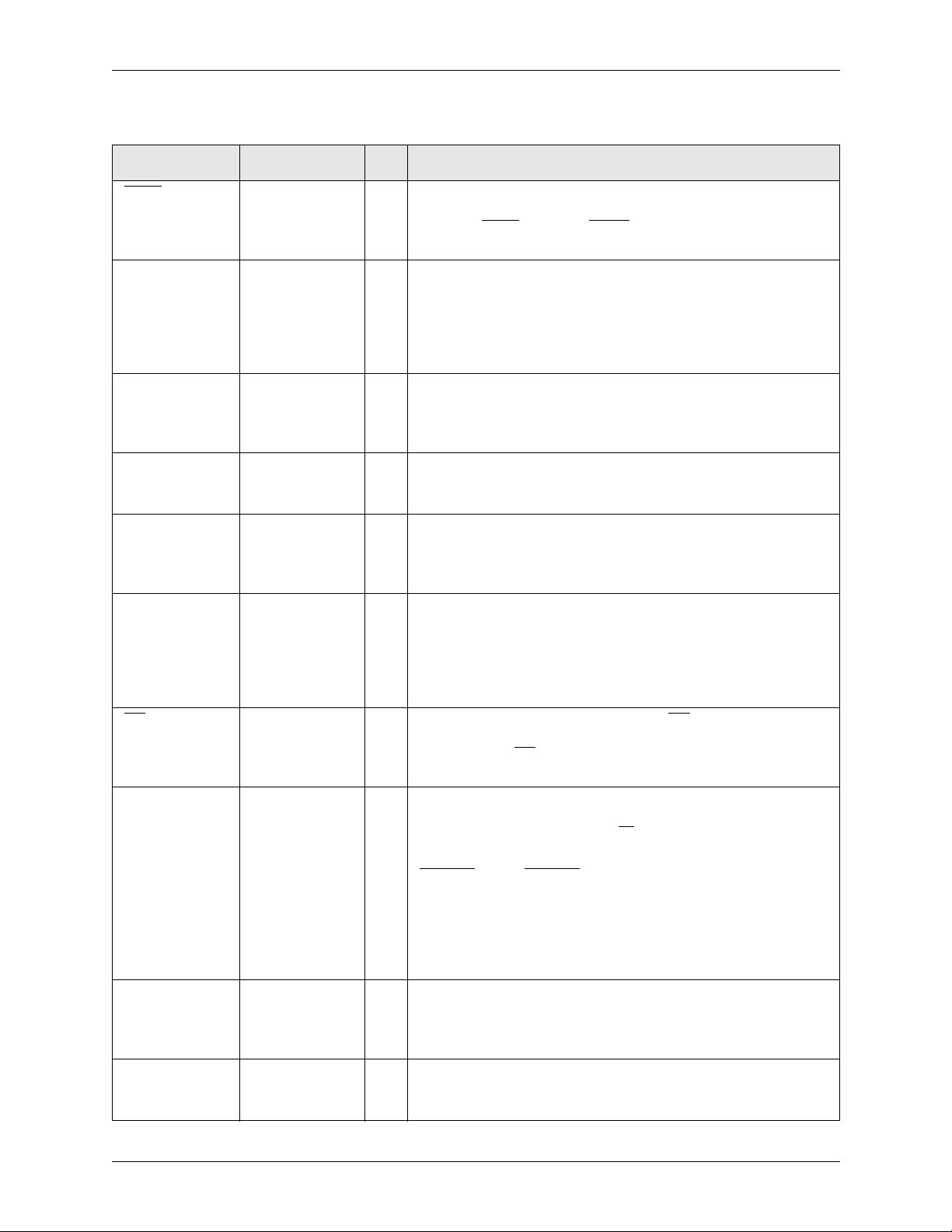

Figure 1-3. CN83 80 Logic Diagram (Ha rdware Mode)

Hardware Mode

VDD

I

I

I

I

I

I

I

I

I

I

I

I

I

HM

RESETHardware Reset

JDIR

JSEL(2:0)

UNIPOLAR

HTERM

PTS(2:0)

CLK_POL

RAWMD[1:4]Raw Mode Select

LLOOP[1:4]

RLOOP[1:4]

ZCS

RTIP[1:4]

RRING[1:4]

Hardware/Host Mode

Jitter Attenuator Path

Jitter Attenuator Size

Unipolar/Bipolar

Transmitter Termination

Clock Polarity

Local Loopback

Remote Loopback

Zero Code Suppression

Receive Tip

Receive Ring

Hardware

Control

Interface

Receiver

(RCVR)

Quad T1/E1 Line Interface

IRQ

JATERR[1:4]

RLOS[1:4]

RCKO[1:4]

RPOSO[1:4] Receive Positive Rail

RNEGO[1:4]

O

Interrupt Request

O

Jitter Attenuator Error Status

Receive Loss of Signal StatusTransmit Pulse Template

O

O

Receive Clock

O

Receive Negative Rail

O

Transmit Clock

Transmit Positive Rail

Transmit Negative Rail

1544 kHz All 1s Clock

2048 kHz All 1s Clock

Transmit Output Enable

Transmit All 1s

CLAD Input

Test Clock In

Test Mode Select

Test Data In

Test Reset In

I

I

I

I

I

I

I

I

I

I

I

I

I

TCLK[1:4]

TPOSI[1:4]

TNEGI[1:4]

TACKI

EACKI

XOE[1:4]

TAIS[1:4]

CLADI

REFCKIReference Clock

TCK

TMS

TDI

TRST

PIO = Programmable I/O

Transmitter

(XMTR)

XRING[1:4]

Clock Rate

Adapter (CLAD)

Boundary Scan

(JTAG)

I = Input, O = Output

XTIP[1:4]

CLK32

CLK1544

CLK2048 E1 Line Rate Clock Out

CLADO

TDO

O

Transmit Tip

O

Transmit Ring

O

32.768 MHz Clock Out

O

T1 Line Rate Clock Out

O

8 KHz Clock Out

O

O

Test Data Out

8380_005

1-4 Conexant N8380DSA

Advance Information

CN8380 1.0 Pin Descriptions

Quad T1/E1 Line Interface

Table 1-1. Ha rdware Signal Definitions (1 of 5)

Pin Label Signal Name I/O Definition

Receiver

RPOSO[1:4]

RDATO[1:4]

RNEGO[1:4]

BPV[1:4]

RCKO[1:4] RX Clock Output O Receive clock output . RCKO is the RPLL recovered l ine rate clock or jitter

RX Positive Rail

(Bipolar Mode)

RX Data (Unipolar

Mode)

RX Negative Rail

(Bipolar Mode)

Bipolar Violation

(Unipolar Mode)

O Line rate data ou tput on the r isi ng or fa lling edg e of RCK O. Th e cloc k edge

is determined by the CLK_POL pin in Hardware Mode or the CLK_POL

register bit [RLIU_CR; addr n1] in Host Mode. In bipolar mode, a high

signal indicates receipt of a positive AMI pulse on RTIP/RRING inputs. In

unipolar mode, RPOSO is redefi ned as RDATO and a high signal indica tes

either a positive or negative AMI pulse on RTIP/RRING inputs.

RPOSO/RDATO is three-stated during device reset.

O Line rate data output on rising or falling edg e of RCKO. The clock e dge is

determined by the CLK_POL pin in Hardware Mode or the CLK_POL

register bit [RLIU_CR; addr n1] in Host Mode. In bipolar mode, a high

signal indicates receipt of a negativ e AMI pul se on RTIP/RRING inputs. In

unipolar mode , RNEG O is rede fined as BP V, and a high si gnal in dicate s the

reception of a BPV which is not part o f a ZCS code (B8ZS or H DB3).

RNEGO/BPV is three-stated during device reset.

attenuated clock output, based on the programmed jitter attenuator

selection. RCKO is three-stated during devic e reset.

RTIP[1:4]

RRING[1:4]

Receive Tip

Receive Ring

I Differential AMI data inputs for direct connection to receive transformer.

Transmitter

TPOSI[1:4]

TDATI[1:4]

TNEGI[1:4] Tx Negative Rail

TCLK[1:4] TX Clock Input I/O Transmit line rate clock. TCLK is the transmit clock for TPOSI and TNEG I

TACKI

EACKI

[1:4] Transmit Output

XOE

[1:4] Transmit AIS

TAIS

Tx Positive Rail

(Bipolar Mode)

Tx Data (Unipolar

Mode)

Input

T1 AIS Clock

E1 AIS Clock

Enable

Alarm

I Positive rail, line rate data source for transmitted XTIP/XRING output

pulses. Data is sampled on the falling edge of TCLK. In bipolar mode, a

high on TPOSI causes a positive output pulse on XTIP/XRING; and a high

on TNEGI causes a negative output pulse. In unipolar mode, TPOSI is

redefined as TDATI and accepts single-rail NRZ data. TNEGI is not used in

unipolar mode.

I Negative rail, l ine rate data input on TCLK falling edge. Refe r to TPOSI

signal definition.

data inputs and for transmitter timing. Normally, TCLK is an input and

samples TPOSI/TNEGI on the falling edge. In Host Mode, TCLK can be

configured as an output to supply a line rate transmit clock from the

CLAD. The timing reference for the TCLK output (and CLAD) can be

selected from six sources.

I

Alternate T1 and E1 transmit clock used to transm it AIS (all 1s alarm

signal) when the primary transmit clock source, TCLK, fails. TACKI (T1) or

EACKI (E1) is either manually or automatically swi tched to replace TCLK

I

[LIU_CTL; addr n3]. Syste ms without an AIS clock should connect TACKI

and EACKI to gro und.

P

A low signal enables XTIP and XRING output drivers. Otherwise outputs

I

are high impedance.

P

In Hardware Mode, a low signal causes AIS (unframed all 1s)

I

transmission on XTIP/XRING outputs. In Host Mode, these pins can be

enabled or disabled [LIU_CTL; addr n3]. If disabled, they are not used and

may be left unconnected.

N8380DSA Conexant 1-5

Advance Information

1.0 Pin Descriptions CN8380

Quad T1/E1 Line Interface

Table 1-1. Ha rdware Signal Definitions (2 of 5)

Pin Label Signal Name I/O Definition

XTIP[1:4]

XRING[1:4]

Transmit Tip

Transmit Ring

O Complementary AMI transmitter line outputs for direct connection to

transmit transformer. Optionally, both outputs are three-stated when XOE

is high.

Clock Rate Adapter (CLAD)

CLADI CLAD Input I CLAD input timing reference used to phase/frequency lock the CLAD

outputs to an input clock frequency selected in the range of 8 kHz to

32,768 kHz [CLAD_CR; addr 02]. Systems which do not use CLADI should

connect CLADI to ground. In Hardware Mode, the CLAD timing reference

automatically switches to internal free-run operation if clock edges are not

detected on CLADI pin.

REFCKI Reference Clock I System must apply a 10 MHz ± 50 ppm (E1) or +

to act as the frequency reference for the internal numericall y controlled

oscillator (NCO). REFCKI det ermines the frequency accuracy and stability

of the CLAD output clocks when operating in free-run mode [CLAD_CR;

addr 02]. REFCKI is the baseband reference for all CLAD/JAT functions

and is used internall y to generate clocks of various frequency locked to a

selected receive or external clock.

32 ppm (T1) clock signal

Note

: REFCKI is always required.

CLK32 32 MHz Clock

Output

CLK1544 T1 Clock Output O Fixed rate 1.544 MHz T1 line rate clock output provided by the CLAD. May

CLK2048 E1 Clock Output O Fixed rate 2.048 MHz E1 line rate clock output provided by the CLAD. May

CLADO CLAD Output O In Hardware Mode, CLADO is a fixed rate 8 kHz clock output pro v ided by

O Fixed rate 32.768 MHz cl ock output provided by t he CLAD. May be used

by framers, such as the CN8398 octal T1/E1 framer, to provide system

timing reference.

be used for TCLK or TACKI clock sources. This clock is locked to the

selected CLAD timing ref e rence.

be used for TCLK or EACKI clock sources. This clock is locked to the

selected CLAD timing ref e rence.

the CLAD. In Host Mode, CLADO may be configured to operate at one of

14 different clock freq uencies [CSEL; addr 03] that include T1 or E1 line

rates. CLADO is typically programmed to supply system clocks that are

phase-locked to the selected receive or CLAD timing reference [CLAD_CR;

addr 02].

Hardware Control Signals

HM Hardware Mode

P

A high on HM places the device in Hardware Mode, enabling all hardware

I

control pin functions. A low on HM places the device in H ost Mode,

disabling some hardware-mode-only pin functions and enabling the serial

port signals on the dual function pins listed bel ow. The serial po rt signals

allow serial host access to the device registers. Refer to the Host Serial

Control Signals se ction of this table.

JSEL(2) / SDI

[1:4] Raw Mode

RAWMD

JSEL(1) / CS

JDIR / SCLK JATERR(1) / SDO

P

Low selects receiver Raw mode. Applicable only in Hardware Mode. In

I

Raw mode, RPOSO and RNEGO represent the data slicer outputs and

RCKO is the logical OR of RPOSO and RNEGO.

1-6 Conexant N8380DSA

Advance Information

CN8380 1.0 Pin Descriptions

Quad T1/E1 Line Interface

Table 1-1. Ha rdware Signal Definitions (3 of 5)

Pin Label Signal Name I/O Definition

RESET Hardware Reset

P

Active low asynchronous hardware reset. A falling edge forces registers to

I

their default, power-up state. Output pins are forced to the high impedance

state while RESET is ass erted. RESET is not mandat ory at power-up

because an internal power-on reset circuit performs an identic al function.

P

UNIPOLAR Unipolar Mode

Select

Applicable only in Hardware Mode. A high signal on UNIPOLAR configures

I

all RPOSO outputs and TPOSI inputs to operate with unipolar, NRZformatted data. In this mo de, RN EGO report s non-ZC S BPVs and TNE GI is

not used. A low signal on UNIPOLAR configures all channels’

RPOSO/RNEGO and TPOSI/TNEGI interfaces to operate with bipolar,

dual-rail, NRZ formatted data .

P

ZCS Zero Code

Suppression

Select

Applicable only in Hardware Mode. A high signal on ZCS enables the

I

transmit ZCS encoder and the receive ZCS decoder if unipolar mode is

enabled (UNIPOLAR = 1). In Bipolar Mode (UNIPOLAR = 0), the ZCS

encoder and decoder are disabled and ZCS is ignored.

P

CLK_POL Rx Clock Polarity

Select

Applicable only in Hardware Mode. High s ets RPOSO/R NEGO to be output

I

on the falling ed ge o f RC KO. Low sets RPOSO/RN EGO to be o utp ut on the

rising edge of RCKO

PTS(2:0) Transmit Pulse

T emplate Select

P

Applicable only in Hardware Mode. The PTS(2:0) control bus selects the

I

transmit pulse template and the line rate (T1 or E1) globally for all

channels. Refer to the description of HTERM in this table and to the

transmit pulse configurations in Table 2-3.

P

HTERM Transmitter

Hardware

Termination

Applicable only in Hardware Mode. If an external tran smit termination

I

resistor is used to meet return loss specifications; a transformer with a 1:2

turns ratio is used, and HTERM i s set high to allow the transmitter to

compensate for the increased load. Refer to the Transmitter section of this

table and Tables 2-4 through 2-8 for transmitter termina ti on con fig ura ti on

options.

IRQ

Interrupt Request

D

Active low, open drain output. In Host Mode, IRQ indicates one or more

O

pending interrupt requests ([ISR; addr n6] and [CSTAT; addr 06]). In

Hardware Mode, IRQ is the logical NOR of the four internal transmitter

driver performance monitor outputs.

P

JSEL(2:0) Jitter Attenuator

Select

Applicable only in Hardware Mode. The JSEL and JDIR pins determine the

I

JAT configuration. JSEL(2:0) enables and selects the JAT depth as shown

in the table below. SDI/JSEL(2) and CS /JSEL(1) are dual function pins.

JSEL(2:0) JAT Mode

000 8 bits

001 16 bits

010 32 bits

011 64 bits

100 128 bits

111 Disable JAT

P

JDIR Jitter Attenuator

Direction

Applicable only in Hardware Mode. JDIR determines the path in which the

I

JAT is inserted. If JDIR is low, the JAT (if enabled) is placed in the receive

path; if high, the JAT (if enabled) is placed in the transmit path. Refer to

the description for JSEL(2:0). SCLK/JDIR is a dual function pin.

JATERR[1:4] Jitter Attenuator

Error

O Applicable only in Hardware Mode. A high on JATERR indicates an

overflow or underflow error in the jitter attenuator elastic store.

JATERR(1) / SDO is a dual function pin.

N8380DSA Conexant 1-7

Advance Information

1.0 Pin Descriptions CN8380

Quad T1/E1 Line Interface

Table 1-1. Ha rdware Signal Definitions (4 of 5)

Pin Label Signal Name I/O Definition

RLOS [1:4] Receive Loss of

Signal

ORLOS is asserted low when 100 (T1) or 32 (E1) consecutive 0s (no

pulses) are received at the l ine interface or when the received signal level

is approximately 1 8 dB below nominal for at least 1 ms.

LLOOP [1:4]

Local Loop

P

These pins are always enabled in Hardware Mode and may be en abled or

I

disabled in Host Mode [LIU_CTL; addr n3]. A low on LLOOP initiates Local

RLOOP [1:4]

Remote Loop

Analog Loopback and a low on RLOOP initiates Remote Line Loopback.

P

I

Local Digital Loo pback is initiated if both signals are asserted together.

Boundary Scan Signal s (JTAG)

TDO Test Data Output O Test data output p e r IEEE Std. 1149 .1-1990. Three-st ate output used for

reading all serial conf iguration and test data f r om internal test logic.

Updated on the falling edge of TCK.

P

TDI Test Data Input

Test data input per IEEE Std. 1149.1-1990. Used for loading all serial

I

instructions and data into internal test logic. Sampled on the rising edge of

TCK. TDI may be left unconnected if not us ed.

TMS Test Mode Select

P

Active-low test mode select input per IEEE Std 1149.1-1990. Internally

I

pulled-up input signal use d t o co ntrol the test lo gi c state machine.

Sampled on the risi ng edge of TCK. TMS may be left unconnected if not

used.

P

TCK Test Clock

Test clock input per IEEE Std. 1149.1-1990. Used for all test interface and

I

internal test-logic operations. If not used, TCK should be pulled low.

TRST

Reset

P

Active low reset. TRST is pulled up internally and may be left unconnected

I

if not used.

Host Serial Control Signals

CS Chip Select

SDI Serial Data In

P

In Host Mode, CS is an active low input used to enable read/write access

I

with the host serial control port. CS

P

In Host Mode, SDI is the serial data input for the host serial control port.

I

/JSEL(1) is a dual function pin.

SDI/JSEL(2) is a dual function pin.

SDO Serial Data Out O In Host Mode, SDO is the serial data output for the host seria l control por t.

SDO/JATERR[1] is a dual function pin.

SCLK Serial Clock

P

In Host Mode, SCLK is the serial clock input for the host serial control

I

port. SCLK/JDIR is a dual function pin.

Power Supply Pins and No-Connect Pins

VAA

GND

VAAT[1:4]

Analog Supp ly

Ground

Tx Driver Supply

I+3.3 V + 5%. Power supply pair for the analog circuitry.

I+3.3 V +

5%. Power supply pairs for the transmitter driver circuitry. These

pin pairs should each be bypassed with a tantalum capacitor value of at

GNDT[1:4]

VAAR

GNDR

Ground

Rx Analog Supp ly

Ground

least 10

I + 3.3 V +

µF.

5%. Power supply pair for the analog receiver circuitry.

1-8 Conexant N8380DSA

Advance Information

CN8380 1.0 Pin Descriptions

Quad T1/E1 Line Interface

Table 1-1. Ha rdware Signal Definitions

(5 of 5)

Pin Label Signal Name I/O Definition

VAACL

GNDCL

VDD

VSS

VGG ESD Rail I To insure 5 V tolerance in mixed + 5 V / + 3.3 V systems, this input must

N.C. No Connect — No-connect pins are reserved for future device compati bility and should

NOTE(S):

1. I/O Types:

I = Standard input

P =

Input with internal pull-up resister

I

O = Standard output

OD = Output with open drain

2. Legend:

[#] = Port number

(#) = Bit number

CLAD Supply

Ground

Digital Supply

Ground

I + 3.3 V + 5%. Power supp ly pair for the CLAD PLL circuitry.

I + 3 .3 V + 5%. Power supply pairs for the di gital circuitry.

be connected to + 5 V. If all logic input signals are 3.3 V levels, then this

pin may be connected to the 3.3 V supply.

be left unconnected.

N8380DSA Conexant 1-9

Advance Information

1.0 Pin Descriptions CN8380

Quad T1/E1 Line Interface

1-10 Conexant N8380DSA

Advance Information

2

2.0 Circuit Description

2.1 Overview

The CN8380 includes four identical T1/E1 transceiver channels and a common

CLAD packaged in a 128-pin MQFP carrier. It is designed to interface T1/E1

framers, or to operate as a stand-alone line interface for synchronous or

plesiochronous mappers and multiplexers. The CN8380 is ideal for high line

density, short-haul applications that require low power (3.3 V supply) operation.

The configurable T1/E1 operation and common line interface design allow s

support for single-board T1 and E1 designs.

Customer premise applications are supported by an on-chip JAT which

conforms to AT&T PUB 62411 and a selectable transmit pulse shape which

conforms to FCC Part 68, Pulse Option A. Selectable unipolar or bipolar interface

options and internal ZCS encoding and decoding are useful in many multiplexer

and mapper applications.

In the most simple configuration, Hardware Mode, the device is controlled

using dedicated hardware control pins. In this mode, the four channels are

configured globally to identical operating modes (T1, E1, transmit termination,

jitter attenuators, and so on). Each channel has device pins dedicated for channel

control and status, such as loopback controls, bipolar/unipolar interface modes,

and loss of signal indicators. Hardware Mode is selected by pulling the HM pin

high.

Host Mode allows control of the device through a 4-line serial port. In this

mode, all control and status functions can be accessed using internal registers.

Several additional features are also available in Host Mode, such as individual

channel operating mode configuration (T1 /E1, transmit termination, jitter

attenuators, etc.) and programmable CLAD output frequencies. Host Mode is

selected by grounding the HM pin.

The CN8380 incorporates printed c irc uit board testability circuits in

compliance with IEEE Std P1149.1a–1993, IEEE Standard Test Access Port and

Boundary–Scan Architecture, commonly known as JTAG (Joint Test Action

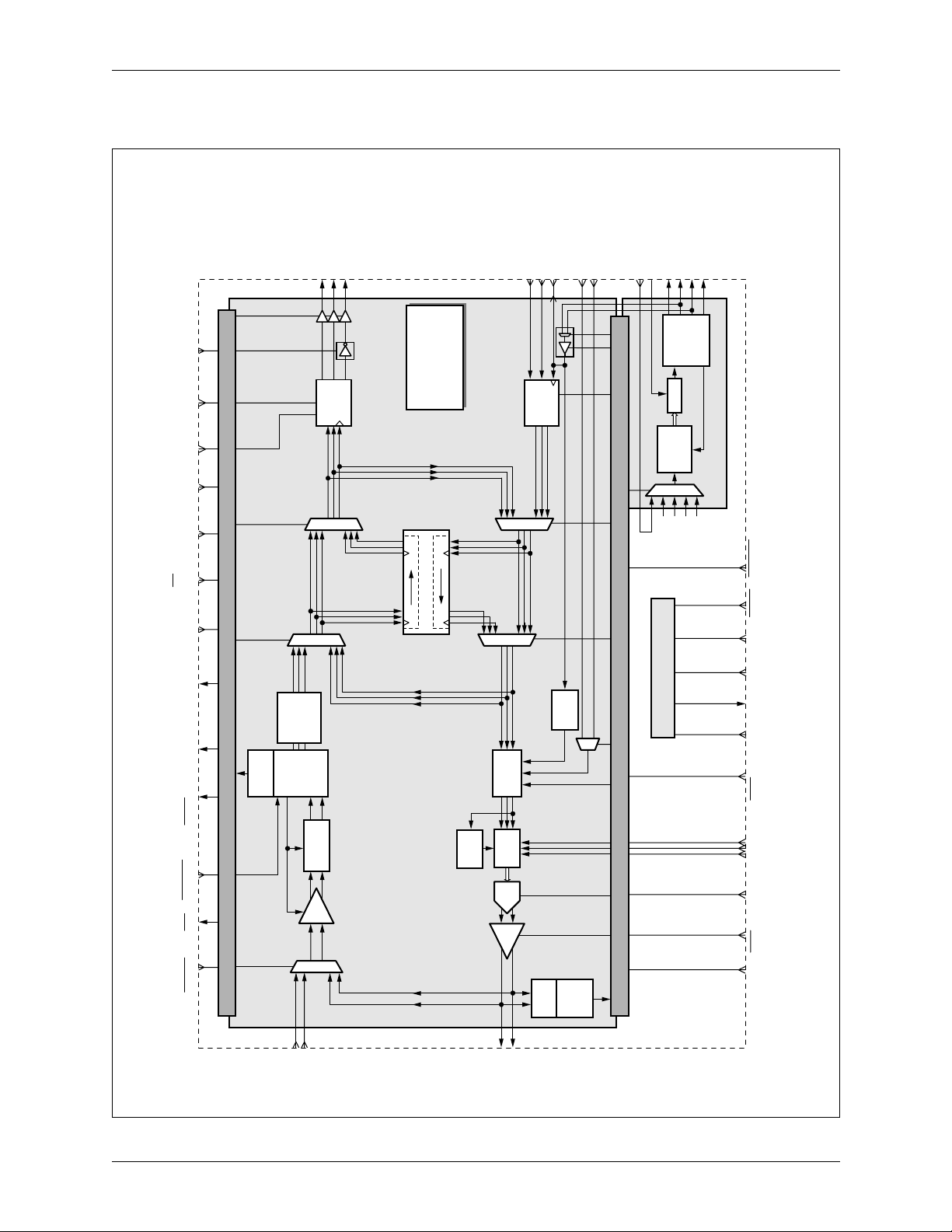

Group). A detailed block diagram is displayed in Figure 2-1.

N8380DSA Conexant 2-1

Advance Information

2.0 Circuit Description CN8380

2.1 Overview

Figure 2-1. Detailed Block Diagram

CLK_POL

UNIPOLAR

ZCS

JDIRLLOOP[n] IRQ JATERR[n]

SCLK

RPOSO[n]

RNEGO[n]

RCKO[n]

RZCS

Decode

0

1

Note:

Only one LUI is

shown. The other

three are identical.

Remote

Line

Loopback

1

TCLK[n]

TPOSI[n]

TNEGI[n]

TZCS

Encode

0

TACKI

EACKI

Quad T1/E1 Line Interface

CLADI

CLK1544 (1.544 MHz)

REFCKI

CLADO

CLK32 (32.768 MHz)

CLK2048 (2.048 MHz)

Chain

Divider

NCO

CLAD

Phase

Detector

CS

JSEL(1) JSEL(0)RLOS[n]

SDI

JSEL(2)

SDO

JATERR[1]

RAWMD[n]

Control

RLOS

Detect

1

Clock

Recovery

Peak

Detect

0

RPLL

and

Slicer

Adaptive

Equalizer

VGA

1

RCKO[3]

RCKO[2]

RCKO[1]

RCKO[4]

Jitter Attenuator

0

Local

Digital

Loopback

Local

Analog

Loopback

8X

TPLL

1

AIS

Gen

Pulse

Shape

DAC

DRV

0

Control

JTAG

Mon

Clock

CKT

DPM

Short

Detect

TRSTTCLKTDO

TDI TMS RLOOP[n]HM

PTS(2:0)

HTERM

XOE[n] TAIS[n]

RTIP[n]

RRING[n]

XTIP[n]

XRING[n]

8380_006

2-2 Conexant N8380DSA

Advance Information

CN8380 2.0 Circuit Description

Quad T1/E1 Line Interface

2.2.1 Hardware Mode

2.2.2 Host Mode

2.2 Configuration and Control

2.2 Configuration and Control

In Hardware Mode, the device is controlled using dedicated hardware control

pins. In this mode, the four channels are configured globally to identical

operating modes (T1, E1, tr ansmit termination, j itter atten uators, and so o n). Each

channel has device pins dedicated for channel control and status, such as

loopback controls, bipolar /unipolar i nterface modes, and loss of sig nal indicators.

Refer to Table 1-1,

pins. Hardware Mode is selected by pulling the HM pin high.

In Host Mode, control of the device is through a four-line serial port. In this

mode, all control and status functions can be accessed using internal registers.

Refer to Chapter 3.0,

selected by grounding the HM pin.

Hardw are Signal Definitions

Registers

, for a description of each register. Host Mode is

, for a description of all hardw are

2.2.3 Host Serial Control Interface

The CN8380 serial interface is a four-wire, slave interface which allows a host

processor or framer with a compatible master serial port to communic ate with t he

LIU. This interface allows the host to control and query the CN8380 status by

writing and reading internal registers. One 8-bit register in the LIU can be written

via the SDI pin or read from the SDO pin at the clock rate determined by SCLK.

The serial port is enabled by pulling the chip select pin,

the read and write cycles. Refer to Figure 2-2 for host serial port signals.

The serial interface uses a 16-bit process for each write or read operation.

During a write or read operation, an 8-bit cont rol word, consistin g of a read /wri te

control bit (R/W) and a 7-bit LIU register address (A[6:0]) is transmitted to the

LIU using the SDI pi n. If the operation is a write operation (R/W = 0), an 8-bit

register data (D[7:0]) byte follows the address on the SDI p in. This data is

received by the CN8380 and stored in the addressed register. If the operation is a

read operation (R/W = 1), the CN83 80 output s th e addr essed register contents on

the SDO pin. The signal input on SDI is sampled on the SCLK falling edge, and

data output on SDO changes on the SCLK rising edge.

CS

, active (low) during

N8380DSA Conexant 2-3

Advance Information

2.0 Circuit Description CN8380

2.2 Configuration and Control

Figure 2-2. Host Serial Port Signals

CS

SCLK

R/W

SDI

SDO

CS

A0 A1 A2 A3 A4 A5 A6

Quad T1/E1 Line Interface

Read Timing

Address/Control Byte

D0 D1 D2 D3 D4 D5 D6 D7

Register Data Byte

Write Timing

SCLK

SDI

SDO

8380_007

2.2.4 Reset

A0 A1 A2 A3 A4 A5 A6

R/W

Address/Control Byte

D0 D1 D2 D3 D4 D5 D6 D7

Register Data Byte

The CN8380 supports three reset methods: power-on reset, hard reset i ni tiat ed by

RESET

the

pin, and soft reset initiated by the RESET bit in the Global

Configuration Register [GCR; addr 01]. In Host Mode, all three reset methods

produce the same results as listed below. In Hardware Mode, power-on reset and

hard reset produce the same results as shown; and soft reset is not applicable.

After RESET is complete, t he following is true:

Hardware Mode Host Mode

Digital receiver outputs

(RPOSO[1:4] and RNEGO[1:4],

RCKO[1:4]) are enabled.

Digital receiver outputs (RPOSO[1:4]

and RNEGO[1:4], RCKO[1:4]) are

three-stated.

Transmitter line outputs (XTIP[1:4]

and XRING[1:4]) are enabled

XOE

(controlled by

).

Transmitter line outputs (XTIP[1:4]

and XRING[1:4]) are three-stated.

2-4 Conexant N8380DSA

Advance Information

CN8380 2.0 Circuit Description

Quad T1/E1 Line Interface

2.2.4.1 Power-on Reset

2.2 Configuration and Control

Hardware Mode Host Mode

CLK1544, CLK2048, and CLADO

clock outputs are enabled.

Transmitter clocks, TCLK[1:4], are

configured as inputs.

IRQ

The

pin is enabled (controlled

CLK1544, CLK2048, and CLADO

clock outputs are three-stated.

Transmitter clocks, TCLK[1:4], are

configured as inputs.

IRQ

The

pin is three-stated.

by DPM).

All interrupt sources are disabled.

All configuration registers are set to

default values as listed in Section 3.1,

Address Map

.

An internal power-on reset process is initiated during power-up. When VDD has

reached approximately 2.6 V, the internal reset process begins and continues for

300 ms maximum if REFCLK is applied. If REFCLK is not pr esen t, t he CN83 80

remains in the reset state.

2.2.4.2 Hard Reset

2.2.4.3 Soft Reset

Hard reset is initiated by bringing the

internal reset process completes in 5 µs maximum. If the

continuously, the clock and dat a o utp ut s and th e

following output pins are forced to high impedance while

RESET

pin active (low). Once initiated, the

RESET

pin is held active

IRQ

pin remain three-stated . The

RESET

is held active:

RPOSO[1:4] CLADO

RNEGO[1:4] TCLK[1:4]

RCKO[1:4]

XTIP[1:4]

IRQ

RLOS[1:4]

XRING[1:4:] JATERR[1:4]

CLK1544 SDO

CLK2048 TDO

In Host Mode, soft reset is in itiated by writing a one to the RESET bit in the

Global Configuration register [addr 01]. The RESET bit is self-clearing. Once

initiated, the internal reset process comp letes in 5 µs maximum and the device

enters normal operation.

N8380DSA Conexant 2-5

Advance Information

2.0 Circuit Description CN8380

2.3 Receiver

Quad T1/E1 Line Interface

2.3 Receiver

Bipolar AMI pulses are input on the receiver input pins, RTIP[n] and RRING[n].

The receiver recovers clock and data from the AMI signal which has been

attenuated and distorted due to the line characteristics. The AMI pulses are

converted into bipolar or unipolar, NRZ data and output on RPOSO[n] and

RNEGO[n], along with the recovered clock on RCKO[n]. Figure 2-3 illustrates

the relationship between the AMI received signal, the recovered clock, and the

data outputs. This section discusse s each receiver block from the line input to the

digital outputs.

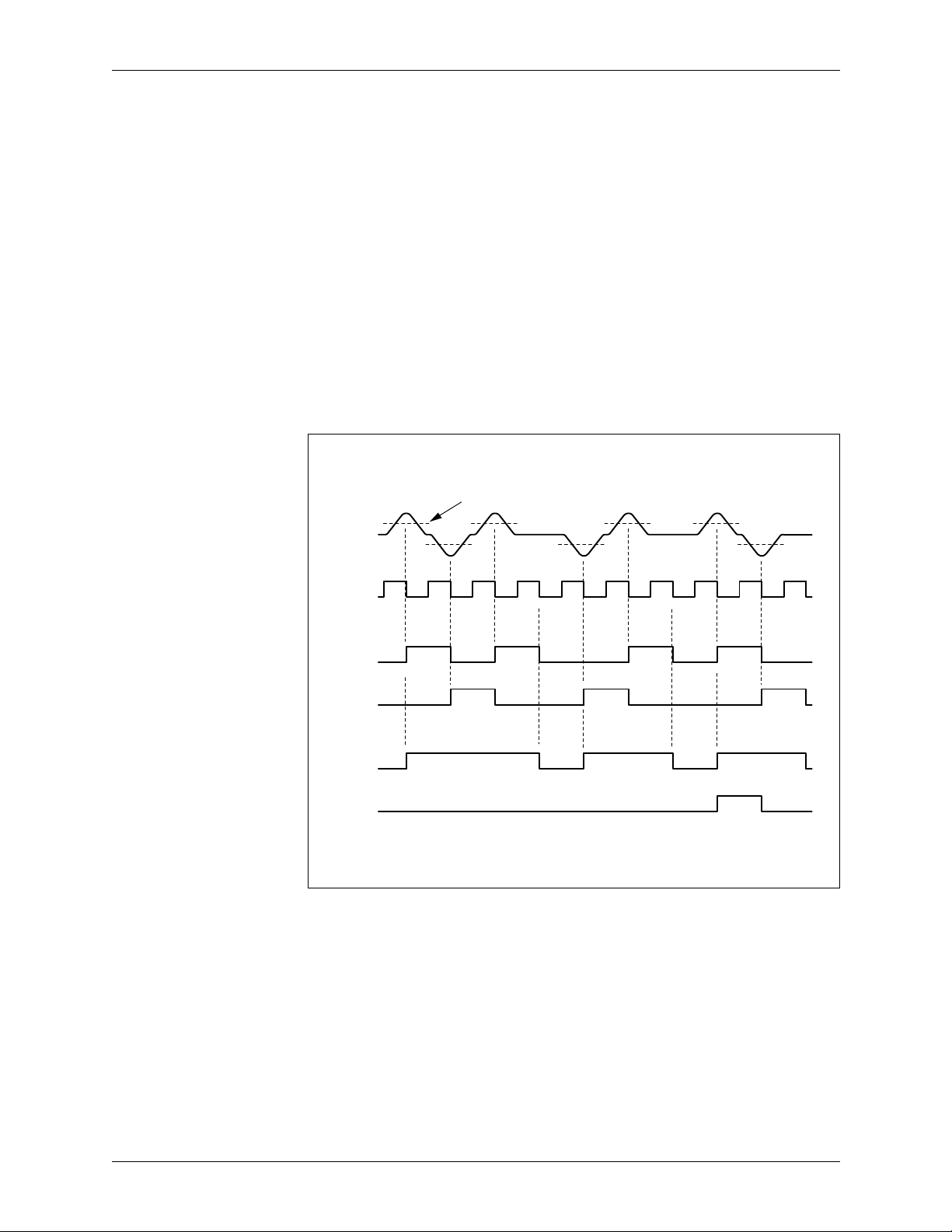

Figure 2-3. Receiver Signals

Data Slicer Level

(50% of Peak)

Internal

Equalized

Received

Signal

2.3.1 Data Recovery

RCKO

RPOSO

(Bipolar)

RNEGO

(Bipolar)

RDATO

(Unipolar)

BPV

(Unipolar)

111 11 1100

BPV

The receiver recovers data by normalizing th e input signal wit h an aut omatic ga in

control (AGC) circuit, removing distortion with an equalizer, and extracting the

data using a data slicer . The transfer functio n of the equalizer is adjusted based on

the average peak value of the input signal. The AGC maintains the equalizer’s

average peak output level to a constant value. The data slicer compares the

equalizer output to a threshold value equal to 50% of the average peak equalizer

output level and produces both positive and negative pulse detect signals. The

data slicer outputs are re-t imed using the recovered clock and routed to the RZCS

decoder (or to the JAT ).

8380_008

2-6 Conexant N8380DSA

Advance Information

Loading...

Loading...