CONEX CN8330EPJD, CN8330EPD Datasheet

CN8330

DS3/E3 Framer with 52 Mbps HDLC Controller

The CN8330 is an integral DS3/E3 framer designed to support the transmission

formats defined by ANSI T1.107-1988, T1.107a-1989, T1.404, and ITU-T G.751

standards. All maintenance features required by Bellcore TR-TSY-000009 and AT&T

PUB 54014 are provided. In addition, the CN8330 can be optionally configured as a

High-Level Data Link Controller (HDLC) usable with or without DS3/E3 framing

overhead.

The CN8330 provides framing recovery for M13, C-bit parity, Syntran, and G.751

E3 formatted signals. A First In First Out (FIFO) buffer in the receive path can be

enabled to reduce jitter on the incomi ng data. Transmi t and recei ve data is availabl e to

the host in either serial or parallel byte and nibble formats. Access is provided to the

terminal data link and the Far End Alarm/Control (FEAC) channel, as specified in

T1.107a-1989. Counters are included for frame-bit errors, Line Code Violations

(LCVs), parity errors, and Far End Block Errors (FEBEs).

Two operational modes are available: microprocessor and stand-alone monitor

control modes. The microprocessor control mode monitors all status conditions and

provides configuration control. The stand-alone monitor mode allows the CN8330 to

operate as a monitor providing status and alarm information on external pins.

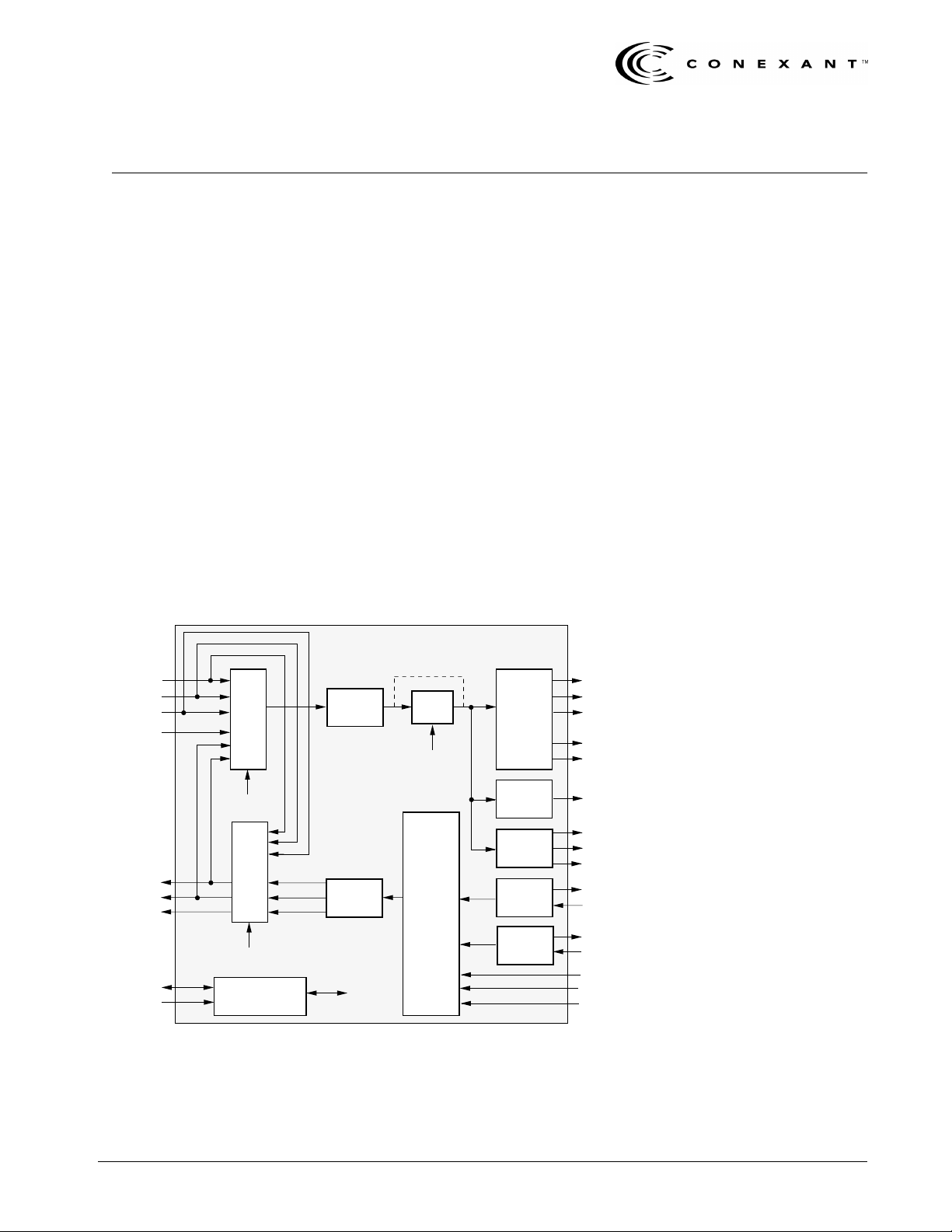

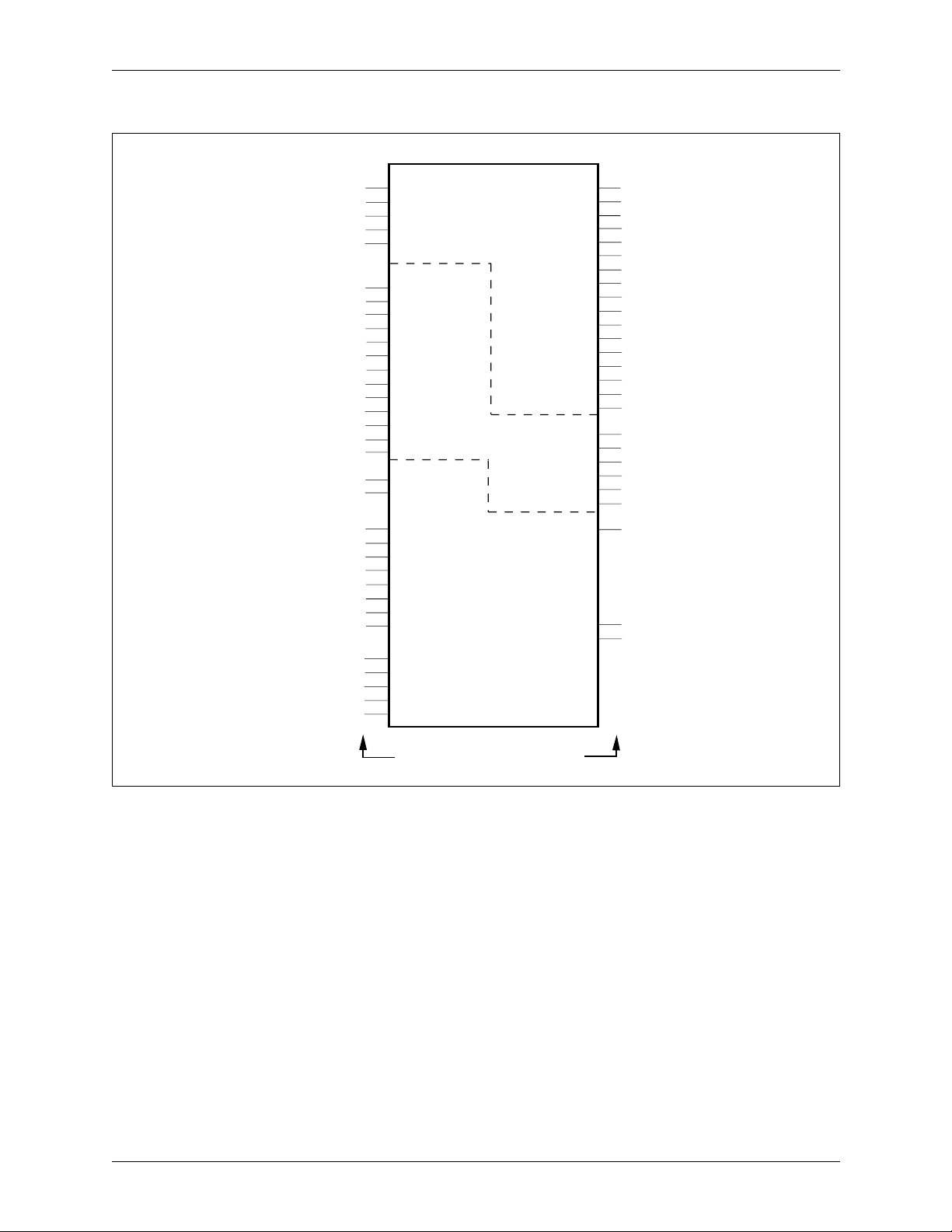

Functional Block Diagram

RXPOS

RXNEG

DS3CKI

TXCKI

TXPOS

TXNEG

TCLKO

AD[7:0]

Control

M

U

X

Source

Loopback

M

U

X

Line

Loopback

Microprocessor

Interface

Unipolar

Conversion

Bipolar

Encoder

To/From

All Blocks

Bypass

FIFO

FIFO

Enable

Framing/

Overhead

Insertion

Framing

Recovery

Overhead/

Data Link

Processing

PPDL

Receiver

PPDL

Transmitter

Overhead/

Data Link

Processing

RXMSY

CBITO

RXCCK

RXDAT

RXCLK

Status

RDAT[7:0]

RXBCK

Status

TXBCK

TDAT[7:0]

TXCCK

CBITI

TXCKI

TXDATI

TXSYI

Distinguishing Features

• Supports DS3/E3 framing modes

• Includes high-speed HDLC controller

(52 MHz)

• Framing recovery for M13, C-bit

parity, Syntran, and G.751 E3 signals

• Serial or parallel (octet or nibble)

interface modes

• Average reframe time of less than

1 ms for DS3 and less than 250 µs

for E3

• Supports the LAP D term inal da ta li nk

and FEAC channel as defined in

T1.107a-1989

• 68-pin PLCC or 80-pin MQFP

surface-mount package

• Operates from a single +5 VDC ±5%

power supply

• Low-power CM OS tec h no lo gy

Applications

• Digital PCM switche s

• Digital Cross-Connect Systems

• Channel Service Units (CSUs )

• Channel extenders

• ATM Switches/Concentrators

•PBXs

• Switched Multimegabit Digital

Service (SMDS) Equipment

• Test equi pm e n t

• Routers (in c luding HSSI por ts)

Data Sheet 100441E

October 13, 1999

Ordering Information

Model Number Package Ambient Temperature

CN8330EPJD 68-Pin Plastic Leaded Chip Carrier (PLCC)

CN8330EPD 80-Pin Metric Quad Flat Pack (MQFP)

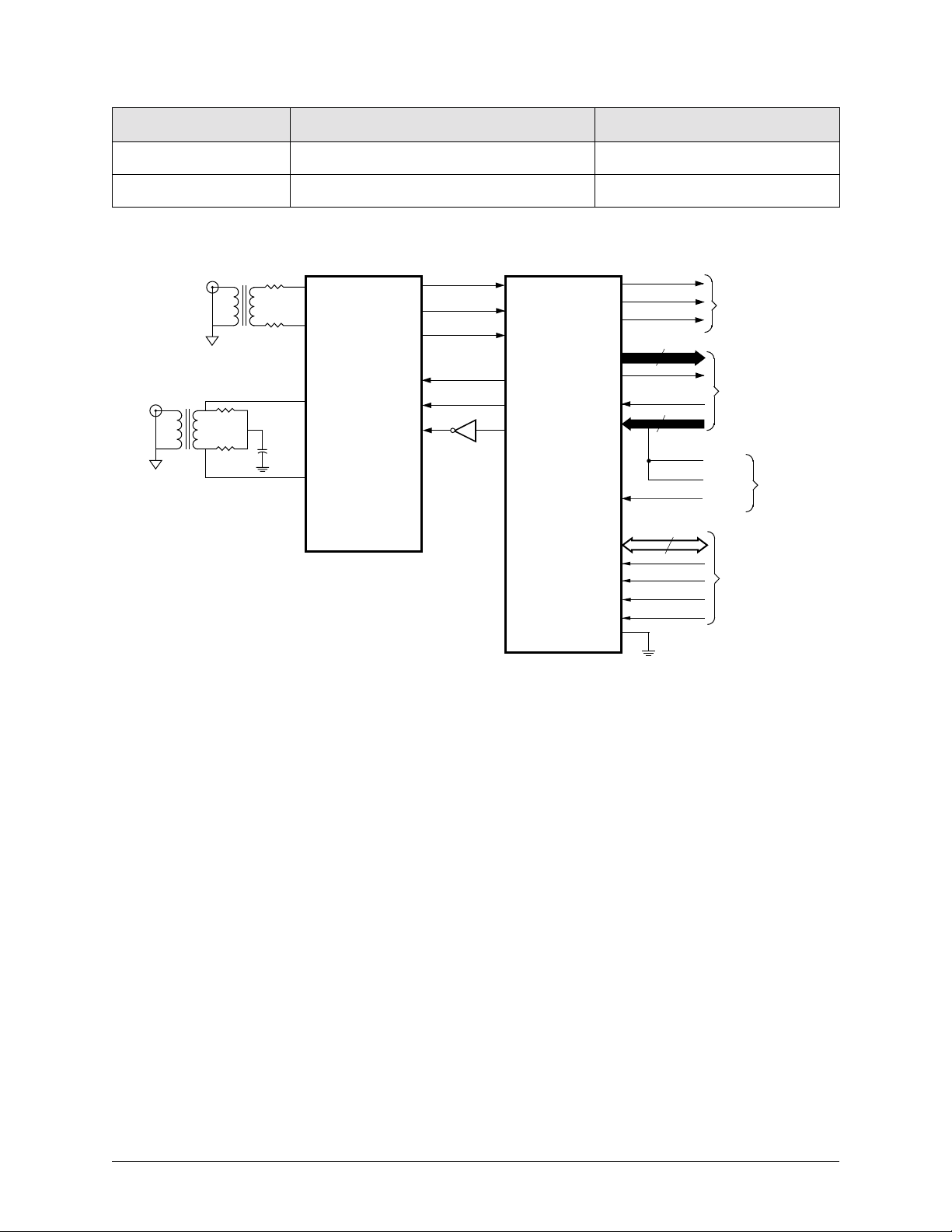

CN8330 Typical DS3 Application

31.6Ω

31.6Ω

37.4Ω

37.4Ω

0.01

RLINE1P

RLINE1N

TLINE1P

TLINE1N

CN8331

RPOS1

RNEG1

RCLK1

TPOS1

TNEG1

TCLK1

CN8330

DS3/E3 Framer

RXPOS

RXNEG

DS3CKI

TXPOS

TXNEG

TCLKO

RXDAT

RXCLK

RXMSY

RDAT[7:0]

RXBCK

TXBCK

TDAT[7:0]

TXCKI

AD[7:0]

RD*

WR*

CS

ALE

MON/MIC*

8

8

TDAT7

TDAT6

8

–40 to 85

–40 to 85

Receive

Serial

Data

Interface

Parallel

Data

Interface

(Also used

for HDLC

payload

data)

(M-Sync)

(Data)

(Clock)

° C

° C

Transmit

Serial

Data

Interface

Microprocessor

Interface

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is

assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent rights of Conexant other than for circuitry embodied in Conexant

products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without

notice.

Conexant products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a

Conexant product can reasonably be expected to result in personal injury or death. Conexant customers using or selling Conexant

products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from

such improper use or sale.

The trademarks “Conexant” and the Conexant symbol are trademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered

trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc.

Printed in U.S.A.

All Rights Reserved

Reader Response: Conexant strives to produce quality documentation, and welcomes your feedback. Please send

comments and suggestions to conexant.tech.pubs@conexant.com. For technical questions, contact your local

Conexant sales office or field applications engineer.

100441E Conexant

Table of Contents

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . v

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

1.0 Product Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

2.0 Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1.1 Brief Block Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1.2 Clock Interface and Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1.2.1 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1.3 Microprocessor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1.3.1 Using with Specific Microcontrollers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1.3.2 Microprocessor Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.1.3.3 Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.2 Line Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.2.1 Transmitter Line Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.2.2 Receiver Line Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.3 Transmitter Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.3.1 Input and Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.3.2 DS3 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.3.3 E3 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

2.3.4 Fra ming Bit Gener ation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

2.3.5 Alarm Signal Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.3.6 Terminal Data Link Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

2.3.6.1 Sending a Message. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.3.6.2 Aborting a Message . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.3.6.3 Transmitter Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.3.6.4 Transmitter Control Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.3.7 TxFEAC Channel Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.3.8 PPDL Transmitter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2.3.9 PPDLONLY Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

2.3.10 Transmitter Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

2.3.11 Test Equipment Specific Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

100441E Conexant i

CN8330

DS3/E3 Framer with 52 Mbps HDLC Controller

2.4 Receiver Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.4.1 Bipolar-to-Unipolar Conversion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.4.2 Receive FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.4.3 Received Signal Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

2.4.4 Fr aming Operat ion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2.4.5 Alarm Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2.4.6 Terminal Data Link Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

2.4.6.1 Receiver Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

2.4.6.2 Receiver Response Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

2.4.7 RxFEAC Channel Reception. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

2.4.8 PPDL Receiver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.4.9 PPDLONLY Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-32

2.4.10 Serial C-Bit Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

2.5 Monito r Mode for Stand-Alone Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

2.5.1 DS3 Monitor Mode Error Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35

3.0 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1 Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

0x00—Mode Control Register (CR00). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

0x01—Terminal Data Link Control Register (CR01) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

0x02—Status Interrupt Control Register (CR02) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

0x03—Transmit FEAC Channel Byte (CR03) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

0x04—Feature Control Register (CR04) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

0x05—PPDL Control Register (CR05). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.2 Status Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

0x10—DS3/E3 Maintenance Status Register (SR00). . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

0x11—Counter Interrupt Status Register (SR01). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

0x12—Data Link Interrupt Status Register (SR02) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

0x13—Receive FEAC Channel Byte (SR03) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

0x14—Terminal Data Link Status Register (SR04). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

0x15—Part Number/Hardware Version Register (SR05) . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

0x16—Shadow Status Register (SR06) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

0x20–0x26—DS3/E3 Error Counters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

0x20—DS3 Parity Error Counter (SR07). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

0x21—DS3 Disagreement Counter (SR08) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

0x22—DS3/E3 Frame Error Counter (SR09) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

0x23—DS3 Path Parity Error Counter (SR10). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

0x24—DS3 FEBE Event Counter (SR11) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

0x25,0x26—DS3/E3 LCV Counter—Low and High Bytes (SR12,SR13) . . . . . . . . . . . . . 3-13

3.3 Memory Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

0x30–0x37—Transmit Terminal Data Link Message Buffer (TxTDL) . . . . . . . . . . . . . . . . 3-14

0x40–0x47—Receive Terminal Data Link Message Buffer (RxTDL) . . . . . . . . . . . . . . . . 3-14

3.4 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

ii Conexant 100441E

CN8330

DS3/E3 Framer with 52 Mbps HDLC Controller

4.0 Mechanical/Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1 Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2 Environmental Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4.2.1 Power Requirements and Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4.3 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

4.3.1 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

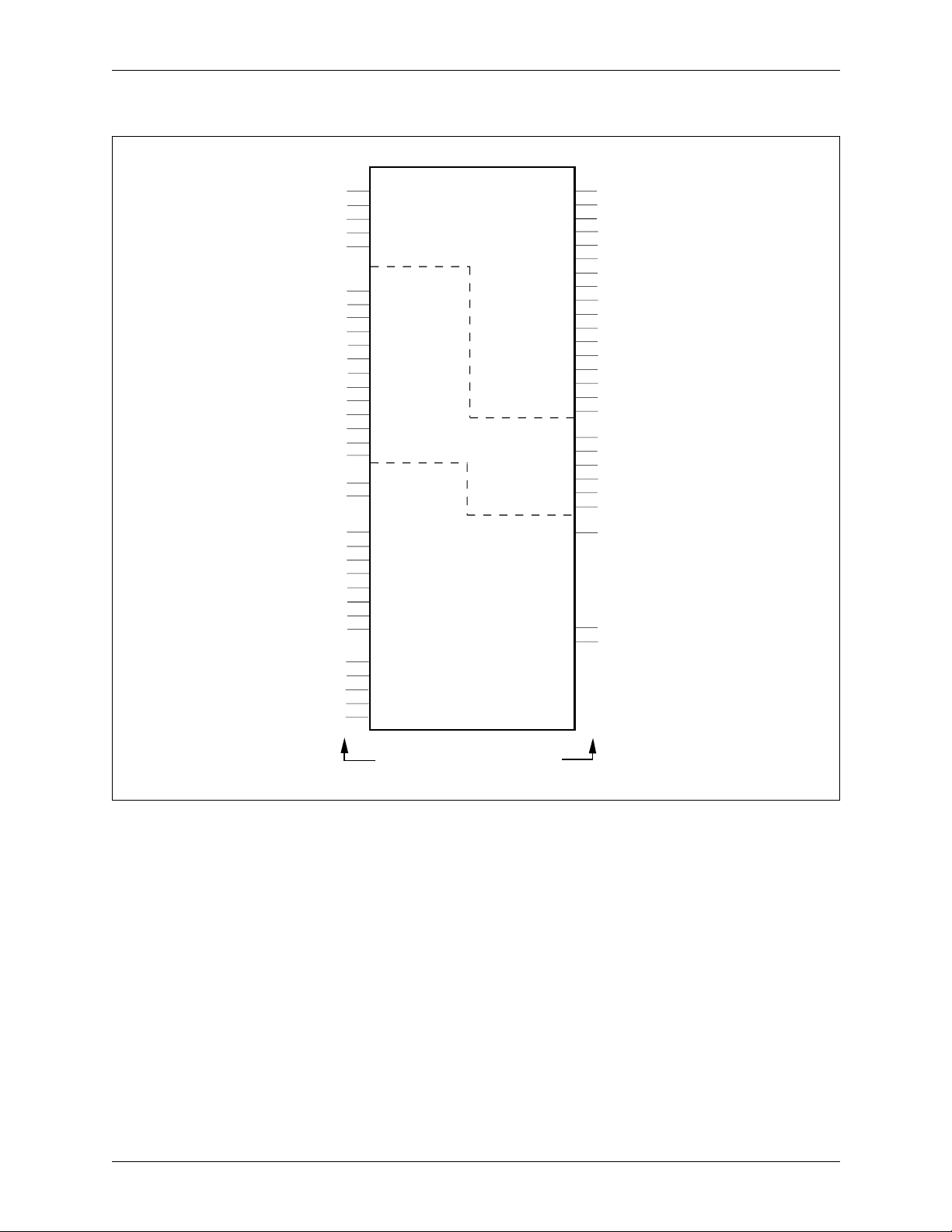

4.4 Mechanical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Appendix A Multimegabit HDLC Formatter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.2 Block and Logic Diagrams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

A.3 PPDL Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

A.3.1 PPDL Receiver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-7

Appendix B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

B.1 DS3CKI Clock Duty Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

B.2 Overhead Bit Insertion in E3 Parallel Payload Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

B.3 HDLC Formatter Mode Support While Config ured for E3 Framing . . . . . . . . . . . . . . . . . . . . . . . B-2

Appendix C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

100441E Conexant iii

CN8330

DS3/E3 Framer with 52 Mbps HDLC Controller

iv Conexant 100441E

CN8330 List of Figures

DS3/E3 Framer with 52 Mbps HDLC Controller

List of Figures

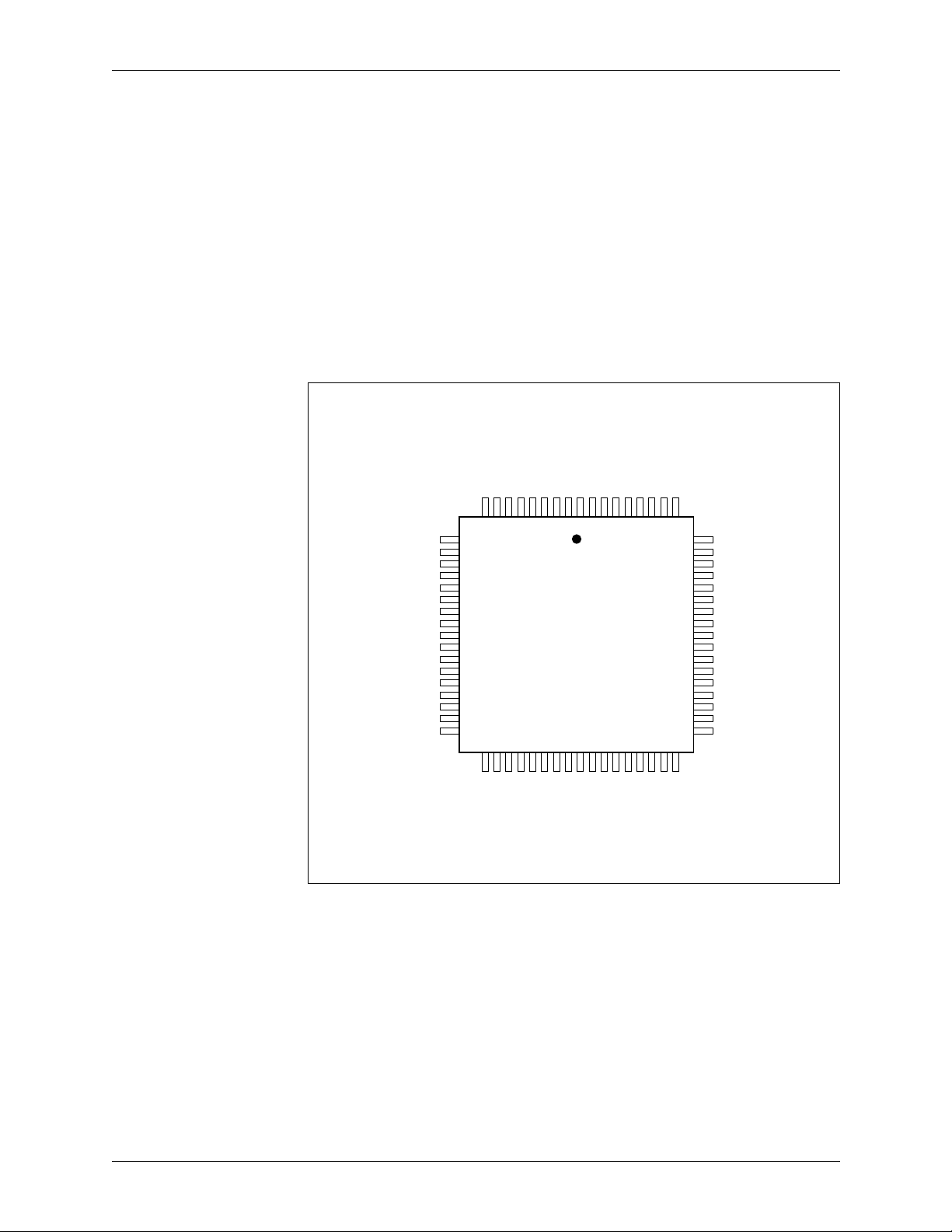

Figure 1-1. CN8330 Pinout Diagram - 68-Pin PLCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

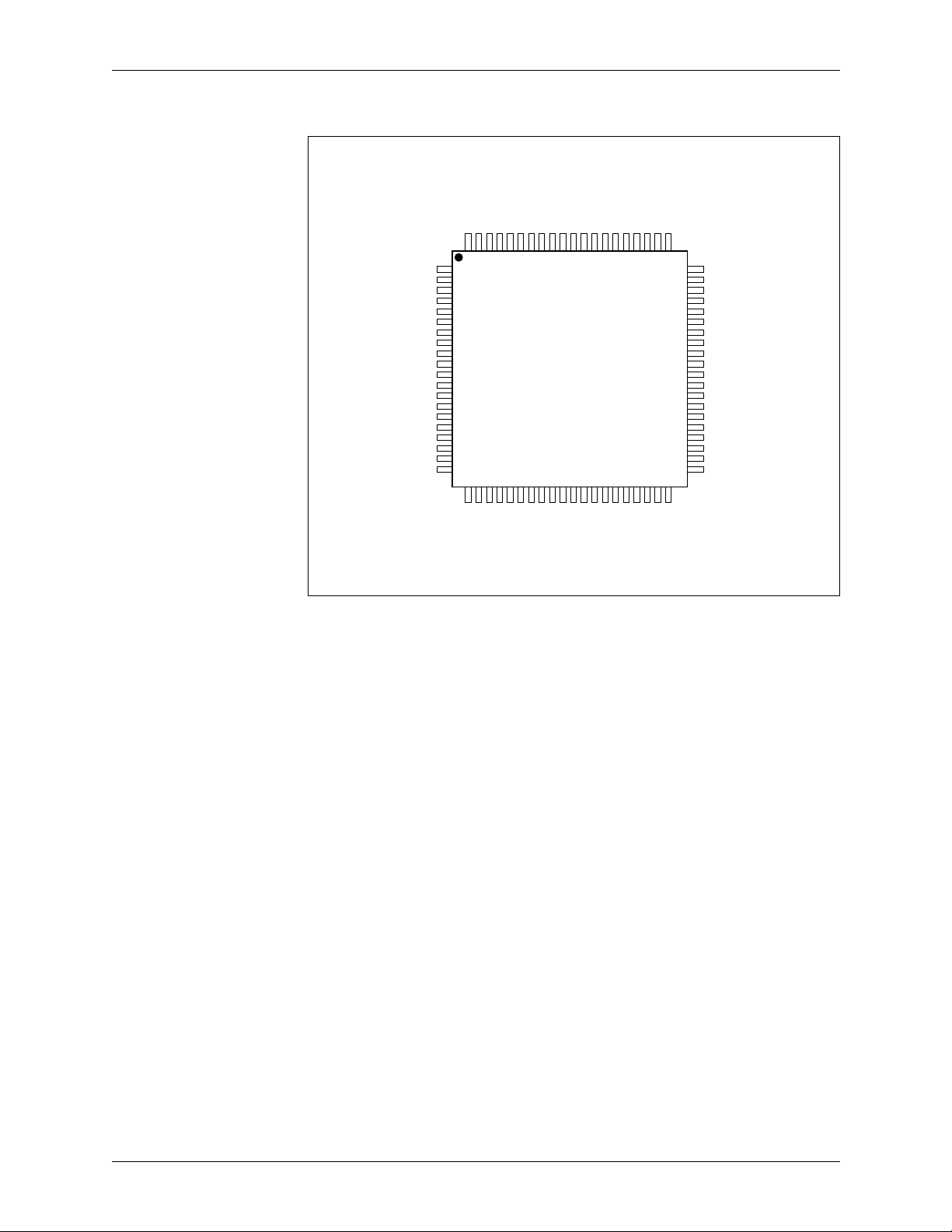

Figure 1-2. CN8330 Pinout Diagram - 80-Pin MQFP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Figure 1-3. CN8330 Framer Functional Logic Diagram - 68-Pin PLCC . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Figure 1-4. CN8330 Framer Functional Logic Diagram - 80-Pin MQFP . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Figure 2-1. Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 2-2. Transmitter Line Driver Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Figure 2-3. Clocked Receiver Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Figure 2-4. Transmitter Timing for Serial DS3 Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Figure 2-5. Transmitter Timing for Parallel DS3 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Figure 2-6. Transmitter Timing for Serial E3 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Figure 2-7. C-Bit Input Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Figure 2-8. PPDL Transmitter Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

Figure 2-9. Nibble Mode with the PPDLONLY Control Pin Low. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

Figure 2-10. VCO Output Signal Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

Figure 2-11. Receiver Timing for Serial DS3 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

Figure 2-12. Receiver Timing for Parallel DS3 Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

Figure 2-13. E3 Receiver Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

Figure 2-14. PPDL Receiver Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31

Figure 2-15. C-Bit Output Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

Figure 2-16. Monitor Mode Error Indication Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35

Figure 4-1. Microprocessor Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Figure 4-2. Output and Input Signal Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Figure 4-3. 68–Pin Plastic Leaded Chip Carrier (J-Bend) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Figure 4-4. 80-Pin Metric Quad Flat Pack (MQFP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Figure A-1. HDLC Formatter Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-2

Figure A-2. HDLC Formatter Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-4

Figure A-3. HDLC Formatter Logic Diagram - 80-Pin MQFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

Figure A-4. PPDL Transmitter Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

Figure A-5. PPDL Receiver Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-9

100441E Conexant v

List of Figures CN8330

DS3/E3 Framer with 52 Mbps HDLC Controller

vi Conexant 100441E

CN8330 List of Tables

DS3/E3 Framer with 52 Mbps HDLC Controller

List of Tables

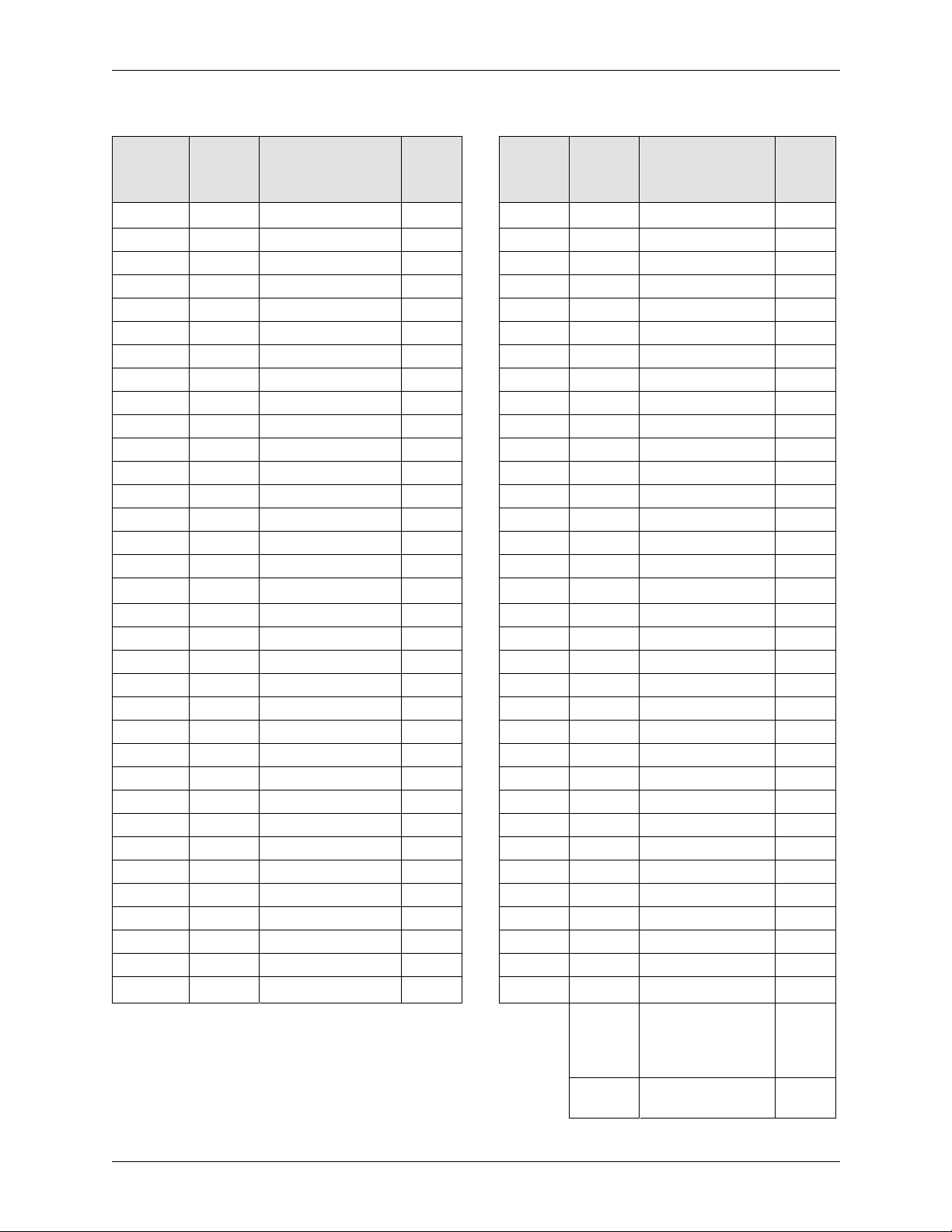

Table 1-1. Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Table 1-2. Hardware Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

Table 2-1. Transmit Encoding Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

Table 3-1. Register Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 -15

Table 3-2. Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

Table 3-3. Transmit Terminal Data Link Message Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

Table 3-4. Receive Terminal Data Link Message Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

Table 4-1. Microprocessor Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Table 4-2. Clock Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Table 4-3. Output Signal Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Table 4-4. Input Setup/Hold Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Table 4-5. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Table 4-6. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Table 4-7. Output Drive Capability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

100nnnx Conexant vii

List of Tables CN8330

DS3/E3 Framer with 52 Mbps HDLC Controller

viii Conexant 100nnnx

1

1.0 Product Description

The CN8330 is a frame synchronization, recovery, and signal generation circuit.

Applications for digital terminals include digi tal cross-connect syst ems, customer

premise multiplexers, channel extenders, network managers, PBXs, Switched

Multimegabit Digital Service (SMDS) equipment, and monitor or test equipment.

The integrated circuit features a High-Level Data Link Control (HDLC) formatter

usable with or without DS3/E3 framing. The CN8330 framer is designed to meet

the requirements of DS3 and E3 transmission and reception formats as per ANSI

T1.107-1988, T1.107a-1989, T1.404, and ITU-T G.751 standards. Both the

LAPD terminal data link and the Far End Alarm Control (FEAC) channel, as

defined in T1.107a-1989, are supported. All maintenance features required by

Bellcore TR-TSY-000009 and AT&T PUB 54014 are furnished. HDLC data

transmission according to ITU-T standard Q.921 and ISO 3309-1984 is

supported, as are SMDS standards prETS 300 214 and TR-TSV-000773.

The framer provides framing recovery for M13, C-bit parity, and G.751 E3

formatted signals. The receiv ed data stream is available serially for unchannelized

applications or for external decoding of the asynchronous multiplexed formats.

The framing circuit has an average reframe time of less than 1 msec for DS3

signals and less than 250 µsec for E3 signals. A First In First Out (FIFO) buffer in

the receive signal path can be enabled to reduce the jitter on the incoming data.

The framer circuitry is capable of operating to 52 MHz, making it compatible

with High-Speed Serial Interface (HSSI) signals or DS3 and E3 signals that are

embedded in SONET STS-1 or SDH STM-1 carriers.

The transmitter can process serial data from an external pin, or in byte- or

nibble-oriented data format from the Payload Parallel Data Link (PPDL) data

port. DS3 overhead bits or E3 Frame Alignment Signal (FAS) bits are

automatically inserted. The parallel data can be form at te d with idle flags, zero

stuffing for transparency, and a selectable 16- or 32-bit Frame Check Sequence

(FCS). Bytes or nibbles without HDLC formatting can also be transmitted. The

transmitter also generates an Alarm Indication Signal (AIS), idle code, yellow

alarm, and all-ones signals. DS3 C-bits (or E3 N-bits) can be inserted into the

data stream from an external source.

The circuit can be configured as a high-speed data formatter without inserting

the CN8330 o verhead bits. This allows the c ircu it t o b e used f or data applications

on communication links other than those requiring DS3 or E3 formatting. Data

bytes can be formatted with HDLC flags and FCS bytes for transmission at any

speed up to 52 MHz.

100441E Conexant 1-1

1.0 Product Description CN8330

DS3/E3 Framer with 52 Mbps HDLC Controller

Configuration, control, and monitoring of t he C N8330 t ermination ci rcui t and

framer are accomplished with a selectable microprocessor control mode that

monitors all status conditio ns and pr ovides configuration control. In DS3 mode a

stand-alone mode of operation is featured. This allows the circuit to operate as a

monitor and provide status and alarm indications to external processing or

counting circuitry including:

• AIS, all-ones

• Yellow alarm

• Loss of signal

• Idle code detection

• Out-of-frame and frame-bit error counting

• Parity error

• LCV (Line Code Violation)

• Path parity

• X-bit disagreement

• FEBE event counting

The received DS3 C-bits (or E3 N-bits) are directed to an external pin to

provide visibility for external processing, as require d.

1-2 Conexant 100441E

CN8330 1.0 Product Description

DS3/E3 Framer with 52 Mbps HDLC Controller

1.1 Pin Descriptions

The CN8330 Framer is pa ckaged i n a 6 8-pin Plastic L eaded Chip Carrier (PLCC)

and an 80-pin Metric Quad Flat Pack (MQFP) and shown in Figure 1-1 and

Figure 1-2 respectively. Pin assignments are listed in numerical order in

Table 1-1. Figure 1-3 and Figure 1-4 illustrate functionally partitioned logic

diagrams of the CN8330. Pin descriptions, labels, and I/O assignments are

detailed in Table 1-2.

Figure 1-1. CN8330 Pinout Diagram - 68-Pin PLCC

RXPOS

RXNEG

DS3CKI

TCLKO

RXDAT

RXMSY

RXBCK/RXGAPCK

RXCLK

IDLE/FRMCAR

VALFCS/TXOVH

GND

FIFEN

VCO

RXCKI

V

INIT*

GND

1.1 Pin Descriptions

AD[0]/LOS

AD[1]/OOF

AD[2]/AIS

AD[3]/YEL

AD[4]/IDLE

AD[5]/PAR

987654321

10

11

12

13

14

15

16

17

DD

18

19

20

21

22

23

24

25

26

2728293031323334353637383940414243

AD[6]/LCV

AD[7]/FRMERR

GND

CN8330

Framer

DD

V

ALE/PAREN

WR*CRC32

RD*/ALM1

CS/ALM0

DLINT/SOURCELB

68676665546362

CNTINT/LINELB

MON/MIC*

61

60

TESTI

59

TXSYO

58

TXCKI

57

TXBCK/TXGAPCK

56

TDAT[7]/TXSYI

55

TDAT[6]/TXDATI

54

TDAT[5]/TXENCI

53

TDAT[4]/LCVERRI

52

GND

51

V

DD

50

TDAT[3]

49

TDAT[2]

48

TDAT[1]

47

TDAT[0]

46

TXCCK

45

CBITI

44

PPDLONLY

VDD

GND

RDAT[2]/AID

RDAT[0]/LOS

RDAT[1]/OOF

RDAT[3]/IDLE

RDAT[4]/FRMERR

RDAT/LCVCAR

RDAT[7]TXNRZ

RDAT[6]/RXOVH

CBITO

TESTO

TXPOS

TXNEG

SNDMSG

RXCCK/TXNRZ

SNDFCS

100441E Conexant 1-3

1.0 Product Description CN8330

1.1 Pin Descriptions DS3/E3 Framer with 52 Mbps HDLC Controller

Figure 1-2. CN8330 Pinout Diagram - 80-Pin MQFP

AD0/LOS

AD1/OOF

AD2/AIS

AD3/YEL

AD4/IDLE

AD5/PAR

AD6/LCV

AD7/FRMERR

GND

GND

VDDALE/PAREN

W*/CRC32

RD*/ALM1

CS/ALMO

DLINT/SOURCELB

CNTINT/LINELB

MON/MIC*NCNC

GND

FIFEN

VCO

RXPOS

RXNEG

DS3CKI

RXCKI

V

TCLKO

INIT*

RXDAT

RXMSY

RXCLK

RXBCK/RXGAPCK

IDLE/FRMCAR

VALFCS/TXOVH

GND

GND

80797877767574737271706968676665646362

1

NC

2

3

4

5

6

7

8

9

DD

10

11

12

13

14

15

16

17

18

19

20

NC

21222324252627282930313233343536373839

NC

RDAT0/LOS

RDAT1/OOF

RDAT2/AIS

RDAT3/IDLE

CN8330

Framer

RDAT7/TXNRZ

RDAT6/RXOVH

RDAT5/LCVCAR

RDAT4/FRMERR

DD

V

GND

GND

CBITO

TXNEG

RXCCK/TXNRZ

TESTO

TXPOS

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

NC

SNDFCS

SNDMSG

NC

NC

TESTI

TXSYO

TXCKI

TXVBCK/TXGAPCK

TDAT[7]/TXSYI

TDAT[6]/TXDATI

TDAT[5]/TXENCI

TDAT[4]/LCVERRI

GND

GND

V

DD

TDAT3

TDAT2

TDAT1

TDAT0

TXCCK

CBITI

PPDLONLY

8330_002

1-4 Conexant 100441E

CN8330 1.0 Product Description

DS3/E3 Framer with 52 Mbps HDLC Controller

1.1 Pin Descriptions

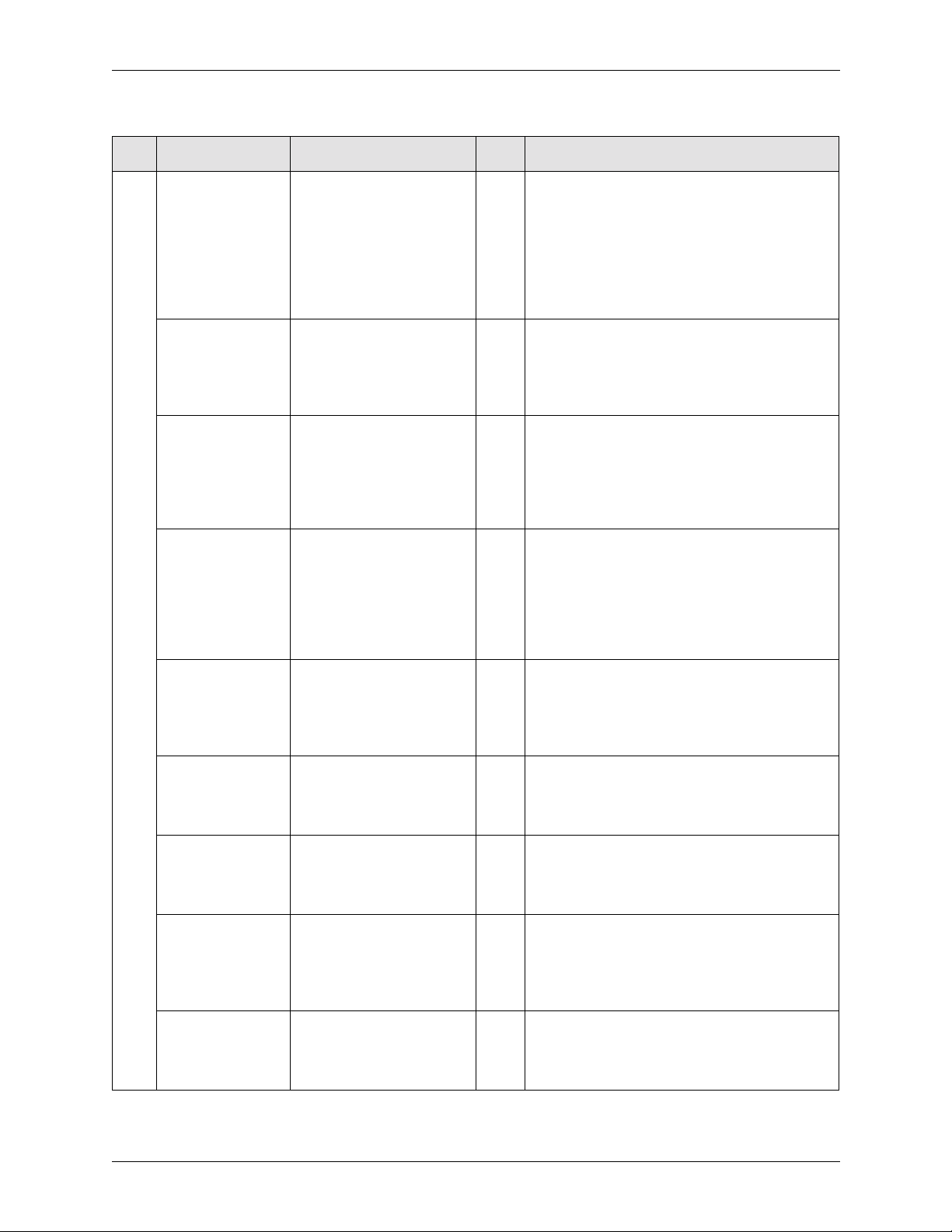

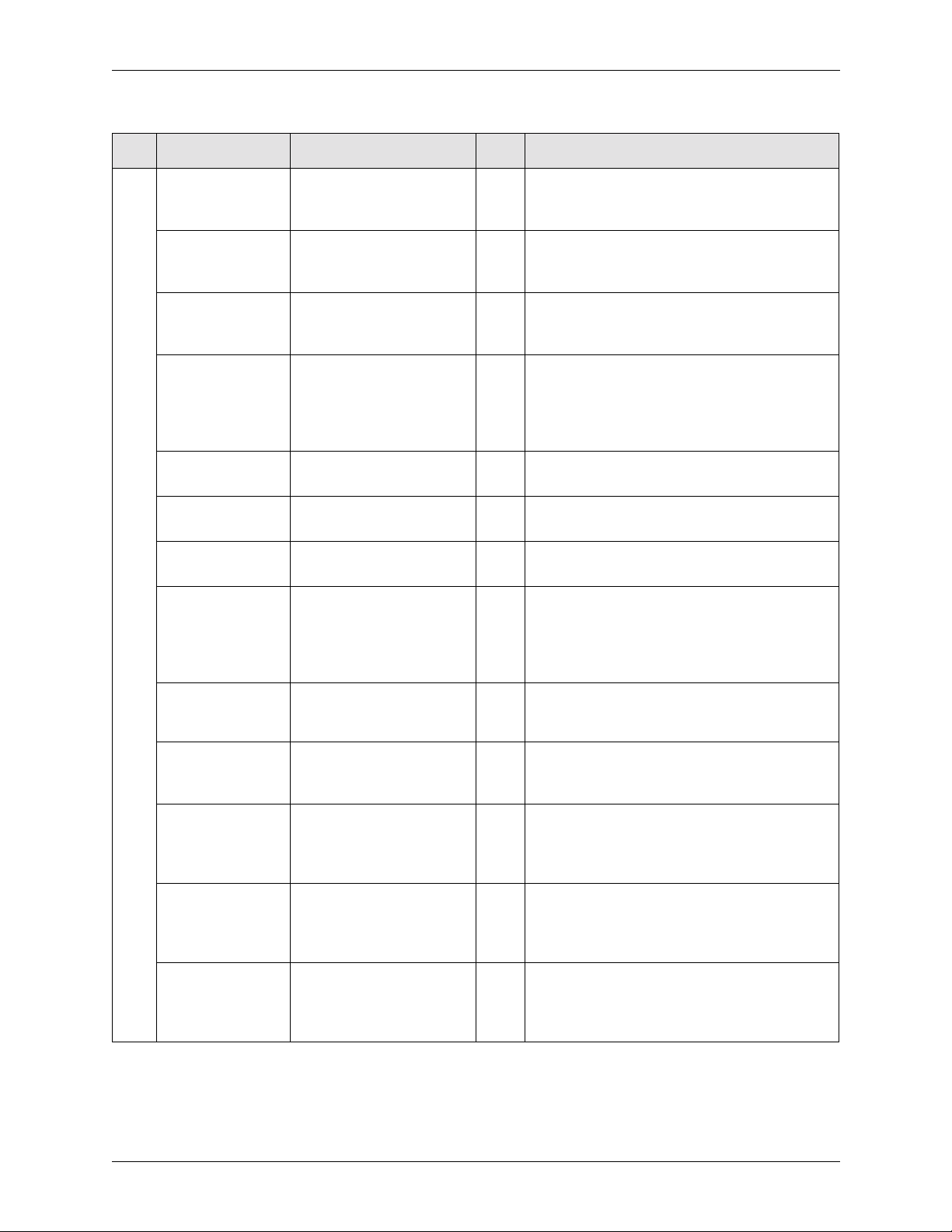

Table 1-1. Pin Descriptions

Pin

(68-Pin

PLCC)

1 72 GND I 35 30 V

2 73 AD[7]/FRMERR B/O 36 31 GND I

3 74 AD[6]/LCV B/O 37 33 CBITO O

4 75 AD[5]/PAR B/O 38 34 RXCCK/TXNRZ O

5 76 AD[4]/IDLE B/O 39 35 TXNEG O

6 77 AD[3]YEL B/O 40 36 TXPOS O

7 78 AD[2]/AIS B/O 41 37 TESTO O

8 79 AD[1]/OOF B/O 42 38 SNDMSG I

9 80 AD[0]/LOS B/O 43 39 SNDFCS I

10 2 GND I 44 41 PPDLONLY I

11 3 FIFEN I 45 42 CBITI I

12 4 VCO O 46 43 TXCCK O

13 5 RXPOS I 47 44 TDAT[0] I

14 6 RXNEG I 48 45 TDAT[1] I

15 7 DS3CKI I 49 46 TDAT[2] I

16 8 RXCKI I 50 47 TDAT[3] I

17 9 V

18 10 TCLKO O 52 49 GND I

19 11 INIT* I 53 51 TDAT[4]/LCVERRI I

20 12 RXDAT O 54 52 TDAT[5]/TXENCI I

21 13 RXMSY O 55 53 TDAT[6]/TXDATI I

22 14 RXCLK O 56 54 TDAT[7]/TXSYI I

23 15 RXBCK/RXGAPCK O 57 55 TXBCK/TXGAPCK O

24 16 IDLE/FRMCAR O 58 56 TXCKI I

25 17 VALFCS/TXOVH O 59 57 TXSYO O

26 18 GND I 60 58 TESTI I

27 22 RDAT[0]/LOS O 61 63 MON/MIC* I

28 23 RDAT[1]/OOF O 62 64 CNTINT/LINELB O/I

29 24 RDAT[2]/AIS O 63 65 DLINT/SOURCELB O/I

30 25 RDAT[3]/IDLE O 64 66 CS/ALM0 I

31 26 RDAT[4]/FRMERR O 65 67 RD*/ALM1 I

32 27 RDAT[5]/LCVCAR O 66 68 WR*/CRC32 I

33 28 RDAT[6]/RXOVH O 67 69 ALE/PAREN I

34 29 RDAT[7]/TXNRZ O 68 70 V

Pin

(80-Pin

MQFP)

Pin Label I/O

DD

Pin

(68-Pin

PLCC)

I5148VDDI

Pin

(80-Pin

MQFP)

1,20,

21,40,

59,60,

61,62

19,32,

50,71

Pin Label I/O

DD

DD

N/C –

GND I

I

I

100441E Conexant 1-5

1.0 Product Description CN8330

1.1 Pin Descriptions DS3/E3 Framer with 52 Mbps HDLC Controller

Figure 1-3. CN 8330 Framer Fun ctional Logic Di agram - 68-Pin PLCC

Rx Bipolar Pos

Rx Bipolar Neg

Rx Line Clock In

Dejittered Clock In

FIFO Enable

Tx Clock In

Tx C/N Bit Serial In

Tx Data Bit MSB/Tx M-Sync In

Tx Data Bit 6/Tx Serial Data In

Tx Data Bit 5/Tx Encoder In

Tx Data Bit 4/LCV Error In

Tx Data Bit 3

Tx Data Bit 2

Tx Data Bit 1

Tx Data Bit LSB

Send FCS

Send Message

Parallel Data Only Select

Test In

InitializationII

Address-Data 0/Loss of Signal

Address-Data 1/Out of Frame

Address-Data 2/Alarm Indication Signal

Address-Data 3/Yellow Alarm Detect

Address-Data 4/Idle Code Detection

Address-Data 5/Parity Error Detect

Address-Data 6/Line Code Violation

Address-Data 7/Frame Bit Error

Address Latch Enable/Parallel Input Enable

Chip Select/Alarm 0

Read*/Alarm 1

Write*/Cycle Redundancy Check 32

Monitor/Microprocessor*

B/O

B/O

B/O

B/O

B/O

B/O

B/O

B/O

13

I

RXPOS

14

I

RXNEG

15

I

DS3CKI

16

I

RXCKI

11

I

FIFEN

58

TXCKI

I

45

CBITI

I

56

TDAT[7]/TXSYI

I

55

TDAT[6]/TXDATI

I

54

TDAT[5]/TXENCI

I

53

TDAT[4]/LCVERRI

I

50

TDAT[3]

I

49

TDAT[2]

I

48

TDAT[1]

I

47

TDAT[0]

I

43

SNDFCS

I

42

SNDMSG

I

44

PPDLONLY

I

60

TESTI

19

INIT*

9

AD[0]/LOS

8

AD[1]/OOF

7

AD[2]/AIS

6

AD[3]/YEL

5

AD[4]/IDLE

4

AD[5]/PAR

3

AD[6]/LCV

2

AD[7]/FRMERR

67

I

ALE/PAREN

64

I

CS/ALM0

65

I

RD*/ALM1

66

I

WR*/CRC32

61

I

MON/MIC*

Receiver

Section

RDAT[7]/TXNRZ

RDAT[6]/RXOVH

RDAT[5]/LCVCAR

RDAT[4]/FRMERR

VALFCS/TXOVH

RXBCK/RXGAPCK

TXBCK/TXGAPCK

Transmitter

Section

Microprocessor

Interface

CNTINT/LINELB

DLINT/SOURCELB

RXDAT

RXMSY

RXCLK

CBITO

RXCCK/TXNRZ

RDAT[3]/IDLE

RDAT[2]/AIS

RDAT[1]/OOF

RDAT[0]/LOS

IDLE/FRMCAR

VCO

TXCCK

TXPOS

TXNEG

TXSYO

TCLKO

TESTO

Rx Serial Data

20

O

Rx M-Sync

21

O

Rx Clock

22

O

Rx C/N Bit Serial Out

37

O

Rx C/N-Bit Clock Out/TxNRZ

38

O

Rx Data Bit MSB/TxNRZ

34

O

Rx Data Bit 6/RX Overhead

33

O

Rx Data Bit 5/ Line Code Violation Carry

32

O

Rx Data Bit 4/Frame Bit Error

31

O

Rx Data Bit 3/Idle Code Detection

30

O

Rx Data Bit 2/Alarm Indication Signal

29

O

Rx Data Bit 1/Out of Frame

28

O

Rx Data Bit LSB/Loss of Signal

27

O

Idle Data Rcvd/Frame Carry

24

O

Valid FCS Rcvd/TX Overhead

25

O

Voltage-Controlled Oscillator Output

12

O

Rx Byte Clock/Gapped Clock

23

O

Tx Byte Clock/Gapped Clock

57

O

Tx C/N Bit Clock

46

O

Tx Bipolar Pos

40

O

Tx Bipolar Neg

39

O

Tx M-Sync Out

59

O

Tx Clock Out

18

O

41

Test Out

O

62

Counter Interrupt/Line Loopback

O/I

63

Data Link Interrupt/Source Loopback

O/I

B = Bidirectional, I = Input, O = Output

1-6 Conexant 100441E

CN8330 1.0 Product Description

DS3/E3 Framer with 52 Mbps HDLC Controller

Figure 1-4. CN 8330 Framer Fun ctional Logic Di agram - 80-Pin MQ FP

B/O

B/O

B/O

B/O

B/O

B/O

B/O

B/O

5

I

RXPOS

6

I

RXNEG

7

I

DS3CKI

8

I

RXCKI

3

I

FIFEN

56

TXCKI

I

42

CBITI

I

54

TDAT[7]/TXSYI

I

53

TDAT[6]/TXDATI

I

52

TDAT[5]/TXENCI

I

51

TDAT[4]/LCVERRI

I

47

TDAT[3]

I

46

TDAT[2]

I

45

TDAT[1]

I

44

TDAT[0]

I

39

SNDFCS

I

38

SNDMSG

I

41

PPDLONLY

I

58

TESTI

11

INIT*

80

AD[0]/LOS

79

AD[1]/OOF

78

AD[2]/AIS

77

AD[3]/YEL

76

AD[4]/IDLE

75

AD[5]/PAR

74

AD[6]/LCV

73

AD[7]/FRMERR

69

I

ALE/PAREN

66

I

CS/ALM0

67

I

RD*/ALM1

68

I

WR*/CRC32

63

I

MON/MIC*

Receiver

Section

RDAT[7]/TXNRZ

RDAT[6]/RXOVH

RDAT[5]/LCVCAR

RDAT[4]/FRMERR

VALFCS/TXOVH

RXBCK/RXGAPCK

TXBCK/TXGAPCK

Transmitter

Section

Microprocessor

Interface

CNTINT/LINELB

DLINT/SOURCELB

RXCCK/TXNRZ

Rx Bipolar Pos

Rx Bipolar Neg

Rx Line Clock In

Dejittered Clock In

FIFO Enable

Tx Clock In

Tx C/N Bit Serial In

Tx Data Bit MSB/Tx M-Sync In

Tx Data Bit 6/Tx Serial Data In

Tx Data Bit 5/Tx Encoder In

Tx Data Bit 4/LCV Error In

Tx Data Bit 3

Tx Data Bit 2

Tx Data Bit 1

Tx Data Bit LSB

Send FCS

Send Message

Parallel Data Only Select

Test In

InitializationII

Address-Data 0/Loss of Signal

Address-Data 1/Out of Frame

Address-Data 2/Alarm Indication Signal

Address-Data 3/Yellow Alarm Detect

Address-Data 4/Idle Code Detection

Address-Data 5/Parity Error Detect

Address-Data 6/Line Code Violation

Address-Data 7/Frame Bit Error

Address Latch Enable/Parallel Input Enable

Chip Select/Alarm 0

Read*/Alarm 1

Write*/Cycle Redundancy Check 32

Monitor/Microprocessor*

RXDAT

RXMSY

RXCLK

CBITO

RDAT[3]/IDLE

RDAT[2]/AIS

RDAT[1]/OOF

RDAT[0]/LOS

IDLE/FRMCAR

VCO

TXCCK

TXPOS

TXNEG

TXSYO

TCLKO

TESTO

1.1 Pin Descriptions

Rx Serial Data

12

O

Rx M-Sync

13

O

Rx Clock

14

O

Rx C/N Bit Serial Out

33

O

Rx C/N-Bit Clock Out/TxNRZ

34

O

Rx Data Bit MSB/TxNRZ

29

O

Rx Data Bit 6/RX Overhead

28

O

Rx Data Bit 5/ Line Code Violation Carry

27

O

Rx Data Bit 4/Frame Bit Error

26

O

Rx Data Bit 3/Idle Code Detection

25

O

Rx Data Bit 2/Alarm Indication Signal

24

O

Rx Data Bit 1/Out of Frame

23

O

Rx Data Bit LSB/Loss of Signal

22

O

Idle Data Rcvd/Frame Carry

16

O

Valid FCS Rcvd/TX Overhead

17

O

Voltage-Controlled Oscillator Output

4

O

Rx Byte Clock/Gapped Clock

15

O

Tx Byte Clock/Gapped Clock

55

O

Tx C/N Bit Clock

43

O

Tx Bipolar Pos

36

O

Tx Bipolar Neg

35

O

Tx M-Sync Out

57

O

Tx Clock Out

10

O

37

Test Out

O

64

Counter Interrupt/Line Loopback

O/I

65

Data Link Interrupt/Source Loopback

O/I

B = Bidirectional, I = Input, O = Output

100441E Conexant 1-7

1.0 Product Description CN8330

1.1 Pin Descriptions DS3/E3 Framer with 52 Mbps HDLC Controller

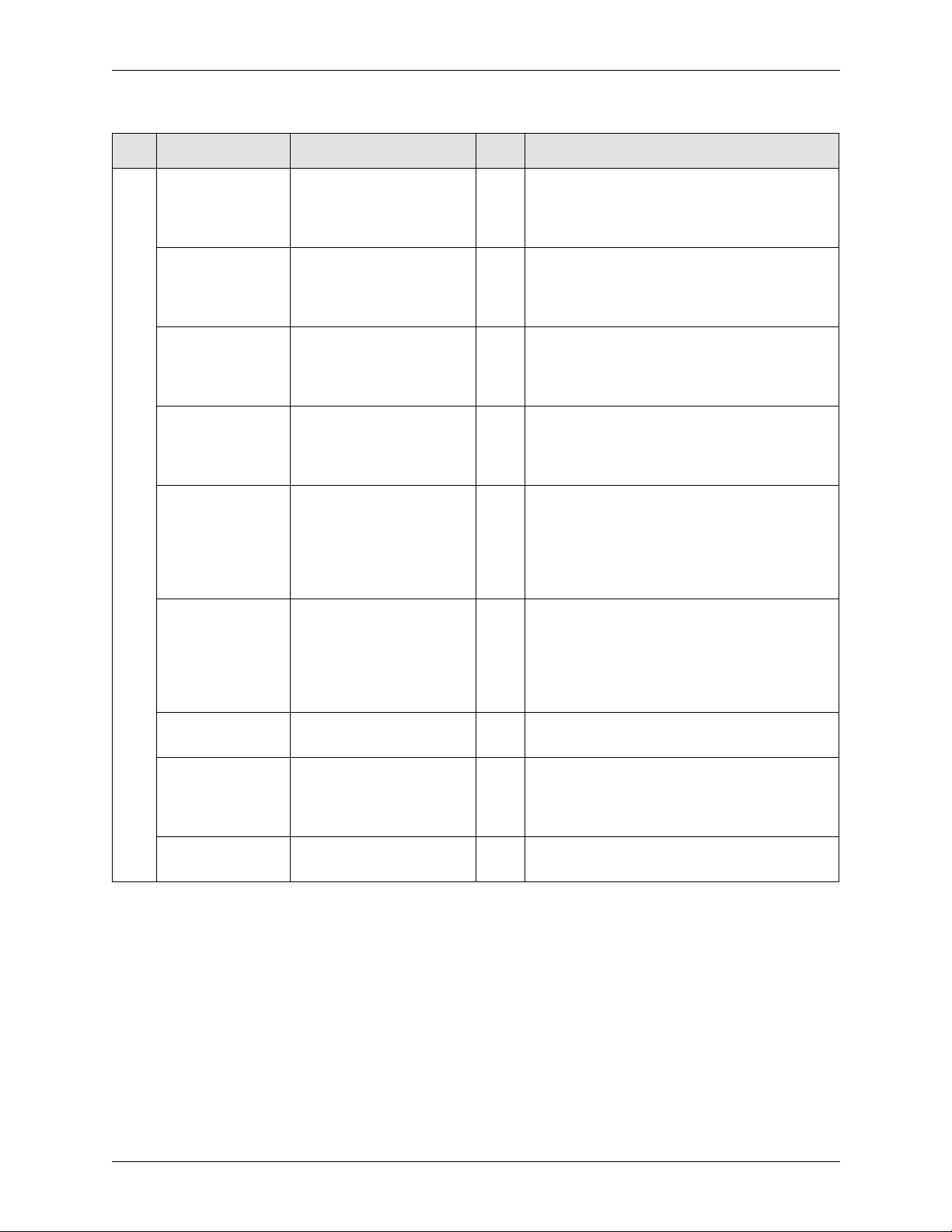

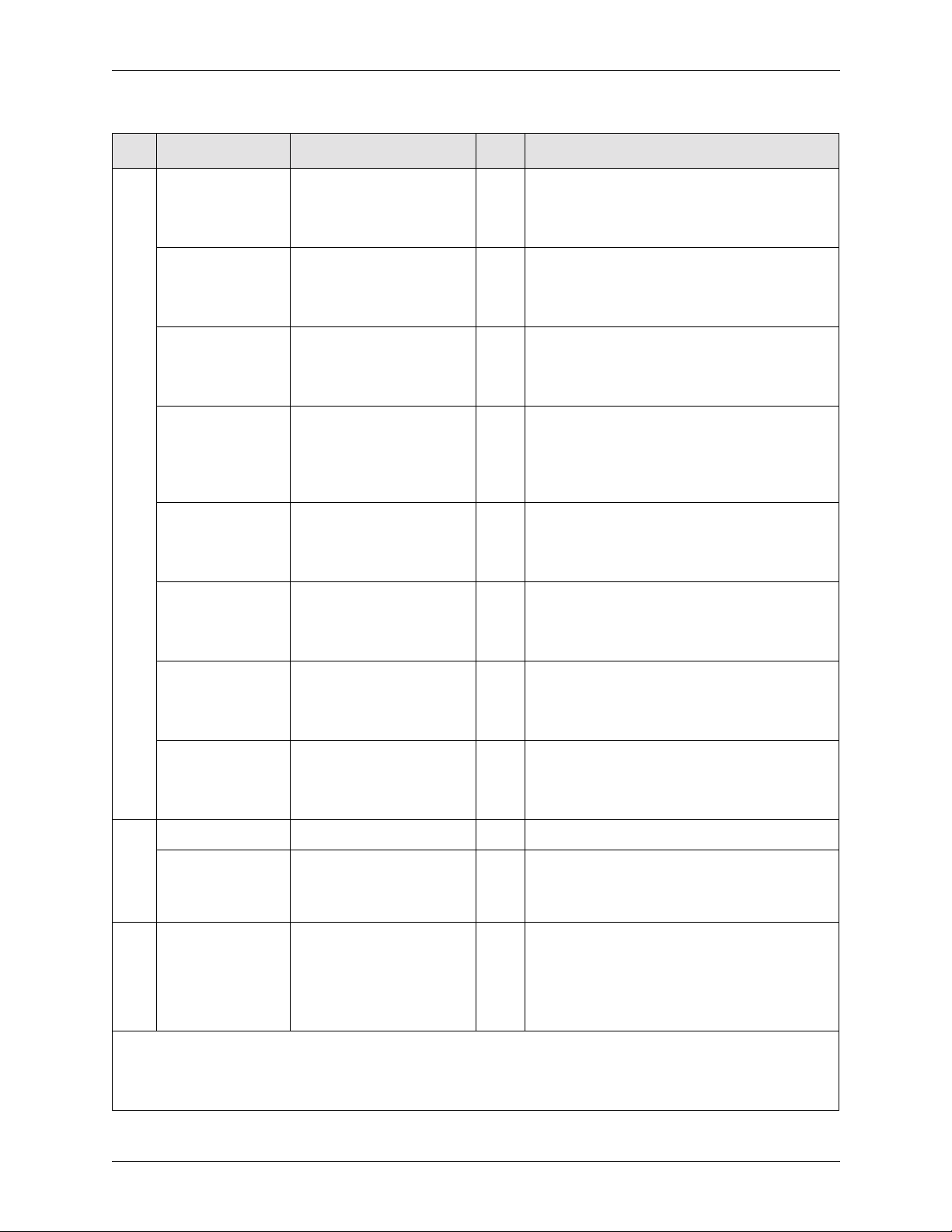

Table 1-2. Hardware Signal Definitions (1 of 5)

Pin Label Signal Name I/O Definition

ALE/PAREN Address L a tch

Enable/Parallel Input Enable

I A dual-purpose active-high signal which, when

MON/MIC* is tied low, is microprocessor-generated

and causes the CN8330 to latch in the address on

the address-data bus. When MON/MIC* is tied high

(stand-alone mode), the parallel input for the PPDL

formatter is e nabled. When this pin is tied low,

transmit data is sourced from the serial input

TDAT[6]/TXDAT.

(1)

CS/ALM0 C hip Select/Alarm 0 I A dual-purpose signal that enabl es read/write

functions when MON/MIC* is tied low, and controls

AIS transmission in stand-alone mode when

MON/MIC* is tied high. Both CS and ALM0 are

active high signals.

(1)

RD*/ALM1 Read/Alarm 1 I A dual-purpose signal tha t en ables read data to be

passed to the address-data bus when MON/MIC* is

tied low, and controls idle code tr ansmission in

stand-alone mode when MON/MIC* is tied high,

WR*/CRC32 Write/Cycle Redundancy

Check 32

RD* is an active low signal and ALM1 is

active-high.

I A dual-purpose signal t hat latches write data from

the address-data bus when MON /MIC* is tied low,

(1)

and controls the Cycle Redundancy Check (CRC)

when MON/MIC* is tied high. WR* is an active low

signal. In stand-alone mode, a high-speed 32-bit

CRC calculation is enabled if CRC32 is high; if low, a

16-bit calculation is performed.

(1)

MON/MIC* Monitor/Microprocessor

Microprocessor Interface

Mode Select

AD[0]/LOS A ddress-Data 0/Loss of

Signal

I Selects either microprocessor mode when tied low,

or stand-alone monitor mode when tied high. The

state of MON/MIC* determines which function the

dual-purpose pin s (AD[7:0]) serve. The standalone

mode is valid only in DS3 mode.

(1)

B/O Part of the bidirectional 8-bit multiplexed

address-data bus when MON/MIC* is tied low. When

in stand-al one mode, this pin is an active-hig h

monitor output ind ic a t in g los s of si gn al.

(1)

AD[1]/OOF Address-Data 1/Out of Frame B /O Part of the bidirectional 8-bit multiplexed

address-data bus when MON/MIC* is tied low. When

AD[2]/AIS Address-Data 2/Alarm

Indication Signal

in stand-al one mode, this pin is an active-hig h

monitor output indicating an out-of-frame state.

B/O Part of the bidirectional 8-bit multiplexed

address-data bus when MON/MIC* is tied low. When

(1)

in stand-al one mode, this pin is an active-hig h

AD[3]/YEL Address-Data 3/Yellow Alarm

Detection

monitor output indicating alarm indication signal

detection.

B/O Part of the bidirectional 8-bit multiplexed

address-data bus when MON/MIC* is tied low. When

in stand-al one mode, this pin is an active-hig h

monitor output indicati ng a yellow alarm.

(1)

(1)

1-8 Conexant 100441E

CN8330 1.0 Product Description

DS3/E3 Framer with 52 Mbps HDLC Controller

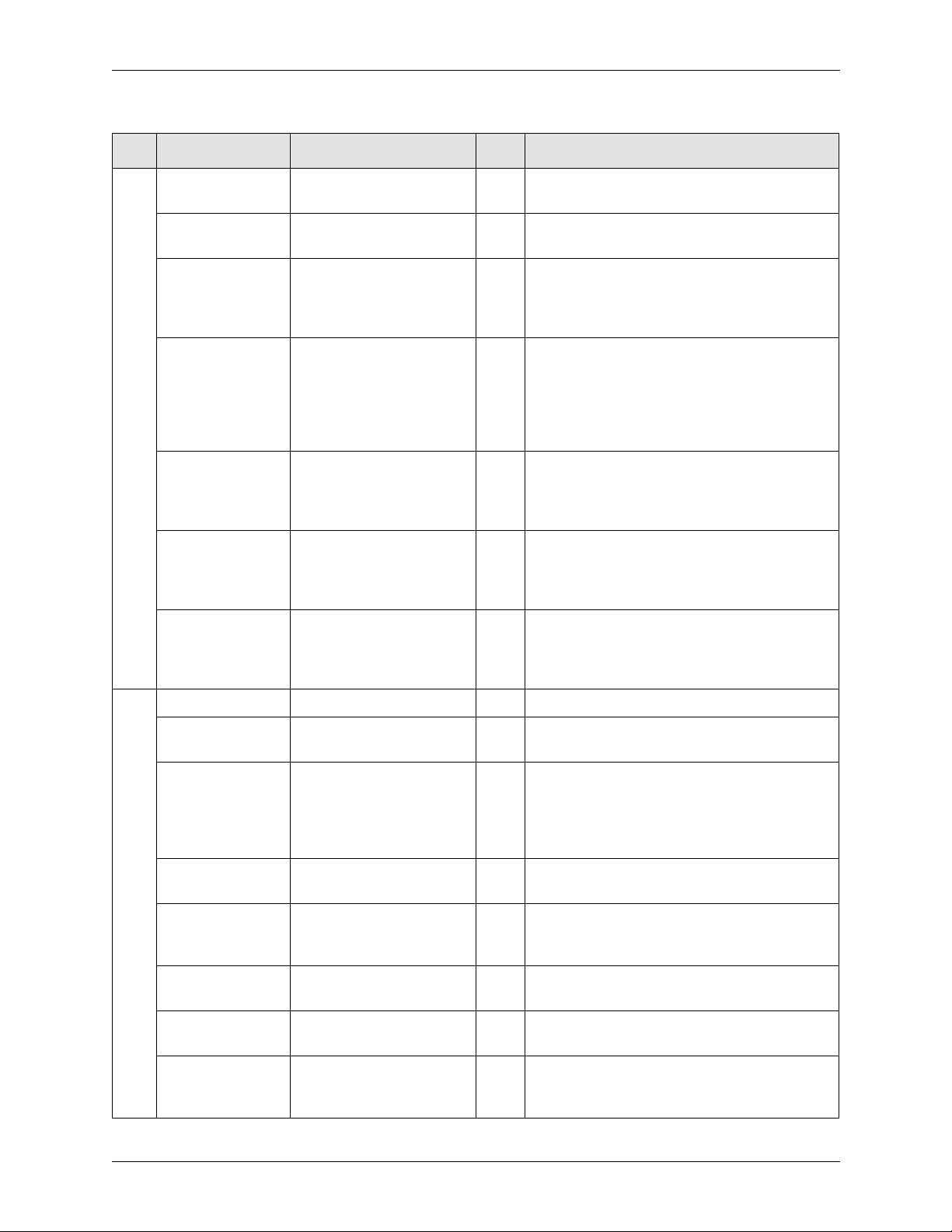

Table 1-2. Hardware Signal Definitions (2 of 5)

Pin Label Signal Name I/O Definition

AD[4]/IDLE Addr ess-Data 4/Idle Code

Detection

AD[5]/PAR Address-Data 5/Parity Error

Detection

AD[6]/LCV Address-Data 6/L ine Code

Violation

AD[7]/FRMERR Address-Data 7/

Frame Bit Error

CNTINT/LINELB Counter Interrupt/

Line Loopback

Microprocessor Interface

DLINT/SOURCELB Data Link Interrupt/Source

Loopback

1.1 Pin Descriptions

B/O Part of the bidirectional 8-bit multiplexed

address-data bus when MON/MIC* is tied low. When

in stand-al one mode, this pin is an active-hig h

monitor output ind ic a tin g an idl e co d e de tec t io n.

(1)

B/O Part of the bidirectional 8-bit multiplexed

address-data bus when MON/MIC* is tied low. When

in stand-al one mode, this pin is an active-hig h

monitor output indicating a parity error.

(1)

B/O Part of the bidirectional 8-bit multiplexed

address-data bus when MON/MIC* is tied low. When

in stand-al one mode, this pin is an active-hig h

monitor output indicating a line code violation.

(1)

B/O Part of the bidirectional 8-bit multiplexed

address-data bus when MON/MIC* is tied low. When

in stand-al one mode, this pin is an active-hig h

monitor output ind ic at in g a fram e bi t err or.

(1)

O/I The composite int e rrupt signal gener a ted by the

error counters when MON/MIC* is tied low. When

MON/MIC* is tied high, this pin controls line

loopback transmission in stand-alone mode. CNTINT

is an active-low output; LIN ELB is an active-high

input.

O/I The composite interru pt signa l gene rated by the data

links when MON/MIC* is tied low. When MON/MIC*

is tied high, this pin controls source loopback

transmission in stand- alone mode. DLINT is an

active-low output; SOURCELB is an active-high

input.

TESTI Test In I Used for test functions only. Should be tied to

ground for normal operation.

INIT* Initialization I Active low initialization control. Not all internal

storage elements are affected by t his signal. See

Clock Interfac e and Initialization in th e Overview

section of the Functional Description chapter.

TESTO Test Out O Used for test functions only. Should be left

disconnected for normal operation.

100441E Conexant 1-9

1.0 Product Description CN8330

1.1 Pin Descriptions DS3/E3 Framer with 52 Mbps HDLC Controller

Table 1-2. Hardware Signal Definitions (3 of 5)

Pin Label Signal Name I/O Definition

TCLKO Transmit Clock Out O Used to clock out the TXP OS and TXNEG output s.

Data is clocked out on the rising edge of TCLKO.

TXPOS, TXNEG Transmit Bipolar

Positive, Negative

TDAT [3:0] Transmit Data Bits 3–0 (Bi t 0

is the LSB)

TDAT[4]/LCVERRI Transmit Data Bit 4/Line

Code Violation Error In

TDAT[5]/TXENCI Transmit Data Bit 5/Transmit

Transmitter Section

TDAT[6]/T XDATI Transmit Data Bit 6/Transmit

TDAT[ 7]/TXS YI Transmit Data Bit7/Transmit

Encoder In

Serial Data

M-Sync In

O The positive and negative pulses generat ed by the

B3ZS/HDB3 encode r.

I In parallel mode

of the byte-oriented data that is input to the PPDL

transmitter in response to the transmit byte c lock,

TXBCK.

I In parallel mode, the TDAT[4] is bit 4 of the

byte-oriented data that is input to the PPDL

transmitter. In serial mode, LCVERRI allows test

equipment to insert LCVs into the transmit stream

under microprocessor control, in both DS3 and E3

modes.

I In parallel mode , TDAT[5] is bit 5 of the

byte-oriented data that is input to the PPDL

transmitter. In serial mode, TXENCI is an alternate

direct input to t he B3ZS/HDB3 enc oder.

I In parallel mode , TDAT[6] is bit 6 of the

byte-oriented data that is input to the PPDL

transmitter. In serial mode, TXDATI is applied to the

transmitter.

I In parallel mode, TDAT[7] is the MSB (Bit 7)of the

byte-oriented data that is input to the PPDL

transmitter. In serial mode, TXSYI is applied to the

transmitter.

(2)

, these bits form the lower nibble

TXSYO Transmit M-Sync Out O The transmit M-frame sync output.

TXCKI Transmit Clock In I TXCKI rising edge is used to sample parallel data,

TXBCK/TXGAPCK Transmit Byte Clock/Gapp e d

Clock

SNDMSG Send Message I In parallel mode, SNDMSG initiates message

SNDFCS Send Frame Check Sequence I In parallel mode, SNDFCS initiates transmission of

Transmitter Section

CBITI Tra nsm it C/N-B it Seria l In I The serial C-bit (DS3 m ode ) o r N - bi t (E 3 m ode) d ata

TXCCK Transmit C/N-Bit Clock O Used to sample the CBITI input on the falling edge of

PPDLONLY Payload Parallel Data Only

Select

while the falling edge is used to sample serial dat a.

O In parallel mode, TXBCK clocks the by te-oriented

data that is input to the PPDL transmitter. In serial

mode, TXGAPCK is a transmit clock that is gapped

during overhead bit intervals in either E3 or DS 3

modes.

transmission in the PPDL transmitter.

the 16- or 32-bit frame check sequence on the PPDC

transmitter.

input to be transmitted.

TXCCK.

I Enables the PPDL- only mode in which no DS3/E3

framing is inserted. This mode is entered by tying

this pin high.

1-10 Conexant 100441E

CN8330 1.0 Product Description

DS3/E3 Framer with 52 Mbps HDLC Controller

Table 1-2. Hardware Signal Definitions (4 of 5)

Pin Label Signal Name I/O Definition

DS3CKI DS3 Receive Line Clock In I Clock input DS3CKI should be connected to a 44.736

RXPOS, RXNEG Receive Bipolar

Positive/Negative

RXCKI Receive Dejittered

Clock In

FIFEN FIFO Enable I An active-high input whi ch enables the internal

RXDAT Receive Serial Data O RXDAT is the serial data bit stream clocked out on

RXMSY Receive M-Sync O The M-frame synchronization output recovered from

1.1 Pin Descriptions

MHz source (34.368 MHz for the E3) derived from

incoming receive data.

I The input positive and negative pulses are sampled

on the rising edge of the receiver input clock

(DS3CKI) and should be a full clock period wide.

I Used to read the received data out of the internal

FIFO (required only if FIFO is enabled). If unused, tie

to ground.

FIFO, used to dejitter the received data by using the

dejittered clock input, RXCKI. When FIFEN is low, the

FIFO is bypassed and the serial data is output with

respect to the incoming clock, DS3CKI.

the rising edge of RXCLK.

the incoming serial data stream.

RXCLK Receive Clock O The receive clock used internally to clock out the

serial data stream onto RXDAT.

RXBCK/RXGAPC K Receive Byte/Gapped Clock O When in serial m ode, RXGAPCK provides a gapped

clock signal during every overhead bit (in both DS3

Receiver Section

CBITO Receive C/N-Bit Serial Ou t O The receive serial C-bit (DS3 mode) or N-bit (E3

RXCCK/TXNRZ Receive C/N-Bit Clock

Out/Transmit NRZ

RDAT[0]/LOS Receive Data Byte 0/Loss of

Signal

RDAT[1]/OOF Receive Data Byte 1/

Out of Frame

RDAT[2]/AIS Receive Data Byte 2/Alarm

Indication Signal

and E3 modes). In parallel mode, RXBCK is used to

internally clock out the receive byte-oriented data on

RDAT[7:0].

mode) data. CBITO changes on the rising edge of

RXCCK.

O A clock that indicates transitions in the CBIT0 signal.

In PPDL-only mode, tran smit NRZ data is availa ble

on this pin.

O Part of the 8-bit data bus output from the PPDL

receiver when parallel mode is enabled. When

parallel mode is disabled, this pin is an active-high

monitor output ind ic a t in g los s of si gn al.

O Part of the 8-bit data bus output from the PPDL

receiver when parallel mode is enabled. When

parallel mode is disabled, this pin is an active-high

monitor output indic a ting out-of-frame.

O Part of the 8-bit data bus output from the PPDL

receiver when parallel mode is enabled. When

parallel mode is disabled, this pin is an active-high

monitor output indicating alarm indication signal.

100441E Conexant 1-11

1.0 Product Description CN8330

1.1 Pin Descriptions DS3/E3 Framer with 52 Mbps HDLC Controller

Table 1-2. Hardware Signal Definitions (5 of 5)

Pin Label Signal Name I/O Definition

RDAT[3]/IDLE Receive Data Byte 3/Idle

Code Detection

RDAT[4]/

FRMERR

RDAT[5]/

LCVCAR

Receive Data Byte 4/F r ame

Error Detection

Receive Data Byte 5/Line

Code Violation Carry

RDAT[6]/RXOVH Receive Data Byte 6/Receive

Overhead Detection

RDAT[7]/TXNRZ Receive Data Byte 7/ Trans-

Receiver Section

IDLE/

mit NRZ Out

Idle/Frame Carry O Set if an idle flag is received after a non-idle

FRMCAR

O Part of the 8-bit data bus output from the PPDL

receiver when parallel mode is enabled. When

parallel mode is disabled, this pin is an active-high

monitor output indicating idle code detection.

O Part of the 8-bit data bus output from the PPDL

receiver when parallel mode is enabled. When

parallel mode is disabled, this pin is an active-high

monitor output indicating frame error detection.

O Part of the 8-bit data bus output from the PPDL

receiver when parallel mode is enabled. When

parallel mode is disabled, this pin is an active-high

ripple carry output from the LCV error counter.

O Part of the 8-bit data bus output from the PPDL

receiver when parallel mode is enabled. When

parallel mode is disabled, this pin is an active-low

monitor output indicating the receive overhead bit

positions.

O Part of the 8-bit data bus output from the PPDL

receiver when parallel mode is enabled. When

parallel mode is disabled, this pin is a monitor

output for the transmit NRZ data.

sequence, when parallel mode is enabled. When

parallel mode is disabled, this pin is an active-high

ripple carry output from the frame error counter.

VALFCS/TXOVH Valid FCS Received/Transmit

Overhead

O Active high if a valid FCS was received, when parallel

mode is enabled. Wh en parallel mode is disabled,

this pin is an active-low t r ansmit overhead bit

position indicator.

VCO Voltage-Controlled Os cillator

Output

O Used as the phase control for the clock recovery

circuit that generates the dejittered clock, RXCKI.

Valid only when FIFEN is high. FIFEN enables the

internal FIFO when tied high.

V

DD

Supply Voltage Four pins are provided for power.

GND Ground Five pins are provided for ground.

VCC and GND

NC Not Connected These pins are not connected internally.

Not Connected

NOTE(S):

(1)

Standalone operation is valid only in DS3 mode.

(2)

Parallel mode is enabled by setting the Parallel Data Enable bit [ParaEn;CR04.3] in the Feature Control Register [CR04; 0x04]

when MON/MIC* is low. When MON/MIC* is high, Parallel mode is entered by tying the ALE/PAREN pin high .

1-12 Conexant 100441E

2.0 Functional Description

2.1 Overview

2.1.1 Brief Block Description

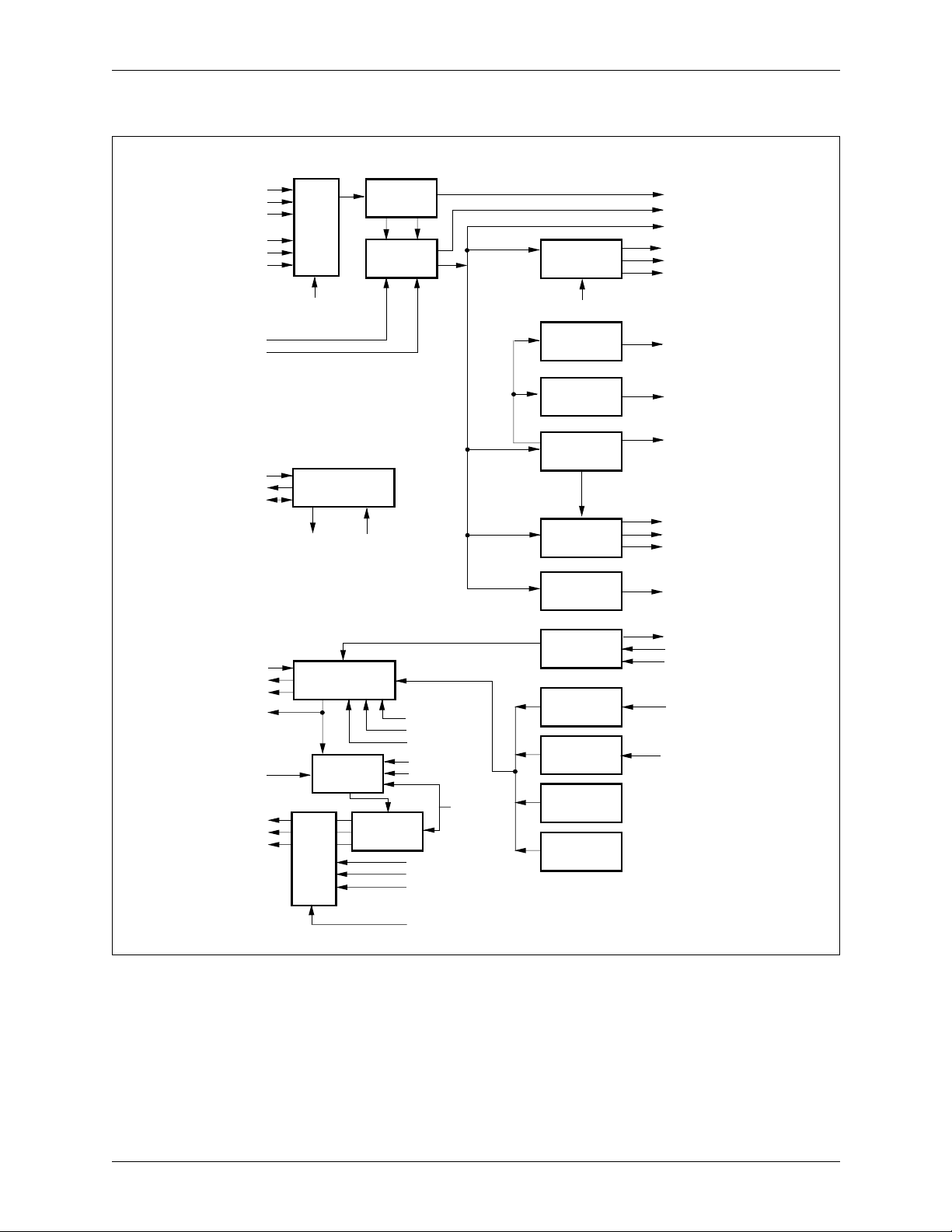

A block diagram of the circuit is illustrated in Figure 2-1. The receive

B3ZS/HDB3 signal is decoded and the bipolar input is converted to a unipolar,

clocked serial data stream. Frame bit conten t is checked and the overhead bit data

links and alarms are extrac ted. The recei v e clock is pro vi ded at the receiv er outp ut

(RXCLK). The data is also connected to a Payload Parallel Data Link (PPDL)

receiver that decodes message blocks using the High-Level Data Link Control

(HDLC) format (Refer to Appendix A in this document for a description of the

HDLC formatter). The recovered data bytes are provided on a parallel output port

with a byte clock. The PPDL receiver can also be programmed to operate in

nibble mode or transparently without HDLC formatting.

A First In First Out (FIFO) memory buffer in the rece ive signal path c an be

enabled to reduce the jitter on t he incomi ng d ata . The receive data is clocked into

the FIFO buffer after bipolar decoding. The FIFO buffer provides a Voltage

Controlled Oscillator (VCO) control signal to an external clock recovery circuit.

A dejittered clock (RXCKI) from the VCO is then used to read the data from the

FIFO buffer to the remainin g receiver circuitry.

The transmitter is capable of sending either serial data from an ext ernal pin, or

byte- or nibble-oriented data from the PPDL data port. DS3 overhead bits or E3

Frame Alignment Signal (FAS) bits are automatically inser ted. Parallel data can

be formatted with idle flags, zero stuf fing for transparency, and a selectable 16- or

32-bit Frame Check Sequ ence (FCS). Bytes or nibbles without HDLC formatting

can also be transmitted. The transmitter is able to send AIS, idle code, yellow

alarm, and all-ones signals. DS3 C-bits (or E3 N-bits) can be optionally inserted

into the data stream from an external source.

LAPD (Link Access Procedure-D) receiver and transmitter circuitry is

provid ed for the terminal data link in DS3 C -bit par ity format and t he E3 mod e. In

C-bit mode, the three C-bits in subframe 5 of the M-frame are used for the

terminal data lin k. In E3 mode, the N-bit is used for the terminal data link.

The microprocessor interface or external outputs monitors all status

indications in the received signal. For both DS3 and E3 modes, indications

include AIS, all-ones, and yellow alarm detection; and Out-of-Frame (OOF) and

frame bit error counting. In addition, loss of signal, idle code, and parity error

detection; line code violation (LCV), path parity, and FEBE event counting; and

parity and X-bit disagreement counting are pro vided for DS3 mode. The recei v ed

DS3 C-bits (or E3 N-bits) are available on an external pin to provide visibility for

external processing, if necessary.

2

100441E Conexant 2-1

2.0 Functional Description CN8330

2.1 Overview DS3/E3 Framer with 52 Mbps HDLC Controller

Figure 2-1. Functional Block Diagram

Receive

RXPOS

RXNEG

DS3CKI

TXPOS

TXNEG

TXCKI

MUX

SOURCELB

Conversion

CLK

Unipolar

FIFO

Buffer

DATA

PPDL

Receiver

Rx Timing

LOS, LCV

VCO

RXDAT, RXCLK

RXBCK

RDAT[7:0]

Status: IDLE

VALFCS

RXCKI

FIFEN

Control

Interrupts

Address/Data

CBITI

TXCCK

TXSYO

TXNRZ Data

FIFO Data

for Line

Loopback

TXPOS

TXNEG

TCLKO

Microprocessor

Interface

Control

Framing and

Overhead Bit

Insertion

MUX

MUX

Status

Encoding

Receive Clock

Bipolar

and Data

Transmit

TXDATI

TXCKI

TXSYI

TXENCI

LINELB

RXPOS

RXNEG

DS3CKI

Test

Equipment

Feature

Select

FEAC

Channel

Terminal

Data Link

Receiver

Frame/

Overhead

Bit Check

Frame

Recovery

Payload

Bit Check

PPDL

Transmitter

FEAC

Channel

Terminal Data

Link

Generator

Payload Bit

Pattern Insert

FEBE

Generation

Receive Byte

Message Buffer

Status: OOF

Frame Error

Parity

Path Parity

FEBE

X Bit

Format

RXMSY

Gapped Clock

CBITO,RXCCK

Status: AIS

IDLE

TXBCK

TDAT[7:0]

SNDMSG, SNDFCS

Transmit Byte

Message Buffer

LINELB

2-2 Conexant 100441E

CN8330 2.0 Functional Description

DS3/E3 Framer with 52 Mbps HDLC Controller

2.1.2 Clock Interface and Initialization

The CN8330 clock input (TXCKI) controls the transmitter. This input should be

supplied with a 44.736 MHz clock in DS3 mode and a 34.368 MHz clock in E3

mode. TDAT[6]/TXDATI is sampled on the falling edge of TXCKI and

TDAT[7]/TXSYI is sampled o n the rising edge of TXCKI. The transmit pulses

TXPOS and TXNEG are clocked out on the rising edge of TCLKO.

DS3CKI is the raw data clock that accomp anies the RXPOS and RXNEG data

pulse inputs for the receiver. If the FIFO buffer is enabled , the data is clocked into

the FIFO buffer after B3ZS/HDB3 decoding. RXCKI is the dejittered version of

DS3CKI and is used to clock the receive data out of the FIFO buffer (if enabled)

to the rest of the receiver circuitry . If the FIFO buffer is disabled, DS3CKI clocks

the data into all of the receiver circuitry and the RXCKI input should be

grounded.

Clock timing requirements are given in the Electrical and Mechanical

Specifications chapter.

2.1.2.1 Initialization The CN8330 can be initialized with an active-low input pulse of at least 200 ns

duration on the INIT* pin. All error counters are initialized to zero when this

input is active low if the transmit and receive clocks are present. Initialization is

not required for proper operation. During initialization (active low) host cannot

read or write any CN8330.

2.1 Overview

2.1.3 Microprocessor Interface

The CN8330 can be controlled by a microprocessor or a microcontroller through

an 8-bit multiplexed address/data interface. An interface to an Intel 8051 family

processor or equivalent, or Motorola 68HC11 family or equivalent is provided.

The microprocessor interface is enabled by tying the MON/MIC* pin low. The

CN8330 is connected to the microprocessor exactly like static RAM.

2.1.3.1 Using with

Specific Microcontrollers

The microprocessor interface i s designed to allow direct connection o f I nt el 8051

family, Motorola 68HC11 family, or equivalent microcontrollers. The controller

interface to the CN8330 consists of 14 pins: Address Latch Enable (ALE), Read

Enable (RD*), Write Enable (WR*), Chip Select (CS ), e ig ht multiplexed

address/data bits (AD[7:0]), and two interrupts (DLINT/SOURCELB and

CNTINT/LINELB). If a 68HC11 controller is used, then its address strobe as is

connected to ALE, Enable is connected to RD*, and Read/Write* (R/W*) is

connected to WR*. The chip select input (CS/ALM0) allows the control of

multiple ICs from a single mi croprocessor. Interrupt outputs are used for data link

and maintenance operations and provide active-low interrupts.

100441E Conexant 2-3

2.0 Functional Description CN8330

2.1 Overview DS3/E3 Framer with 52 Mbps HDLC Controller

2.1.3.2 Microprocessor Interrupts

There are two se parat e i nterrupt pins that can be con nected to the microprocessor

(or microcontroller): Counter and Data Link. The counter interrupt pin

(CNTINT/LINELB) combines seven sources of interrupts on an external pin

connected to the microprocessor. This interr upt signal is active low and is a

composite indication of all interrupt sources that are enabled in the Status

Interrupt Control Register [CR02;0x02]. The interrupt source can be determined

by reading the Counter Interrupt Status Register [SR01;0x11]. The data link

interrupt pin (DLINT/SOURCELB) is a composite indic ation of the interrupts

from four sources. The interrupt source can be determined by reading the Data

Link Interrupt Status Register [SR02;0x12]. When the C-Bit P arit y Mode/ E nable

DLINT bit [CBitP/DL;CR00.0] is not set, the DLINT/SOURCELB pin is held

high (inactive). The two interrupt pins are open-drain outputs and can be

connected to form a single-wire ORed interrupt, if desired.

2.1.3.3 Address Map The register addre ss map f or t he CN83 30 i s g iven in T able 3-1 through Table 3-4,

Register Summary. There are three types of registers: Control Registers, which

can be read or written; St atus Re gist ers and Cou nters w hi ch can on l y be r ead; a nd

Data Link Message Buffers which can be read or written. The Control Registers

serve as latches that are modified by a microprocessor write operation and can

also be read to verify contents. They are located at addresses 0x00–0x05. Statu s

Registers are located at addresses 0x10–0x16. Maintenance Error Counters are

located at addresses 0x20–0x26. The Transmit Terminal Data Link Message

Buffers are located at addresses 0x30–0x37, and the Receive Terminal Data Link

Message Buffers are located at addresses 0x40–0x47. The chip select input

(CS/ALM0) must be high to address the CN8330 and to enable read or write

operations.

2-4 Conexant 100441E

CN8330 2.0 Functional Description

DS3/E3 Framer with 52 Mbps HDLC Controller

2.2 Line Interfaces

2.2.1 Transmitter Line Interface

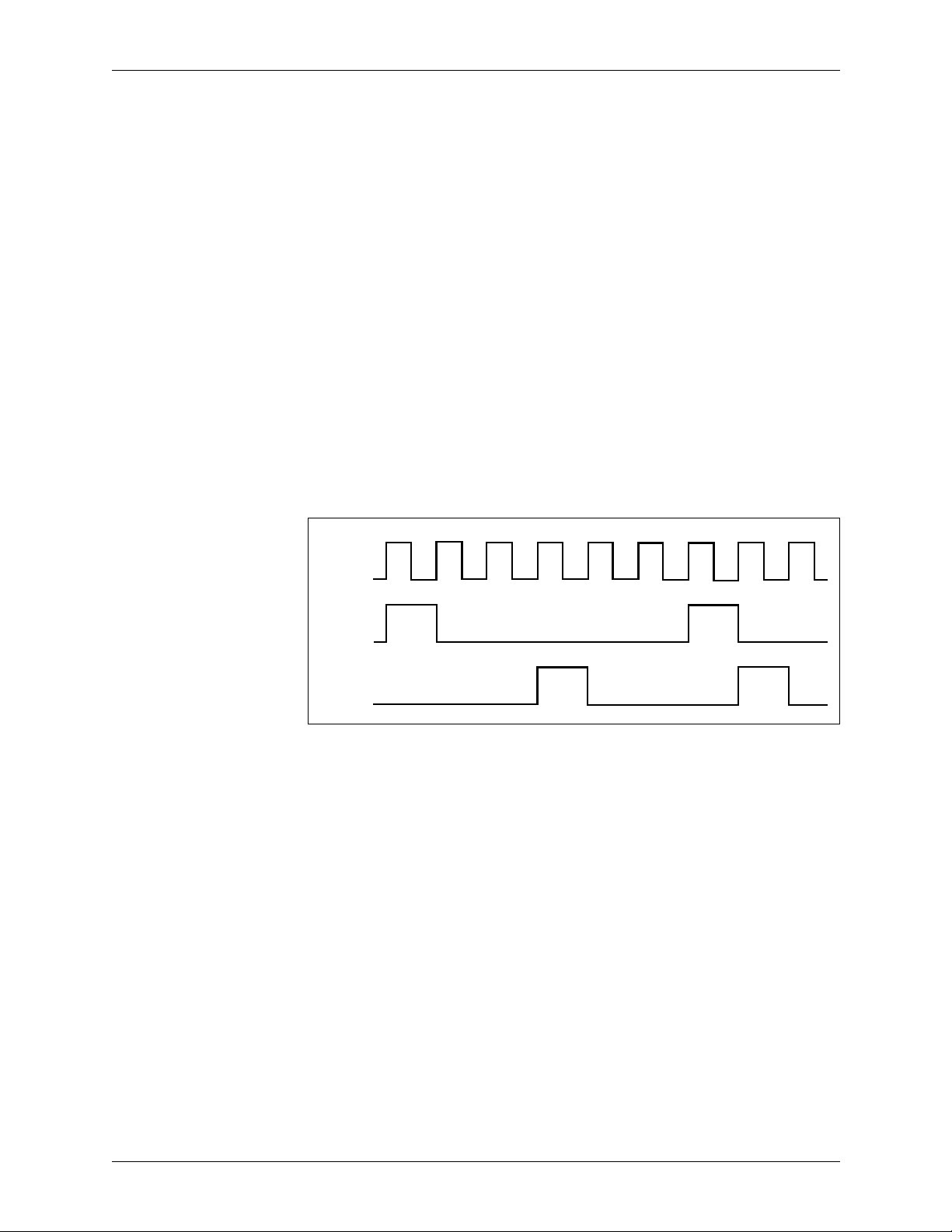

The transmitted line signals are shown in Figure 2-2. Nine bits of a representati ve

output sequence are shown. Separate signal pins provide the appropriate output

signal for positive and negative pulses. The outputs are a full clock period wide

and change on positive clock transitions of the TCLKO pin. For additional

information on the TXPOS and TXNEG output s refer to Transmitter Outputs in

the Transmitter Operation section in this chapter

B3ZS/HDB3 encoding is performed automatically on the output data stream;

however, this encoding can be disabled to send AMI data without any zero code

suppression. Tran smit NRZ data, prior to B3ZS /HDB3 encoding, is also available

on the RDAT[7]/TXNRZ pin when parallel mode is not selected and on the

RXCCK/TXNRZ pin when PPDLONLY mode is selected.

Figure 2-2. Transmitter Line Driver Outputs

2.2 Line Interf aces

TCLKO

TXPOS

TXNEG

100441E Conexant 2-5

2.0 Functional Description CN8330

2.2 Line Interfaces DS3/E3 Framer with 52 Mbps HDLC Controller

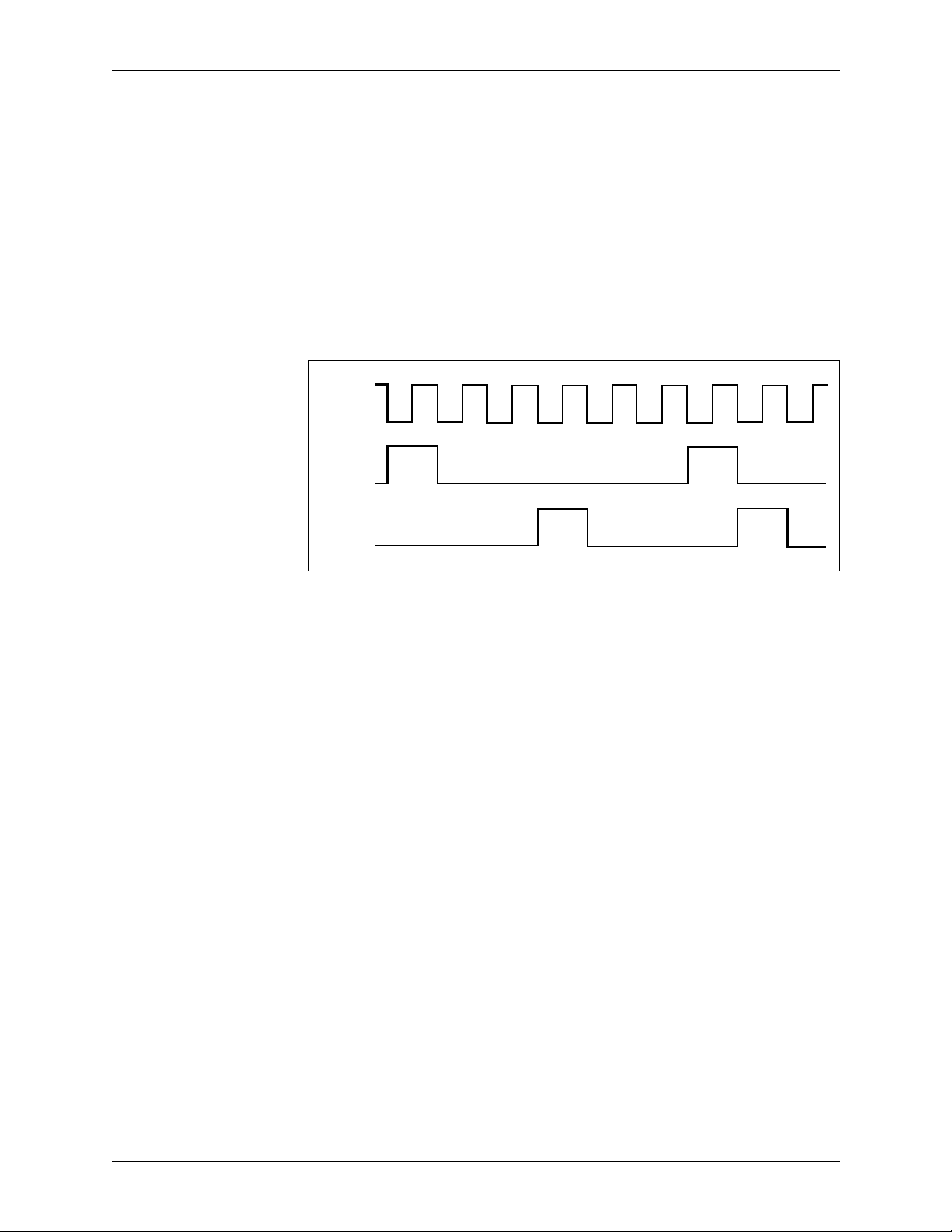

2.2.2 Receiver Line Interface

The line interface for the receive bipo lar signals consists of tw o lo gic-lev el signals

that represent the positive and negative bipolar line pulses (RXPOS, RXNEG)

and an input (DS3CKI) for an externally derived clock at a nominal frequency of

44.736 MHz or 34.368 MHz. The receiver line signals are shown in Figure 2-3.

Nine bits of a representative input sequence are shown. The input signal is

sampled on the rising ed ge of t he cloc k signal. B 3ZS/HDB3 deco ding i s provided

internally. Decoding can be defeated for NRZ input s by connecting the NRZ data

input to both the RXPOS an d RXNEG i nputs or b y sel ecting the AMI mo de/LCV

Type 2 bit [AMI/LCV2;CR04.6] in the Feature Control Register [CR04;0x04].

Figure 2-3. Clocked Receiver Input

DS3CKI

RXPOS

RXNEG

2-6 Conexant 100441E

CN8330 2.0 Functional Description

DS3/E3 Framer with 52 Mbps HDLC Controller

2.3 Transmitter Operation

The transmitter circuit is synchronized to the transmit input data by an external

synchronization signal. The external synchronization signal sets the M-frame

reference for transmitted signals.

2.3.1 Input and Synchronization

The input to the transmitter consists of the transmit serial data input (or the PPDL

transmitter data), transmit clock, and transmit M-frame sync signal. An M-frame

sync signal output is available on the TXSYO pin to synchronize external

circuitry, if desired. If an input sync is not provided, the CN8330 gener ates a sync

internally whose position is indicated by TXSYO. In this case, the sync input

should be grounded. The TDAT[7]/TXSYI is sampled on the rising edge of

TXCKI and TDAT[6]/TXDATI is sampled by the falling edge of TXCKI.

2.3.2 DS3 Mode

2.3 Transmitter Operation

The input bits are synchronized to the M-frame sync signal, which can either be

externally provided or taken from the M-frame sync signal that is internally

generated. Serial input data on TDAT[6]/TXDATI must contain bit positions for

the ove rhead bits, although these are not used unless external insertion is enabled.

The clock frequency is nominally 44.736 MHz and the transmit data input is

sampled on the falling edge of the clock signal. The path delay of the transmitter

from the serial data in put to the positive and negative outputs is six cycles of the

transmit clock. This delay includes B3ZS/HDB3 coding. The delay from the

serial data input to t he NRZ o utput is t w o clock c ycles a nd the co ding delay of the

B3ZS encoder is four clock cycles.

100441E Conexant 2-7

2.0 Functional Description CN8330

2.3 Transmitter Operation DS3/E3 Framer with 52 Mbps HDLC Controller

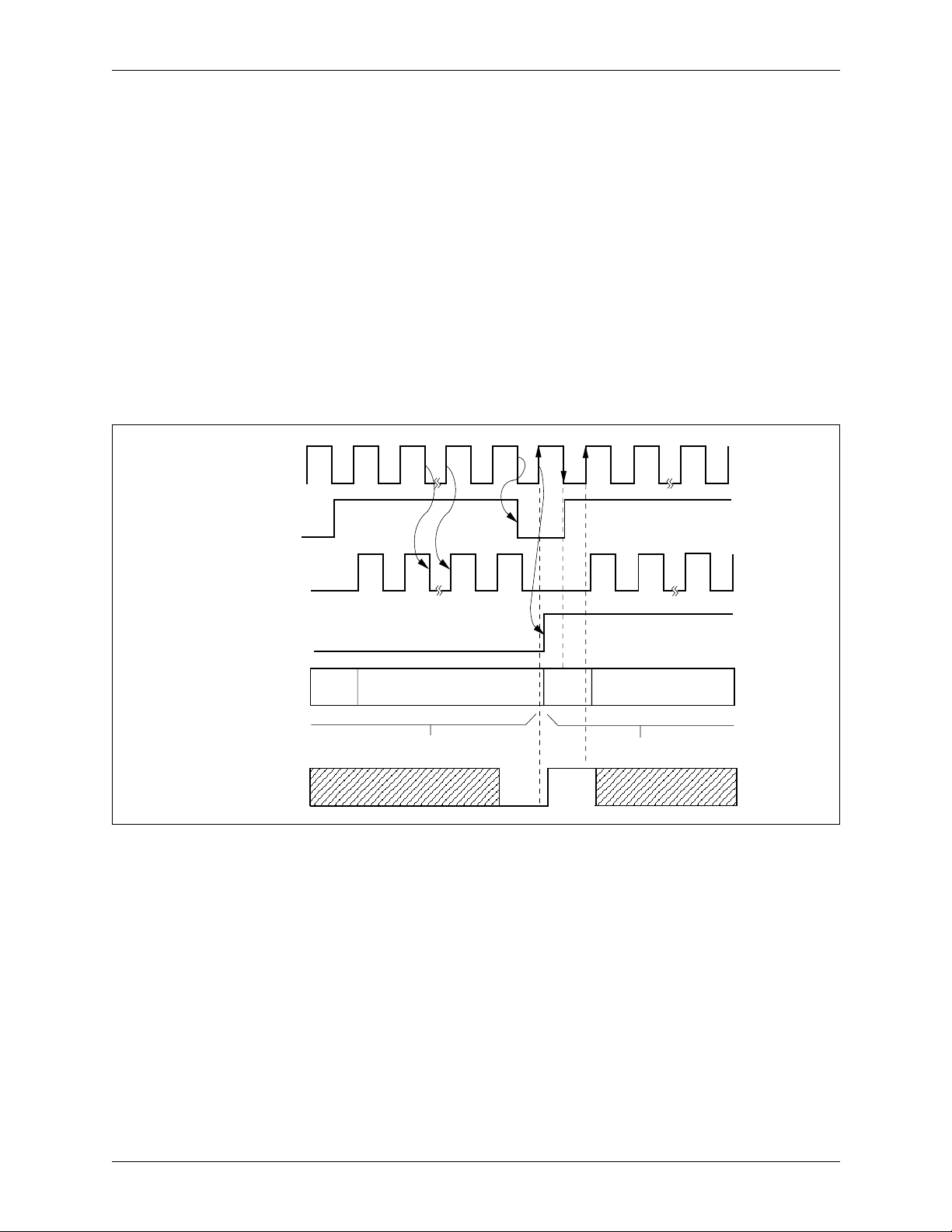

If the TDAT[7]/TXSYI M-frame sync signal is provided, it is sampled on the

rising edge of TXCKI an d should ha ve a l o w-to-h igh tran sition from t he last bit of

the M-frame (bit 680 of subframe 7) to the X1 bit (bit 1 of subframe 1). TXSYO

is clocked out by the rising edge of TXCKI and may be used for synchronization

of external circuitry. Serial data may alternatively be provided in response to the

TXBCK/TXGAPCK pin without the need for pro vidi ng frame synchroni zation or

ov erhea d bit sl ots. The gapped clock output is a gat ed v ersi on of T XCKI with one

pulse gapped for each overhead bit position (one pulse every 85 clock cycles). A

transmit overhead VALFCS/TXOVH bit position indicator pulse is available

when the PPDL is not selected. This pulse is clocked out on the falling edge of

TXCKI and may be of use for providing overhead bits exter nally. A timing

diagram is presented in Figure 2-4 with propagation delays shown as negligible.

Refer to the Electrical and Mechanical Specif ications chapter for actual

propagation delay specifications.

Figure 2-4. Transmitter Timing for Serial DS3 Mode

TXCKI

VALFCS/

TXOVH

TXBCK/

TXGAPCK

TXSYO

TDAT[6]/TXDATI

(Serial In)

TDAT[7]/TXSYI

(Sync In)

Low During Subframe 7

F4

84 Info Bits

Subframe 7

84 Info BitsX1

Subframe 1

Figure 2-5 illustrates the transmitter timing for the parallel DS3 mode. This

mode is enabled by setting the Parallel Da ta Enable bit [ParaEn;CR04.3] in the

Feature Control Register and setting the Disable PPDL Transparency bit

[DisPPDL;CR05.1] in the PPDL Control Register [CR05;0x05]. The SNDMSG

pin should be tied high and the SNDFCS tied low to ensure that flags or FCS

bytes are not transmitted.

2-8 Conexant 100441E

Loading...

Loading...