CONEX BT8954 Datasheet

Bt8954

Voice Pair Gain Framer

The Bt8954 framer has been tailored specifically to meet the needs of voice pair gain

systems (also referred to as “cable relief systems” and “digital subscriber line carriers”)

by providing a direct connection to the DSL modem and the CODEC. It performs data,

clock, and format conversions necessary to construct a Pulse Code Multiplexed (PCM)

channel from a Symmetrical Digital Subscriber Line (SDSL) or a High-Bit-Rate Digital

Subscriber Line (HDSL) channel. The PCM channel consists of transmit and receive

data, clock, and frame sync signals configured for 2–18 voice channels. The PCM

channel connects directly to popular PCM codecs. The Digital Subscriber Line (DSL)

channel interface consists of serial data and clock connected to a RS8973, Bt8970 or a

Bt8960 DSL Transceiver. The Bt8954 supports clear and compressed voice system.

When coupled with a Bt8960, the Bt8954 provides PCM4 functions at greater than 5 km

reach with no voice compression, allowing V.34 modem operation.

At one end, Bt8954 multiplexes payload data from several PCM codecs with the

appropriate overhead and signaling bits into one transport frame that is passed on to the

bit-pump, for transport over a single twisted pair. At the other end, Bt8954

demultiplexes the DSL bit stream into payload data sent to the PCM codec, and

overhead data written into microcomputer-accessible registers.

Embedded Operations Channel (EOC) and signaling overhead can be inserted via the

Microcomputer Interface (MCI). Control and status registers are accessed via the MCI.

One common register group configures the PCM interface formatter, Phase-Locked

Loop (PLL), and PCM Loopback (LB). Another group of DSL channel registers

configures the elastic store FIFOs, overhead muxes, receive framer, payload mapper , and

the DSL loopback. Status registers monitor received overhead, PLL, FIFO, and framer

operations, including CRC and FEBE error counts.

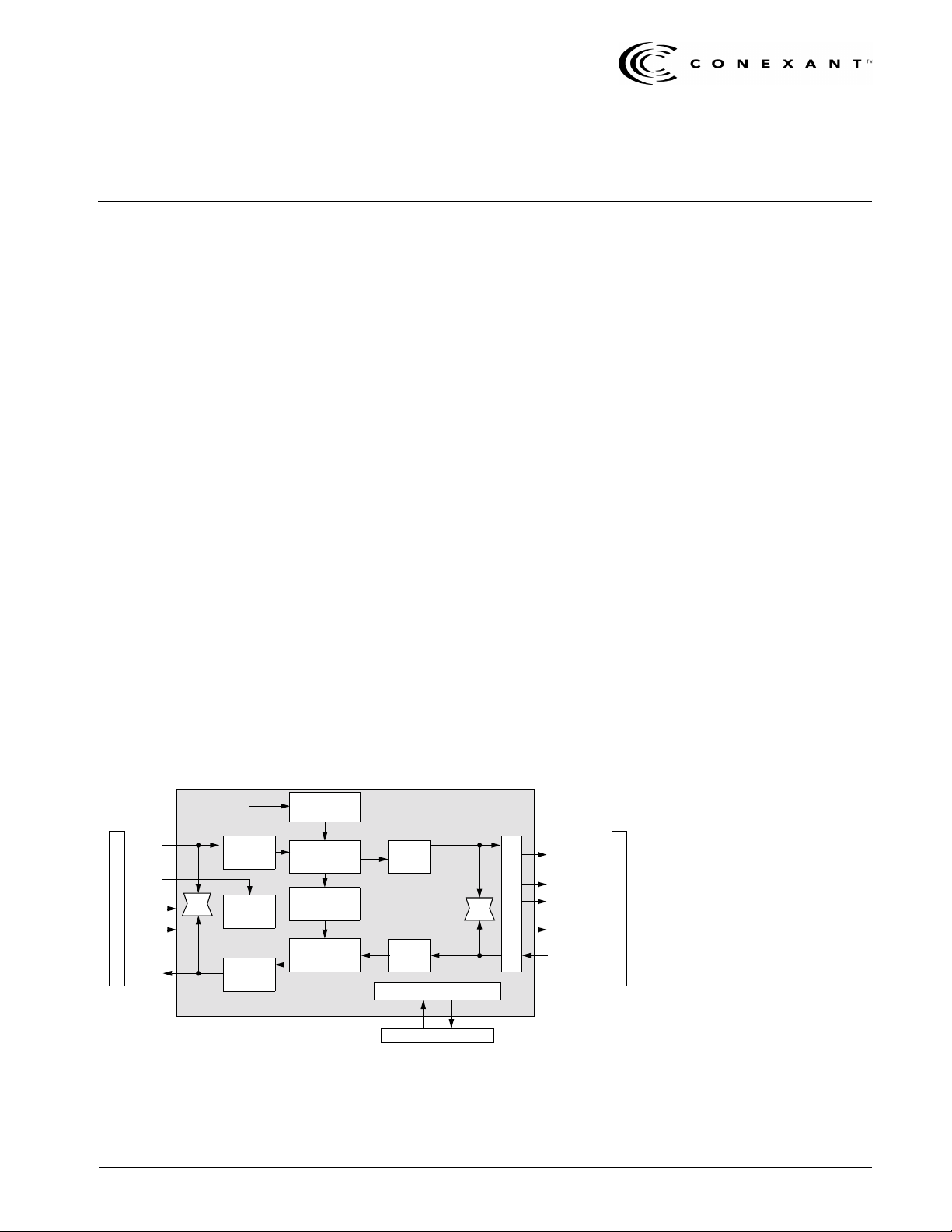

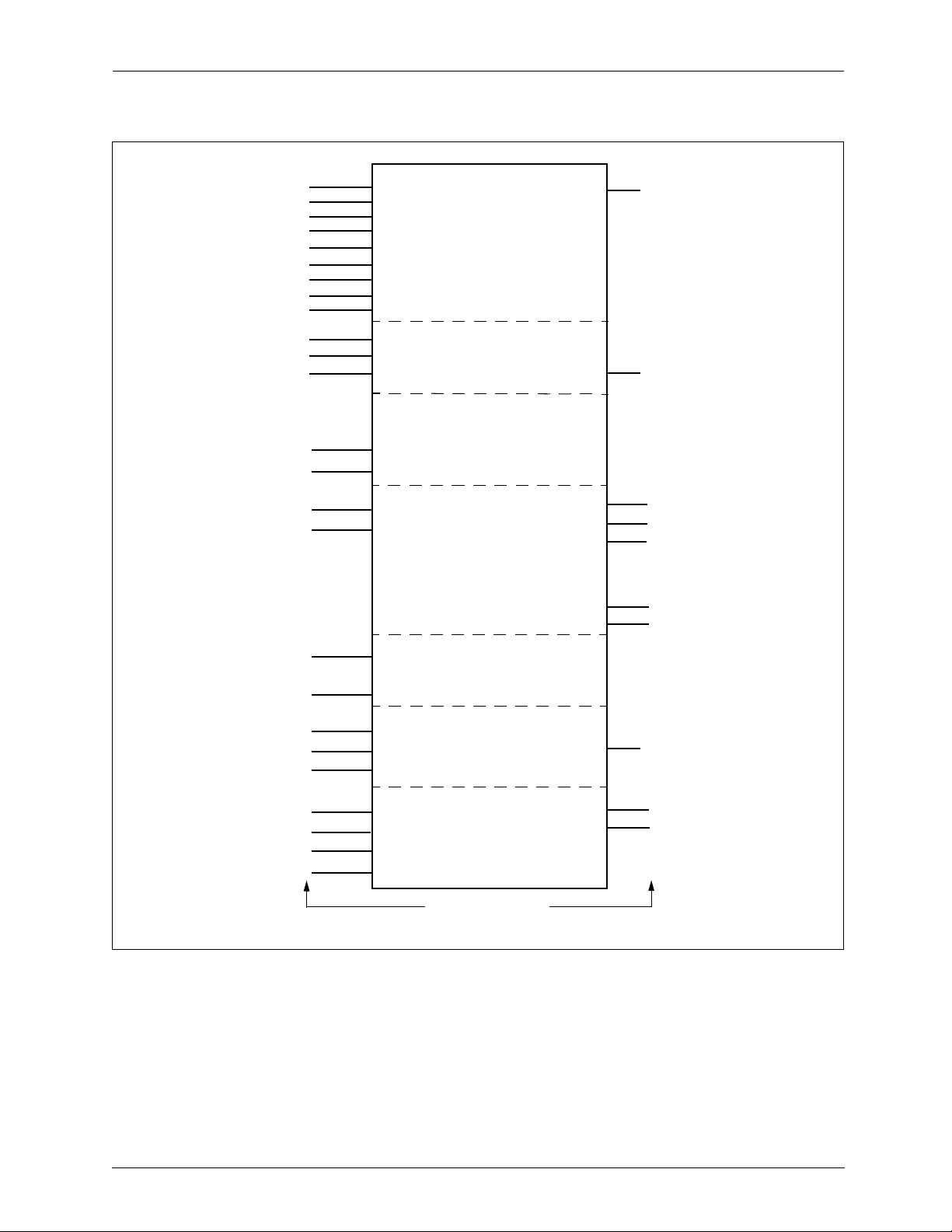

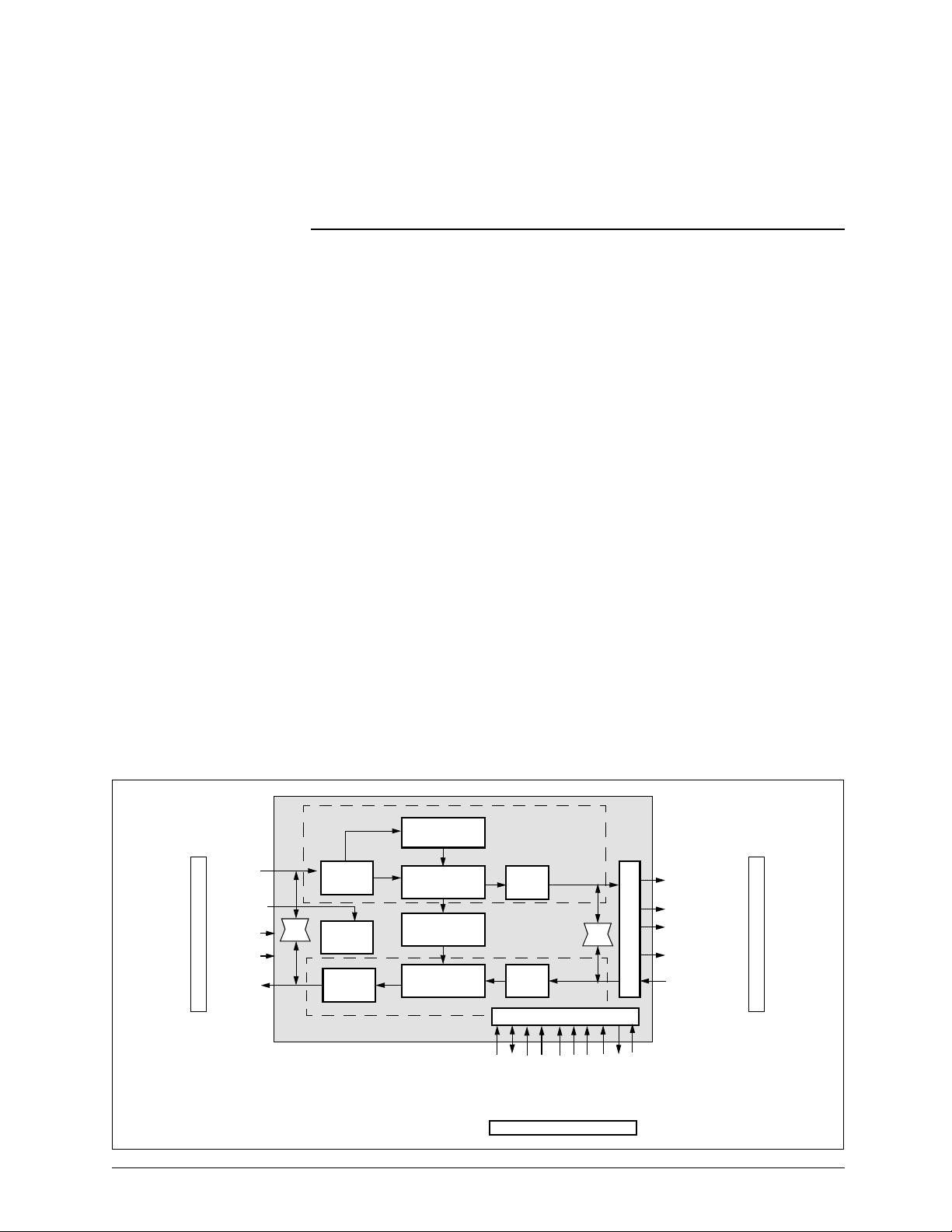

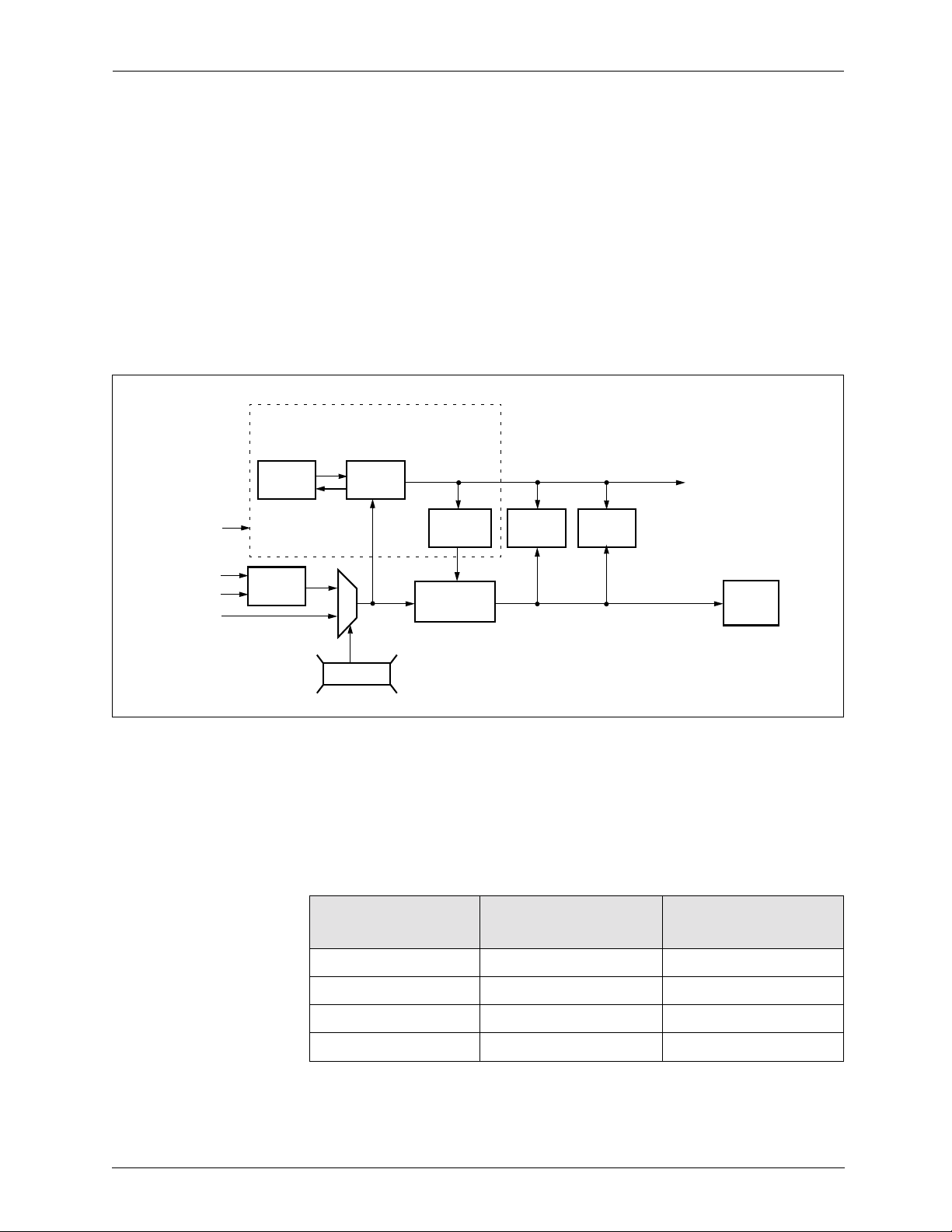

Functional Block Diagram

Receive

Framer

DSL Bit Pump

RDAT

HCLK

BCLK

QCLK

TDAT

LB

2B1Q

Decoder

PLL

2B1Q

Encoder

Payload

Demux

OH/Signaling

Registers

Payload

Mux

PCM

RFIFO

LB

PCM

TFIFO

Microcomputer Interface

PCM Formatter

PCMR

ADPCMCK

PCMCLK

PCMF[18:1]

PCMT

ADPCM/PCM Codecs

Distinguishing Features

• Voice Pair Gain Framer

– Frames and transports PCM data

streams over 12–18,000 ft.

(3.7–5.5 km) distances when

coupled with Bt8960 or Bt8970

• PCM Interface

– Supports popular PCM codecs

– Programmable payload to

support 2–18 64 kbps voice

channels

– 2.048, 1.536 MHz PCM reference

clock generation

– 6.144, 8.192, 20.48 MHz ADPCM

reference clock generation

• DSL Interface

– Connects to Bt8960 or Bt8970

– Supports 160–1168 kbps bit rates

– Error performance monitoring

– Auto tip/ring reversal

• Microcomputer Interface

– Glueless interface to Intel 8051

and Motorola 68302 processors

– Access to overhead and signaling

registers

• Supports ADPCM codecs (32 kbps)

• PCM and DSL loopbacks

• CMOS technology, 5 V operation

• Low-power operation

– Enables compatibility with

line-powered systems

• 68-pin PLCC

• JTAG/IEEE Std 1149.1-1990

• –40 °C to +85 °C operation

Applications

• Voice Pair Gain Systems (Clear)

– PCM2, PCM4(PCM1+3), PCM6,

– PCM8, PCM10/11, PCM12,

PCM18

• ADPCM Voice Pair Gain Systems

(Compressed)

– ADPCM12, ADPCM24, ADPCM36

Microcomputer

Data Sheet N8954DSC

April 7, 1999

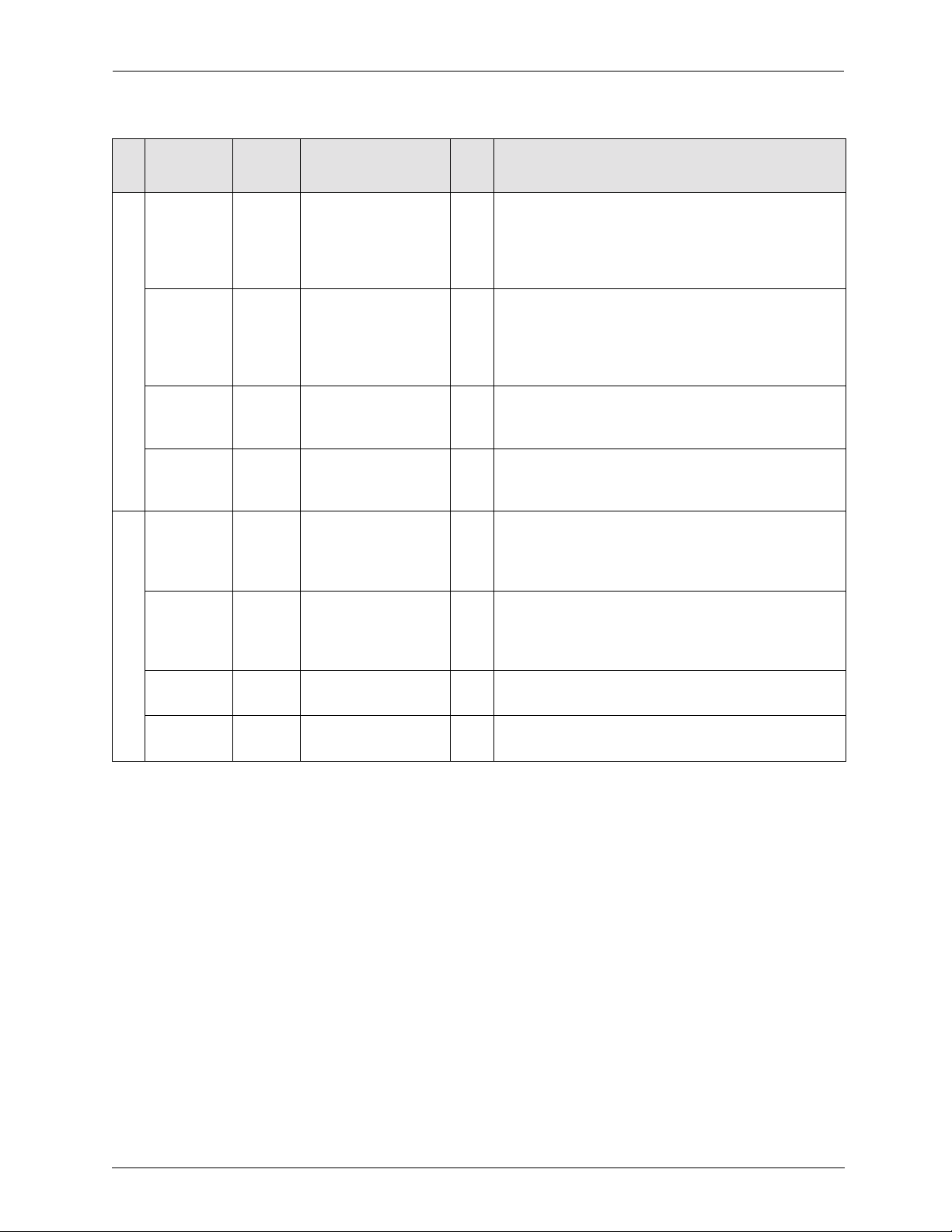

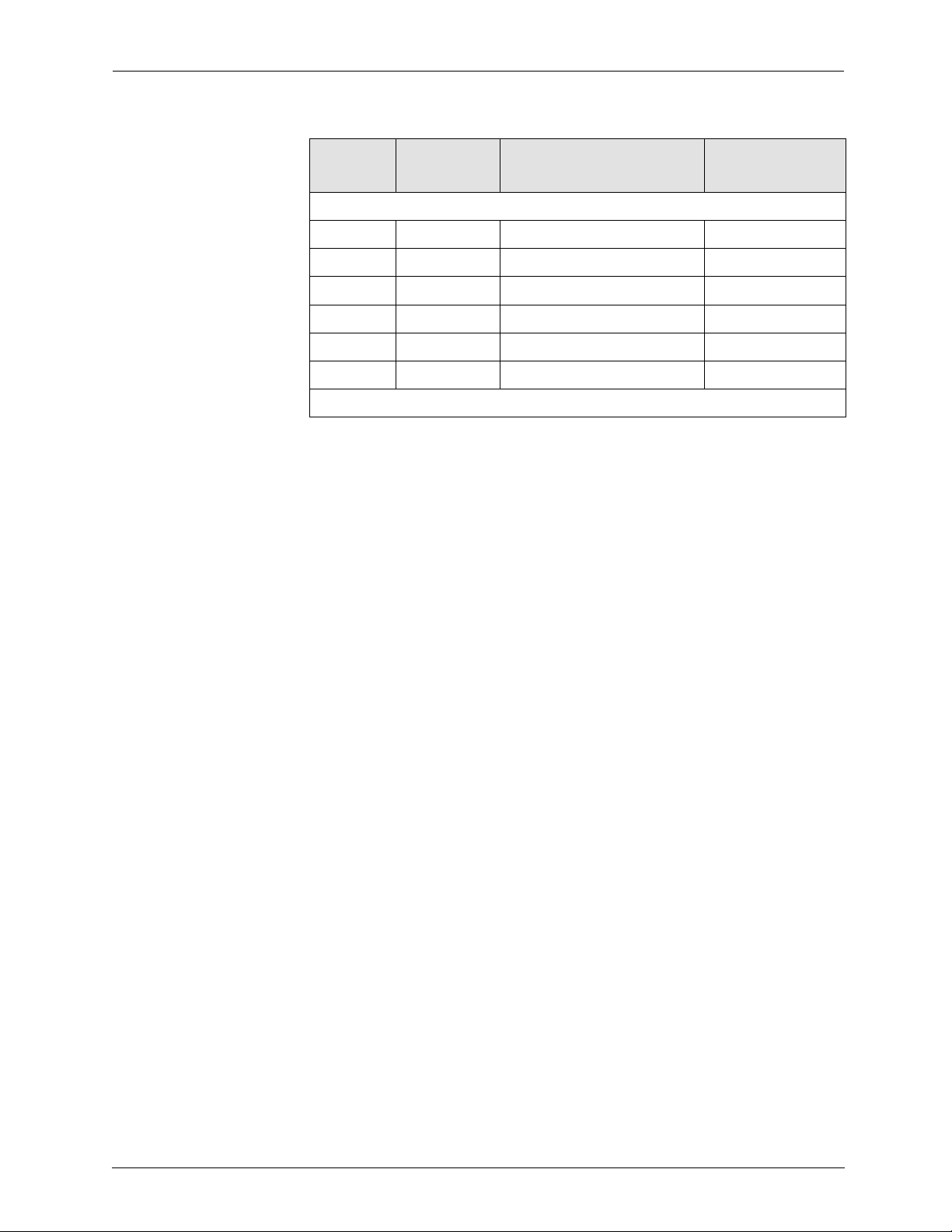

Ordering Information

Model Number Package Ambient Temperature

Bt8954 68-Pin Plastic Leaded Chip Carrier (PLCC) –40 °C to +85 °C

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is

assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent rights of Conexant other than for circuitry embodied in Conexant

products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without

notice.

Conexant and “What’s Next in Communications Technologies” are trademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered

trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc.

Printed in U.S.A.

All Rights Reserved

Reader Response:

To improve the quality of our publications, we welcome your f eedbac k. Please send comments or

suggestions via e-mail to Conexant Reader Response@conexant.com. Sorry, we can't answer your technical

questions at this address. Please contact your local Conexant sales office or local field applications engineer if you

have technical questions.

N8954DSC

Conexant

Table of Contents

Table of Contents

List of Figures

List of Tables

1.0 DSL Systems

1.1 Voice Pair Gain Applications

1.1.1 Repeaters

1.1.2 Subscriber Modem

1.2 System Interfaces

2.0 Pin Descriptions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . iii

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

3.0 Circuit Descriptions

3.1 Overview

3.2 DSL Frame Format

3.2.1 Detailed Frame Structure

3.2.2 Differences Between the DSL and HDSL T1/E1 Frame Formats

3.2.3 Overhead Bit Allocation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.2.2.1 EXTRA_Z_BIT Option

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

. . . . . . . . . . . . . . . . . . . . . 3-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.3 Receiver

3.4 Transmitter

N8954DSC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.3.1 2B1Q Decoder

3.3.2 Receive Framer

3.3.3 CRC Check

3.3.4 Descrambler

3.3.5 Payload Demux

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.4.1 OH/Signaling Registers

3.4.2 Transmit Signaling FIFOs

3.4.3 Payload Mux

3.4.4 CRC Calculation

3.4.5 Scrambler

3.4.6 2B1Q Encoder

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Conexant

iii

Table of Contents

Bt8954

3.5 PCM Formatter

3.6 Loopbacks

3.7 Synchronization

3.7.1 COTF Transmitter Synchronization

3.7.2 RTF Receiver Synchronization

3.7.3 RTF Transmitter Synchronization

3.7.4 COTF Receiver Synchronization

3.7.5 Round Trip Delay

3.8 Microcomputer Interface

3.8.1 Microcomputer Read/Write

3.8.2 Interrupt Request

3.8.3 Reset

3.9 PLL

4.0 Registers

4.1 Register Types

Voice Pair Gain Framer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

3.8.1.1 Multiplexed Address/Data Bus

3.8.1.2 Separated Address/Data Bus

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2 Register Groups

4.3 Address Map

4.4 Transmitter Registers

0x80, 0x81—Transmit Embedded Operations Channel (TEOC_LO, TEOC_HI)

0x82, 0x83—Transmit Indicator Bits (TIND_LO, TIND_HI)

0x84—Transmit Signaling FIFOs (TSFIFO_I, TSFIFO_O)

0x85—Transmit FIFO Water Level (TFIFO_WL)

0x86—Transmit Command Register 1 (TCMD_1)

0x87—Transmit Command Register 2 (TCMD_2)

4.5 Receiver Registers

0x90—Receive Command Register 1 (RCMD_1)

0x91—Receive Command Register 2 (RCMD_2)

4.6 DSL Channel Configuration

0xA0—DSL Frame Length (DFRAME_LEN)

0xA1—Sync Word (SYNC_WORD)

0xA2, 0xA3—Rx FIFO Water Level (RFIFO_WL_LO, RFIFO_WL_HI)

4.7 PLL Configuration

0xB0—PLL_INT Register (PLL_INT)

0xB1—PLL_FRAC_HI Register (PLL_FRAC_HI)

0xB2—PLL_FRAC_LO Register (PLL_FRAC_LO)

0xB3—PLL_A Register (PLL_A)

0xB4—PLL_B Register (PLL_B)

0xB5—PLL_SCALE Register (PLL_SCALE)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

. . . . . . . . . . 4-4

. . . . . . . . . . . . . . . . . . . . . . . . 4-4

. . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

. . . . . . . . . . . . . . . . 4-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

iv

Conexant

N8954DSC

Bt8954

Table of Contents

Voice Pair Gain Framer

4.8 Common

4.9 Interrupt

4.10 Reset

4.11 Receive/Transmit Status

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

0xC0—Command Register 1 (CMD_1)

0xC1—Revision Identification (REV_ID)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

0xD0—Interrupt Status Register (ISR)

0xD1—Interrupt Mask Register (IMR)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

0xD3—Scrambler Reset (SCR_RST)

0xD4—Transmit FIFO Reset (TFIFO_RST)

0xD5—Reset Pointer to Transmit Signaling FIFOs (TSFIFO_PTR_RST)

0xD6—Reset Pointer to Receive Signaling FIFOs (RSFIFO_PTR_RST)

0xD7—Receive Elastic Store FIFO Reset (RFIFO_RST)

0xD8—Receive Framer Synchronization Reset (SYNC_RST)

0xD9—Error Count Reset (ERR_RST)

0xDA—Reset Receiver (RX_RST)

0xDB—Update TSFIFO_O (UPDATE_TSFIFO_O)

0xDC—Update RSFIFO_O (UPDATE_RSFIFO_O)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

. . . . . . . . . . . . . . 4-20

. . . . . . . . . . . . . . 4-20

. . . . . . . . . . . . . . . . . . . . . . . . . 4-21

. . . . . . . . . . . . . . . . . . . . . 4-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-22

0xE0, 0xE1—Receive Embedded Operations Channel (REOC_LO, REOC_HI)

0xE2, 0xE3—Receive Indicator Bits (RIND_LO, RIND_HI)

0xE4—Receive Signaling FIFOs (RSFIFOs)

0xE5—Receive Status 1 (RSTATUS_1)

0xE6—Receive Status 2 (RSTATUS_2)

0xE7—Transmit Status 1 (TSTATUS_1)

0xE8—CRC Error Count (CRC_CNT)

0xE9—Far End Block Error Count (FEBE_CNT)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-27

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

. . . . . . . . . . . . . . . . . . . . . . . 4-22

. . . . . . . . . 4-22

4.12 PCM Formatter

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

0xF0—PCM Frame Length (PFRAME_LEN)

0xF1—PCM Format (PCM_FORMAT1)

5.0 Electrical and Mechanical Specifications

5.1 Electrical Specifications

5.1.1 Absolute Maximum Ratings

5.1.2 Recommended Operating Conditions

5.1.3 Electrical Characteristics

5.1.4 DSL Interface Timing

5.1.5 PCM Interface Timing

5.1.6 Microcomputer Interface Timing

5.1.7 Test and Diagnostic Interface Timing

5.2 Mechanical Specifications

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

N8954DSC

Conexant

v

Table of Contents

Bt8954

Appendix A: Applications

A.1 Interfacing to the Bt8960/Bt8970 HDSL Transceiver

A.2 Interfacing to the Texas Instrument TP3054A PCM Codec

A.3 Interfacing to the Motorola 68302 16-Bit Processor

A.4 Interfacing to the Intel 8051 8-Bit

A.5 References

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

Voice Pair Gain Framer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

vi

Conexant

N8954DSC

Bt8954

List of Figures

Voice Pair Gain Framer

List of Figures

Figure 1-1. Block Diagram of a PCM4 Voice Pair Gain Modem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Figure 1-2. Repeater Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

Figure 1-3. Subscriber Modem (Terminal) System Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Figure 1-4. Bt8954 System Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Figure 2-1. Pin Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Figure 2-2. Bt8954 Functional Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 3-1. Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Figure 3-2. Basic DSL Frame Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

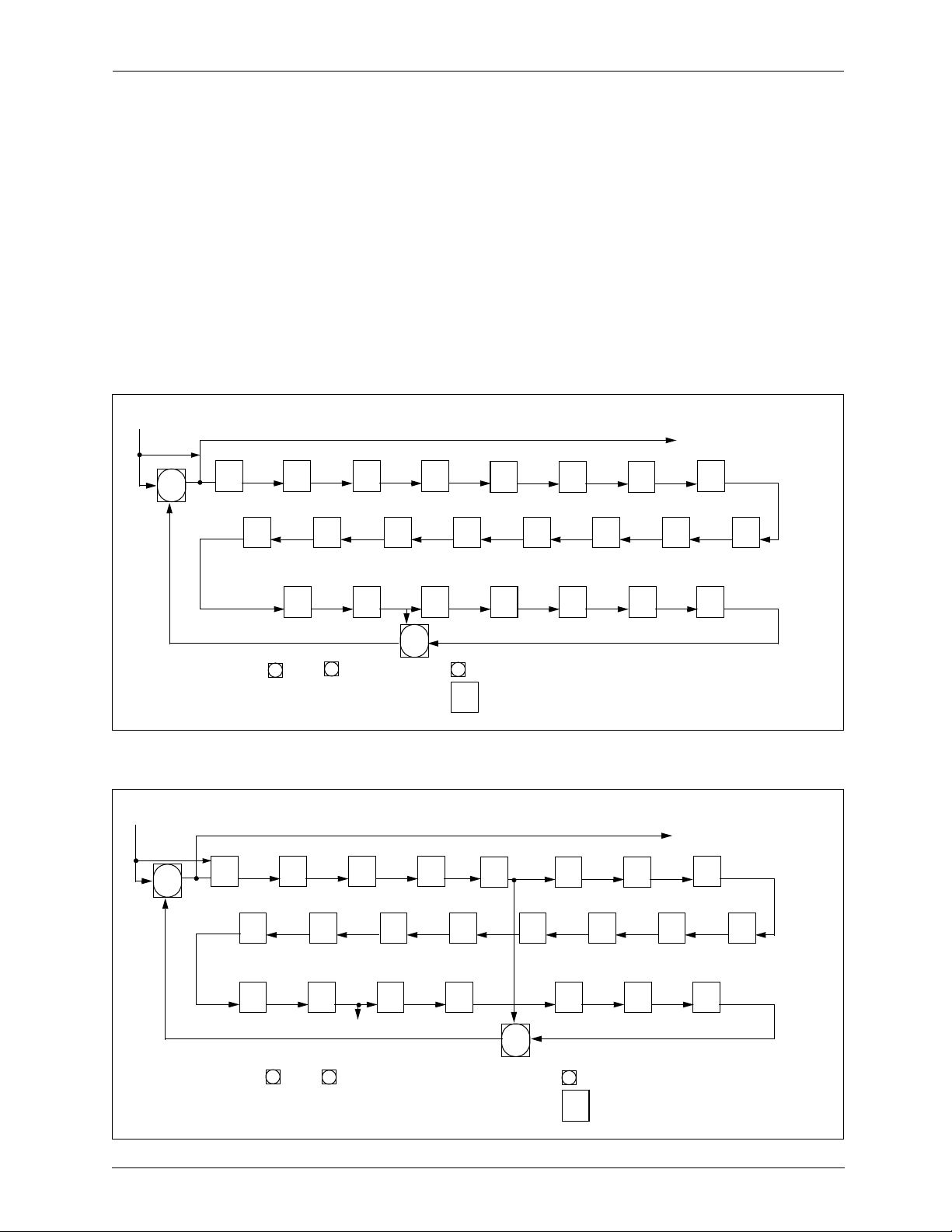

Figure 3-3. Receiver Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

Figure 3-4. Receive Framer Finite State Machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6

Figure 3-5. Threshold Correlation Effect on Expected SYNC Locations . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Figure 3-6. LFSR Structure for Transmission in the Remote → Central Office Direction. . . . . . . . . . . . 3-8

Figure 3-7. LFSR Structure for Transmission in the Central Office → Remote Direction. . . . . . . . . . . . 3-8

Figure 3-8. Transmitter Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Figure 3-9. Double Buffering, Using Transmit S-Bits Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

Figure 3-10. LFSR Structure for Transmission in the Remote → Central Office Direction. . . . . . . . . . . 3-12

Figure 3-11. LFSR Structure for Transmission in the Central Office → Remote Direction. . . . . . . . . . . 3-13

Figure 3-12. PCM Formatter Detail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Figure 3-13. PCMF [18:1] Waveforms for Encoded and Decoded Frame SYNC Modes. . . . . . . . . . . . . 3-15

Figure 3-14. PCM and DSL Loopbacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

Figure 3-15. COTF and RTF Synchronization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-17

Figure 3-16. COTF Transmitter Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-17

Figure 3-17. RTF Receiver Synchronization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

Figure 3-18. RTF Transmitter Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-18

Figure 3-19. COTF Receiver Synchronization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

Figure 3-20. MCI Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20

Figure 3-21. Functional Diagram of the Read and Write Controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

Figure 3-22. Interrupt Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

Figure 3-23. Functional Diagram of the PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

Figure 4-1. Transmit Signaling FIFOs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Figure 4-2. Example of Three Signaling Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Figure 4-3. Receive Signaling FIFOs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-23

Figure 4-4. Example of Three Signaling Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

N8954DSC

Conexant

vii

List of Figures

Bt8954

Figure 5-1. QCLK Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Figure 5-2. DSL Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Figure 5-3. PCM Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Figure 5-4. MCI Write Timing, Intel Mode (MOTEL = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Figure 5-5. MCI Write Timing, Motorola Mode (MOTEL = 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Figure 5-6. MCI Read Timing, Intel Mode (MOTEL = 0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

Figure 5-7. MCI Read Timing, Motorola Mode (MOTEL = 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

Figure 5-8. Internal Write Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

Figure 5-9. JTAG Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

Figure 5-10. Input Waveforms for Timing Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-10

Figure 5-11. Output Waveforms for Timing Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

Figure 5-12. Output Waveforms for Three-State Enable and Disable Tests . . . . . . . . . . . . . . . . . . . . . . 5-10

Figure 5-13. 68-Pin PLCC Package Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-11

Figure A-1. Bt8954 to Bt8960/Bt8970 DSL Transceiver Interconnection. . . . . . . . . . . . . . . . . . . . . . . . A-1

Figure A-2. Bt8954 to Texas Instrument TP3054A PCM Codec Interconnection . . . . . . . . . . . . . . . . . . A-2

Figure A-3. Bt8954 to Motorola 68302 Processor Interconnection . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

Figure A-4. Bt8954 to Intel 8051 Controller Interconnection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

Voice Pair Gain Framer

viii

Conexant

N8954DSC

Bt8954

List of Tables

Voice Pair Gain Framer

List of Tables

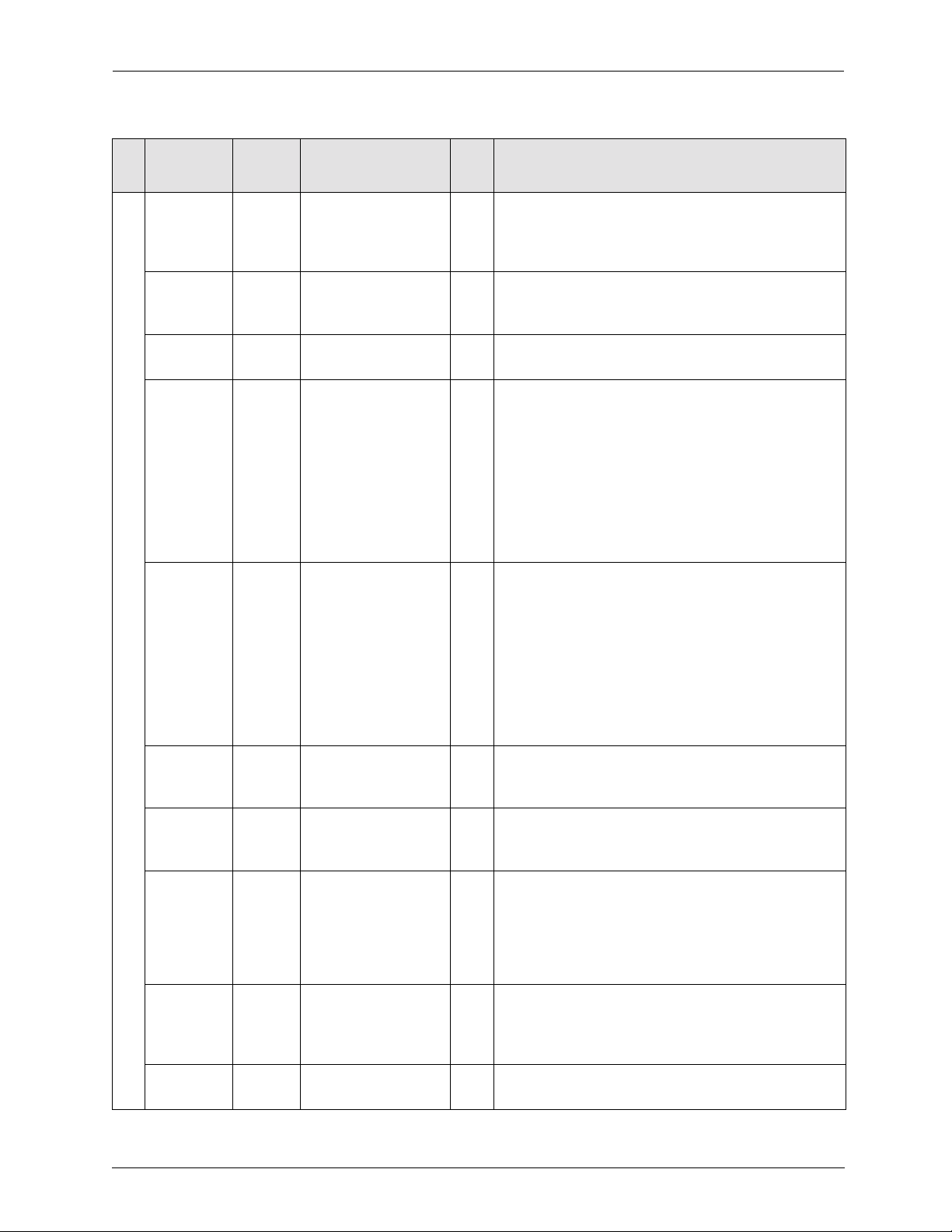

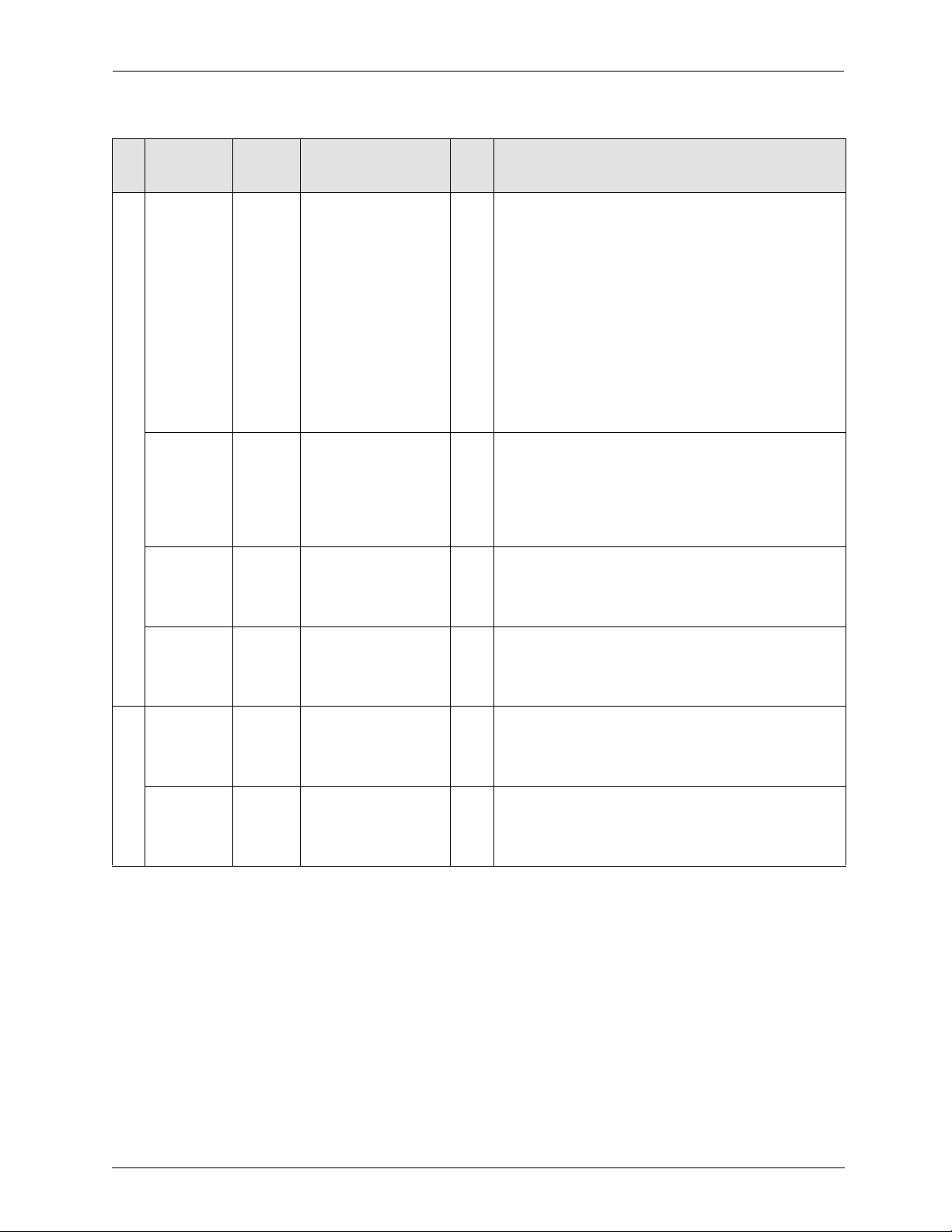

Table 2-1. Hardware Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Table 3-1. DSL Frame Structure and Overhead Bit Allocation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

Table 3-2. 2B1Q Decoder Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

Table 3-3. 2B1Q Encoder Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

Table 3-4. PCM and DSL Loopbacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-16

Table 3-5. PLL_X Register Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

Table 3-6. PLL_C Register Bit Representation of PLL_W and PLL_Y . . . . . . . . . . . . . . . . . . . . . . . . 3-26

Table 3-7. PLL_P Register Bit Representation of P_FACTOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

Table 3-8. Factors for fPLL = 196.608 MHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-27

Table 3-9. Factors for fPLL = 204.800 MHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-28

Table 4-1. Address Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Table 4-2. Transmitter Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Table 4-3. DSL Receive Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Table 4-4. DSL Channel Configuration Write Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

Table 4-5. PLL Configuration Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-14

Table 4-6. Common Command Write Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

Table 4-7. Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

Table 4-8. Reset Write Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

Table 4-9. Receive and Transmit Status Read Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-22

Table 4-10. PCM Formatter Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

Table 5-1. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Table 5-2. Recommended Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Table 5-3. Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Table 5-4. QCLK Timing Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Table 5-5. DSL Interface Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-3

Table 5-6. PCM Interface Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Table 5-7. Microcomputer Interface Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

Table 5-8. Microcomputer Interface Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

Table 5-9. Test and Diagnostic Interface Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

Table 5-10. Test and Diagnostic Interface Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

N8954DSC

Conexant

ix

List of Tables

Bt8954

Voice Pair Gain Framer

x

Conexant

N8954DSC

1

1.0 DSL Systems

1.1 Voice Pair Gain Applications

A well-established market exists for voice pair gain systems. In such systems,

several simultaneous phone conversations are transported over a single twisted

pair. These systems are used by telecommunications service providers to

maximize the utilization of the existing copper plant and allow it to provision

many more telephone circuits than is possible with ordinary 4 kHz analog

transport. The external interfaces of voice pair gain systems, at both the Central

Office and remote ends, are analog POTS lines. Two carrier techniques facilitate

single pair gain transmission: Frequency Domain Multiplexed Systems (FDM)

and Time Domain Multiplexed Systems (TDM). In FDM systems each voice

channel is modulated by a successively higher carrier such that the composite

transmission consists of several frequency bands. In TDM systems the voice data

is digitized and sampled in a channel-multiplexed fashion. Although FDM

systems are currently fielded, recent trends are clearly toward TDM systems

because of the inherent advantages associated with digital transmission.

N8954DSC

Traditional PCM4 (also called “1+3”) voice pair gain systems use a

combination of 2:1 Adaptive Differential Pulse Code Modulation (ADPCM)

compression and basic rate Integrated Service Digital Network (ISDN)

U-interface devices to transport four-voice conversations on one twisted pair . The

disadvantage of this scheme is that clear 64 kbps channel capacity is lost due to

the ADPCM voice compression algorithm. This may prevent high-speed

facsimile and data transmissions from being transported reliably. Since

telecommunication service providers want to provision telephone equipment that

can be used for business purposes, this disadvantage has caused them to seek

alternative solutions that can handle data as well as voice. When used with a

Digital Subscriber Line (DSL) bit pump, such as the Bt8960, PCM4 systems can

be constructed to transmit clear 64 kbps channels, thereby enabling voice, fax,

and data transmission.

The Bt8954 with a higher speed DSL bit pump, such as the Bt8970, allows a

greater number of voice conversations to be simultaneously carried over a single

twisted pair. The Bt8954/Bt8970 comb ination can facilitate up to 18 64-kbps time

slots. If clear channel capability is needed, this combination results

18 (PCM18) systems. When used with 2:1 ADPCM voice compression,

the Bt8954/Bt8970 combination makes up to 36 voice channels possible.

Conexant

in up to

1-1

1.0 DSL Systems

Bt8954

1.1 Voice Pair Gain Applications

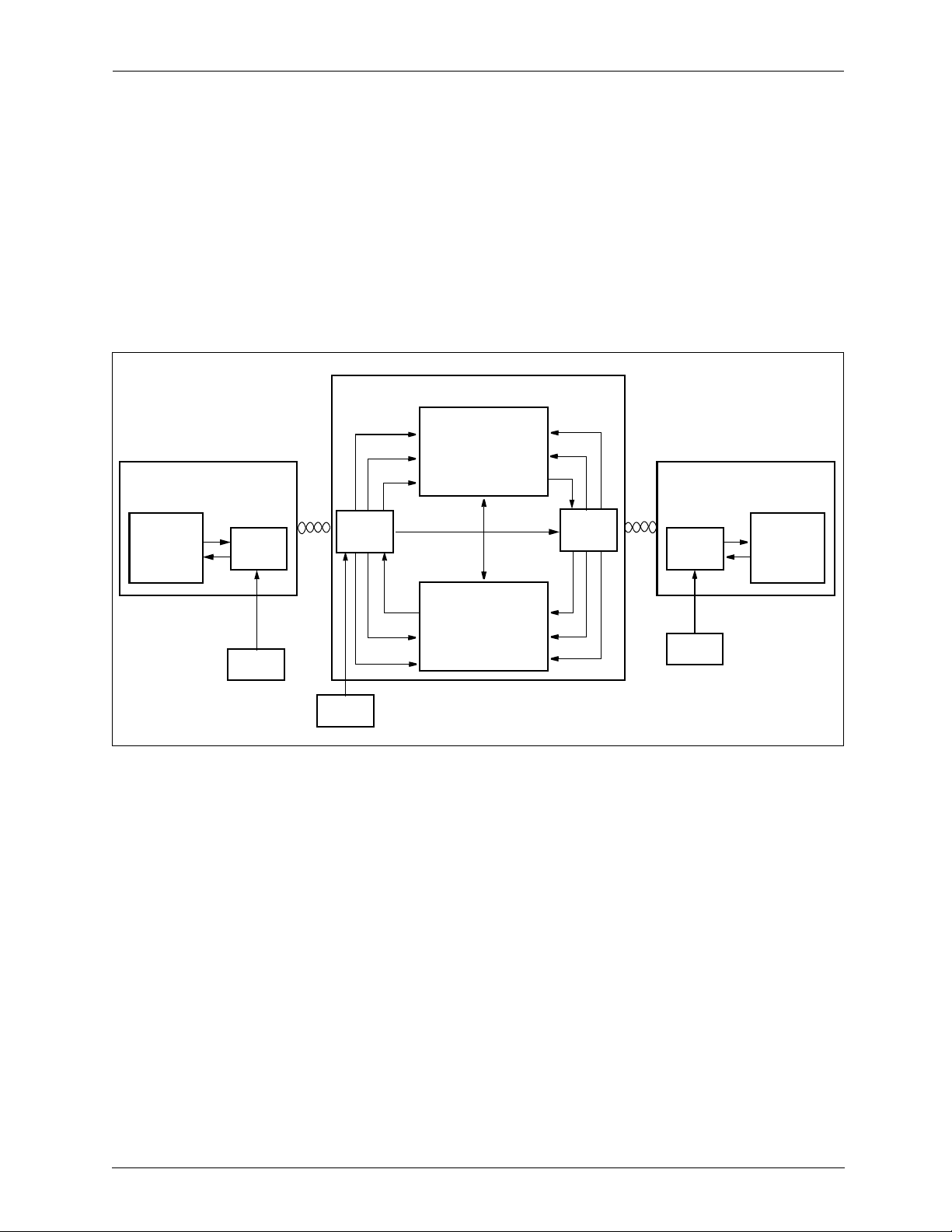

Bt8954’s position among the key elements of a PCM4 (4-channel) voice pair

gain modem is illustrated in Figure 1-1. The Pulse Code Multiplexed (PCM)

codec and Subscriber Line Interface Circuit (SLIC) chips for each channel

perform the transmit encoding (A/D conversion) and receive decoding (D/A

conversion) of voice signals. The time-division multiplexing of the voice signals

on the PCMT and PCMR serial buses is as follows: Bt8954 informs PCM

Codec_n with the PCMFn frame sync when to expect the next byte from Bt8954

on the PCMR bus, and when to put its next byte on the PCMT bus. In this way,

Bt8954 uses the PCMFn frame sync to designate the time slot that Codec_n has

access to the PCMR and PCMT buses.

Figure 1-1. Block Diagram of a PCM4 Voice Pair Gain Modem

QCLK

BCLK

RDAT

TDAT

Bt8954

VPG Framer

Hybrid

Bt8960/70

Bit Pump

PCMCLK

PCMR

PCMT

CODEC1

FSX1/FSR1

PCMF1

Voice Pair Gain Framer

SLIC1

C1 C2 DET* E0

.

Microcomputer

1.1.1 Repeaters

CODEC4

FSX4/FSR4

PCMF4

Logic

SLIC4

C1 C2 DET* E0

Figure 1-2 illustrates a pair of Bt8954 repeaters placed in line between Central

Office and remote terminals to extend the transmission distance. For each Bt8954

repeater, the BCLK/QCLK is connected to the BCLK/QCLK of its source

transceiver while the BCLK_REP/QCLK_REP is connected to the BCLK/QCLK

of its destination transceiver. The Central Office Bt8954 gets its

HCLK/BCLK/QCLK from the Central Office transceiver, which generates them

from a free-running crystal. The repeater transceiver connected to the Central

Office recovers its HCLK, BCLK, and QCLK from the HDSL line. These signals

then drive the HCLK, BCLK, and QCLK pins of the Central Of fice to Remote

Terminal Bt8954, and the HCLK, BCLK_REP, and QCLK_REP pins of the

Remote Terminal to Central Office Bt8954. The repeater transceiver connected to

the Remote Terminal receives HCLK from the repeater transceiver connected to

the Central Office. The repeater transceiver connected to the Remote Terminal

generates BCLK/QCLK and drives the BCLK/QCLK pins of the Remote

Terminal to Central Office Terminal Bt8954. The repeater transceiver drives the

BCLK_REP/QCLK_REP pins of the Central Office Terminal to Remote

Terminal Bt8954.

1-2

In Repeater Mode, the Bt8954 does not use the FIFOs. First, data received

from the bit pump is descrambled.

Conexant

N8954DSC

Bt8954

1.0 DSL Systems

Voice Pair Gain Framer

registers. The CRC is then calculated and inserted. Then the data is scrambled and

transmitted to the destination bit pump.

descrambles like Bt8954 in the remote terminal. That is, SCRAM_TAP = 0

[TCMD2; 0x87.1] but DSCRAM_TAP = 1 [RCMD_2; 0x91.4].

like Bt8954 in the Central Office terminal. That is, SCRAM_TAP = 1

[TDMD2; 0x87.1] but DSCRAM_TAP = 0 [RCMD_2; 0x91.4].

Figure 1-2. Repeater Block Diagram

Central Office Terminal

Bt8954

TDAT

RDAT

Bt8960/

Bt8970

1.1 Voice Pair Gain Applications

Next, EOC and IND overhead are inserted from the Bt8954 EOC and IND

Bt8954 (C→R) scrambles like Bt8954 in the Central Office terminal but

Bt8954 (R→C) scrambles like Bt8954 in the remote terminal but descrambles

Repeater

Bt8954 (C→R)

Bt8960/

Bt8970

BCLK

QCLK

RDAT TDAT

HCLK

BCLK_REP

QCLK_REP

Bt8960/

Bt8970

Remote Terminal

Bt8960/

Bt8970

Bt8954

RDAT

TDAT

XTAL

XTAL

Bt8954 (R→C)

TDAT

QCLK_REP

BCLK_REP

RDAT

QCLK

BCLK

XTAL

N8954DSC

Conexant

1-3

1.0 DSL Systems

Bt8954

1.1 Voice Pair Gain Applications

1.1.2 Subscriber Modem

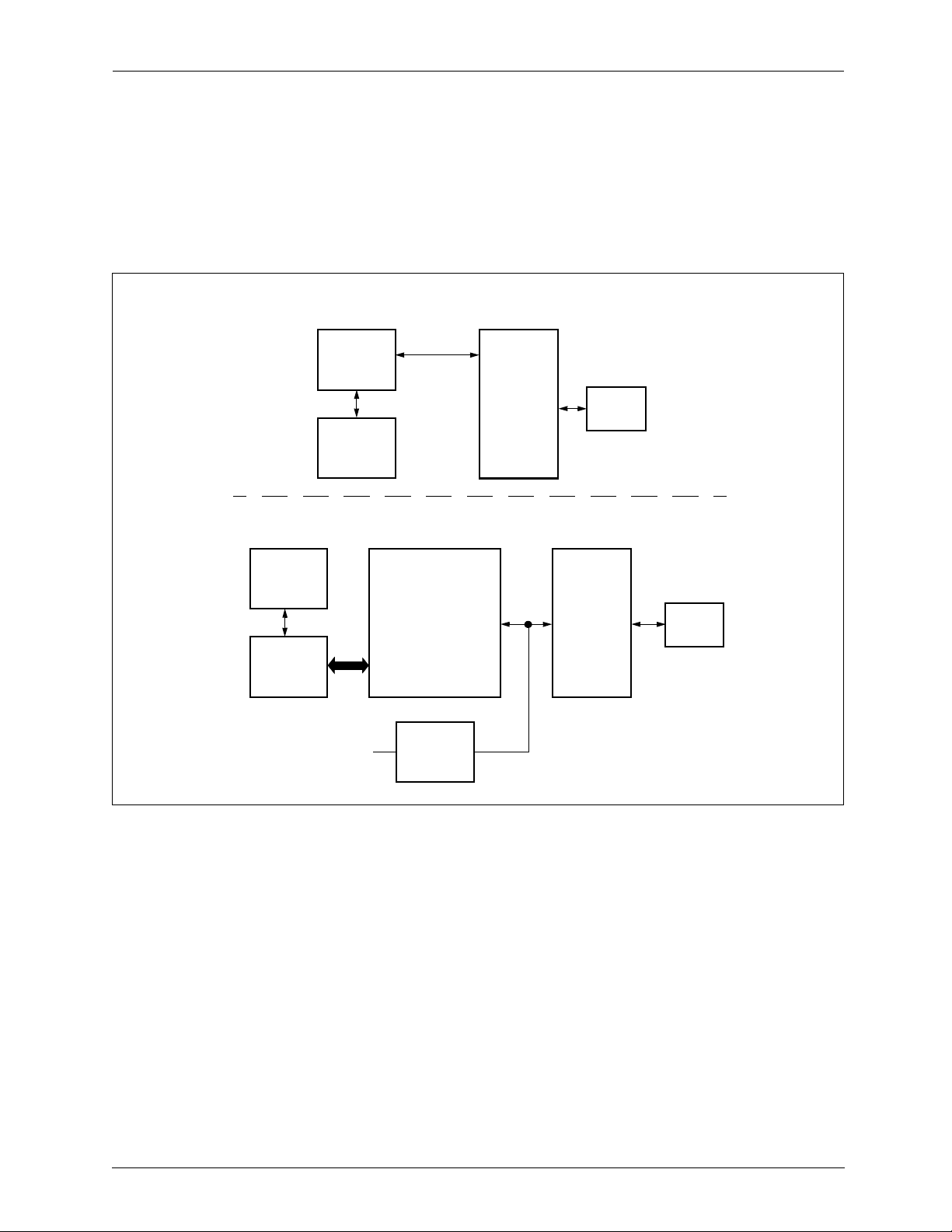

Figure 1-3 illustrates a DSL data modem application where a Central Processing

Unit (CPU) delivers PCM data directly to Bt8954. Alternatively, a multichannel

communications controller such as Bt8472/4 can be used to manage the transfer

of data between the CPU and the PCM channel through a local shared memory.

Figure 1-3. Subscriber Modem (Terminal) System Block Diagram

Single Channel Payload

CPU

PCM Serial

Port

Bt8954

Memory

Multichannel Payload

Voice Pair Gain Framer

Bit Pump

CPU

Shared

Memory

PCI

Bt8472/4

HDLC Controller

CODECPOTS

PCM

Bt8954

Bit Pump

1-4

Conexant

N8954DSC

Bt8954

1.0 DSL Systems

Voice Pair Gain Framer

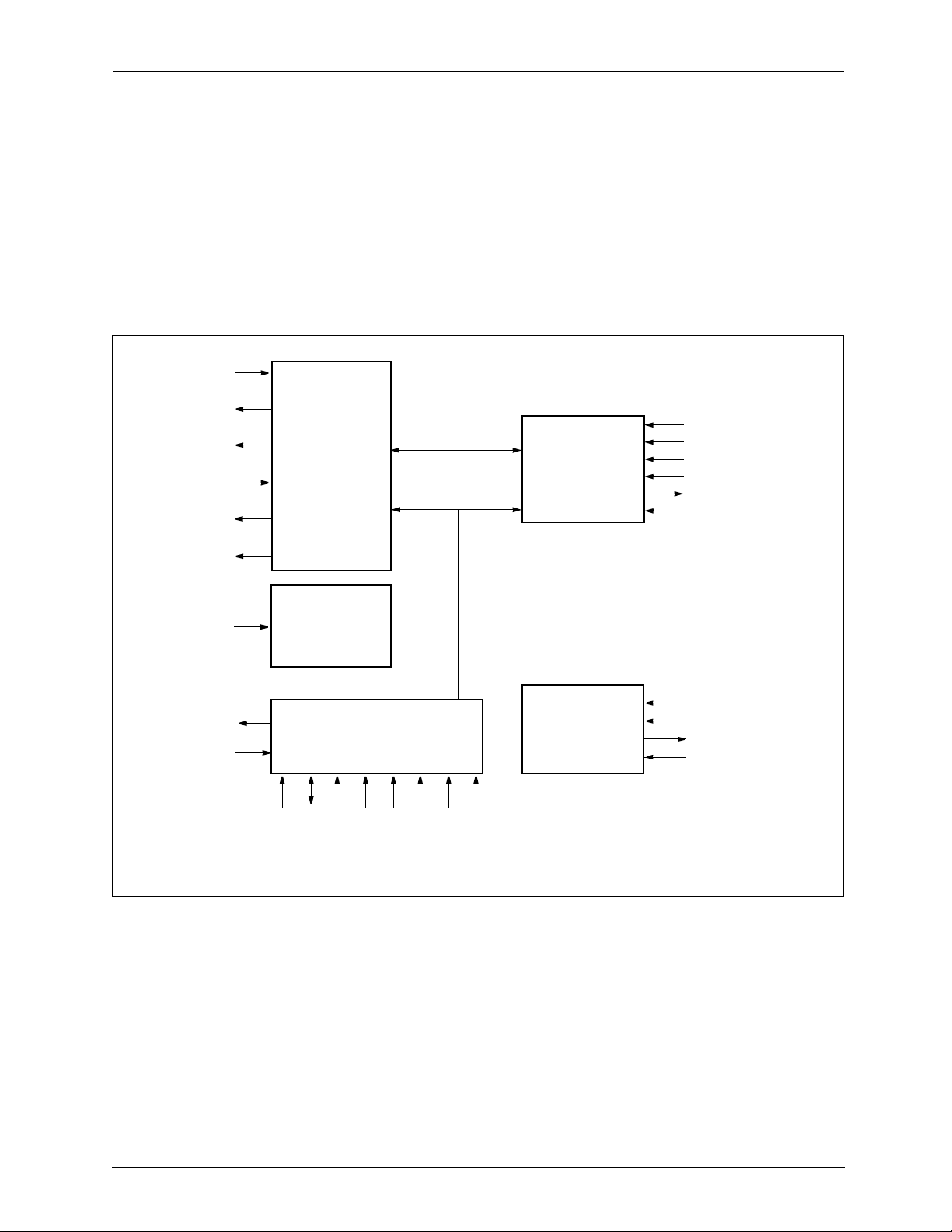

1.2 System Interfaces

System interfaces and associated signals for the Bt8954 functional circuit blocks

are illustrated in Figure 1-4. Circuit blocks are described in the following

sections, and signals are defined in Table 2-1.

Figure 1-4. Bt8954 System Interfaces

PCMT

ADPCMCK

PCMCKO

PCMCKI

PCMR

PCM

Interface

DSL

Interface

1.2 System Interfaces

BCLK_REP

QCLK_REP

BCLK

QCLK

TDAT

RDAT

PCMF[18:1]

HCLK

IRQ*

RST*

ADDR[7:0]

PLL

Microcomputer

Interface

CS*

AD[7:0]

ALE

RD*/DS*

WR*/R/W*

MOTEL*

MUXED

Test

Access

TCK

TDI

TDO

TMS

N8954DSC

Conexant

1-5

1.0 DSL Systems

Bt8954

1.2 System Interfaces

Voice Pair Gain Framer

1-6

Conexant

N8954DSC

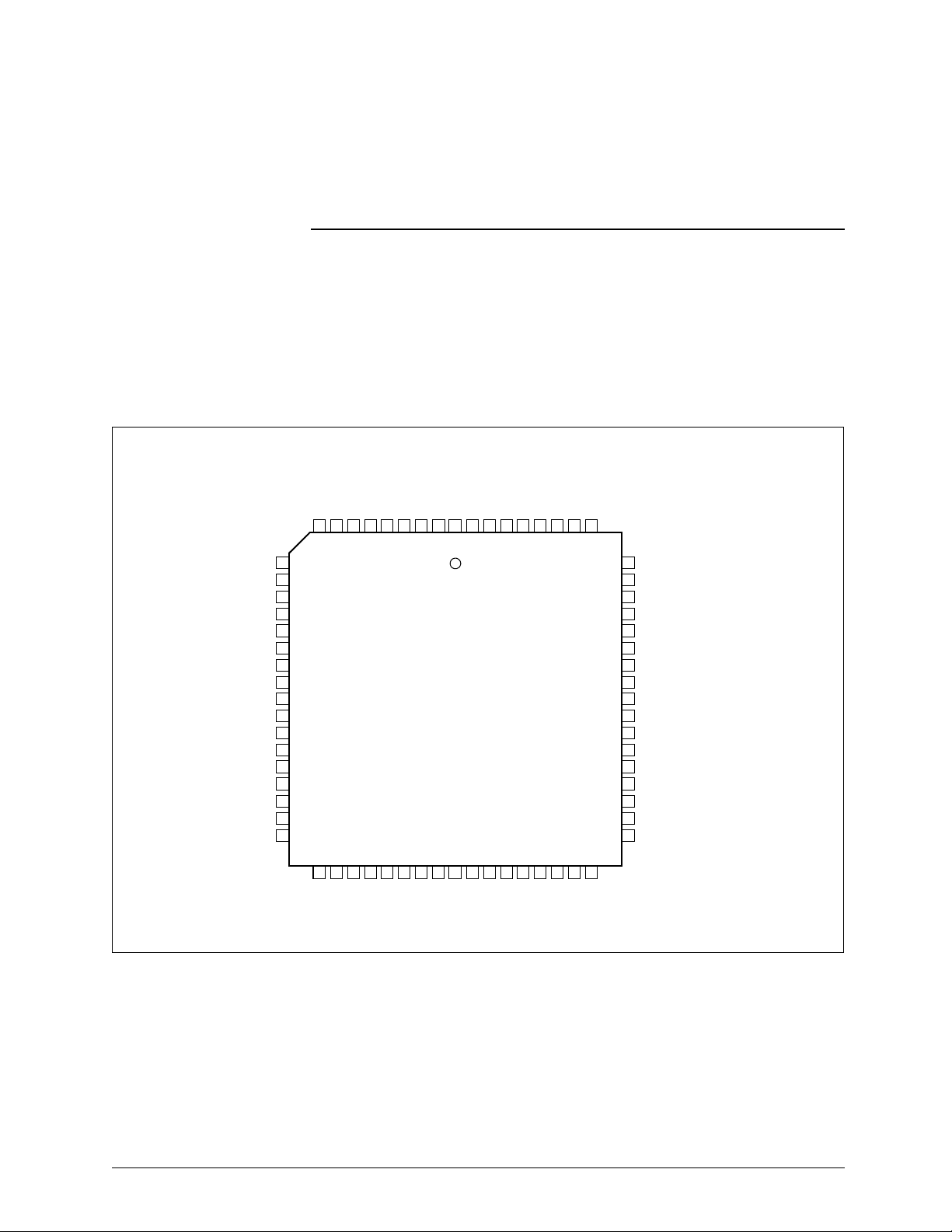

Figure 2-1. Pin Diagram

2

2.0 Pin Descriptions

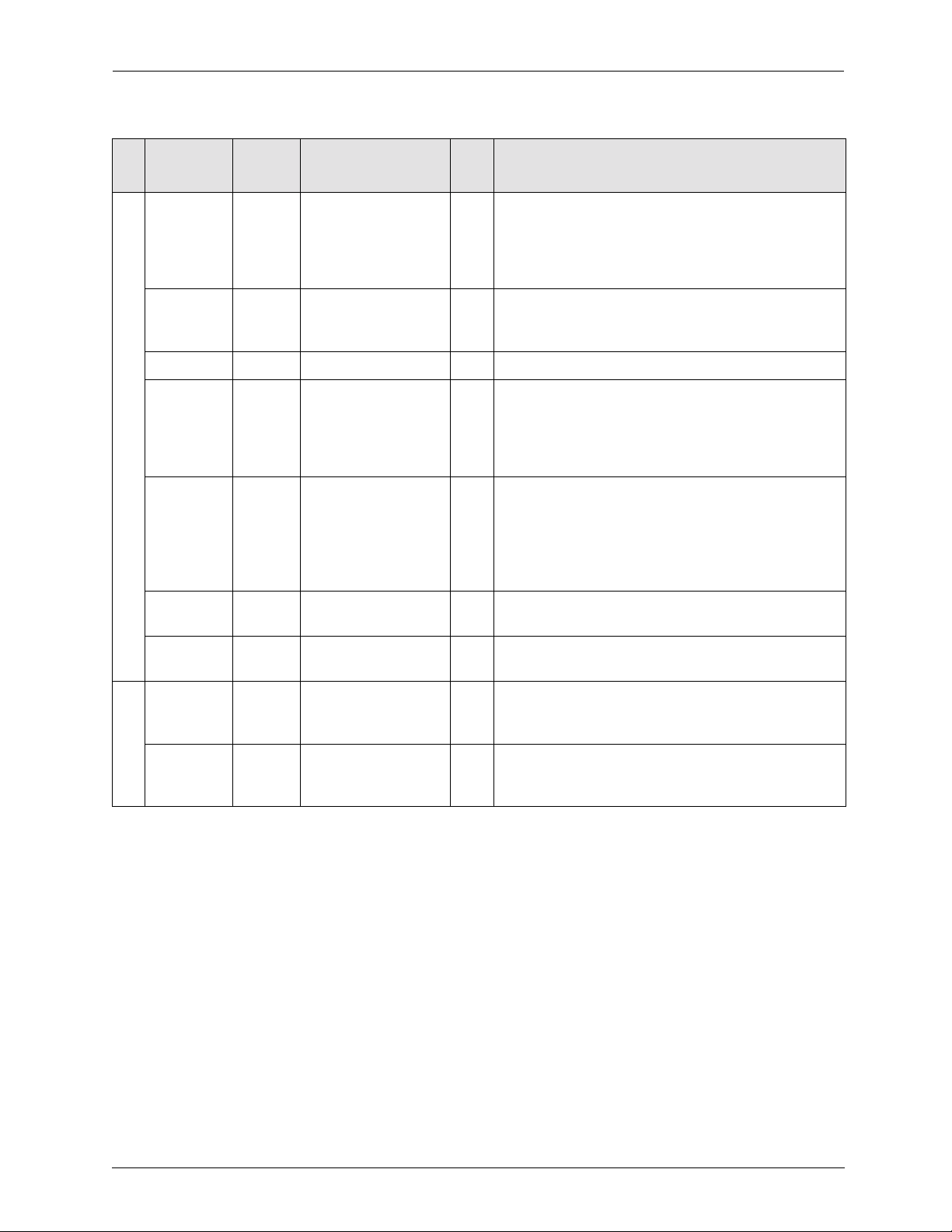

Bt8954 pin assignments for the 68-pin Plastic Leaded Chip Carrier (PLCC)

package are illustrated in Figure 2-1. The functional pinout for the Bt8954 is

illustrated in Figure 2-2, and the signals are defined in Table 2-1.

QCLK

QCLK_REP

CS*

RD*/DS*

WR*/R/W*

ALE

ADDR[6]

VDD

GND

ADDR[5]

ADDR[4]

ADDR[3]

ADDR[2]

ADDR[1]

ADDR[0]

IRQ*

GND

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

HCLK

DTEST

8

9

28

27

VDD

AD[7]

BCLK_REP

BCLK

5

6

7

30

29

AD[5]

AD[6]

TDAT

RDAT

4

32

31

AD[3]

AD[4]

PLL_VDD

PCMF[18]

2

3

Bt8954

34

33

AD[1]

AD[2]

PCMF[16]

PCMF[17]

PLL_GND

1

67

68

37

36

35

AD[0]

MUXED

MOTEL*

PCMR

PCMF[14]

PCMF[15]

64

65

66

40

39

38

TCK

TDO

RST*

PCMCKO

PCMCKI

VDD

61

62

63

43

42

41

TDI

TMS

GND

60

ADPCMCK

59

PCMF[13]

58

PCMF[12]

57

PCMF[11]

56

PCMF[10]

55

PCMF[9]

54

VDD

53

GND

52

PCMF[8]

51

PCMF[7]

50

PCMF[6]/EPCMF[6]

49

PCMF[5]/EPCMF[5]

48

PCMF[4]/EPCMF[4]

47

PCMF[3]/EPCMF[3]

46

PCMF[2]/EPCMF[2]

45

PCMF[1]/EPCMF[1]

44

PCMT

N8954DSC

Conexant

2-1

2.0 Pin Descriptions

Bt8954

Figure 2-2. Bt8954 Functional Pinout

Motorola/Intel

Write*/Read/Write

Address Latch Enable

Interrupt Request

Address Data

Reset

Chip Select

Read/Data Strobe

Quaternary Clock

Receive Data

Bit Clock

BCLK Repeater

QCLK Repeater

PCM Transmit Data Input

PCM Clock Input

I

I

I

I

I/O

16, 19-24

I

I

I

I

I

I

I

I

I

I

I

36

14

15

37

28-35

38

12

13

10

5

6

7

11

43

63

MOTEL*

WR*/R/W*

ALE

MUXED

AD[7:0]

ADDR[6:0]Address Bus

RST*

CS*

RD*/DS*

QCLK

RDAT

BCLK

BCLK_REP

QCLK_REP

PCMT

PCMCKI

Microcomputer

Interface

DSL Interface

Repeater Pins

PCM Interface

IRQ* Interrupt Request

TDAT

PCMCKO

ADPCMCK

PCMR

PCMF[18:1]

EPCMFn[6:1]

25

4

62

59

64

44-51

54-58

65-68,3

44-49

Voice Pair Gain Framer

OD

O

Transmit Data

PCM Clock Output

O

ADPCM Clock Output

O

O

PCM Receive Data Output

PCM Frame Sync

O

PCM Frame SyncO

HCLK Input

Digital Test

JTAG Test Data In

JTAG Test Mode Select

Power Supply

Power Supply

8

I

I

I

I

I

HCLK

9

DTEST

41

TDI

42

TMS TDO JTAG Test Data Out

39

TCKJTAG Test Clock

61, 27

VDD

17, 53

VDD

2

PLL_VDDPLL Power Supply

1

PLL_GNDPLL Ground

I/O = Bidirectional, OD = Open Drain

Test and Diagnostic

I = Input, O = Output,

PLL

Interface

Power and

Ground

GND_O

GND_IC

40

26, 60

18, 52

O

Ground

GroundI

2-2

Conexant

N8954DSC

Bt8954

2.0 Pin Descriptions

Voice Pair Gain Framer

Table 2-1. Hardware Signal Definitions

Pin Label

MOTEL* 36 Motorola/Intel* I Selects between Motorola and Intel hands hake conventions

ALE 15 Address Latch Enable I Falling-edge-sensitive input. The value of AD[7:0] when

CS* 12 Chip Select I Active-low input used to enable read/write operations on the

RD*/DS* 13 Read/Data Strobe I Bimodal input for controlling read/write access on the MCI.

Pin

Number

(1 of 4)

Signal Name I/O Definition

for the RD*/DS* and WR*/R/W* signals.

MOTEL* = 1 for Motorola protocol: DS*, R/W*;

MOTEL* = 0 for Intel protocol: RD*, WR*.

MUXED = 1, or of ADDR[7:0] when MUXED = 0, is internally

latched on the falling edge of ALE.

Microcomputer Interface (MCI).

When MOTEL* = 1 and CS* = 0, RD*/DS* behaves as an

active-low data strobe, DS*. Internal data is output on

AD[7:0] when DS* = 0 and R/W* = 1. External data is

internally latched from AD[7:0] on the rising edge of DS*

when R/W* = 0.

When MOTEL* = 0 and CS* = 0, RD*/DS* behaves as an

active-low read strobe RD*. Internal data is output on

AD[7:0] when RD* = 0. Write operations are not controlled

by RD* in this mode.

WR*/R/W* 14 Write/Read/Write I Bimodal input for controlling read/write access on the MC I.

When MOTEL* = 1 and CS* = 0, WR*/R/W* behaves as a

read/write select line, R/W*. Internal data is output on

AD[7:0] when DS* = 0 and R/W* = 1. External data is

internally latched from AD[7:0] on the rising edge of DS*

when R/W* = 0.

When MOTEL* = 0 and CS* = 0, WR*/R/W* behaves as

an active-low write strobe, WR*. External data is internally

latched from AD[7:0] on the rising edge of WR*. Rea d

Microcomputer Interface (MCI)

AD[7:0] 28–35 Address-Data[7:0] I /O Eight-bit bidirectional multiplexed address-data bus.

ADDR[6:0] 19–24, 16Address Bus [6:0]

(Not Multiplexed)

MUXED 37 Addressing Mo de Select I Controls the MCI addressing mode.

IRQ* 25 Interrupt Request O,ODActive-low open-drain output that indicate requests for

operations are not controlled by WR* in this mode.

AD[7] = MSB, AD[0] = LSB. Usage is controlled using the

MUXED signal.

I Provides a glueless interface to microcomputers with

separate address and data buses. ADDR[6] = MSB, ADDR[0]

= LSB. Usage is controlled using the MUXED signal.

When MUXED = 1, the MCI uses AD[7:0] as a multiplexed

signal for address and data (typical of Intel processors).

When MUXED = 0, the MCI uses ADDR[7:0] as the

address input and AD[7:0] for data only (typical of Motorola

processors).

interrupt. Asserted whenever at least one unmasked interrupt

flag is set. Remains inactive whenever no unmasked

interrupt flags are present.

RST* 38 Reset I Asynchronous, active-low, level-sensitive input that resets

the framer .

N8954DSC

Conexant

2-3

2.0 Pin Descriptions

Bt8954

Table 2-1. Hardware Signal Definitions

Pin Label

BCLK 6 Bit Clock I Corresponds to the DSL channel. BCLK operates at the 2B1Q

QCLK 10 Quaternary Clock I Operates at the 2B1Q symbol rate (1/2 bit rate) and identifies

DSL Interface

Pin

Number

(2 of 4)

Signal Name I/O Definition

symbol rate. The rising edge of BCLK outputs 2x TDAT. The

falling edge of BCLK samples QCLK at the RDAT input. (In

the repeater terminal, BCLK is the BCLK from the bit pump to

which RDAT is connected.)

NOTE(S):

The BCLK signal from the bit-pump to the channel unit

device is sensitive to overshoot and undershoot. The BCLK

sensitivity could cause bit-errors in the system . A 100 Ω

series terminating resistor might be required to help dampen

the overshoot and undershoot. The bit-pump line cards

include a 74HCT244 to drive the long traces through the

motherboard 96-pin connectors.

sign and magnitude alignment of both the RDAT and TDAT

serially encoded bit streams.

1 = magnitude bit. In the Repeater Terminal, BCLK is the

BCLK from the bit pump to which RDAT is connected.

Refer to Appendix A, page 81.

The falling edge of BCLK samples QCLK: 0 = sign bit;

Voice Pair Gain Framer

TDAT 4 Transmit Data O DSL transmit data output at the bit rate on the rising edge of

BCLK. Serially encoded with the 2B1Q sign bit aligned to the

QCLK low level and the 2B1Q magnitude bit aligned to the

QCLK high level.

RDAT 5 Receive Data I DSL receive data input sampled on the falling edge of BCLK.

The serially encoded 2B1Q sign bit is sampled when QCLK is

low, and the 2B1Q magnitude bit is sampled when QCLK is

high.

BCLK_REP 7 BCLK from destination

bit pump in a repeater

terminal

QCLK_REP 11 QCLK from destination

Repeater Pins

bit pump in a repeater

terminal

I BCLK from the bit pump to which the Bt8954 TDAT is

connected in a repeater terminal. It is used only in the

repeater mode and should be tied to VDD or GND in

non-repeater terminals.

I QCLK from the bit pump to which the Bt8954 TDAT is

connected in a repeater terminal. It is used only in the

repeater mode and should be tied to VDD or GND in

non-repeater terminals.

2-4

Conexant

N8954DSC

Bt8954

2.0 Pin Descriptions

Voice Pair Gain Framer

Table 2-1. Hardware Signal Definitions

Pin Label

PCMCKO 62 PCM Clock Output O Outpu t P CM clock for sending and receiving bits from PCM

PCMCKI 63 PCM Clock Input I Sends and receives bits from PCM codecs. Controls the PCM

ADPCMCK 59 ADPCM Clock Output O Used by ADPCM chips. It is 10x or 4x PCMCKO.

PCMFn 3,

PCM Interface

EPCMFn 44-49 Encoded PCM Frame

Pin

Number

44-51,

54-58,

65-68

PCM Frame Sync (n =

1,...,18)

Sync

(n = 1,...,6)

(3 of 4)

Signal Name I/O Definition

codecs. It is generated by the PLL and is 1.536 MHz or

2.048 MHz depending on the PLL configu r ation. Connect to

receive/transmit bit clocks and receive/transmit master

clocks of PCM codecs. In normal operation, tie to PCMCKI.

Formatter, reads from the RFIFO, and writes into the TFIFO.

In normal operation, tie to PCMCKO.

O Frame sync pulse for receiving bits from and transmitting

bits to a PCM codec. Connect to receive/transmit frame

syncs of the PCM codec. This signal is low if not connected

to any PCM codec. It supports both short-frame and

long-frame operations.

O Channel number of bits received from and transmitte d to

PCM codecs. Connect to a decoder to generate

receive/transmit frame syncs for PCM codecs. For n = 1,..,6,

EPCMFn is multiplexed with PCMFn depending on the

ENC_FSYNC configuration in the PCM Format register

[PCM_FORMAT; 0xF1.6].

PCMR 64 PCM Receive Data

Output

PCMT 43 PCM Transmit Data

Input

HCLK 8 HCLK Input I Connects to the HCLK output of the Bt8960/70 bit pump. It is

PLL

DTEST 9 Digital Test I DTEST–Active high test input used by Conexant to enable an

O Serial bit stream to PCM codecs is shifted out at the rising

edge of PCMCKI.

I Serial bit stream from the PCM codecs is sampled at the

falling edge of PCMCKI.

32xBCLK or 64xQCLK and is used as the PLL clock

reference.

internal test mode. This input should be tied to ground

(GND).

N8954DSC

Conexant

2-5

2.0 Pin Descriptions

Bt8954

Table 2-1. Hardware Signal Definitions

Pin Label

TDI 41 JTAG Test Data Input I Test data input per IEEE Std 1149.1-1990. Used for loading

TMS 42 JTAG Test Mode Select I Test mode select input per IEEE Std 1149.1-1990. Internally

TDO 40 JTAG Test Data Output O Test data output per IEEE Std 1149.1-1990. Three-state

Test and Diagnostic Interface

TCK 39 JTAG Test Clock I Test clock input per IEEE Std 1149.1-1990. Used for all test

VDD 17,

Pin

Number

Power Supply I Power supply pins for the I/O buffers and core logic

27,

53,

61

(4 of 4)

Signal Name I/O Definition

all serial instructions and data into internal test l ogi c.

Sampled on the rising edge of TCK. TDI can be left

unconnected if it is not being used because it is pulled up

internally.

pulled-up input signal that controls the test-logic state

machine. Sampled on the rising edge of TCK. TMS can be left

unconnected if it is not being used because it is pulled up

internally.

output used for reading all serial configuration and test data

from internal test logic. Updated on the falling edge of TCK.

interface and internal test-logic operations. If unus ed, TCK

should be pulled low.

functions.

5VDC±5%.

Voice Pair Gain Framer

GND 18,

26,

52,

60

Power and Ground

PLL_VDD 2 PLL Power Supply P Dedicated supply pin for the PLL circuitry. Connect to VDD

PLL_GND 1 PLL Ground G Dedicated ground pin for the PLL circuitry. Must be held at

Ground G Ground pins for the I/O buffers and core logic functions.

Must be held at the same potential as PLL_GND.

externally.

the same potential as GND.

2-6

Conexant

N8954DSC

3

3.0 Circuit Descriptions

3.1 Overview

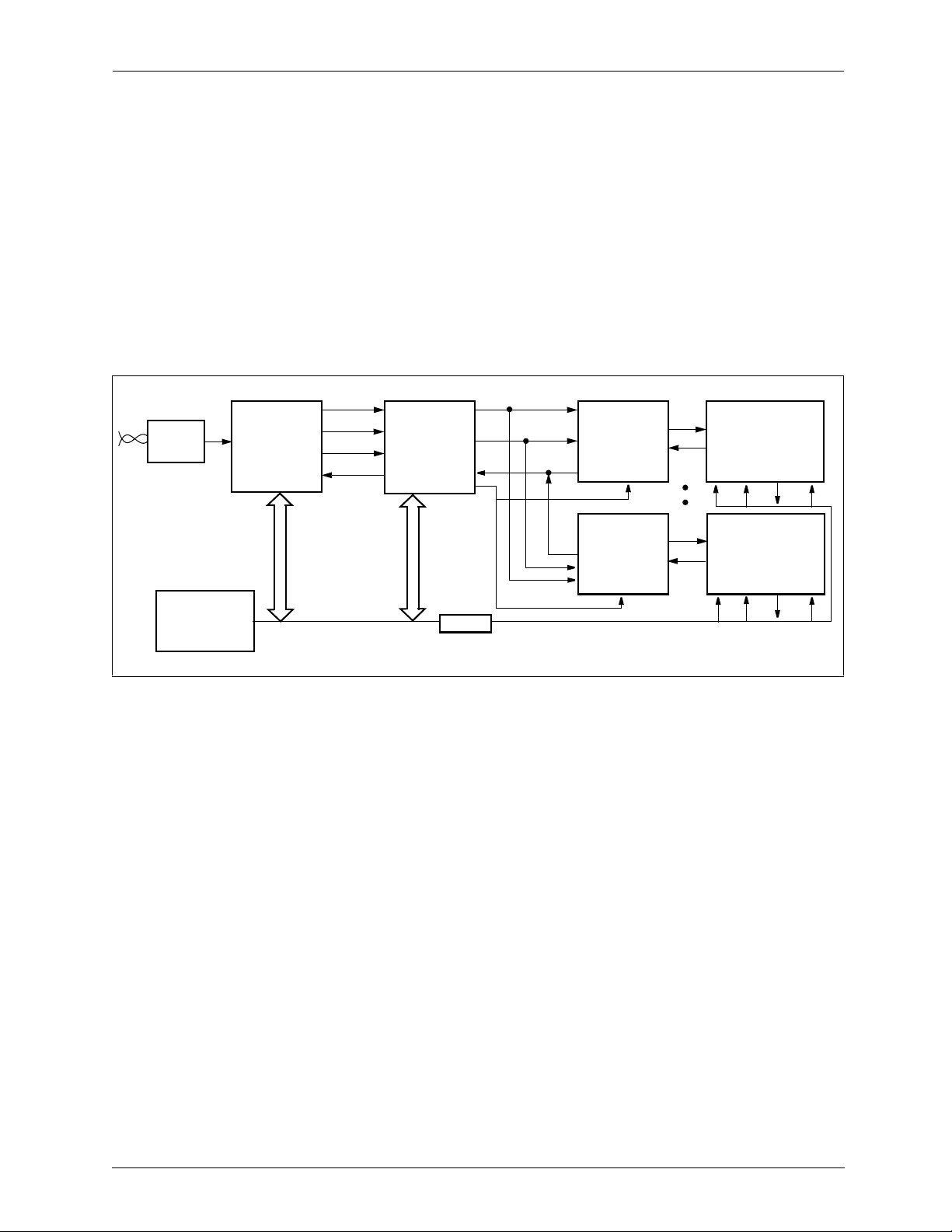

Figure 3-1 details the major blocks and pins of Bt8954. After the 2B1Q decode of

the bit stream is received from the DSL bit pump, the Receive Framer detects the

beginning of the Digital Subscriber Line (DSL) frame, and generates the required

pulses for synchronizing the different demultiplexing functions. The Payload

Demux block strips overhead bits from the DSL frame and puts the payload for

the different Pulse Code Multiplexed (PCM) time slots into the PCM RFIFO.

The PCM RFIFO is emptied through the PCMR pin.

On the transmit side, the PCM TFIFO is filled with serial data on PCMT.

Payload data from the TFIFO is multiplexed with signaling data from the

signaling registers and overhead from the OH (overhead) registers. The

multiplexed data is then sent to the DSL bit pump, through the TDAT pin, after

being 2B1Q encoded.

PCM and DSL loopback functions are performed using the loopback blocks.

The PCMCLK, ADPCMCK, and the internal clock are generated and

synchronized to BCLK with the PLL. The PLL uses HCLK as its clock reference.

Figure 3-1. Block Diagram

RDAT

HCLK

BCLK

QCLK

DSL Bit-Pump

TDAT

N8954DSC

Receiver

LB

Transmitter

2B1Q

Decoder

PLL

2B1Q

Encoder

Receive

Framer

Payload

Demux

OH/Signaling

Registers

Payload

Mux

Conexant

PCM

RFIFO

LB

PCM

TFIFO

Microcomputer Interface

CS*

DS*

ALE

AD[7:0]

MUXED

ADDR[7:0]

Microcomputer

WR/RW*

IRQ*

MOTEL*

PCM Formatter

RST*

PCMR

ADPCMCK

PCMCLK

PCMF[18:1]

PCMT

ADPCM/PCM Codecs

3-1

3.0 Circuit Descriptions

Bt8954

3.2 DSL Frame Format

3.2 DSL Frame Format

The DSL frame is the fundamental data element of the bit streams transmitted and

received by Bt8954 at the DSL interface. It is patterned after the 2 T1, 2 E1, and

3 E1 frame structures. Figure 3-2 illustrates the basic format of a DSL frame.

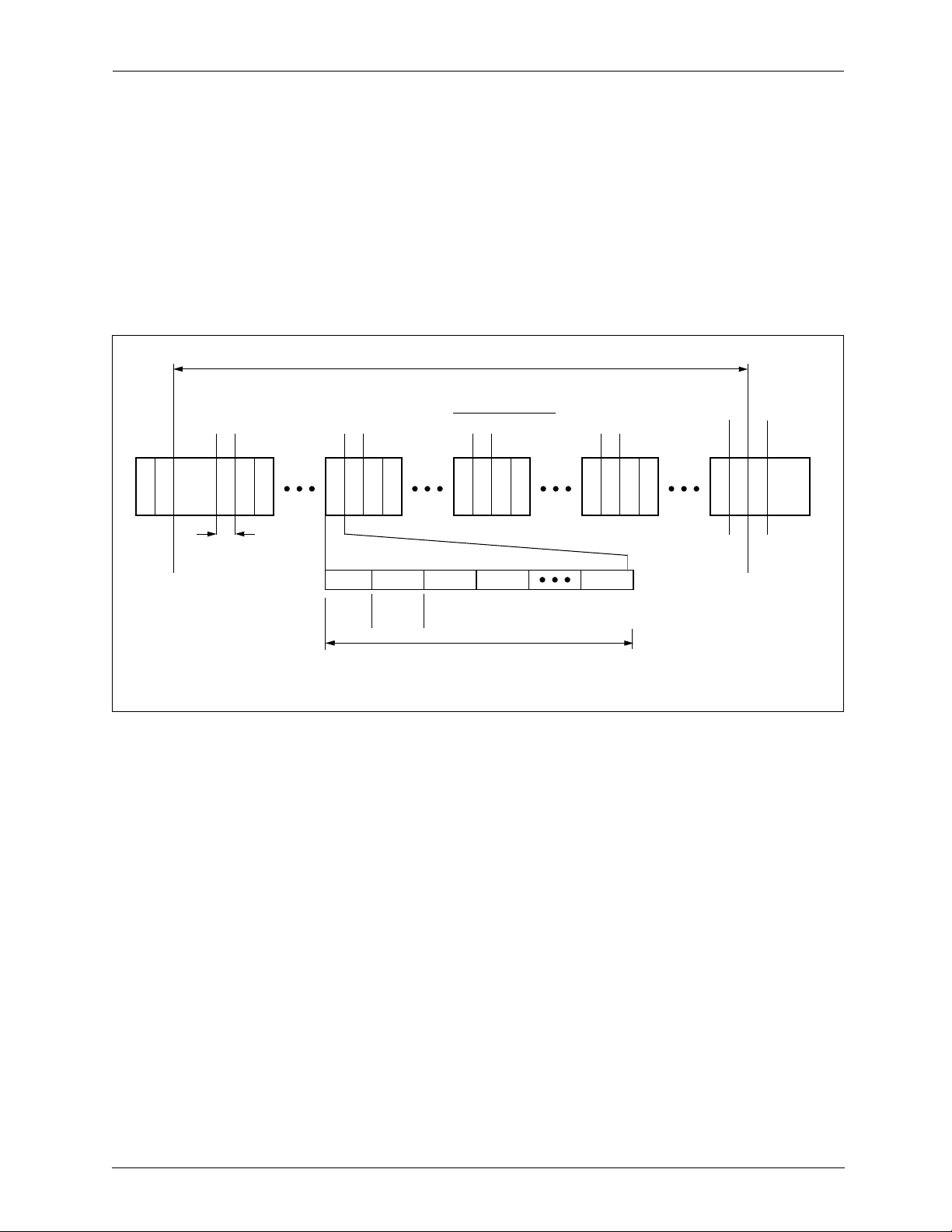

Figure 3-2. Basic DSL Frame Format

0 ms

1Q

7Q

S

S

Sync

t

t

Word

q

q

1

2

D

B

O

0

H

1

12x(4N+0.5S)

B

0

2

DSL Frame

#Quats = 4 x (48N + 6S) + 24 = 192N + 24S + 24

#Bits = 2 x (192N + 24S + 24)

Bit Rate (kbps) = 2 x (192N + 24S + 24)

5Q

B

D

B

1

2

B

O

1

1

H

3

4

6 ms

5Q 5Q

B

D

B

2

O

2

4

H

5

= (64N + 8S + 8)

B

2

6

Voice Pair Gain Framer

6 ms

1Q1Q

S

B

D

B

3

6

B

O

3

3

H

7

8

S

B

4

8

Sync

t

t

Word

q

q

1

2

1/(32N + 4S + 4) ms

S-Bits Byte1 Byte2 Byte3 Byte_N

0-8 Bits 8 Bits

3.2.1 Detailed Frame Structure

Each frame has a 6 ms duration and is made up of 48 payload blocks. Each block

contains S number of S-bits (for data signaling) and N number of bytes where N

is the number of PCM time slots. The microcomputer selects the number of S-bits

in the NUM_SBITS [3:0] field of Transmit Command register 2

[TCMD_2; 0x87.5:2] and the N number of PCM time slots in the NUM_

CHAN[4:0] field of the PCM Format register [PCM_FORMAT; 0xF1.4:0]. S-bits

vary from 0 to 8 bits, while N varies from 1 to 18 time slots. Groups of 12 payload

blocks are concatenated, and each group is separated by an ordered set of DOH

(DSL ov erhead) bits. A 14-bit SYNC word pattern identifies the beginning of the

DSL frame.

Forty-eight overhead bits are defined in one DSL frame with the last 2 bits

used for stuffing. This corresponds to an 8 kbps (48 bits/6 ms) overhead bit rate.

The 2 bits of stuffing are the average number of stuffing bits per frame since the

transmitter alternatively transmits 0 bits of stuffing or 4 bits of stuffing in each

frame.

Bnn

#Quats = (4N + 0.5S)

#Bits = 2 x (4N + 0.5S)

“6+”“6-”

LEGEND:

Bnn = Payload Blocks 1-48

DOH = DSL Overhead

S-bits = Data Signaling Bits

N = # of Voice Channels

3-2

Conexant

N8954DSC

Bt8954

3.0 Circuit Descriptions

Voice Pair Gain Framer

3.2.2 Differences Between the DSL and HDSL T1/E1 Frame Formats

The DSL frame format is similar to the T1/E1 frame formats that are transported

on one HDSL loop. The main difference is due to the number of S-bits. While

fixed as 1 F-bit/block and 1 Z-bit/block for the T1 and E1 HDSL frame f ormats, it

can vary between 0 and 8 bits for the DSL frame format. The number of S-bits is

allow e d to v ary up to 8 bits so that a v ariab le numb er of D-channel bit r ates (up to

64 kbps) can be supported.

3.2.2.1 EXTRA_Z_BIT Option

Some systems (e.g., PCM11) require an extra 8 kbps Z-bit field in addition to the

basic frame structure outlined in Figure 3-2. T o accommodate such systems, each

block of the DSL frame has an extra Z-bit (preceding the S-bits field) that can be

enabled for transmit when EXTRA_Z_BIT in Command register 1

[CMD_1; 0xC0.5] is set. For example, a PCM11 system can have a 784 kbps bit

rate consisting of 704 kbps (11x64 kbps) of payload, 8 kbps of ov er head, 64 kbps

of signaling information, and 8 kbps of the extra Z-bit. This extra Z-bit field is a

dummy field and is not accessible through the MC.

3.2.3 Overhead Bit Allocation

The overhead bit allocation of the DSL frame is the same as that of the HDSL

frame given in Table 3-1.

3.2 DSL Frame Format

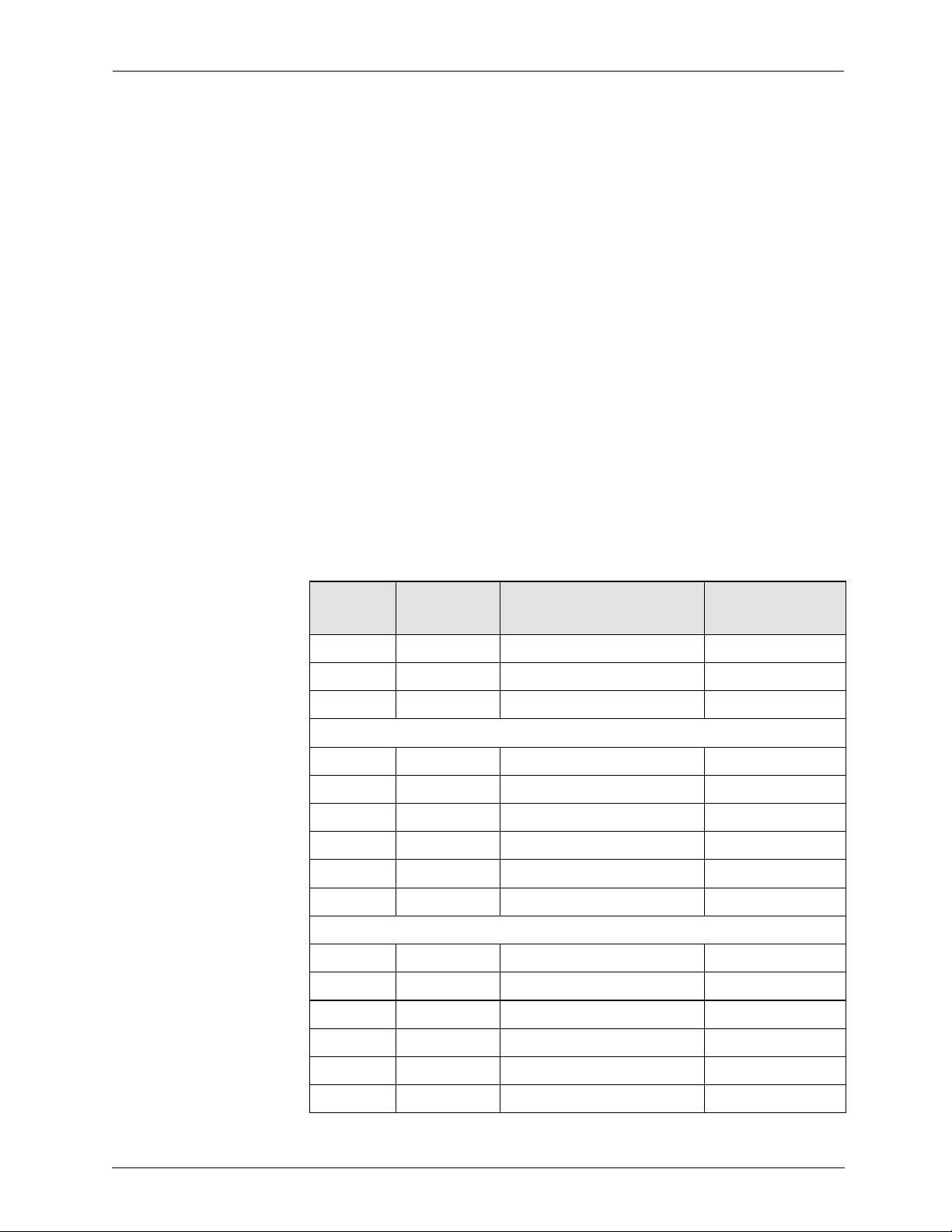

Table 3-1. DSL Frame Structure and Overhead Bit Allocation

DOH Bit

Number

1–14 SW1–SW14 SYNC Word —

15 losd Loss of Signal IND[12]

16 febe Far End Block Error IND[11]

17–20 eoc1–eoc4 Embedded Operations Channel EOC[12]–EOC[9]

21–22 crc1–crc2 Cyclic Redundancy Check —

23 ps1 HTU-R Power Status IND[10]

24 ps2 Power Status Bit 2 IND[9]

25 bpv Bipolar Violation IND[8]

26 eo c5 Embedded Operations Channel EOC[8]

27–30 eoc6–eoc9 Embedded Operati ons Channel EOC[7]–EOC[4]

31–32 crc3–crc4 Cyclic Redundancy Check —

33 hrp HDSL Repeater Present IND[7]

Symbol Bit Name DOH Register Bit

Payload Blocks 1–12

Payload Blocks 13–24

(1 of 2)

N8954DSC

34 rrbe Repeater Remote Block Error IND[6]

35 rcbe Repeater Central Block Error IND[5]

36 rega Repeater Alarm IND[4]

Conexant

3-3

3.0 Circuit Descriptions

Bt8954

3.2 DSL Frame Format

Voice Pair Gain Framer

Table 3-1. DSL Frame Structure and Overhead Bit Allocation

DOH Bit

Number

37–40 eoc10–eoc13 Embedded Operations Channel EOC[3]–EOC[0]

41–42 crc5–crc6 Cyclic Redundancy Check —

43 rta Remote Terminal Alarm IND[3]

44 rtr Ready to Receive IND[2]

45 uib Unspecified Indicator Bit IND[1]

46 uib Unspecified Indicator Bit IND[0]

Symbol Bit Name DOH Register Bit

Payload Blocks 25–36

Payload Blocks 37–48

(2 of 2)

3-4

Conexant

N8954DSC

Bt8954

3.0 Circuit Descriptions

Voice Pair Gain Framer

3.3 Receiver

The receiver performs SYNC word detection, overhead extraction, descrambling

of payload data, error performance monitoring, and payload mapping of DSL data

from the received DSL frame into the PCM RFIFO. Figure 3-3 illustrates the

receiver block diagram. The receiver consists of the 2B1Q decoder, receive

framer, descramb ler, CRC check, and payload demux.

Figure 3-3. Receiver Block Diagram

Receive Framer

State

CNT

BCLK

Sync

Detector

STUFF

Detector

CRC

CHK

3.3 Receiver

RDSL_6ms

Payload

Demux

QCLK

RDAT

TDAT

2B1Q

Decoder

3.3.1 2B1Q Decoder

0

1

PD_LOOP

Descrambler

RDAT_DESCR

PCM

RFIFO

The 2 Binary, 1 Quaternary (2B1Q) decoder provides the capability to connect

directly to the Bt8960/70 DSL transceivers. The 2B1Q decoder samples and

aligns the incoming sign and magnitude data. Refer to Table 3-2 for 2B1Q

mapping.

Table 3-2. 2B1Q Decoder Alignment

First Bit

(Sign)

10+3

11+1

01–1

Second Bit

(Magnitudes)

Quaternary Symbol

(Quat)

N8954DSC

00–3

Conexant

3-5

3.0 Circuit Descriptions

Bt8954

3.3 Receiver

3.3.2 Receive Framer

Voice Pair Gain Framer

The receive framer generates the RDSL_6ms pulse after detecting the SYNC

WORD. RDSL_6ms generates pointers that control overhead extraction in the

CRC and OH demux circuitry. The MC initializes the framer to the OUT_OF

SYNC state by writing an y data value to SYNC_RST [0xD8]. F rom the OUT_OF

SYNC state, the framer advances to SYNC_A CQUIRED when the SYNC w ord is

detected. The framer searches all bits received on RDAT to locate a match with

the SYNC word pattern, SYNC_WORD [0xA1].

Due to the possibility of Tip/Ring connector reversal, all sign bits received on

RDAT might be inverted. Therefore, the receive framer searches for both the

programmed SYNC word value and the sign-inverted SYNC word value.

Consequently, a maximum of two values of the SYNC word are used in finding

the frame location. If the SYNC word detected is a sign-in verted version of the

configured SYNC word, the framer sets the Tip/Ring Inversion [TR_INVERT]

status bit of the Receive Status 1 register [RSTATUS_1; 0xE5.6] and

automatically inverts the sign of all quats received on RDAT.

After detecting the SYNC WORD and changing to the SYNC_ACQUIRED

state, the framer progresses through a programmable number of intermediate

SYNC_ACQUIRED states before entering the IN_SYNC state. In each

SYNC_ACQUIRED state, the framer searches for the previously detected SYNC

word v alue in one of tw o locations based upon the absence or presence of the four

STUFF bits (detected by the STUFF Detector). If the SYNC word is detected in

one of the two possible locations, the STATE_CNT[2:0] counter is incremented

[RSTATUS_2; 0xE6.2:0]. When STATE_CNT[2:0] increments to the value

selected by the REACH_SYNC[2:0] criteria [RCMD_1; 0x90.2:0], the framer

changes to the IN_SYNC state. During the SYNC_ACQUIRED state, if valid

SYNC is not detected at one of the two possible locations, the framer returns to

the OUT_OF_SYNC state as illustrated in Figure 3-4.

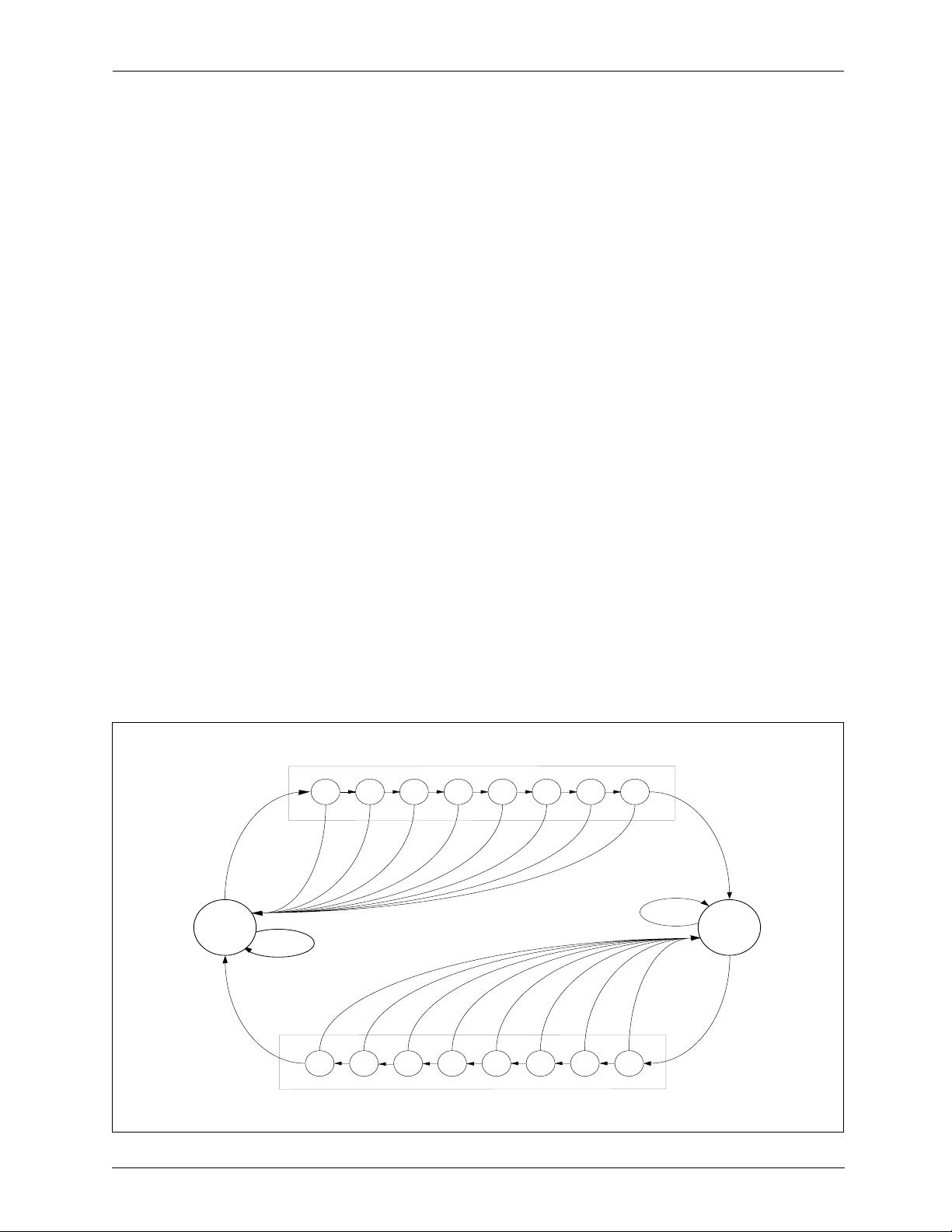

Figure 3-4. Receive Framer Finite State Machine

Consecutive SYNC_ACQUIRED states per REACH_SYNC criteria

SYNC

NO SYNC

OUT_OF

SYNC

NO SYNC

NO

SYNC

87654321

Consecutive SYNC_ERRORED states per LOSS_SYNC criteria

87654321

SYNC

SYNC

IN_SYNC

SYNC

NO SYNC

3-6

Conexant

N8954DSC

Bt8954

3.0 Circuit Descriptions

Voice Pair Gain Framer

After entering IN_SYNC, the framer either remains IN_SYNC as successive

SYNC words are detected or regresses to the SYNC_ERRORED state if SYNC

pattern errors are found. During SYNC_ERRORED states, the number of

matching bits from each comparison of received SYNC word and the

programmed SYNC word pattern must meet or exceed the programmed pattern

match tolerance specified by THRESH_CORR [RCMD_2; 0x91.3:0]. If the

number of matching bits falls below tolerance, the framer expands the locations

searched to quats on either side of the expected location, as illustrated in

Figure 3-5. After detecting a SYNC pattern error and changing to the

SYNC_ ERRORED state, the framer passes through a programmable number of

intermediate SYNC_ERRORED states, before entering the OUT_OF SYNC

state. STATE_CNT increments for each frame in which SYNC is not detected

until the count reaches the LOSS_SYNC[2:0] criteria [RCMD_1; 0x90.5–3] and

the framer enters the OUT_OF SYNC state. If at any time during the

SYNC_ERRORED state the framer detects a completely correct SYNC word

pattern at one of the valid frame locations, then framer returns to the IN_SYNC

state. The ETSI standard, for HDSL transport, recommends the

REACH_SYNC = 2 and LOSS_SYNC = 6 framing criteria.

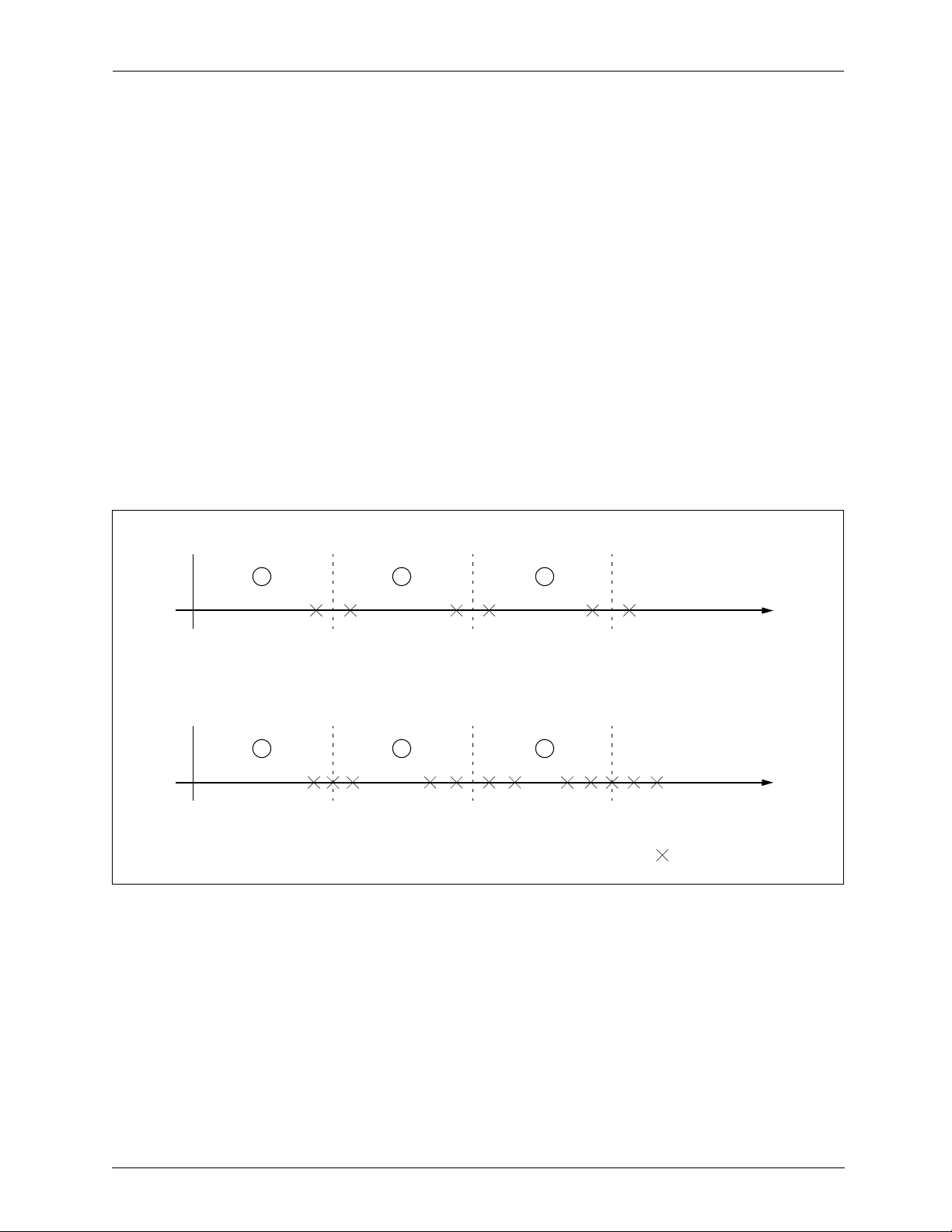

Figure 3-5. Threshold Correlation Effect on Expected SYNC Locations

3.3 Receiver

SYNC Pattern ≥ THRESH_CORR

SYNC_ERRORED

SYNC Pattern < THRESH_CORR

SYNC_ERRORED

3.3.3 CRC Check

SYNC_ERRORED

1

–1q +1q –1q +1q –1q +1q

6 ms 12 ms 18 ms0

SYNC_ERRORED

1

–2q +2q –1q +1q –2q +2q

6 ms 12 ms 18 ms0

2

2

–3q +3q +4q–4q

SYNC_ERRORED

SYNC_ERRORED

The CRC Check block calculates a CRC value for every receiv ed DSL frame. The

CRC Check block reports an error if the CRC in the current frame (calculated at

the other end’s transmitter) does not match the CRC that was calculated for the

previous DSL receive frame. Individual DSL block errors are reported in the

CRC_ERROR bit of the Receive Status 2 register [RSTATUS_2; 0xE6.5] and

accumulated in the CRC Error Count register [CRC_CNT; 0xE8]. The CRC

calculation in the receiver is exactly the same as that in the transmitter.

3

t

3

t

q = 2 bits = 1 quat

= Search Location

N8954DSC

Conexant

3-7

3.0 Circuit Descriptions

Bt8954

3.3 Receiver

3.3.4 Descrambler

The MC enables the descrambler by setting DSCRAM_EN bit of the Receive

Command register and selects the descrambler algorithm via the DSCRAM_ TAP

[RCMD_2; 0x91.5,4]. The descrambler, if enabled, descrambles all DSL receive

data except the SYNC word. The algorithm is chosen from one of two possible

choices, depending on whether Bt8954 is located at the Central Office or at a

Remote Site.

The descrambler is basically a 23-bit-long Linear Feedback Shift register

(LFSR). The algorithm chosen determines the feedback points. The LFSR

structure and polynomials for the two descrambler algorithms are illustrated in

Figure 3-6 and Figure 3-7. The descrambler is clocked with BCLK.

Figure 3-6. LFSR Structure for Transmission in the Remote

Scrambled Input (bk)

x

-1

k-1

z

x

-1

k-2

z

x

-1

k-3

z

x

-1

z

+

x

k-16

x

-1

k-15

z

x

-1

k-14

z

x

-1

k-13

z

z

→

Central Office Direction

x

-1

z

k-12

x

k-5

-1

z

k-4

-1

z

x

-1

k-11

Voice Pair Gain Framer

Unscrambled Output (ck)

x

k-6

-1

z

z

x

-1

k-10

x

k-7

-1

z

x

-1

k-8

z

x

-1

k-9

z

x

-1

k-17

z

x

-1

k-18

z

x

-1

k-19

z

+

Polynomial: ck = xk-23

xk-18 b

+

Figure 3-7. LFSR Structure for Transmission in the Central Office

Scrambled Input (bk)

x

-1

z

k-1

-1

z

+

k

x

k-2

x

-1

k-3

z

+

= Modulo-2 Summation (XOR gate)

-1

= Delay Element (D flip-flop clocked with BCLK)

z

x

k-4

-1

z

-1

z

+

x

k-16

x

-1

k-15

z

x

-1

k-17

z

x

-1

k-14

z

x

-1

k-18

z

x

-1

k-13

z

x

-1

k-19

z

x

-1

k-12

z

-1

z

x

-1

k-20

z

→

Remote Direction

x

k-5

-1

z

x

k-20

z

x

z

-1

z

-1

k-11

-1

x

x

x

k-21

k-6

z

k-21

x

-1

k-22

z

Unscrambled Output (ck)

x

-1

k-7

z

x

-1

z

k-10

-1

x

z

k-22

-1

x

-1

k-23

z

x

-1

k-8

z

x

-1

k-9

z

x

-1

k-23

z

Polynomial: ck = xk-23

3-8

xk-5

+

b

+

k

Conexant

+

+

= Modulo-2 Summation (XOR gate)

-1

= Delay Element (D flip-flop clocked with BCLK)

z

N8954DSC

Loading...

Loading...