CONEX Bt861KRF, Bt860KRF Datasheet

Bt860/861

Multiport YCrCb to NTSC / PAL

Digital Video Encoder

The Bt860/861 is a multiport digital video encoder with pixel synchronization and

per-pixel blending capabilities. The three 8-bit YCrCb data ports allow for a variety of

video and graphic overlay configurations useful in video set-top box applications.

The Bt860/861 is specifically designed for video systems requiring composite,

Y/C (S-Video), and simultaneous component YUV or RGB (SCART) video signals.

Worldwide video standards are supported, including NTSC-M (N. America, Taiwan,

Japan), PAL-B,D,G,H,I (Europe, Asia), PAL-M (Brazil), PAL-N (Uruguay, Paraguay),

PAL-Nc (Argentina), PAL-60, NTSC-443, and SECAM. The Bt860 and Bt861 are

functionally identical except that the Bt861 can output the Macrovision 7.x anticopy

algorithm.

Multisource video is a key feature of the Bt860/861. Two general purpose ports

(P and OSD) allow synchronization with sources that can share clock and frame

timing control with the Bt860/861, such as digital video and graphic overlay content

generated by an MPEG video decoder. A third port (VID) is specifically configured to

interface with video decoders such as those in the Conexant VideoStream decoder

family. Any pair of these three ports can be synchronized and blended.

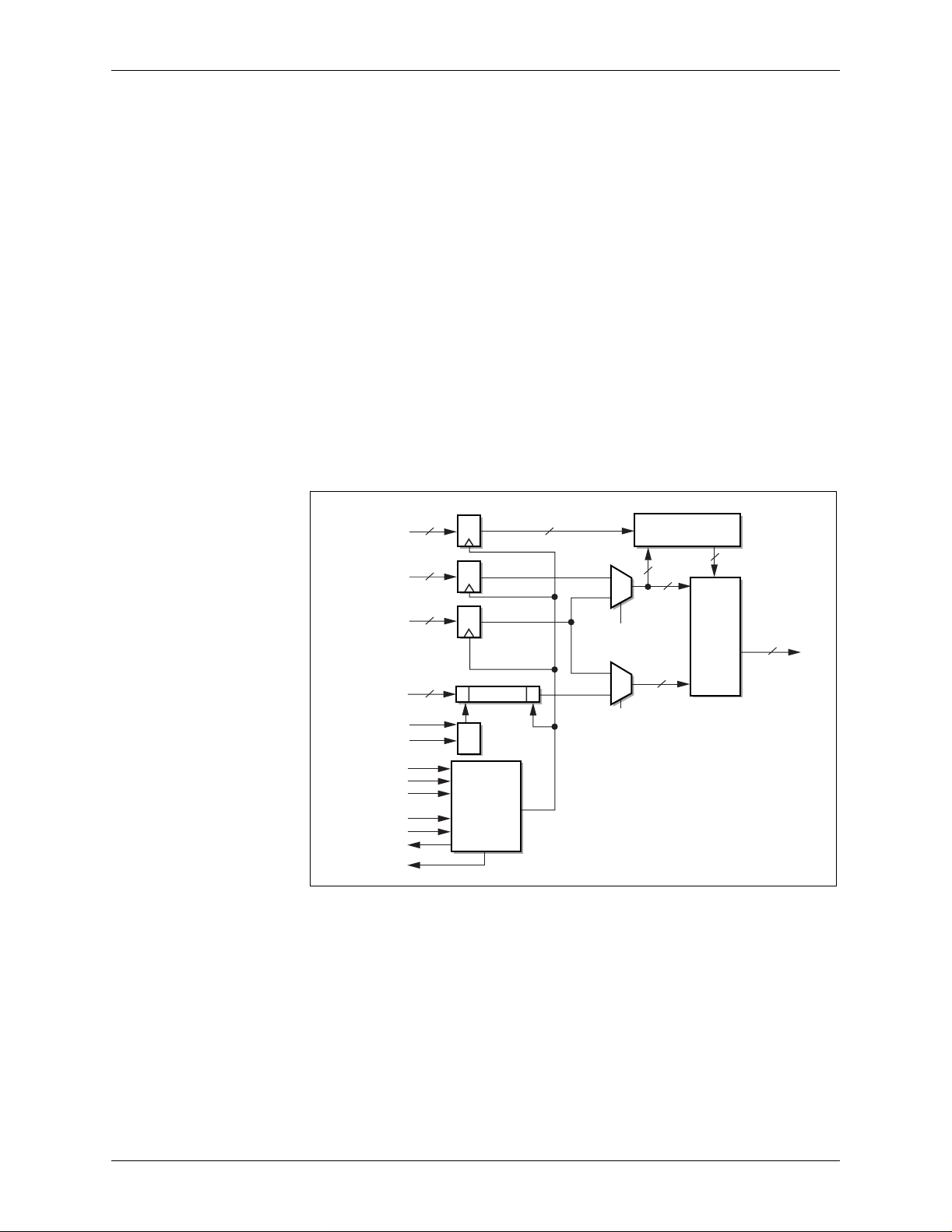

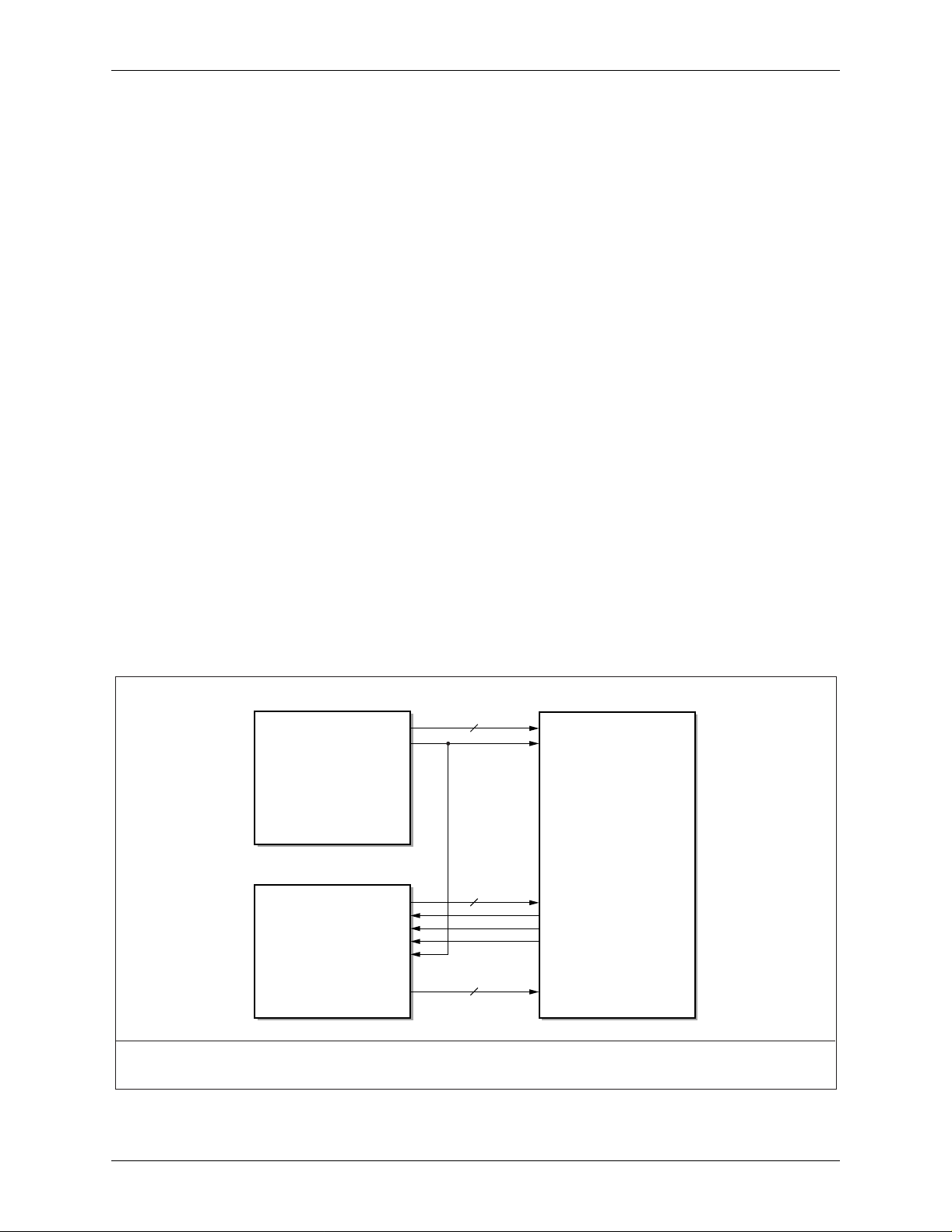

Functional Block Diagram

SICSID ALTADDRRESET* VREF

TTXDAT

TTXREQ

VID[7:0]

VIDCLK

VIDHACT

VIDVACT

VIDVALID

VIDFIELD

HSYNC*

VSYNC*

BLANK*

FIELD

ALPHA[1:0]

P[7:0]

OSD[7:0]

CLKO

XTI

XTO

CLKIN

Teletext

Encoder

Pixel

Sync.

and

Mixing

XTAL

OSC

1.3 MHz

LPF

PLL

Serial

Interface

2x

Upsampling

Clock

Generation

Mod.

and

Mixer

Internal

Internal

VREF

VREF

/

Color

Space

Convert

SECAM

FSADJ1

10

DAC

10

DAC

10

DAC

10

DAC

10

DAC

10

DAC

FSADJ2

COMP1

DAC A

DAC B

DAC C

DAC D

DAC E

DAC F

COMP2

Distinguishing Features

• Six 10-bit DACs with individual power

management

• Simultaneous output of YUV, S-Video,

and CVBS, or RGB (SCART), S-Video,

and CVBS

• Current drive output DACs for superior

video quality and reduced system cost

• Dynamic video load sensing for reduced

power operation

• Three sharpness filter options (1,2,3.5 dB

gain) and four reduction filter options

• Programmable adjustment of brightness,

contrast, color saturation, and hue

• Glueless interface with a video decoder

• Three 8-bit YCrCb 4:2:2 inputs for overlay

or blending

• ITU-R BT.656, ITU-R BT.601 digital video

input options

• NTSC-M, PAL (B,D,G,H,I), PAL-M, PAL-N,

NTSC-443, PAL-Nc, PAL-60 and SECAM

video output

• 2x upsampling and internal filtering for

reduced cost

• Master or slave video timing with

programmable HSYNC* delay

• Interlaced/noninterlaced operation

• Macrovision 7.x copy protection (Bt861)

• Closed Captioning and Extended Data

Services encoding

• Teletext encoding (WST system B)

• 400 kHz serial programming interface

• On-board voltage reference

• Reduced power modes

• Programmable luma delay (two channels)

• 3.3 V supply, 5 V-tolerant inputs

• Copy Generation Management System

(CGMS) support

• VARIS-II and Wide Screen Signalling

(WSS) multiple aspect ratio support

• Internal color bar generation

• Blue field generation

• 80-pin MQFP package

Related Products

• Bt852, Bt868/869, Bt864A/865A,

Bt866/867

• Bt835, Bt829A/B

Applications

• Digital cable television systems

• Satellite TV receivers (DBS/DVB/DSS)

• DVD players

• Video CD players

• Digital cameras

• PC add-on cards

• Video editing

Data Sheet D860DSA

July 27, 1999

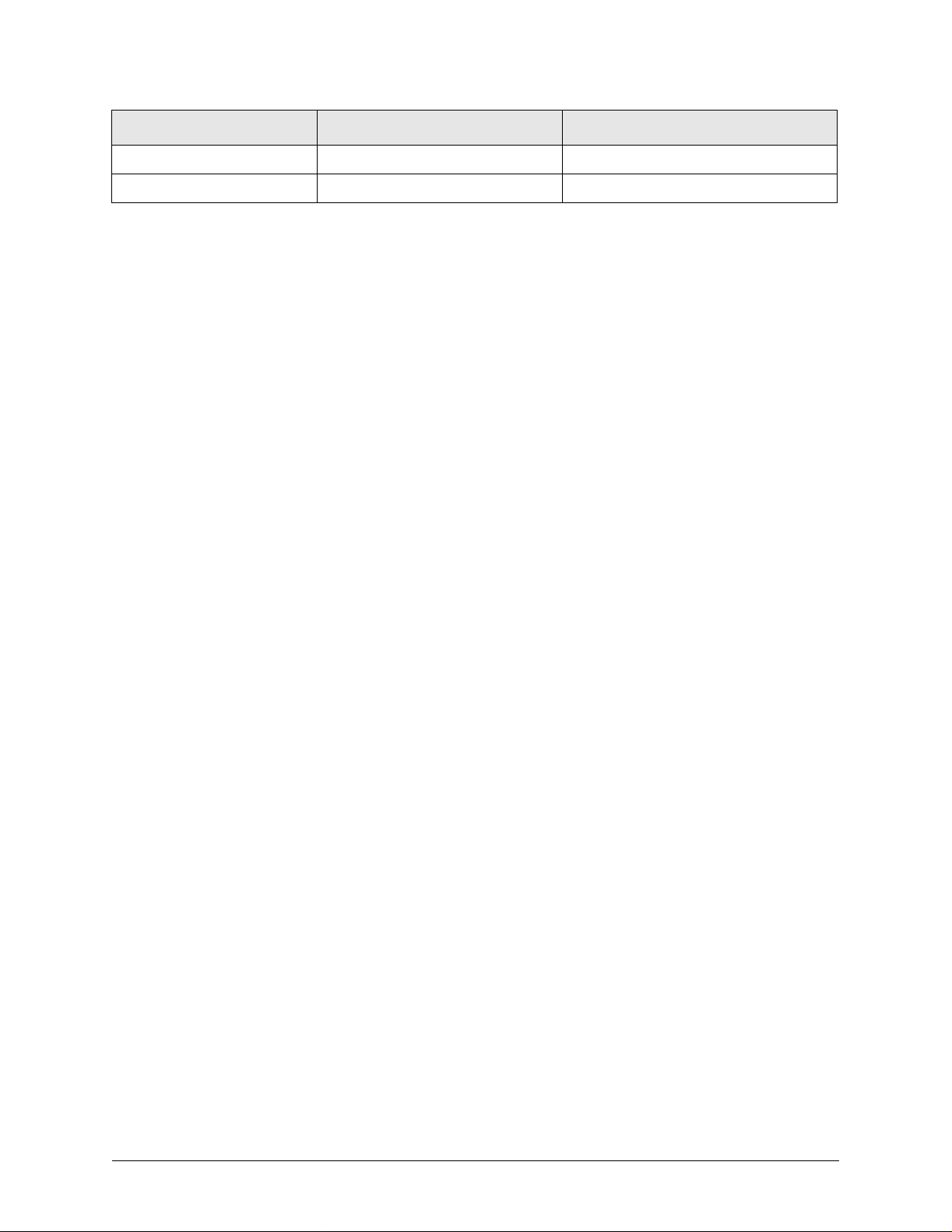

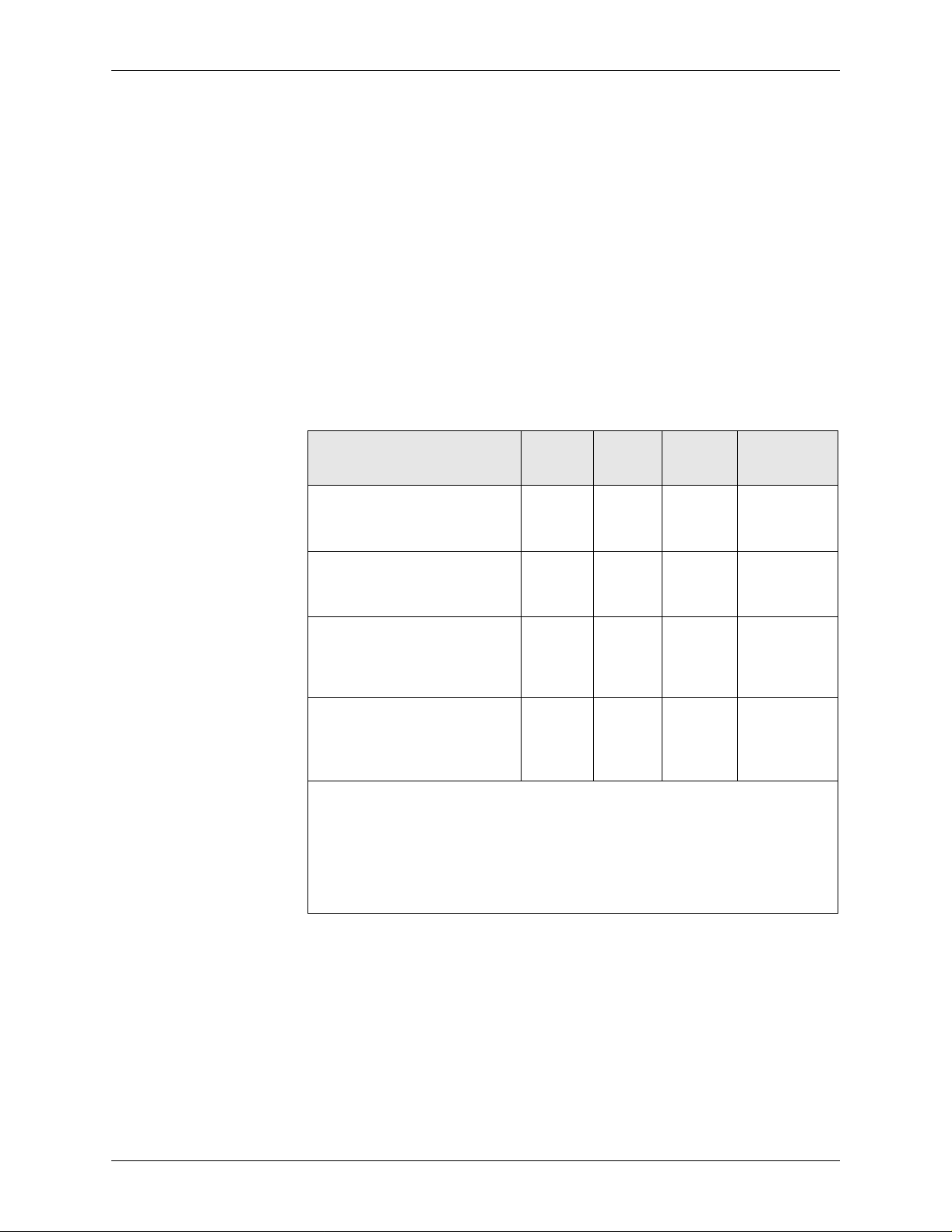

Ordering Information

Model Number Package Operating Temperature

Bt860KRF 80–Pin MQFP 0

Bt861KRF 80–Pin MQFP 0

C–70 °C

°

C–70 °C

°

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is

assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent rights of Conexant other than for circuitry embodied in Conexant

products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without

notice.

Conexant products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a

Conexant product can reasonably be expected to result in personal injury or death. Conexant customers using or selling Conexant

products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from

such improper use or sale.

Conexant and “What’s Next in Communications Technologies” are trademarks of Conexant Systems, Inc.

This device is protected by U .S . patent numbers 4,631,603, 4,577,216, and 4,819,098, and other intellectural property rights. The use

of Macrovision’s copy protection technology in the device must be authorized by Macrovison and is intended for home and other

limited pay-per-view uses only, unless otherwise authorized in writing by Macrovision. Reverse engineering or disassembly is

prohibited.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered

trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc.

Printed in U.S.A.

All Rights Reserved

Reader Response:

To improve the quality of our publications, we welcome your feedback. Please send comments or

suggestions via e-mail to Conexant Reader Response@conexant.com. Sorry, we can't answer your technical

questions at this address. Please contact your local Conexant sales office (listed on back page) or applications

engineer if you have technical questions.

D860DSA Conexant

Table of Contents

List of Figures

List of Tables

1.0 Functional Description

1.1 Pin Descriptions

1.2 Functional Overview

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

2.0 Inputs and Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1 Reset

2.2 Digital Video Ports

2.3 Configurations and Timing

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1.1 Initialization and Power-up Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.2.1 The P Port

2.2.2 The VID Port

2.2.3 The OSD Port

2.2.4 Overlay Modes and Alpha Blending

2.2.5 Alpha Pin Blending

2.2.6 Content-based Blending

2.3.1 ITU-R BT.601 Configurations and Timing

2.3.2 ITU-R BT.656 Timing

2.3.3 VID Port (Video Decoder Locked) Timing

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

2.4 Clock Selection

2.4.1 Crystal Inputs and the PLL

D860DSA Conexant iii

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Table of Contents Bt860/861

3.0 Digital Processing and Functionality

3.1 Video . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1 Video Standards

3.1.2 Analog Horizontal Sync

3.1.3 Analog and Digital Vertical Sync

3.1.4 Analog Video Blanking

3.1.5 Subcarrier and Burst Generation

3.1.6 Subcarrier Phasing (SC_H Phase)

3.1.7 Noninterlaced Operation

3.2 Effects. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

3.2.1 Chrominance Disable

3.2.2 Internal Filtering

3.2.3 Internal Colorbars, Blue Field, and Black Burst

3.2.4 Setup

3.2.5 YUV and RGB Multipliers

3.2.6 Programming Values to Comply with YPrPb and RGB

3.2.7 Programmable Video Adjustments Controls

3.2.8 Macrovision Encoding (Bt861 Only)

3.2.9 Outputs

3.2.10 Luminance Delay

3.2.11 Special SCART Signals

3.2.12 Output Connection Status

3.2.13 Output Filtering and SINX/X Compensation

3.2.14 Low Power Features

3.2.15 Teletext Operation of Bt860/861

3.2.16 Wide Screen Signaling

3.2.17 Copy Generation Management System

3.2.18 Closed Captioning and Extended Data Services

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

3.2.7.1 Hue Adjust

3.2.7.2 Brightness Adjust

3.2.7.3 Contrast Adjust

3.2.7.4 Saturation Adjust

3.2.7.5 Sharpness Adjust

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

3.2.15.1 Teletext Timing Mode 1

3.2.15.2 Teletext Timing Mode 2

3.2.15.3 General Teletext Operation

3.2.18.1 Closed Captioning Pass-through

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

Multiport YCrCb to NTSC/PAL /SECAM

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

. . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-20

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-30

iv Conexant D860DSA

Bt860/861 Table of Contents

Multiport YCrCb to NTSC/PAL /SECAM

4.0 Applications

4.1 PC Board Considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1.1 Component Placement

4.1.2 Power and Ground Planes

4.1.3 Device Decoupling

4.1.4 Power Supply Decoupling

4.1.5 COMP Decoupling

4.1.6 VREF Decoupling

4.1.7 VBIAS Decoupling

4.1.8 Digital Signal Interconnect

4.1.9 Analog Signal Interconnect

4.1.10 ESD and Latchup Considerations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

5.0 Serial Programming Interface and Registers

5.1 Serial Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1.1 Device Address

5.1.2 Writing Data

5.1.3 Reading Data

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2 Internal Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.2.1 Register Bit Map

5.3 Register Index

5.4 Register Detail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

6.0 Parametric Data and Specifications

6.1 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1.1 Electrical Parameters

6.2 Mechanical Drawing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

D860DSA Conexant v

Table of Contents Bt860/861

Multiport YCrCb to NTSC/PAL /SECAM

vi Conexant D860DSA

Bt860/861 List of Figures

Multiport YCrCb to NTSC/PAL /SECAM

List of Figures

Figure 1-1. Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

Figure 1-2. Detailed Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Figure 2-1. Pixel Latching and Blending Mechanism. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

Figure 2-2. Alpha Blending Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

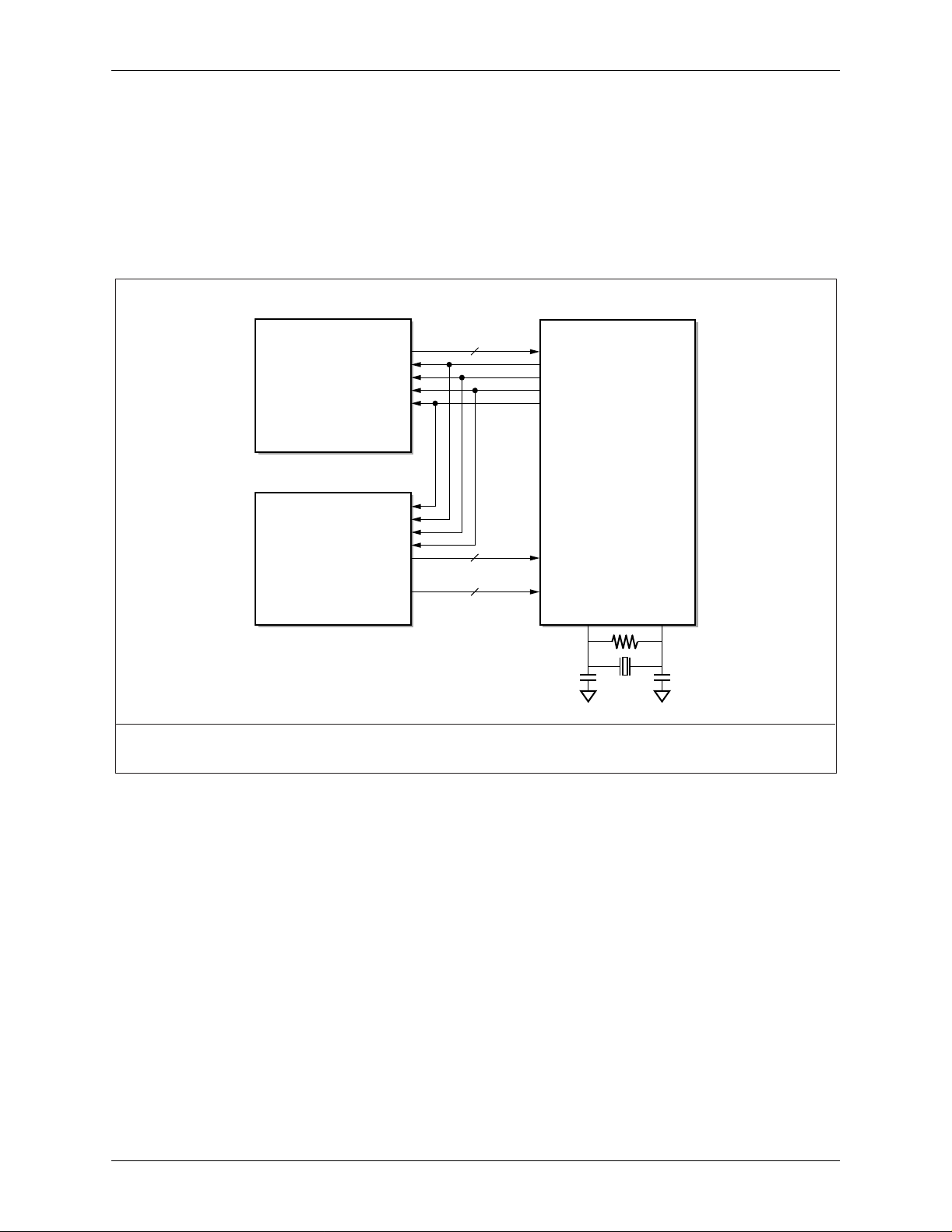

Figure 2-3. Timing Mode 1 Connection Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

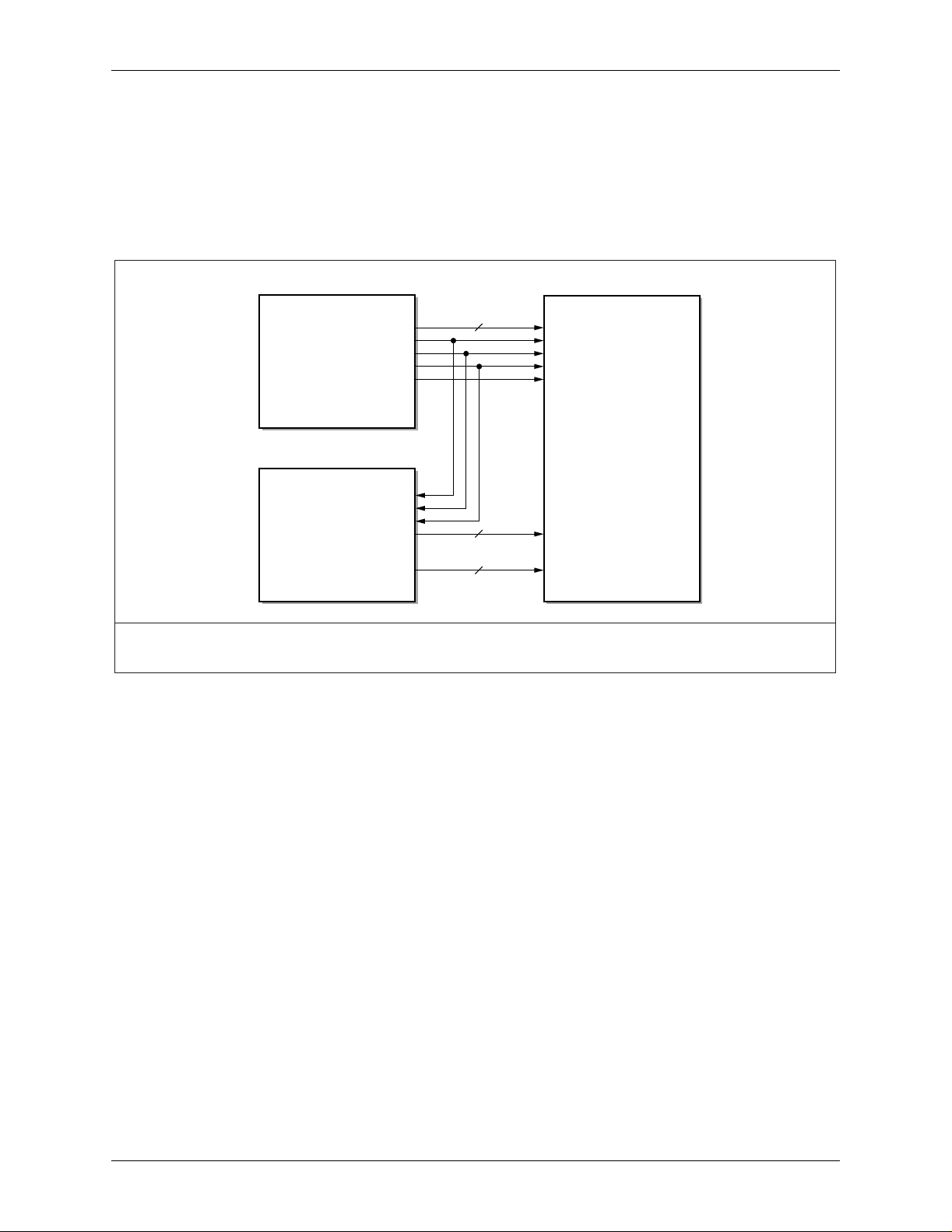

Figure 2-4. Timing Mode 2 Connection Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

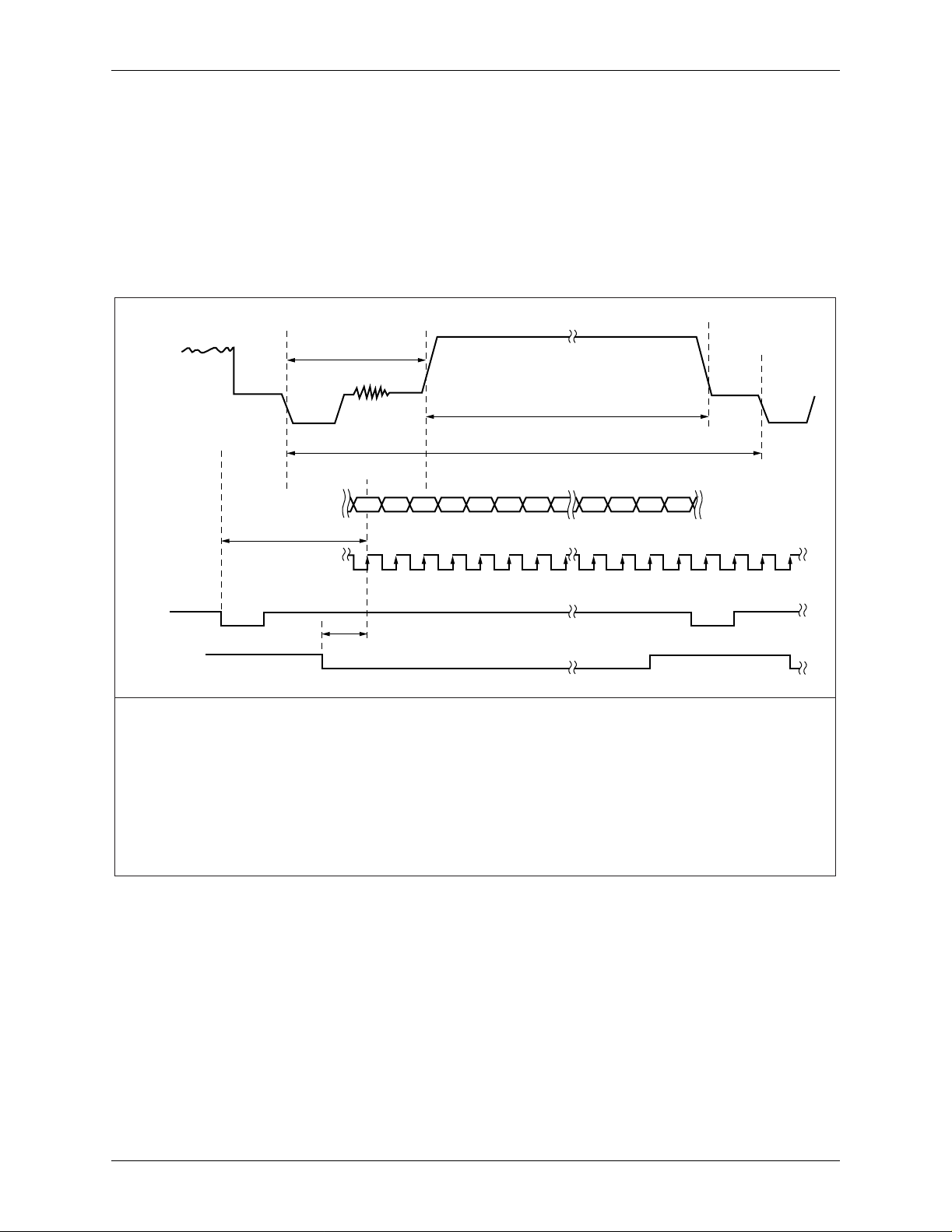

Figure 2-5. Pixel Timing for Timing Modes 1 and 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Figure 2-6. Timing Mode 3 and 4 Connection Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Figure 2-7. 625 Line ITU-R BT.656 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

Figure 2-8. 525 Line ITU-R BT.656 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

Figure 2-9. Video Decoder Connection Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

Figure 2-10. Timing and Clock Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

Figure 3-1. NTSC Vertical Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

Figure 3-2. PAL Vertical Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Figure 3-3. Luminance Upsampling Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

Figure 3-4. Luminance Upsampling Filter with Peaking and Reduction Options . . . . . . . . . . . . . . . . . 3-13

Figure 3-5. Close-Up of Luminance Upsampling Filter with Peaking and Reduction Options . . . . . . . 3-14

Figure 3-6. Luminance Reduction Filters Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Figure 3-7. Luminance Peaking Filter Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Figure 3-8. Chrominance Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Figure 3-9. Chrominance Wide Bandwidth Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Figure 3-10. SECAM High Frequency Pre-emphasis Filter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Figure 3-11. SECAM Low Frequency Pre-emphasis Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

Figure 3-12. YUV Video Format (Internal Colorbars). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

Figure 3-13. RGB Video Format (Internal Colorbars). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

Figure 3-14. Composite and S-Video Format (Internal Colorbars). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

Figure 3-15. SCART Function on ALTADDR Pin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-23

Figure 3-16. Teletext Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

Figure 3-17. P:Q Ratio Counter Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-26

Figure 3-18. WSS Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

Figure 3-19. CGMS Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

Figure 3-20. Closed Captioning or Extended Data Service Waveform (Null Sequence) . . . . . . . . . . . . . 3-30

Figure 4-1. Typical Connection Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Figure 4-2. Recommended Crystal Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Figure 5-1. Serial Programming Interface Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Figure 5-2. Serial Programming Interface Typical Write Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Figure 5-3. Serial Programming Interface Typical Read Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Figure 6-1. Pixel and Control Data Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Figure 6-2. 80 MQFP Package Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

D860DSA Conexant vii

List of Figures Bt860/861

Multiport YCrCb to NTSC/PAL /SECAM

viii Conexant D860DSA

Bt860/861 List of Tables

Multiport YCrCb to NTSC/PAL /SECAM

List of Tables

Table 1-1. Pin Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Table 2-1. Alpha Blending Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Table 2-2. Configurable Timing States. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Table 3-1. Target Video Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Table 3-2. Register Programming Values for NTSC and PAL Video Standards (ITU-R BT.601) . . . . . . . 3-4

Table 3-3. Register Programming Values for NTSC and PAL Video Standards (Square Pixel). . . . . . . . 3-6

Table 3-4. Register Programming Values for SECAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

Table 3-5. 100/0/75/0 Colorbars as Described in EIA-770.1. EIA-770.1. . . . . . . . . . . . . . . . . . . . . . . . 3-16

Table 3-6. 100/0/75/0 Colorbars for a 625-Line System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

Table 3-7. Composite and Luminance Amplitude. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

Table 3-8. Composite and Chrominance Magnitude. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

Table 3-9. DAC Format Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

Table 3-10. P:Q Ratio Counter Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

Table 3-11. Teletext Line Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

Table 3-12. Closed Captioning and Extended Data Services Control Bits. . . . . . . . . . . . . . . . . . . . . . . . 3-29

Table 4-1. Typical Parts List. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Table 5-1. Serial Address Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Table 5-2. Register Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Table 5-3. Register Index. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

Table 6-1. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

Table 6-2. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Table 6-3. AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

Table 6-4. Video Quality Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

D860DSA Conexant ix

List of Tables Bt860/861

Multiport YCrCb to NTSC/PAL /SECAM

x Conexant D860DSA

1

1.0 Functional Description

1.1 Pin Descriptions

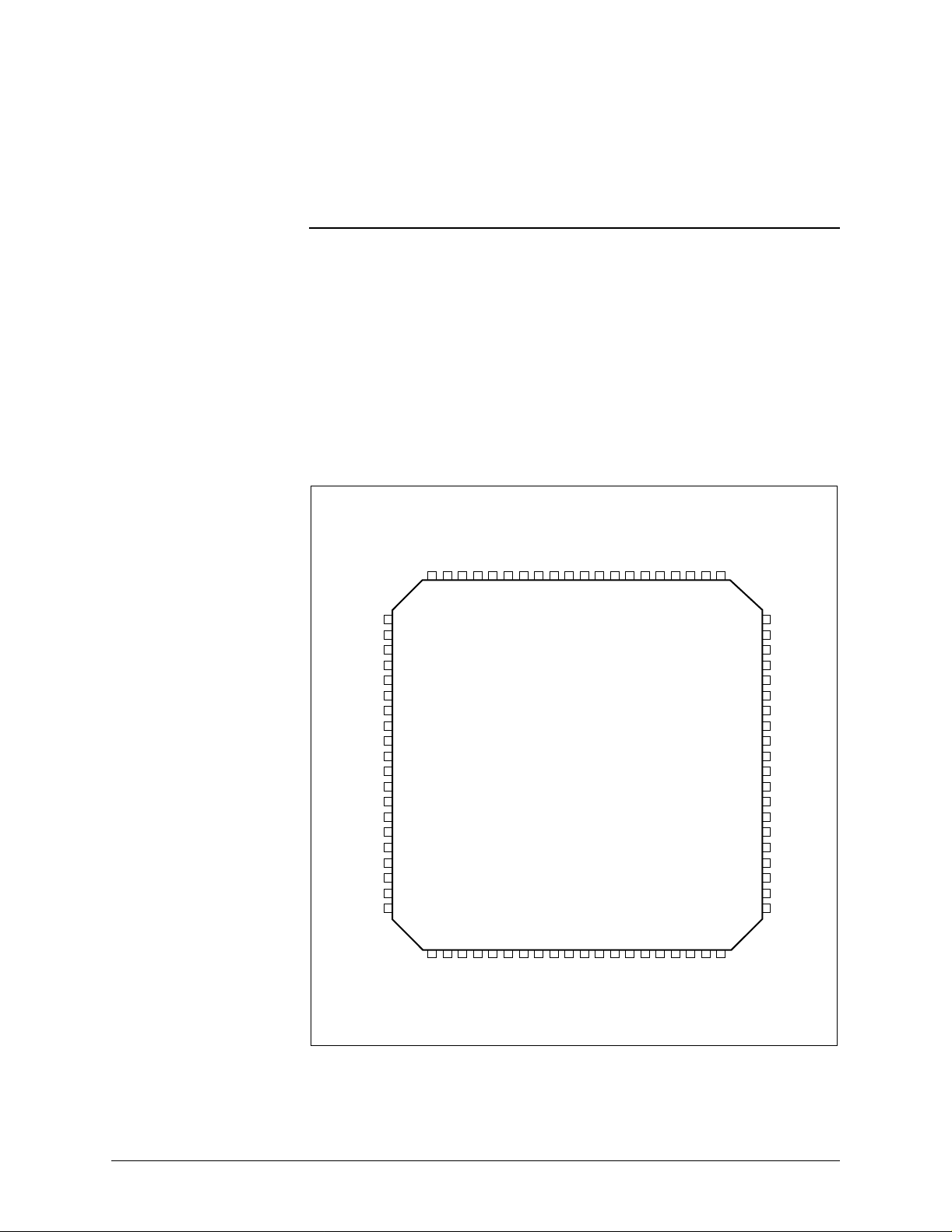

Figure 1-1. Pinout Diagram

GND

PGND

XTI

XTO

VPLL

CLKO

CLKIN

VIDFIELD

TTXREQ

TTXDAT

SID

SIC

GND

VDD

VID0

VID1

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

1

VID2

2

VID3

3

VID4

VID5

4

VID6

5

VID7

6

VDD

7

GND

P0

P1

P2

P3

GND

P4

P5

8

9

10

11

12

13

14

15

16

17

18

19

20

80-pin MQFP

VIDCLK

VIDVALID

VIDVACT

VIDHACT

VDDMAX

VDD

64

RESET*

63

GND

ALTADDR

61

62

AGND

60

DACA

59

DACB

58

DACC

57

VBIAS1

56

VAA

55

COMP1

54

FSADJ1

53

VAA

52

AGND

51

AGND

50

VREF

49

FJADJ2

48

COMP2

47

VAA

46

VBIAS2

45

DACD

44

DACE

43

DACF

42

41

AGND

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

P7

P6

BLANK*

VSYNC*

FIELD

HSYNC*

GND

VDD

ALPHA1

ALPHA0

OSD1

OSD0

OSD3

OSD2

OSD5

OSD4

GND

VDD

OSD6

OSD7

861_027

D860DSA Conexant 1-1

1.0 Functional Description Bt860/861

1.1 Pin Descriptions

Multiport YCrCb to NTSC/PAL /SECAM

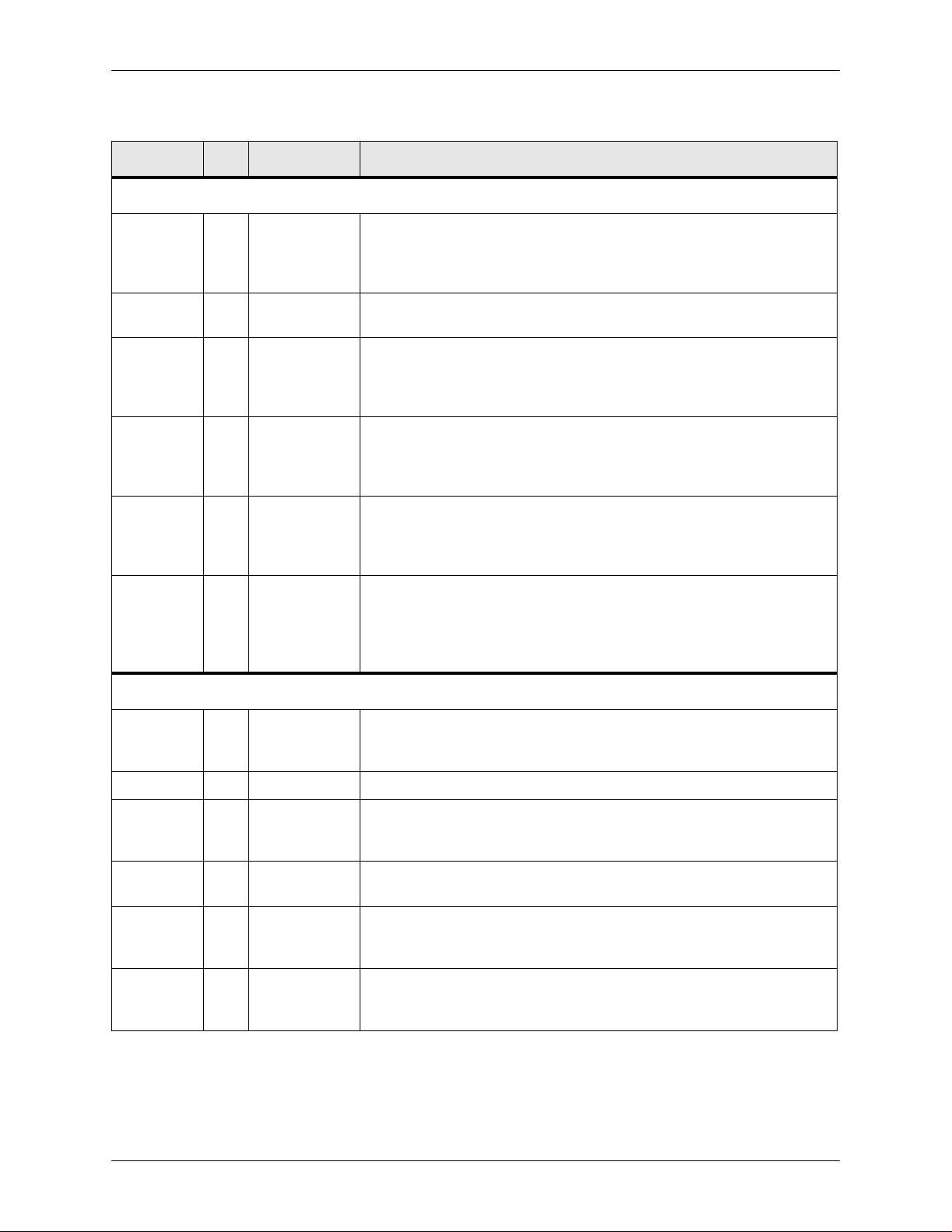

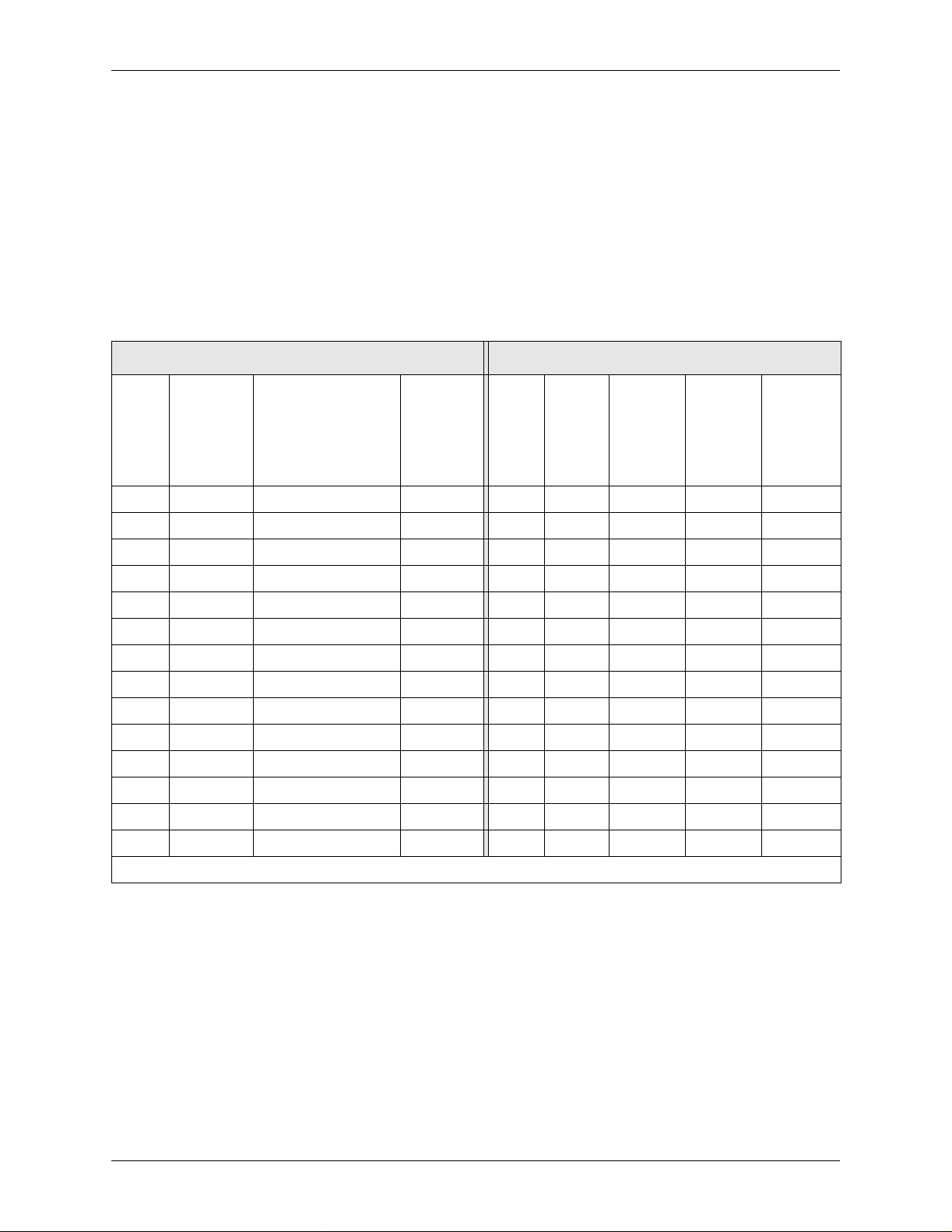

Table 1-1. Pin Assignments (1 of 3)

Pin Name I/O Pin # Description

PRIMARY VIDEO PORT

P[7:0] I 22-19, 16-13 Primary video input port (TTL compatible)

(1)

. Accepts pixel data in 8-bit YCrCb 4:2:2

format in either ITU-R BT.601 or ITU-R BT.656 control formats. A higher index

corresponds to a greater bit significance. By default, data is latched on the rising

edge of the system clock

(2)

.

CLKO O 70 2x pixel clock output. The clock generated by the PLL is produced at this pin when

register bit CLKO_DIS = 0.

VSYNC* I/O 24 Vertical sync input/output (TTL compatible). As an output (master mode operation),

VSYNC* follows the rising edge of the system clock. As an input (slave mode

operation), VSYNC* is, by default, registered on the rising edge of the system

(2)

. The VSYNCI register bit controls the polarity of this signal.

clock

HSYNC* I/O 25 Horizontal sync input/output (TTL compatible). As an output (master mode

operation), HSYNC* follows the rising edge of the system clock. As an input (slave

mode operation), HSYNC* is, by default, registered on the rising edge of the system

(2)

. The HSYNCI register bit controls the polarity of this signal.

clock

BLANK* I 23 Composite blanking control input (TTL compatible). By default, BLANK* is

registered on the rising edge of the system clock

(2)

. The video data inputs are

ignored while BLANK* is a logical 0. The BLANKI register bit controls the polarity of

this signal.

FIELD O 26 Field control output (TTL compatible). FIELD transitions after the rising edge of the

system clock, two clock cycles following a falling HSYNC*. The FIELDI register bit

controls the polarity of this signal. The state of this pin at power-up determines the

default state of the PCLK_SEL register bit and the initial clock source. If not

externally loaded, this pin will be pulled low with an internal pull-down resistor.

SECONDARY VIDEO PORT

VID[7:0] I 6-1, 80-79 Secondary video input port (TTL compatible). Accepts pixel data in 8-bit YCrCb

4:2:2 format. A higher index corresponds to a greater bit significance. By default,

data on the VID port is latched by the rising edge of VIDCLK

(1)

VIDCLK I 9 Pixel clock for secondary video input port

VIDHACT I 12 Horizontal active display region. A logical 1 indicates data on VID[7:0] is in the

horizontal display region.

The VIDHACTI register bit controls the polarity of this

.

signal. By default, data on VIDHACT is latched by the rising edge of VIDCLK

VIDVACT I 11 Vertical active display region. The VIDVACTI register bit controls the polarity of this

signal. By default, data on VIDVACT is latched by the rising edge of VIDCLK

(1) (3)

.

(1) (3)

.

(1) (3)

.

VIDFIELD I 72 Field indicator for video input port. A logical 1 indicates data is from an even field.

The VIDFIELDI register bit controls the polarity of this signal. By default, data on

VIDFIELD is latched by the rising edge of VIDCLK

(1) (3)

.

VIDVALID I 10 Video data valid qualifier. A logical 1 indicates data on VID[7:0] is valid data. The

VIDVALIDI register bit controls the polarity of this signal. By default, data on

VIDVALID is latched by the rising edge of VIDCLK

(1) (3)

.

1-2 Conexant D860DSA

Bt860/861 1.0 Functional Description

Multiport YCrCb to NTSC/PAL /SECAM

1.1 Pin Descriptions

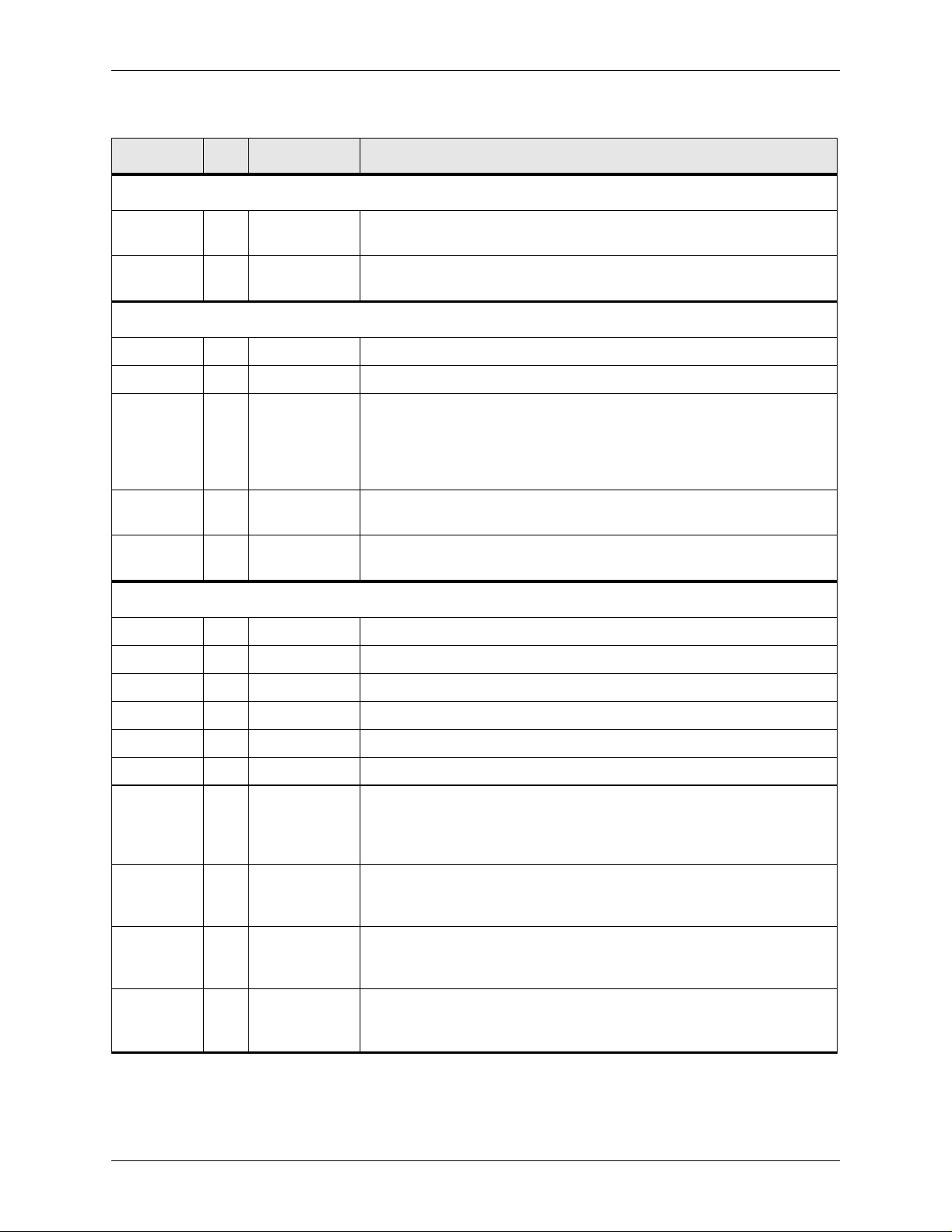

Table 1-1. Pin Assignments (2 of 3)

Pin Name I/O Pin # Description

GRAPHIC AND BLENDING PINS

OSD[7:0] I 40-39, 36-31 Dedicated graphic overlay port (TTL compatible.) Accepts pixel data in 8-bit YCrCb

4:2:2 format. Data is latched on the rising edge of the system clock

ALPHA[1:0] I 30-29 Alpha blend pins. Provides for 1-, 2-, or 4-bit external blend selection between video

and graphic overlay data. Data is latched on the rising edge of the system clock

(1) (2)

.

TELETEXT AND SERIAL CONTROL INTERFACE

TTXDAT I 74 Teletext data input (TTL compatible)

TTXREQ O 73 Teletext request output (TTL compatible).

ALTADDR I/O 62 Alternate slave address input (TTL compatible). This pin is sampled immediately

following a power-up or pin reset. A logical 1 corresponds to write address of 0x88

and a read address of 0x89, while a logical 0 corresponds to a write address of 0x8A

and a read address of 0x8B. See Chapter 5.0, for more detail. This pin also provides

special SCART signals when register field SCART_SEL≠00.

SID I/O 75 Serial programming interface data input/output (TTL compatible). Data is written to

and read from the device via this serial bus.

(1)

.

(1) (2)

.

SIC I 76 Serial programming interface clock input (TTL compatible). The maximum clock rate is

400 kHz.

ANALOG VIDEO

DACA O 59 DAC A output. See Table 3-9.

DACB O 58 DAC B output. See Table 3-9.

DACC O 57 DAC C output. See Table 3-9.

DACD O 44 DAC D output. See Table 3-9.

DACE O 43 DAC E output. See Table 3-9.

DACF O 42 DAC F output. See Table 3-9.

FSADJ1

FSADJ2

VREF O 49 Voltage reference pin. A 1.0 µF ceramic capacitor must be used to decouple this pin

COMP1

COMP2

I53

48

O54

47

Full-scale adjust control pin. Resistors RSET1 and RSET2 connected between these

pins and AGND control the full-scale output current of the DACs. For standard

operation, use the nominal values shown under Recommended Operating

Conditions. FSADJ1 controls DACs A/B/C and FSADJ2 controls DACs D/E/F.

to AGND. The capacitor must be as close to the device as possible to keep lead

lengths to an absolute minimum.

Compensation pin. A 0.1 µF ceramic capacitor must be used to decouple this pin to

VAA. The capacitor must be as close to the device as possible to keep lead lengths

to an absolute minimum.

VBIAS1

VBIAS2

O56

45

DAC bias voltage. Use a 0.1 µF ceramic capacitor to bypass this pin to AGND; the

capacitor must be as close to the device as possible to keep lead lengths to an

absolute minimum.

D860DSA Conexant 1-3

1.0 Functional Description Bt860/861

1.1 Pin Descriptions

Multiport YCrCb to NTSC/PAL /SECAM

Table 1-1. Pin Assignments (3 of 3)

Pin Name I/O Pin # Description

SYSTEM PINS

CLKIN I 71 2x pixel clock input (TTL compatible).

RESET* I 63 Reset control input (TTL compatible). Setting to zero resets video timing

(horizontal, vertical, subcarrier counters to the start of VSYNC of first field), the

serial control interface, and all registers. RESET* must be a logical 1 for normal

operation. Holding this pin low for 50 clocks or more will ensure that all functions

are properly reset.

XTI I 67 Crystal input for PLL.

XTO O 68 Crystal output for PLL.

POWER AND GROUND

VAA — 55, 46, 52 Analog power. See Section 4.1 of this document.

VDD — 7, 28, 38, 64, 78 Digital power. See Section 4.1 of this document.

AGND — 41, 50, 51, 60 Analog ground. See Section 4.1 of this document.

GND — 8, 17, 27, 37,

Digital ground. See Section 4.1 of this document.

61, 65, 77

VPLL — 69 Dedicated power supply for PLL.

PGND — 66 Dedicated ground for PLL.

VDDMAX I 18 This pin must be tied to the maximum digital input value. Use 3.3 V if only 3.3 V

inputs are used, and 5 V if 3.3/5 V inputs are used.

NOTE(S):

(1)

If these inputs are not used, they should be connected to GND.

(2)

These input are normally sampled on the rising edge of the system clock, but can be sampled on the falling edge by setting

register bit PCLK_EDGE = 1.

(3)

These inputs are normally sampled on the rising edge of VIDCLK, but can be sampled on the falling edge by setting register bit

VIDCLK_EDGE = 1.

1-4 Conexant D860DSA

Bt860/861 1.0 Functional Description

Multiport YCrCb to NTSC/PAL /SECAM

1.2 Functional Overview

The Bt860/861 is a highly programmable 3.3 V multiport digital video encoder

with pixel synchronization and per-pixel blending capabilities. It is equipped with

three 8-bit YCrCb data ports that allow a variety of video and graphic overlay

configurations useful in video set top box applications.

The three 8-bit YCrCb data ports allow two video streams and one

alpha-blended overlay stream. For switching between video sources (such as a

video decoder and an MPEG source), while providing a common OSD interface

using the part’s overlay and alpha capabilities.

The Bt860/861's VID port uses a PLL and FIFO to allow direct interfacing

with asynchronous video sources, such as the Bt835 video decoder.

In slave mode, the Bt860/861 can be configured to accept either

ITU-R BT.656-compliant timing (EAV and SAV codes) or ITU-R BT.601 data

timing (HSYNC* and VSYNC* signals). The Bt860/861 can also act as timing

master, producing ITU-R BT.601 timing.

The Bt860/861 supports worldwide video standards, including:

• NTSC-M (N. America, Taiwan, Japan)

• PAL-B, D, G, H, I (Europe, Asia)

• PAL-M (Brazil)

• PAL-N (Uruguay, Paraguay)

• PAL-Nc (Argentina)

• PAL-60, NTSC-443

•SECAM

The Bt860/861 has six 10-bit current-out video DACs, specifically designed

for video systems requiring the generation of high quality composite, Y/C

(S-Video), and simultaneous component YUV or RGB (SCART) video signals.

Two of the composite output signals can be programmed with a 0–7 clock

luminance delay. The connection status of each DAC can be dynamically

monitored through the serial programming interface.

The Bt860/861 has several low power options, including sleep mode (only the

serial programming interface and PLL are operational), individual DAC disable,

PLL disable, and 3.3 V operation. The 3.3 V digital inputs can be configured to

be 5 V-tolerant.

The luminance upsampling filter is enhanced to provide a narrow transition

region and a low stopband. Programmable luminance sharpness filters provide

0,1, 2, and 3.5 dB peaking options at higher video frequencies, and four reduction

filters are added for smoothed step response. To reduce the complexity of the

required reconstruction filter, 2x upsampling is implemented.

The Bt860/861 can produce internally generated colorbars and blue field

signals.

A 400 kHz serial programming interface (I

system programming.

The Bt860/861 provides support for Closed Captioning (CC) and Extended

Data Services (XDS), Teletext (WST system B), Copy Generation Management

System (CGMS), VARIS-II, and Wide Screen Signaling (WSS).

The Bt860 and Bt861 are functionally identical except that the Bt861 can

output the Macrovision 7.x anticopy algorithm.

1.2 Functional Overview

2

C-compatible) is provided for fast

D860DSA Conexant 1-5

1.0 Functional Description Bt860/861

1.2 Functional Overview

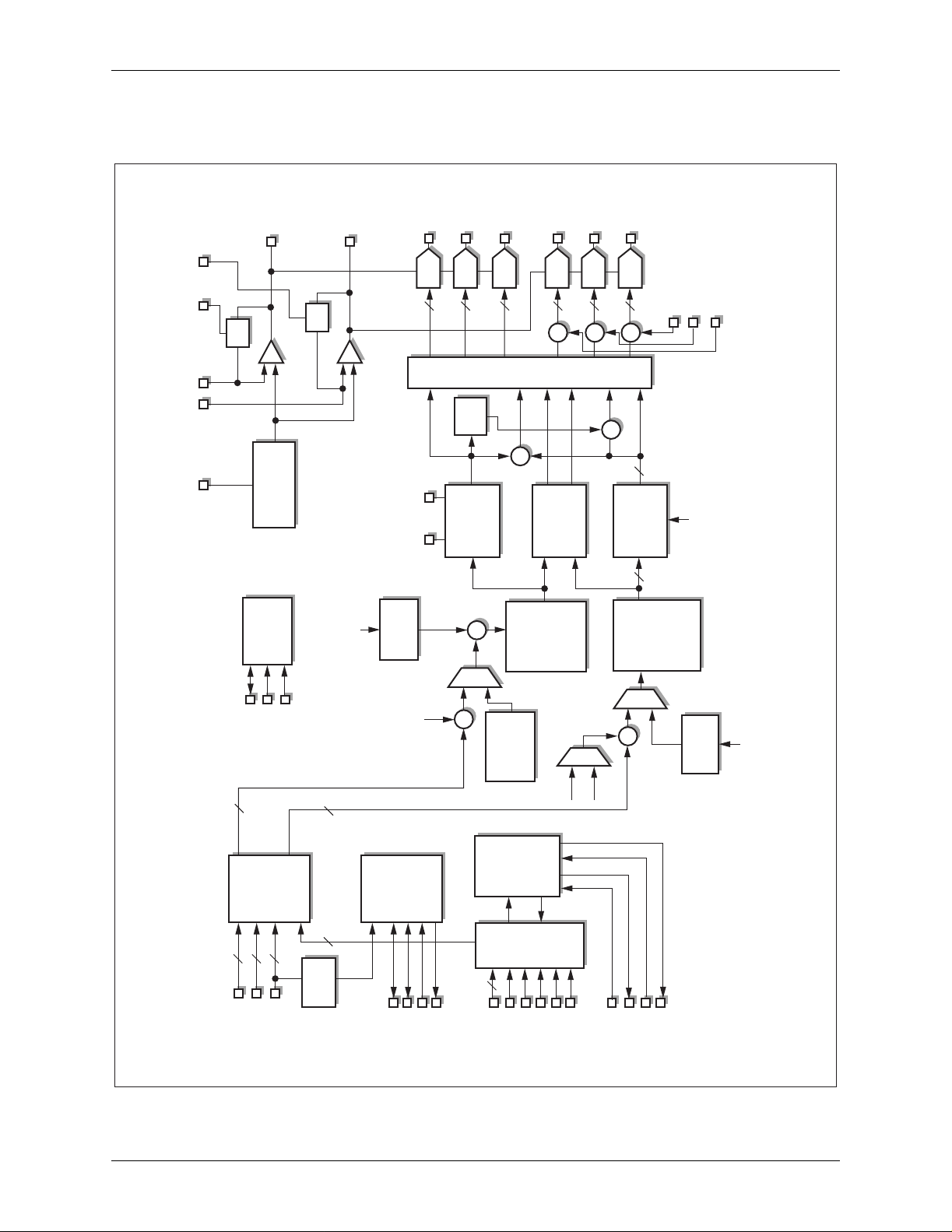

Figure 1-2. Detailed Block Diagram

COMP1

FB

FSADJ1

FSADJ2 VBIAS1 VBIAS2

VREF

Reference

Internal Voltage

FB

COMP2

Multiport YCrCb to NTSC/PAL /SECAM

DAC B

DAC A

DAC

10

Y

DAC

10

Luma

DAC C

DAC

10

CVBS

Delay

Out

Mux

U/V

DAC D

DAC

10

X

RGB

+

TTXREQTTXDAT

Color

Teletext

and CGMS

Space

Convert

DAC E

DAC

10

X

DLY

CVBS

+

10

DAC F

DAC

X

C

10

Modulator,

Mixer and

M_COMP_F

M_COMP_E

HUE_OFF

SECAM Filt.

M_COMP_D

Serial

Control

SIC

SID

10

Y

Alpha

8

2

8

OSD[7:0]

ALPHA[1:0]

Interface

ALTADDR

CRCB

Mixing

P[7:0]

10

8

656

Decoder

Sync

SYNC_AMP

Video

HSYNC*

Processor

M_Y

Timing

Control

FIELD

BLANK*

VSYNC*

9

+

X

Closed

8

VID[7:0]

Luminance

2x Upsample

Captioning,

Macrovision

Clock

PLL and

Generation

and

FIFO

Locking

VIDCLK

VIDVALID

and

Cross Color

M_CR

Control

VIDVACT

VIDHACT

Peaking Filt.

M_CB

VIDFIELD

and 2X

1.3 MHz LPF

X

XTI

CLKO

CLKIN

Matrix

Upsample/

Multiplication

Burst

XTO

Processor

BST_AMP

861_028

1-6 Conexant D860DSA

2

2.0 Inputs and Timing

2.1 Reset

The Bt860/Bt861 has the following reset methods:

• power-up reset

• RESET* pin reset

• software reset register bit

Power-up reset occurs when the part is powered-up. A pin reset occurs when

the RESET* pin is held low. (It is recommended that the pin be held low for a

minimum of 50 system clock cycles.) Both power-up and pin reset cause the

initialization of all chip functions, including video timing and serial programming

registers.

Writing a 1 to register bit SRESET (1B[7]) resets all serial programing

registers to their default states, listed in Section 5.0.

2.1.1 Initialization and Power-up Configuration

At power-up all registers reset to their initial values (see Section 5.0).

The state of the FIELD pin at power-up (or pin reset) determines the default

state of the PCLK_SEL register bit and the initial clock source. If the FIELD pin

is pulled high, the initial clock source is the CLKIN pin; if the FIELD pin is

pulled low, the initial clock source is from the PLL and requires a crystal at the

XTI and XTO pins. If not loaded, the FIELD pin is pulled low with the pin’s

internal pull-down resistor.

The power-up configuration is interlaced NTSC-M, 27 MHz black burst

video, as listed in the default values of the register bit map.

To enable active video, black burst video must be turned off by setting

NOTE:

register bit EACTIVE (1D[1]) to 1. Other video configurations must be

programmed using the part’s serial programming interface registers.

D860DSA Conexant 2-1

2.0 Inputs and Timing Bt860/861

2.2 Digital Video Ports

Multiport YCrCb to NTSC/PAL /SECAM

2.2 Digital Video Ports

Internally, data to the Bt860/861 is treated as either video, overlay, or alpha data.

Video data is the primary visual program content, while overlay data is used for

informational or navigational content displayed over the visual program. Alpha

data controls the pixel blending of the video and overlay content. Sufficient

flexibility exists in the Bt860/861 to allow for a variety of source and blending

configurations and interesting visual effects.

Video data is supplied by either the P (Primary Video) port, or the VID

(Secondary Video) port. Overlay data can be supplied by either the P port or the

OSD (On Screen Display) port. Alpha data can be supplied by the ALPHA port,

or embedded in the two LSBs of the overlay luminance data. Figure 2-1

illustrates the pixel latching and blending mechanism.

Figure 2-1. Pixel Latching and Blending Mechanism

ALPHA

OSD

2

8

8

P

2

OVERLAY_SEL

2

Overlay

Stream

Blend

Detection

8

4

Pixel

Blender

8

VID

VIDCLK

VIDVALID

VIDHACT

VIDVACT

VIDFIELD

CLKIN

XTI

XTO

CLKO

8

VIDEO_SEL

PLL

and

Clock

Logic

8

Video

Stream

861_042

2-2 Conexant D860DSA

Bt860/861 2.0 Inputs and Timing

Multiport YCrCb to NTSC/PAL /SECAM

2.2.1 The P Port

The P port can accept video data from a variety of digital video sources. It is

designed specifically to interface directly with commercial MPEG video decoders

and D1 digital video sources. The P port supports both ITU-R BT.601 timing

(HSYNC* and VSYNC* signals), and ITU-R BT.656 timing (SAV and EAV

codes).

Data on the P[7:0] pins can be treated as either video or overlay data,

controlled by the VIDEO_SEL (1A[3]) and OVRLAY_SEL (1A[4]) register bits

(see Figure 2-1). Data on this port must be presented in 8-bit YCrCb 4:2:2 digital

video format. The P[7:0] pins are latched using the system clock as configured

using register bits PCLK_SEL (19[7]) and PCLK_EDGE (19[1]).

2.2.2 The VID Port

The VID port is specially configured for broadcast video sources, such as from a

television tuner or local cable system. It can accept a 27 MHz YCrCb 4:2:2 video

stream at the same pixel rate as the other ports, or it can accommodate alternate

clock rates, such as the 8xF

decoders. Since the time base for these sources is external to the system and

therefore asynchronous to the local pixel clock, the Bt860/861 provides a

mechanism that synchronizes these two domains. When using the VID port in

locking mode, the Bt860/861 immediately synchronizes its vertical timing to the

vertical timing presented on the VIDVACT pin, and gradually adjusts its

horizontal timing and clock rate to further synchronize with the VID port.

VIDCLK latches the incoming data into a FIFO, and data is extracted at the

appropriate pixel rate for internal processing.

The average active horizontal pixel count must be equal to the value

programmed into the HACTIVE register field. For example, the Bt835 generates

pixels at a rate of 14.32 Mpix/s when used for NTSC video capture, but the actual

valid pixel count per line is determined by the video mode required. For support

of 27 MHz streams, 720 valid pixels will be delivered per line. This configuration

is compatible with other video devices connected to the Bt860/861 and running

with a continuous pixel rate of 13.5 Mpix/s. The Bt860/861 will generate the

necessary video timing and pixel clock to act as master for the other video device.

The VID port can be configured as the video source by setting register bit

VIDEO_SEL (1A[3]) to 1. Data on this port must be presented in 8-bit YCrCb

4:2:2 digital video format.

2.2 Digital Video Ports

clock rate used by the Bt835 family of video

sc

2.2.3 The OSD Port

The OSD port is functionally very similar to the P port, except that it cannot decode

ITU-R BT.656 timing. As the overlay source, this port can be mixed with the video

stream using one of the alpha-mixing modes described in Section 2.2.5. While

intended as an overlay source, the OSD port can be configured to be the sole image

content by using the appropriate blend programming.

The overlay source is selected by setting register bit OVRLAY_SEL (1A[4])

to 1. Data on this port must be presented in 8-bit YCrCb 4:2:2 digital video

format. The OSD[7:0] pins are latched using the system clock as configured by

register bits PCLK_SEL (19[7]) and PCLK_EDGE (19[1]).

D860DSA Conexant 2-3

2.0 Inputs and Timing Bt860/861

2.2 Digital Video Ports

Multiport YCrCb to NTSC/PAL /SECAM

2.2.4 Overlay Modes and Alpha Blending

The Bt860/861 can be configured to display only a single video stream, or to mix

any combination of two data ports (P, VID, and OSD). Programming register field

ALPHAMODE (1A[6:5]) to 00 and register bit BLENDMODE (1A[7]) to 1

selects the internal video bus as the sole source of data, regardless of the alpha

source. In this mode, either the VID port or the P port can be used as the video

source, which is selected by register bit VIDEO_SEL (1A[3]). Other

combinations of the ALPHAMODE and BLENDMODE programming will allow

blending of the video and overlay buses. Table 2-1 lists all valid input modes.

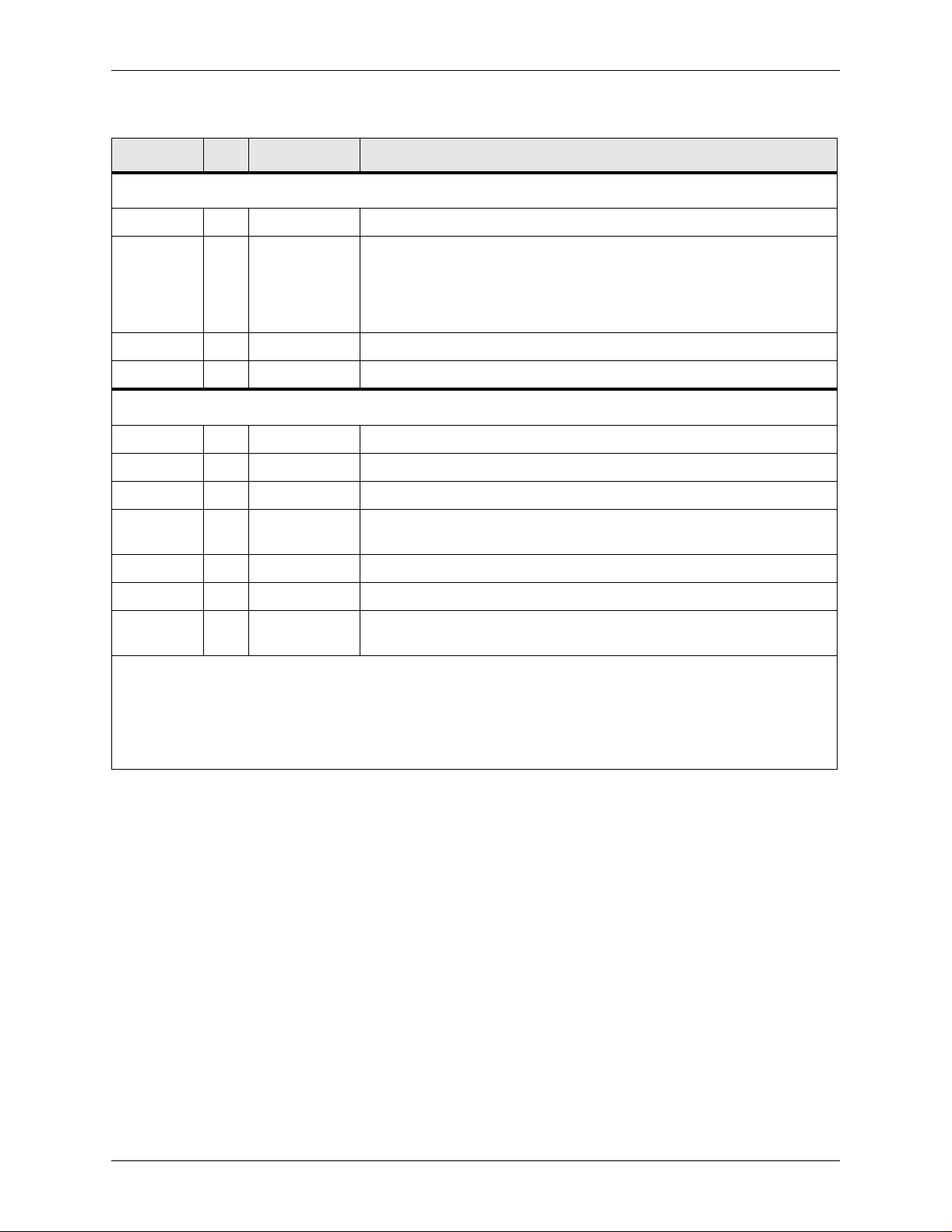

Table 2-1. Alpha Blending Configurations

Configuration Programming

Use

Video source

VID None None None 100 1 X No

VID P ALPHA[1:0] 1 bit

VID P ALPHA[1:0] 2 bit

VID P ALPHA[1:0] 4 bit

VID P P LSBs 2 bit

VID OSD ALPHA[1:0] 1 bit

VID OSD ALPHA[1:0] 2 bit

VID OSD ALPHA[1:0] 4 bit

VID OSD OSD LSBs 2 bit

P None None None

P OSD ALPHA[1:0] 1 bit

P OSD ALPHA[1:0] 2 bit

P OSD ALPHA[1:0] 4 bit

P OSD OSD LSBs 2 bit

NOTE(S):

Overlay source

X or XX = Don’t care.

Alpha Source

Blending depth

BLENDMODE

101 1 0 Yes

110 1 0 Yes

111 1 0 No

0XX 1 0 Yes

101 1 1 Yes

110 1 1 Yes

111 1 1 No

0XX 1 1 Yes

100 0 X No

101 0 1 Yes

110 0 1 Yes

111 0 1 No

0XX 0 1 Yes

ALPHAMODE

VIDEO_SEL

OVERLAY_SEL

ALPHA_LUT_X

Data from the overlay source may be applied with varying levels of

transparency, from fully transparent, no overlay, to fully opaque, full overlay. A

4-bit blend multiplier provides sixteen levels of mixing. The value 1111 is a

special case allowing the overlay data to pass completely unmixed. In all other

cases the value applied to the video path is (1 – blend / 16), and the value applied

to the overlay path is (blend / 16), where blend is the 4-bit multiplier value.

Two methods are used to generate the 4-bit multiplier. The multiplier value

can come either from a four-entry by 4-bit lookup table (LUT), or directly from

the ALPHA pins. In both cases, the blend multiplier value will be applied to both

luma and chroma for the co-sited components (Cb0:Y0:Cr0) and a separate

multiplier applied for the (Y1) component.

2-4 Conexant D860DSA

Bt860/861 2.0 Inputs and Timing

Multiport YCrCb to NTSC/PAL /SECAM

2.2.5 Alpha Pin Blending

The ALPHA[1:0] pins are used to select the amount of blending per pixel when

BLENDMODE = 1. The pins are sampled at the system clock rate and samples

during both luma and chroma components may be captured to create 1-, 2-, or

4-bit blend factors. For 1- and 2-bit blend modes, the multiplier LUT (in registers

ALPHA_LUT_0 through ALPHA_LUT_3 is programmed with user-defined

multiplier values.

In 1-bit blend mode, the ALPHA[0] pin indexes registers ALPHA_LUT_0

and ALPHA_LUT_3 to generate the multiplier value. In 2-bit blend mode, the

ALPHA[1:0] pins are used as a 2-bit index for registers ALPHA_LUT_0 through

ALPHA_LUT_3.

In 4-bit blend mode, the four bits required are captured in successive load

clocks from ALPHA[1:0]. The two LSBs of the 4-bit value are latched during the

luma portion of the overlay data load, and the two MSBs are latched during the

chroma component load. These four bits provide a direct multiplier for the

blending module. Figure 2-2 illustrates the alpha blending timing diagram.

Figure 2-2. Alpha Blending Timing Diagram

System Clock

2.2 Digital Video Ports

8-bit Overlay

Data

4-bit Alpha

2-bit Alpha

OSD[7:0]/P[7:0]

ALPHA[1]

ALPHA[0]

ALPHA[1]

ALPHA[0]

Cb0Y0Cr0Y1Cb2Y2Cr2Y

A[3]0A[1]0A[3]1A[1]1A[3]2A[1]2A[3]3A[1]

A[2]0A[0]0A[2]1A[0]1A[2]2A[0]2A[2]3A[0]

A[1]

A[0]

0

0

A[1]

A[0]

1

1

ALPHA[1]

NOTE(S):

1-bit Alpha

2-bit Content-

based Alpha

ALPHA[0]

OSD[1]/P[1]

OSD[0]/P[0]

A[0]

A[1]

A[0]

0

0

0

A[0]

A[1]

A[0]

1

1

1

1. Shaded areas indicate which video components are affected by each multiplier or index.

2. A blank data packet means this data carries no alpha information.

A[1]

A[0]

A[0]

A[1]

A[0]

3

3

3

2

2

2

2

2

A[1]

A[0]

A[0]

A[1]

A[0]

3

3

3

3

3

861_026

2.2.6 Content-based Blending

Content-based blending uses the two LSBs of the overlay byte associated with the luma

pixel to address the multiplier lookup table (registers ALPHA_LUT_0 through

ALPHA_LUT_3). This method is selected by setting BLENDMODE = 0, and is a

convenient means of using blending when no alpha pins exist from the overlay device.

D860DSA Conexant 2-5

2.0 Inputs and Timing Bt860/861

2.3 Configurations and Timing

Multiport YCrCb to NTSC/PAL /SECAM

2.3 Configurations and Timing

The Bt860/861 is capable of various ITU-R BT.601, ITU-R BT.656, and

decoder-locked configurations. Table 2-2 lists several ITU-R BT.601 and

ITU-R BT.656 configurations, and Section 2.3.3 discusses decoder-locked

configurations. In any of these configurations, it is possible to synchronize a

primary video source with an alternate video source. These two sources can then

be alpha-mixed, or independently selected for external display. Alpha mixing is

discussed in detail in Section 2.2.5.

Table 2-2. Configurable Timing States

Description

Bt860/861 is timing master,

HSYNC*, VSYNC*, and FIELD

are outputs.

(1)

Timing

Mode

,

100 1

SLAVE EN_656 SYNC_CFG

Bt860/861 is timing slave, timing

derived from HSYNC*, VSYNC*,

and BLANK* signals

Bt860/861 is timing slave, timing

derived from ITU-R BT .656 codes.

HSYNC*, and VSYNC* are

unused.

Bt860/861 is timing slave, timing

derived from ITU-R BT .656 codes.

HSYNC*, VSYNC*, and FIELD

are outputs.

NOTE(S):

(1)

Decoder locking using the VID port requires the part to be in timing mode 1, except

SYNC_CFG = 1 is only required if synchronization with other sources is required.

(2)

Either the BLANK* pin or the HBLANK, VBLANK, HACTIVE, and VACTIVE register can be

used for blanking.

3. Configurations not listed are not recommended.

4. X = Don’t care.

(2)

.

(1)

210 X

311 0

411 1

2-6 Conexant D860DSA

Bt860/861 2.0 Inputs and Timing

Multiport YCrCb to NTSC/PAL /SECAM

2.3.1 ITU-R BT.601 Configurations and Timing

Master and slave ITU-R BT.601 configurations are listed in Table 2-2 as timing

modes 1 and 2. Timing mode 1 is the ITU-R BT.601 master mode. An example

connection diagram is illustrated in Figure 2-3. In this example, both video

sources are slaved to the Bt860/861.

.

Figure 2-3. Timing Mode 1 Connection Example

Video Slave Bt860/861

8

Optional OSD Source, Timing Slave

P[7:0]

HSYNC*

VSYNC*

CLKO

FIELD

2.3 Configurations and Timing

(1)

NOTE(S):

(1)

It is not required that the clock be sourced from the Bt860/861.

8

2

OSD[7:0]

ALPHA[1:0]

XTI XTO

861_009

D860DSA Conexant 2-7

2.0 Inputs and Timing Bt860/861

2.3 Configurations and Timing

Timing mode 2 is the ITU-R BT.601 slave mode. An example connection

diagram is illustrated in Figure 2-4. In this example, the source feeding the P port

is the timing master, and both the optional OSD source and the Bt860/861 are

timing slaves. Although additional sources are shown in these diagrams, it is not

necessary to have more than one video source.

Figure 2-4. Timing Mode 2 Connection Example

Video Master Bt860/861

Optional OSD Source, Timing Slave

Multiport YCrCb to NTSC/PAL /SECAM

8

8

P[7:0]

HSYNC*

VSYNC*

(1)

CLKIN

BLANK*

OSD[7:0]

NOTE(S):

(1)

It is not required that the clock is sourced external to the Bt860/861.

When the Bt860/861 is configured for ITU-R BT.601 timing, the HSYNC*,

VSYNC*, FIELD, and BLANK* pins synchronize the Bt860/861 to external

video sources. In master mode, HSYNC* field, and VSYNC* are outputs and the

BLANK* pin is not used. All timing is generated internally and blanking is

determined by the HBLANK, VBLANK, HACTIVE, and VACTIVE registers. In

slave mode, HSYNC*, VSYNC* and BLANK* are inputs and the encoder’s

timing is controlled by an external master. Blanking is set either by the internal

HBLANK, VBLANK, HACTIVE, and VACTIVE registers (register bit

BLK_IGNORE = 1) or by a blanking signal on the BLANK* pin (register bit

BLK_IGNORE = 0).

2

ALPHA[1:0]

861_007

2-8 Conexant D860DSA

Bt860/861 2.0 Inputs and Timing

Multiport YCrCb to NTSC/PAL /SECAM

If the registers are used to determine video blanking (register bit

BLK_IGNORE = 1), the first component of the first active pixel of a line should

be presented to the encoder at HBLANK + 2 rising system clock edges after the

falling edge of HSYNC* for master mode, and HBLANK + 3 rising system clock

edges after the falling edge of HSYNC* for slave mode. The correct order of the

pixel components is Cb

timing relationship.

Figure 2-5. Pixel Timing for Timing Modes 1 and 2

(1)

t

1

Video Out

Pixel

Data

System

Clock

(4)

t

4

Cb

Y

0

0

2.3 Configurations and Timing

, Y0, Cr0, Y1, Cb2, Y2, Cr2.... Figure 2-5 illustrates this

0

(2)

t

2

(3)

t

3

Cr

Cb

Y

0

1

Cr

Y

2

2

2

Pixel Timing

(5)

HSYNC*

t

5

BLANK*

NOTE(S):

(1)

Blanking times (t1) are listed in Tables 3-1 through 3-4. Desired front porch blanking is set by the HBLANK register.

HBLANK = t1 + 14

(2)

The number of active pixels per line (t2) is set by the HACTIVE register.

(3)

The total number of system clocks per line (t3) is set by the HCLK register.

(4)

The first component of the first active pixel of the line should be placed HBLANK + 2 (or 3 for slave mode) rising system

clock edges after falling HSYNC*(t

(5)

When the BLANK* pin is used, the first component of the first pixel must arrive 3 rising system clock edges after the

falling edge of BLANK* (t

).

5

) in order to coincide with the end of horizontal blanking.

4

If the BLANK* signal is used to determine video blanking (in slave mode

only), the first component of the first active pixel of a line should be presented to

the encoder three rising system clock edges after the falling edge of the BLANK*

signal. Figure 2-5 illustrates this relationship.

861_006

D860DSA Conexant 2-9

2.0 Inputs and Timing Bt860/861

2.3 Configurations and Timing

The HBLANK register sets the line blanking time from the midpoint of the

falling edge of the analog horizontal sync pulse to the end of blanking. The

HACTIVE register sets the number of active pixels after the horizontal blanking

period has ended. See Tables 3-1 through 3-4 for appropriate HBLANK and

HACTIVE programming values for various NTSC, PAL, and SECAM video

standards.

Pixel and data timing (P, OSD, ALPHA, HSYNC*, VSYNC*, BLANK*) are

by default, latched into the Bt860/861 on the rising edge of the system clock, but

can be latched on the falling edge of the system clock if register bit PCLK_EDGE

(19[1]) is set high. The system clock can be seen on CLKO or CLKIN when

appropriate. Legal setup and hold times must be observed.

2.3.2 ITU-R BT.656 Timing

Data on the P port can be routed through the part’s ITU-R BT.656 timing

translator only when the system clock is 27 MHz, by setting register bit

EN_656 (1A[2]) high. This is accomplished using timing modes 3 or 4 (see

Table 2-2). Figure 2-6 illustrates an example connection diagram. ITU-R BT.656

timing derives vertical and horizontal timing information from the video data

stream (SAV and EAV codes). These codes are internally converted to HSYNC*

and VSYNC* signals, which can be then be produced on the Bt860/861’s

HSYNC*, VSYNC*, and FIELD pins. ITU-R BT.656 timing (also known as D1

timing) is illustrated in Figures 2-7 and 2-8. The resultant video is automatically

aligned to conform to ITU-R BT.656 video and blanking placement. The contents

of the HBLANK, HACTIVE, VACTIVE, and VBLANK registers are ignored,

except when register bit BLK_IGNORE = 1.

Multiport YCrCb to NTSC/PAL /SECAM

Figure 2-6. Timing Mode 3 and 4 Connection Example

CCIR656 Timing, Video Master Bt860/861

OSD Source, Timing Slave

NOTE(S):

(1)

It is not required that the clock is sourced external to the Bt860/861.

8

8

2

P[7:0]

(1)

CLKIN

OSD[7:0]

HSYNC*

VSYNC*

FIELD

ALPHA[1:0]

861_010

2-10 Conexant D860DSA

Bt860/861 2.0 Inputs and Timing

Multiport YCrCb to NTSC/PAL /SECAM

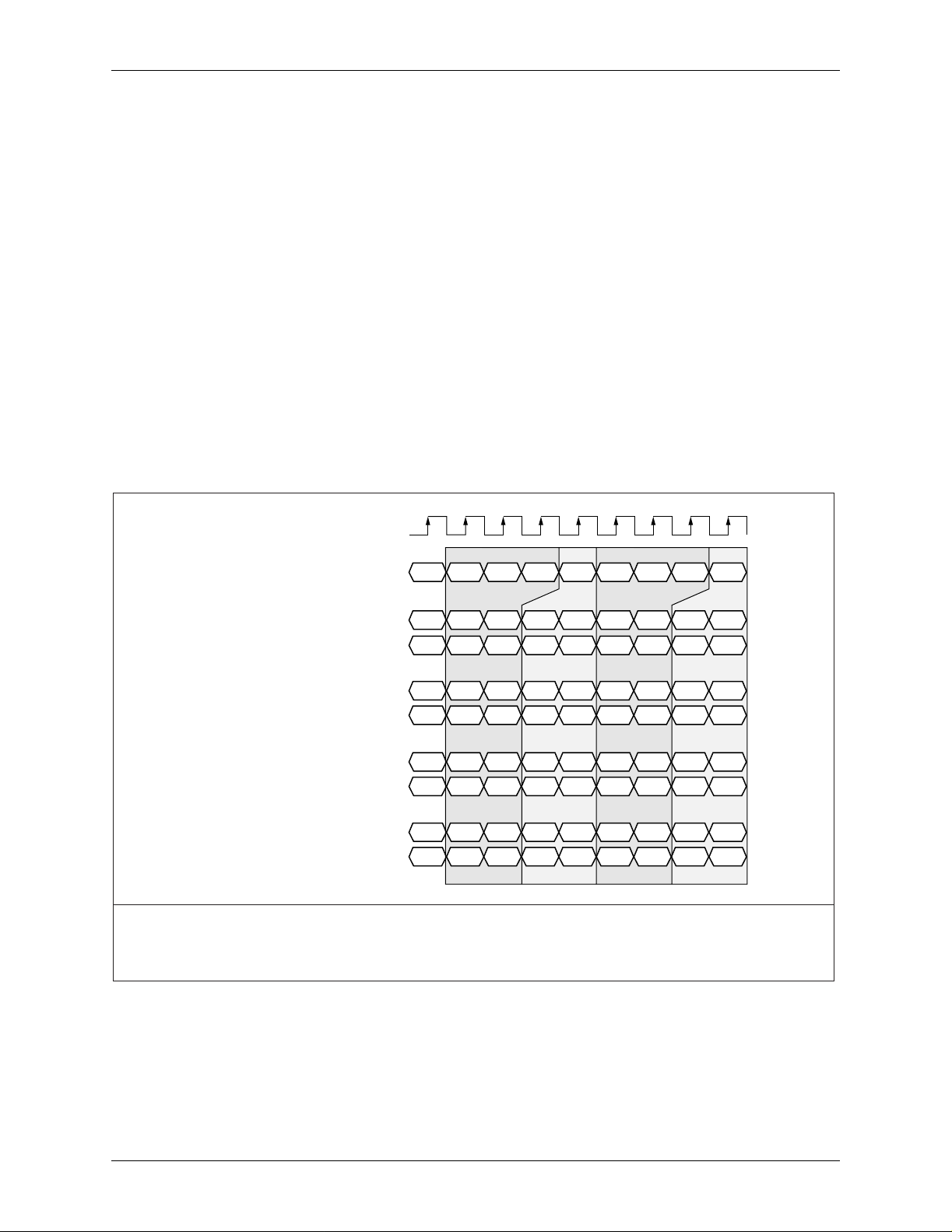

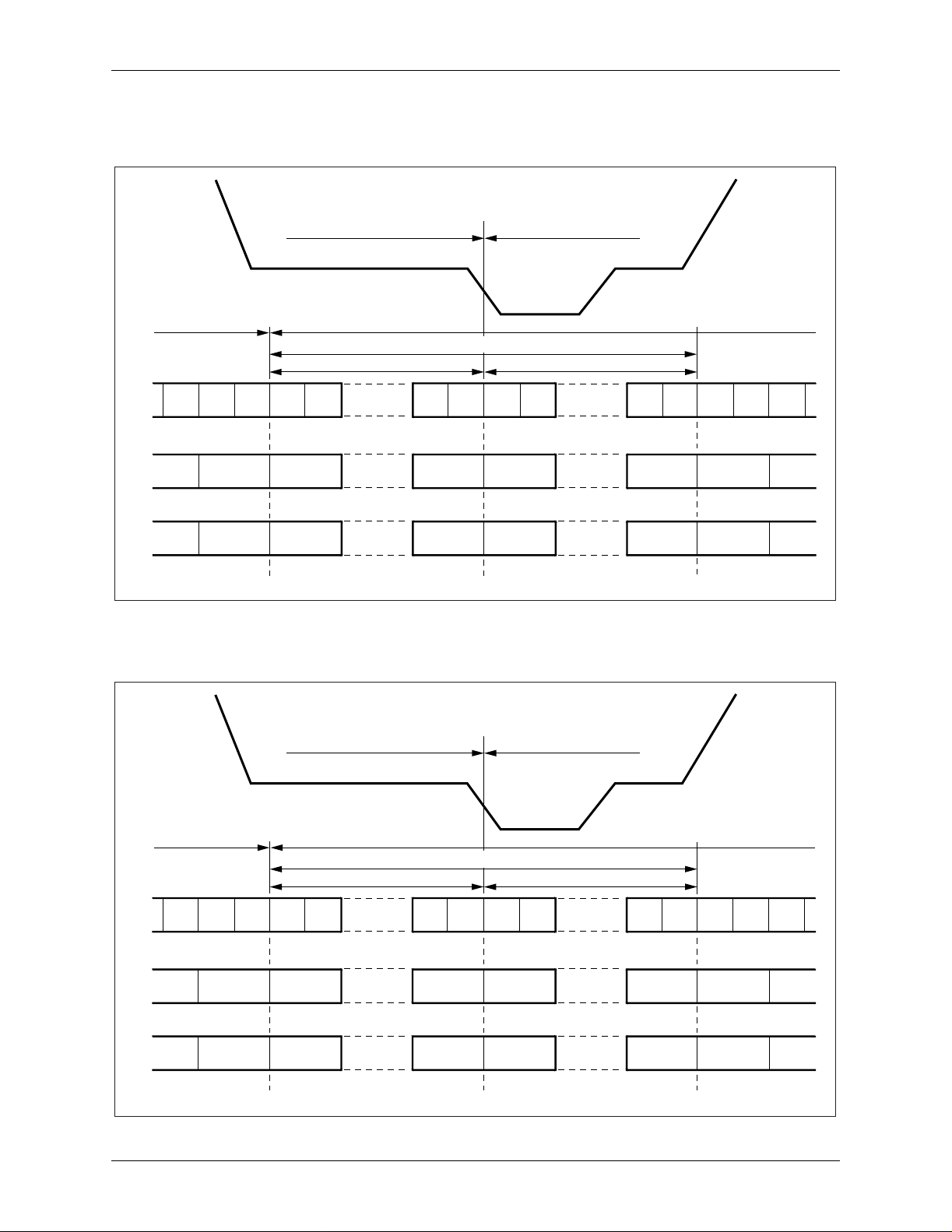

Figure 2-7. 625 Line ITU-R BT.656 Timing

Analog Line n – 1

n

Digital Line

Luminance Samples

717 718

Cr Samples

Cb Samples

– 1 Digital Line

719 720 721 730 731 732 733 862 863 0 1 2

359 360 365 366 431 0 1

12

2.3 Configurations and Timing

O

H

Digital Blanking

T

Analog Line

132

n

n

T

359 360 365 366 431 0 1

T

: luminance sampling period

Figure 2-8. 525 Line ITU-R BT.656 Timing

Analog Line n – 1

n

Digital Line

Luminance Samples

717 718

Cr Samples

– 1 Digital Line

719 720 721 734 735 736 737 856 857 0 1 2

359 360 367 368 428 0 1

16

861_005a

O

H

Digital Blanking

T

Analog Line

122

n

n

T

Cb Samples

359 360 367 368 428 0 1

T

: luminance sampling period

861_005b

D860DSA Conexant 2-11

2.0 Inputs and Timing Bt860/861

2.3 Configurations and Timing

In this configuration, the Bt860/861 is a slave to the ITU-R BT.656 data

stream. However, the HSYNC*, VSYNC* and FIELD pins can be configured as

outputs for synchronization with a video slave on the OSD port. While in this

configuration, the HSYNC*, VSYNC*, and FIELD timing is identical to

ITU-R BT.601 master mode timing.

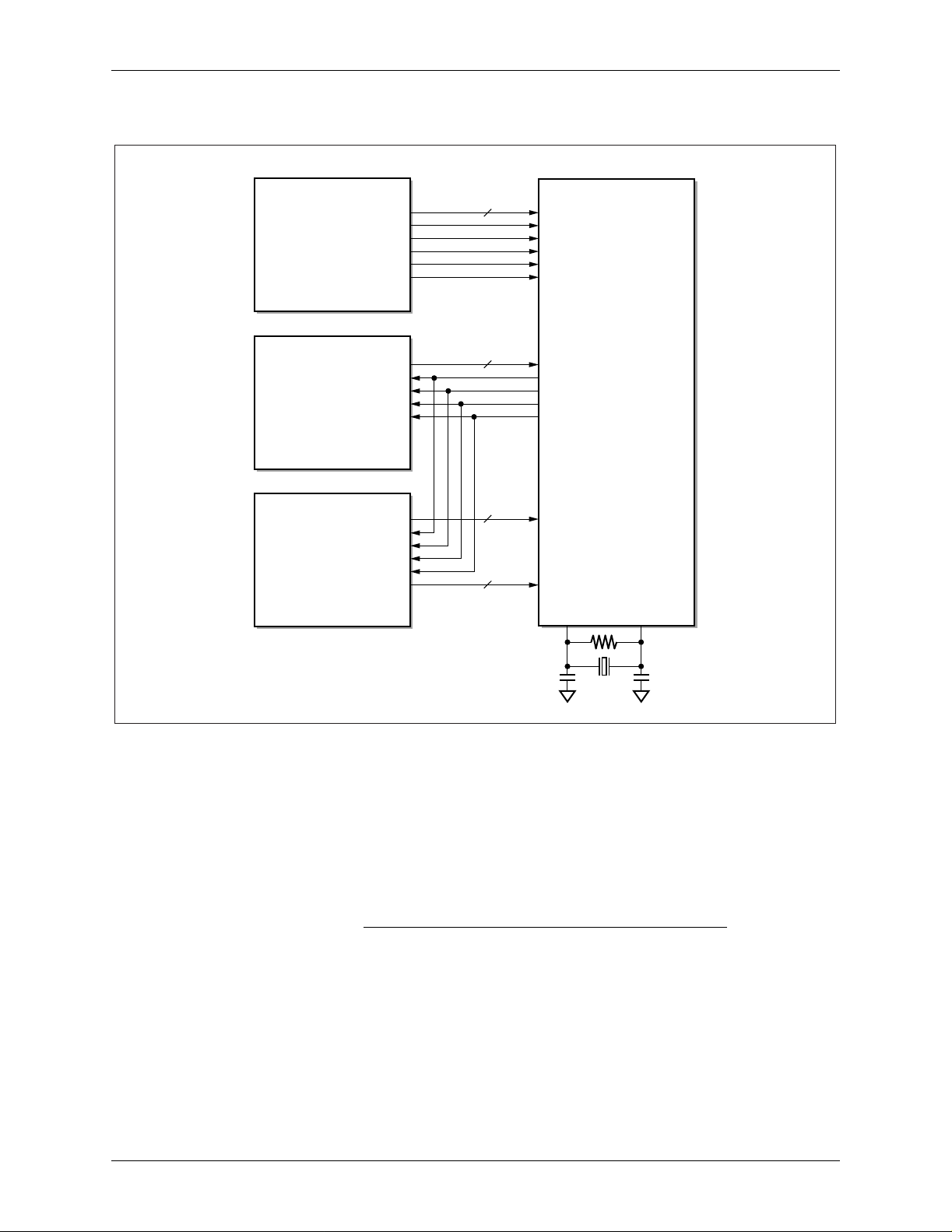

2.3.3 VID Port (Video Decoder Locked) Timing

The VID port can accept video signals from a video decoder, such as the Bt835,

and is buffered using a FIFO to support asynchronous video streams. The internal

logic will automatically pulls data from the FIFO when required. The data lines

for the VID port are VID[7:0], and the control lines are VIDCLK, VIDHACT,

VIDVACT, VIDFIELD, and VIDVALID. Figure 2-9 illustrates an example

configuration using the Bt835 and the Bt860. The PLL and the horizontal and

vertical counters are adjusted to track the incoming data on the VID port. The

Bt860/861 can be configured to output HSYNC* and VSYNC* signals in order

to synchronize with the P, OSD, and ALPHA signals. Timing mode 1 must be

used when the VID port is selected in conjunction with a source on the P or OSD

ports. The PLL (using the XTI and XTO inputs) must be selected as the system

clock source.

Multiport YCrCb to NTSC/PAL /SECAM

2-12 Conexant D860DSA

Bt860/861 2.0 Inputs and Timing

Multiport YCrCb to NTSC/PAL /SECAM

Figure 2-9. Video Decoder Connection Example

Bt835 Video Decoder Bt860/861

VD[15:8]

CLKX2

VALID

ACTIVE

VACTIVE

FIELD

MPEG-2 Decoder

Graphic Processor

2.3 Configurations and Timing

8

8

8

VID[7:0]

VIDCLK

VIDVALID

VIDHACT

VIDVACT

VIDFIELD

P[7:0]

CLKO

HSYNC*

VSYNC*

FIELD

OSD[7:0]

2

ALPHA[1:0]

XTI XTO

Follow these steps to lock a video decoder to this port:

Connect to the data and control pins as illustrated in Figure 2-9.

1.

Select the correct effective clock frequency using the PLL_FRACT and

2.

PLL_INT registers, and choose the XTAL inputs as the system clock

source using register bit PCLK_SEL (19[7]). See Section 2.4.1, and the

PLL_FRACT and PLL_INT register descriptions.

Set these locking registers to the following values:

3.

FIELD NAME VALUE

XL_MDSEL[1:0] 11

XL_SATEN 1

XL_SAT[3:0] 1

Set the part for Timing Mode 1 (see Table 2-2).

4.

Initiate locking by setting the LOCK (1C[5]) register bit high and the

5.

LC_RST (1C[6]) register bit low.

861_008

When unlocking the Bt861 to a source on the VID port, set the

NOTE:

LOCK (1C[5]) register bit low and the LC_RST (1C[6]) register bit high.

D860DSA Conexant 2-13

2.0 Inputs and Timing Bt860/861

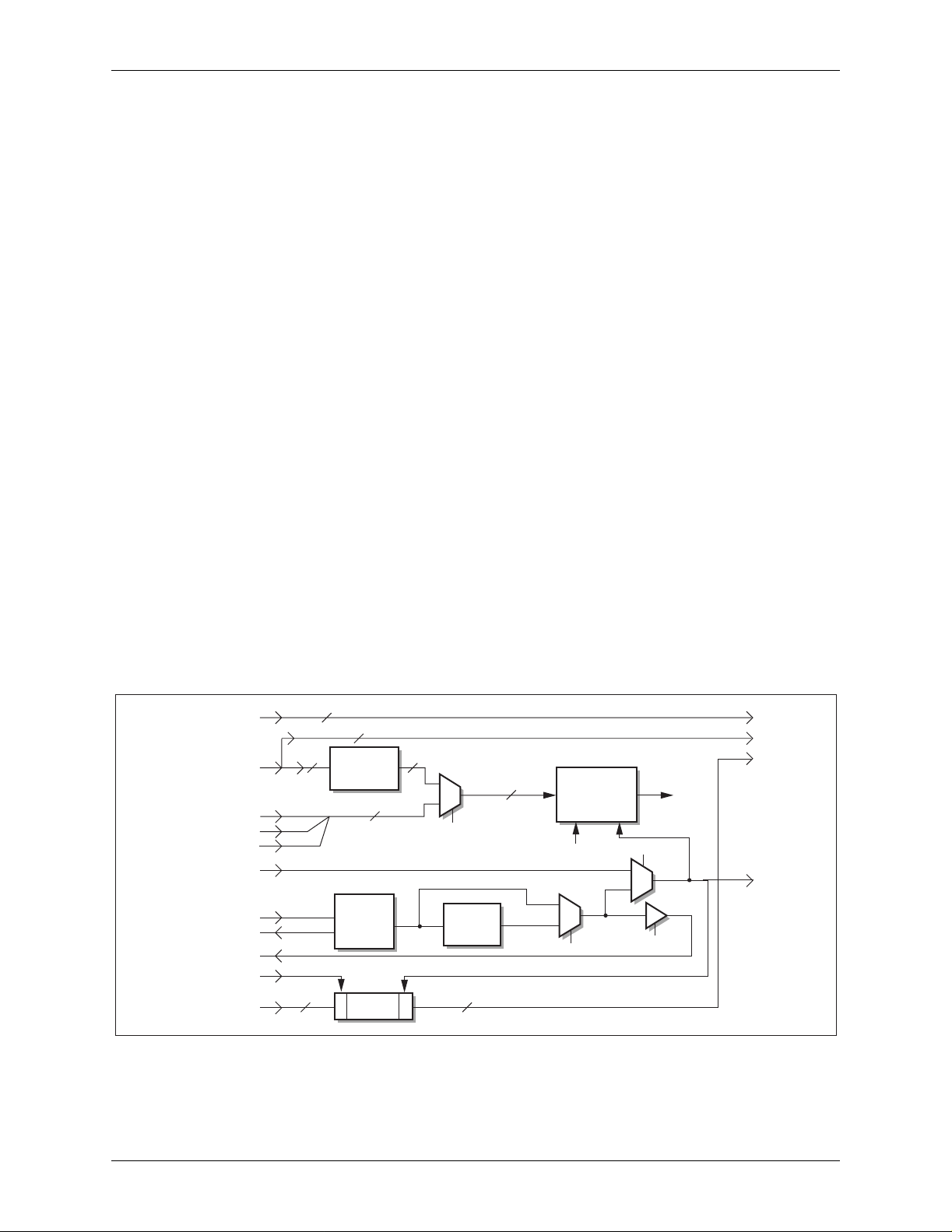

2.4 Clock Selection

2.4 Clock Selection

The internal pixel clock (PCLK) can be derived from either the CLKIN input or

the crystal inputs. The PCLK_SEL register bit (19[7]) controls which of these

two inputs will become the pixel clock.

2.4.1 Crystal Inputs and the PLL

The crystal inputs (XTI and XTO) drive a buffered oscillator to create a clock.

This clock is routed through the PLL if register bit BY_PLL (1D[3]) is 0, and

bypasses the PLL untouched if BY_PLL is 1. Figure 2-10 illustrates the clock

block diagram. If PCLK_SEL is low, this becomes the system clock.

The PLL_FRACT and the PLL_INT registers determine the PLL clock

frequency multiplier. The default setting generates a 27.0 MHz clock, using a

14.31818 MHz crystal.

If the VID port is enabled using the LOCK (1C[5]) register bit, the PLL is

controlled by the tracking servo mechanism.

The frequency programmed through PLL_FRACT and PLL_INT is used as a

base around which the VID port locking mechanism adjusts the system clock.

The PLL_FRACT and PLL_INT registers remain unaffected by the locking

mechanism, and when locking is disabled (through the LOCK bit), the

PLL_FRACT and PLL_INT registers once again determine the exact PLL

frequency.

Multiport YCrCb to NTSC/PAL /SECAM

Figure 2-10. Timing and Clock Block Diagram

OSD[7:0]

P[7:0]

HSYNC*

VSYNC*

BLANK*

CLKIN

XTI

XTO

CLKO

VIDCLK

VID[7:0]

8

8

CCIR656

8

Timing

Translator

3

Xtal

Inverter

and Buffer

88

FIFO

3

1

0

EN_656

PLL

OSD[7:0]

P[7:0]

VID[7:0]

3

Encoder

Timing

Block

SLAVE

1

0

BY_PLL

System

Block

PCLK_SEL

1

0

CLKO_DIS

System

Clock

861_025

2-14 Conexant D860DSA

Loading...

Loading...