CONEX CN8223, BT8222EPFF, BT8222EPFE Datasheet

CN8223

ATM Transmitter/Receiver with UTOPIA Interface

The CN8223 ATM Transmitter/Receiver with UTOPIA Level 1 interface provides a

single-access ATM service termination for User-to-Network (UNI) and

Network-to-Network Interfacing (NNI) in conformance with ATM Forum UNI and NNI

Specification 94/0317; Bellcore Specifications TR-TSV-000772, TR-TSV-000773,

TR-NWT-000253, and T1S1/92-185; ITU Recommendations I.432, G.707, G.751,

G.832, and Q.921; and ETSI prETS 300 213 and 300 214. Both Customer Premise

Equipment (CPE) and switching system interface functions are provided. The CN8223

provides DS1, E1, DS3, E3, E4, STS-1, and STS-3c (and STM-1) ATM cell alignment

functions. The system interface is via a parallel FIFO port or UTOPIA interface. In

addition, the CN8223 terminates the operations and maintenance flows F1, F2, and F3.

The CN8223 provides four FIFO port interfaces and one UTOPIA interface. Each

receiver port can be programmed with a particular Virtual Channel Identifier/Virtual

Path Identifier (VCI/VPI) address for message routing. VCI/VPI pages can also be

selected via masking registers.

The microprocessor can set control registers for insertion of selected header fields

by the transmitter on an individual port basis. The microprocessor can also control

insertion of all overhead and can insert errors in selected fields for test equipment

applications.

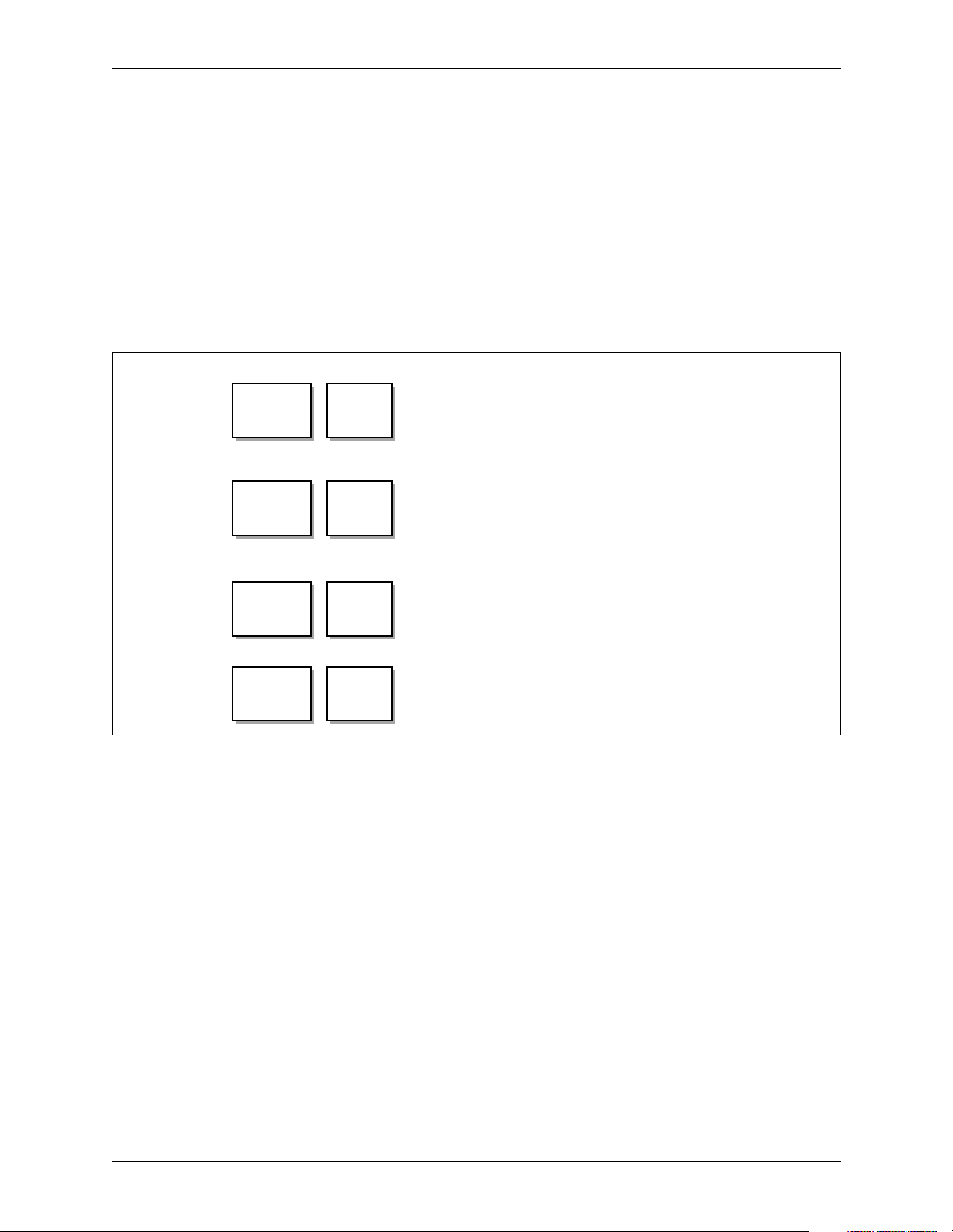

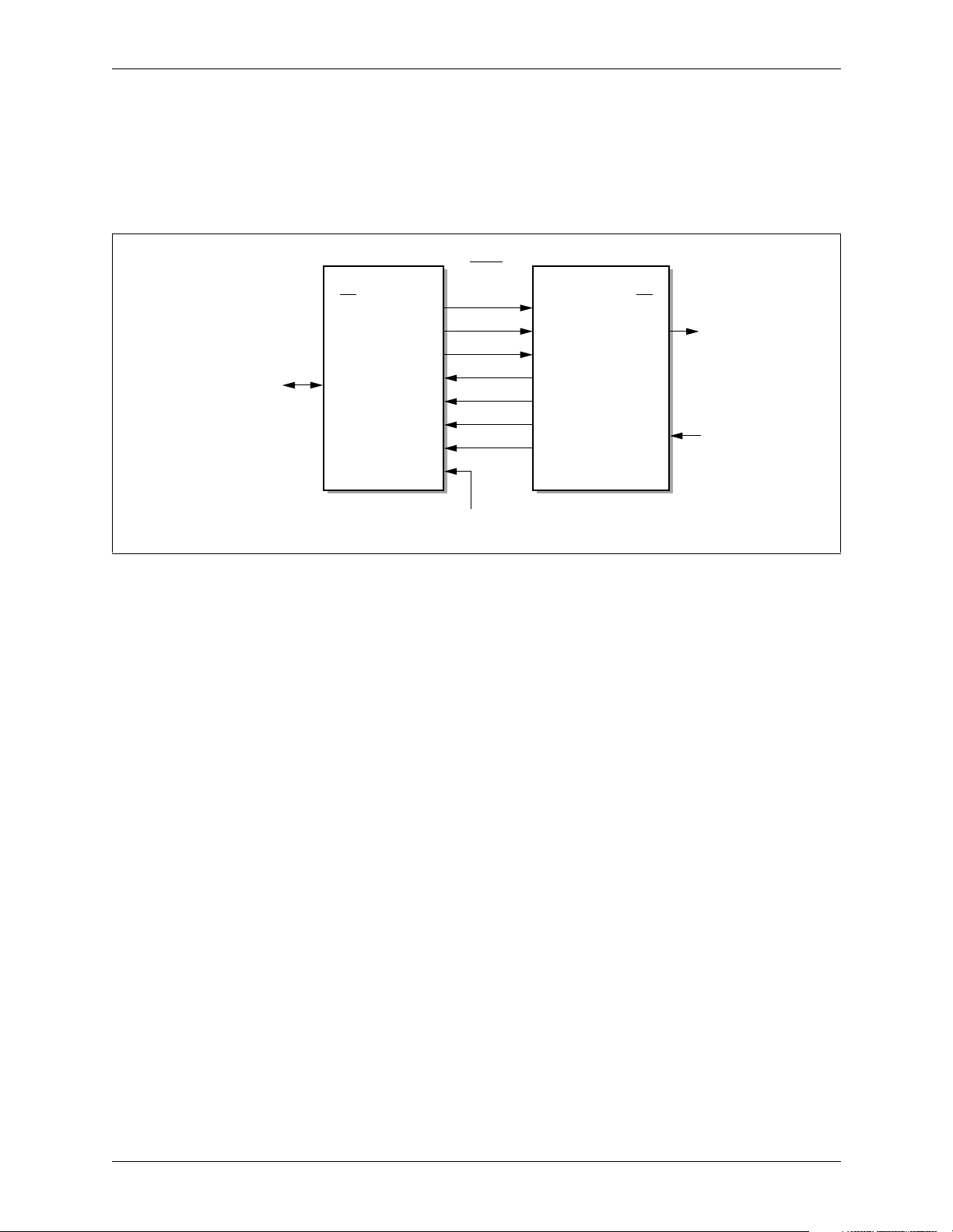

Functional Block Diagram

Data

Bus

Port

Control

UTOPIA

or FIFO

Interface

Microprocessor

Address

78

8

8

Cell

FIFO

8

4-Port

FIFO

Interface

8

Cell

Generation

Header

Filter

ATM Layer Physical Framing

52 Control Registers

28 Status Registors

TX

Rate

Control

Cell

Validation

Microprocessor

Microprocessor

Interface

8

8

Data Line Overhead

16

Cell

Alignment

HEC or

PLCP

HDLC

Data

Link

Framers

DS3

E3 (G.751)

E3 (G.832)

STS-1

E4 (G.832)

STS-3c

STM-1

TAXI

8

1

ATM

UNI

1

8

Distinguishing Features

• Integrates 7 line framers with ATM

layer processing according to ATM

Forum UNI and NNI Specifications

• UTOPIA Level 1 interface

• Internal framers for DS3, E3 (G.751,

G.832), E4 (G.832), STS-1, STS-3c,

STM-1

• PLCP and G.804 HEC cell alignment

for all data rates from 1.544 Mbps to

155 Mbps

TM

• Direct interface to TAXI

or external

T1/E1 framers

• ATM and SMDS cell modes

• 4 FIFO ports with header screening,

formatting, and transmit priority

controls

• Idle cells generated and screened

• Statistics counts latched on

one-second intervals

• Error detection and insertion

• Option insertion or generation of all

line and cell overhead

• Serial or parallel line interface

• Available evaluation module

reference design and software

• Supports Automatic Protection

Switching (APS)

Applications

• WAN equipment

• ATM switches

• Test equipment

• ATM routers and hub

8223_042

Data Sheet 100046C

March 8, 2000

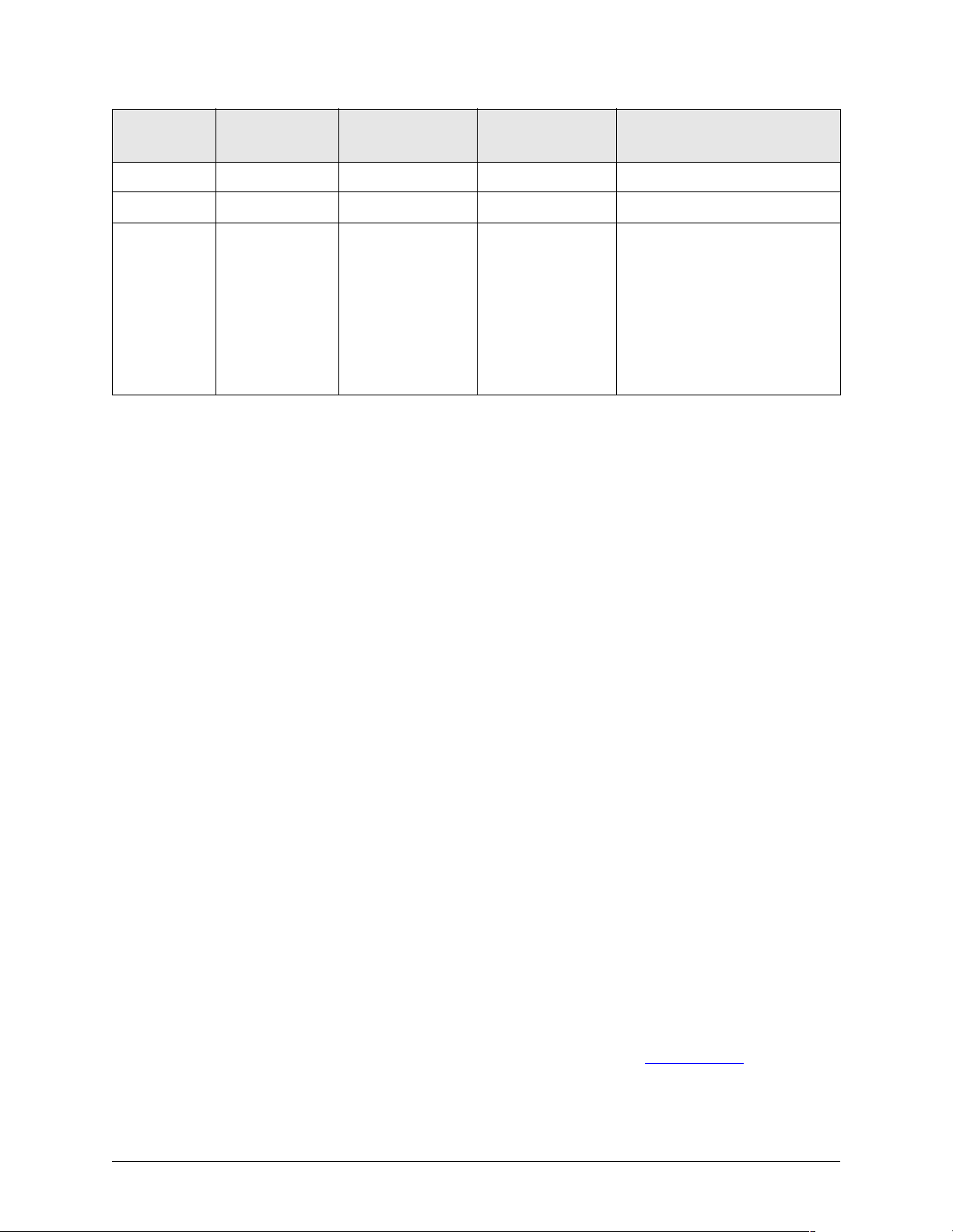

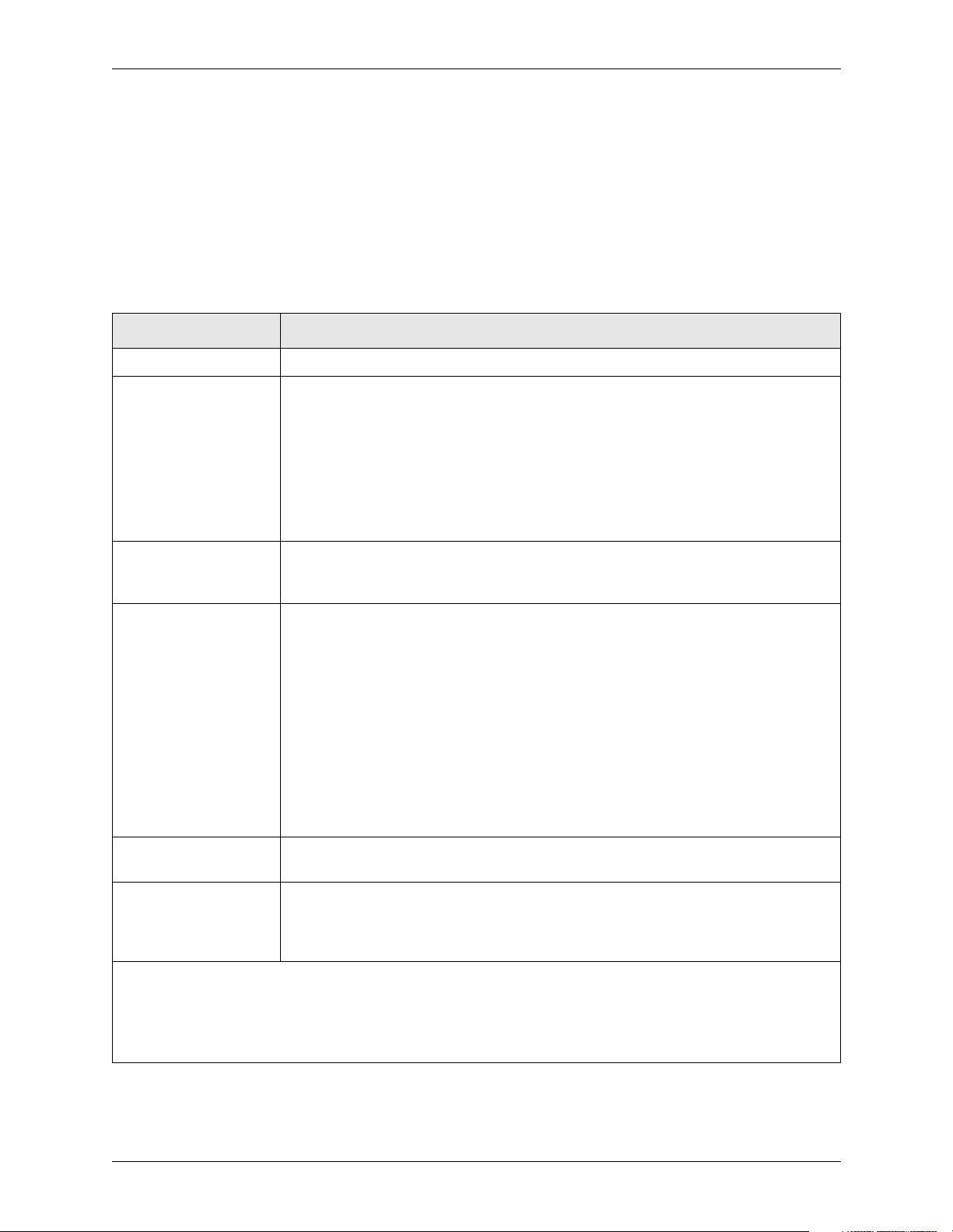

Ordering Information

Part Number

Generic Part

Number

28222-13 Bt8222EPFE

28222-14 Bt8222EPFF

28233-11 CN8223EPF

Operating

Temperature

–40

°C to 85 °C

°C to 85 °C

–40

–40

°C to 85 °C

Package

Description

Reduced Features

160-pin PQFP —

160-pin PQFP —

160-pin PQFP The CN8223 is based on the Bt8222

device. The only change from the

Bt8222 to the CN8223 is the TTL

I/O pad ring. The I/O structure

allows the CN8223 to function in a

3.3/5 V environment. No new

features, errata fixes, etc., have

been added to the CN8223 other

than TTL threshold inputs.

© 1999, 2000, Conexant Systems, Inc.

All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. (“Conexant”) products. These materials are

provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no

responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at

any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for

conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as

provided in Conexant’s Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING

TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A

PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTIAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY

PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE

ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE

MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL

DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE

OF THESE MATERIALS.

Conexant products are not intended for use in medical, life saving or life sustaining applications. Conexant customers using or selling

Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages

resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant™, the Conexant C™ symbol, and “What’s Next in

Communications Technologies”™. Product names or services listed in this publication are for identification purposes only, and may be

trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant’s disclaimer information posted at

incorporated by reference.

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and

suggestions to conexant.tech.pubs@conexant.com. For technical questions, contact your local Conexant

applications engineer.

www.conexant.com which is

sales office or field

100046C Conexant

Table of Contents

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

1.0 Product Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2 CN8223 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2.1 Internal Framers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2.2 UTOPIA Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2.3 Programmable Parity Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2.4 Test and Diagnostic Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2.5 Microprocessor Interface Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.3 Line Framing Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.3.1 Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.3.2 Line Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.3.3 BIP-8 Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.3.4 Alarm Detection/Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.4 ATM Cell Processing Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.4.1 Cell Generation Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.4.2 Tx Rate Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.4.3 Cell Validation Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.5 FIFO Port/UTOPIA Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.5.1 UTOPIA Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.5.2 FIFO Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.5.3 ATM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1.6 Line Interface Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.7 CN8223 Versions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1.8 CN8223 Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1.8.1 CN8223 as a DS3 or E3 G.751 Framer without ATM Cell Delineation. . . . . . . . . . . . . . . . 1-16

1.9 Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

1.10 Pin Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

10046C Conexant iii

Table of Contents CN8223

ATM Transmitter/Receiver with UTOPIA Interface

2.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1 Microprocessor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.1.1 8/16-Bit Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.1.2 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.2 Line Framers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2.1 Internally Framed Transmit Line Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.2.1.1 High-Speed PECL Transmit Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.2.2 Internally Framed Receive Line Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.2.2.1 High-Speed PECL Receive Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.2.2.2 Receiver Framing Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.2.3 Externally Framed Transmit Line Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.2.4 Externally Framed Receive Line Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.3 Overhead Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.3.1 Internal DS3 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

2.3.2 Internal G.832 E3/E4 Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.3.3 Internal G.751 E3 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

2.3.4 STS-1 and STS-3c/STM-1 Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.3.5 Transmit Framing Overhead Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

2.3.6 Receive Framing Overhead Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2.4 Status and Alarms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

2.4.1 Status and Counter Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

2.4.2 Alarm Signal Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-20

2.4.3 Alarm Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

2.5 Parallel Line Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.5.1 TAXI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.5.2 Transmit Parallel Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

2.5.3 Receive Parallel Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

2.6 ATM Cell Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

2.6.1 Cell Generation for Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

2.6.1.1 CELL_GEN_x Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

2.6.1.2 Cell Generation Status and Status Interrupts for Transmit . . . . . . . . . . . . . . . 2-28

2.6.2 Cell Validation for Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-29

2.6.2.1 HEC Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.6.2.2 CELL_VAL Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-30

2.6.2.3 Interrupts and Status Counters for Cell Validation. . . . . . . . . . . . . . . . . . . . . 2-32

2.6.3 PLCP Cell Generation for Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

2.6.4 PLCP Cell Validation for Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35

2.6.4.1 PLCP Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35

2.6.5 PLCP Transmit/Receive Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-36

iv Conexant 100046C

CN8223 Table of Contents

ATM Transmitter/Receiver with UTOPIA Interface

2.7 FIFO Port/UTOPIA Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

2.7.1 FIFO Interface Inputs and Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

2.7.2 Transmit Port Priority Mechanism. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-40

2.7.3 Transmit Rate Shaping Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-41

2.7.4 Receive Port Addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-41

2.7.4.1 Header Screening . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-42

2.7.4.2 Output Screening . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-42

2.7.5 UTOPIA Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-43

2.8 FEAC Channel and HDLC Data Link Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-44

2.8.1 FEAC Channel Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-44

2.8.2 FEAC Channel Receiver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-45

2.8.3 HDLC Data Link Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-45

2.8.3.1 Sending a Message. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-46

2.8.3.2 Aborting a Message . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-47

2.8.3.3 Transmitter Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-47

2.8.3.4 Transmitter Control Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48

2.8.4 HDLC Data Link Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-48

2.8.4.1 Receiver Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-49

2.8.4.2 Receiver Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-50

2.8.5 Receiver Response Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-51

3.0 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1 Registers Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.2 Control Register Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.3 Configuration Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

0x00—CONFIG_1 (Configuration Control Register 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

0x01—CONFIG_2 (Configuration Control Register 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

0x02—CONFIG_3 (Configuration Control Register 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

0x29—CONFIG_4 (Configuration Control Register 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

0x31—CONFIG_5 (Configuration Control Register 5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

0x2B—UTOPIA_1 (Utopia Port Control Register 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

0x2C—UTOPIA_2 (Utopia Port Control Register 2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

3.4 Transmit Control Registers

0x03—TXFEAC_ERRPAT (Transmit FEAC/Error Pattern Register) . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

0x60—DL_CTRL_STAT (HDLC Data Link Control and Status Register) . . . . . . . . . . . . . . . . . . . . . 3-15

0x04–0x07—CELL_GEN_x (Cell Generation Control Registers) . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

0x08—TX_RATE_23 (Transmit Rate Control Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

0x09—TX_RATE_01 (Transmit Rate Control Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

0x0A—TX_IDLE_12 (Transmit Idle Header Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

0x0B—TX_IDLE_34 (Transmit Idle Header Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

0x2A—IDLE_PAY (Transmit Idle Cell Payload Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-18

0x0C–0x13—TX_HDRx_12, TX_HDRx_34 (Transmit Header Registers) . . . . . . . . . . . . . . . . . . . . 3-18

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

100046C Conexant v

Table of Contents CN8223

ATM Transmitter/Receiver with UTOPIA Interface

3.5 Receive Control Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

0x14—CELL_VAL (Cell Validation Control Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

0x15–0x1C—HDR_VALx_12, HDR_VALx_34 (Receive Header Value Register) . . . . . . . . . . . . . . . 3-21

0x1D–0x24—HDR_MSKx_12, HDR_MSKx_34 (Receive Header Mask Register) . . . . . . . . . . . . . . 3-22

0x25, 0x26—RX_IDLE_12, RX_IDLE_34 (Receive Idle Header Registers) . . . . . . . . . . . . . . . . . . . 3-23

0x27, 0x28—IDLE_MSK_12, IDLE_MSK_34 (Receive Idle Header Mask Register) . . . . . . . . . . . . 3-23

3.6 Interrupt Enable Control Registers

0x2D—EN_LINE_INT (Enable Line Interrupts) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

0x2E—EN_EVENT_INT (Enable Event Interrupts) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-25

0x2F—EN_OVFL_INT (Enable Overflow Interrupts). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

0x30—EN_CELL_INT (Enable Cell Interrupts). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

0x32—TX_K1K2 (Transmit K1 and K2 Value) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

0x33—RX_K1K2 (Receive K1 and K2 value) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-27

3.7 Status Register Overview

0x38—LINE_STATUS (Line Framer/PHY Interrupt Status Register) . . . . . . . . . . . . . . . . . . . . . . . . 3-29

0x39—EVENT_STATUS (Event Interrupt Status Register). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-36

0x3A—OVFL_STATUS (Counter Overflow Interrupt Status Register) . . . . . . . . . . . . . . . . . . . . . . . 3-37

0x3B—CELL_STATUS (Interrupt Status Register). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-38

0x3C—RXFEAC_VER (Receive FEAC/Part Number/Version Number Register) . . . . . . . . . . . . . . . . 3-38

3.8 Event/Error Counters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-39

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

4.0 Electrical and Mechanical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1 Power Requirements and Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.3 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.3.1 Microprocessor Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.3.2 Line Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

4.3.3 FIFO Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

4.3.4 UTOPIA Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

4.3.5 TAXI Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

4.4 Mechanical Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

Appendix A:Transmit FIFO Port Rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.1 Rate Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.2 Port Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

A.3 Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

Appendix B:Acronym List. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

vi Conexant 100046C

CN8223 List of Figures

ATM Transmitter/Receiver with UTOPIA Interface

List of Figures

Figure 1-1. CN8223 Detailed Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Figure 1-2. Line Framer Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Figure 1-3. CN8223 Cell Processing Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

Figure 1-4. FIFO Port/UTOPIA Interface Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-10

Figure 1-5. Line Interface Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

Figure 1-6. CN8223 Connected to CAT 5 or PMD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

Figure 1-7. CN8223 Connected to Bt8360 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-14

Figure 1-8. CN8223 Connected to Bt8510 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-15

Figure 1-9. CN8223 Connected to Bt8370 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-15

Figure 1-10. CN8223 Connected to TDK 78P7200. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

Figure 1-11. CN8223 Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

Figure 1-12. CN8223 Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

Figure 2-1. CN8223 Receiver Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

Figure 2-2. CN8223 Transmitter Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Figure 2-3. Internal Framer Transmitter Interface Timing with Line Encoding. . . . . . . . . . . . . . . . . . . . 2-4

Figure 2-4. Internal Framer Transmitter Interface Timing Without Line Encoding. . . . . . . . . . . . . . . . . 2-5

Figure 2-5. Internal Framer Receiver Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Figure 2-6. Timing for Internal Framer Receiver, Encoder Disabled . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Figure 2-7. DS1 Interface Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Figure 2-8. E1 Interface Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Figure 2-9. DS3 Interface Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Figure 2-10. E3 Interface Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Figure 2-11. Receiver DS1 Line Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

Figure 2-12. Transmit Framing Overhead Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

Figure 2-13. Receive Framing Overhead Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

Figure 2-14. Transmit Parallel Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

Figure 2-15. Receive Parallel Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

Figure 2-16. Transmit FIFO Port Interface Timing, 53-Octet Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-38

Figure 2-17. Receive FIFO Port Interface Timing, 53-Octet Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-39

Figure 3-1. LINE_STATUS and OOF Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

Figure 3-2. Register Summary, Cheat Sheet 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-46

Figure 3-3. Register Summary, Cheat Sheet 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-47

Figure 4-1. Local Processor Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Figure 4-2. Line Interface Timing—DS1, E1, DS3, E3 External Framers . . . . . . . . . . . . . . . . . . . . . . . . 4-7

Figure 4-3. Line Interface Timing–Internal Framers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Figure 4-4. Parallel Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Figure 4-5. Overhead Port Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

100046C Conexant vii

List of Figures CN8223

ATM Transmitter/Receiver with UTOPIA Interface

Figure 4-6. FIFO Port Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

Figure 4-7. UTOPIA Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

Figure 4-8. TAXI Port Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

Figure 4-9. CN8223 160-Pin Plastic Quad Flat Pack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

viii Conexant 100046C

CN8223 List of Tables

ATM Transmitter/Receiver with UTOPIA Interface

List of Tables

Table 1-1. CN8223 Version Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

Table 1-2. Hardware Signal Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-20

Table 2-1. Valid CONFIG_1 Line Mode Settings, Bits 7–0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Table 2-2. Internal Framer Transmitter Interface Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Table 2-3. Internal Framing Unencoded Transmitter Connections (STS-3c, STM-1, E4) . . . . . . . . . . . 2-5

Table 2-4. Internal Framer Receiver Interface Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

Table 2-5. Connections for Internal Framer Rx, Encoder Disabled (STS-3c, STM-1, E4). . . . . . . . . . . 2-7

Table 2-6. Serial External Framer Transmitter Interface Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Table 2-7. External Framing Mode Receiver Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Table 2-8. DS3 Overhead Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

Table 2-9. G.832 E3 and E4 Overhead Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Table 2-10. G.751 E3 Overhead Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Table 2-11. C1 Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

Table 2-12. STS-1, STS-3c, and STM-1 Overhead Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

Table 2-13. Status Indications for All Modes (Register 0x38) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-21

Table 2-14. Pin Connections between TAXI Chipset and CN8223 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

Table 2-15. Transmit Parallel Interface Mode Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

Table 2-16. Receive Parallel Interface Mode Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-25

Table 2-17. Cell Generation Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

Table 2-18. Overhead Field Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

Table 2-19. Status Octet Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-31

Table 2-20. PT Header Field and User Data Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-31

Table 2-21. FEBE Controls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

Table 2-22. C1 Octet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-34

Table 2-23. FIFO Interface Pin Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

Table 2-24. FIFO Transmit Pin Functional Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-39

Table 2-25. FIFO Receive Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-40

Table 2-26. Priority Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-40

Table 2-27. UTOPIA Interface Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-43

Table 2-28. Byte Transmission Times for Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-46

Table 3-1. ATM Transmitter/Receiver Status Registers, Counters, and Data Link Control . . . . . . . . . . 3-1

Table 3-2. ATM Transmitter/Receiver Microprocessor Control Registers . . . . . . . . . . . . . . . . . . . . . . . 3-2

Table 3-3. Valid Combinations of CONFIG_1, Bits 0–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

Table 3-4. Alarm Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

Table 3-5. Alarm Transmission—STS–1/STS–3c/STM–1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

Table 3-6. Overhead Generation Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

Table 3-7. CELL_GEN_x Control Register Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

Table 3-8. Tx_HDRx Register Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-18

Table 3-9. HDR_VALx Register Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

100046C Conexant ix

List of Tables CN8223

ATM Transmitter/Receiver with UTOPIA Interface

Table 3-10. HDR_MSKx Register Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-22

Table 3-11. ATM Transmitter/Receiver Status Registers, Counters, and Data Link Control . . . . . . . . . 3-28

Table 3-12. STS-1,STS-3c, STM-1 LINE_STATUS Bit Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-30

Table 3-13. DS3 PLCP and Direct Mapping Mode LINE_STATUS Bit Definitions. . . . . . . . . . . . . . . . . 3-31

Table 3-14. E3 G.832, E4 G.832 LINE_STATUS Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-32

Table 3-15. E3 G.751 LINE_STATUS Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-33

Table 3-16. External Framer, 57-Octet Mode, LINE_STATUS Bit Definitions . . . . . . . . . . . . . . . . . . . . 3-34

Table 3-17. Status Indications for All Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-35

Table 3-18. Line and Interface Events/Errors Counters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-39

Table 3-19. Counted Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-40

Table 3-20. Internal STS-1, STS-3c Event/Error Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-41

Table 3-21. Internal DS3 PLCP and Direct Mapping Modes Event/Error Counters. . . . . . . . . . . . . . . . 3-42

Table 3-22. Internal G.832 E3/E4 Event/Error Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-43

Table 3-23. Internal G.751 E3 Event/Error Counters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-44

Table 3-24. External Framer, 57-Octet Mode Event/Error Counters . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-45

Table 4-1. DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Table 4-2. Microprocessor Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Table 4-3. Line Interface Timing—DS1, E1, DS3, E3 External Framers . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Table 4-4. Line Interface Timing—Internal Framers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

Table 4-5. Parallel Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Table 4-6. Overhead Port Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Table 4-7. FIFO Port Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

Table 4-8. UTOPIA Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

Table 4-9. TAXI Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

Table A-1. Cell Thresholds (1 of 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

x Conexant 10046C

1

1.0 Product Description

The CN8223 ATM Physical Interface (PHY) device is a transmitter/receiver

which converts several types of frames to ATM cells and vice versa. The device

contains framers for DS3, E3, E4, STS-1, STS-3c, and STM-1. This chapter

provides an overview of the CN8223, describing its primary features and

applications. A block diagram and a logic diagram are included.

1.1 Block Diagram

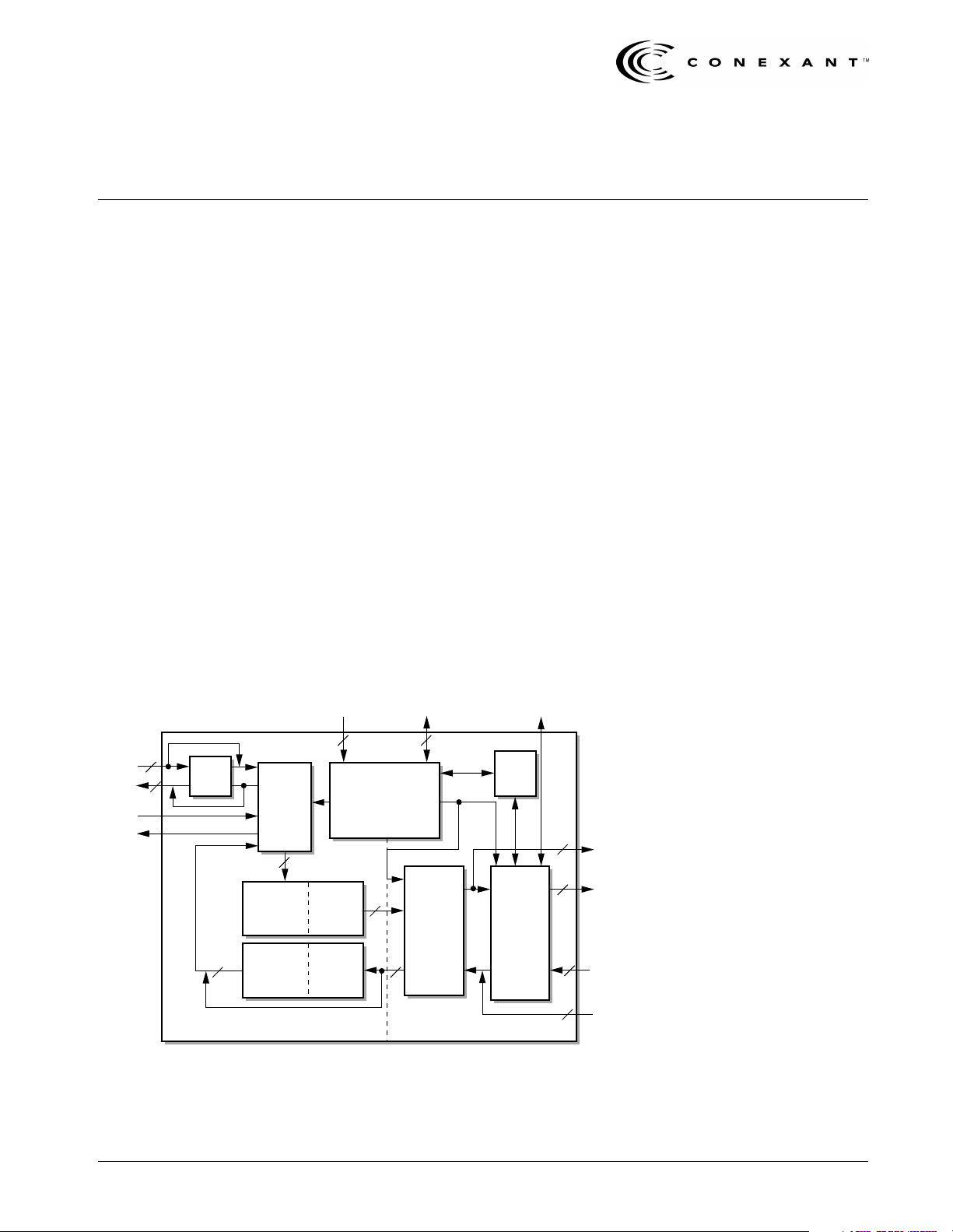

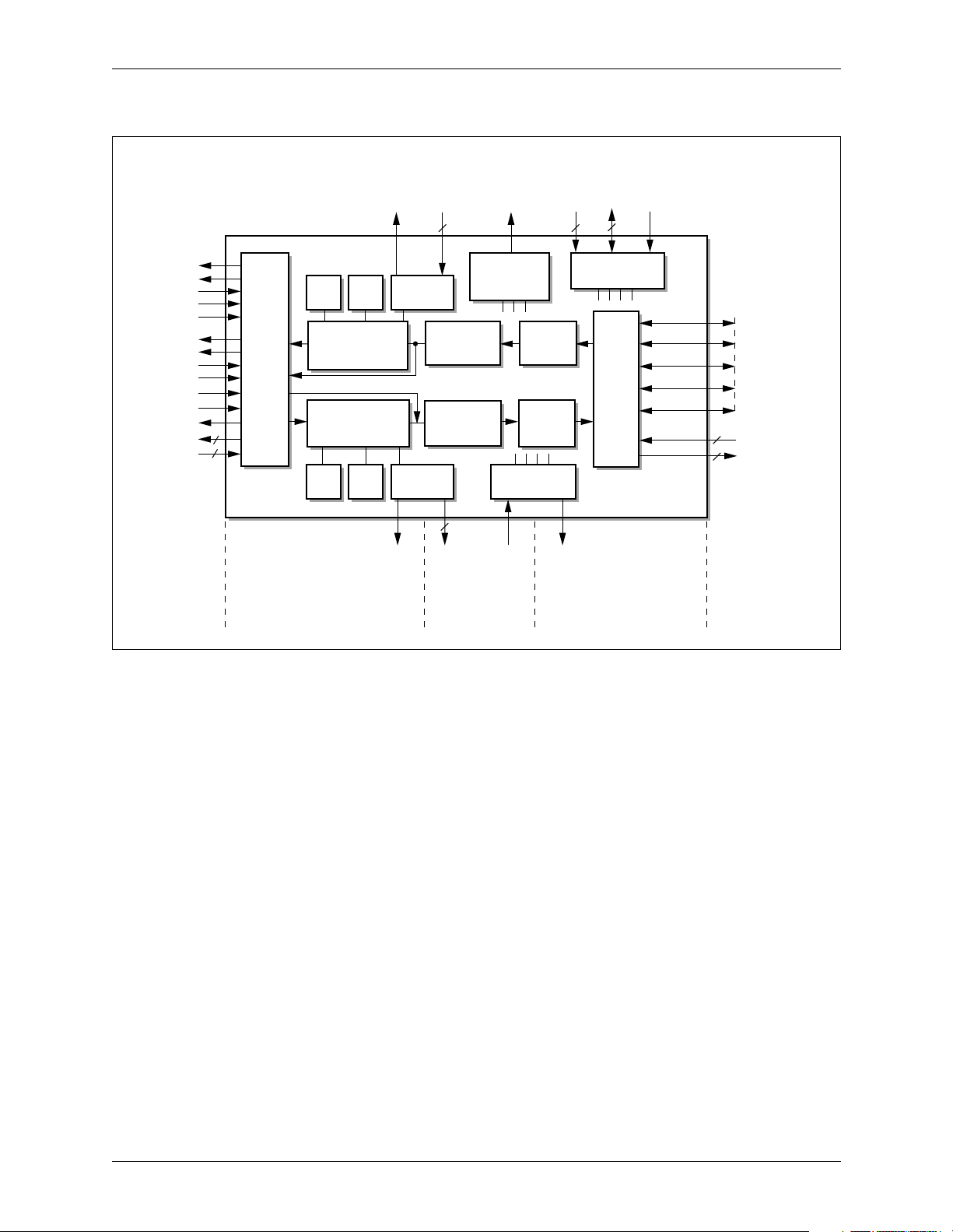

Figure 1-1 is a detailed block diagram of the CN8223. The host system transmits

octet-wide data to the CN8223 via the UTOPIA or FIFO ports. This data is

assembled into ATM cells by the PHY and formatted for serial line transmission

by the CN8223’s line framers. In the receive direction, serial network data is

framed into octets by either internal or external line framers and passed to the

ATM cell processing block. Octet data is then aligned into ATM cells, checked,

and sent through the UTOPIA or FIFO ports to the host system.

The line framer block connects to external interfaces for line reception and

transmission. The line framer has interfaces for seven data rates and provisions

for external serial or parallel framers. Also included are overhead interfaces, data

links, and event counters.

The HEC/PLCP ATM cell alignment block accepts octet data from the line

framer block. It generates cells for transmission and validates received cells.

Included are HEC/PLCP generators and detectors, data scramblers, and counters.

The FIFO Port/UTOPIA interface communicates with the next layer of ATM

processing, usually residing in the host system. It directs received cell traffic to

four ports, controls transmit priority and rate, and has counters for events and

errors.

100046C Conexant 1-1

1.0 Product Description CN8223

1.1 Block Diagram ATM Transmitter/Receiver with UTOPIA Interface

Figure 1-1. CN8223 Detailed Block Diagram

PRCLK

CS~

AS~

16

W/R~

OE~

SEL8BIT

TMRKR

TOVH_CLK A[7:1]

TXOVH

DL_INT

STAT_INT D[15:0]

8

8

TCLKO_HS

TXOUT_HS

TXCKI_HS±

RXCKI_HS±

RXIN_HS±

TCLKO

TXOUT

TXCKI

RXCKI

RXIN

RCV_HLD

LOCD

TXOUT[7:0]

RXIN[7:0]

Interrupt Control

and PLCP

Framer

and PLCP

Framer

8

Section

Cell Counters

Performance

Monitoring

Generation,

and Priority

Validation

Rx VPI/VCI

Screening

Clock and

Control

ONESECI

8KCKI

NTEST

TEST1, 3

RESET

Microprocessor

Interface

Tx Cell

Tx Rate

Rx Cell

ONESECO

FIFO Data Ports Section

4-Port

FIFO

Data

Interface

UTOPIA

Interface

and

4-Cell

Buffers

Port 0 Ctrl

Port 1 Ctrl

Port 2 Ctrl

Port 3 Ctrl

UTOPIA Ctrl

CN8223

FCTRL_OUT[16:0]

FCTRL_IN[7:0]

FDAT_IN

9

FDAT_OUT

9

8223_001

±

±

Line

Interfaces

High

Speed

Medium

Speed

9

Parallel

Interface

9

Line Framer Section Cell Processing

Tx

HDLC

HDLC

Tx

FEAC

DS3, E3, E4, STS-1

STS-3c, STM-1

G.832

Transmit Framer

DS3, E3, E4, STS-1

STS-3c, STM-1

G.832

Receive Framer

Rx

Rx

FEAC

Overhead

Insert

Overhead

Extract

RMRKR

ROVH_CLK

Tx

Transmit G.832

Receive G.832

Rx

RXOVH

1-2 Conexant 100046C

CN8223 1.0 Product Description

ATM Transmitter/Receiver with UTOPIA Interface

1.2 CN8223 Features

The CN8223 ATM Transmitter/Receiver provides a single-access ATM service

termination for UNI and NNI. It conforms to the following specifications and

recommendations:

• ATM Forum UNI Specification 94/0317

• Bellcore Specifications TR-TSV-000772, TR-TSV-000773,

TR-NWT-000253, and T1S1/92-185

• ITU Recommendations I.432, G.707, G.751, G.832, and Q.921

• ETSI draft standards prETS 300 213 and 300 214

Both terminal and switching system interface functions are provided. The

CN8223 provides DS1, E1, DS3, E3, E4, STS-1, and STS-3c (STM-1) Physical

Layer Convergence Procedure (PLCP) functions. It optionally provides for the

generation and validation of AAL3/4 and AAL5 ATM cell payloads. The system

interfaces to the ATM layer through either a UTOPIA-compatible port or a

parallel FIFO port. Provisions for source rate control are included in the

transmitter circuitry.

1.2 CN8223 Features

1.2.1 Internal Framers

1.2.2 UTOPIA Port

Internal framers are included for DS3 C-bit parity format, G.751 E3 format,

G.832 E3 and E4 formats, and STS-1/STS-3c/STM-1 formats. Cell delineation is

via either PLCP framing overhead or G.832 Header Error Control (HEC)

alignment. The CN8223 parallel line interface allows octet recovery/transmission

externally for 100 Mbps TAXI or other interfaces.

The DS1, DS3, E1, and E3 data stream interfaces connect directly to Conexant

framers (Bt8360C for DS1, Bt8510B for E1, Bt8370 for E1/T1 with integral Line

Interface Unit (LIU), and Bt8330B for DS3 and E3). DS1 and DS3 PLCP

functions conform to Bellcore Standard TR-TSV-000773; E1 PLCP conforms to

ETSI draft standard prETS 300 213; and E3 PLCP conforms to ETSI draft

standard prETS 300 214. Transmit and receive functions are provided for all line

rates up to 155 Mbps.

The UTOPIA port conforms to the ATM Forum UTOPIA Level 1 Specification

(Version 2.01) and provides both octet- and cell-based handshaking. The interface

contains transmit and receive buffer FIFOs with a depth of four cells

programmable for reduced latency requirements per ATM Forum document

94/0317. This interface conforms to the Saturn Compliant Interface for ATM

PHY Devices Specification.

The microprocessor can set control registers for insertion of selected header

fields by the transmitter on an individual port basis. Also, the processor can

control insertion of all overhead and can insert errors in selected fields for test

equipment applications.

100046C Conexant 1-3

1.0 Product Description CN8223

1.2 CN8223 Features ATM Transmitter/Receiver with UTOPIA Interface

1.2.3 Programmable Parity Protection

Programmable parity protection is available on the system interface. Read and

write strobes allow addressing of up to four distinct data sources and output to

four distinct destinations. Each transmitter port has a programmable priority

level. If the priority levels are the same, the ports are addressed in sequence. Each

receiver port can be programmed with a particular VCI/VPI address for message

routing. Also, VCI/VPI pages can be selected via masking registers. Cells can be

routed to multiple ports for broadcast capability and enhanced test, diagnostic,

and maintenance functions. Also, the cell validation function can be programmed

to correct single-bit header errors.

1.2.4 Test and Diagnostic Functions

The CN8223 provides access to the ATM protocol at all levels for test and

diagnostic functions. Octet-wide simultaneous interfaces are provided for

transmit and receive access to PLCP slots (57 octets), ATM cells (53 octets), cells

without HEC (52 octets), or cell payload only (48 octets). This interface allows

the implementation of test and diagnostic systems. Also, per-cell status can be

optionally provided in place of the HEC octet on Port 3 in a special output mode.

1.2.5 Microprocessor Interface Features

All control and status functions are provided via a direct microprocessor

interface. Also, the microprocessor can control the external framers as required.

The microprocessor interface can be used with either an 8- or 16-bit data bus with

separate address and data signals. Interrupt outputs are provided for status

information on cell and physical layer performance and for data link operations.

The interface is a clocked 8- or 16-bit data interface with an address strobe and a

single read/write control.

1-4 Conexant 100046C

CN8223 1.0 Product Description

ATM Transmitter/Receiver with UTOPIA Interface

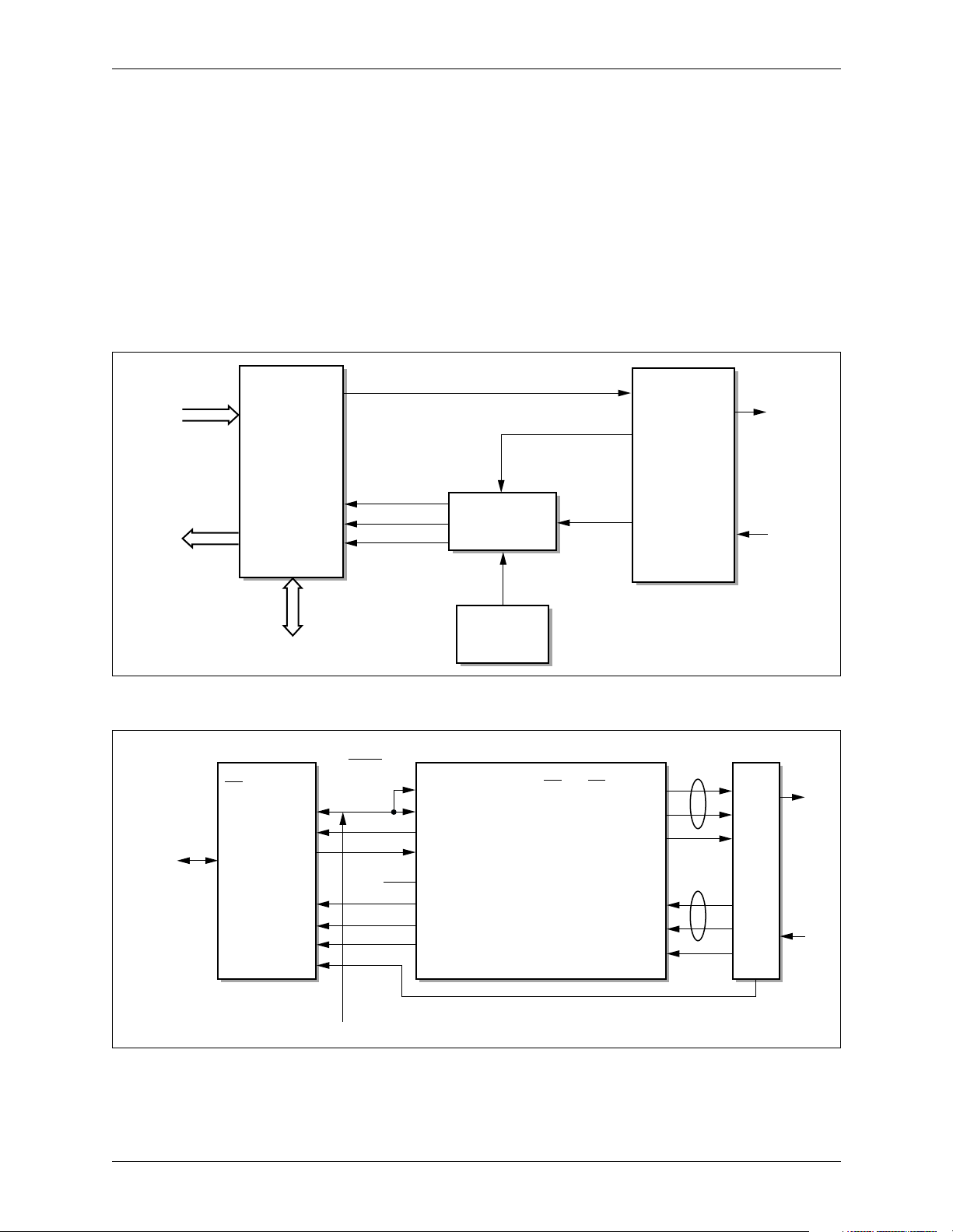

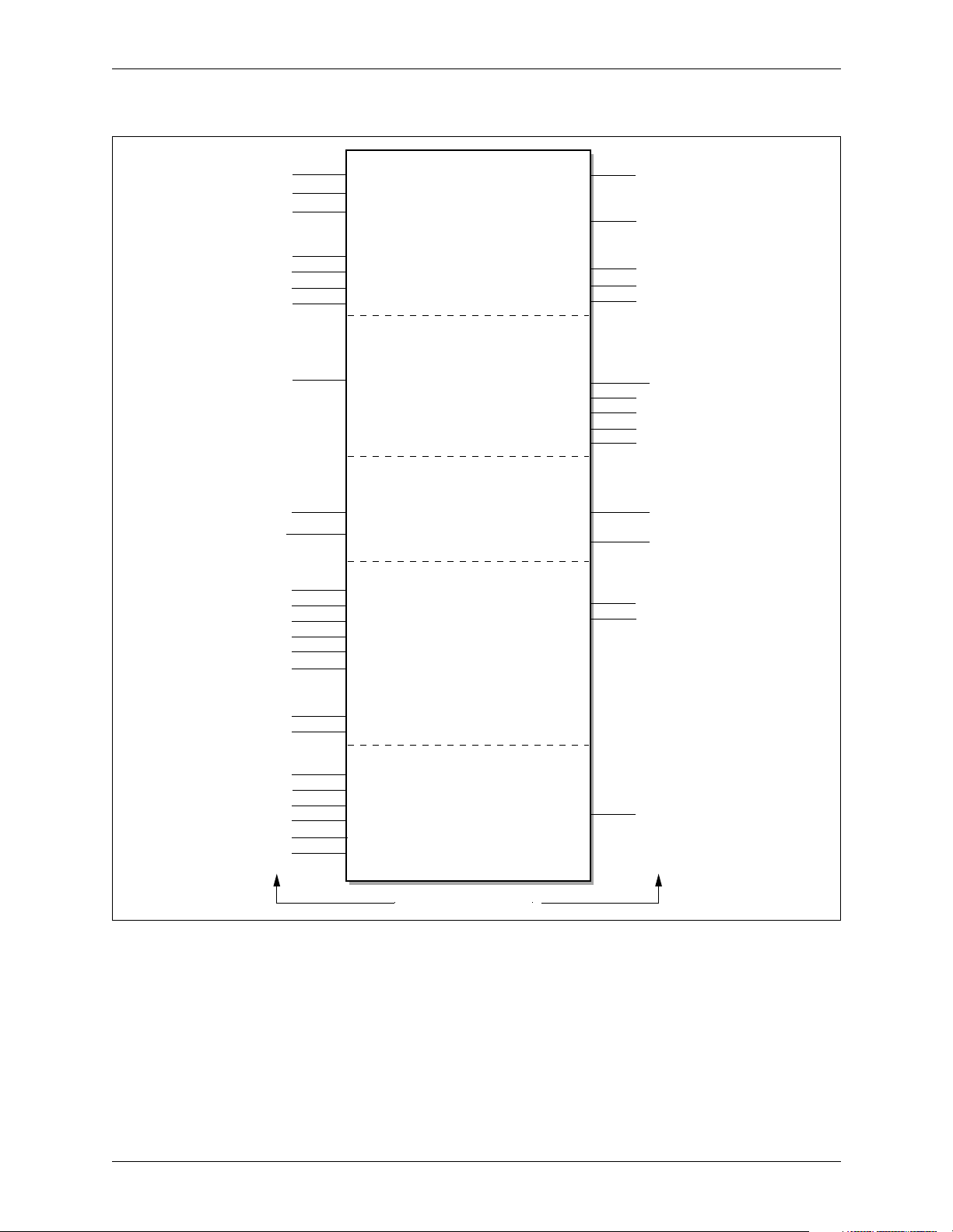

1.3 Line Framing Functions

The CN8223 provides framers for DS3, E3 (both G.751 and G.832), E4 (G.832),

STS-1, and STS-3c/STM-1 formatted serial streams. The line receive circuitry

recovers the frame location from the serial stream and provides cell octets to the

physical layer block for cell delineation. The transmit circuitry receives cell octets

from the cell generation or physical layer blocks and adds line framing overhead

information as required. The LIU receive interface detects both Loss-of-Signal

(LOS) and Line Code Violations (LCVs). The active edge of the transmit output

clock is selectable. Figure 1-2 illustrates the line framer functions of the CN8223.

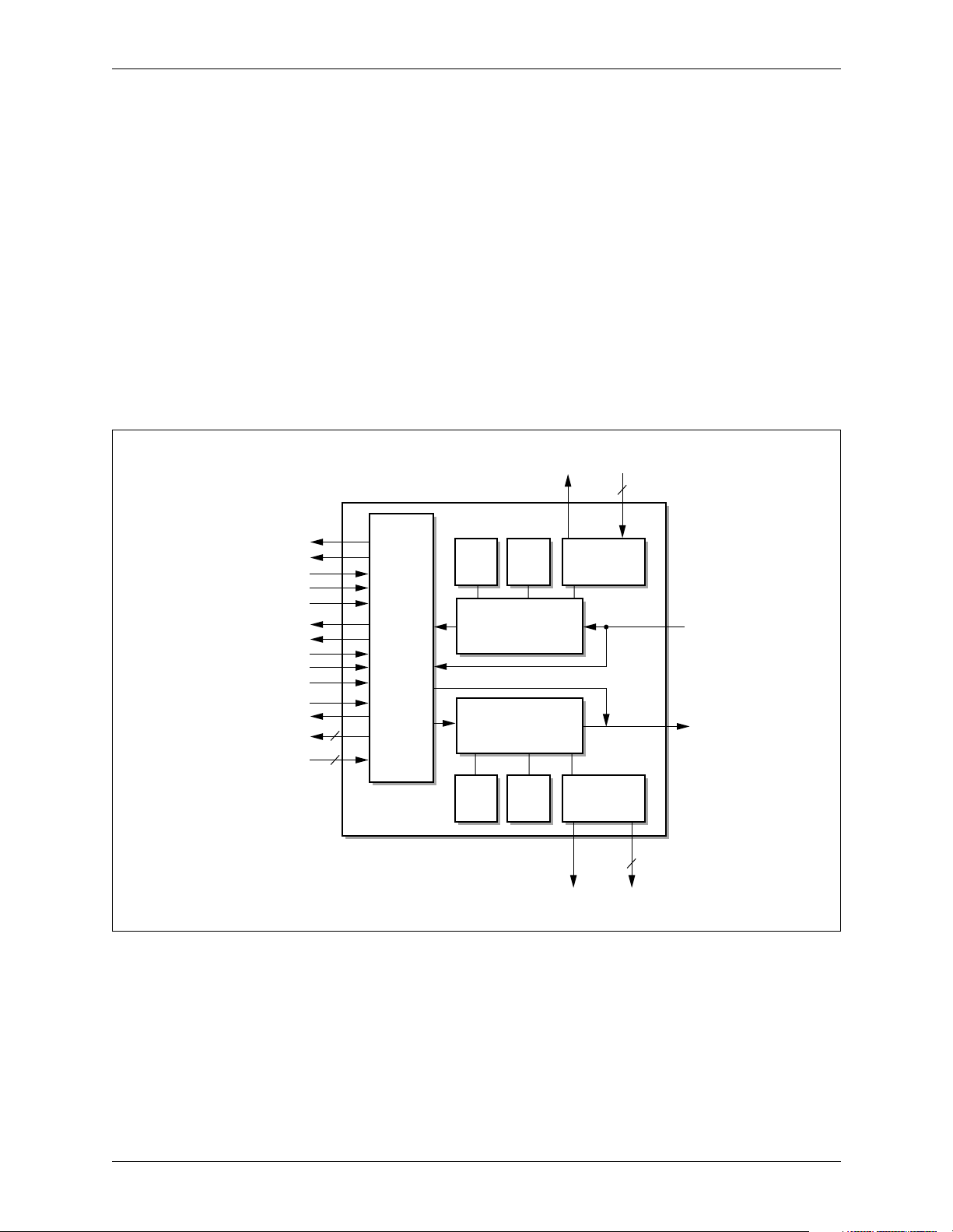

Figure 1-2. Line Framer Diagram

TCLKO_HS

TXOUT_HS

TXCKI_HS±

RXCKI_HS±

RXIN_HS±

TCLKO

TXOUT

TXCKI

RXCKI

RXIN

RCV_HLD

LOCD

TXOUT[7:0]

RXIN[7:0]

±

±

9

9

Line

Interfaces

High

Speed

Medium

Speed

Parallel

Interface

TMRKR

TOVH_CLK

Tx

HDLC

DS3, E3, E4, STS-1

Transmit Framer

DS3, E3, E4, STS-1

STS-3c, STM-1

Receive Framer

Rx

HDLC

Tx

FEAC

STS-3c, STM-1

Rx

FEAC

1.3 Line Framing Functions

TXOVH

8

Tx

Overhead

Insert

CN8223

Cell

Processing

Rx

Overhead

Extract

8

RMRKR

ROVH_CLK

RXOVH

8223_002

CN8223 line framing functions include the following:

• STS-1, STS-3c, STM-1, DS3, E3, E4, TAXI

• External framer interface

• Parallel interface

• Unframed serial interface

• HDB3/B3ZS encode/decode

• Line overhead insertion/extraction

• SONET scrambling

• Error insertion

• Alarm detection/generation

100046C Conexant 1-5

1.0 Product Description CN8223

1.3 Line Framing Functions ATM Transmitter/Receiver with UTOPIA Interface

1.3.1 Interfaces

The CN8223 has a serial external framer interface for T1, E1, T3, and E3. The

internal B3ZS/HDB3 encoder/decoder can be bypassed in any mode for direct

input/output of NRZ data and clock.

The line signal interface consists of clock, serial or octet data, and sync

signals from either the internal or external framers. Both framed and unframed

modes are usable at DS1, E1, DS3, and E3 line rates. In framed mode, the

frame/overhead bit positions of the transmission format are located through a

synchronization signal and are generated as idle bits or ignored. In unframed

mode, a serial signal that contains no line overhead bit positions is expected.

The transmitter interface has a clock signal input and provides a serial or octet

data output. The receive signal interface consists of input clock and serial or octet

data from the transmission physical layer framer. Also, synchronization inputs are

provided for use with external framers. The transmit and receive sections of the

interface are clocked independently.

A parallel line interface is available for external framers and other devices. It

consists of a receive clock and octet and a transmit clock and octet. This interface

permits clocking externally recovered octets directly to and from the cell

delineation function block. Use of the parallel interface assumes all line overhead

information has been removed externally and proper octet alignment has been

recovered.

1.3.2 Line Loopback

A line loopback connects the receive clock and data inputs directly to the transmit

clock and data outputs. LCVs are preserved in this loopback. Raw yellow alarm

indications and Out-of-Frame (OOF) events are integrated to provide yellow

alarm and Loss-of-Frame (LOF) indications, respectively. PHY error counters can

be programmed to accumulate errors over one-second periods and latch the

results. Line framing functions are described in detail in Section 2.2.

1-6 Conexant 100046C

CN8223 1.0 Product Description

ATM Transmitter/Receiver with UTOPIA Interface

1.3.3 BIP-8 Code

The octet Bit Interleaved Parity (BIP-8) code is checked and error status

generated for the Far End Block Error (FEBE) function and yellow alarm. BIP-8

code violations and framing-octet errors are counted. OOF events are detected

and counted. The transmitter output can be looped to the receiver input for test

purposes and to perform startup self-tests and diagnostics.

In all PHY modes, an OOF input from the internal or external framer can be

used to indicate that the received signal is not being received correctly. This input

inhibits cell validation functions and initiates cycle stuffing, when required.

1.3.4 Alarm Detection/Generation

All line alarm and error conditions including BIP codes are monitored and

reported in status registers and event counters. Alarms and errors can be

configured to generate an interrupt to the microprocessor. The CN8223 can

transmit alarm and error conditions under microprocessor control.

1.3 Line Framing Functions

100046C Conexant 1-7

1.0 Product Description CN8223

1.4 ATM Cell Processing Functions ATM Transmitter/Receiver with UTOPIA Interface

1.4 ATM Cell Processing Functions

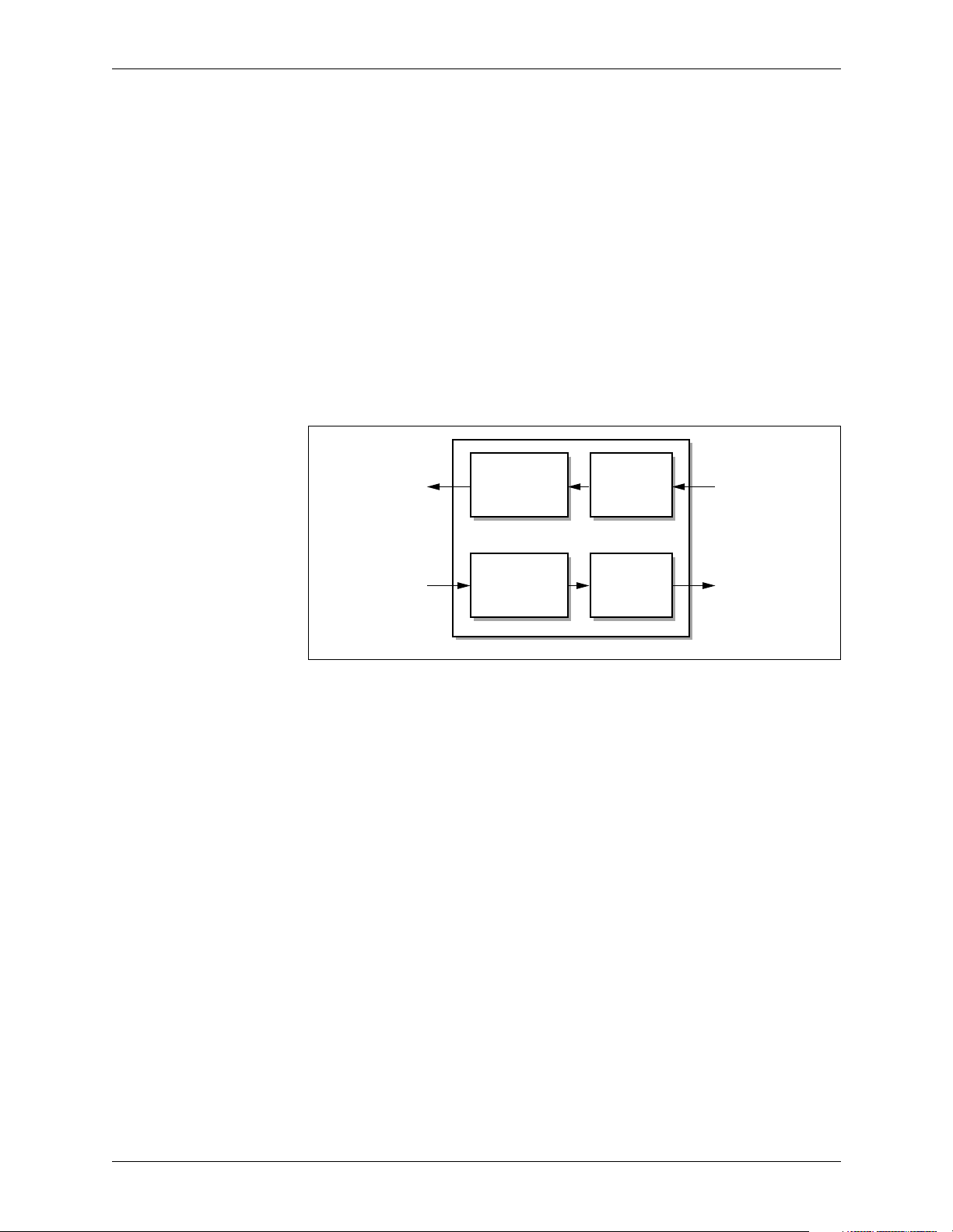

Figure 1-3 illustrates the CN8223 cell processing block, which assembles

received octet data from the line framers into ATM cells. During transmit, this

block constructs ATM cells for the line transmitter circuits. The ATM cell

processing block can generate or receive either the 57-octet framed PLCPs or the

53-octet direct-mapped formats. Status indications include 16-bit counters for

PLCP OOF or Loss-of-Cell (LOC) delineation events, framing-octet errors, and

BIP-8 code violations for both the near and far end. All alarm indications are

provided and can be programmed to generate interrupts.

Figure 1-3. CN8223 Cell Processing Block

Transmit G.832

and PLCP

Framer

Line Framers

Block

Receive G.832

and PLCP

Framer

Tx Cell

Generation,

Tx Rate

and Priority

FIFO/UTOPIA

Ports Block

Rx Cell

Validation

Rx VPI/VCI

Screening

CN8223 cell processing block features include the following:

• Selectable HEC or PLCP alignment

• HEC calculation for ATM or SMDS

• HEC correction

• HEC Coset generation

• PLCP overhead control

• PLCP events and alarms control

• AAL3/4 CRC and length check support

• SONET scrambling

• ATM payload scrambling

• Error insertion

8223_003

1-8 Conexant 100046C

CN8223 1.0 Product Description

ATM Transmitter/Receiver with UTOPIA Interface

1.4.1 Cell Generation Functions

The CN8223 ATM cell processing block provides flexible control for cell

generation. Cell generation is the formatting of 48-octet payload segments into

53-octet ATM cells, and the generation of appropriate header octets, HEC, and

payload Cyclic Redundancy Check (CRC) calculations as required by the AAL

formats. The CN8223 provides modes that perform this cell generation function,

along with modes that allow insertion of any or all of the various header fields

from either the FIFO interface or from microprocessor control registers. Four cell

generation modes are available in the CN8223. Cell generation functions are

described in detail in Section 2.6.

1.4.2 Tx Rate Control

Two Rate Control registers [0x08, 0x09] are provided for each of the four ports to

allow programmable rate shaping of cell transmission. The ratio of active to idle

cells is programmable with 0.4 % granularity. Status counts of non-idle cells

transmitted are maintained for each of the four sources.

1.4.3 Cell Validation Functions

1.4 ATM Cell Processing Functions

Cell validation refers to the checking of cells coming in from the PHY block for

proper format. The CN8223 provides modes that deliver 48-, 52-, or 53-octet

cells, or 57-octet PLCP slots to the FIFO output ports. The validation process is

described in detail in Section 2.6.

Protocol verification includes HEC validation with ATM or SMDS/802.6

coverage, validation of payload length per segment type, and correct payload

CRC value. Status reporting of validation steps is via error counters and status

register indications. Status bits can be programmed to generate interrupts to the

microprocessor. Each validation step can be individually disabled.

100046C Conexant 1-9

1.0 Product Description CN8223

1.5 FIFO Port/UTOPIA Interface ATM Transmitter/Receiver with UTOPIA Interface

1.5 FIFO Port/UTOPIA Interface

The CN8223 FIFO Port/UTOPIA interface is the data connection for the host

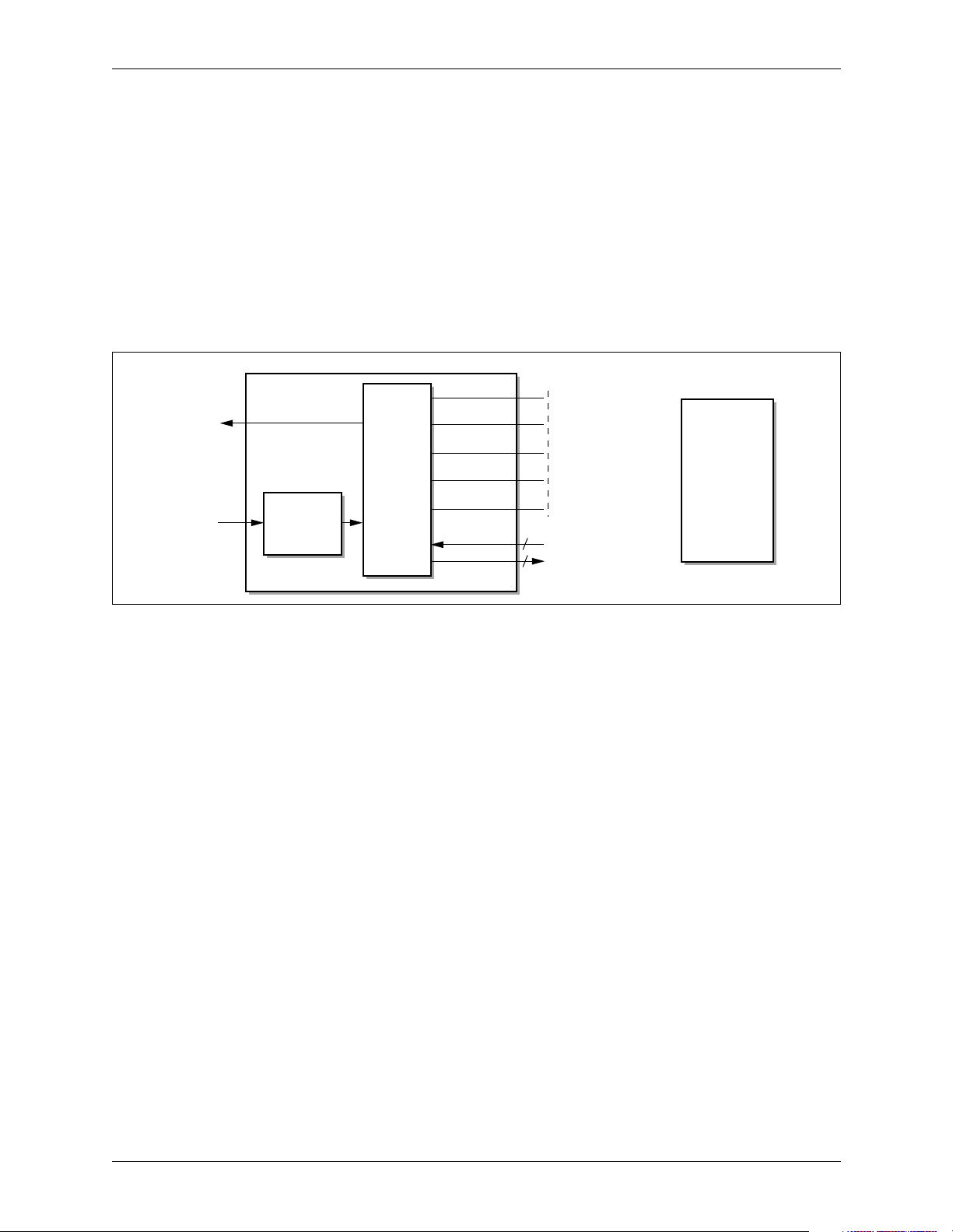

system. Figure 1-4 illustrates the functions in this block. This block has two

modes for interfacing with ATM cells: four FIFO ports or one ATM Forum Level

1 Compliant UTOPIA port.

Figure 1-4. FIFO Port/UTOPIA Interface Block

ATM Cell

Processing

Block

Rx VPI/VCI

1.5.1 UTOPIA Mode

Screening

Port 0 Ctrl

4-Port

FIFO

Data

Interface

UTOPIA

Interface

and

4-Cell

Buffers

FIFO port/UTOPIA interface block features include the following:

• Four byte-wide FIFO ports

• UTOPIA port with four-cell buffer

• Port rate and priority control

• Idle cell TX/Rx

• Per-port ATM header screening

• 48-, 52-, 53-, and 57-octet cell modes

Port 1 Ctrl

Port 2 Ctrl

Port 3 Ctrl

UTOPIA Ctrl

FCTRL_OUT[16:0]

FCTRL_IN[7:0]

9

FDAT_IN

FDAT_OUT

9

ATM Layer

Cell Processing

FIFO

8223_004

UTOPIA mode implements a single 25 MHz, 8-bit plus parity bidirectional

interface with four cells of internal FIFO in both directions. Parity is optional.

When the UTOPIA interface mode is used, only 53-octet output is available.

1.5.2 FIFO Ports

Cells are routed to one of four output ports if a match to that port’s programmable

header value is made. This can be used to route received VCI/VPIs to a chosen

port. Four modes are available for FIFO port cell output:

• A test mode writes the entire 57-octet PLCP slot to the FIFO interface.

• A 53-octet mode writes the 53-octet ATM cell to the FIFO interface.

• A 52-octet mode writes the ATM cell without the HEC octet to the FIFO

interface.

• A final mode delivers 48-octet cell payloads to the FIFO interface.

1-10 Conexant 100046C

CN8223 1.0 Product Description

ATM Transmitter/Receiver with UTOPIA Interface

1.5.3 ATM Interface

Each cell is sent to a buffer to allow for header processing before being output to

the ATM interface. The buffer length is 10 octets for G.751 PLCP modes, and 6

octets for HEC alignment. A “cell-valid” output is provided to indicate that none

of the enabled error checks detected an error. The UTOPIA internal FIFO or

external circuitry is notified to discard the cell when the valid indication goes

inactive. Idle cells are automatically deleted from the ATM layer output. Parity

and control/delineation signals are provided with each octet at the port interface.

The microprocessor receives status and error counts as cell validation proceeds.

All event and error counters can be programmed to cause an interrupt on

overflow. Reading the interrupt source register allows the microprocessor to

identify overflows and thus update internal counts. All counters can be read by the

microprocessor and are cleared when read.

1.5 FIFO Port/UTOPIA Interface

100046C Conexant 1-11

1.0 Product Description CN8223

1.6 Line Interface Applications ATM Transmitter/Receiver with UTOPIA Interface

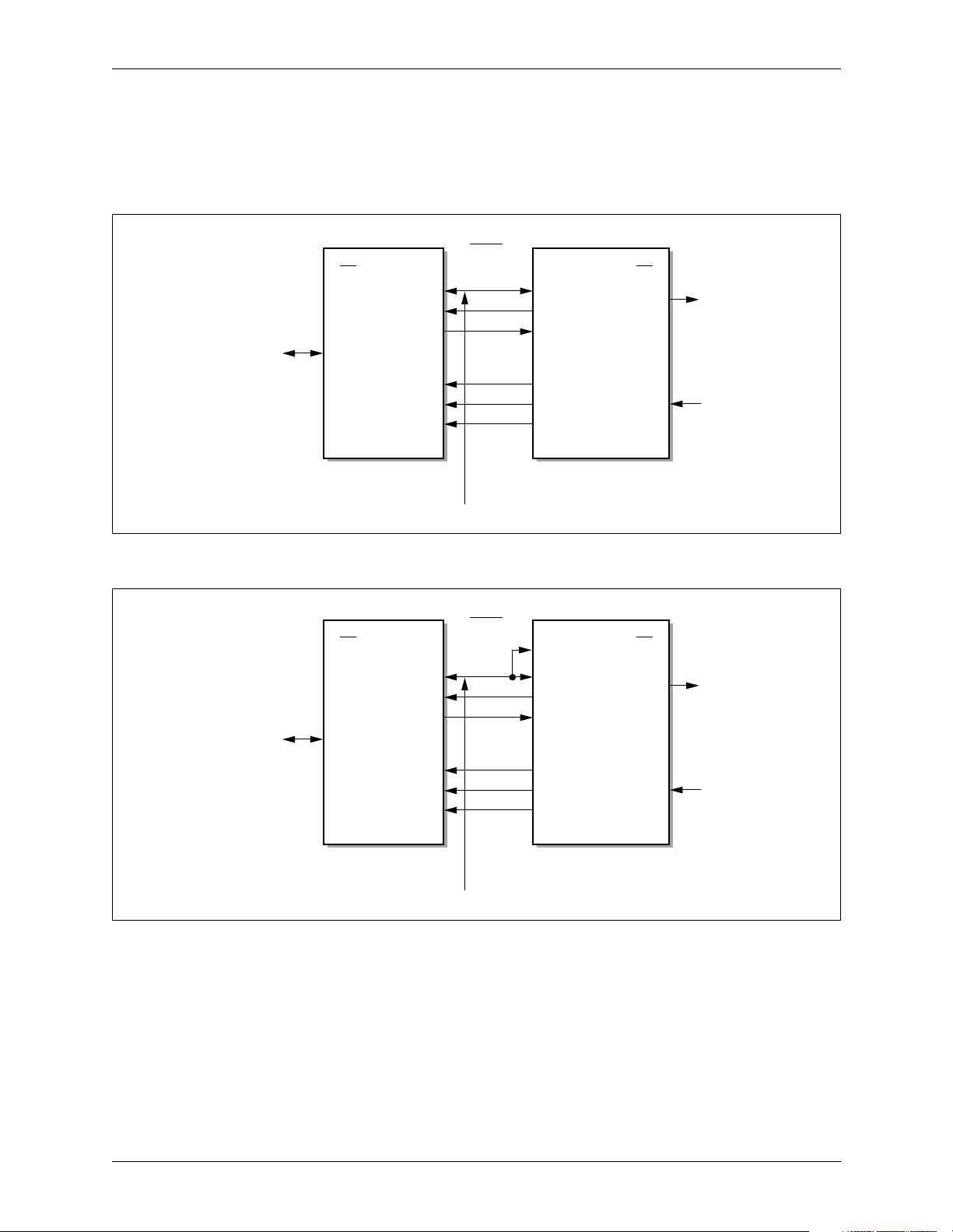

1.6 Line Interface Applications

With minimal glue logic, the CN8223 provides interfaces to STS-3c, STM-1,

DS3, E3, TAXI, DS1, or E1 equipment. Multiple line rates can be supported with

a single design if the line interface is on a daughter card. Figure 1-5 illustrates the

configuration for several line interfaces.

Figure 1-5. Line Interface Applications

SONET

Fiber

Copper

Line

Fiber or

Copper

Copper

Line

STS-3c, STM-1 Interface

Optical

Transceiver

DS3, E3 Interface

Line

Transformer

TAXI Interface

Optical or

Electrical

Interface

DS1 or E1 Interface

Line

Transformer

Clock

Recover

Line

Interface

Unit Chip

AMD

TAXI

Chipset

Bt8360 or

Bt8510 or

Bt8370

CN8223

High-Speed

Serial Line

Interface

CN8223

Low-Speed

Serial Line

Interface

CN8223

External Framer

Parallel Interface

CN8223

External Framer

Serial Interface

CN8223 Signal Names

TXCKI_HS+/–, TCLKO_HS+/–, TXOUT_HS+/–,

RXCKI_HS+/–, RXIN_HS+/–

TXCKI, TCLKO, TXPOS, TXNEG,

RXCKI, RXPOS, RXNEG, RXLOS

TXCKI, TCLKO, TXIN, TXOUT[8:0],

RXCKI, RXIN, TXOUT[8:0], RCV_HLD

TXCKI, TXIN, TXOUT[3],

RXCKI, RXIN[0,3,4]

8223_005

1-12 Conexant 100046C

CN8223 1.0 Product Description

ATM Transmitter/Receiver with UTOPIA Interface

1.7 CN8223 Versions

Table 1 -1 describes the revision history of the Bt8222 device. The Bt8222 is the

predecessor of the CN8223.

Table 1-1. CN8223 Version Descriptions

Version Description

Bt8222KPF Baseline version (derived from the Bt8220/1).

Bt8222KPFB All Bt8222KPF functionality plus:

The version number was changed to 62H in the lower byte of the RX_FEAC_VER register.

A software reset was added to CONFIG_5, bit 7. When active high, this is a software equivalent

to pin 118.

Additional overhead insertion capability for STS-3c, STM-1: G1, K2 #1, and Z2 #3 can be

inserted from the external overhead bus. It is controlled by CONFIG_3, bit 6. This is used for

automatic protection switching.

CONFIG_5 has a new receive status indication. CONFIG_5, bit 9 now shows octet G1, bit 5 of

received frames.

1.7 CN8223 Versions

Bt8222KPFC All Bt8222KPFB functionality plus:

The version number was changed to 63H in the lower byte of the RX_FEAC_VER register.

The STM-1 C2 transmit octet = 0x13. The C2 receive octet is checked for 0x01 or 0x13.

Bt8222KPFD or

Bt8222EPFD

Bt8222EPFE All Bt8222KPFD/EPFD functionality plus:

Bt8222EPFF All Bt8222EPFE functionality plus:

Legend for Version Numbers:

K = Temperature range 0

°C to 85 °C

E = –40

PF = Package code = 160-pin PQFP

A/B/C/D/E = Product version

All Bt8222KPFC functionality plus:

The version number was changed to 64H in the lower byte of the RX_FEAC_VER register.

TAXI command strobe timing eliminates the need for an external buffer.

The G1 octet complies with T1.105. The RDI alarm includes bit 7.

The K1/K2 registers were added to provide further support for SONET APS.

HEC integration was removed.

The device complies with a footnote in the UTOPIA specification that allows RxENB~ to be

permanently asserted by the ATM layer.

Disable HEC Check (bit 9 in CELL_VAL) was changed when in UTOPIA mode to be consistent

with FIFO mode.

Payload checking will comply with the ATM standards (lengths 8-44).

When switching to PLCP mode dynamically, the device will go to an OOF state.

FIFO read strobes are forced inactive (high) during hardware or software resets.

RMRKR[1] was changed to be an 8 kHz output synchronized to the received PLCP frame.

Line Loopback (bit 9) in the CONFIG_3 register (0x02) is cleared upon assertion of RESET (pin

118).

Receive STS/SDH pointer processing complies with standards.

°C to 70 °C

100046C Conexant 1-13

1.0 Product Description CN8223

1.8 CN8223 Applications ATM Transmitter/Receiver with UTOPIA Interface

1.8 CN8223 Applications

The CN8223 can be connected to several types of framers and PMDs. Figure 1-6

illustrates a general application where the CN8223 is connected to either a CAT 5

or Fiber Optic PMD. Figure 1-7 illustrates an example implementation of the

CN8223 using a Bt8360 External T1 Framer.

Figure 1-6. CN8223 Connected to CAT 5 or PMD

UTOPIA

Tx Bus

CN8223

UTOPIA

Rx Bus

Control Bus

Figure 1-7. CN8223 Connected to Bt8360

CN8223

Pin

30

TXCKI

ATM

Layer

Cells

32

36

10

18

15

19

TXIN

TXOUT[3]

RXCKI

RXIN[3]

RXIN[0]

RXIN[4]

TXDATO

RXDATI

RXLOS*

RxData ±

RxCLK ±

TxCLK ±

(Analog Devices

AD6116)

OR

(Cypress

Semiconductor

CX7B952)

Signal

TXCKI

TXSYI

RXCKI

RXSYI

TxData ±

Loss of Signal

Clock Recovery

Circuit

19.44 MHz

Oscillator

XBCKI

XCKI

XBSFSYO

XPCMI

SLSYI

RCKO/SLCKI

RFSYO/SLFSYO

RPCMO/SLPCMO

Bt8360

Pin Pin

29

43

27

30

50

37/49

38/41

36/55

Raw RD ±

7

6

8

63

62

61

CAT 5 UTP

Engineering

(PE-68532G or

PE-68538G)

Transceiver

(Sumitomo

SDM 4201-XC)

XPOSO

XNEGO

XCKO

RPOSI

RNEGI

RCKI

Pulse

OR

Fiber

Module

8223_006

Tx Data

Tx

LIU

Rx Data

Rx

Derived

Tx Clock

System Clock

8223_007

1-14 Conexant 100046C

CN8223 1.0 Product Description

ATM Transmitter/Receiver with UTOPIA Interface

Figure 1-8 illustrates an example implementation of the CN8223 using a

Bt8510 External E1 Framer. Figure 1-9 illustrates an example implementation of

the CN8223 using a Bt8370 External T1/E1 Framer.

Figure 1-8. CN8223 Connected to Bt8510

CN8223

Pin

ATM

Layer

Cells

30

32

36

10

18

15

TXCKI

TXIN

TXOUT[3]

RXCKI

RXIN[3]

RXIN[0]

Signal

TXCKI

TXSYI

T XPAT O

RXCKI

RXSYI

RXDATI

System Clock

XCKI

XSYNCO

XPCMI

RCKO

RSYNCO

RPCMO

Bt8510

Pin

29

27

30

37

38

36

1.8 CN8223 Applications

Tx

Rx

8223_008

Figure 1-9. CN8223 Connected to Bt8370

Pin

30

32

36

10

18

15

ATM

Layer

Cells

CN8223

TXOUT[3]

RXIN[3]

RXIN[0]

TXCKI

TXIN

RXCKI

System Clock

Signal

TXCKI

TXSYI

T XPAT O

RXCKI

RXSYI

RXDATI

TSBCKI

TCKI

TMSYNC

TPCMI

RCKO

RMSYNC

RPCMO

Bt8370

Pin

37

64

36

34

48

44

42

Tx

Rx

8223_009

100046C Conexant 1-15

1.0 Product Description CN8223

1.8 CN8223 Applications ATM Transmitter/Receiver with UTOPIA Interface

Figure 1-10 illustrates an example implementation of the CN8223 using a

TDK 78P7200 T3 LIU. Unused pins on the CN8223 must be tied as follows:

unused RXIN_8:0 pins tie to ground, PECL inputs RXCKI_HS±, RXIN_HS±,

and TXCKI_HS± tie to +5 V.

Figure 1-10. CN8223 Connected to TDK 78P7200

ATM

Layer

Cells

Pin

31

35

34

10

17

16

19

30

CN8223

TCLKO

TXOUT[2]

TXOUT[1]

RXCKI

RXIN[2]

RXIN[1]

RXIN[4]

TXCKI

Signal

System Clock

(44.736 MHz)

TDK 78P7200

TCLK

TNEG

TPOS

RCLK

RNEG

RPOS

LOWSIG

Pin

27

15

14

23

24

25

27

Tx

Rx

8223_010

1.8.1 CN8223 as a DS3 or E3 G.751 Framer without ATM Cell Delineation

The CN8223 can be used as a DS3 or an E3 G.751 framer with parallel input and

serial output by making the following changes:

• Set the configuration registers for transparent operation.

• Disable the parallel interface.

• Disable line loopback.

In this setup, the receive frame sync pulse is on pin 43, TXOUT[5]. Data is

received on pin 56, TXOUT[6]. The receive clock is derived from the LIU device.

Data is transmitted through the parallel UTOPIA interface.

1-16 Conexant 100046C

CN8223 1.0 Product Description

ATM Transmitter/Receiver with UTOPIA Interface

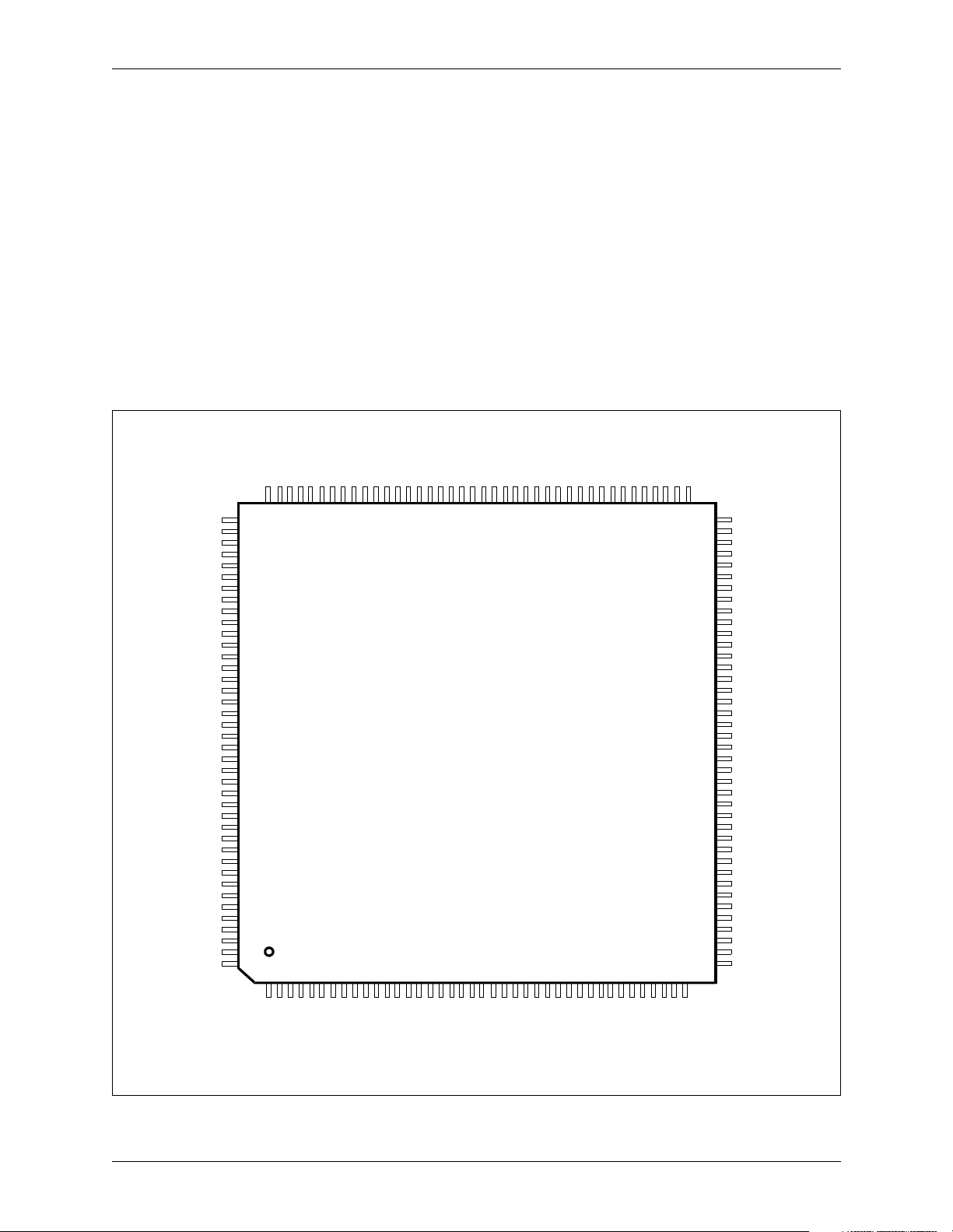

1.9 Logic Diagram

The CN8223 is a single CMOS integrated circuit, packaged in a 160-pin Plastic

Quad Flat Pack (PQFP). Figure 1-11 illustrates a CN8223 logic diagram. The line

framer/PHY interface consists of 33 pins. The framing overhead interface

consists of 22 pins. The FIFO interface consists of 18 data pins, 8 control inputs,

and 17 control outputs. The microprocessor interface consists of 8 clock and

control inputs, a 16-bit data bus, a 7-bit address bus, and 2 interrupt outputs.

Additionally, there are 11 power and 12 ground pins. Detailed pin descriptions are

given in Table 1 -2 .

Clock and control inputs consist of an external 8 kHz reference for the PLCP

at E3 and DS3 rates, a one-second input to synchronize status collection timing in

multiple-port applications, a “hold receiver” input that can externally disable cell

validation when an external framer loses frame or signal, three test inputs, and a

reset input. A one-second clock output is provided to allow synchronization of

status collection for multiple CN8223s or for CN8223s and framers. When a

single CN8223 is used, ONESECO should be connected to ONESECI. This

timing output is derived from the external 8 kHz reference clock input on 8KCKI.

An 8 kHz clock from the line receiver is available on RMRKR[1], pin 8.

1.9 Logic Diagram

NOTE: RMRKR[1] is not available in DS-3 direct cell mapping mode.

100046C Conexant 1-17

1.0 Product Description CN8223

1.9 Logic Diagram ATM Transmitter/Receiver with UTOPIA Interface

Figure 1-11. CN8223 Logic Diagram

Receive Clock Input

Receive Clock In PECL

Receive Serial In PECL

Receive Input

Transmit Clock Input

Transmit Clock In PECL

Transmit Input

Transmit Overhead

Bus In

FIFO Data Bus In

FIFO Control Input

8/16-Bit Mode Select

Processor Clock

Chip Select

Address Strobe

Write/Read Control

Output Enable

Processor Data Bus

Address Bus

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I/O

I

10

11,12

20,21

15–19,

154,155

22,25

30

23,24

32

44–51

98–105,

108

109–116

37

97

96

94

95

92

65,

68–79,

82–84

85–91

RXCKI

RXCKI_HS

RXIN_HS±

RXIN[8:0]

TXCKI

TXCKI_HS

TXIN

Line Framer/PHY

±

±

Framing Overhead

TXOVH[7:0]

UTOPIA/FIFO

FDAT_IN[8:0]

FCTRL_IN[7:0]

SEL8BIT

PRCLK

~

CS

AS~

W/R~

OE~

D[15:0]

A[7:1]

Microprocessor

Interface

Interface

Interface

FCTRL_OUT[16:0]

Interface

TCLKO

TXOUT[8:0]

TCLKO_HS

TXOUT_HS±

LOCD

RXOVH[7:0]

RMRKR[1:0]

ROVH_CLK[1:0]

TOVH_CLK

TMRKR

FDAT_OUT[8:0]

DL_INT

STAT_INT

±

31

33–36,

42,43,

56–58

28,29

38,39

122

2–5,

156–159

8,9

6,7

55

52

143–145,

148–153

124–132,

135–142

63

64

Transmit Clock Output

O

Transmit Outputs

O

Transmit Clock Out PECL

O

Transmit Serial Out PECL

O

Loss of Cell Delineation

O

Receive Overhead Bus Out

O

Receive Overhead Markers

O

O

Receive Overhead Clocks

Transmit Overhead Clock

O

Transmit Overhead Marker

O

O

FIFO Data Bus Out

O

FIFO Control Outputs

OOFEAC/HDLC Interrupt

Status/Counter Interrupt

8 kHz Clock Input

One-Second Clock Sync

Receiver Hold Input

Test Input

Test Inputs

Reset

62

I

I

I

I

117,

I

I

61

123

59

119

118

8KCKI

ONESECI

RCV_HLD

NTEST

TEST1, TEST3

RESET

Clock and Control

I = Input, O = Output

ONESECO

60

O One-Second Output

8223_011

1-18 Conexant 100046C

CN8223 1.0 Product Description

ATM Transmitter/Receiver with UTOPIA Interface

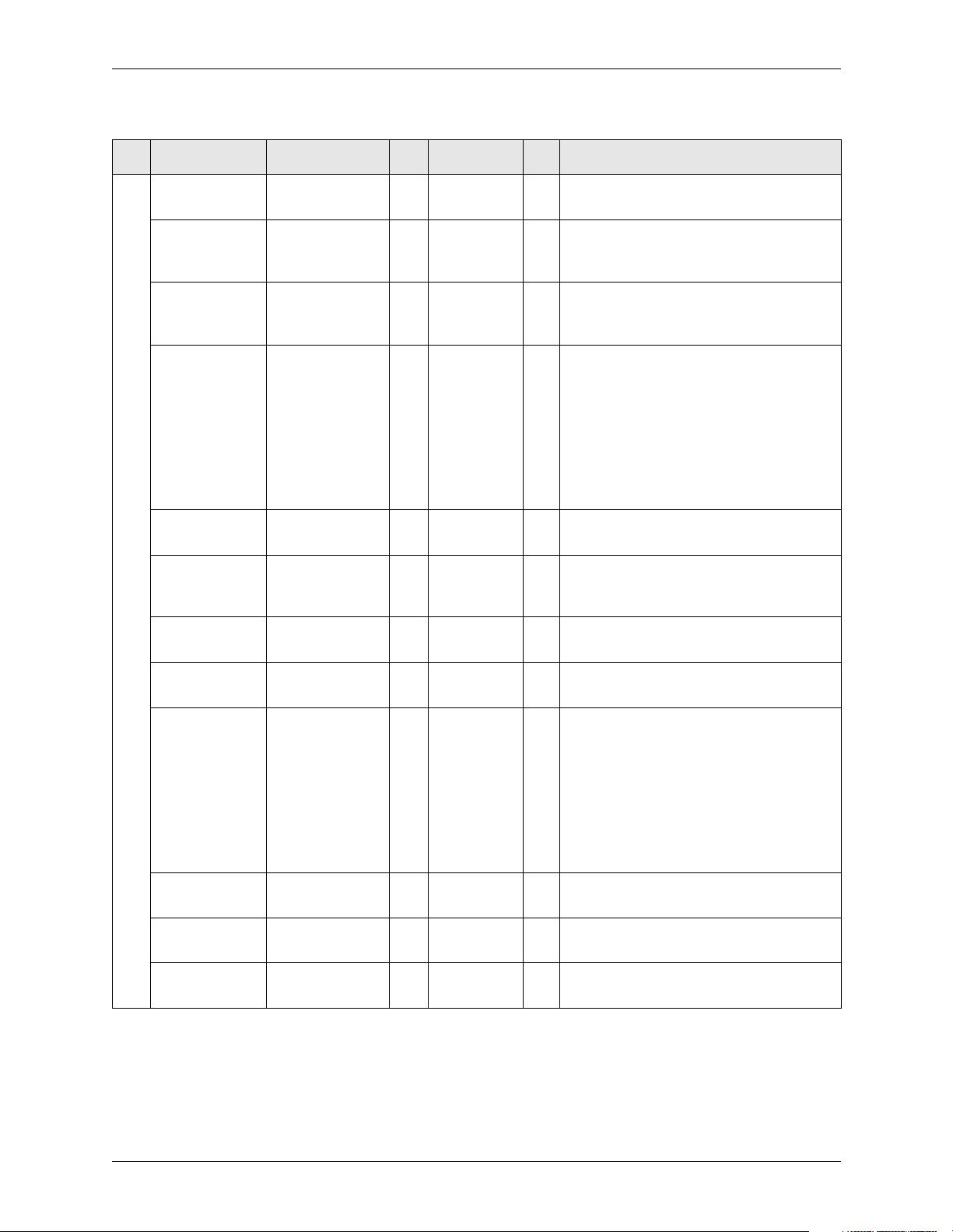

1.10 Pin Definitions

Figure 1-12 is a pinout diagram for the 160-pin ATM Transmitter/Receiver.

Table 1 -2 lists pin names and numbers. Generally, all unused input pins should be

connected to ground and unused outputs should be left unconnected. However, if

pins TXOVH_7 to TXOVH_0 or RXIN_8 to RXIN_0 are not used, they must be

tied to a logic low level. Some of the RXIN pins may be used depending on the

configuration. If PECL inputs, RXCKI_HS±, RXIN_HS±, or TXCKI_HS±, are

not used, they must be tied to +5 V power.

Figure 1-12. CN8223 Pinout Diagram

FDAT_IN[8]

FCTRL_IN[3]

FCTRL_IN[2]

FCTRL_IN[1]

FCTRL_IN[0]

VCC

112

111

110

109

108

107

Transmitter/Receiver

10111213141516171819202122232425262728293031323334353637383940

GND

LOCD

RCV_HLD

FCTRL_OUT[0]

FCTRL_OUT[1]

FCTRL_OUT[2]

FCTRL_OUT[3]

FCTRL_OUT[4]

FCTRL_OUT[5]

FCTRL_OUT[6]

FCTRL_OUT[7]

FCTRL_OUT[8]

GND

VCC

FCTRL_OUT[9]

FCTRL_OUT[10]

FCTRL_OUT[11]

FCTRL_OUT[12]

FCTRL_OUT[13]

FCTRL_OUT[14]

FCTRL_OUT[15]

FCTRL_OUT[16]

FDAT_OU T[0]

FDAT_OU T[1]

FDAT_OU T[2]

GND

VCC

FDAT_OU T[3]

FDAT_OU T[4]

FDAT_OU T[5]

FDAT_OU T[6]

FDAT_OU T[7]

FDAT_OU T[8]

RXIN[7]

RXIN[8]

RXOVH[0]

RXOVH[1]

RXOVH[2]

RXOVH[3]

VCC

VCC

TEST3

119

121

120

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

123456789

RESET

118

TEST1

117

FCTRL_IN[7]

116

FCTRL_IN[6]

115

FCTRL_IN[5]

114

FCTRL_IN[4]

113

GND

106

FDAT_IN[7]

105

FDAT_IN[6]

104

FDAT_IN[5]

FDAT_IN[4]

FDAT_IN[3]

FDAT_IN[2]

FDAT_IN[1]

FDAT_IN[0]

PRCLK

CS*

W/R*

AS*

GND

OE*

A[7]

A[6]

99989796959493929190898887868584838281

103

102

101

100

AT M

CN8223

1.10 Pin Definitions

A[5]

A[4]

A[3]

A[2]

A[1]

D[15]

D[14]

D[13]