CONEX AR P46, AR 20441, AR 20431, AR 11627 Datasheet

Data Sheet (Preliminary)

Conexant Proprietary Information

Doc. No.100394B

October 19, 1999

AccessRunner

ADSL Modem Device Set for PCI Applications

Controller-less, Scalable, Discrete Multitone-based, G.dmt- and G.litecompliant, ADSL Modem Device Set for PCI Applications

Conexant’s AccessRunner ADSL modem device set is compliant

with the full-rate ANSI T1.413 Issue 2 and ITU G.dmt (G.992.1)

ADSL standards, and with the splitterless ITU G.lite (G.992.2)

specification. This rate-adaptive solution is designed for controllerless PCI desktop applications and supports downstream data rates

of up to 8 Mbps and upstream data rates of up to 1 Mbps.

The device set takes advantage of the processing power available

with most new computers by eliminating the need for a separate

microcontroller, resulting in a cost-effective solution suitable for

both G.dmt and G.lite applications. Host-based software provides

support for current industry standards for PPP over AAL5 over

ATM over ADSL and RFC 1483 for Windows 98 and Windows

2000.

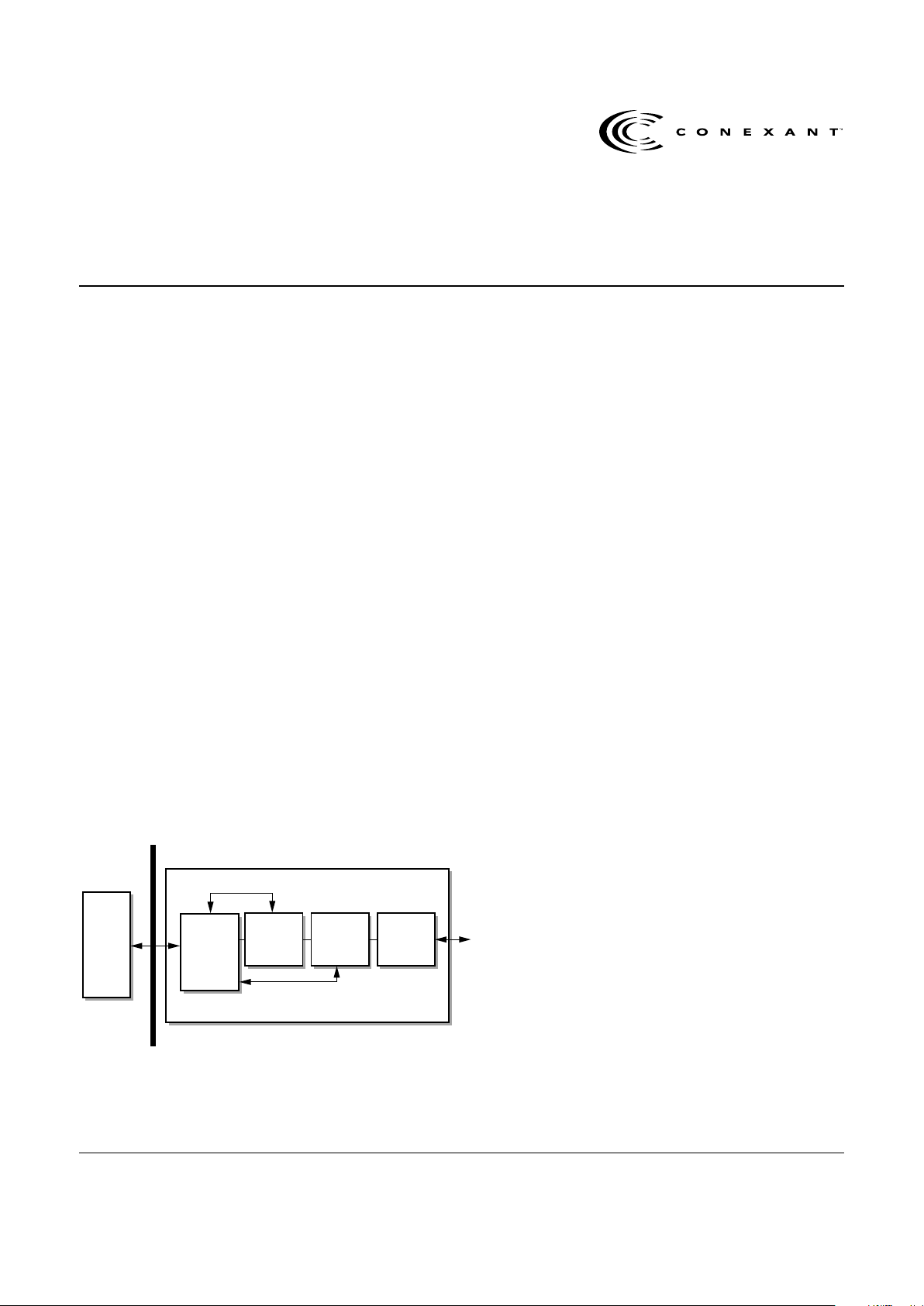

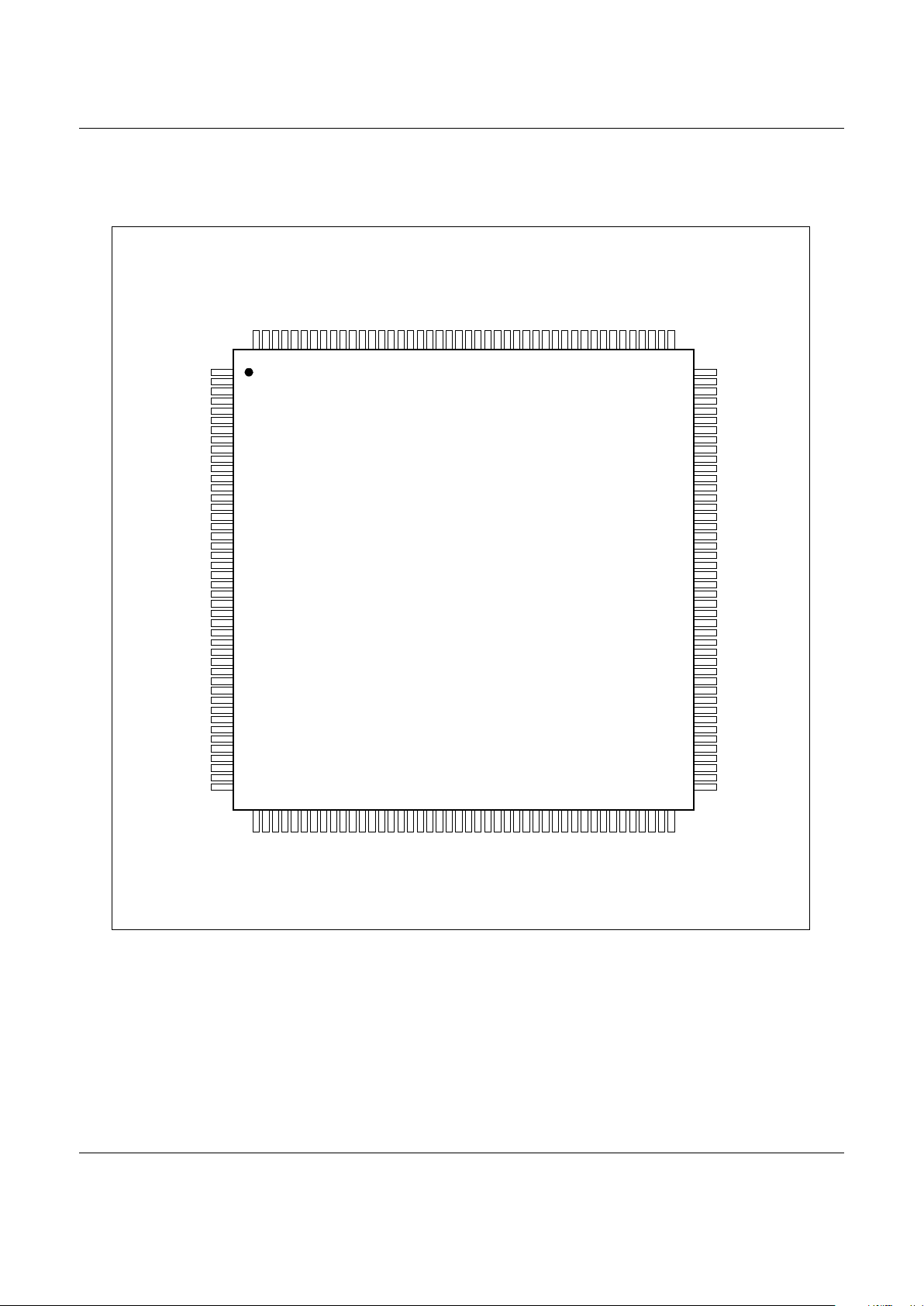

The device set, as shown in Figure 1, consists of four chips:

•

PCI bus interface (AccessRunner P46 in a 176-pin TQFP)

•

DMT-based data pump (AccessRunner 11627 in a 176-pin

TQFP)

•

Analog front end (AccessRunner 20431 in a 32-pin TQFP)

•

Line driver (AccessRunner 20441 in a 16-pin SSOP or

32-pin TQFP)

PCI Bus

HostBased

ADSL

Controller

Software

P46

PCI Bus

Interface

176-pin TQFP

11627

ADSL DMT

Data Pump

176-pin TQFP

20431

Analog Front

End

32-pin TQFP

20441

Line Driver

16-pin TSSOP

Telephone

Line

Figure 1. AccessRunner ADSL Modem for PCI Applications

Features

•

Complete controller-less PCI ADSL

solution

•

Compliant with ADSL standards

−

Full-rate ANSI T1.413 Issue 2 and ITU

G.dmt (G.992.1) standards

−

Splitterless ITU G.lite (G.992.2)

specification

•

DMT modulation and demodulation

•

Full-rate adaptive modem

−

Maximum downstream rate of 8 Mbps

−

Maximum upstream rate of 1 Mbps

•

Supports splitterless ADSL

implementation

•

WAN mode support: PPP over AAL5/ATM

over ADSL via Windows 98/2000

•

LAN mode support: RFC 1483 via

Windows 98/2000

•

Compliant with PCI Local Bus

Specification, Revision 2.2

•

Compliant with PCI Bus Power

Management Interface Specification,

Version 1.0

•

Tone detection for low power mode

D20431 AFE Features

•

Receive signal path includes:

−

Integrated hybrid receiver circuit with

programmable gain

−

High pass filtering and 27dB of

Automatic Gain Control (AGC) to

improve signal-to-echo ratio

−

14-bit ADC

•

Transmit signal path includes:

−

30dB of AGC for transmit power control

−

Low pass filtering to suppress noise in

the receive band

−

14-bit DAC

•

Independent digital serial data and control

interfaces

•

Low power tone detection mode.

AccessRunner

Controller-less ADSL Modem Device Set for PCI Applications

2

Conexant

Doc. No. 100394B

Proprietary Information October 19, 1999

ADSL (Asymmetric Digital Subscriber Line) is a transmission

technology used to carry user data over a single twisted pair line

from the Central Office to the customer premises. The downstream

(Central Office to Customer Premises) direction typically supports

a much higher data rate than the upstream or return (Customer

Premises to Central Office) channel. This asymmetric nature lends

itself to applications like remote LAN access, Internet access, and

video delivery. The downstream data rates can go up to 8 Mbps.

The upstream data rates can go up to 1 Mbps. Actual data rates

depend on the transceiver implementation, loop length,

impairments, and transmitted power.

The Conexant ADSL Modem Device Set for PCI Applications is

based upon a scalable architecture. This architecture will enable

the device set to support an emerging set of ADSL specifications

called G.lite. G.lite is expected to make it possible for telcos to

deploy consumer-oriented, “always on” 1.5 Mbps Internet access

services without the need for splitter equipment or wiring changes

at the customer premises.

D20441 Line Driver Features

•

Differential input and output line driver

•

Thermal shutdown capability

•

Line impedance matching during powerdown

•

Fixed differential gain

11627 ADSL DMT Data Pump

Features

•

Low power (0.5W) consumption

•

DSP-based programmable ADSL data

pump

•

No external Interleave RAM, 16 Kbytes

built-in

•

Single 3.3V ± 5% power supply

•

Echo cancellation

•

Digital interface and rate buffering

•

ADSL framing

•

Forward Error Correction (FEC) encoding

and decoding and interleaving

•

Constellation encoding/decoding

•

IFFT modulation and FFT demodulation

•

Transmit and receive signal digital filtering

•

Time domain equalization

•

Frequency domain equalization

•

Clock recovery

•

CRC and scrambling

•

Digital interface framing

•

ATM mode

•

Bit-synchronous mode

Ordering Information

Product Package Device Number

AccessRunner P46

PCI Bus Interface 176-pin TQFP P46

AccessRunner 11627

ADSL Discrete Multit one (DM T ) Dat a Pump 176-pin TQFP 11627

AccessRunner 20431

Analog Front End 32-pin TQFP 20431

16-pin SSOP 20441-12

AccessRunner 20441

Line Driver

32-pin TQFP 20441-11

Revision History

Revision Date Comments

A 07/09/99 Initial release

B 10/19/99 Defined dash numbers and updated figures f or 20441 l ine driver, changed document number f rom DS L-

015, A

Information provided by Conexant Systems, Inc. is believed to be accurate and reliable. However, no responsibility is assumed by Conexant for its use, nor any

infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of

Conexant other than for circuitry embodied in Conexant products. Conexant reserves the right to change circuitry at any time without notice. This document is

subject to change without notice.

Conexant products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Conexant product can reasonably be

expected to result in personal injury or death. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree

to fully indemnify Conexant for any damages resulting from such improper use or sale.

Conexant, “What's Next in Communications Technologies”, AccessRunner, LANfinity, and the Conexant logo, are trademarks of

Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective

companies. All other marks mentioned herein are the property of their respective owners.

©1999, Conexant Systems, Inc.

All Rights Reserved

Controller-less ADSL Modem Device Set for PCI Applications AccessRunner

Doc. No. 100394B

Conexant

3

October 19, 1999 Proprietary Information

Detailed Description

P46 PCI Bus Interface

The P46 PCI bus interface is the bridge device

between the 11627 ADSL DMT data pump and the

host computer. It provides the control, interface, and

data manipulation for the 11627 data pump, the

20431 AFE, the 20441 line driver, and hybrid

circuitry. It is compliant with the PCI Local Bus

Specification, Revision 2.2 and PCI Bus Power

Management Interface Specification, Version 1.0.

20431 Analog Front End

The 20431 AFE is designed for use in full-rate and

G.lite (G.992.2) ADSL modems. The ADSL AFE

interfaces with the transmit line driver (20441) and

the hybrid receive circuitry on the analog side, and

with the ADSL DMT data pump (11627) on the digital

side. The receive section filters out the unwanted

echo and boosts the wanted signal before

performing an A/D conversion. The transmit section

converts digital data to analog signals and performs

a smoothing operation before presenting the signals

to the line driver.

The 20431 is designed to operate from a 3.3V supply

(nominal), assuming that it is regulated within ± 5%. The

maximum allowable supply voltage is 3.6V.

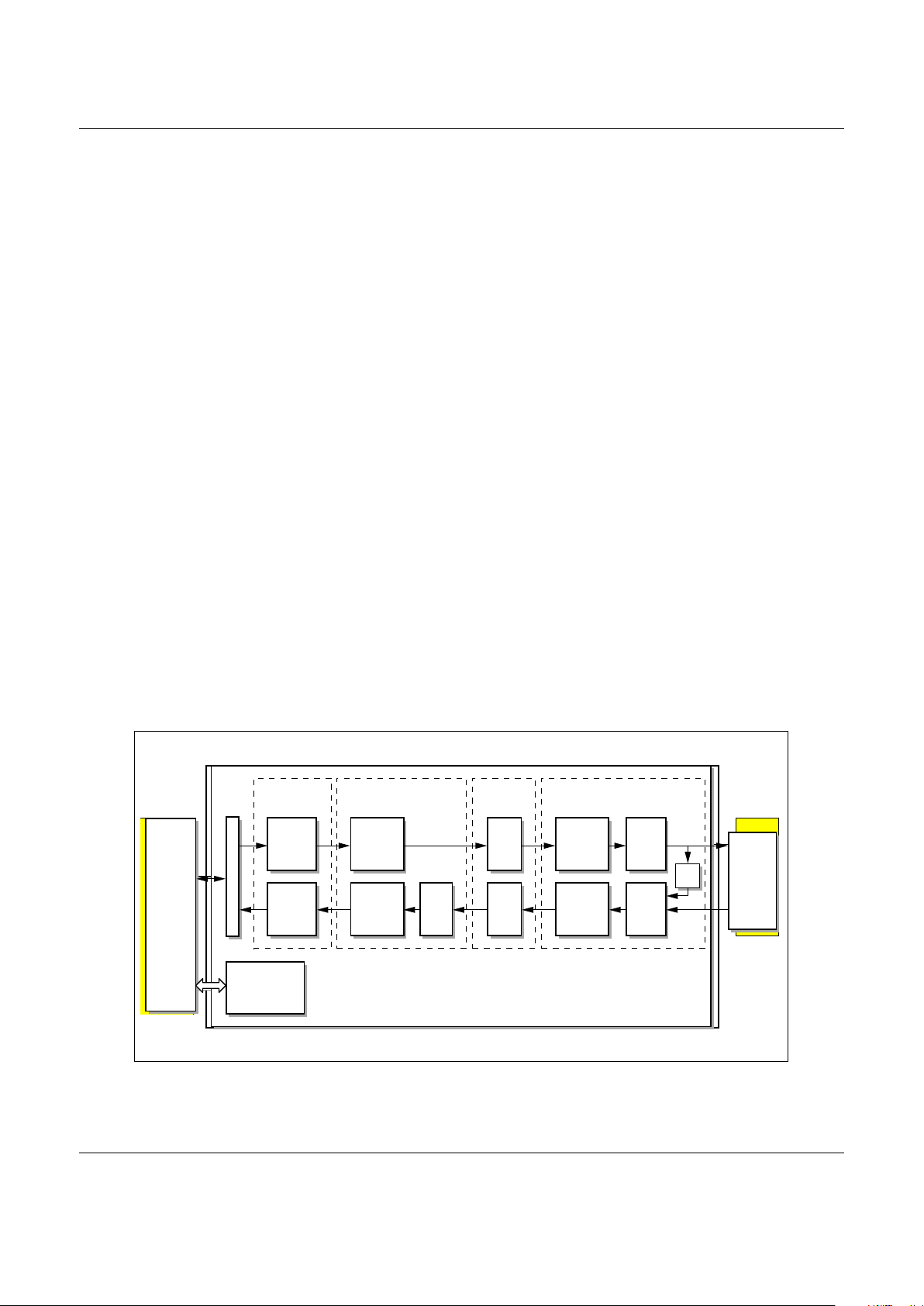

11627 ADSL DMT Data Pump

The 11627 DMT data pump is a T1.413 Issue 2 and

G.992.1 compliant custom digital signal processing

(DSP) chip built specifically for DMT ADSL

transmission for use in ADSL modems. Brief

descriptions of each functional block within the data

pump are provided in the following sections; refer to

Figure 2.

ATM Transmission Convergence (TC)

In the transmit direction, this block is in charge of

embedding ATM cells into the serial data streams

being fed into the digital interface.

In the receive direction, this block extracts the ATM

cell boundaries from the serial data streams coming

from the digital interface.

To reduce traffic on the PCI bus, the TC block

performs idle cell insertion in the transmit direction

and idle cell deletion and header error correction in

the receive direction.

DSL015002

ATM TC

DI

Transmit

Block

DI

Receive

Block

Digital

Interface (DI)

Bit Parser

and QAM

Encoder

QAM

Decoder

and Bit

Parser

AM EncoderDecoder

FEQ

IFFT

FFT

FFT

Transmit

Filter

Time

Domain

Equalizer

ADC

Intf

AFE Interface

DAC

Intf

PCI

Controller

(P46)

Microcontroller

Interface

AFE

(20431)

DMT Data Pump (11627)

EC

Figure 2. AccessRunner 11627 DMT Data Pump Functional Block Diagram

AccessRunner

Controller-less ADSL Modem Device Set for PCI Applications

4

Conexant

Doc. No. 100394B

Proprietary Information October 19, 1999

Digital Interface (DI)

The DI Transmit Block performs the following

functions: transmit data multiplexing and buffering,

fast and interleave data stream framing, transmit

data synchronization control, eoc/aoc insertion, CRC

encoding, scrambling, FEC encoding, and data

interleaving.

The DI Receive Block performs the following

functions: data de-interleaving, FEC decoding,

descrambling, CRC check, receive data

synchronization and receive clock generation,

demultiplexing and buffering of receive data and

receive eoc/aoc.

QAM Encoder/Decoder

The QAM Encoder/Decoder performs the following

functions: constellation encoding, clock recovery,

receive gain compensation, frequency domain

equalization (FEQ), slicing, and constellation

decoding. The block also performs other functions

like frequency domain signal processing, signal

power, error power averaging and computations

related to frequency domain training.

FFT

The FFT performs IFFT for modulation of the

transmit symbol, and FFT for demodulation of the

receive symbol.

Analog Front End (AFE) Interface

The AFE Interface performs the following functions:

transmit signal filtering, time domain equalization,

and time domain signal power averaging, and echo

cancellation (EC).

Microcontroller Interface

The microcontroller interface enables the host

computer via the PCI controller to set parameters to

control DSP sequencing and to read/write

coefficients or data.

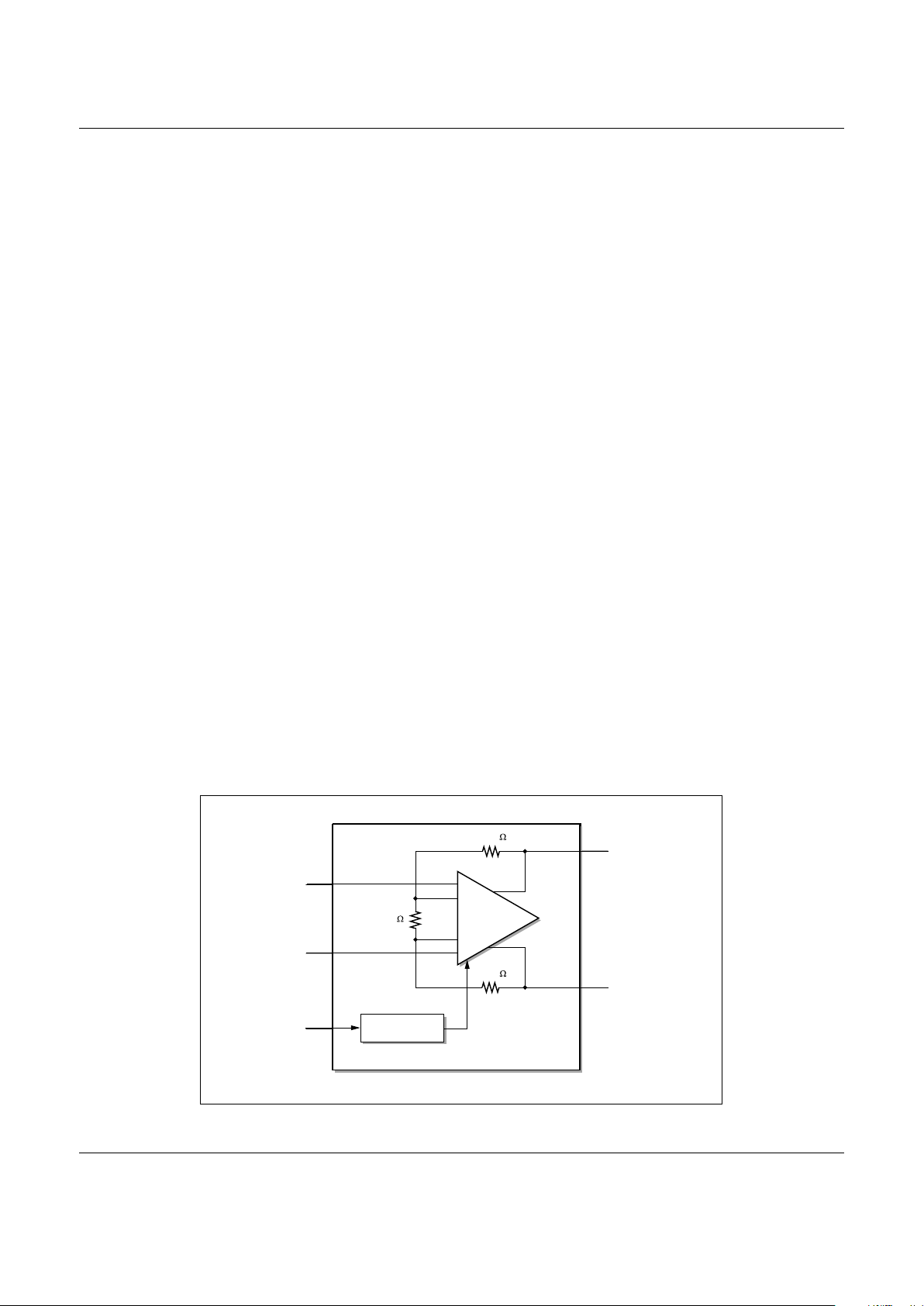

20441 Line Driver

The 20441 line driver is designed for use in full-rate

and G.lite (G.992.2) ADSL modems. It is optimized

for ideal ADSL performance providing low noise,

high bandwidth, and superior linearity. The 20441

line driver transmits a DMT modulated signal in the

25 – 132 kHz band. It operates from a single 5V

±TBD% supply, refer to

Figure 3.

The driver is optimized for ADSL performance: it has

a very low noise figure, high bandwidth and good

linearity.

()

Current Control

Block

Line Driver

(20441)

+

+

+

248.4

248.4

400

OUTP_DRV

OUTM_DRV

INP_DRV

INM_DRV

RBIAS

DSL015_003

Figure 3. AccessRunner 20441 Line Driver

Controller-less ADSL Modem Device Set for PCI Applications AccessRunner

Doc. No. 100394B

Conexant

5

October 19, 1999 Proprietary Information

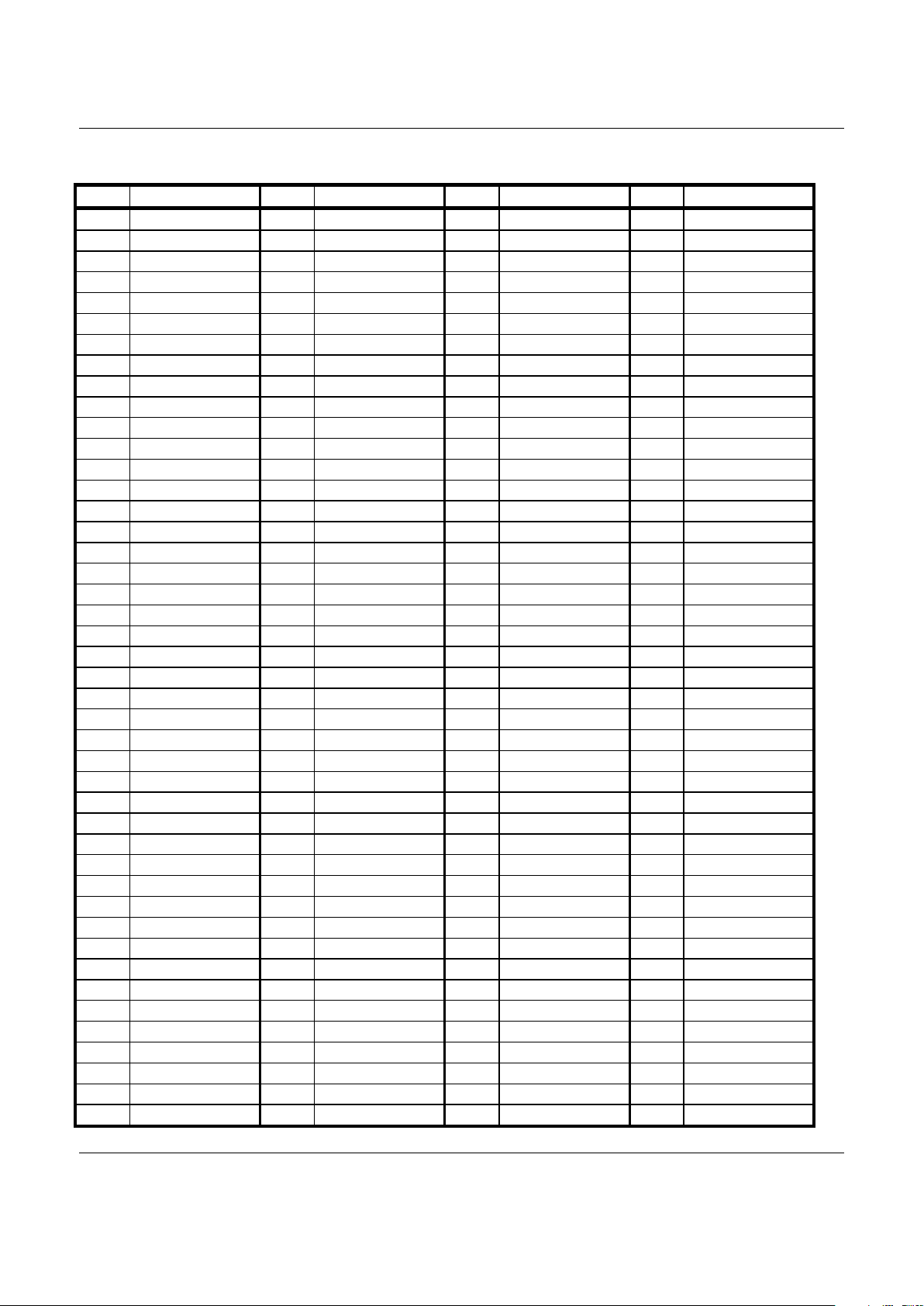

P46 PCI Bus Interface Device Hardware Pins and Signals

The pin assignments for the P46 are shown in Figure 4 and listed in Table 1. The signals are defined in Table 2.

45464748495051525354555657585960616263646566676869707172737475767778798081828384858687

88

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

VDD

DP_WR#

DP_A[0]

DP_A[1]

DP_A[2]

DP_A[3]

DP_A[4]

DP_A[5]

DP_A[6]

DP_A[7]

GND

DP_A[8]

DP_A[9]

VDD

DP_IRQ#[0]

DP_IRQ#[1]

AFE_WAKEUP

AFE_CTRLOUT

AFE_CTRLIN

AFE_STB

AFE_SCLK

GND

DP_RDATAS0

DP_RXSOC0

VDD

DP_RCLKAS0

DP_TDATLS0

DP_TXSOC0

DP_TCLKLS0

GND

NC

VDD

PCI_VAUXDET

PCI_VPCIDET

NC

PCI_VAUXEN#

PCI_VPCIEN#

NC

SCANMODE

SCANEN

GNDNCNC

NC

VDD

PCI_AD[7]

PCI_AD[6]

GND

PCI_AD[5]

PCI_AD[4]

VDD

PCI_AD[3]

PCI_AD[2]

GND

PCI_AD[1]

PCI_AD[0]

VDD

PCI_PME

EEPROM_DIN

EEPROM_DOUT

EEPROM_CLK

EEPROM_CS

VDD

VGG2

DP_D[0]

DP_D[1]

GND

DP_D[2]

DP_D[3]

GND

DP_D[4]

DP_D[5]

VDD

DP_D[6]

DP_D[7]

DP_D[8]

DP_D[9]

DP_D[10]

DP_D[11]

GND

DP_D[12]

DP_D[13]

VDD

DP_D[14]

DP_D[15]

DP_CS#

DP_RD#

GND

VDD

PCI_AD[24]

PCI_CBE#[3]

PCI_IDSEL

GND

PCI_AD[23]

PCI_AD[22]

VDD

PCI_AD[21]

PCI_AD[20]

GND

PCI_AD[19]

PCI_AD[18]

VDD

PCI_AD[17]

PCI_AD[16]

GND

PCI_AD[15]

PCI_CBE#[2]

VDD

PCI_FRAME#

PCI_IRDY#

GND

PCI_TRDY#

PCI_DEVSEL#

PCI_STOP#

PCI_PERR#

VDD

PCI_SERR#

PCI_PAR

PCI_CBE#[1]

GND

PCI_AD[14]

PCI_AD[13]

VDD

PCI_AD[12]

PCI_AD[11]

GND

PCI_AD[10]

PCI_AD[9]

VDD

PCI_AD[8]

PCI_CBE#[0]

GND

PCI_INTA#

PCI_RST#

VDD

PCI_CLK

GND

PCI_GNT#

PCI_REQ#

PCI_AD[31]

VDD

PCI_AD[30]

PCI_AD[29]

GND

PCI_AD[28]

PCI_AD[27]

VDD

PCI_AD[26]

PCI_AD[25]

GND

VGG1

VDD

GPIN0

GPIN1

GPIO[0]

GPIO[1]

GPIO[2]

GPIO[3]

GND

VDD

GPIO[4]

GPIO[5]

GPIO[6]

GPIO[7]

GND

VDD

GPIO[8]

GND

TDI_GPIO[9]

TMS_GPIO[10]

VDD

TRSTN_GPIO[11]

REFCLK

PCI_VPCIPREFER

TCK

TDO

DSL015004

Figure 4. P46 Pinout Diagram

AccessRunner

Controller-less ADSL Modem Device Set for PCI Applications

6

Conexant

Doc. No. 100394B

Proprietary Information October 19, 1999

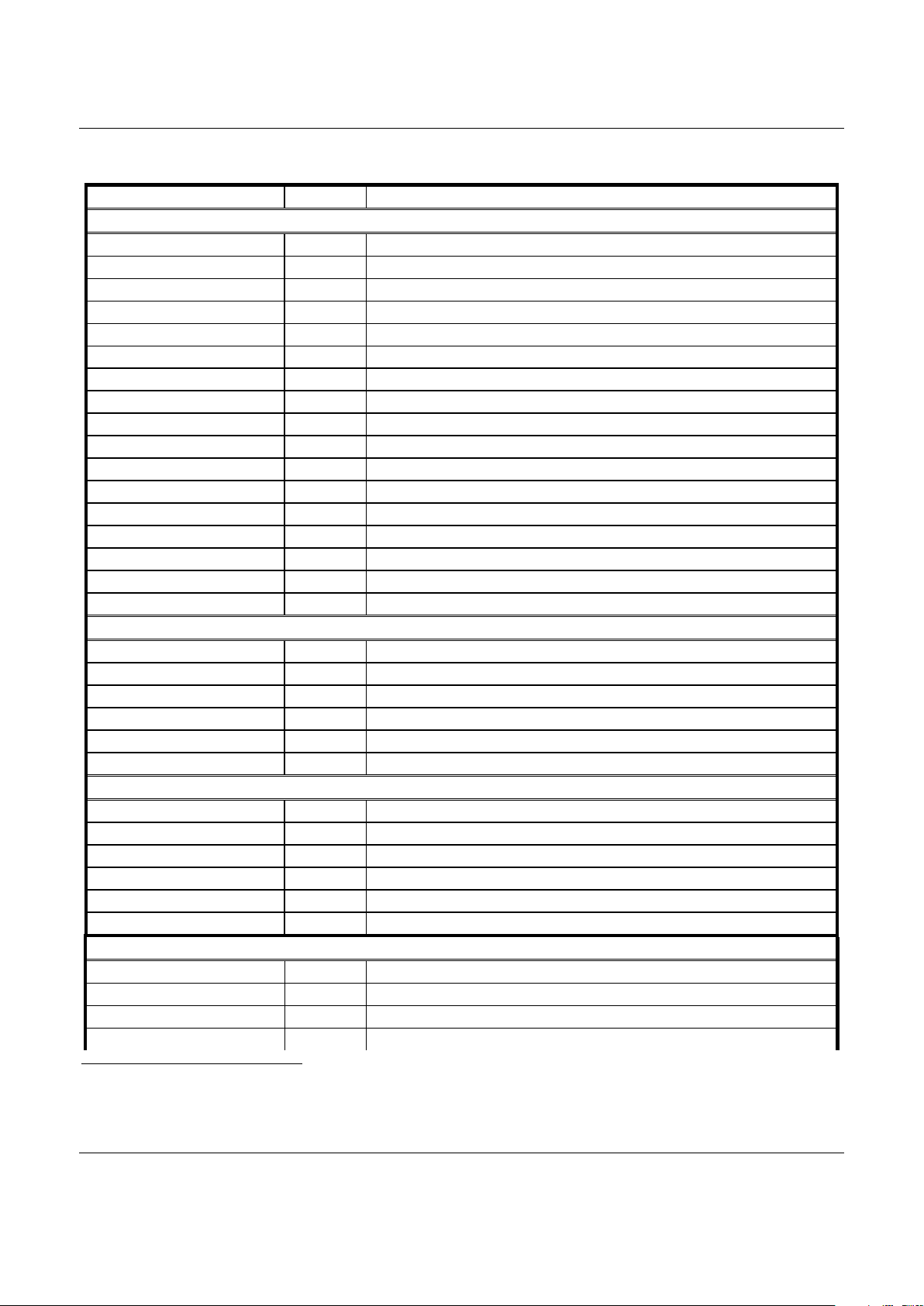

Table 1. P46 Pin Designations by Number

Pin No. Signal Pin No. Signal Pin No. Signal Pin No. Signal

1 VDD 45 VDD 89 VDD 133 VDD

2 GPIN0 46 PCI_AD[24] 90 PCI_AD[7] 134 DP_WR#

3 GPIN1 47 PCI_CBE#[3] 91 PCI_AD[6] 135 DP_A[0]

4 GPIO[0] 48 PCI_IDSEL 92 GND 136 DP_A[1]

5 GPIO[1] 49 GND 93 PCI_AD[5] 137 DP_A[2]

6 GPIO[2] 50 PCI_AD[23] 94 PCI_AD[4] 138 DP_A[3]

7 GND 51 PCI_AD[22] 95 VDD 139 DP_A[4]

8 GPIO[3] 52 VDD 96 PCI_AD[3] 140 DP_A[5]

9 GPIO[4] 53 PCI_AD[21] 97 PCI_AD[2] 141 DP_A[6]

10 VDD 54 PCI_AD[20] 98 GND 142 DP_A[7]

11 GPIO[5] 55 GND 99 PCI_AD[1] 143 GND

12 GPIO[6] 56 PCI_AD[19] 100 PCI_AD[0] 144 DP_A[8]

13 GPIO[7] 57 PCI_AD[18] 101 VDD 145 DP_A[9]

14 GPIO[8] 58 VDD 102 PCI_PME 146 VDD

15 GND 59 PCI_AD[17] 103 VGG2 147 DP_IRQ#[0]

16 TDI_GPIO[9] 60 PCI_AD[16] 104 EEPROM_DIN 148 DP_IRQ#[1]

17 TMS_GPIO[10] 61 GND 105 EEPROM_DOUT 149 AFE_WAKEUP

18 VDD 62 PCI_AD[15] 106 EEPROM_CLK 150 AFE_CTRLOUT

19 REFCLK 63 PCI_CBE#[2] 107 EEPROM_CS 151 AFE_CTRLIN

20 TRSTN_GPIO[11] 64 VDD 108 VDD 152 AFE_STB

21 PCI_VPCIPREFER 65 PCI_FRAME# 109 DP_D[0] 153 AFE_SCLK

22 VDD 66 PCI_IRDY# 110 DP_D[1] 154 GND

23 TCK 67 GND 111 GND 155 DP_RDATAS0

24 TDO 68 PCI_TRDY# 112 DP_D[2] 156 DP_RXSOC0

25 GND 69 PCI_DEVSEL# 113 DP_D[3] 157 VDD

26 PCI_INTA# 70 PCI_STOP# 114 GND 158 DP_RCLKAS0

27 PCI_RST# 71 PCI_PERR# 115 DP_D[4] 159 DP_TDATLS0

28 VDD 72 VDD 116 DP_D[5] 160 DP_TXSOC0

29 PCI_CLK 73 PCI_SERR# 117 VDD 161 DP_TCLKLS0

30 GND 74 PCI_PAR 118 DP_D[6] 162 GND

31 PCI_GNT# 75 PCI_CBE#[1] 119 DP_D[7] 163 PCI_VAUXDET

32 PCI_REQ# 76 GND 120 DP_D[8] 164 PCI_VPCIDET

33 PCI_AD[31] 77 PCI_AD[14] 121 DP_D[9] 165 VDD

34 VDD 78 PCI_AD[13] 122 DP_D[10] 166 NC

35 PCI_AD[30] 79 VDD 123 GND 167 NC

36 PCI_AD[29] 80 PCI_AD[12] 124 DP_D[11] 168 NC

37 GND 81 PCI_AD[11] 125 DP_D[12] 169 NC

38 PCI_AD[28] 82 GND 126 VDD 170 NC

39 PCI_AD[27] 83 PCI_AD[10] 127 DP_D[13] 171 NC

40 VGG1 84 PCI_AD[9] 128 DP_D[14] 172 PCI_VAUXEN#

41 VDD 85 VDD 129 DP_D[15] 173 PCI_VPCIEN#

42 PCI_AD[26] 86 PCI_AD[8] 130 DP_CS# 174 SCANMODE

43 PCI_AD[25] 87 PCI_CBE#[0] 131 DP_RD# 175 SCANEN

44 GND 88 GND 132 GND 176 GND

Controller-less ADSL Modem Device Set for PCI Applications AccessRunner

Doc. No. 100394B

Conexant

7

October 19, 1999 Proprietary Information

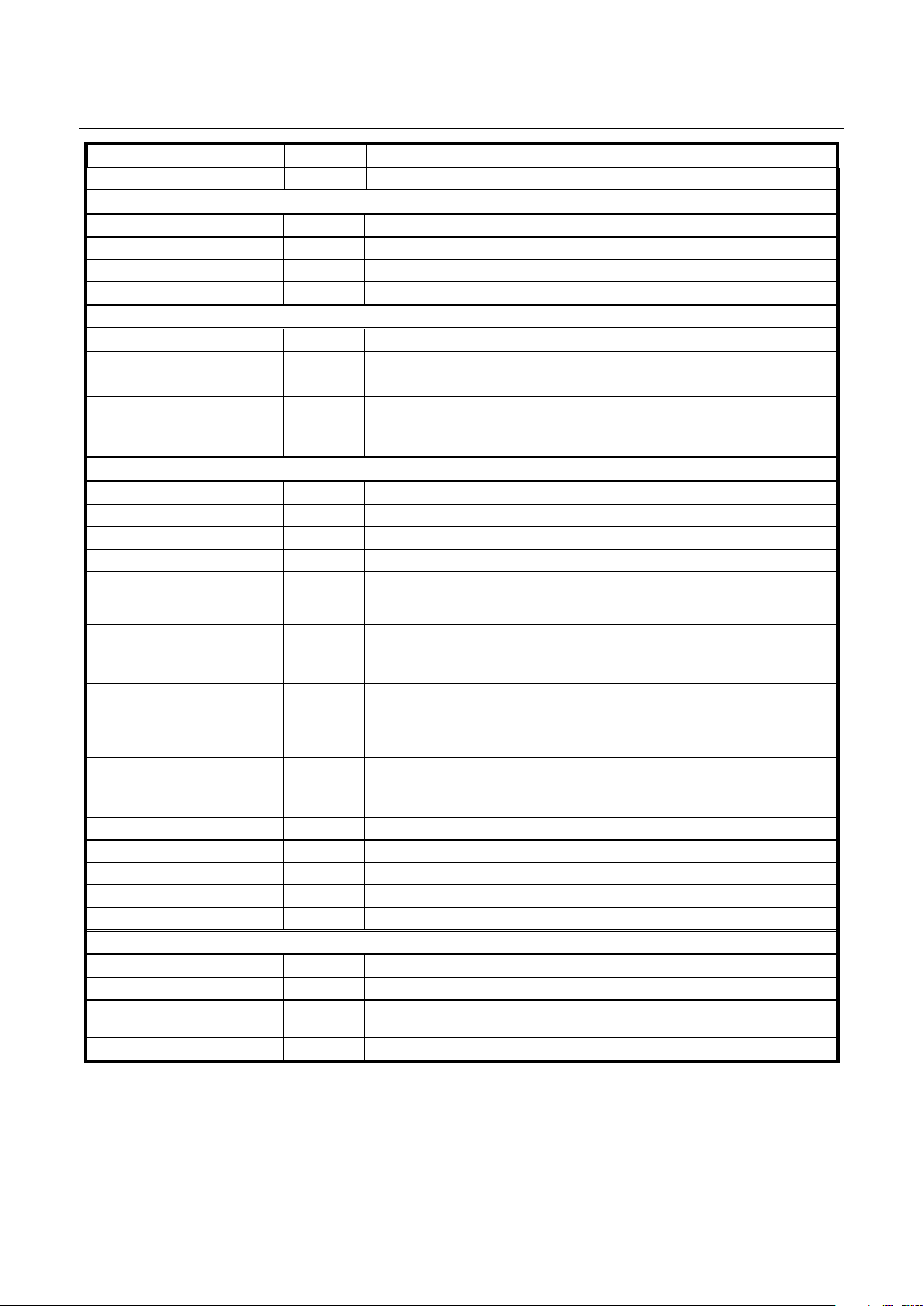

Table 2. P46 Pin Signals by Group

Pin Name I/O

1

Description

PCI INTERFACE

PCI_AD[31:0] I/O Address/Data

PCI_CBE#[3:0] I/O Command/Byte Enables

PCI_FRAME# I/O Frame

PCI_IRDY# I/O Initiat or Ready

PCI_TRDY# I/O Target Ready

PCI_PAR I/O Parity (Even)

PCI_STOP# I/O Target Stop

PCI_DEVSEL# I/O Target Response Device Select

PCI_IDSEL I Unique Select for Configuration

PCI_PERR# I/O Parity Error

PCI_SERR# O System Error

PCI_REQ# O Master Request

PCI_GNT# I Grant

PCI_CLK I PCI clock

PCI_RST# I (S) Reset

PCI_INTA# O Interrupt A

PCI_PME O PCI Power Management Event Signal

ADSL DMT DATA PUMP (11627) SERIAL CHANNEL INTERFACE

DP_RDATAS0 I Receive AS0/ATM0 Serial Data

DP_RXSOC0 I Receive ATM0 S tart of Cell

DP_RCLKAS0 I Receive AS0/ATM0 Data Clock

DP_TDATLS0 O Transmit LS0/ATM0 Seri al Data

DP_TXSOC0 O Transmit ATM0 Start of Cel l

DP_TCLKLS0 I Transmit LS 0/ATM0 Data Clock

ADSL DMT DATA PUMP (11627) MICRO INTERFACE

DP_WR# O Data Pump Device Write Enable

DP_RD# O Data Pump Device Read Enable

DP_D[15:0] I/O (PU) Data Pump Data Lines

DP_A[9:0] O Data Pump A ddress Lines

DP_CS# O Data Pump Chip Sel ect

DP_IRQ#[1:0] I (PU,S) Data Pump Interrupt Request Lines

ANALOG FRONT END INTERFACE

AFE_SCLK I Serial AFE Clock

AFE_STB O AFE Strobe

AFE_CTRLIN O Serial Data Sent to AFE

AFE_CTRLOUT I Serial Data Received from AFE

1

PD Resistive pull-down

PU Resis tive pull-up

S Schmitt

AccessRunner

Controller-less ADSL Modem Device Set for PCI Applications

8

Conexant

Doc. No. 100394B

Proprietary Information October 19, 1999

Pin Name I/O

1

Description

AFE_WAKEUP I (S) DSL Power Management Wakeup Signal from AFE

SERIAL EEPROM

EEPROM_CS O EEPROM Chip Select

EEPROM_CLK O EEPROM Clock

EEPROM_DIN I EEPROM Data Input

EEPROM_DOUT O EEPROM Data Output

PCI POWER MANAGEMENT

PCI_VAUXDET I (PD,S) Vaux Detect

PCI_VPCIDET I (PD,S) Vpci Detect

PCI_VAUXEN# O Vaux Enable

PCI_VPCIEN# O Vpci Enable

PCI_VPCIPREFER I This pin is used to determine whether Vpci or Vaux is the preferred power suppl y.

1=Vpci preferred, 0=Vaux preferred

MISCELLANEOUS

GPIO[1:0] I/O (PU,S) General Purpose Schmitt I nput /Output

GPIO[2:5], GPIO[8] I/O (PU) General Purpose Input/Output

GPIO[6] I/O General Purpose Input/Output (also used for act i ve low reset)

GPIO[7] I/O General Purpose Input/Output (also used for acti ve high reset)

TDI_GPIO[9] I / O (P U) JTAG test data i nput OR general purpose input/output. Functi on of this pin is

dependant upon value of JTAGEN bit. When operating in JTAG mode this signal

contains serial data that i s shifted in on the rising edge of TCK.

TMS_GPIO[10] I/O (PU) JTAG test mode select OR general purpose input/output.

Function of this pin is dependant upon value of JTAGEN bit. When operating in JTAG

mode this siganl controls the operation of the TAP cont rol l er.

TRSTN_GPIO[11] I/O (PU) JTAG reset OR general purpose i nput/output.

Function of this pin is dependant upon value of JTAGEN bit. When operating in JTAG

mode, a high to low transition on t hi s signal forces the TAP controller into a logic reset

state.

TCK I JTAG clock.

TDO O JTAG data output. This pin generates serial data that is shifted out on t he f alling edge

of TCK..

GPIN0 I (S) General purpose schmitt input (m odem ri ng det ect)

GPIN1 I (PU,S) General purpos e schmitt input (modem of fhook)

SCANEN I (PD) Scan chain enable. Used to s hi f t data in and out of the scan c hai n.

SCANMODE I (PD) Scan mode enable pin. When tied high it will put the device into scan t est mode.

REFCLK I 35.328 MHz reference clock used to create the internal 53 MHz system clock

POWER AND GROUND

VDD 3.3V Power

GND Ground

VGG1 I/O Clamp Power Supply for PCI Signalling Environment (connect to VIO pin of PCI

Bus)

VGG2 I/O Clamp Power Supply for B ackend (connect to 3.3 vol t supply)

Loading...

Loading...