,

~

.........

•

"'

J

'*

zao

S

INGLE

REFERENCE MANUAL

BOARD

SBC880

ro~t1PUTER

1

\ j

"'-

;. .

\.

.

,

•

Copyright

No

part

transcribed,

human

or

electronic,

o

the

r wi s e ,

8614

Hamilton

SUNTRONICS

respect

to

product

agreement.

revise

the

notify

this

content

any

agreement

(c)

1982

of

this

stored

computer

mechanical,

wit

Ave.

CO., INC.

the

it

describes

Further,

pUblication

hereof

person

to

the

publication

h0 u t

Huntington

contents

contrary

COPYRIGHT

by

COMPUTIME.

in

a

retieval

language,

magnetic,

the

exp

makes

of

is

SUNTRONICS

and

without

of

such

may

res

s wr

Beach,

DI

SCLAlMER

no

representations

this

manual

covered

to

m~ke

obligation

revision

exisits.

NOTICE

All

be

system,

in

any

optical,

itt

CO.,

changes

Rights

reproduced,

or

form

en

permiss

California

itself,

by

a

INC.

or

reserves

of

SUNTRONICS

changes,

.

Reserved

translated

or

chemical,

ion

92646

or

whether

warranty

from

Worldwide.

transmitted,

by

any

manual,

0 f ooMPUTI

U.S.A.

warranties

or

or

the

time

to

00.,

except

into

means,

not

repair

right

time

INC.

when

any

or

ME

with

the

,

to

in

to

an

i

•

SECTION

SECTION

SECTION

SECTION

I

GENERAL

II

FUNCTIONAL

I I I I

IV

NTERF

BOARD

SECTIONVDETAIL

APPENDIX

APPENDIX

APPEl·mIX

APPENDIX

APPENDIX

S~·

S

T'E1'Y1.

- A

- B

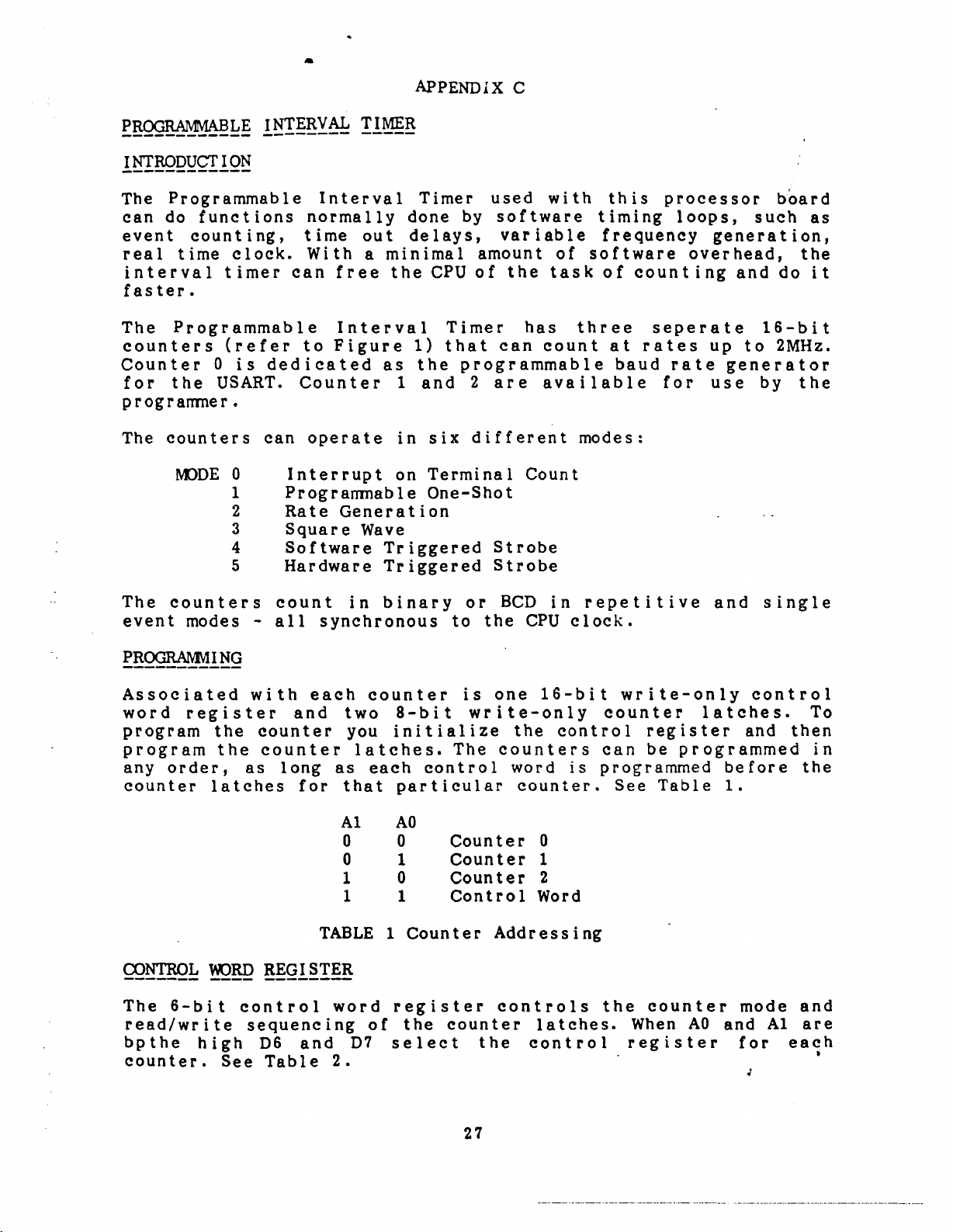

- C

- D

- E

l\DN I

USART-TIMER

USART

PROGRA\'l\W3LE

PARALLEL

INTERFACING

TOR

TABLE

DESCRIPTION

DESCRIPTION

ACES

OPTIONS

..............••••....•.

.•.....•.•.....••.....

DESCRIPTION

OF

CONTENTS

......•.........

............•

.•.••...•.•••••..•

AND

I/O

INTERVAL

PRINTER

NON-

••••••••••••••••••••••••••••••••

INSTALLATION.....

IEEE

DYNAMIC

ADDRESS

TII'rIER

Page

ING.

MEMORY

Number

1

3

5

9

11

15

19

27

31

33

35

•

NTRODUcrION

I

------------

The SBC880

is

compatible

contains

board

The

board

enough

system

conservatively

in

and

you

Before

with

for

EPROM

FEATURES

--------

An

on

by

8

Power-on

EPROM

of

location

In

provided

is

location,

tested

receive

installing

the

a

2708

then

board

static

may

64K

or

addition

not

used

SBC880

jump

optionally

(U23)

and

a

Processor

with

features

or

as

is

manufactured

rated

to

it.

features

EPROM.

refer

EPROM

RAM

is

more

of

are

to

the

it

can

and

total

Board

the

the

assure

the

If

to

Section

can

may

be

available

be

RAM.

the

EPROM,

be

the

of

2K

SECTION

GENERAL

is

IEEE

to

main

to

CPU

assure

that

board

and

you

want

V

be

addressed

used

used

Devices

2708,

located

static

bytes

DESCRIPTION

a

powerful

S100/696

allow

its

board

using

quality

long

the

board

read

this

options.

to

use

Board

on

in

place

directly

in

shadow

that

2716

an

ram

EPROMS

additional

on

is

of

ram may

any

I

bus

use

in

life.

will

manual

The

one

options

any"1K

of

to

mode

can

1K

used

Z80

based

standard.

as

a

a

larger

components

All

work

and become

board

of

for

or

the

the

EPROM

to

be

or

the

lK

boundary.

instead

be

present

design

The

stand

alone

system.

boards

are

properly

comes

the

configured

other

modifications.

2K

boundary.

EPROM

if

(or

allow

used

4118

of

the

in

static

If

at

on

the

static

the

the

the

SBC880

single

that

burned

familiar

type

desired.

RAM).

full

EPROM

ram

EPROM

EPROM

board.

which

are

when

of

A lK

The

use

RAM.

is

The

model

and

baud

board

rate

signals

terminal

connector(J1).

wit

h buf

is

occasionally

fer

connected

rib

bon.

be

selected

A

DMA

MWRT

under

Two

The

prgrammable

timer

A 4MHz

capability

signal

control

connector

is

available

is

equipped

is

programmable

required

equipment

Reverse

edt

ype de

needed

device.

crystal

for

2

generated

of

DMA

timers

output

J2.

for

and

A

use

vic

It

can

or

4

is

provided

on

logic

controls

parallel

at

with

by

by

terminal

may

channel

es

sue

as

a bUSy

sense

provide

MHz

operation.

the

or

are

connector

a

USART

means

be

connected

capability

has

things

s a I I s Ys t em

as

well

CPU

board

a

front

available

are

input

J2.

1

and

of

a

type

equipment

pr i nt er

or

ready

such

as

or

panel.

for

available

and

a

a RS232

interface.

programmable

is

directly

is

available

s.

Th

ere

indication

as

out

tim

a

means

of

elsewhere

use

by

user

at

the

parallel

timer.

provided

to

the

ve r

sec

from

of

paper

i ng

having

in

the

programs.

parallel

output

RS232

for

hanne 1

and

system

The

All

for

use

the

or

can

the

I/O

port

All

tor

stable

both

5-100

all

design.

sides,

on

bus

board

plated

sijnals

voltages

A

quality

are

through

fUlly

to

PC

holes

buffered

assure

board

and

is

gold

and

an

electrically

used

plated

regulators

with

contacts.

solder

are

clean

mask

used

and

on

2

-

FUNCTIONAL

SECTION

DESCRIPTION

II

Z80A

----

The

Z80

required

address

the

simp

A

bus,

timers.

for

clear

STATUS

------

The

control

by

device

and

access

acknowledgment

bus.

CPU

---

SBC880

microprocssor.

Z80. The 8BC880

1e jumpe r .

crystal

the

the

signal.

AND

---

status

a

DMA

control

is

to

bus

controller

Z80A

Associated

EPROM

CONTROL

-------

signals

device

and

memory.

is

requested

a

read

and

CPU,

and

and

for

single

and

a 8

reset

BUFFERS

-------

control

to

to

the

signal

The

write

bit

can

circuit

the

with

the

allow

The

duration

by

board

Z80

bi-directional

be

Baud

this

circuitry

8-100

DMA

activating

from

microcomputer

provides

to

memory and

run

provides

rat

circuit

buffers

bus.

a

transfer

device

the

at

of

CPU

either

timer,

are

which

interface

These

assumes

the

the

is

the

data

all

and

also

buffers

of

DMA

CPU

made

major

the

4

or

the

the

data

control

transfer.

DMA

available

designed

control

I/O

ports.

bus

are

2

MHz

timing

the

two

wait

generates

the

state

CPU

may be

between

request

around

sighals

A

16

generatedby

by

changing

for

the

SlOO

programmable

generator

a

power-on

status

tri-stated

the

DMA

on

thestatus

When a

signal,

on

the

DMA

8-100

the

bit

a

and

the

ADDRESS

The

CPU's

!2~!~

The

The

The

address

circuitry

devices

then

eight

or

devices

or

buffers

when

provide

Q~

data

data

I/O

8-100

I/O

the

data

BUFFER

buffer

sixteen

on

when a

~Q££~g

out

bus

out

output

when

data

input

are

CPU

address

the

CPU

transfer

the

address

buffer

signals

bus

will

cycles.

they

cycles

disabled

is

are

in

driving

is

a 16

board.

is

an8bit

only

The

transferring

bus

to

is

devices

during

bit

bits

The

of

data

for

from

contain

data

provided

data

tri-state

to

buffer

is

the

duration

tri-state

the

out

external

memory

to

the

3

the

to

CPU

valid

bus

data

to

to

the

write

data

buffer

8-100

is

occur.

of

buffer

the

data

will

to

CPU

to

out

bus

also

memory.

the

The

the

8-100

during

be

during

board.

or

I/O

buffers.

tri-stated

tri-stated

which

and

DMA

data

which

data

output

drives

to

device

transfer.

drives

out

memory

memory

The

The

other

by

will

write

by

read

data

cycles

data

the

DMA

the

bus.

DMA

in

~n

buffers

accessed

CPU

The

bu

memory

address

on

the

EPROM

----

The

EPROM

static

boundary

lK

BY

--

--

are

dlsabled

to

allow~t~

s.

decode

bits

board.

can

RAM

(4118

and

8 STATIC

-

------

and

the

selects

be

type).

optional

RAM

---

whenever

and

a

lK

device

control

the

(2708

The

ram

devices

being

circuitry

EPROM

type),

EPROM

can

on

accessed

or

static

2K

may be

be

selected

the

decodes

(2716

selected

CPU

to

R_~

type),

on

board

place

the

that

on

any

are

data

hig~

is

or

a

any

lK

boundary.

being

on

order

located

lK

lK

or

the

by 8

2K

The

type

lK

of

of

refresh.

diagnostic

of

the

SBC880

The

the

I/O

I/O

add

ports

ressbus

operations.

The

serial

interface.

USART

P~W3LE

------------

Two

8253

is

programmable

or

crystal

on-board

ram

This

provided

ram

tests

as

decode

on

the

I/O

The

baud

a

8251.

TIMERS

------

8254

timer

controlled

ram

may

on a

a

stand

and

control

t 0 de t e r

board

provides

rate

timers

can

clock

may

is

be

bad

be

static

used

dynami~

alone

circuitry

min

e w

are

asynchronous

is

provided

are

be

used.

oscillator

selected

to

ram

system.

hen

being

available

The

to

(2114

hold

type)

the

board

decodes

the

US

ART,

address

communication

by a

programmable

for

timers

on

the

any

stack

or

the

tim

for

use

are

board.

lK

boundary.

and

when

it

allows

lower

e r 0 r

input

on

the

clocked

requires

running

the

8

bits

par

or

via

a RS232

timer.

board.

from

The

no

use

of

a I I e I

output

The

An

the

An

8

bit

provided

circuitry

parallel

on

the

output

board.

(74LS373 and

port

The

and

ports

74LS374).

a 8

bit

parallel

are

4

implemented

input

with

port

TTL

are

type

•

EPRO:\1INTERF

The

EPROM

conditions:

1.

When

power-on

unconditionally

power

or

latch

and

set

(2708

through

compares

2.

When

memory

compares

the

ACE

will

power-on

on

the

is

the

tin

gs 0 r

type)

not

8131

be

selected

jump

latch

system

reset

address

the

the

15

to

address

using

read

operat

with

comparator)

SECTION

INTERFACES

for

jump

is

latch

enabled

is

selected

is

set

any

reset

button

when a memory

EPROM

the

bit

the

the

being

8131

SW3.

11

phantom

ion

EPROM

read

se 1e c t s

(U30)

For

through

is

per

switch

III

access

until

time

2K

option

formed

(I

set.

the

the

is

pressed.

read

·operation

compares

wit

ch SW3.For

compares

x 8

EPROM

15

to

(Q

settings

under

to

U

The

latch

system

the

to

wi

th

the

present)

EPROM

is

is

The

to

address

(2716

SW3.

R

present)

an

(as

following

and

U23

reset.

powered

power-on

is

performed

the

switch

1K x 8 E

bits

type)

and

address

detected

the

The

PRO

U30

that

is

up

M

10

a

by

The

EPROM

is

used

signal

CPU

WR!

tow

RA~

The

r i

ted

iss

EPROM

directional

through

directly

have

the

access

programs

boa

r d

can

even

PHANTOM

-------

When

only

pre

for

latch

when

the

selected

sse

all

dan

is

address

Likewise

on

latch.

data

from

reset

may

the

MEMRD

is

accessed

signal

a t a i n

e I ec

ted.

or

optional

data

the

data

access

S-100

the

EPROM

to

be

commun i

the

S-100

M:>DE

----

phantom

d

the

memory

set.

memory

I/O

input

Therefore,

an

I/O

operation.

optionally

signal

dur

is

jumpered

tot

he

bus

and

out

the

EPROM

bus

run

or

cat

in

optional

in

e

bus

EPROM

after

powe

read

r-

operations

During

external

and

the

device

The

be

ing

memory

to

RAMduri

RAM

only

bus

drivers.

or

operational

EPROM

wit

hat

is

completely

option

a

power-up

0 n I

at

this

output

program

into

EPROM

replaced

is

replaced

the

is

directly

appears

optional

~'1.

to

diagnose

e r

is

chi

time

to

the

cycles

memory

select

read

~~

ng

min

sse

that

a

in

by a 4118

by

and wr i

WE!

me

m0 r y wr i t e cyc I es w

input

MRQ

RAM.

so

te

operations.

to

connected

on

the

S-100

NOTE

condition

This

a I

R~~.

feature

a

and

that

It

failing

run

only

is

allows

d i ag

not

to

inoperative.

used

or

memory

board

when

1.

The

occur

are

the

EPROM

after

switch

(Q

to

R

the

EPROM

while

write

in

a

unaffected

can

a

power-up

can

cut)

system

wi

operation

normal

be

be

When

that

the

the

RAM

RAM

The

allow

to

bus

the

the

hen

the

CPU

indirectly

CPU

CPU

the

bican

necessary

suc~essfully

diagnostic

5-100

nos

the

bus.

tic

EPROM

t

The

est

reset

lIb

e seIec

the

power-on

ted

will

fashion.

by

the

power-

used

set

o.r

to

to

boot

syst"em

detect

to

s

is

is

5

the

by

the

into

starting

memory. A jump

the

8131

power-on

comparator.

data

in

memory

effectively

power-up

comparator

cannot

disappears

or

system

ad&tess

latch

is

to

is

select

now

reset

of

the

the

starting.

and

reset,

the

accessed

from

operation.

code

will

the

the

reset

EPROM

EPROl\l

in

a

system

that

address

because

normal

the

the

can

until

EPROM

will

then

power-on

not

be-accessed

Q

to

fashion

needed

program

be

·latch.

R

is

and

at

detected

open).

the

the

boots

When

(the

The

EPRQ;\l

next

A 1K x 8 b I 0 c k 0 f s

chips

com

When a memory

the

switch,

memory

(

low)

wr i

connected

accessed

available

U8ART

allows

bus

memory

board

diagnostic

scratchpad

run

signals

located

with

necessary

board

bus

RAM

ext

its

data

RA~

on

the

board.

paresaddres

comparator

the

C8/

ted

write

a t

a t a i n

the

operation

WE

to

directly

at

the

will

function

diagnostics

is

inoperative.

diagnostic

that

contains

programs

and

properly

on

in

no

RAM

data

i s a I

ernaIde

da t a i g

even

the

the

conflicts

if

your

is

accessed

in

bus

lowed

vic

nor

instead.

will

be

available

s

operation

detects

lead

/ in

to·

the

8-100

stack

8-100

same

receivers

t 0

erespondin

ed bY

When

taticRAM

The

RAM

bit

s

lOt

is

a

goes

is

put

s 0 f

the

CPU

RAM.

bi-directional

by

the

data

independently

to

be

An

example

on

the

the

can

operations.

if

the

bus.

address

between

system

during

sup

ply

the

boardan

your

to

i s imp I erne n

is

selected

hr0

performed

match

active

performed

the

The

CPU.

out

performed

of

board

balance

use

RAM

In

board

normal

space

the

uses

a

a

are

da

tad

g t·)

system

help

you

ted

u

by a 8131

ugh

1St

0

the

RAM

by

the

CPU

between

(low)

RAM

RAl'vl0nth

The

bus.

this

while

of

the

The

being

as

memory

full

memory

disabled

ire

the

by

use,

other

64K

the

at

the

CPU

chi

pst

data

RAM

The

on-board

of

the

the

feature

diagnosing

the

on-board

diagnostic

diagnosed

the

memory

devices.

of

read

and

c t 1Y

address

WR/

0 a I

e

boardis

bus

data

8-100

board

system

on-board

RAM.

operation

the

tot

the5amemem0rye

d

the

0 n-

boa

r d

RAM

get

is

inoperative,

your

system

singtwo

211 4

comparator

se

lee

t s

(MRQ

RAM

signal

and

would

chips.

low

is

~~~,

bus

when

be

a

dynamic

active)

and

the

is

the

CPU

d

ire

can

only

indirectly

EPROM

and

the

running

memory.

static

RAM

routines

was

affecting

RA\1

in

ycur

This

Whenever

will

the

the

on-board

he CPU. Th

yc 1e W 0 u1d have

RA:,l

w0 u 1d

the

on-board

going

again.

RAM

that

wit

ch.

and

RAM

When

active

c t 1Y

and

this

8-100

RAM

The

for

would

may

system

on-

8-100

static

usa

sup

ply

a

to

be

a

be

be

n

The

CPU

compares

and

looks

access

address

8131

to

comparator

select

I/O

address

is

I/O

devices

for

in

process.

devices.

the

are

bits

10RQ

to

Address

and

address

individual

selected

A3

be

The

through

active

CPU

bits

I/O

by an 8131

uses

bits

Ai

devices

6

A7

(high)

address

A3

through

and

on

to

the

indicating

A2

the

comparator.

I/O

bits

are

A7

are

decoded

AO

board

select

through

tested

as

The 8131

switch

that

with

follows:

an

A7

by

gates

I/O

to

the

RD

1-

0 1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

-

Device

-~25!

"'11

" "

"

" "

"

"

"

Input

Output

Input

Output

tl

"

"

WR

A2

(f-

n-

0 0

0

0

0

1

0

0

0

1

0

0

0

1

1

0

1 0

1

0 1

1 0 1

1

0 1 1 0 8251

1 1

1

0 1 1

1

1

Al

n-

0 1

0

1

1

1 1

1

0

0

1

AO

(f-

0

1

0

0

1

0

0

1

0

I

1

Selected

fTmer---

tl

"

"

"

"

Port

Port

Port

Port

USART

"

tl

"

OQeratlon

Read-baue

Write

Read

Write

Read

Write

baud

counter

counter

counter

counter

Illegal

Write

Read

Write

Read

Write

Read

Write

Read

Write

mode word

input

output

input

output

data

data

status

control

rate

rate

1

1

2

2

port

port

port

port

register

register

registe'

register

time

time

The

I/O

final

select

through

selected.

active)

cycle

low,

aninput

selects

the

parallel

selected

8253

----

The

TIMER

-----

board

circuitry

8253.

for

the

transmit

timer

counter.

of

timer

a

32

bit

out

putsare

for

C

I/O

switch

A7

will

NOTE

a

different

(WR

active)

the

output

with

INTERFACE

---------

provides

to

Timer

zero

8251

and

zero

(GO)

The

two

counter/timer.

ava i IabI e

a

description

port

that

at

cyc I e s e

input

AO

high

the

count

is

USART

receive

is

output

(CS)

and

address

which

cause

for

operation

the

port.

and

or

a 2Mhz

used

and

clock

tied

of

the

for

of

for

determine

the

some

same

lee

t s

Adderss

output

low.

inputs

as

its

inputs

active

timer

two

The

use

the

8253

each

what

I/O

devices

devices

takes

address.

the

i n

bit

ports

clock

of

timer

a

programmable

output

of

(high)

one

(01)

timers

gate

ate

inputs,

0 nnec

functions.

device

during

place

put

AO

and

from

is

connected

the

to

can

is

state

on

than

When

po r

is

A2

t,

ignored

the

the

zero

and

baud

USART.

permanently

is

connected

be

used

count

torJ2.

determined

of

address

the

an

input

for

is

high

and

an

when

same

clock

timer

rate

directly

The

gate

together

inputs,

Re

fer

by

bits

board

to

cycle

an

output

and

Al

0 ut pu tcYc I e

accessing

devices

are

oscillator

one

of

generator

to

input

enable

to

to

the

and

to

Ap

pend i x

this

input

form

count

the

A3

be

(RD

is

the

the

to

8251A

-----

Tim

e r z e

the

transmit

Transmit

1489

a

of

the

by

a

1488

transmit

by

the

input

has

no

USART

-----

roo

data

RS232

USART.

Jl

1489

can

other

INTERFACE

---------

f

the

and

at

receiver

Transmit

RS232

pin

11

and

be

sensed

affect

8253 d i v

receive

the

RS232

and

data

transmitter

input

provided

as

on

the

idesthe2MH

clocks

connector

applied

(TXD)

to

at

the

RS232

to

the

a

status

operation

7

(TXC

to

from

J1

DSR/

bit

z c I 0 ck dow

and

Jl

pin

2

the

receive

the

US

pin

3.

The

connector

input

in

the

of

the

RXC)

is

ART

of

status

USART.

nan

to

level

data

is

level

reverse

is

level

the

USART.

register

This

d

provide

the

shifted

input

shifted

channel

shifted

allows

s

USART.

by

(RXD)

This

and

programs

I/O

devices.

to

permanently

the

RS

232 i nt erface i 5 a Iway s

partusedfor

will

functional

not

be

description

sensea

The

at

the

the

used

nott-rpady

CTS/

input

input

of

USART wi I I

on

the

of

the

or

buffer

of

the

rea

be

board.

USART

the

USART

USART.

dy

tot

full

This

cond

is

tells

ransmit

it

tied

dat

ions

active

the

a.

on

USART

Theact

an 8 251A 0 r 9 551.The0Ide

Refer

to

Appendix

B

device.

ser

(low)

r 8

for

ial

that

ua I

2,5

.

1

a

The RS232

device

connected

RS232

the

4

and

connector

connector.

5.

Carrier

BAUD

----

When

s e

16

I e c

times

RATE

----

the

tedthat

divisors

application.

connector

without

device

Data

detect

DIVISORS

--------

baud

the

will

Baud

---9600--

4800

1200

modems.

will

jumpers

Request

terminal

Pins

rate

wi I I d i v

baud

rate

be

Rate

2400

600

300

150

110

is

configured

be

to

ready

6,

8

timer

ide

desired.

of

help

Any modem

satisfied

together

send

is

is

and

20.

is

initialized

the

2MHz c 10 c k t 0 a f r e

in

to

allow

by

the

jumpered

jumpered

The

following

selecting

Divisor

-----13

26

52

104

208

417

833

1136

direct

signals

jumpers

following

to

to

required

on

RS232

Clear

Data

a

divisor

list

the

connection

the

board.

signals

to

send

set

ready

must

que

nc y t

of

baud

one

for

by

hat

to

the

The

at

Pins

and

be

rate

your

a

i s

The

parallel

triggered

and

need

register

latched

This

during

The

clock

an

parallel

transparent

da

tad

ire

por

tis

the

latch

low

(input

the

CPU

the

I/O

output

register.

no

additional

is

provided

at

the

will

I/O

output

input

latch.

c t I y

se Iec

tedduri

inputs

port

data

bus.

connector

rising

transition

tot

he

when

selected)

The

J2.

port

The

cycle.

port

The

CPU

ng

is

register

buffering.

to

the

(low

every

is

tri-state

b i - d

the

the

latch

will

latch

implemented

outputs

The

I/O

to

connector

high)

time

implemented

buffers

ire

c t

ion

I

/0

in

put

select

be

latched

strobe

8

are

clock

transition

the

a I da

cyc

strobe

signal

with

buffered

J2.

output

with

on

tab

Ie.

Th

and

is

to

a

this

u s w

e da

goes

then

made

a

74LS374

the

Output

of

port

74LS373

chip

hen

tap

from

presented

available

on

the

output

this

is

selected

the

resentat

edge-

chip

port

data

clock.

octal

provide

i n

put

high

is

to

to

at

•

(':,.

«-

SECTION

IV

OPTION1ON

------

-

--

The SBC880

follows:

l.

Z

2.

Y

3.

F

to

4.

H

5.

J

6.

L

7.

P

8.

P

9.

L

10.

H

1l.

V

to

12.

X

OPTION

------

TI

3

Voltage

1 •

2.

3 . J

4.

5.

6.

7•

8.

9 • V

10.

11.

12.

13.

2

-

-

F

to

H

to

to

L

P

to

P

to

L

to

H

to

to

X

to

y

to

Z

to

Sw

BOARD

-----

comes

K

to

to

G

G

to

to

K

to

M

to

0

to

N

to

K

to

M

W

V

to

2716

EPRQ\1

G

K

to

M

0

N

K

M

W

V

G

K

i t c h

open

open

shorted

I

shorted

shorted

open

shorted

open

open

open

shorted

open

EPRQ\1

shorted

I

shorted

shorted

shorted

open

shorted

open

open

shorted

open

open

open

6

EPROM

-----

etched

of

SW3

BOARD

-

2708

for

closed

the

OPTIONS

EPROM

2708

EPROM.

1

nte

1 . F

2.

3. J

4.

5.

6.

7

.•

8 . H

9.

10.

11.

12 . Z

13.

14.

The se

+5

I

to

H

to

to

L

to

P

to

0

to

L

to

to

V

to

X

to

Y

to

to

Sw

itch

G

to

defaults

vo

I t

G

open

1

shorted

K

open

open

M

open

0

N

shorted

K

shorted

1\1

shorted

W

shorted

V

open

open

G

K

open

6

+5

EPRQ\1

SW3

of

are

closed

as

OPTION

------

10.

1l.

12.

l.

2 .

3.

4.

5.

6 •

7.

8.

9.

3

-

-

F

H

J

L

L

H

P

p

V

X

y

Z

4118 RA.\i

G

to

to

to

to

to

to

to

to

to

to

to

to

open

1

shorted

K

open

M

open

K

open

M

shorted

a

shorted

N

open

W

open

V

shorted

G

shorted

K

shorted

substituted

for

9

EPRO:\1

OPTION

------

An

EPRO~

board

Phantom

1.

2.

4 -

Power-on

- - "

is

must

etched

mode

T

to

Q

to

be

as

U

shorted

R

shorted

Jump

present

for

follows:

the

~

no

'tt_

to

2708

Phantom

use

the

EPROM

Mode

power-on

and

the

jump

power-on

feature.

jump

with

The

no

Q~I!Q~

~

The Eprom

1.

2.

Q~I!Q~

The

~

EPROM

1.

2.

OPTION

------

To

7 -

-

disable

1.

2.

Q~!!Q~

This

~

option

-

Power-on

must

T

to

Q

to

-

No

or

T

to

Q

to

No

address

Q

to

T

to

-

l\IWRT

be

U

shorted

R

open

Power-on

optional

U

open

R

shorted

EPROM

R

open

U

open

genera

is

etched

Jump

present

RAM

selection

ted

on

with

Jump

the

to

may

by

Phantom

use

this

be

used

of

the

CPU

board.

Mode

option.

with

EPROM

this

entirely.

option.

1.

2.

Q~!!Q~

1.

2.

Q~!!Q~

1.

2.

C

D

~

C

D

!Q

C

D

to

to

-

MWRT

to

to

-

to

to

E

shorted

E

open

E

open

E

open

MWRT

E

open

E

shorted

generated

generated

by

by

external

CPU

and

10

devices

external

devices

•

SECTION

DETAIL

DESCRIPTION

V

-Refer

each

ADDRESS

-------

The

During

(ADDSB/) low

can

DATA

----

During

is

74LS241

disable

DATA

----

to

functional

BUS

---

address

DMA

then

IN

BUS

--

---

memory

received

the

1.

EPROM

2.

On-board

3.

Programmable

4.

Parallel

5.

Memory

OUT

---

the

bus

operations

to

place

and

type

data

BUS

---

SBC880

block

of

tri-state

its

read

driven

device.

in

or

optional

static

1/0

write

schematic

that

the

own

address

or

I/O

Circuitry

buffers

timer

port

or

CPU

the

the

input

to

ram

ram

selected

1/0

while

follows.

is

buffered

DMA

the

under

selected

output

device

address

on

operations,

CPU

selected

selected

reading

using

will

bus

drivers.

the

bus.

bi-directional

is

provided

the

following

operation

the

74LS241

drive

the

S-100

(l/2

conditions:

in

progress

de"scriptions

devices.

S-100

The

data

data

of

pin

DMA

bus

7420)

of

22

device

in

bus

by a

to

Th e

CPU

bus

by 74LS241

the

operations.

bus

This

~L~

STATUS

------

Status

provided

device

bu f

Control

bus

may

control

the

signals.

as

the

system

MWRITE

to

may

CPU

wi I I dr i

will

device

SIGNALS

-------

fer

by

drive

other

you

CPU

disable

be

disabled

b i - d

to

A

disable

to

signals

to

the

may

one

received

contains

signal,

drive

to

a I

signals

section

pin

of

the

half

This

boardis

the

ire

c t

type

devices

DMA

ve

pin

place

SM1,

S-100

low

PSYNC,

19

bus.

of

buffer

it

a 1way s

then

buffer

by

ion

a I da

buffers.

on

device

23

(DODSB/)0nth

the

data

data

SMEMR,

bus

pin

the

(C/CDSB/)

another

18 (STATDSB/)

DMA

PWR/, and

of

a 8097

The

the

8097

may be

has

you

on

the

STATDSB/

tabusis

The

the

wishing

out

on

the

by

a 8097

de

vic

type

low

MWRITE

buffer

controlled

this

the

may

sour

device

the

buffer

cut

board.

buffers

S-100

to

buffers

bus.

SIN?,

e

PDBIN

to

signal

ceo

that

the

signal

dr I ve n

bus

transfer

e S- 100

on

SOUT, SINTA,

type

low

tog

tri-state

a

disable

is

that

in

permanently

f

the

is

etch

If

desired,

when

provide

during

the

tri-state

to

inc

are

provided

was

several

M\\"R

to

between

tot

provided

he S-100 da

write

memory

data

bus

tri-stat

0 n t r 0 I 0 f

buffer.

this

used

be

a

D~iA

board

I

TE

the

the

on

to

buffer

by

ways:

enabled

s igna I• I f you r

points

device

data

the

data

a

lowstat

and

allow

and

source

MM~ITE

buffer.

the

to

A

DMA

to

the

the

SWO/

the

the

and

control

The

so

C

is

tao

ut

from

write

out

the

are

A

D7.1A

status

bus.

S-100

device

gain

bus

by

board

that

of

the

and

buffer

~sing

e.

E

11

the

poi

E.

bus.

n t s

This

provided

or

a

signal

floatin

control

signal

Can

option

g

of

is

This

d E~a n

the

the

the

left

option

dotIien

requires

MWRITE

with

MWR

ITE s i g na

bus.

floating.

the

is

signal

same

Data

ins

that

enabled

tal

lin

that

timing.

Ion

in

memory

g a j um

the

is

the

by

cutting

DMA

enabled

This

S

-100

may

per

device

by

is

bus

be

the

bet

weenpoi

hav~

the

STATDBS/

necessary

wh i

let

overwritten

etch

between

n t s 0

a

buffer

signal

to

prevent

ransferrin

if

and

to

g

this

The

signal

active

RD/

w

hen

and

the

MWRITE

(low)

(low)

OTHER

SINTA

the

CPU. SWO/

any

input

indication

SWO/

inactive

SX

TRQ

/ i s

required

transfers.

at

the

CONTROL

-------

The

goes

signals

active

device

PSYNC

valid

developed

IEEE

CPU

S-100

memory

active

memory

is

being

RD

/ i

sac

PHLDA

CPU. Th

th~

requesting

of

the

signal

DMA

only

device

goes

point

properly.

SOUT

(low)

IORQ/

s i g na 1s

is

active

at

the

at

the

STATUS

goes

active

cycles.

that

is

active

(low)

not

by

SHLTA

CPU.

SIGNALS

-------

when

signal

I/O

by

specification.

(low)

read

acknowledged

t i v e

goes

iss

i g na I a c k

bus.

BUSRQ/

active

in

its

PHLDA/

is

active

at

the

CPU.

are

active

RD/and

(high)

CPU.

SMl

CPU.

SIGNALS

(high)

goes

active

This

a

write

(low)

will

ge n

era

ted

the

CPU. SXTRQ/

goes

OUTPUT

------

PSYNC, PWR/

(low).

the

goes

or

memory

a

flip

refresh

at

of

I/O

(low)

active

C/CDSB/

device

active

flop

cycles.

the

input

at

(high)

now

device

The

CPU

going

drives

active

the

when

operation

is

always

SINP

(low)

when

goes

when

signal

or

when

be

active

by

active

and

wants

(high)

cycle.

and

The

CPU.

cycle

(SINTA

the

when

1e dge s a

with

generates

S-100

BUSRQ/

where

(high)

is

at

when

active

the

MREQ/are

signals

active

Ml/

(low)

when

output

RD/

is

(high)

the

boa

is

(high)

PDBIN

will

to

momentarily

The

produces

PSYNC

PWRl

The

RC"~S

si;r-al

is

in

high).

CPU 0 r w

BUSAK/

DMA

the

highest

this

(low).

BUSRQ/

signal

has

gone

a

driven

WR/

CPU.

active

(high)

and

the

is

used

cycle

inactive

r d b ec a

used

when

are

be

driven

take

timing

signal

active

process

PDBIN

hen

r e

signal

PHOLD/

active

DMA

and

cannot

and

(high)

SMEMR

WR/

and

when

IORQ/

CPU

to

is

at

the

use

to

request

HLTA/

tri-stated

control

timing

is

PDBIN

is

S I

NTAisac

goes

questan

priority

goes

active

access

IORQ/

(low)

go

is

provide

going

(high)

0 n I y 8

low

at

for

as

not

(low)

goes

or

active

active

in

active

and

be

when

is

MREG/

Ml/

active

not

to

CPU.

goes

when

by

of

the

this

defined

produced

when

active

when

din

may

response

(low).

the

can

tri-stated.

signals

the

signals

active

at

the

are

goes

(low)

performing

an

take

or

SINTA

The

bit

da t a i s

16

bi

active

C/CDSB/

a

DMA

the

bus.

start

signal

WRi

an

interrup~

(high)

t i

ve

(low)

d i

cat

est

take

(low)

CPU

be

perfomed

are

(high)

CPU.

active

active

at

early

place.

signal

t

data

(low)

type

The

of

any

by

the

during

goes

when

when

(h

i g

h).

at

the

hat

control

to

the

when

BUSAK/

is

at

is

is

a

a

a

12

CONTROL

-------

SIGNALS

-------

Ir?UT

-----

The

because

signal

IEEE

only'S

SIXTN/

access.

this

will

EP~1

one

wait

is

access

being

cycles

panel

goes

active

(low)

input

bus,

signal

make

wait

clock

state

normally

cycle

accessed

(wait

type

active

(low)

atthe

to

the

non-maskable

d r iven

active

devices

DMA

---

active

(low)

to

CONTROL

-------

5-100

Since

is

the

state

cycle

generator

used

devices

(high),

CPU.This

the

signal

request

LINES

-----

bus

bit

is

a

response

a

16

bit

ignored.

WAIT/

generator

during

by

by

inserting

holds

states)

to

WAIT/

at

the

S-100

CPU. When

NMI/

interrupt

(low)

at

a t

the

access

signal

accesses

access

The

signal

accesses

must

slow

PRDY/

desired.

halt

is

one

NMI/

goes

request

the

CPU. r

signals

can

be

memory

wait

active

or

goes

bus,

of

is

active

5 - 1 0 0

he

to

the

5IXTN/

are

to

a

is

never

go

active

make

to

enabled

states

XRDY

single

active

the

the

driven

input

bUS,

PHOLD/

bus.

is

required

request

XRDY

the

the

on-board

by

or

I/O

(low)

is

step

(low).

signal

maskable

active

(low)

to

the

signal

not

requested

or

(low)

WAIT/

at

for

normally

for

PROY

a

jumper

devices

the

the

When

INT/

used

by'

a

when

at

signal

EPROM.

CPU.

the

number

processor.

by

the

16

by

the

option.

to

used

PINT/

will

the

CPU.

bit

the.

driven

active

The

extend

The

is

be

interrupt

at

the

(low)

the

CPU

at

the

CPU.

This

When PHOLD/

s i gn a I BU5RQ/ wi I I

is

used

by

board

~emory

board,

CPU.

EPROM

PRDY/

device

of

clock

by

front

PWAIT/

driven

active

request

S-100

is

the

The

low

The

for

an

the

is

be

DMA

The

operations

states

AD05B/

active

5MEMR,

may

C/CDSB/

active

primary

the

tri-states

(low).

5M1,

be

tri-stated

tri-states

(low).

are

PHLDA s i g na I

I:X\1A

control

SYSTE\l

------

A

positive

51.

The

the

places

at

on

are

A

positive

voltage

regUlator

should

POWER

-----

This

regulator

+5

volt

around

S-100

the

board

decoupled

be

voltage

bus

is

is

present

lines

0005B/,

data

STATDSB/

SImA

When

going

signals

LINES

-----

8

volts

is

output

the

pin

to

with

16

volts

regulated

decoupled

used

out

bus

the

and

by

the

a

DMA

active

and

DC

is

regulated

decoupled

is

board.

52.

The

develop

1.5

DC

on

S-100

to

tri-state

AD05B/,

drivers

address

tri-states

SWO/

when

STATD5B/

signal

device

(h

drive

should

on

decoupled

A

negative

voltage

-12

volts

uf

capacitors

should

on

the

by

a

bus

5TATD5B/,

when

bus

drivers

the

it

is

if

selected

PSYNC, PWR/

is

granted

i g

h)

i t

wi

its

own

be

present

on

the

its

input

by

.1

16

is

regulated

and

at

be

present

1.5

board

uf

pins

to

capacitor

50

the

and

it

is

status

driven

I I

signals

on

board

by

uf

volts

-5

thier

at

develop

and

bus

drivers

C/CD5B. OOD5B/

driven

when

signals

active

by

a

jumper

and

POBIN

access

nor

rna I I Y 8 C t i

on

to

5-100

to

a

1.5

bus

develop

uf

capacitors

DC

should

by

two

volts.

Both

inputs

8-100

bus

+12

at

its

53.

active

it

is

SOUT,

(low).

when

to

the

vat

the

bus.

pins

+5

capacitor

at

be

regUlators

regUlators

and

pin

volts.

input

for

DMA

tri-

(low).

driven

SINP,

MWRITE

option.

driven

bus

e

the

1

and

volts.

and

various

present

outputs.

2.

This

The

and

by

a

13

SYSTEM

------

The

board

oscillator.

flop.

the

the

The 2

clock

The

CPU

S-100

MHz

is

CLOCK

-----

generates

2/4

and

bus

clock

always

The

MRs

related

at

is

2

4

MHz

jumpers

02.

provided

MHz

all

timing

clock

circuitry.

An

inverted

and

is

is

selects

directly

not

from

divided

which

The

version

affected

a 4

selected

to

S-100

MHz

down

clock

of

by

crystal

to

rate

clock

02

bus

the

2

is

provided

as

2/4

controlled

MHz

is

is

provided

CLOCK/.

MHz

by a

applied

~s

jumper.

flip

to

to

01.

This

~!~!§M

!!~~~!

When PRESET

capacitor

driven

signal

is

then

1.

2.

3.

4.

The

reset

released

takes

circuit

during

on

low

is

synchronized

applied

The Z80

The 8251

POC

The

for

to

charge

de-bounces

power

!:~£!:!QNS

is

driven

by

this

the

to

line

system

the

following

CPU

USART

at

the

S-100

power-on

signal

jump

will

approximately

the

100

the

up.

active

is

discharged.

reset

to

the

bus

latch

remain

uf

capacitor

reset

(low)

button

system

circuits:

active

470

milliseconds

switch

at

clock

(low)

to

and

the

This

being

a

provides

S-100

signal

pressed.

with

~fter

due

true

bus,

a

flip

the

to

level.

a

is

The

switch

the

This

reset

a

100

normally

PRESET

flop

and

time

same

signal

uf

is

it

14

Swi

tch

SWI

-

selects

US

ART

the

TIMER

base

APPENDIX

AND

address

I/O

A

ADDRESS

range

of

ING

8

addresses

RANGE

-----

00-07

08-0F

10-17

18-IF

20-27

28-2F

30-37

38-3F

40-47

48-4F

50-57

58-SF

60-67

68-6F

70-77

78-7F

80-87

88-8F

90-97

98-9F

AO-A7

A8-AF

BO-B7

B8-BF

CO-C7

C8-CF

DO-D7

D8-DF

EO-E7

E8-EF

FO-F7

F8-FF

SWl

SW2

X

X X X X

X X

X

X X

X

X

X

X X X X

X

X X

X

X X X

X X

X X

X

SW3

X X X X

X X X X

X

X X X

X

X

X X X

X X

X

X

SW4 SW5

X X

X X

X X

X X

X

X X

X

X X

X

X X

X

X

X

X

X

X

X

X

X

X

X·

X

X

First

2nd

3rd

4th

5th

6th

7th

8th

address

"

"

"

"

"

"

"

XO

Xl

X2

X3

X4

X5

X6

X7

or

or

or

or

or

or

or

or

X8

X9

XA

XB-

XC

XD

XE

XF-

- Timer

-

"

"

tl

Parallel

-

-

"

-

USART

"

o

Data

1

2

Control

Data

Control

15

"

"

Input

"

and

"

Ou

tputPort

"

"

SWI - 5

SWI -

SWl - 3

SWl - 2

SWl - 1

------

4

~j

~~

-

[~~~~~~

[~~~~~~~~

---Sase

-~I/O

Address

PorI

Seleelion

Seleelion

A2

Al

--------------------------------------

Timer

"

"

"

Parallel

II

US

ART

"

0

Data

1

"

2

Control

"

I/O

"

Data

Control

0 0 0

0 0 1

0 1

0 1

1

1

1

1 1 1

0 0

0

1

AO

0

1

1

0

16

Pin

---

No

--

-

.

TABLE

1

CONNECTORJlSIGNALS

Function

--------

11

20

PIN

---1--

10

11

12

14

15

16

17

18

19

20

21

22

23

24

25

2

3

4

5

6

7

8

2

3

4

5

6

7

8

9

NO

RS232

RS232

Requestto

Clear

Data

Signal

Carrier

Reverse

Data

TABLE

CONNECTOR

FUNCTIONS

--Output-Port

Counter

Transmit

Receive

to

Set

Ground

Detect

Channel

Terminal

2

J2

SIGNALS

Output

Output

Output

Output

Output

Output

Output

Signal

Output

Counter

Counter

InDut

In~ut

ln~~t

Input

Input

Input

Input

Input

Port

Port

Port

Port

Port

Port

Port

Port

Signal

Input

Port

input)

Counter

Send

Send

Ready

Port

Port

Port

Port

Port

Port

Port

Ground

Port

1

Gate

2

Gate

Data

Data

Data

Data

Data

Data

Data

Data

Ground

Strobe

1

Output

2

Output

Data

Data

Transmit

Ready

Data

Data

Data

Data

Data

Data

Data

Data

Clock

Input

Input

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

(also

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

counter

2

17

•

TH I S PAGE

LEFT

BLANK

18

-

APPENDIX

USART

8251

or

B

9551

computer

The

tasks:

1.

Output

2.

Input

3.

Outputs

4.

Inputs

Control

they

USART.

The

monitoring

conditions,

codes.

or

control

INITIALIZATION

--------------

The

s

tar

following

following

operations.

which

codes

are

status

Program

USART

tin

g a

it

used

the

when and how

signals

may be

new

power-up

completion

Following

can

program

control

status

data

data

determine

to

register

USART

logic

initialized

se

neither

controlling

codes

to

be

that

set

or

contents

operation

may

may

be

ria

1 I

and

of

a

transmit

transmitted

has

been

the

mode

reset

read

be

used

/0

subsequently

one

reset,

data,

based

to

following

seq

ue nc e •

activity

the

nor

the

USART

received

the

control

will

in

write

on

request

and

USART

receive

performs

USART

signals

be

order

reading

interrupts.

a

system

The

may

preceeding

enters

data.

the

will

read

to

data

USART mus t be

be

opearate

output

by

determine

or

output

status

reset

reset

an

the

bit

or

at

a new

idle

following

in

and

by

the

program

error

control

levels,

prior

res

any

time

set

state

to

e t

of

in

The

USARTis

from

needed

mode

a cornnand.

the

to

control

ASYNCHRONOUS

C/O=1

C/D=O

[~

FIGt~E

i

nit

i a

liz

ed

wit

processor.

initialize

is

Figure

followed

the

1

USART

by

OPERATION

1\DOE

--~~---

CONTROL

DATA

1.

Control

-

1

~~~~~~~NG

Word

h

two,

shows

one

or

Sequence

19

t hr ee 0 r f 0 ur

the

sequence

for

synchronous

two

SYNC

SY~~CHP.oNOUS

r-----------

1\1ODE

SYNC#1

SYNC#2

(OPTIONAL)

DATA

for

Initialization.

con

of

control

operation,

characters,

OPERATION

CO~~TRO

t r 0 I w0 r ds

words

the

and

then

INITIALING

SEQUENCE

Only

command

logic

proper

Following

as

operation,

mode

characters.

For

out

subsequent

commands.

anticipating

signal

a

internal

destination

a mode

byte)

either

put

or

single

bytes

a

reset,

control.

then

output

asychronous

a

sac

byte

There

following

-

address

and

to

the

0 nt r 0 I

output

are

a

mode

SYNC

the

based

the

If

next,one

as

control

two

control

an

is

character

chip

on

first

the

or

synchronous

cod

e i

as

ways

internal

set

directs

the

control

mode

or

codes

sin

control

in

input;

aside

bytes.

control

sequence

control

two

bytes

will

t e r

pre

which

Following

reset

for

code

codes

control

command.

mode

For

in

which

output

specifies

(as

be

operation,

ted

control

this

interpreted

a

are

to

information

it

is

determined

the

sac

interpreted

logic

an

may

external

bytes,

be

possible,

to

is

received.

interpreted

synchronous

by

as

SYNC

next

0

mm

and.

return

reset

its

the

byte

AI I

as

to

The

Control

asynchronous

and

relationship

transmitter

or

or

the

USART

code

1

specifies

transmitted

every

mode

BIT

of

NO

--O,r-

2,

3

4

5

6

interprets

clock

64th

operation

mode cod.; s

bits

operation

between

clock

DESCRIPTION

-OO-~-SYNC-M)DE

0

asynchronous

rate.

on

every

pulse.

00

01

10

11

0

1

0

1

0

1

5 BITS

=

6 BITS

=

7

=

8 BITS

=

PARITY

=

PARITY

=

ODD

=

EVEN

=

SYNDET

=

SYNDET

=

and

as

1

is

specified.

data

Asynchronous

check

synchronous.

BITS

PARITY

PARITY

determine

transfer,

pulse,

A

zero

PER

CHARACTER

PER

CHARACfER

PER

CHARACTER

PER

CHARACTER

DISABLE

EN..WLE

OUTPUT

INPUT

as

shown

whether

A

non-zero

operation

baud

serial

on

in

both

rate

every

bits

in

data

Figure

synchronous

value

and

16th

defines

and

may be

clock

0

and

2

and

in

receiver

received

pulse,

1

defines

bits

3.

or

0

the

or

For

determine

data

synchronous

character.

7

the

0

1

FIGURE

and

number

2

SYNC

=

1

SYNC

=

2.

Synchronous

asynchronous

of

data

CHARACTERS

CHARACTER

Mode

modes,

bits

which

20

Control

control

will

Code

be

bits

present

2

and

in

3

each

-

For

whether

whether

mo

bits,

11/2,

differs

Control

stop

specified

cases,

pUlses,

s ynch

as

data

synchronous

de a cha

bits

In"

synchronous

ron

internal

specified

stream

BIT

--0,1-

there

odd

or

rat

e r

an

optional

or

2

trailing

for

synchronous

code

the

respectively.

bits

will

with

half

i za t

NO

ion

synchonization

by

in

and