Page 1

Technical

Reference

Guide

for

Compaq Deskpro 4000N and 4000S Personal Computers

Page 2

This hardcopy is designed to be placed into a standard 3-ring binder. Provided below is a title block that

can be copied and cut out and placed into the slip or taped onto the edge of the binder.

Deskpro 4000N and 4000S Personal Computers

TRG

Page 3

Technical Reference Guide

NOTICE

The information in this document is subject to change without notice.

COMPAQ COMPUTER CORPORATION SHALL NOT BE LIABLE FOR TECHNICAL OR

EDITORIAL ERRORS OR OMISSIONS HEREIN; NOR FOR INCIDENTAL OR

CONSEQUENTIAL DAMAGES RESULTING FROM THE FURNISHING, PERFORMANCE,

OR USE OF THIS MATERIAL. IT IS THE RESPONSIBILITY OF MANUFACTURERS TO

ENSURE THAT DEVICES DESIGNED TO BE USED WITH COMPAQ PRODUCTS

COMPLY WITH FCC CLASS B EMISSIONS REQUIREMENTS.

This guide contains information protected by copyright. No part of this document may be

photocopied or reproduced in any form without prior written consent from Compaq Computer

Corporation.

1997 Compaq Computer Corporation

All rights reserved. Printe d in the USA

Compaq, Deskpro, LTE, Contura, Presario, ProLinea

Registered U.S. Patent and Trademark Office

Product names mentioned in this document may be trademarks and/or registered trademarks of other companies.

For more information regarding specifications and Compaq-specific parts please contact Compaq

Computer Corporation, Industry Relations Department.

Compaq Deskpro 4000N and 4000S Personal Comput ers

Technical Reference Guide for

First Edi tion - Se ptember 1997

Document Number DSK-109A/0907

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition – September 1997

i

Page 4

Technical Reference Guide

Compaq Deskpro 4000N and 4000S Personal Computers

ii

Firs t Edition – Sept ember 1997

Page 5

Technical Reference Guide

TABLE OF CONTENTS

CHAPTER 1 INTRODUCTION.............................................................................................................

1.1 ABOUT THIS GUIDE........................................................................................................... 1-1

1.1.1 USING THIS GUIDE..................................................................................................... 1-1

1.1.2 ADDITIONAL INFORMATION SOURCES.................................................................. 1-1

1.2 NOT ATIONAL CONVENTIONS..........................................................................................1-2

1.2.1 VALUES........................................................................................................................ 1-2

1.2.2 RANGES........................................................................................................................ 1-2

1.2.3 SIGNAL LABELS.......................................................................................................... 1-2

1.2.4 REGISTER NOTATION AND USAGE ......................................................................... 1-2

1.2.5 BIT NOTATION............................................................................................................ 1-2

1.3 C OMMON ACRONYMS AND ABBREVIATIONS.............................................................. 1-3

CHAPTER 2 SYSTE M OVERVIEW .....................................................................................................

2.1 INTRODUCTION..................................................................................................................2-1

2.2 FEATURES...........................................................................................................................2-2

2.2.1 STANDARD FEATURES..............................................................................................2-2

2.2.2 MODEL DIFFERENCES ...............................................................................................2-3

2.2.3 OPTIONS.......................................................................................................................2-3

2.3 MECHANICAL DESIGN...................................................................................................... 2-4

2.3.1 CABINET LAYOUT...................................................................................................... 2-4

2.3.2 CHASSIS LAYOUT....................................................................................................... 2-6

2.3.3 SYSTEM BOARD LAYOUT.........................................................................................2-7

2.4 SYSTEM ARCHITECTURE..................................................................................................2-8

2.4.1 MICROPROCESSOR................................................................................................... 2-10

2.4.2 MEMORY.................................................................................................................... 2-10

2.4.3 SUPPORT CHIPSET.................................................................................................... 2-11

2.4.4 MASS STORAGE........................................................................................................ 2-11

2.4.5 SERIAL AND PARALLEL INTERFACES .................................................................. 2-11

2.4.6 UNIVERSAL SERIAL BUS INTERFACE................................................................... 2-12

2.4.7 GRAPHICS SUBSYSTEM ........................................................................................... 2-12

2.5 SPECIFICATIONS.............................................................................................................. 2-13

CHAPTER 3 PROCESSOR/MEMORY SUBSYSTEM........................................................................

3.1 INTRODUCTION..................................................................................................................3-1

3.2 PE NTIUM MMX-BASED PROCESSOR/MEMORY SUBSYSTEM.....................................3-2

3.2.1 PENTIUM MMX MICROPROCESSOR.........................................................................3-3

3.2.2 BUS/PROCESSING SPEED SELECT............................................................................ 3-4

3.2.3 SECONDARY (L2) CACHE MEMORY........................................................................ 3-4

3.2.4 SYSTEM MEMORY......................................................................................................3-5

3.2.5 SUBSYSTEM CONFIGURATION.................................................................................3-8

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition – September 1997

iii

Page 6

Technical Reference Guide

CHAPTER 4 SYSTEM SUPPORT.........................................................................................................

4.1 INTRODUCTION..................................................................................................................4-1

4.2 PCI BUS OVERVIEW ........................................................................................................... 4-2

4.2.1 PCI CONNECTOR ......................................................................................................... 4-3

4.2.2 PCI BUS MASTER ARBITRATION..............................................................................4-4

4.2.3 PCI BUS TRANSACTIONS...........................................................................................4-5

4.2.4 OPTION ROM MAPPING ............................................................................................. 4-8

4.2.5 PCI INTERRUPT MAPPING.........................................................................................4-9

4.2.6 PCI CONFIGURATION............................................................................................... 4-10

4.3 ISA BUS OVERVIEW......................................................................................................... 4-11

4.3.1 ISA CONNECTOR ...................................................................................................... 4-12

4.3.2 ISA BUS TRANSACTIONS......................................................................................... 4-13

4.3.3 DIRECT MEMORY ACCESS......................................................................................4-15

4.3.4 INTERRUPTS.............................................................................................................. 4-18

4.3.5 INTERVAL TIMER ..................................................................................................... 4-22

4.3.6 ISA CONFIGURATION............................................................................................... 4-22

4.4 SYSTEM CLOCK DISTRIBUTION.................................................................................... 4-23

4.5 REAL-T I ME C LOCK AND C ONFIGURATION MEMORY............................................... 4-24

4.5.1 CONFIGURATION MEMORY BYTE DEFINITI ONS ................................................ 4-25

4.6 I / O MAP AND REGI ST E R ACCESSING............................................................................ 4-41

4.6.1 SYSTEM I/O MAP ......................................................................................................4-41

4.6.2 87307 I/O CONTROLLER CONFIGURATION........................................................... 4-42

4.7 SYST EM MANAGEMENT SUPPORT ............................................................................... 4-44

4.7.1 FLASH ROM WRITE PROTECT................................................................................ 4-44

4.7.2 PASSWORD PROTECTION........................................................................................ 4-45

4.7.3 I/O SECURITY............................................................................................................4-46

4.7.4 USER SECURITY........................................................................................................ 4-46

4.7.5 TEMPERATURE SENSING........................................................................................ 4-47

4.7.6 POWER MANAGEMENT ........................................................................................... 4-48

CHAPTER 5 INPUT/OUTPUT INTERFACES.....................................................................................

5.1 INTRODUCTION..................................................................................................................5-1

5.2 ENHANCED IDE INTERFACE............................................................................................ 5-1

5.2.1 IDE PROGRAMMING................................................................................................... 5-1

5.2.2 IDE CONNECT ORS ...................................................................................................... 5-8

5.3 DISKETTE DRIVE INTERFACE........................................................................................5-10

5.3.1 DISKETTE DRIVE PROGRAMMING........................................................................ 5-11

5.3.2 DISKETTE DRIVE CONNECTOR.............................................................................. 5-14

5.4 SERIAL INTERFACES....................................................................................................... 5-15

5.4.1 RS-232 INTERFACE ................................................................................................... 5-15

5.4.2 SERIAL INTERFACE PROGRAMMING....................................................................5-16

5.5 PARALLEL INTERFACE................................................................................................... 5-21

5.5.1 STANDARD PARALLEL PORT MODE..................................................................... 5-21

5.5.2 ENHANCED PARALLEL PORT MODE..................................................................... 5-22

5.5.3 EXTENDED C APABILIT IES PORT MODE............................................................... 5-22

5.5.4 PARALLEL INTERFACE PROGRAMMING.............................................................. 5-23

5.5.5 PARALLEL INTERFACE CONNECT OR ................................................................... 5-27

Compaq Deskpro 4000N and 4000S Personal Computers

iv

Firs t Edition – Sept ember 1997

Page 7

Technical Reference Guide

5.6 KEYBOARD/POINTING DEVICE INTERFACE ............................................................... 5-28

5.6.1 KEYBOARD INTERFACE OPERATION ................................................................... 5-28

5.6.2 POINTING DEVICE INTERFACE OPERATION.......................................................5-30

5.6.3 KEYBOARD/POINTING DEVICE INTERFACE PROGRAMMING ......................... 5-30

5.6.4 KEYBOARD/POINTING DEVICE INTERFACE CONNECTOR ................................ 5-34

5.7 ETHERNET INTERFACE...................................................................................................5-35

5.7.1 NIC CONFIGURATION/CONTROL ........................................................................... 5-36

5.7.2 NIC CONNECTORS....................................................................................................5-36

5.8 UNIVERSAL SERIAL BUS INTERFACE........................................................................... 5-37

5.8.1 USB CONFIGURATION..............................................................................................5-37

5.8.2 USB CONTROL...........................................................................................................5-38

5.8.3 USB CONNECTOR ..................................................................................................... 5-38

CHAPTER 6 GRAPHICS SUBSYSTEM...............................................................................................

6.1 INTRODUCTION..................................................................................................................6-1

6.2 SUBSYSTEM DESCRIPTION .............................................................................................. 6-2

6.2.1 S3 TRIO64V2/GX GRAPHICS CONTROLLER ........................................................... 6-2

6.2.2 S3 TRIO64V2/GX GRAPHICS CONFIGURATIONS ...................................................6-3

6.2.3 S3 TRIO64V2/GX GRAPHICS SUBSYSTEM PROGRAMMING.................................6-4

6.2.4 MONITOR POWER CONTROL....................................................................................6-5

6.2.5 CONNECTORS ............................................................................................................. 6-6

CHAPTER 7 POWER SUPPLY AND DIST RIBUTION.......................................................................

7.1 INTRODUCTION..................................................................................................................7-1

7.2 POWE R SUPPLY ASSEMBLY/CONTROL .......................................................................... 7-1

7.2.1 POWER SUPPLY ASSEMBLY......................................................................................7-2

7.2.2 POWER CONTROL.......................................................................................................7-3

7.3 POWER DISTRIBUTION...................................................................................................... 7-4

7.3.1 3.5/5/12 VDC DISTRIBUTION......................................................................................7-4

7.3.2 LOW VOLTAGE DISTRIBUTION................................................................................ 7-5

7.4 SI GNAL DIST RIBUTION..................................................................................................... 7-6

CHAPTER 8 BIOS ROM .......................................................................................................................

8.1 INTRODUCTION..................................................................................................................8-1

8.2 BOOT FUNCTIONS.............................................................................................................. 8-2

8.2.1 BOOT BLOCK...............................................................................................................8-2

8.2.2 QUICKBOOT.................................................................................................................8-2

8.2.3 SILENTBOOT ............................................................................................................... 8-2

8.3 AC CESSING CONFIGURATION MEMORY ....................................................................... 8-3

8.3.1 ACCESSING CMOS...................................................................................................... 8-3

8.3.2 SETTING DEFAULT PARAMETERS.......................................................................... 8-3

8.3.3 ACCESSING CMOS FEATURE BITS........................................................................... 8-4

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition – September 1997

v

Page 8

Technical Reference Guide

8.4 C LIE NT MANAGEMENT SUPPORT................................................................................... 8-5

8.4.1 SYSTEM ID................................................................................................................... 8-7

8.4.2 SYSTEM INFORMATION TABLE ............................................................................... 8-7

8.4.3 TEMPERATURE SENSOR .......................................................................................... 8-12

8.4.4 DRIVE FAULT PREDICTION.....................................................................................8-12

8.4.5 DIMM SUPPORT.........................................................................................................8-13

8.4.6 SECURITY FUNCTIONS............................................................................................ 8-15

8.4.7 ACCESSING CMOS FEATURE BITS......................................................................... 8-16

8.5 PNP SUPPORT.................................................................................................................... 8-17

8.6 POWE R MANAGEME NT SUPPORT ................................................................................. 8-18

APPENDIX A ERROR MESSAGES AND CODES.............................................................................A

A.1 INTRODUCTION.................................................................................................................A-1

A.2 POWE R-ON MESSAGES..................................................................................................... A-1

A.3 BEE P C ODE MESSAGES.................................................................................................... A-1

A.4 POWE R-ON SELF T E ST (POST) MESSAGE S.................................................................... A-2

A.5 PROCE SSOR ERROR MESSAGES (1

A.6 ME MORY ERROR MESSAGES (2

XX-XX

A.7 KE YBOARD ERROR MESSAGES (30

A.8 PRINT E R ERROR MESSAGES (4

XX-XX

A.9 VI DE O ( GRAPHICS) ERROR MESSAGES (5

A.10 DISKETTE DRIVE ERROR MESSAGES (6

A.11 SERIAL INTERFACE ERROR MESSAGES (11

A.12 MODEM COMMUNICATIONS ERROR MESSAGES (12

A.13 HARD DRIVE ERROR MESSAGES (17

A.14 HARD DRIVE ERROR MESSAGES (19

A.15 VIDEO (GRAPHICS) ERROR MESSAGES (24

A.16 AUDIO ERROR MESSAGES (3206A.17 NETWORK INTERFACE E RROR MESSAGES (60

A.18 SCSI INTERFACE E RROR MESSAGES (65

A.19 POINTING DEVICE INTERFACE ERROR MESSAGES (8601-

) ...................................................................... A-3

XX-XX

) ........................................................................... A-4

)....................................................................... A-4

X-XX

)............................................................................ A-5

).......................................................... A-5

XX-XX

) ......................................................... A-6

XX-XX

)................................................... A-6

XX-XX

).................................... A-7

XX-XX

)............................................................... A-8

XX-XX

)............................................................... A-9

XX-XX

) .................................................... A-9

XX-XX

)......................................................................... A-10

XX

) ........................................... A-10

XX-XX

, 66XX-XX, 67XX-XX) ....................... A-11

XX-XX

).............................. A-11

XX

A.20 CEMM PRIVILEDGED OPS ERROR MESSAGES........................................................ A-12

A.21 CEMM EXCEPT I ON E RROR MESSAGES ................................................................... A-12

APPENDIX B ASCII CHARACTER SET .............................................................................................

B.1 INTRODUCTION..................................................................................................................B-1

APPENDIX C KEYB O ARD ...................................................................................................................

C.1 INTRODUCTION..................................................................................................................C-1

C.2 KEYSTROKE PROCESSING................................................................................................C-2

C.2.1 TRANSMISSIONS TO THE SYSTEM ..........................................................................C-3

C.2.2 KEYBOARD LAYOUTS...............................................................................................C-4

C.2.3 KEYS .............................................................................................................................C-7

C.2.4 KEYBOARD COMMANDS.........................................................................................C-10

C.2.5 SCAN CODES.............................................................................................................C-10

Compaq Deskpro 4000N and 4000S Personal Computers

vi

Firs t Edition – Sept ember 1997

Page 9

Technical Reference Guide

C.3 SCANNER DESCRIPTION.................................................................................................C-14

C.3.1 SCANNER OPERATION.............................................................................................C-15

C.3.2 SCANNER INTERFACE.............................................................................................C-18

C.3.3 SCANNER SPECIFICATIONS/REQUIREMENTS ...................................................... C-20

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition – September 1997

vii

Page 10

Technical Reference Guide

LIST OF FIGURES

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

F

IGURE

2–1. C

2–2. C

2–3. C

2–4. C

2–5. S

2–6. C

2–7. M

3–1. P

3–2. P

3–3. S

4–1. PCI B

4–2. 32-B

4–3. T

4–4. PCI C

4–5. ISA B

4–6. ISA E

4–7. M

4–8. C

5–1. 40-P

5–1. 50-P

5–2. 34-P

5–3. S

5–4. S

5–5. P

OMPAQ DESKPRO

ABINET LAYOUT

ABINET LAYOUT

HASSIS LAYOUT

YSTEM BOARD LAYOUT

OMPAQ DESKPRO

ICROPROCESSOR ARCHITECTURAL DIAGRAM

ROCESSOR/MEMORY SUBSYSTEM ARCHITECTURE

ENTIUM

YSTEM MEMORY MAP

YPE

ONFIGURATION MEMORY MAP

ERIAL INTERFACES BLOCK DIAGRAM

ERIAL INTERFACE CONNECTOR (MALE

ARALLEL INTERFACE CONNECTOR (FEMALE

MMX M

US DEVICES AND FUNCTIONS

PCI B

IT

0 C

ONFIGURATION CYCLE

ONFIGURATION SPACE MAP

US BLOCK DIAGRAM

XPANSION CONNECTOR

ASKABLE INTERRUPT PROCESSING

IDE C

IN

IDE C

IN

IN DISKETTE DRIVE CONNECTOR

5–6. 8042-TO-K

5–7. K

5–8. E

5–9. E

5–10. E

5–11. U

6–1. S3 T

6–2. VGA M

7–1. P

7–2. P

7–3. L

7–4. S

C–1. K

C–2. K

C–3. U.S. E

C–4. N

C–5. U.S. E

C–6. N

C–7. U.S. E

C–8. N

C–9. S

C–10. S

EYBOARD OR POINTING DEVICE INTERFACE CONNECTOR

THERNET INTERFACE BLOCK DIAGRAM

THERNET

THERNET

NIVERSAL SERIAL BUS CONNECTOR (ONE OF TWO AS VIEWED FROM REAR OF CHASSIS

64V2/GX-B

RIO

ONITOR CONNECTOR

OWER SUPPLY ASSEMBLY

OWER CABLE DIAGRAM

OW VOLTAGE SUPPLY

IGNAL DISTRIBUTION DIAGRAM

EYSTROKE PROCESSING ELEMENTS

EYBOARD-TO-SYSTEM TRANSMISS I ON OF CODE 58H

NGLISH

ATIONAL

NGLISH WINDOWS

ATIONAL WINDOWS

NGLISH WINDOWS

ATIONAL WINDOWS

CANNER ELEMENTS

CANNER OPERA TION FLOW CHART

4000S P

, F

, R

, T

4000N

ERSONAL COMP UTER WITH MONITOR

RONT VIEW

EAR VIEW

OP VIEW

, C

.......................................................................................2-4

.........................................................................................2-5

............................................................................................2-6

OMPONENT SIDE

4000S S

AND

.....................................................................2-7

YSTEM ARCHITECTURE

................................................................ 2-10

ICROPROCESSOR INTERNAL ARCHITECTURE

.......................................................................................................3-7

.....................................................................................4-2

US CONNECTOR

(32-B

IT TYPE

) ..................................................................... 4-3

........................................................................................4-6

......................................................................................4-7

................................................................................................4-11

..........................................................................................4-12

, B

LOCK DIAGRAM

......................................................................................4-24

ONNECTOR

ONNECTOR

. ................................................................................................. 5-8

. ................................................................................................. 5-9

.............................................................................. 5-14

............................................................................. 5-15

DB-9

AS VIEWED FROM REAR OF CHASSIS

DB-25

EYBOARD TRANSMISS I ON OF CODE EDH

......................................................................... 5-35

AUI C

RJ-45 C

ONNECTOR

ONNECTOR

ASED GRAPHICS SUBSYSTEM

(DB-15,

VIEWED FROM REAR

......................................................................................5-36

, (F

, B

LOCK DIAGRAM

EMALE

DB-15,

AS VIEWED FROM THE REAR OF CHASSIS

....................................................................7-1

..................................................................................................7-4

, B

LOCK DIAGRAM

.........................................................................7-5

.......................................................................................7-6

, B

LOCK DIAGRAM

(101-KEY) K

(102-KEY) K

EYBOARD KEY POSITIONS

EYBOARD KEY POSITIONS

(101W-KEY) K

(102W-KEY) K

EYBOARD KEY POSITIONS

(101WE-KEY) K

(102WE-KEY) K

, B

LOCK DIAGRAM

EYBOARD KEY POSITIONS

..........................................................................C-14

EYBOARD KEY POSITIONS

EYBOARD KEY POSITIONS

..............................................................................C-16

.......................................2-1

, B

LOCK DIAGRAM

..............2-9

............................................................3-2

...........................................3-3

.................................................... 4-18

)........... 5-15

AS VIEWED FROM REAR OF CHASSIS

, T

IMING DIAGRAM

............................ 5-28

).. 5-27

............................................... 5-34

)............................................. 5-36

)... 5-38

, B

LOCK DIAGRAM

...................................6-2

).... 6-6

....................................................C-2

, T

IMING DIAGRAM

..........................C-3

.......................................................C-4

............................................................C-4

...................................C-5

........................................C-5

.................................C-6

......................................C-6

Compaq Deskpro 4000N and 4000S Personal Computers

viii

Firs t Edition – Sept ember 1997

Page 11

T

ABLE

1–1. A

LIST OF TABLES

CRONYMS AND ABBREVIATIONS

Technical Reference Guide

.......................................................................................1-3

2–1. A

T

ABLE

T

2–2. S

ABLE

T

2–3. G

ABLE

T

2–4. E

ABLE

T

2–5. E

ABLE

T

2–6. P

ABLE

T

2–7. D

ABLE

T

2–8. 8X CD-ROM D

ABLE

T

2–9. H

ABLE

3–1. P

T

ABLE

T

3–2. P

ABLE

T

3–3. SW1 BUS/C

ABLE

T

3–4. SDRAM P

ABLE

T

3–5. SPD A

ABLE

T

3–6. H

ABLE

4–1. 32-B

T

ABLE

T

4–2. PCI B

ABLE

T

4–3. PCI D

ABLE

T

4–4. PCI F

ABLE

T

4–5. PCI D

ABLE

T

4–6. PCI/ISA B

ABLE

T

4–7. ISA E

ABLE

T

4–8. D

ABLE

T

4–9. DMA P

ABLE

T

4–10. DMA C

ABLE

T

4–11. M

ABLE

T

4–12. M

ABLE

T

4–13. I

ABLE

T

4–14. I

ABLE

T

4–15. C

ABLE

T

4–16. C

ABLE

T

4–17. S

ABLE

T

4–18. 87307 I/O C

ABLE

T

4–19. S

ABLE

RCHITECTURAL COMPARISON

UPPORT CHIPSETS

RAPHICS SUBSYSTEM OVERVIEW

NVIRONMENTAL SPECIFICATIONS

LECTRICAL SPECIFICATIONS

HYSICAL SPECIFICATIONS

ISKETTE DRIVE SPECIFICATIONS

ARD DRIVE SPECIFICATIONS

ROCESSOR/MEMORY ARCHITECTURAL HIGHLIGHTS

ENTIUM

OST

EFAULT

YSTEM MANAGEMENT CONTROL REGISTERS

MMX M

ORE SPEED POSITIONS TO

ERFORMANCE TIMES

DDRESS MAP

/PCI B

RIDGE CONFIGURATION REGISTERS

PCI B

IT

US MASTERING DEVICES

EVICE CONFIGURATION ACCESS

UNCTION CONFIGURATION ACCES

EVICE IDENTIFICATION

RIDGE CONFIGURATION REGISTERS FOR THE

XPANSION CONNECTOR PINOUT

DMA C

AGE REGISTER ADDRESSES

ONTROLLER REGISTERS

ASKABLE INTERRUPT PRIORITIES AND ASSIGNMENTS

ASKABLE INTERRUPT CONTROL REGISTERS

NTERVAL TIMER FUNCTIONS

NTERVAL TIMER CONTROL REGISTERS

LOCK GENERATION AND DISTRIBUTION (PENTIUM-BASED SYSTEM

ONFIGURATION MEMORY

I/O MAP...........................................................................................................4-41

YSTEM

..........................................................................................................2-11

RIVE SPECIFICATIONS

ICROPROCESSOR BUS/CORE SPEED SWITCH SETTINGS

(SDRAM DIMM).................................................................................3-6

US CONNECTOR PINOUT

HANNEL ASSIGNMENTS

ONTROLLER PN

.............................................................................................2-8

....................................................................................2-12

....................................................................................2-13

...........................................................................................2-13

...............................................................................................2-13

.....................................................................................2-14

................................................................................ 2-14

...........................................................................................2-15

............................................................3-1

GPIO A

SSIGNMENTS

...................................................3-4

............................................................................................3-5

(VT82C595) .............................................. 3-8

.................................................................................4-3

...........................................................................................4-4

................................................................................4-6

..............................................................................4-7

.............................................................................................4-8

VT82C586 (P55C-B

............................................................................... 4-12

......................................................................... 4-15

................................................................................... 4-16

......................................................................................4-17

.................................................... 4-19

.................................................................. 4-19

.........................................................................................4-22

........................................................................... 4-22

(CMOS) MAP....................................................................... 4-25

P S

TANDARD CONTROL REGISTERS

................................................................... 4-44

.............................3-4

ASED SYSTEMS

)4-10

)............................... 4-23

........................................ 4-42

5–1. IDE PCI C

T

ABLE

T

5–2. IDE B

ABLE

T

5–3. IDE ATA C

ABLE

T

5–4. IDE C

ABLE

T

5–5. 40-P

ABLE

T

5–6. 40-P

ABLE

T

5–7. D

ABLE

T

5–8. D

ABLE

T

5–9. 34-P

ABLE

T

5–10. DB-9 S

ABLE

T

5–11. S

ABLE

ONFIGURATION REGISTERS

US MASTER CONTROL REGISTERS

ONTROL REGISTERS

ONTROLLER COMMANDS

IDE C

IN

IN

ISKETTE DRIVE CONTROLLER CONFIGURATION REGISTERS

ISKETTE DRIVE CONTROLLER REGISTERS

IN DISKETTE DRIVE CONNECTOR PINOUT

ERIAL INTERFACE CONFIGURATION REGISTERS

ONNECTOR PINOUT

IDE C

ONNECTOR PINOUT

ERIAL CONNECTOR PINOUT

................................................................................5-2

.............................................................................5-2

.........................................................................................5-3

..........................................................................................5-6

.......................................................................................5-8

.......................................................................................5-9

............................................. 5-11

....................................................................... 5-12

................................................................... 5-14

................................................................................. 5-15

.............................................................. 5-16

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition – September 1997

ix

Page 12

Technical Reference Guide

T

5–12. S

ABLE

T

5–13. P

ABLE

T

5–14. P

ABLE

T

5–15. DB-25 P

ABLE

T

5–16. 8042-TO-K

ABLE

T

5–17. K

ABLE

T

5–18. CPU C

ABLE

T

5–19. K

ABLE

T

5–20. USB I

ABLE

T

5–21. USB C

ABLE

T

5–22. USB C

ABLE

ERIAL INTERFACE CONTROL REGISTERS

ARALLEL INTERFACE CONFIGURATION REGISTERS

ARALLEL INTERFACE CONTROL REGISTERS

ARALLEL CONNECTOR PINOUT

EYBOARD COMMANDS

EYBOARD/MOUSE INTERFACE CONFIGURATION REGISTERS

OMMANDS TO THE

EYBOARD/POINTING DEVICE CONNECTOR PINOUT

NTERFACE CONFIGURATION REGISTERS

ONTROL REGISTERS

ONNECTOR PINOUT

........................................................................ 5-17

......................................................... 5-23

................................................................... 5-24

.......................................................................... 5-27

.................................................................................. 5-29

........................................... 5-30

8042...................................................................................... 5-32

........................................................ 5-34

................................................................. 5-37

.............................................................................................5-38

..............................................................................................5-38

6–1. G

T

ABLE

T

6–2. S3 T

ABLE

T

6–3. GD5436 PCI C

ABLE

T

6–4. S

ABLE

T

6–5. S3-S

ABLE

T

6–6. M

ABLE

T

6–7. DB-15 M

ABLE

7–1. P

T

ABLE

8–1. PNP C

T

ABLE

T

8–1. PNP BIOS F

ABLE

T

8–2. APM BIOS F

ABLE

T

A–1. P

ABLE

T

A–2. B

ABLE

T

A–3. P

ABLE

T

A–4. P

ABLE

T

A–5. M

ABLE

T

A–6. K

ABLE

T

A–7. P

ABLE

T

A–8. V

ABLE

T

A–9. D

ABLE

T

A–10. S

ABLE

T

A–11. S

ABLE

T

A–12. H

ABLE

T

A–13. H

ABLE

T

A–14. H

ABLE

T

A–15. A

ABLE

T

A–16. N

ABLE

T

A–17. SCSI I

ABLE

T

A–18. P

ABLE

T

A–19. CEMM P

ABLE

T

A–20. CEMM E

ABLE

RAPHICS SUBSYSTEM COMPARISON

64V2/GX-B

RIO

TANDARD

ONITOR POWER MANAGEMENT CONDITIONS

OWER SUPPLY SPECIFICATIONS

OWER-ON MESSAGES

EEP CODE MESSAGES

OWER-ON SELF TEST

ROCESSOR ERROR MESSAGES

EMORY ERROR MESSAGES

EYBOARD ERROR MESSAGES

RINTER ERROR MESSAGES

IDEO (GRAPHICS

ISKETTE DRIVE ERROR MESSAGES

ERIAL INTERFACE ERROR MESSAGES

ERIAL INTERFACE ERROR MESSAGES

ARD DRIVE ERROR MESSAGES

ARD DRIVE ERROR MESSAGES

ARD DRIVE MESSAGES

UDIO ERROR MESSAGES

ETWORK INTERFACE ERROR MESSAGES

OINTING DEVICE INTERFACE ERROR MESSAGES

VGA M

PECIFIC CONTROL REGISTER MAPPING

ONITOR CONNECTOR PINOUT

LIENT MANAGEMENT FUNCTIONS

UNCTIONS

NTERFACE ERROR MESSAGES

RIVILEGED OPS ERROR MESSAGES

XCEPTION ERROR MESSAGES

ASED SUBSYSTEM EXTENDED

ONFIGURATION SPACE REGISTERS

I/O M

ODE

.....................................................................................................8-17

UNCTIONS

(INT15) ..................................................................................... 8-19

..................................................................................................... A-1

..................................................................................................... A-1

(POST) M

............................................................................................. A-4

.............................................................................................. A-5

) E

RROR MESSAGES

................................................................................................. A-9

............................................................................................. A-10

..................................................................................6-1

................................................................................6-4

APPING

.........................................................................6-5

...............................................................................6-6

.........................................................................................7-2

(INT15) ................................................................ 8-5

ESSAGES

........................................................................ A-2

......................................................................................... A-3

.......................................................................................... A-4

.............................................................................. A-5

.................................................................................. A-6

............................................................................. A-6

............................................................................. A-7

...................................................................................... A-8

...................................................................................... A-9

...................................................................... A-10

............................................................................. A-11

......................................................................... A-12

VGA M

.........................................6-3

ODES

...............................................................6-4

....................................................................6-5

........................................................... A-11

.................................................................. A-12

B–1. ASCII C

T

ABLE

C–1. K

T

ABLE

T

C–2. K

ABLE

T

C–3. S

ABLE

T

C–4. S

ABLE

T

C–5. S

ABLE

Compaq Deskpro 4000N and 4000S Personal Computers

x

HARACTER SET

EYBOARD-TO-SYSTEM COMMANDS

EYBOARD SCAN CODES

CANNER PERFORMANCE CHART

CANNER

CANNER SPECIFICATIONS

I/F S

IGNALS

....................................................................................................B-1

...............................................................................C-10

.................................................................................................C-11

.....................................................................................C-17

.....................................................................................................C-18

...............................................................................................C-20

Firs t Edition – Sept ember 1997

Page 13

Chapter 1

INTRODUCTION

1. Chapter 1 INTRODUCTION

Technical Reference Guide

1.1

ABOUT THIS G UIDE

This guide provides technical information about the Compaq Deskpro 4000N and 4000S

Personal Computers. This document includes information regarding system design, function, and

features that can be used by programmers, engineers, technicians, and system administrators.

1.1.1 USING THIS G U ID E

This guide consists of chapters and appendices. The chapters primarily describe the hardware

and firmware elements contained within the chassis and specifically deal with the system board

and the power supply assembly. The appendices contain general information about standard

peripheral devices such as the keyboard as well as separate audio or other interface cards, as well

as other general information in tabular format.

1.1.2 ADDITIONAL INFORMATION SOURCES

This guide does not describe in detail other manufacturer’s components used in the product

covered. For more information on individual commercial-off-the-shelf (COTS) components refer

to the indicated manufacturers’ documentation. The products covered by this guide use

architecture based on industry-standard specifications that can be referenced for detailed

information.

Hardcopy documentation sources:

♦ The Lotus/Intel/Microsoft Expanded Memory Specification, Ver. 4.0

♦ PCI Local Bus Specification Revision 2.1

♦ Extended Industry Standard Architecture Expansion Bus Technical Reference Guide,

p/n 130584, Second Edition, Compaq Computer Corporation

♦ Compaq Basic Input/Out System (BIOS) Technical Reference Guide

Doc.# 074A/0693, Fourth Edition, Compaq Computer Corporation

Online information sources:

♦ Compaq Computer Corporation: http://www.compaq.com

♦ Intel Corporation: http://www.intel.com

♦ VIA Technologies Incorporated: http://www.via.com

♦ National Semiconductor: http://www.national.com

♦ S3 Incorporated: http://www.S3.com

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

1-1

Page 14

Chapter 1 Introduction

1.2 NOTATIONAL CONVENTIONS

1.2.1 VALUES

Hexadecimal values are indicated by the letter “h” following an alpha-numerical value. Binary

values are indicated by the letter “b” following a value of ones and zeros. Memory addresses

expressed as “SSSS:OOOO” (SSSS = 16-bit segment, OOOO = 16-bit offset) can be assumed as

a hexadecimal value. Values that have no succeeding letter can be as sumed t o be decimal.

1.2.2 RANGES

Ranges or limits for a parameter are shown as a pair of values separated by two dots:

Example: Bits <7..4> = bits 7, 6, 5, and 4.

1.2.3 SIGNAL LABELS

Signal names are indicated using abbreviations, acronyms, or, if possible, the full signal name in

all capital letters. Signals that are meant to be active low are indicated with a dash immediately

following the name.

1.2.4 REGISTER NOTATION AND USAGE

This guide uses standard Intel naming conventions in discussing the microprocessor’s (CPU)

internal registers. Registers that are accessed through programmable I/O using an indexing

scheme are indicated using the following format:

03C5.17h

Index port

Data port

In th e e xam ple above, reg ist er 03C5.17h i s accessed by writing the index port value 17h to the

index address (03C4h), followed by a write to or a read from port 03C5h.

1.2.5 BIT NOTATION

Bit values are labeled with bit <0> representing the least-significant bit (LSb) and bit <7>

representing the most-significant bit (MSb) of a byte. Bytes, words, double words, and quad

words are typically shown with most-significant portions on the left or top and the leastsignificant portions on the right or bottom respectively.

1-2

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 15

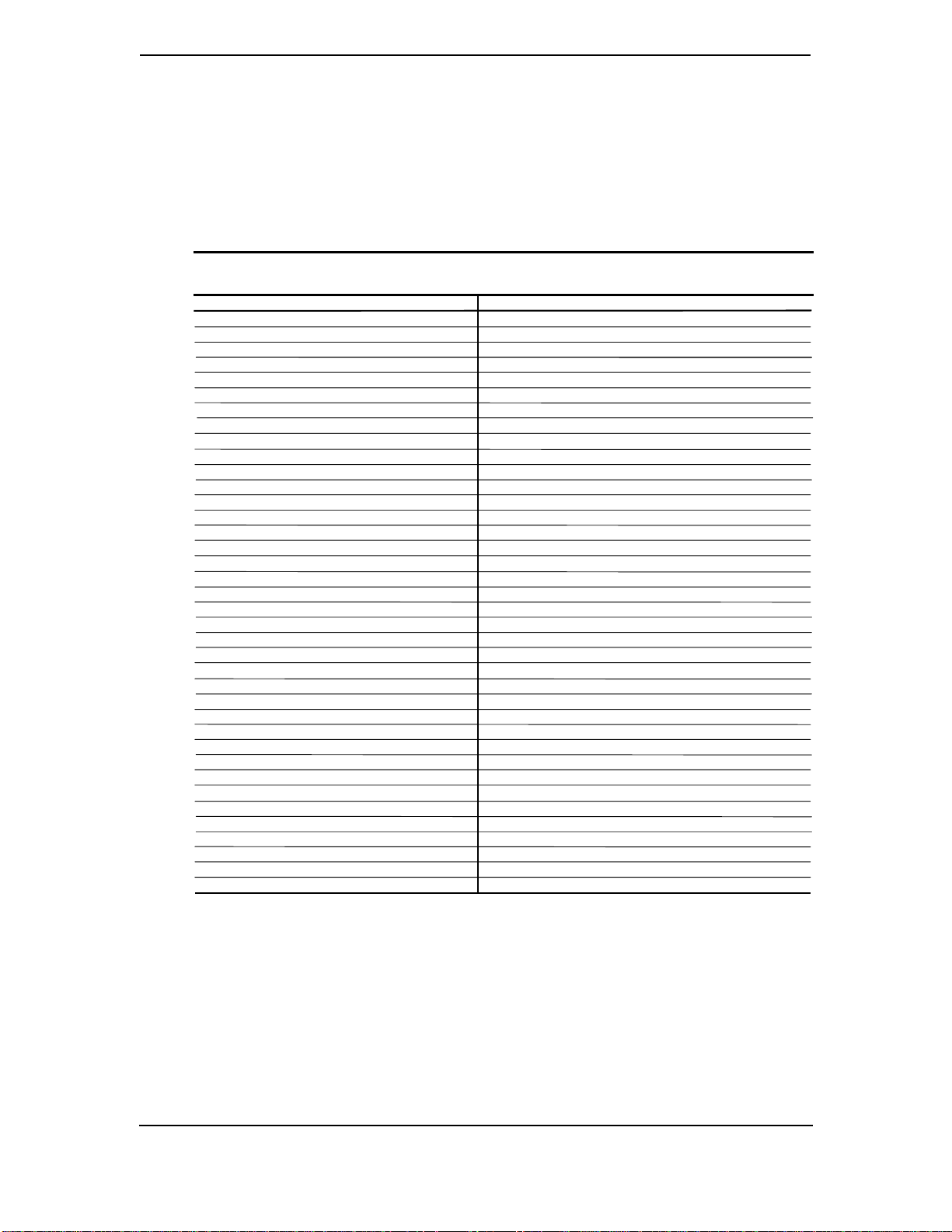

1.3 COMMON ACRONYMS AND ABBREVIATIONS

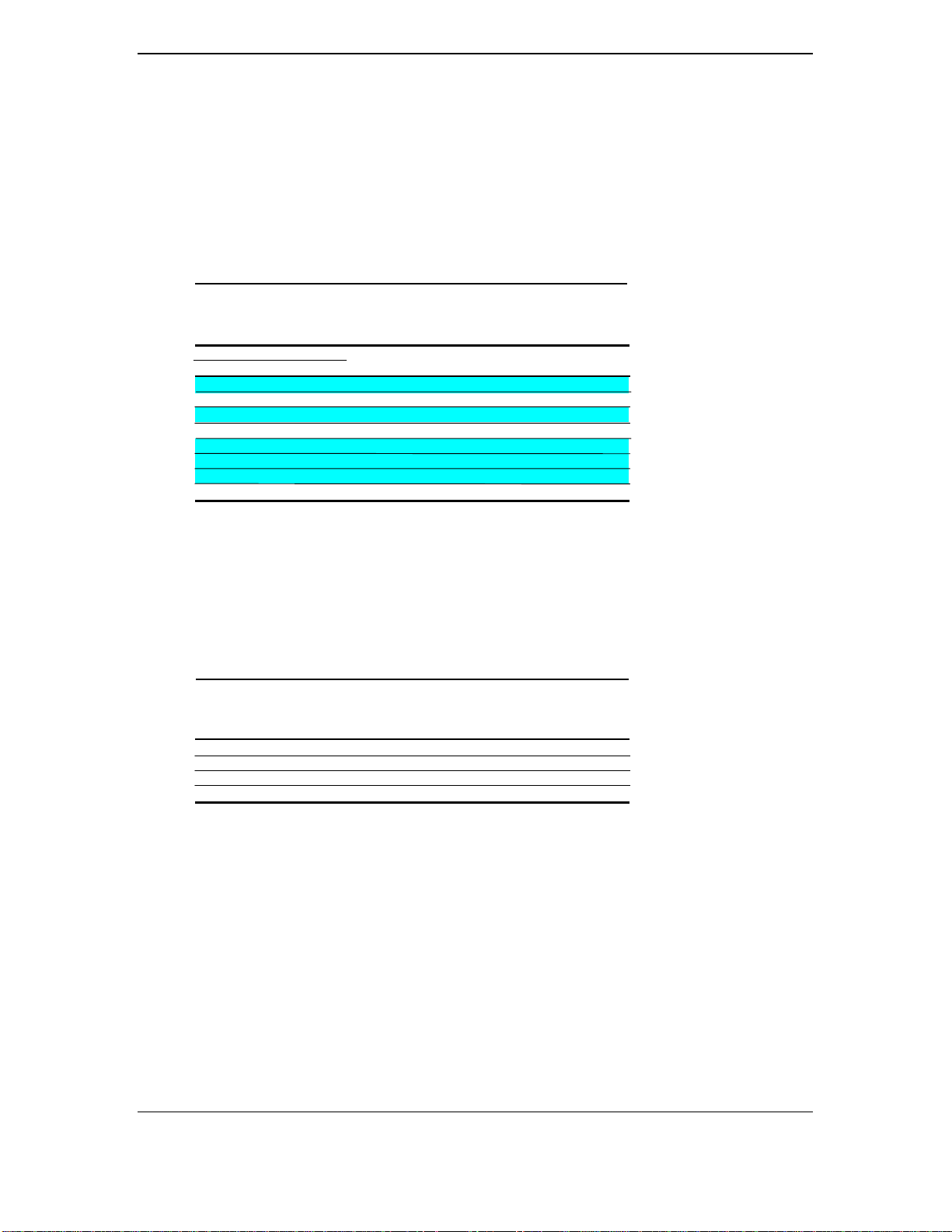

Table 1-1 lists the acronyms and abbreviations used in this guide.

Technical Reference Guide

Table 1–1.

Acronyms and Abbreviations

Table 1-1.

Acronyms and Abbreviations

Acronym/Abbreviation Descriptio n

A ampere

AC alternating current

ACPI Advanced Configuration and Power Interface

A/D analog-to-digital

AGP advanced graphics port

API application programming interface

APM advanced power management

ASIC application-specific integrated circuit

AT 1. attention (commands) 2. 286-based PC architecture

ATA AT attachment (mode)

AVI audio-video interleaved

AVGA Advanced VGA

BCD binary-coded decimal

BIOS basic input/outp ut system

bis second/new revision

BitBLT bit block transfer

BNC Bayonet Neill-Concelman (connector)

bps or b/s bits per second

BSP Bootstrap processor

CAS column address strobe

CD compact disk

CD-ROM compact disk read-only memory

CDS compct disk system

CF carry flag

CGA color graphics adapter

Ch channel

CLUT color look-up table (pallete)

cm centimeter

CMC cache/memory controller

CMOS complimentary metal-oxide semiconductor (configuration memory)

Cntlr controller

codec compressor/decompressor

CPQ Compaq

CPU central processing unit

CRT cathode ray tube

CSM Compaq system management / Compaq server management

DAA direct access arrangement

DAC digital-to-analog converter

db decibel

DC direct current

DCH DOS compatibility hole

DDC Display Data Channel

DF direction flag

Continued

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

1-3

Page 16

Chapter 1 Introduction

Table 1-1. Acronyms and Abbreviations

Acronym/Abbreviation Descriptio n

DIMM dual inline memory module

DIN Deutche IndustriNorm (connector standard)

DIP dual inline package

DMA direct memory access

dpi dots per inch

DRAM dynamic random access memory

DRQ data request

EDID extended display identification data

EDO extended data out (RAM type)

EEPROM electrically eraseable PROM

EGA enhanced graphics adapter

EIA Electronic Industry Association

EISA extended ISA

EPP enhanced parallel port

EIDE enhanced IDE

ESCD Extended System Configuration Data (format)

EV Environmental Variable (data)

ExCA Exchangeable Card Architecture

FIFO first in / first out

FL flag (register)

FM frequency modulation

FPM fast page mode (RAM type)

FPU Floating point unit (numeric or math coprocessor)

ft foot

GB gigabyte

GND ground

GPIO general purpose I/O

GPOC general purpose open-collector

GUI graphics user interface

h hexadecimal

HW hardware

hex hexadecimal

Hz hertz

IDE integrated drive element

IEEE Institute of Electrical and Electronic Engineers

IF interrupt flag

I/F interface

in inch

INT interrupt

I/O input/output

IPL initial program loader

IrDA Infra Red Data Association

IRQ interrupt request

ISA industry standard architecture

JEDEC Joint Electron Device Engineering Council

Kb / KB kilobits / kilobytes (x 1024 bits / x 1024 bytes)

Kb/s kilobits per second

kg kilogram

KHz kilohertz

kv kilovolt

Continued

Continued

1-4

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 17

Technical Reference Guide

Table 1-1. Acronyms and Abbreviations

Acronym/Abbreviation Descriptio n

lb pound

LCD liquid crystal display

LED light-emitting diode

LIF low insertion force (socket)

LSI large scale integration

LSb / LSB least significant bit / least significant byte

LUN logical unit (SCSI)

MMX multimedia extensions

MPEG Motion Picture Experts Group

MOSFET Metal oxide silicon field effect transistor

ms millisecond

MSb / MSB most significant bit / most significant byte

mux multiplex

MVA motion video acceleration

MVW motion video window

n

NIC network interface card/controller

NiCad nickel cadmium

NiMH nickel-metal hydride

NMI non-maskable interrupt

ns nanosecond

NT nested task flag

NTSC National Television Standards Committee

NVRAM non-volatile random access memory

OEM original equipment manufacturer

OS operating system

PAL 1. programmable array logic 2. phase altering line

PC personal computer

PCI peripheral component interconnect

PCM pulse code modulation

PCMCIA Personal Computer Memory Card International Association

PF parity flag

PIN personal identification number

POST power-on self test

PROM programmable read-only memory

PTR pointer

RAM random access memory

RAS row address strobe

rcvr receiver

RF resume flag

RGB red/green/blue

RH Relative humidity

RMS root mean square

ROM read-only memory

RPM revolutions per minute

RTC real time clock

R/W read/write

variable parameter/value

Continued

Continued

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

1-5

Page 18

Chapter 1 Introduction

Table 1-1. Acronyms and Abbreviations

Acronym/Abbreviation Descriptio n

SCSI small co mput er system interface

SDRAM Synchronous Dynamic RAM

SEC Single Edge-Connector

SECAM sequential colour avec memoire (sequential color with memory)

SF sign flag

SGRAM Synchronous Graphics RAM

SIMM single in-line memory module

SIT system inform ation table

SMI system m anagement interrupt

SMM system management mode

SMRAM system m anagement RAM

SPD serial presence detect

SPP standard parallel port

SRAM static RAM

STN super twist pneumatic

SVGA super VGA

SW software

TAD telephone answering device

TAM telephone answering machine

TCP tape carrier package

TF trap flag

TFT thin-film transistor

TIA Telecommunications Information Administration

TPE twisted pair ethernet

TPI track per inch

TTl transistor-transistor logic

TV television

TX transmit

UART universal asynchronous receiver/transmitter

us / µs microsecond

USB Universal Serial Bus

UTP unshielded twisted pair

Vvolt

VESA Video Electronic Standards Association

VGA video graphics adapter

vib vibrato

VLSI very large scale integration

VRAM Video RAM

Wwatt

WRAM Windows RAM

ZF zero flag

ZIF zero insertion force (socket)

Continued

1-6

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 19

Chapter 2

SYSTEM OVERVIEW

Technical Reference Guide

2.

2.1

Chapter 2 SYSTEM O VERVIEW

INTRODUCTION

The Compaq Deskpro 4000N and 4000S Personal Computers are based on Pentium

microprocessors featuring MMX technology and designed with a n emph a si s on speed, storage

capacity, and multimedia compatibility to meet the requirements of the business environment.

These models feature architectures incorporating the PCI and ISA buses. All models are easily

upgradeable and expandable to keep pace with th e n eeds of the office or home.

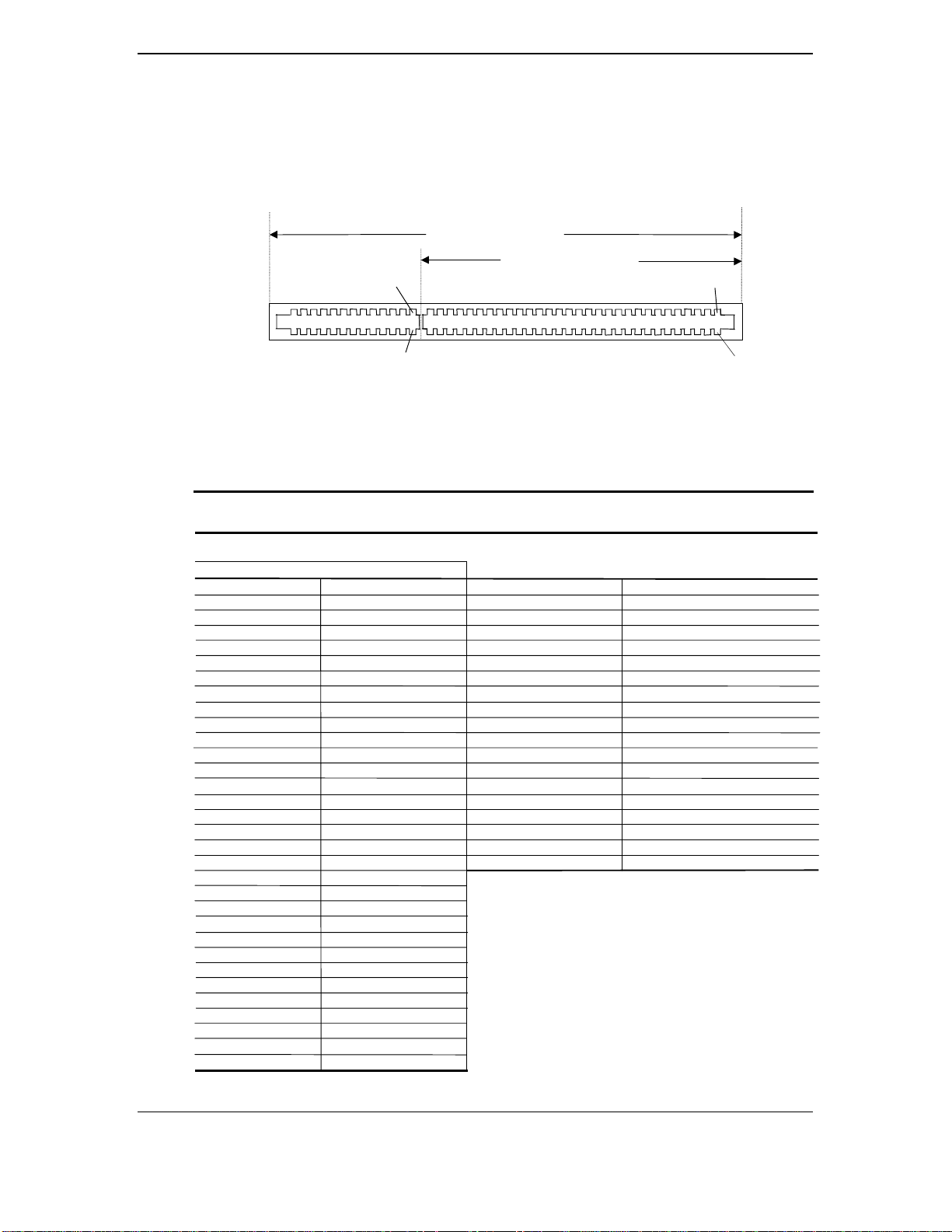

Figure 2–1.

Compaq Deskpro 4000N and 4000S Personal Computers

Compaq Deskpro 4000S Personal Computer with Monitor

First Edition -September

2-1

Page 20

Chapter 2 System Overview

2.2 F EATURES

This section describes the standard and distinguishing features.

2.2.1 STANDARD FEATURES

The following standard features are included on all models:

♦ Pentium micr oprocessor with MMX tech nology

♦ 256-KB second-level cache

♦ 16 or 32 megabytes of SDRAM, with support for ECC and SDP m emory

♦ Integrated S3 Trio64V2/GX graphics controller with 2-MB frame

♦ Enha nced IDE controller support i ng Ultra ATA (UDMA) modes 0-2

♦ Hard drive fault prediction

♦ PCI con nector

♦ Two serial interfaces

♦ Parallel interface

♦ Two universal serial bus ports

♦ Integrated n etwork interface controller (RJ-45/AUI ports)

♦ Compaq Space Saver keyboard w/Windows support

♦ Compaq PS/2-type mouse

♦ APM 1.2 power management suppor t

♦ Plug ’n Play compatible (with ESCD support)

♦ Energy Star compliant

♦ 76-watt, surge-tolerant power supply

The Deskpro 4000N and 4000S support the Intelligent Manageability features listed below:

Configuration

Management

Remote ROM Flash RAM Type Data ECC RAM Fault Prediction Memory Change Alert

Remote Security DMI BIOS SMART II Hard Drive Ownership Tag

Remote Wakeup Asset Tag Monitor Fault Diag. Config. Cntrl. Hardware

Remote Shutdown Sys. Serial # UDMA Integrity Log. Setup Password

Replicated Setup Sys. Manuf./Model Proactive Backup Power-On Password

ACPI-Ready Sys. Board Rev. Level Thermal Sensor QuickLock/QuickBlank

Dual-State Power Sw. ROM rev. Diskette Boot Cntrl.

Failsafe Boot Bloc k ROM Hard Drive Type Data Diskette Write Cntrl.

Asset

Management

Monitor Type Data I/O Port En/Dis. Cntrl.

Compaq Insight Ed itio n Cable Lock Provision

Fault

Management

Security

Management

The Intelligent Manageability features provide support for DMI 2.0, Compaq Insight Manager,

and Management Solutions Partners.

2-2

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 21

2.2.2 MODEL DIFFERENCES

Deskpro 4000N Deskpro 4000S

PCI connector: 1 1 (shared slot)

ISA connector: none 1 (shared slot)

OS installed: Windows NT 4.0 Windows 95

Remot e boot support: Yes No

Diskette drive installed: No Yes

Hard drive size: 1.6 or 2.1 GB 2.1 GB

CD-ROM support: No Yes

2.2.3 OPTIONS

Options that are specific to the Compaq Deskpro 4000N and 4000S Series Personal Computers

include:

♦ System Memory: 8 -MB DIMM

16-MB DIMM

32-MB DIMM

64-MB DIMM

128-MB DIMM

Technical Reference Guide

Compaq Deskpro Computers are easily upgraded and enhanced with peripher a l devices designed

to meet PCI and ISA standards. The Compaq Deskpro Personal Computers are compatible with

peripherals design for Plug ’n Play operation.

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition -September

2-3

Page 22

Chapter 2 System Overview

2.3 MECHANICAL DESIGN

This section illustrates the layout used by the formfactor. In addition, this section includes the

layout of the system board.

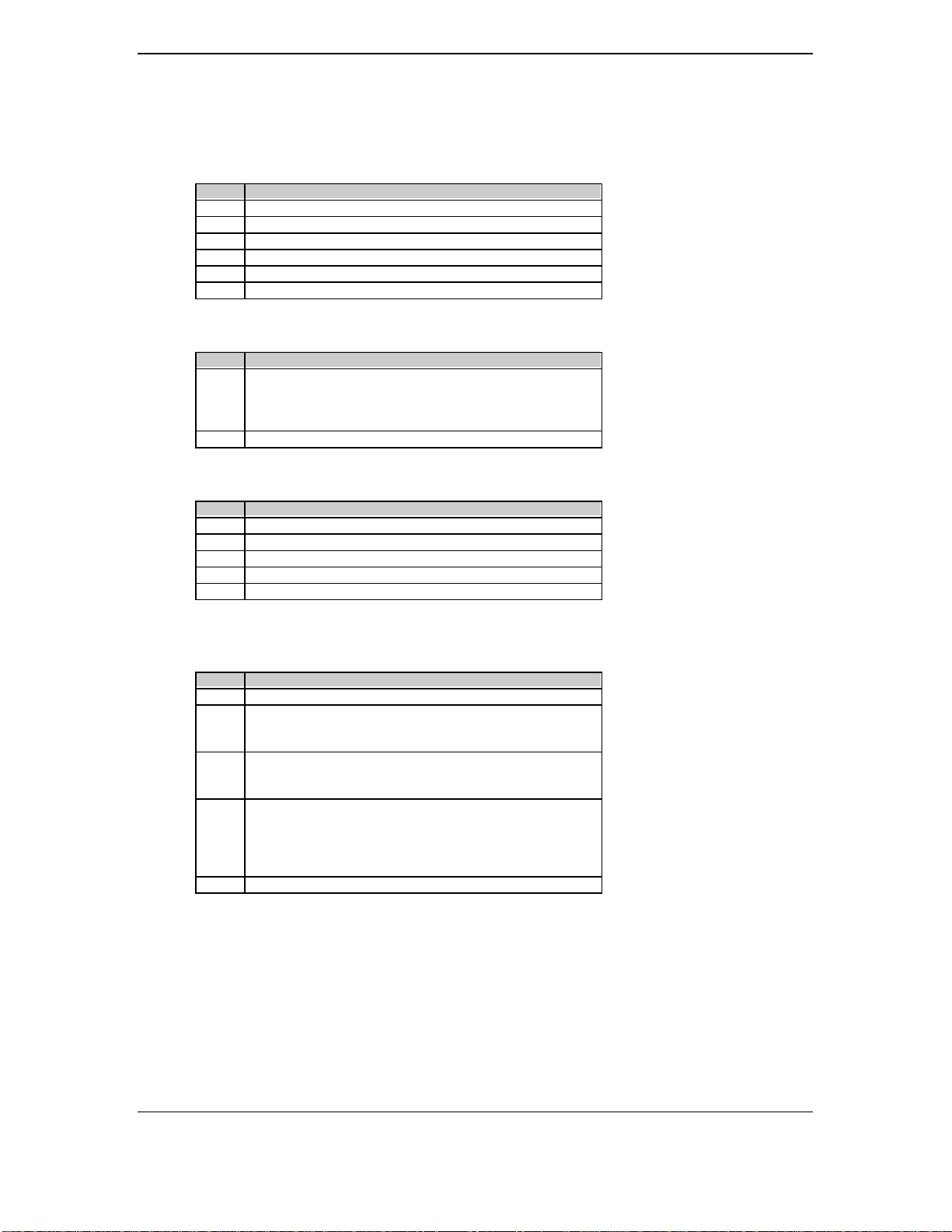

2.3.1 CABINET LAYOUT

NOTES:

[1] Deskpro 4000S only

[2] Front panel access on 4000S only.

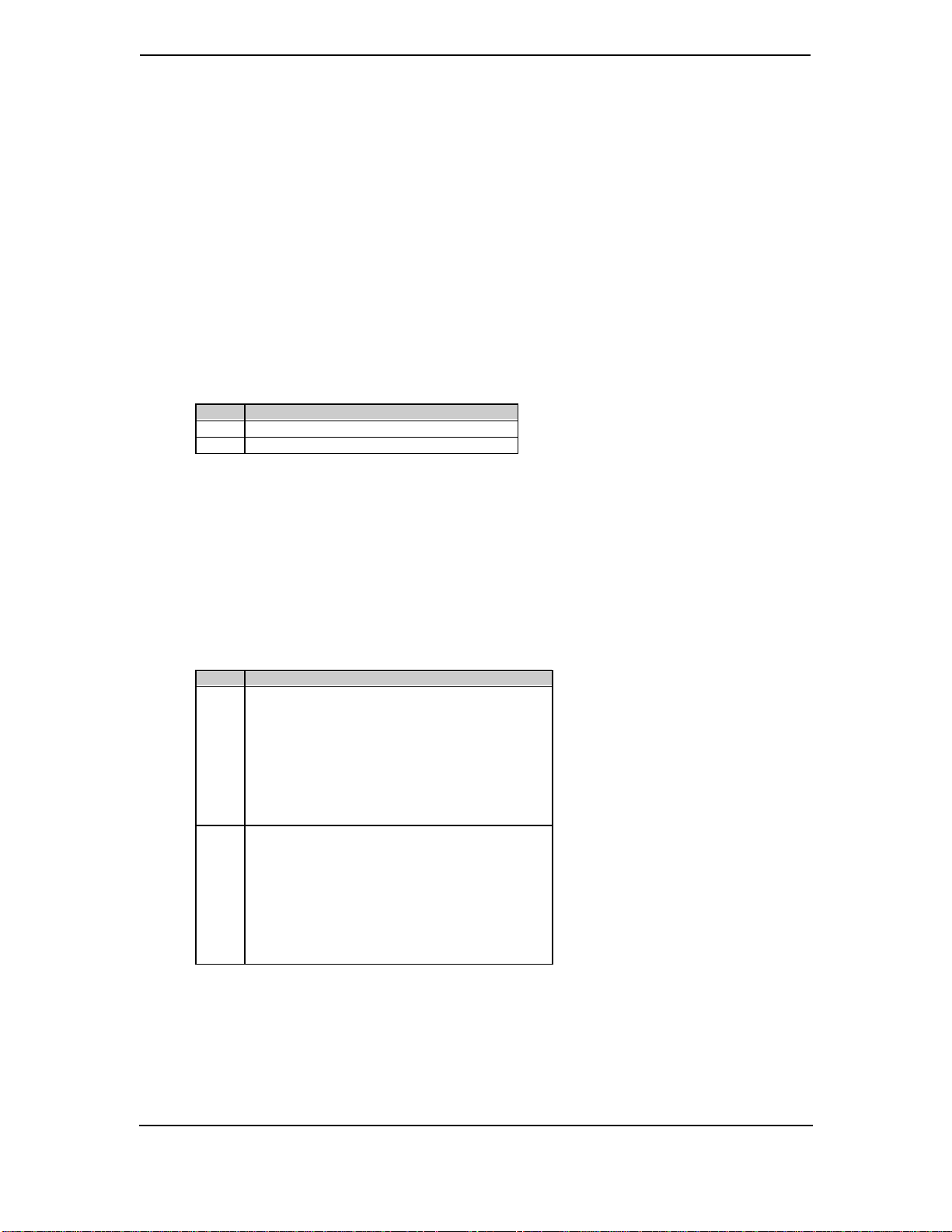

Figure 2–2.

Item Function

1 Power Switch

2 Power-On Light

3 Hard Drive Activity Light

4 1.44 MB Diskette Drive (3.5” Drive) [1]

5 1/3 Height Drive Bay (3.5” or 5.25” Drive) [2]

6 1/3 Height Drive Bay (3.5” or 5.25” Drive)

Cabinet Layout, Front View

4 5 6

1

2

3

2-4

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 23

Technical Reference Guide

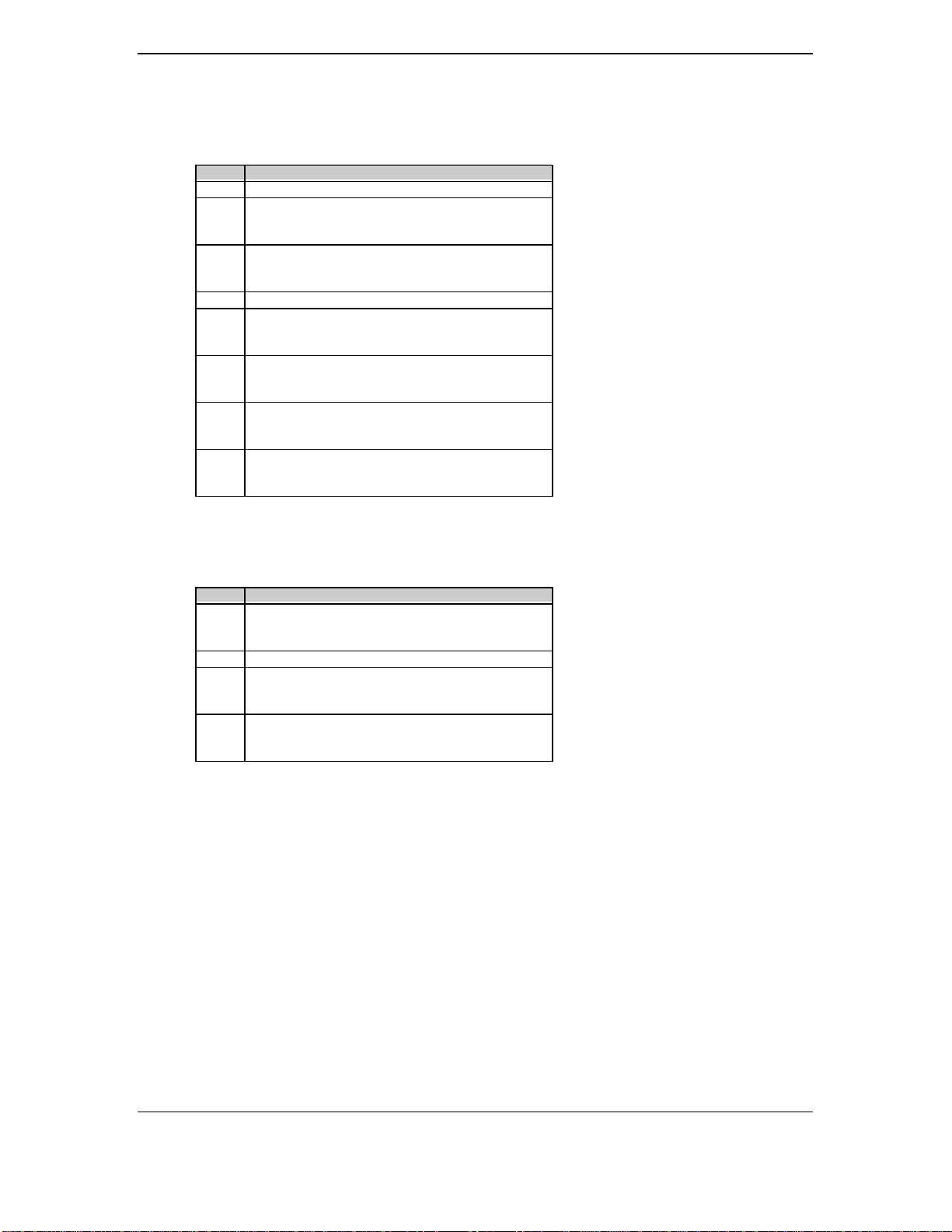

2 4 6 101112

1 3

Item Function

1 AC Line In Connector

2 Line Voltage Select Switch

3 Universal Serial Bus Interface port 1

4 Universal Serial Bus Interface port 2

5 Parallel Interface Connector

6 Serial Interface Connector B

7 Serial Interface Connector A

8 Network Interface AUI Connector

9 Network Interface RJ-45 Connector

10 Mouse Connector

11 Keyboard Connector

12 Monitor Interface

7

8

95

Figure 2–3. Cabinet Layout, Rear View

Compaq Deskpro 4000N and 4000S Personal Computers

2-5

First Edition -September

Page 24

Chapter 2 System Overview

]

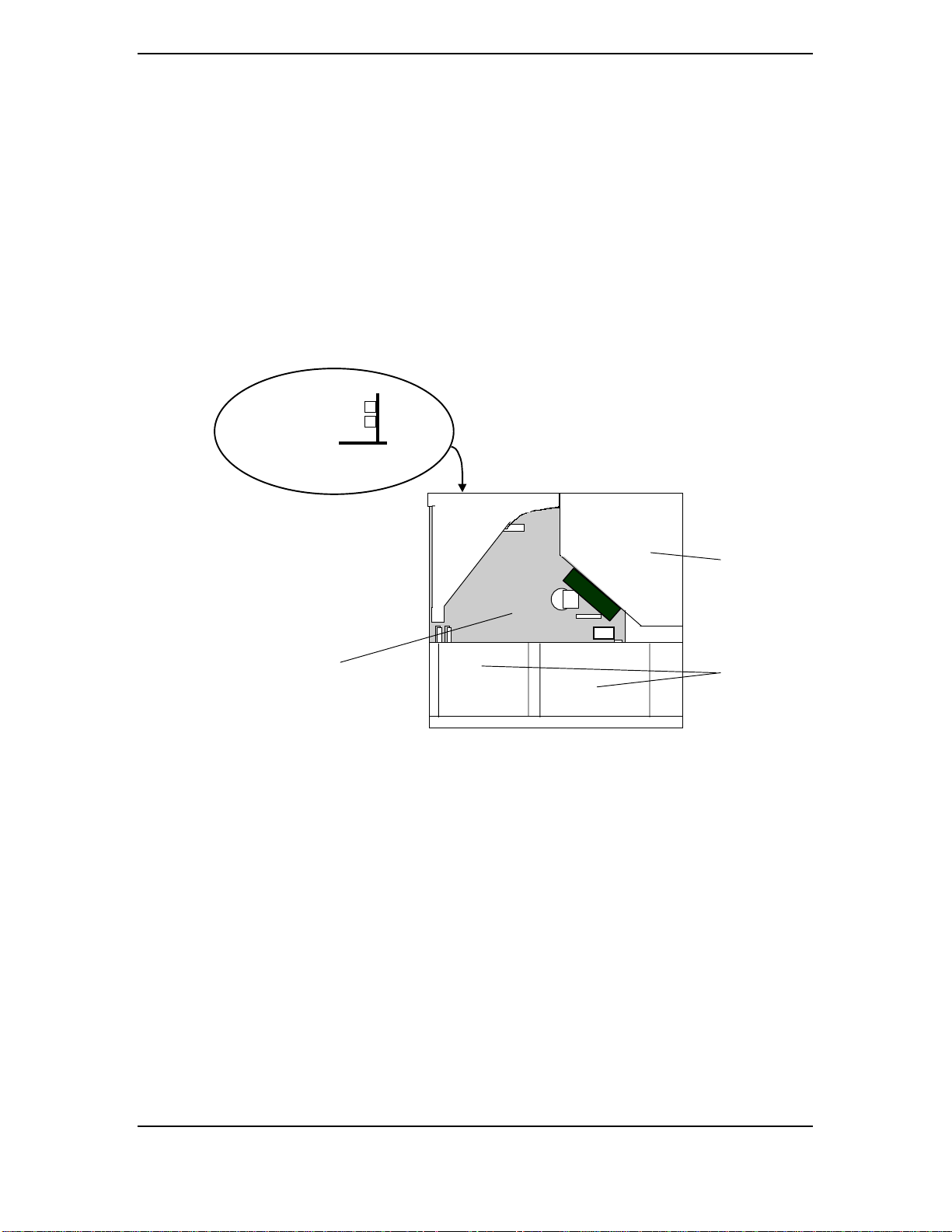

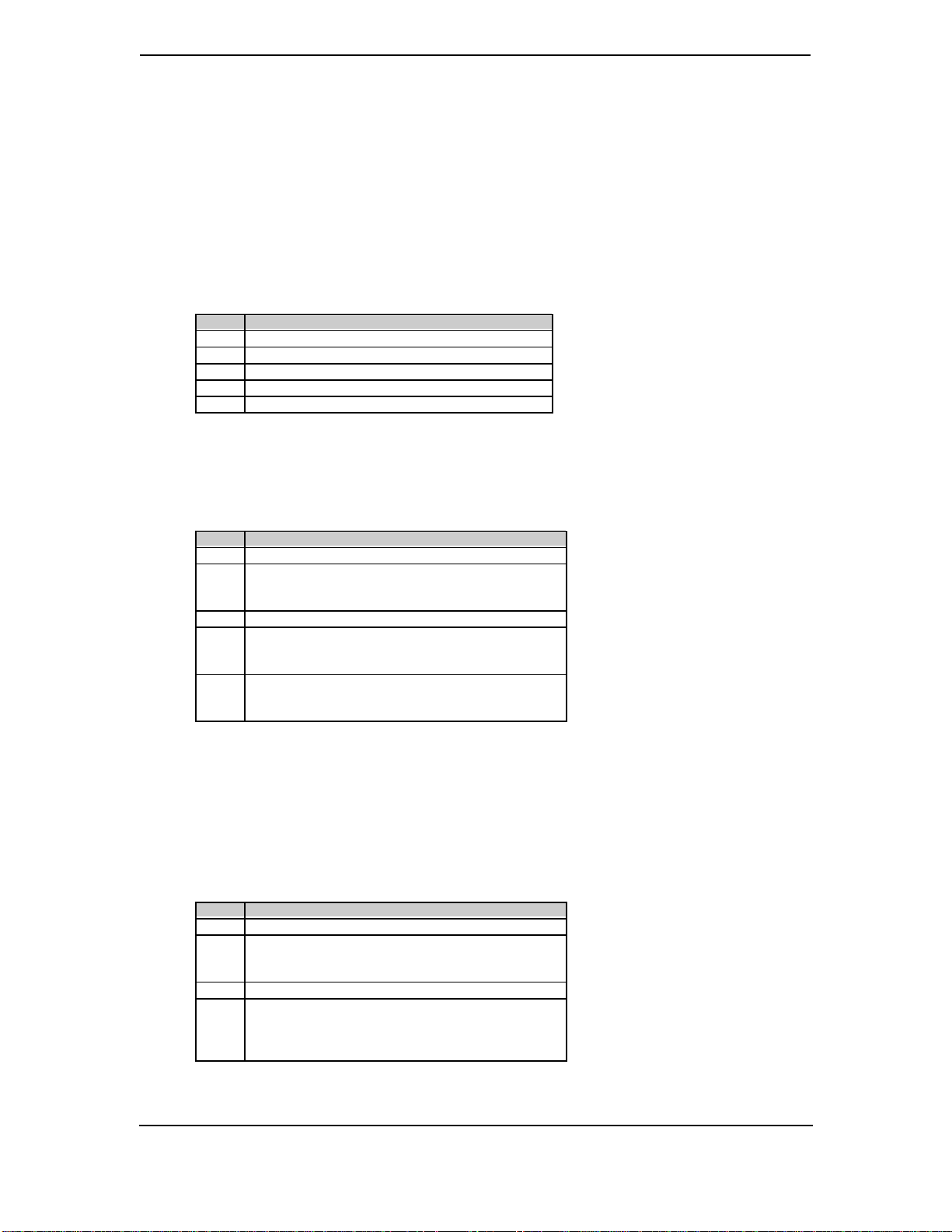

2.3.2 CHASSIS LAYOUT

ISA Combo Slot 1 [1

PCI Combo Slot 1

Slots On Riser Card,

Rear View

Back

System Board

NOTES:

[1] Deskpro 4000S only

Figure 2–4.

Power Supply

Drive Bays

Front

Chassi s La yout, Top Vi ew

2-6

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 25

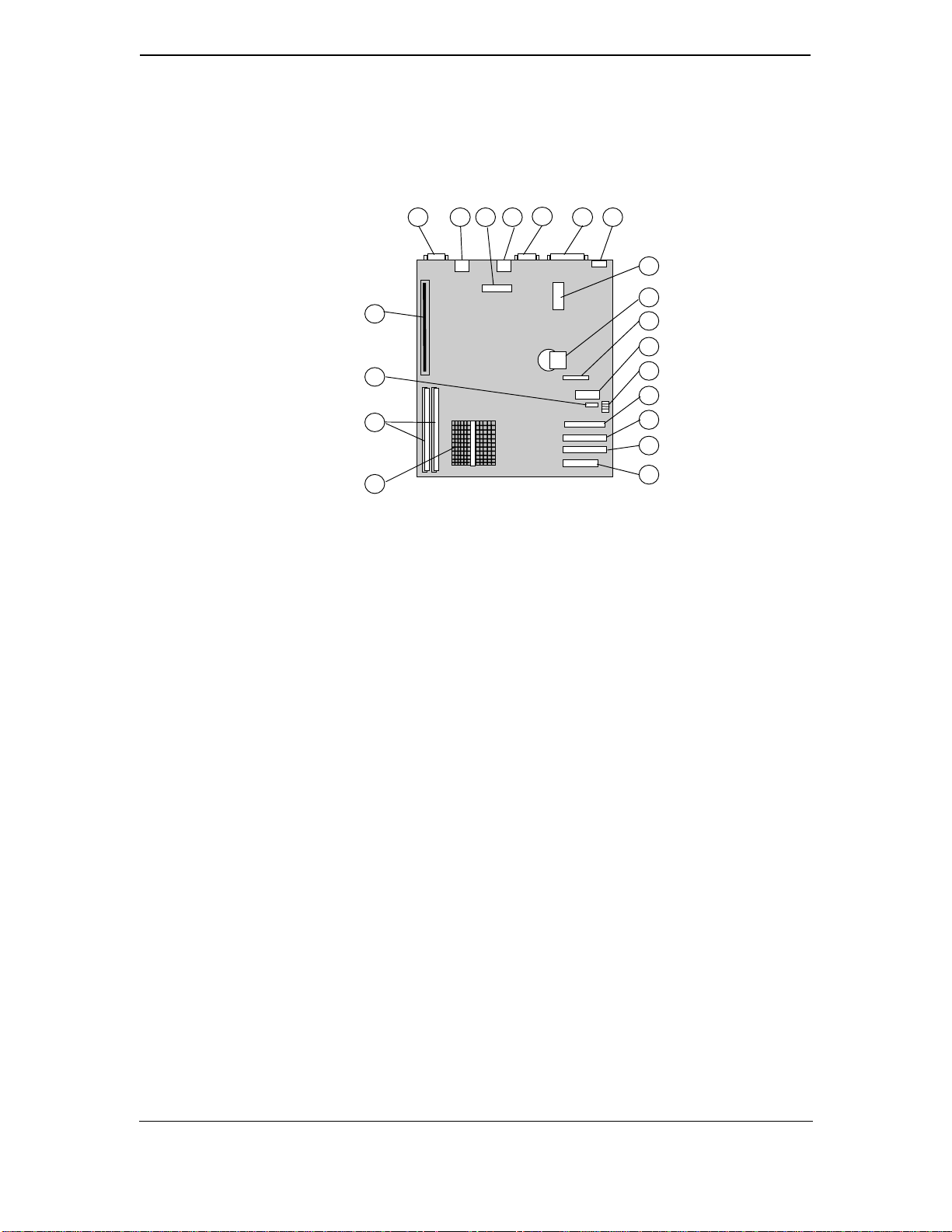

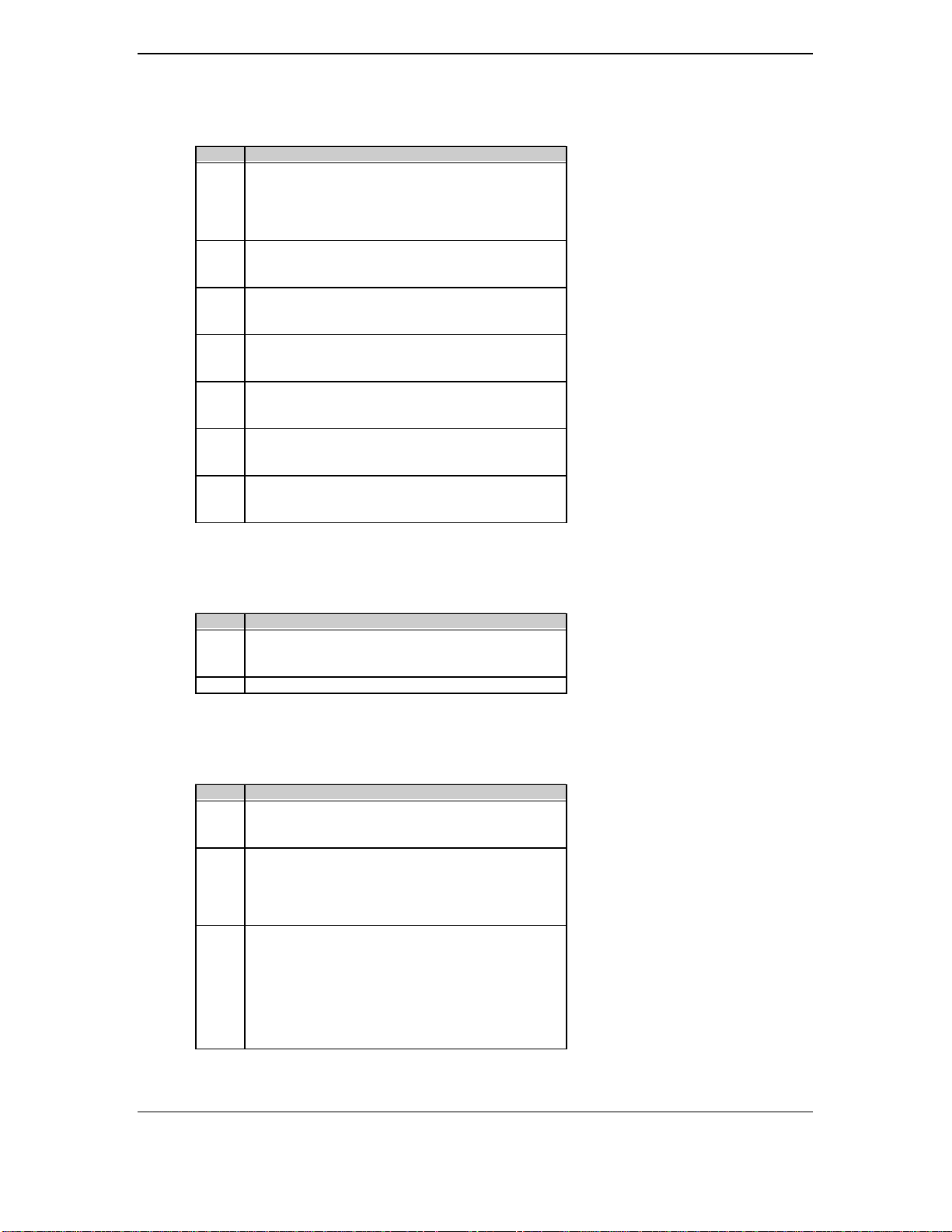

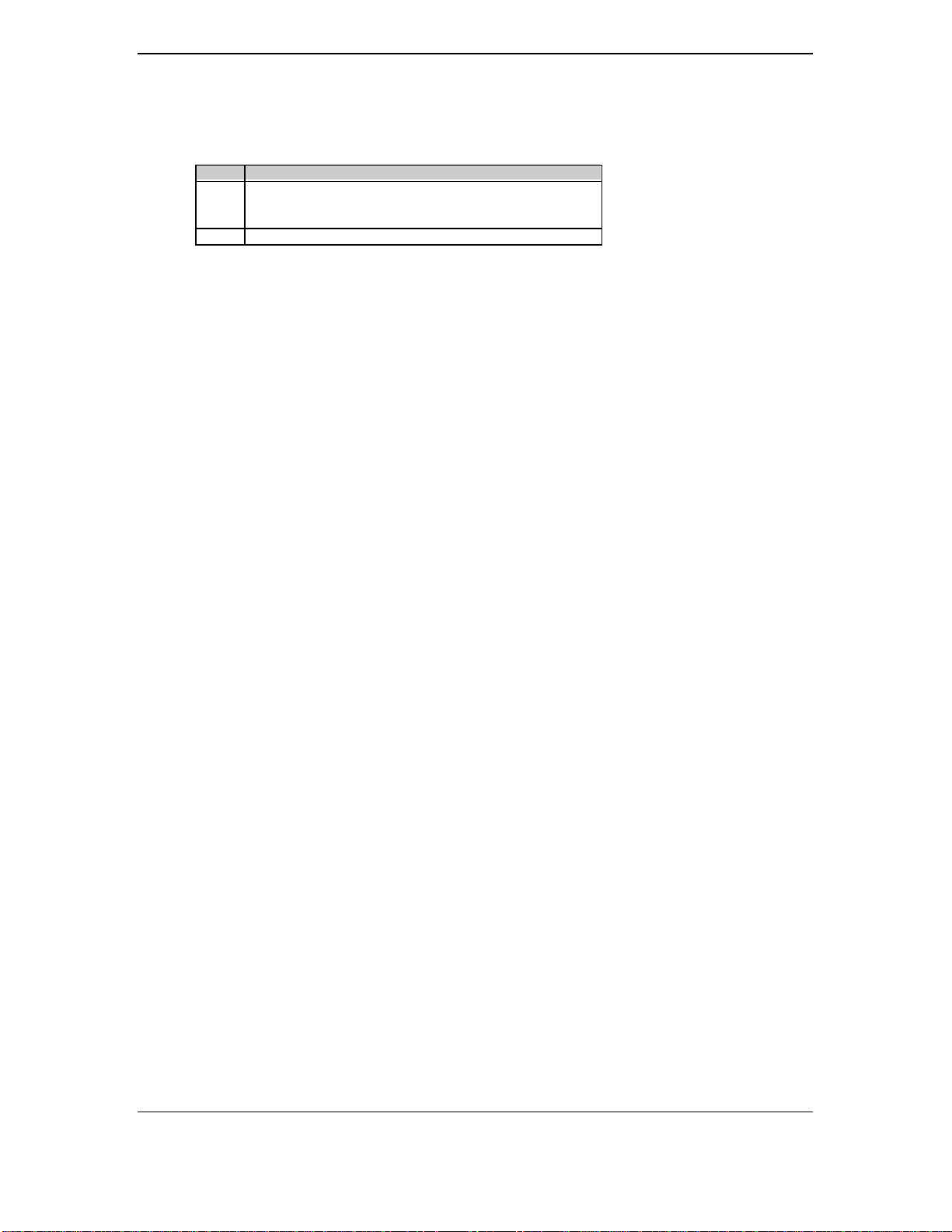

2.3.3 SYSTEM BOARD LAYOUT

1 3

20

19

18

Technical Reference Guide

2

4

6 7

5

8

9

10

11

12

13

14

15

17

16

System Board

p/n 006582-xxx (4000S)

or

p/n 007602-xxx (4000N)

Item Function

1 Graphics monitor connector (J2)

2 Top, Mouse interface connector; Bottom, keyboard connector (J9)

3 NIC AUI connector header (P15)

4 NIC RJ-45 connector (J5)

5 Serial interface connector (P24)

6 Parallel interface connector (J3)

7 Universal serial bus connectors (J6)

8 Power supply connector (P17)

9 RTC/CMOS Battery

10 RTC/CMOS battery replacement header (P14)

11 Power switch, PWR/HD LED cable connector (P16)

12 Processing frequency configuration switch (SW1)

13 CD-ROM connector (P25)

14 Secondary IDE connector (P21)

15 Primary IDE connector (P20)

16 Diskette drive connector (J1)

17 Microprocessor (in type 7 socket)

18 DIMM sockets (J7, J8)

19 CD-ROM drive connector P25 audio out (J11)

20 Riser card connector (J4)

Figure 2–5.

System Board Layout, Component Side

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition -September

2-7

Page 26

Chapter 2 System Overview

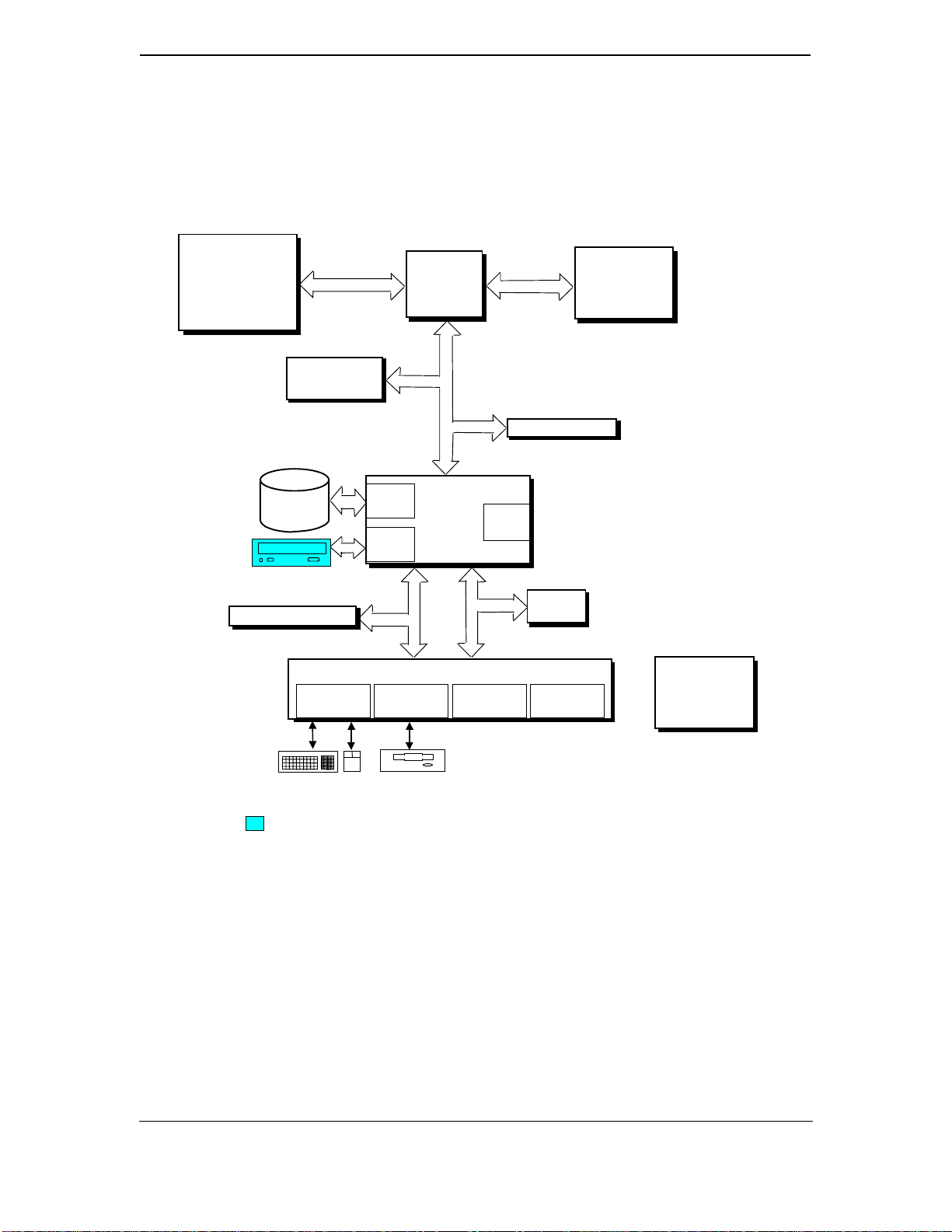

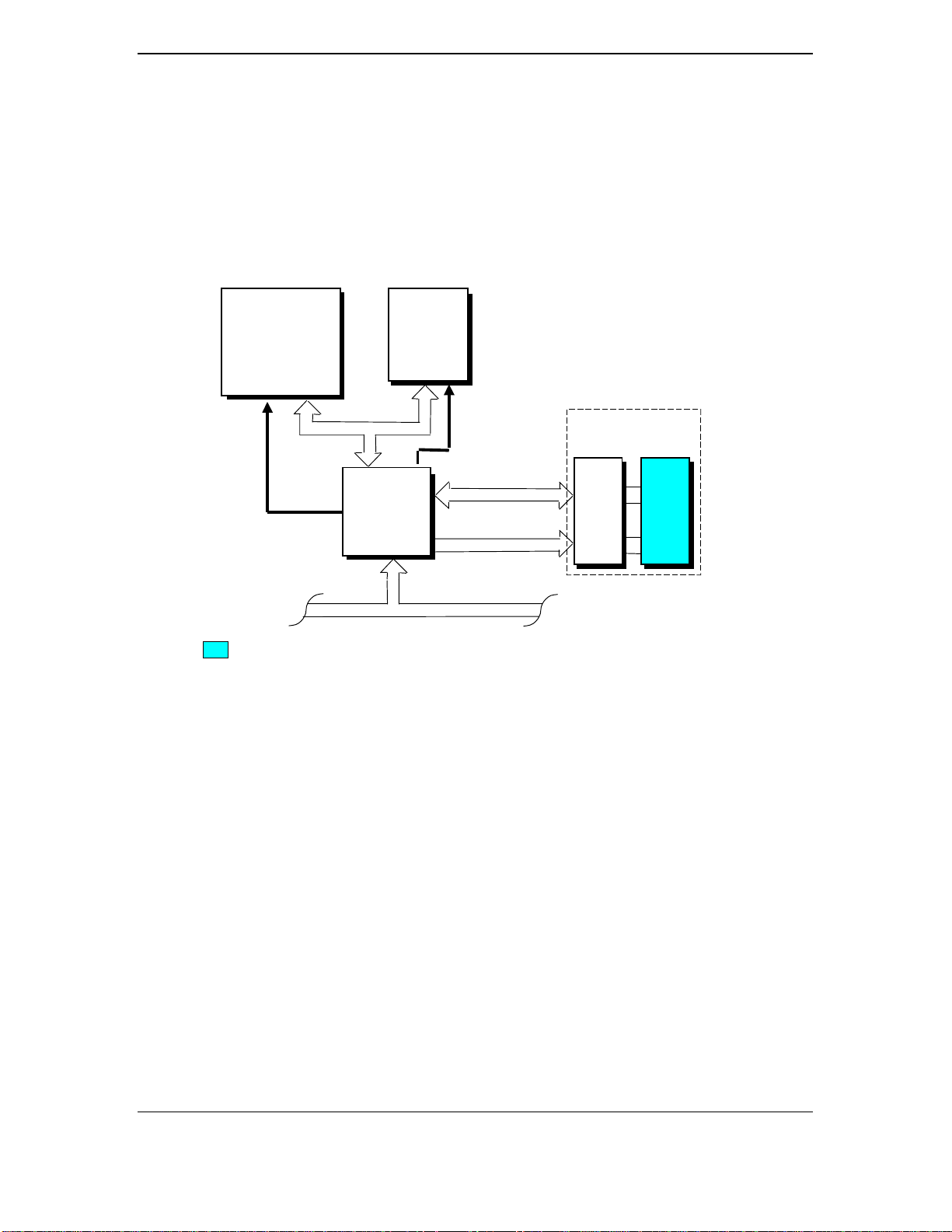

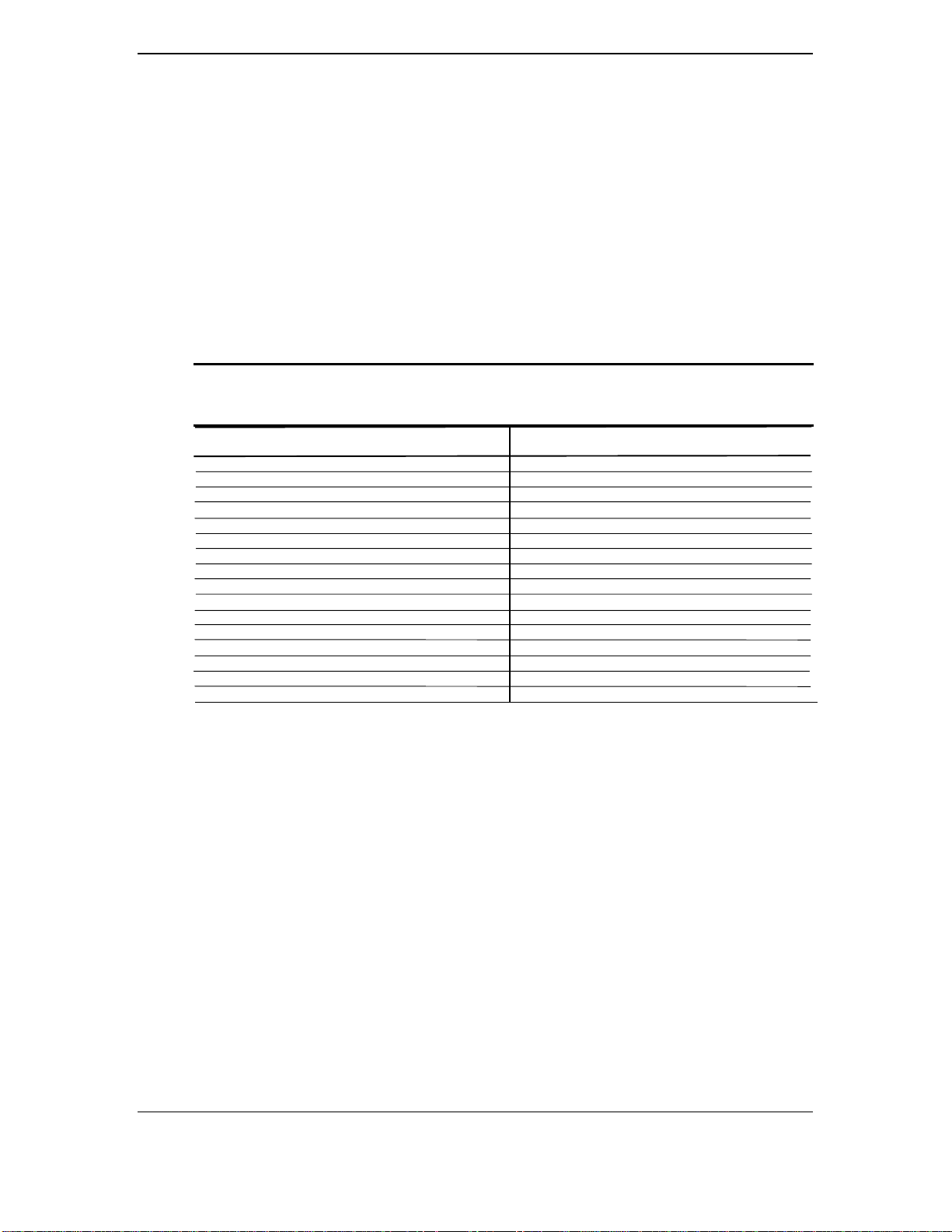

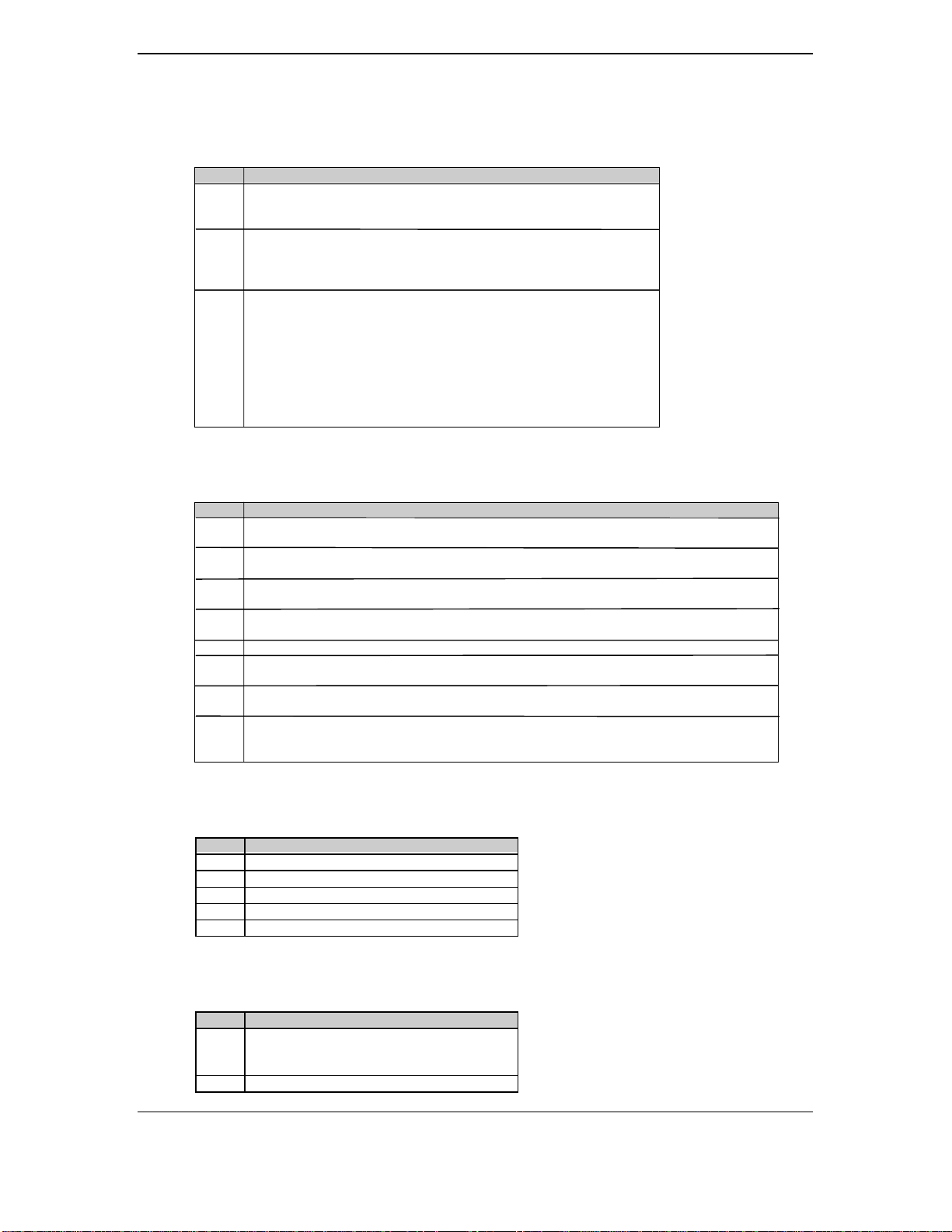

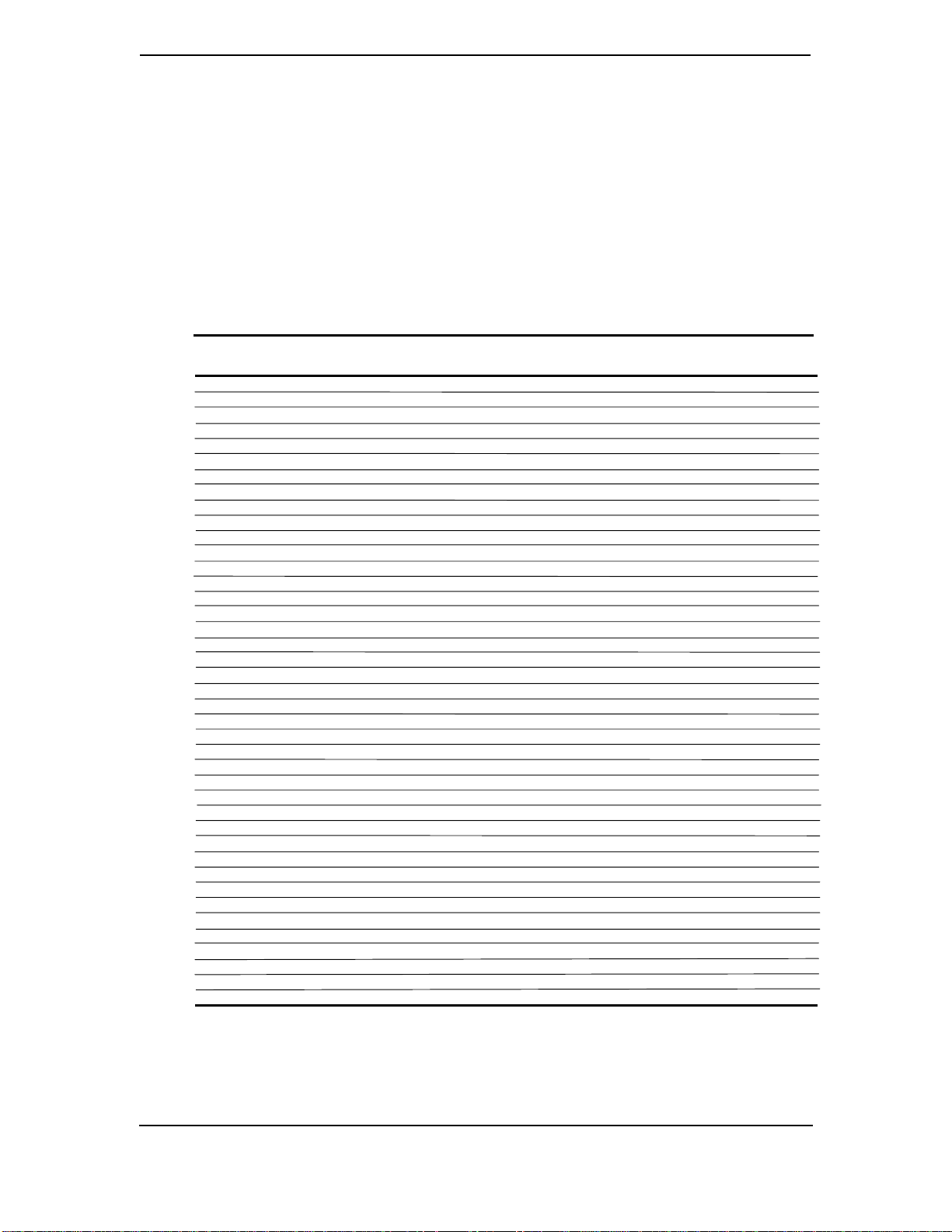

2.4 SYSTEM ARCHITECTURE

The Compaq Deskpro 4000N and 4000S Personal Computers featur ing MMX technology are

based on a Pent i u m MXX micropr ocessor matched with a support chipset that is complimentary

in design. Both th e “N” and “S” systems share the same basic architecture (Figure 2-7), which

utilizes three main buses: the Host bus, the Peripheral Component Interconnect (PCI) bus, and

the Industry Standard Architecture (ISA) bus.

The Host bus provides high performance support for CPU, cache and system memory accesses,

and on these systems is set to operate at 66 MHz. The 32-bit PCI bus provides support for the

graphics subsystem, the EIDE controllers, and expansion devices designed for high performance.

The PCI bus operates at 33 MHz. The ISA bus provides a standard 8-MHz interface for the

input/output (I/O) devices such as the keyboard, diskette drive, serial and parallel interfaces, as

well as the addition of 16- or 8-bit expansion devices.

The CPU/PCI and PCI/ISA bridge functions are handled by the specific support chipset matched

with the microprocessor employed. The support chipset also provides memory controller and data

buffering functions as well as bus control and arbitration functions.

The I/O port functions and diskette dri ve controller ar e in t egra t ed in t o th e PC87307 I/O

Controller. This component also includes the real time clock and battery-backed configuration

memory (CMOS).

Table 2-1 lists the archit ectural highlights.

Table 2–1.

Architectural Comparison

Table 2-1

.

Architectur al Overview

Microprocessor Pentium MMX

Support Chipset VIA VP2

System Memory

Standard installed:

Expandable to:

Cache Memory

L1:

L2:

Graphics Subsystem S3 TrioV2-based

NOTES:

[1] Depending on model

[2] Integrated with the microprocessor

Type

16/32 MB [1]

256 MB

32 KB [2]

256 KB

integrated on board

The following subsections provide a description of the key functions and subsystems.

2-8

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 27

Technical Reference Guide

(2)

]

Microprocessor

and Cache Memory

Hard Drive

CD-ROM

ISA Connector [1

64-Bit Host Bus

Graphics

Subsystem

EIDE

Keyboard/

Mouse I/F

North

Bridge

Pri.

IDE I/F

Sec.

IDE I/F

8-/16-Bit

ISA Bus

PC 87307 I/O Controller

South

Bridge

Diskette

I/F

32-Bit

PCI Bus 0

USB

I/F (2)

X-Bus

Serial

I/F

Mem. Bus

PCI Connector

System

Memory

BIOS

ROM

Parallel

I/F

EIDE

Hard Drive

Power

Supply

NOTES:

CD models only.

[1] Deskpro 4000S only.

Figure 2–6. Compaq Deskpro 4000N and 4000S System Architecture, Block diagram

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition -September

2-9

Page 28

Chapter 2 System Overview

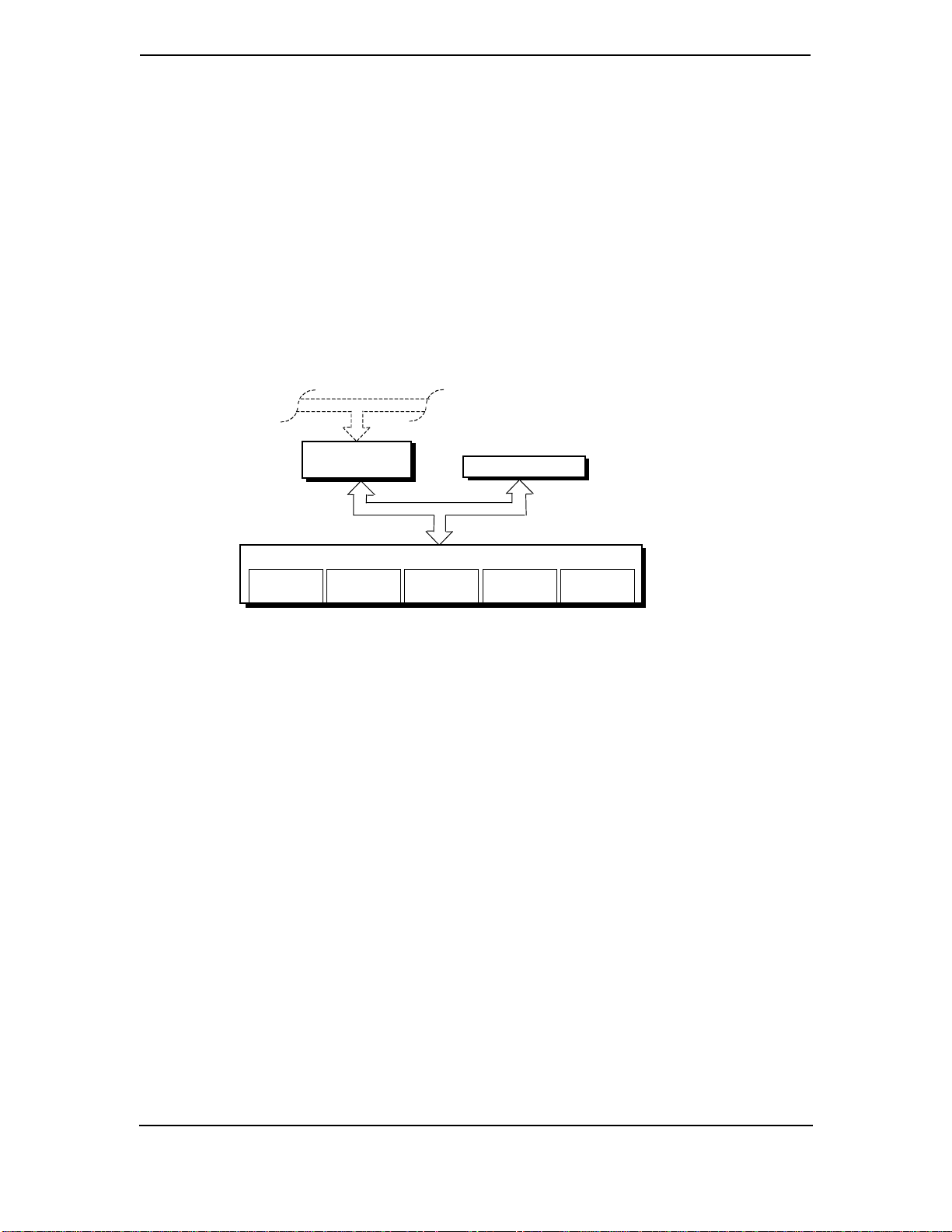

2.4.1 MICROPROCESSOR

The Compaq Deskpro 4000N and 4000S Personal Computers feature the Pentium MMX

microprocessor that is backward-compatible with software written for x86-type processors. The

Pentium MMX microprocessor inclu des a 3 2 KB L1 cache and ext ensions t o the inst ruction set

that pr ovide higher per forman ce for processing graphics and video code. The microprocessor is

mounted in a ZIF type-7 socket that allows replacing and/or upgrading.

Pentium MMX Microprocessor

Figure 2–7.

2.4.2 MEMORY

This system includes 256 kilobytes of SRAM for secondary (L2) cache support of the

microprocessor’s primary (L1) cache. The L2 cache is arranged as direct-mapped, write-through

using synchronous pi p elined bur st SRAMs.

For system memory two 168-pin DIMM sockets are provided with 16 or 32 megabytes of unbuffered SDRAM installed depending on model. System memory can be expanded up to 256

megabytes using 8-, 16-, 32-,64-, and 128-MB DIMMs. Both EDO and SDRAM DIMMs are

supported (SDRAM DIMMs are recommended). T he system supports the use of ECC memory as

well.

Dual-ALU

CPU w/MMX

Branch

Prediction

(Mounted in Type 7 Connector)

32-KB

Cache

Dual Pipeline

Math Coproc.

Micr oprocessor A rchitectu ral Diag ram

The system ROM utilizes a flash ROM component that contains the BIOS and stores PCI, ESCD,

and EV data. The BIOS is updateable by remote or local flashing of the ROM, which includes

boot bloc k ROM support .

2-10

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 29

2.4.3 SUPPORT CHIPSET

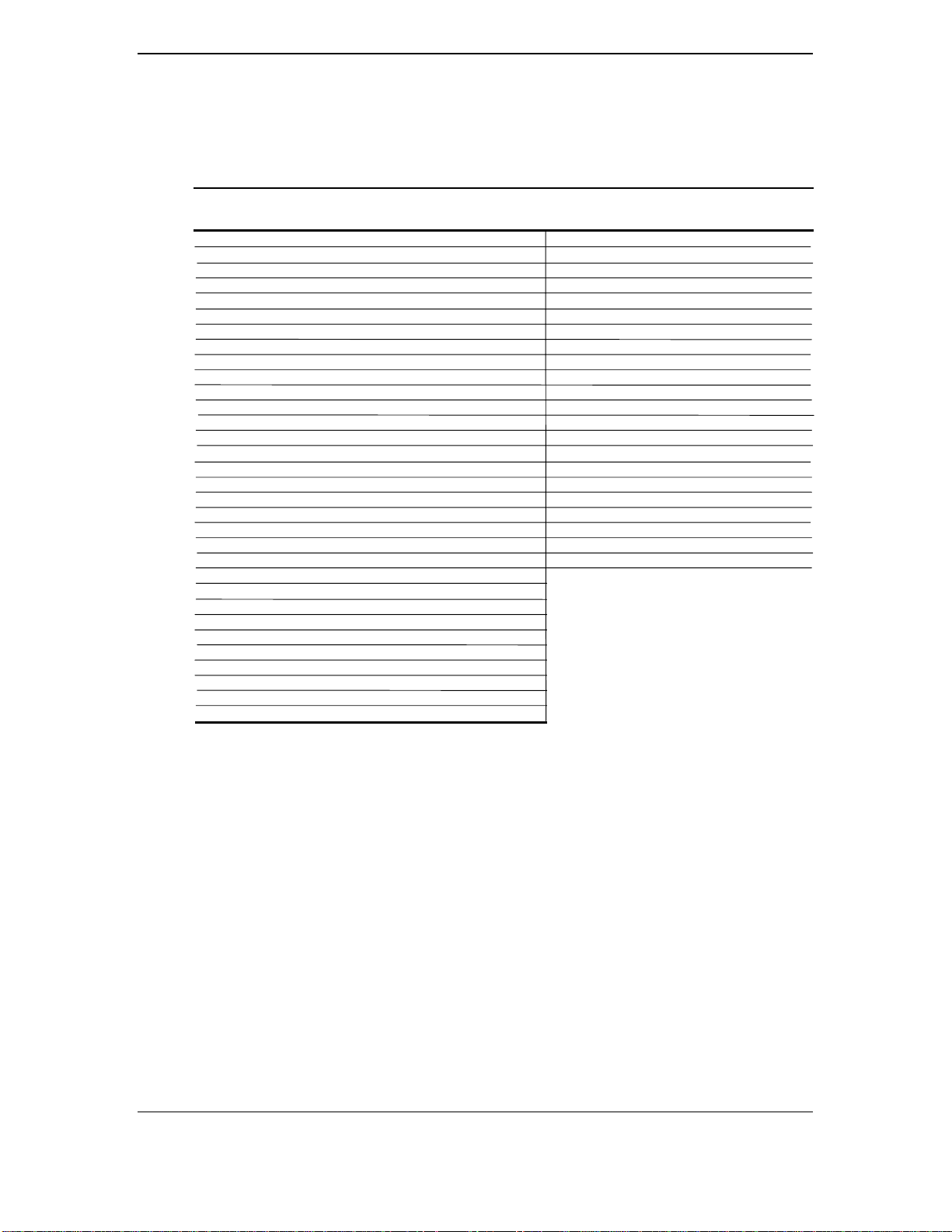

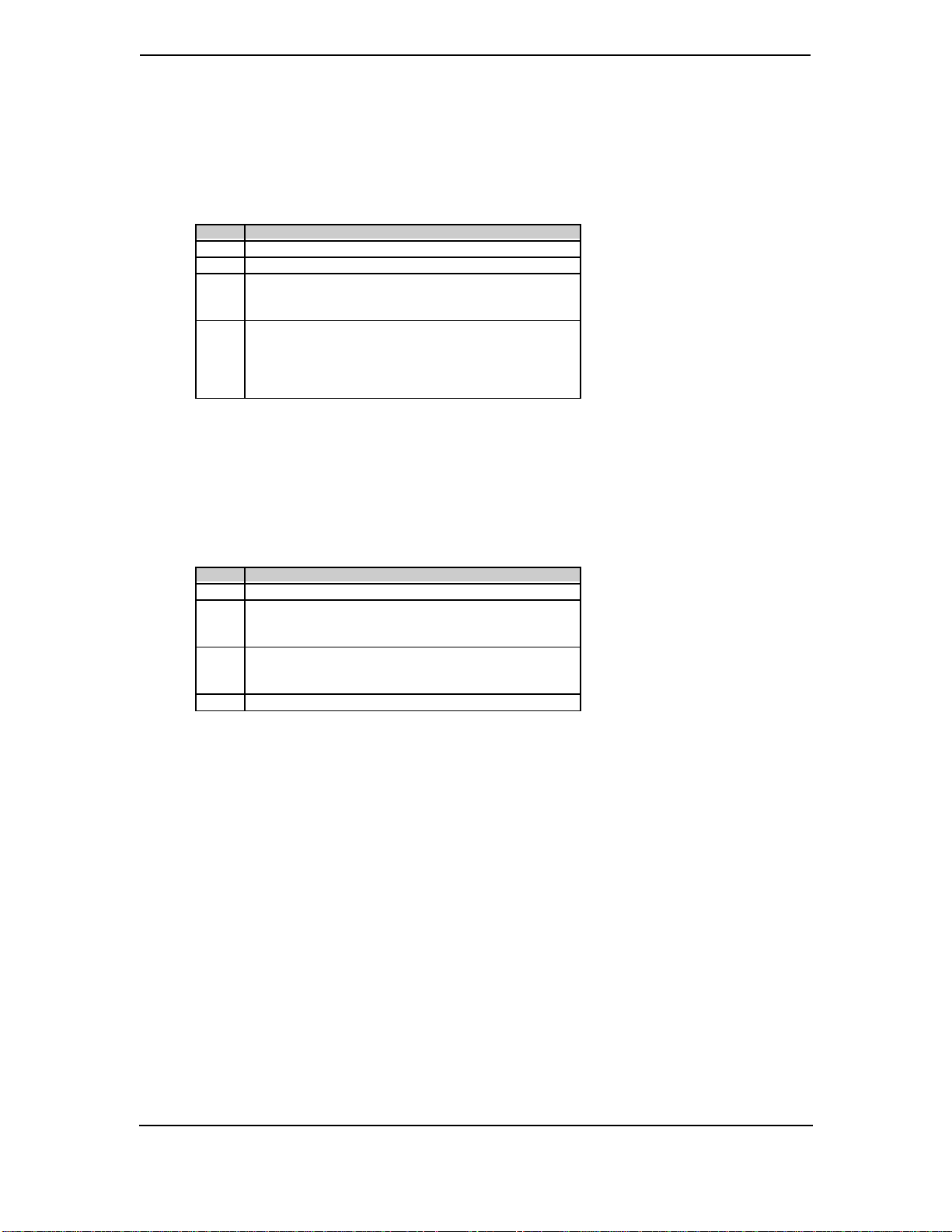

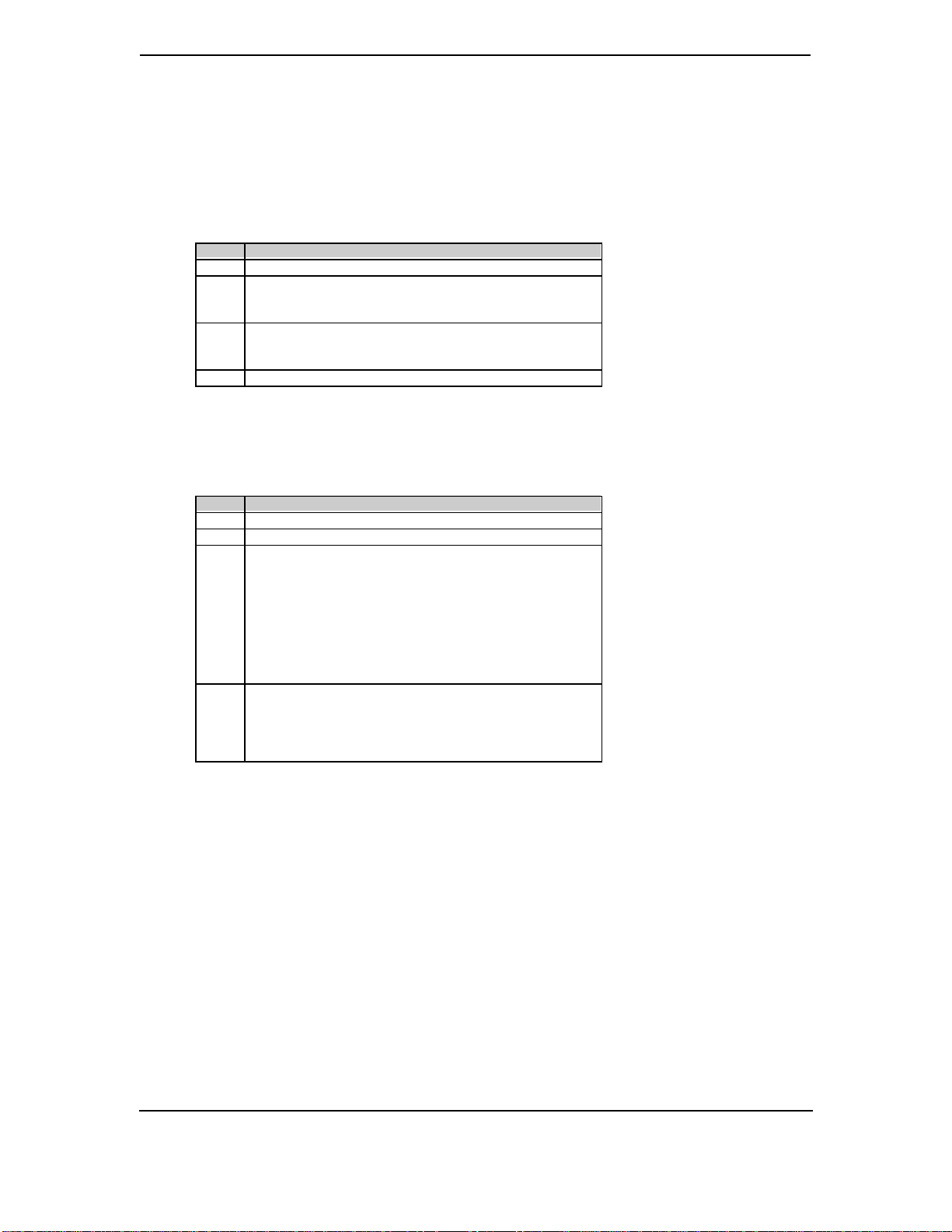

Table 2-2 shows the chipsets used for the Deskpro 4000N and 4000S systems.

Technical Reference Guide

Table 2–2.

Function Component

Host/PCI (North) Bridge:

System Controller

Data Buffer

PCI/ISA (South) Bridge:

EIDE Controller

DMA Controller

Interrupt Controller

Timer/Counter

NMI Registers

Reset Control Reg.

USB I/F

I/O Controller:

Keyboard I/F

Diskette I/F

Serial I/F

Parallel I/F

RTC/CMOS Mem.

GPIO Ports

Support Chipsets

2.4.4 MASS STORAGE

Table 2-2.

Support Chipsets

VT82C595

“

“

VT82C586

“

“

“

“

“

“

“

87307

“

“

“

“

“

“

A 1.6- or 2.1-GB EIDE hard drive may be installed, depending on series/model. All models

include a PCI bus mastering Enhanced IDE (EIDE) controller that provides two EIDE interfaces

supporting two IDE devices. Master/slave drive selection is determin ed usin g t he cable-select

method, eliminating the need to move jumpers when re-configuring drives. The mass storage

drive bay capacity is determined by the form factor (refer to Section 2.3, Mechanical Design). All

Deskpro 4000S models include a 3.5 inch 1.44-MB diskette drive installed.

2.4.5 SERIAL AND PARALLEL INTERFACES

All models include two serial and one parallel port available at the rear of the unit chassis. The

serial and parallel ports are integrated into a PC87307 I/O Controller component. The serial

ports use 16550/16450-equivalent logic and are RS-232-C compatible and operate at baud rates

up to 115,200. The parallel interface is Enhanced Parallel Port (EPP1.9) and Enhanced

Capability Port (ECP) compatible, and supports bi-directional data transfers.

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition -September

2-11

Page 30

Chapter 2 System Overview

2.4.6 UNIVERSAL SERIAL BUS INTERFACE

Two Universal Serial Bus (USB) ports are included, each providing a high speed interface for

future systems and/or peripherals. The USB interface operates at 12 Mbps and provides hot

plugging/unplugging (Plug ’n Play) functionality.

2.4.7 GRAPHICS SUBSYSTEM

The graphics subsystem is integrated on the system board and operates off the PCI bus. The

subsystem is based on the S3 Trio64 V2/GX controller and includes two megabytes of SGRAM.

The subsystem provides a maximum resolution of 1280 x 1024 with 256 colors.

NOTE:

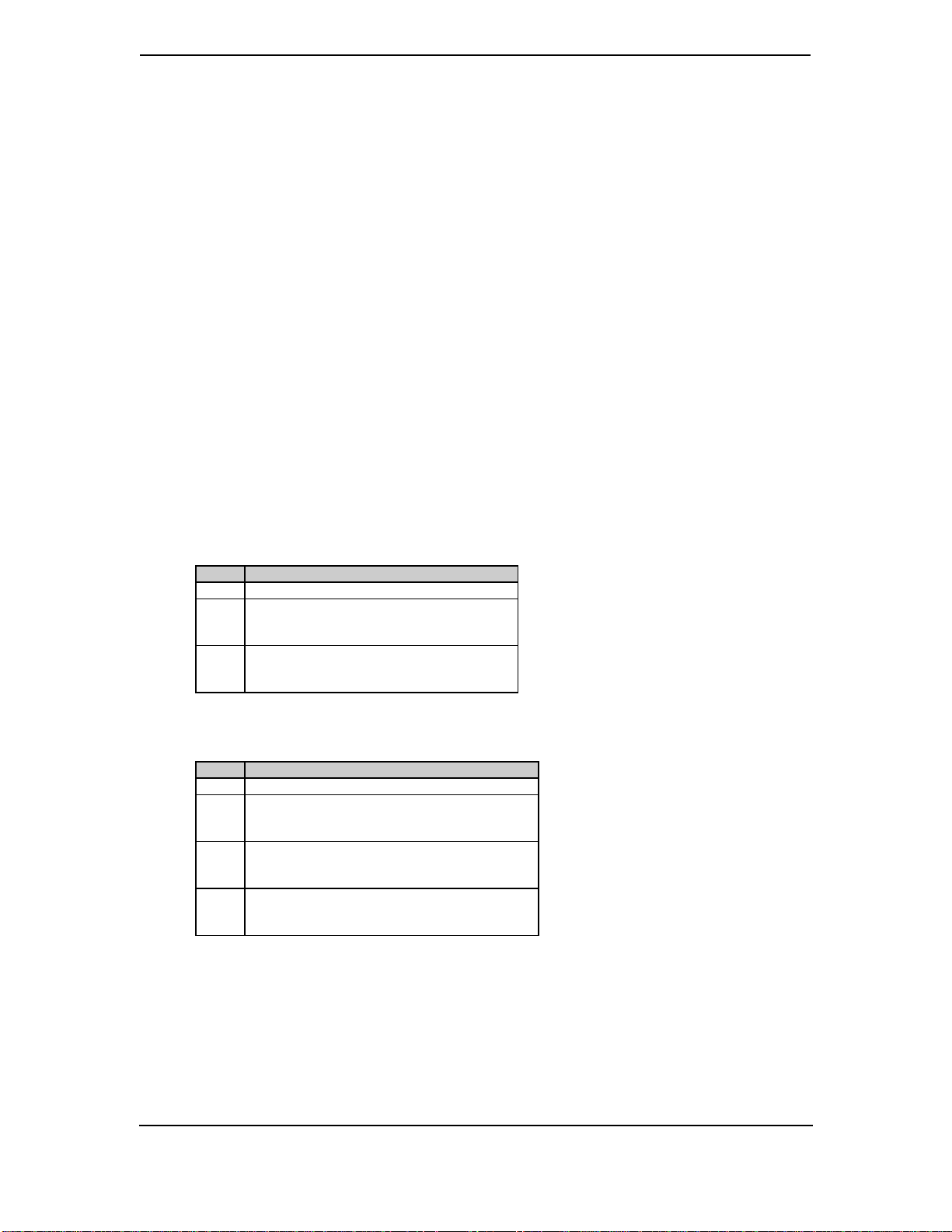

Table 2–3.

The graph i cs subsystem is not upgradeable.

Graphics Subsystem Overview

Table 2-3.

Graphics Subsystem Overview

Parameter Type

Graphics Controller S3 Trio64V2

Graphics Memory 2 MB SGRAM

Maximum Resolution 1280x1024 @ 256 colors

2-12

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 31

2.5 SPECIFICATIONS

This section includes the environmental, electrical, and physical specifications for the Compaq

Deskpro 4000N and 4000S Series Personal Computers.

Technical Reference Guide

Table 2–4.

Environmental Specifications

Table 2-4.

Environmental Specifications

Parameter Operating Nonoperating

Air Temperature 50

Shock N/A 60.0 g for 2 ms half-sine pulse

Vibration 0.000215g^ 2/Hz, 10-300 Hz [1] 0.0005g^ 2/Hz, 10-500 Hz [1]

Humidity 80% RH @ 36

Maximum Altitude 10,000 ft (3048 m) 30,000 ft (9,144 m)

NOTE:

Table 2–5.

Values are subject to change without notice.

[1] 0.5 grms nominal.

Electrical Specifications

o

to 95o F (10o to 35o C) -24o to 140o F (-30o to 60o C)

o

C (no hard drive) 95% RH @ 36o C

Table 2-5.

Electrical Specifications

Parameter Domestic International

Input Line Voltage:

Nominal:

Maximum:

Input Line Frequency Range:

Nominal:

Maximum:

Power Supply

Maximum Continuous Power:

Maximum Line Current Draw:

100 - 120 VAC

90 - 132 VAC

50 - 60 Hz

47 - 63 Hz

75 watts

5.5 A

200 - 240 VAC

180 - 264 VAC

50 - 60 Hz

47 - 63 Hz

75 watts

?? watts

3.0 A

Table 2–6.

Physical Specifications

Table 2-6.

Physical Specific ations

Dimension Measurement

Height 3.56 in (9.00 cm)

Width 112.50 in (31.80 cm)

Depth 14.60 in (37.10 cm)

Weight 20 lb (9.08 kg)

NOTE:

Metric measurements shown in parenthesis.

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition -September

2-13

Page 32

Chapter 2 System Overview

Table 2–7. Diskette Drive Specifications

Paramemter Measurement

Media Type 3.5 in 1.44 MB/720 KB diskette

Height 1/3

Bytes per Sector 512

Secto rs per T rack:

High Density

Low Density

Tracks p er Side:

High Density

Low Density

Read/Write Heads 2

Average Access Time:

Track-to-Track (high/low)

Average (high/low)

Settling Time

Latency Average

Table 2-7.

Diskette Drive S pec ifications

18

9

80

80

3 ms/3 ms

94 ms/94ms

15 ms

100 ms

Table 2–8. 8x CD-ROM Drive Specifications

Table 2-8.

20x CD-ROM Drive Spec ifications

Paramemter Measurement

Media Type Mode 1,2, Mixed Mode, CD-DA,

Center Hole Diameter 15 mm

Disc Diameter 8/12 cm

Disc Thickness 1.2 mm

Track Pitch 1.6 um

Laser

Beam Divergence

Output Power

Typr

Wave Length

Average Access Time:

Random

Full Stroke

Audio Output Level 0.7 Vrms

Cache Buffer 128 KB (min)

Data Transfer Time

Sustained

Startup Time

Photo CD, Cdi , CD-XA

53.5 +/- 1.5

53.6 0.14 mW

790 +/- 25 nm

150 ms

600 ms

3000 KB/s

7 secs (nom)

°

GaAs

2-14

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 33

Technical Reference Guide

Table 2–9. Hard Drive Specifications

Table 2-9.

Hard Drive Specifications

Parameter 1.6 GB 2.1 GB

Interface: EIDE EIDE

Drive Type: 65 65

Drive Size: 5.25 in 5.25 in

Transfer Rate

Heads:

Interface:

Seek Time (w/settling)

Single Track:

Average:

Full Stroke:

Disk RPM: 4500 4500

EDMA Support: Mode 2 Mode 2

PIO Support: Mode 4 Mode 4

Power Mode Command Support: Yes Yes

Drive Fault Prediction: SMART II SMART II

94.0 Mb/s

16.7 MB/s

2.0 ms

11.0 ms

25.0 ms

27.2-55 Mb/s

16.7 MB/s

2.0 ms

12.0 ms

22.0 ms

Compaq Deskpro 4000N and 4000S Personal Computers

First Edition -September

2-15

Page 34

Chapter 2 System Overview

This page is intentionally blank.

2-16

Compaq Deskpro 4000N and 4000S Personal Computers

Firs t Edition - September 1997

Page 35

Chapter 3

PROCESSOR/

MEMORY SUBSYSTEM

Technical Reference Guide

3.

3.1

Chapter 3 PROCESSOR/MEMORY SUB S YSTEM

INTRODUCTION

This chapter describes the processor/cache memory subsystem of the Compaq Deskpro 4000N

and 4000S Series of Personal Computers.

This chapter includes the following topics:

♦ Pentium MMX-based processor/m em or y subsystem [3.2] page 3-2

♦ Klamath-based processor/memory subsystem [3.4] page 3-12

Table 3-1 lists the highl i ghts of the processor/memory architecture.

Table 3–1.

Processor/Memory Architectural Highlights

Table 3-1.

Processor/Memory

Architectur al Highlights

Feature Type/Amount

Support Chipset VT82C595

System Memory

Standard installed:

Expandable to:

Cache Memory

L1:

L2:

NOTES:

[1] Integrated into the microprocessor

16 or 32 MB SDRAM

256 MB

32 KB [1]

256 KB

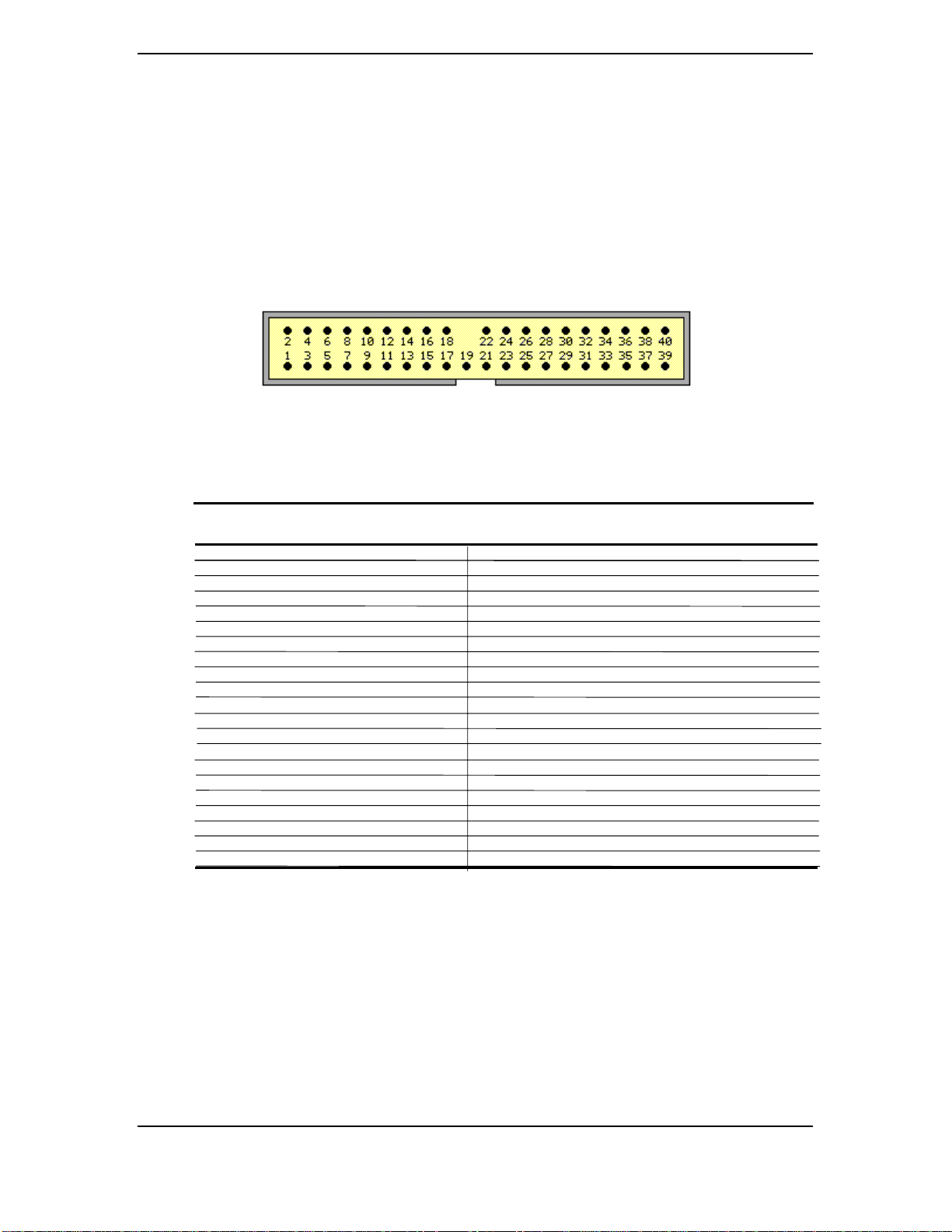

Compaq Deskpro 4000N and 4000S Personal Computers