CompanyXacc C1030-5510 User Manual

USBS6

V 0.3 June 29, 2010 User Manual C1030-5510

SPARTAN-6TM FPGA board with USB2.0,

SPI-Flash and JTAG interface.

Order number: C1030-5510

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -1- preliminary

Copyright information

Copyright © 2010 CESYS GmbH. All Rights Reserved. The information in this document is

proprietary to CESYS GmbH. No part of this document may be reproduced in any form or

by any means or used to make derivative work (such as translation, transformation or

adaptation) without written permission from CESYS GmbH.

CESYS GmbH provides this documentation without warranty, term or condition of any kind,

either express or implied, including, but not limited to, express and implied warranties of

merchantability, fitness for a particular purpose, and non-infringement. While the

information contained herein is believed to be accurate, such information is preliminary,

and no representations or warranties of accuracy or completeness are made. In no event

will CESYS GmbH be liable for damages arising directly or indirectly from any use of or

reliance upon the information contained in this document. CESYS GmbH will make

improvements or changes in the product(s) and/or program(s) described in this

documentation at any time.

CESYS GmbH retains the right to make changes to this product at any time, without notice.

Products may have minor variations to this publication, known as errata. CESYS GmbH

assumes no liability whatsoever, including infringement of any patent or copyright, for sale

and use of CESYS GmbH products.

CESYS GmbH and the CESYS logo are registered trademarks.

All product names are trademarks, registered trademarks, or service marks of their

respective owner.

⇒ Please check www.cesys.com to get the latest version of this document.

CESYS Gesellschaft für angewandte Mikroelektronik mbH

Zeppelinstrasse 6a

D – 91074 Herzogenaurach

Germany

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -2- preliminary

Overview

Summary of USBS6

USBS6 is a low-cost multilayer PCB with SPARTAN-6TM FPGA and USB 2.0 Interface. 34

I/O balls of the FPGA are available on standard 2.54mm headers, 81 I/O balls can be

reached through a industry standard VG 96-pin connector. It offers multiple configuration

options including USB and onboard SPI-Flash and can also be used standalone without

the need of a USB interface.

Feature list

Form factor 120x100mm

XILINX SPARTAN-6

USB2.0 Controller CYPRESSTM CY7C68013A

FPGA configuration Using USB2.0, JTAG or SPI-Flash

Memory 16Mb SPI-Flash Numonyx M25P16,

Peripherals USB TO SERIAL UART FTDI FT232R,

Expansion connectors 2x25-Pin standard RM2.54mm header,

Clock Onboard 48MHz clock signal,

TM

XC6SLX16-2CSG324C

128Mb Quad-SPI-Flash Macronix MX25L12845EMI-10G,

1Gb low-power DDR SDRAM Micron

Technology MT46H64M16LFCK-5

HEX rotary DIP switch,

3 status, 5 user LEDs

VG 96-pin connector

up to two optional onboard clocks,

external clock sources possible.

Included in delivery

The standard delivery, order no. C1030-5510, includes:

• One USBS6

• One USB cable 1,5m

• One CD-ROM containing the user's manual (English), drivers, libraries, tools and

example source code.

All parts are ROHS compliant.

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -3- preliminary

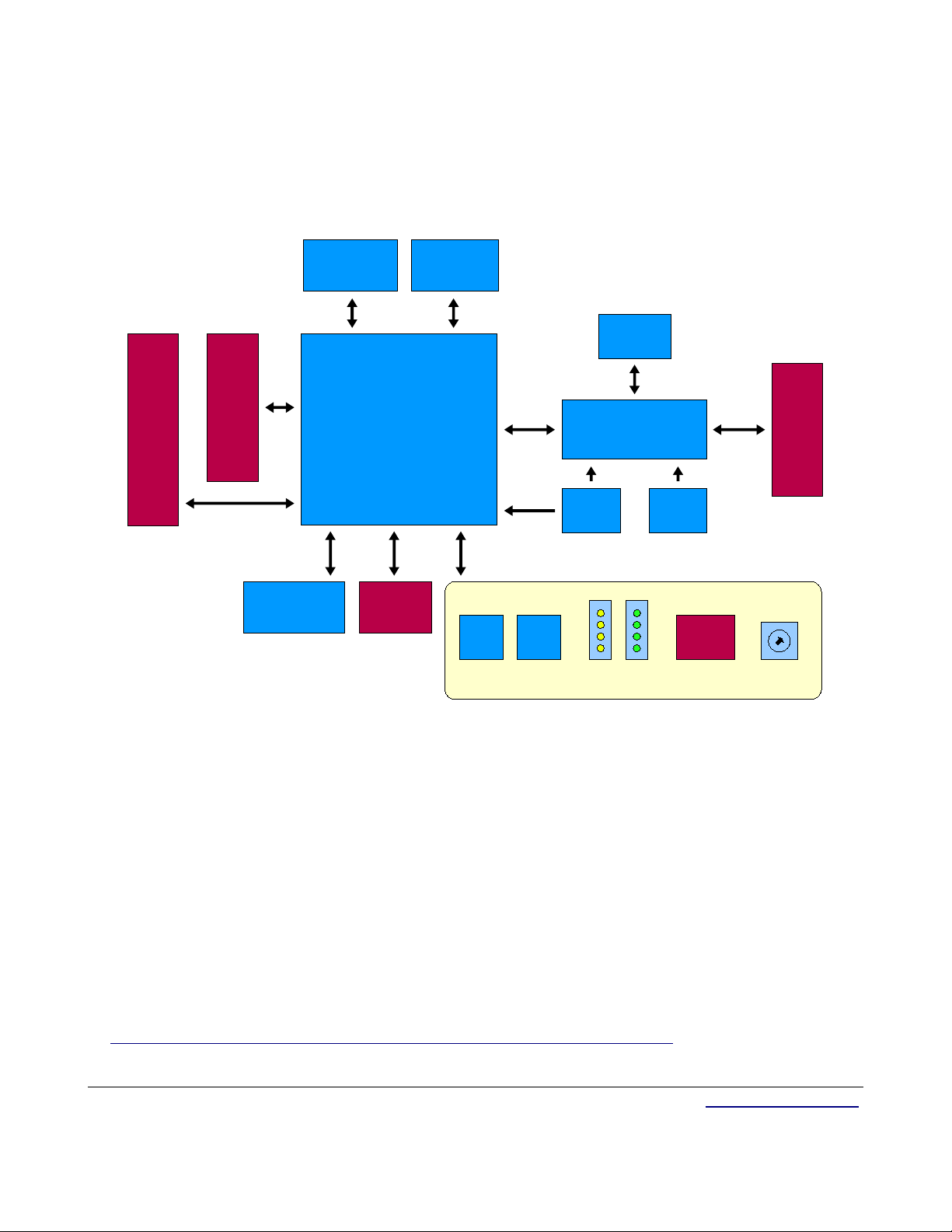

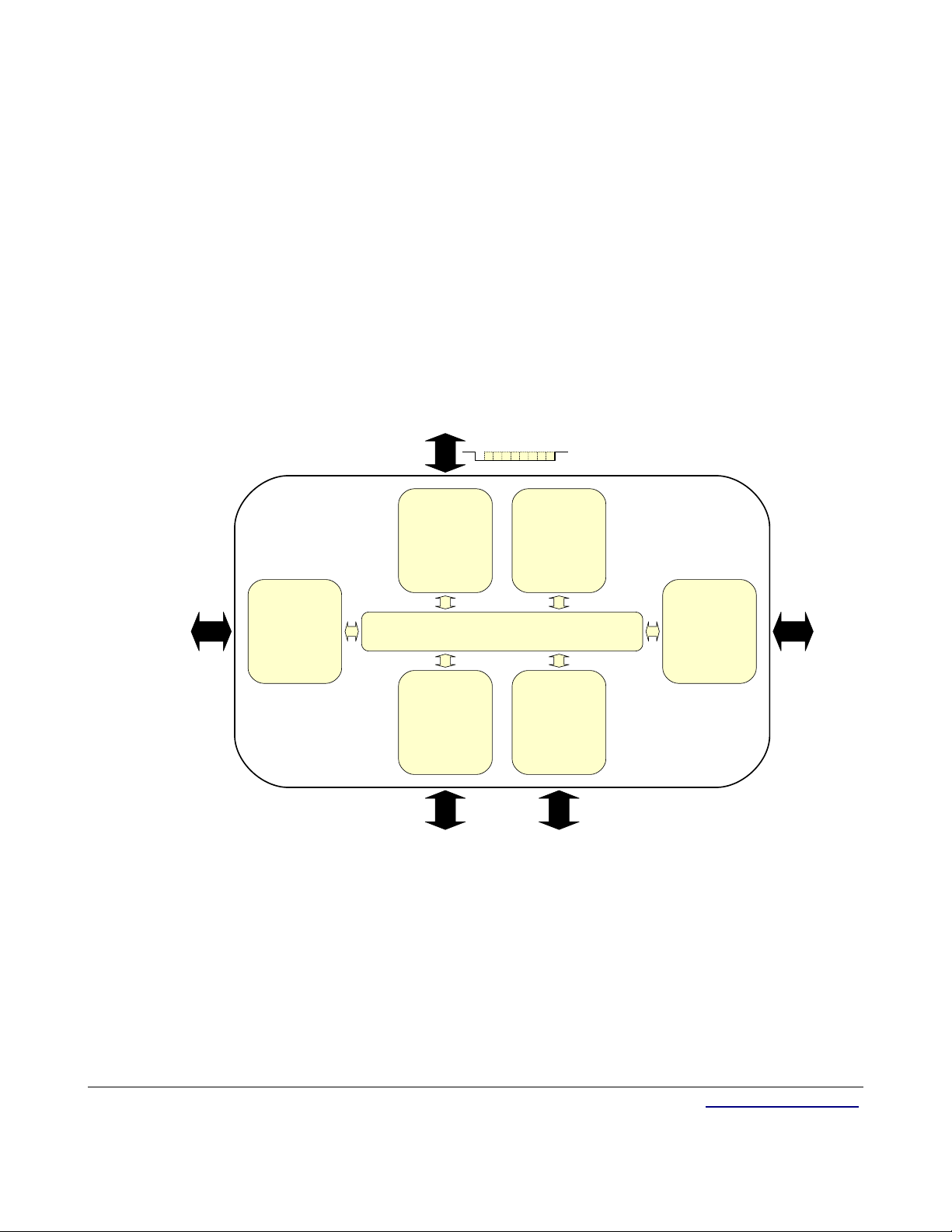

Hardware

USB-Connector

64kb I²C

EEPROM

Oscillator

24 MHz

OSC OSC

USB /

SERIAL

Optional

Oscillators

3 status &

5 user LEDs

USB to

UART

HEX rotary

DIP switch

Peripherals

USB2.0

CYPRESS FX-2

JTAG

XILINX FPGA

Spartan-6

81 I/O on

VG 96-pin connector

34 I/O on

2x25-pin header

Oscillator

48 MHz

128Mb

QSPI Flash

16Mb SPI Flash

for configuration

1 Gb low-power

DDR SDRAM

Block Diagram

Figure 1: USBS6 Block Diagram

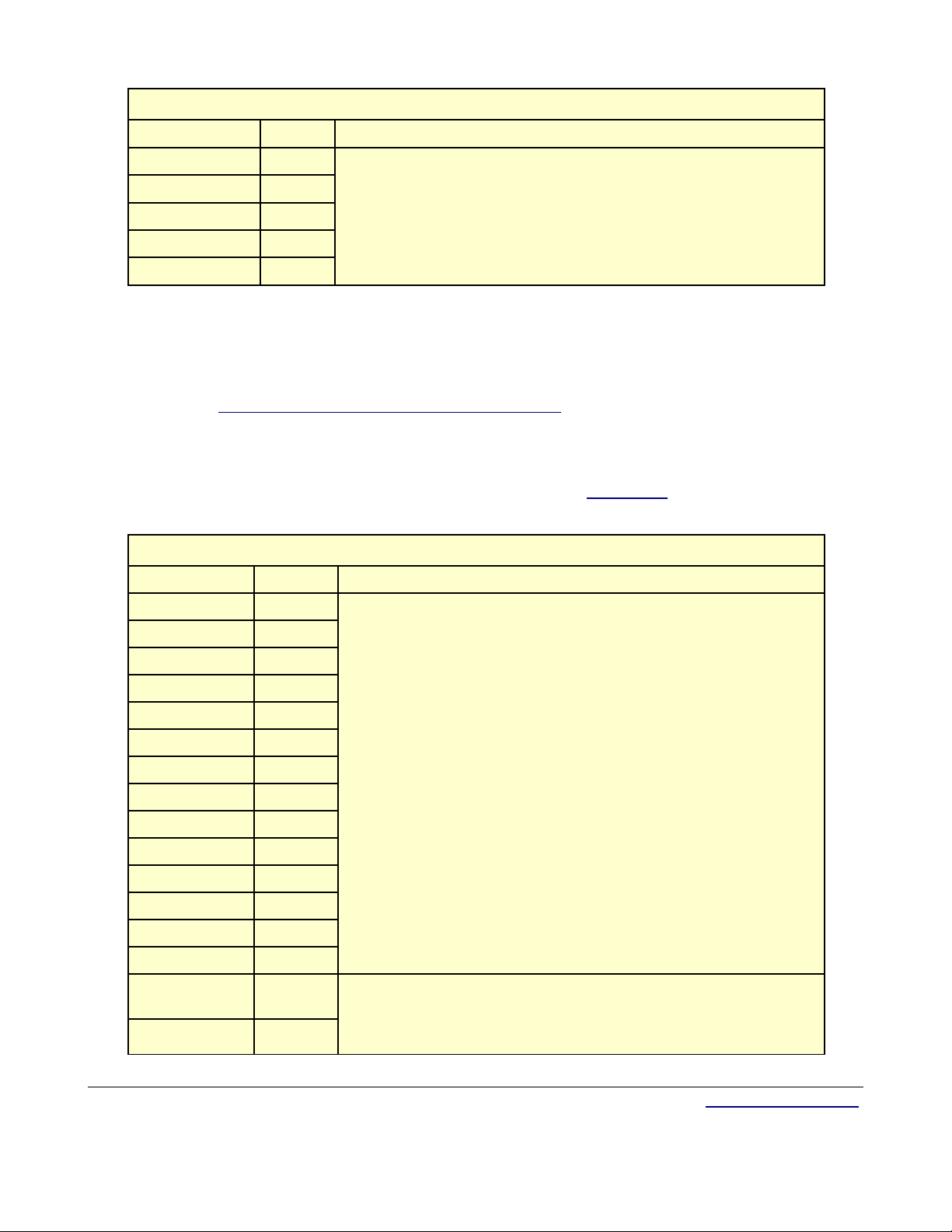

Spartan-6TM FPGA

XC6SLX16-2CSG324C FPGA features:

Logic cells 14,579

Configurable logic blocks (Slices / Flip-Flops) 2,278 / 18,224

Max distributed RAM (kb) 136

DSP Slices 136

Block RAM Blocks (18kB / Max(kb) ) 32 / 576

CMTs 2

For details of the SPARTAN -6TM FPGA device, please look at the data sheet at:

http://www.xilinx.com/support/documentation/data_sheets/ds160.pdf

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -4- preliminary

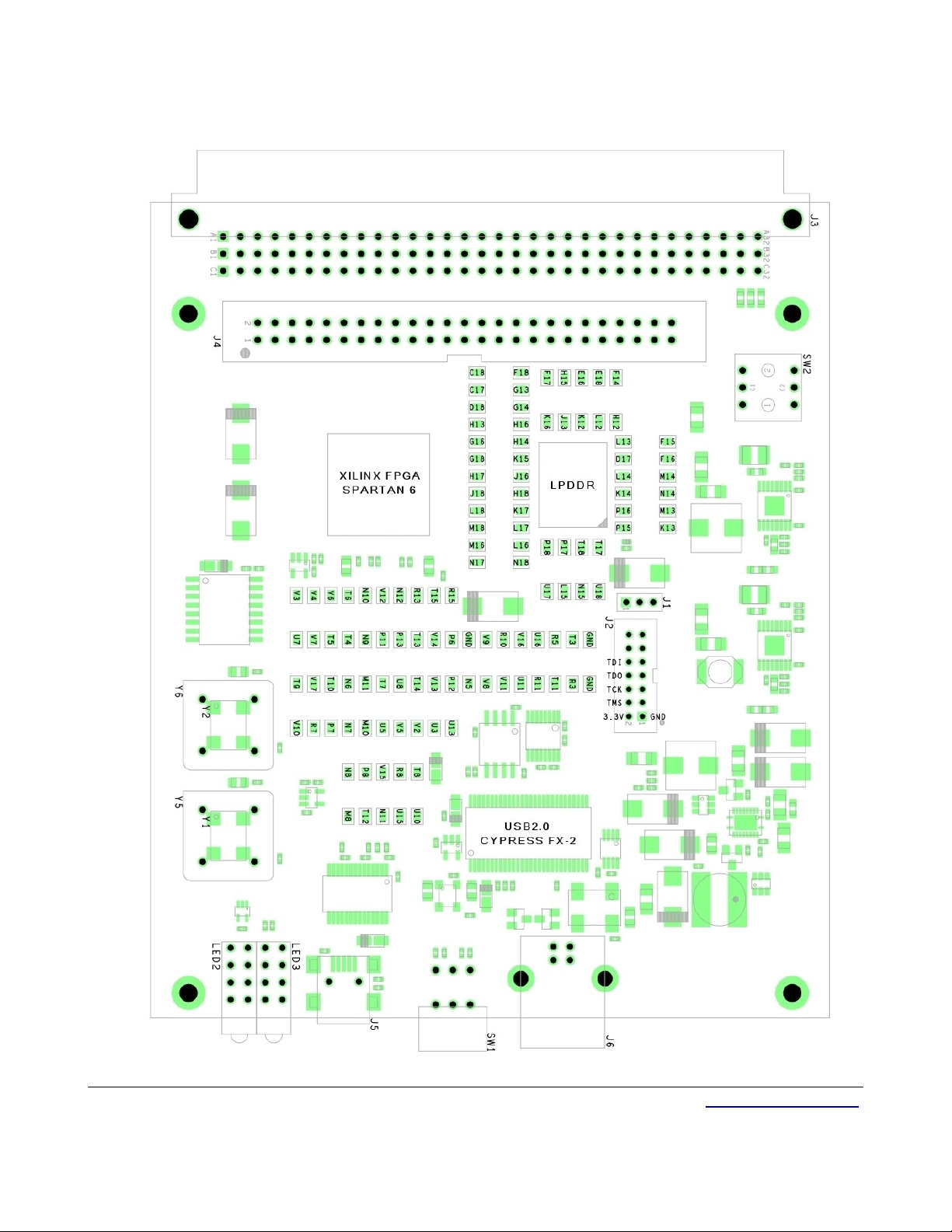

Figure 2: USBS6 Top View

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -5- preliminary

Powering USBS6

USBS6 may be used bus-powered (see SW2 below) without the need of any external

power supply other than USB. In this mode VCCO_IO on J3,PIN A3, B3, C3 sourcing

capability is limited due to the fact, that USB power supply current is limited depending on

which system is used as host. Typically USB hosts allow up to 500mA. In bus-powered

mode, at first only FX2 is enabled. After successful connection to the operating system the

further power-on sequencing behavior depends on UDK configuration. Until the release of

UDK2.0 only the API could enable further power-on sequencing, therefore after plugging

an USB cable it also was necessary to start an application like cesys- Monitor before the

FPGA and other devices turned on. With v2.0 and upcoming releases of UDK framework

the user now can decide which power-on behavior fits best. Power-on sequencing through

API or as soon as USB cable is plugged in. Default mode is API- controlled.

Modes of operation

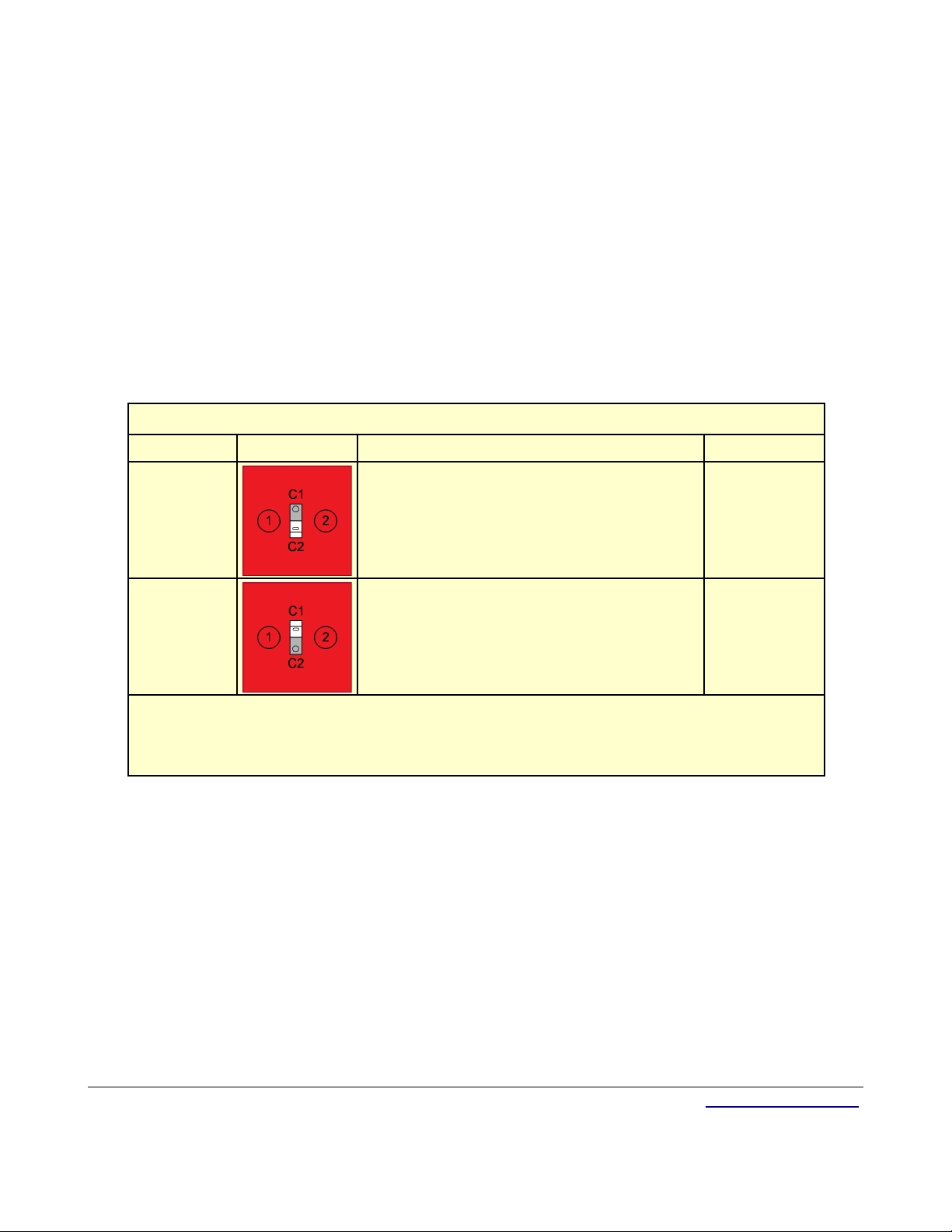

Mode SW2 Comment * VCCO_IO

Bus- powered USB is used as power supply input. 3.3V@ ??? mA

Self- powered Connect 5V power supply to VG- 96pin external

expansion connector J3 PINS A1, B1 and C1.

Minimum required supply current: ???A

* The actual required supply current strongly depends on FGPA design and may exceed the

minimum required.

** In self-powered mode the actual VCCO_IO current limit depends on sourcing capability of

external 5V power supply and may be less.

3.3V@ 3 A **

If the attached USB2.0 host interface should not be used as power supply, it is possible to

use USBS6 self-powered (see SW2 above). In this mode an external 5V power supply

must be connected to the external expansion connector J3, PINS A1, B1 and C1. All

onboard voltages are enabled as soon as an external power supply is applied. VCCO on

BANK0 and BANK3 is tied together to VCCO_IO but routed independent from other supply

voltages. Therefore in self-powered mode maximum current available on J3,PIN

A3, B3, C3 (VCCO_IO) mainly depends on the external power supply to the limit of the

onboard regulator, which is about 3A. As default VCCO_IO is regulated to 3.3V to enable

3.3V signaling levels on the external expansion connectors. Other signaling levels may be

supported but require adjustment of the onboard synchronous buck regulator to the desired

value.

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -6- preliminary

! It is strongly recommended to check XILINXTM UG381 about Spartan-6 FPGA SelectIO

Signal Standards on XILINXTM website.

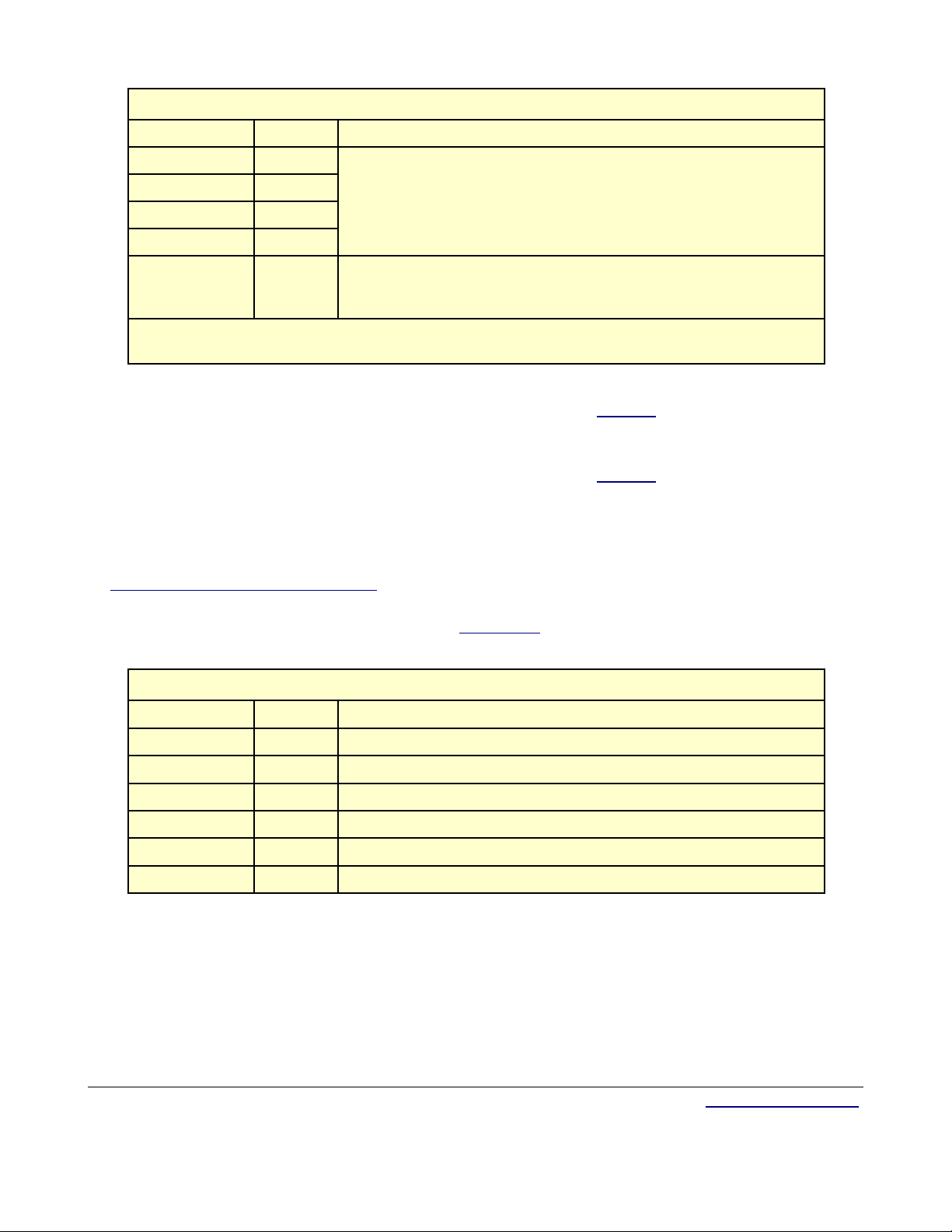

Configuration

Configuration of USBS6 can be accomplished in several ways: JTAG, SPI-Flash or USB.

The default configuration mode is booting from SPI-Flash. After powering on the FPGA,

USBS6 always tries to configure itself from the attached Flash using SPI Master mode. If

no valid design is stored in the SPI-Flash the FPGA has to be configured via JTAG or USB.

JTAG configuration is supported at any time after the FPGA is properly powered on. For

downloading designs via JTAG ISE WebPACK from XILINXTM is recommended. The tool

can be downloaded from XILINX web page free of charge. As JTAG connector USBS6

implements a standard 2x7-Pin header with 2mm pitch which is compatible to recent

XILINXTM platform cables.

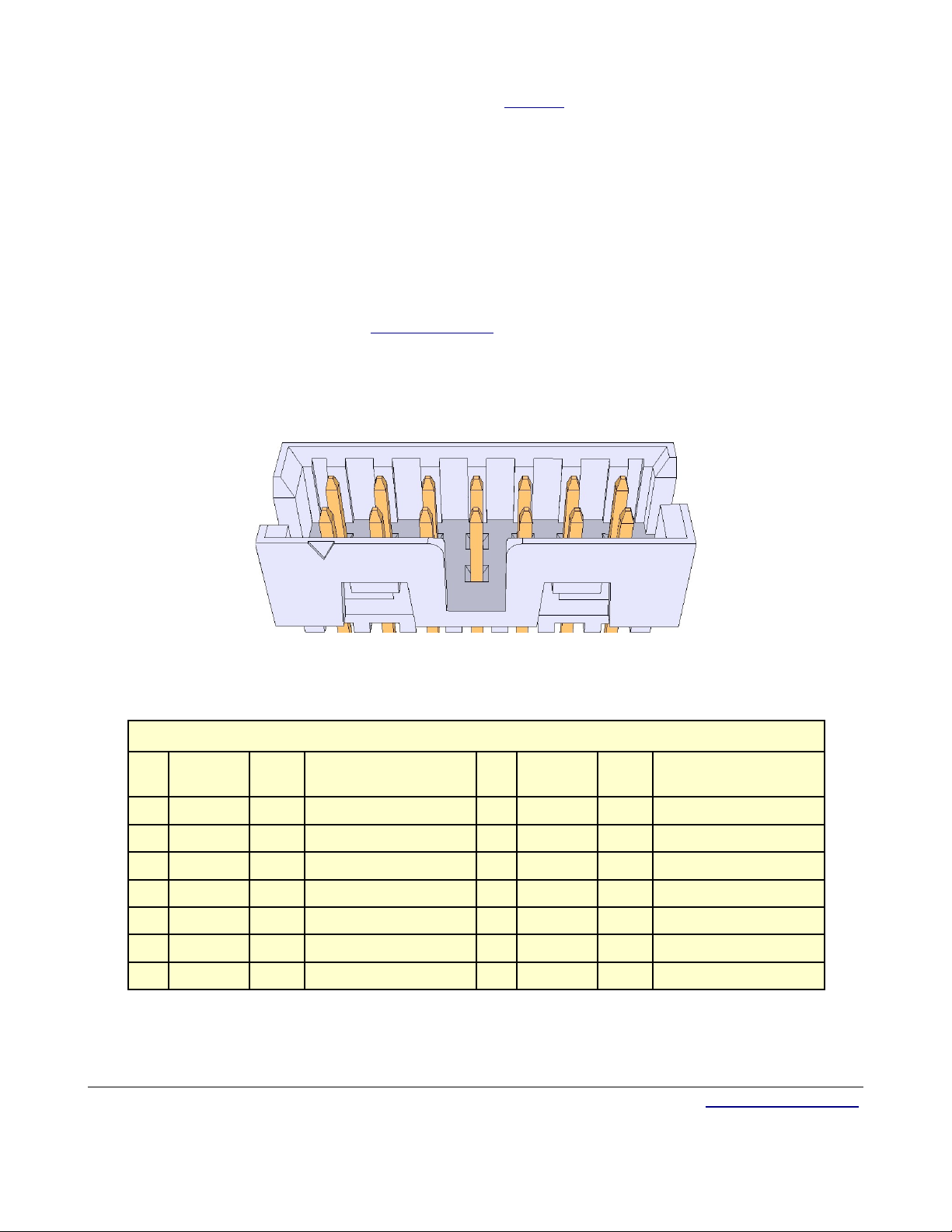

Figure 3: JTAG connector J2

J2 JTAG connector

PIN Signal

Name

1 GND -- Ground signal 2 VCCAUX -- 3.3V auxiliary supply.

3 GND -- Ground signal 4 TMS B18 Test Mode Select.

5 GND -- Ground signal 6 TCK A17 Test Clock.

7 GND -- Ground signal 8 TDO D16 Test Data Out.

9 GND -- Ground signal 10 TDI D15 Test Data In.

11 GND -- Ground signal 12 -- -- No connection.

13 GND -- Ground signal 14 -- -- No connection.

For further information on the different configuration solutions for XILINX

FPGA

IO

Comment PIN Signal

Name

FPGA

IO

Comment

TM

SPARTAN-6

TM

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -7- preliminary

FPGA the reader is encouraged to take a look at the user guide UG380 on XILINXTM web

page.

USB2.0 controller

CYPRESSTM FX2LPTM is a highly integrated, low power USB2.0 microcontroller, that

integrates USB2.0 transceiver, serial interface engine (SIE), enhanced 8051 microcontroller and a programmable peripheral interface. More information on usage of FX2LP

in conjunction with Spartan-6 can be found in chapter C.

USB2.0 FX2LPTM Microcontroller CYPRESSTM CY7C68013A

Signal Name FPGA IO Comment

FX2_IFCLK V9 Clock input for both, FX2 and FPGA. 48MHz clock is provided by an

external oscillator.

FX2_SLWR U8 FX2 input, FIFO write-strobe.

FX2_SLRD T7 FX2 input, FIFO read-strobe.

FX2_SLOE V11 FX2 input, output-enable, activates FX2 data bus.

FX2_PKTEND V8 FX2 input, packet end control signal, causes FX2 to send data to host

at once, ignoring 512 byte alignment (so called “short packet”).

! Short packets sometimes lead to unpredictable behavior at host

side, wherefore short packets are not support!

TM

FX2_FIFOADR0 R10

FX2_FIFOADR1 U3

FX2_FLAGA V16 FX2 output, EP2 “empty” flag.

FX2_FLAGB U16 FX2 output, EP2 “almost empty” flag.

FX2_FLAGC U11 FX2 output, EP6 “almost full” flag.

FX2_FD0 R11 16-Bit bidirectional FIFO data bus.

FX2_FD1 T14

FX2_FD2 V14

FX2_FD3 U5

FX2_FD4 V5

FX2_FD5 R3

FX2_FD6 T3

FX2_FD7 R5

FX2_FD8 N5

FX2_FD9 P6

FX2_FD10 P12

FX2 input, endpoint buffer addresses, only two endpoints are used:

EP2 (OUT, ADR[1:0] = b”00”) and EP6 (IN, ADR[1:0] = b”10”).

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -8- preliminary

USB2.0 FX2LPTM Microcontroller CYPRESSTM CY7C68013A

Signal Name FPGA IO Comment

FX2_FD11 U13

FX2_FD12 V13

FX2_FD13 U10

FX2_FD14 R8

FX2_FD15 T8

External memory

USBS6 offers the opportunity to use various external memory architectures in one´s FPGA

design. With Micron Technology MT46H64M16LFCK-5 up to 1Gbit of high-speed low-

power DDR SDRAM is available. The integrated memory controller of Spartan-6TM devices

enables system designers to implement state-of-the-art memory interfaces without the

need to develop a whole memory controller Soft-IP all on their own. Some examples on

how to implement LPDDR with Spartan-6 are available in chapter C.

LPDDR SDRAM MT46H64M16LFCK-5

Signal Name FPGA IO Comment

MCB1_A0 H15

MCB1_A1 H16

MCB1_A2 F18

MCB1_A3 J13

MCB1_A4 E18

MCB1_A5 L12

MCB1_A6 L13

MCB1_A7 F17

MCB1_A8 H12

MCB1_A9 G13

MCB1_A10 E16

MCB1_A11 G14

MCB1_A12 D18

MCB1_A13 C17

MCB1_BA0 H13 Bank address inputs: BA0 and BA1 define to which bank an ACTIVE,

MCB1_BA1 H14

Address inputs: Provide the row address for ACTIVE commands, and

the column address and auto precharge bit (A10) for READ or

WRITE commands, to select one location out of the memory array in

the respective bank. During a PRECHARGE command, A10

determines whether the PRECHARGE applies to one bank (A10

LOW, bank selected by BA0, BA1) or all banks (A10 HIGH). The

address inputs also provide the op-code during a LOAD MODE

REGISTER command.

READ, WRITE, or PRECHARGE command is being applied. BA0

and BA1 also determine which mode register is loaded during a

LOAD MODE REGISTER command.

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -9- preliminary

LPDDR SDRAM MT46H64M16LFCK-5

Signal Name FPGA IO Comment

MCB1_RAS_n K15

MCB1_CAS_n K16

MCB1_WE_n K12

MCB1_CS_n --

MCB1_CKE_n D17 Clock enable: CKE HIGH activates, and CKE LOW deactivates, the

MCB1_RZQ N14 Input termination calibration pin used with the soft calibration module.

MCB1_ZIO No connect signal used with the soft calibration module to calibrate

MCB1_CK G16 Clock: CK is the system clock input. CK and CK# are differential

MCB1_CK_n G18

MCB1_DQ0 M16

MCB1_DQ1 M18

Command inputs: RAS#, CAS#, and WE# (along with CS#) define

the command being entered. *

internal clock signals, input buffers, and output drivers. Taking CKE

LOW enables PRECHARGE power-down and SELF REFRESH

operations (all banks idle), or ACTIVE power-down (row active in any

bank). CKE is synchronous for all functions except SELF REFRESH

exit. All input buffers (except CKE) are disabled during power-down

and self refresh modes.

External 100 Ohm resistor to GND.

the input termination value.

clock inputs. All address and control input signals are sampled on the

crossing of the positive edge of CK and the negative edge of CK#.

Input and output data is referenced to the crossing of CK and CK#

(both directions of the crossing).

MCB1_DQ2 L17

MCB1_DQ3 L18

MCB1_DQ4 H17

MCB1_DQ5 H18

MCB1_DQ6 J16

MCB1_DQ7 J18

MCB1_LDQS K17 Data strobe for Lower Byte Data bus: Output with read data, input

MCB1_LDM L16 Input data mask: DM is an input mask signal for write data. Input data

MCB1_UDM L15

MCB1_DQ8 N17 Data input/output: Upper Byte Data bus.

MCB1_DQ9 N18

MCB1_DQ10 P17

MCB1_DQ11 P18

Data input/output: Lower Byte Data bus.

with write data. DQS is edge-aligned with read data, center-aligned in

write data. It is used to capture data.

is masked when DM is sampled HIGH along with that input data

during a WRITE access. DM is sampled on both edges of DQS.

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -10- preliminary

LPDDR SDRAM MT46H64M16LFCK-5

Signal Name FPGA IO Comment

MCB1_DQ12 T17

MCB1_DQ13 T18

MCB1_DQ14 U17

MCB1_DQ15 U18

MCB1_UDQS N15 Data strobe for Upper Byte Data bus: Output with read data, input

with write data. DQS is edge-aligned with read data, center-aligned in

write data. It is used to capture data.

* As the memory device interface of Spartan-6 supports only one device, CS# signal is not

supported by Spartan-6 MCB. CS# is pulled LOW via an external 0 Ohm resistor.

! It is strongly recommended to check XILINXTM user guide UG388 about Spartan-6

TM

FPGA Memory Controller on XILINXTM website.

! It is strongly recommended to check XILINXTM user guide UG416 about Spartan-6

TM

FPGA Memory Interface Solutions on XILINXTM website.

User specific data can be stored in up to 128Mb of non-volatile Flash-memory. The

SPI- compliant interface guarantees ease of use and when speed matters

Macronix MX25L12845EMI-10G supports Q- SPI with data-rates up to 50 MByte/s in fast

read double transfer rate mode. Some examples on how to implement a SPI- compliant

interface with Spartan-6TM are available in chapter C.

Q- SPI Flash MX25L12845EMI-10G

Signal Name FPGA IO Comment

MX_CS_n T6 Active- low Chip Select.

MX_SCLK V4 Clock Input.

MX_SIO0 V6 Serial Data Input (SPI) / Serial Data IO (Dual- or Q- SPI).

MX_SIO1 T4 Serial Data Input (SPI) / Serial Data IO (Dual- or Q- SPI).

MX_SIO2 U7 Active- low Write Protect (SPI) / Serial Data IO (Dual- or Q-SPI).

MX_SIO3 V7 Not connect pin (SPI) / Serial Data IO (Dual- or Q-SPI).

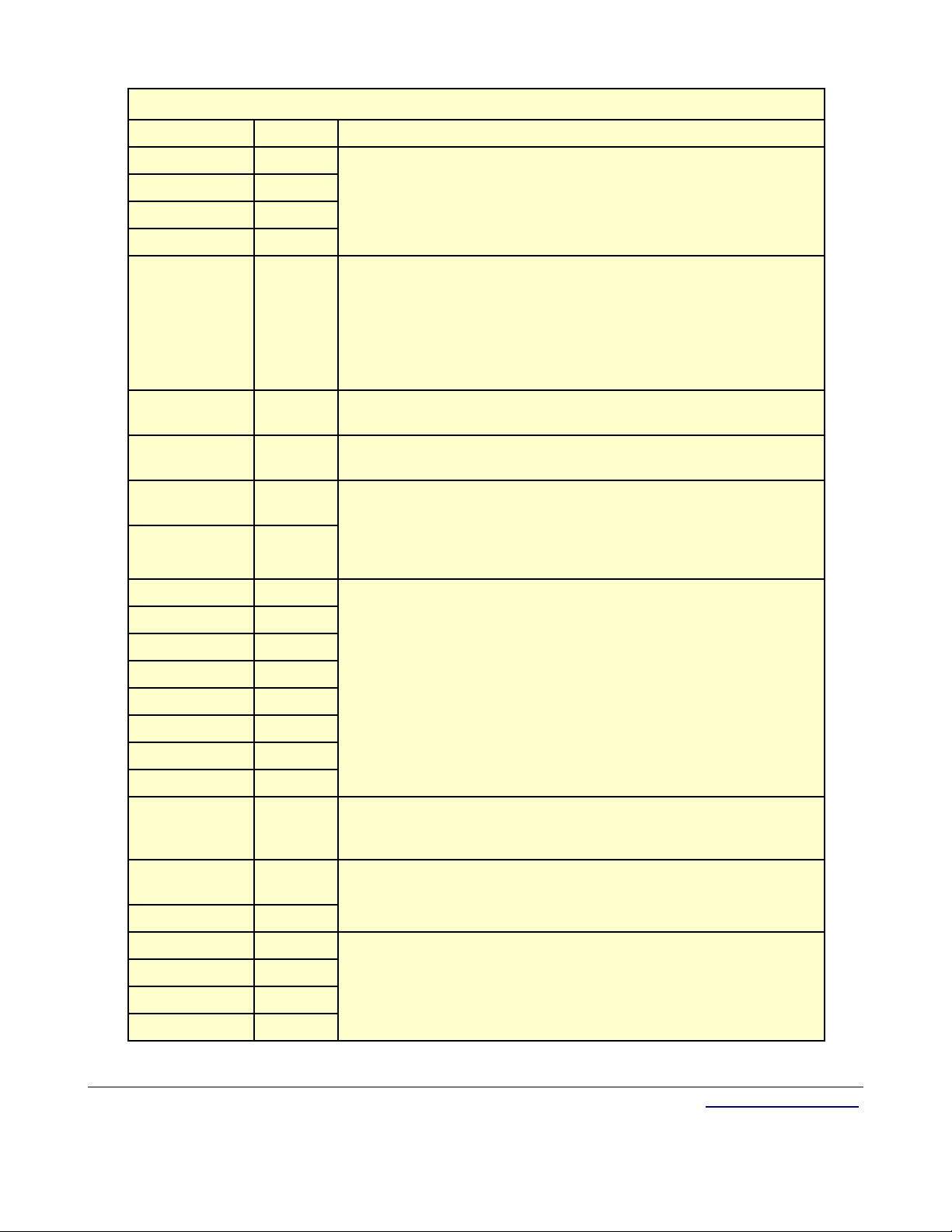

Peripherals

USBS6 integrates several peripheral devices. Three system and five user- configurable

LEDs, one HEX rotary DIP switch and one USB to SERIAL UART are available. Power

supply status and FPGA configuration are observable through the system LEDs. The user-

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -11- preliminary

configurable LEDs allow to make internal monitoring status signals visible by driving the

appropriate FPGA IO to a HIGH level.

Figure 4: Bitte durch Orginalbild ersetzen

LEDs

Signal Name FPGA IO Comment

SYS_LED0 -- Internal 5V power supply.

SYS_LED1 -- Power OK- signal from onboard voltage regulator.

SYS_LED2 V17 Illuminates to indicate the status of the DONE pin if FPGA is

successfully configured.

USER_LED0 P7 User- configurable LED.

USER_LED1 N7 User- configurable LED.

USER_LED2 P8 User- configurable LED.

USER_LED3 N6 User- configurable LED.

USER_LED4 R7 User- configurable LED.

The HEX rotary DIP switch is of binary coded type. The four weighted terminals are

externally pulled HIGH with 4,7 kOhm resistors, the common terminals are connected to

GND. Therefore the four FPGA inputs behave like a complementary binary coded

hexadecimal switch.

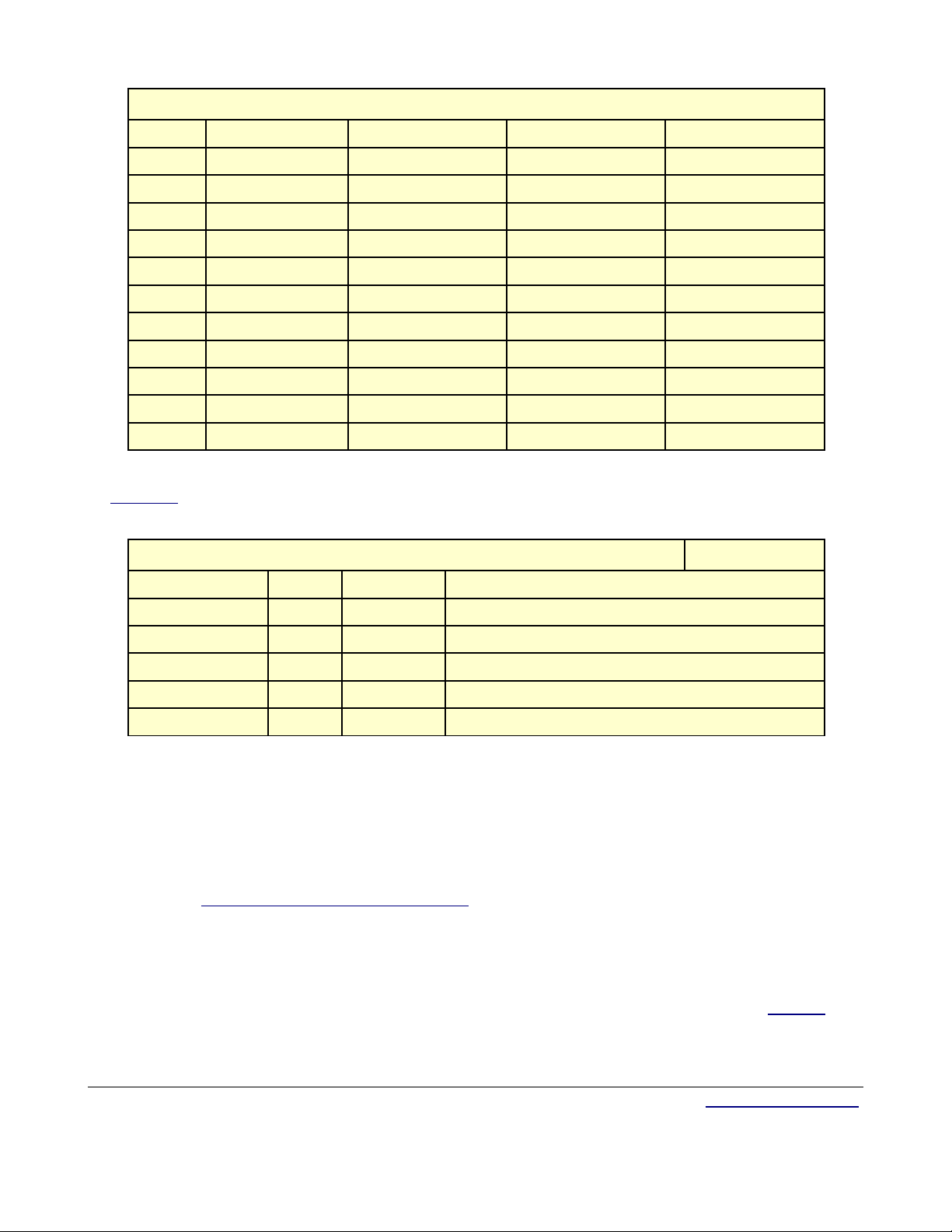

HEX rotary DIP switch

DIAL FPGA Pin N8 FPGA Pin M11 FPGA Pin M10 FPGA Pin N9

0 1 1 1 1

1 0 1 1 1

2 1 0 1 1

3 0 0 1 1

4 1 1 0 1

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -12- preliminary

HEX rotary DIP switch

DIAL FPGA Pin N8 FPGA Pin M11 FPGA Pin M10 FPGA Pin N9

5 0 1 0 1

6 1 0 0 1

7 0 0 0 1

8 1 1 1 0

9 0 1 1 0

A 1 0 1 0

B 0 0 1 0

C 1 1 0 0

D 0 1 0 0

E 1 0 0 0

F 0 0 0 0

FT232R from FTDI is a USB to serial UART interface.

USB to serial UART interface

Signal Name FPGA IO Direction Comment

FTDI_TXD U15 FPGA IN Transmit asynchronous data output for FT232R.

FTDI_RXD V15 FPGA OUT Receiving asynchronous data input for FT232R.

FTDI_RTS_n N11 FPGA IN Request to send control output for FT232R.

FTDI_CTS_n M8 FPGA OUT Clear to send control input for FT232R.

FTDI_RESET_n T12 FPGA OUT Active low reset pin for FT232R.

External expansion connectors

On connectors J3 and J4 up to 115 general purpose FPGA IO are accessible. Bank 0 and

Bank 3 of the FPGA are configured for 3.3V signaling level. Differential IO standards as for

example LVDS are supported too. Detail information about IO pairing is available in

paragraph IO pairing and etch length report of chapter D.

! IO on connectors J3 and J4 are directly connected to FPGA IO and therefore are only 3.3

Volt tolerant. NEVER apply voltages outside the interval [-0.95V..4.1V] as this may lead to

severe damage of FPGA and attached components. For more information regarding DC

and switching characteristics of Spartan-6 FPGA please consult documentation DS160 on

XILINXTM website

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -13- preliminary

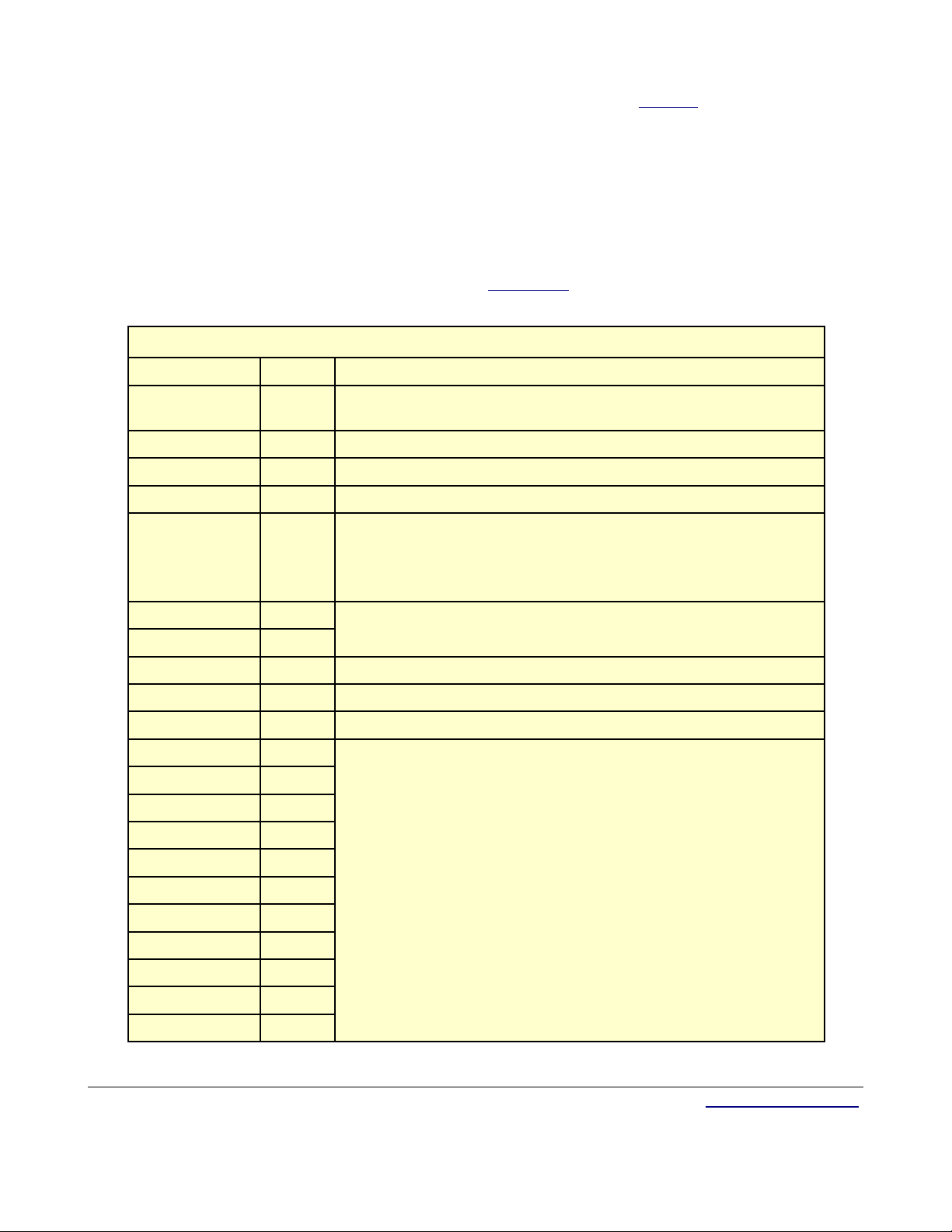

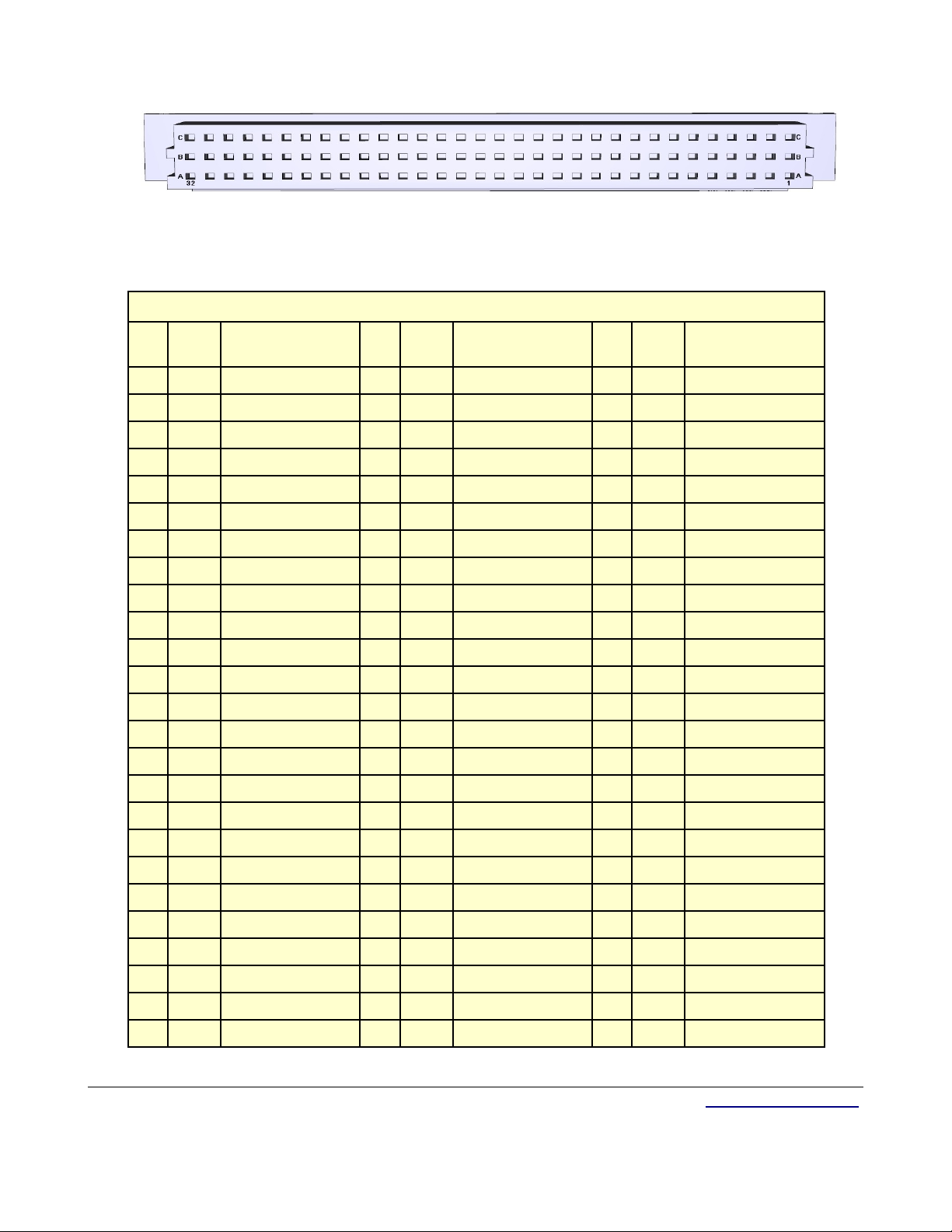

Figure 5: VG 96-pin external expansion connector J3

J3 VG 96-pin external expansion connector

PIN FPGA

IO

A32 -- GND B32 -- GND C32 -- GND

A31 F13 VG96_IO78 B31 E13 VG96_IO79 C31 C4 VG96_IO80

A30 F12 VG96_IO75 B30 E12 VG96_IO76 C30 F11 VG96_IO77

A29 D11 VG96_IO72* B29 C11 VG96_IO73* C29 E11 VG96_IO74

A28 G11 VG96_IO69 B28 F10 VG96_IO70 C28 G8 VG96_IO71

A27 G9 VG96_IO66 B27 F9 VG96_IO67 C27 F8 VG96_IO68

A26 D9 VG96_IO63* B26 C9 VG96_IO64* C26 D8 VG96_IO65

A25 E7 VG96_IO60 B25 E8 VG96_IO61 C25 C8 VG96_IO62

A24 D6 VG96_IO57 B24 C6 VG96_IO58 C24 F7 VG96_IO59

A23 F6 VG96_IO54 B23 F5 VG96_IO55 C23 E6 VG96_IO56

A22 -- GND B22 -- GND C22 -- GND

A21 E4 VG96_IO51 B21 D3 VG96_IO52 C21 F4 VG96_IO53

A20 H7 VG96_IO48 B20 G6 VG96_IO49 C20 F3 VG96_IO50

A19 H4 VG96_IO45* B19 H3 VG96_IO46* C19 J7 VG96_IO47

A18 H6 VG96_IO42 B18 H5 VG96_IO43 C18 J6 VG96_IO44

Comment PIN FPGA

IO

Comment PIN FPGA

IO

Comment

A17 K4 VG96_IO39* B17 K3 VG96_IO40* C17 L6 VG96_IO41

A16 L7 VG96_IO36 B16 K6 VG96_IO37 C16 M5 VG96_IO38

A15 L5 VG96_IO33* B15 K5 VG96_IO34* C15 E3 VG96_IO35

A14 L4 VG96_IO30 B14 L3 VG96_IO31 C14 E1 VG96_IO32

A13 C2 VG96_IO27 B13 C1 VG96_IO28 C13 G3 VG96_IO29

A12 D2 VG96_IO24 B12 D1 VG96_IO25 C12 G1 VG96_IO26

A11 F2 VG96_IO21 B11 F1 VG96_IO22 C11 J3 VG96_IO23

A10 H2 VG96_IO18* B10 H1 VG96_IO19* C10 J1 VG96_IO20

A9 K2 VG96_IO15 B9 K1 VG96_IO16 C9 M3 VG96_IO17

A8 L2 VG96_IO12 B8 L1 VG96_IO13 C8 M1 VG96_IO14

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -14- preliminary

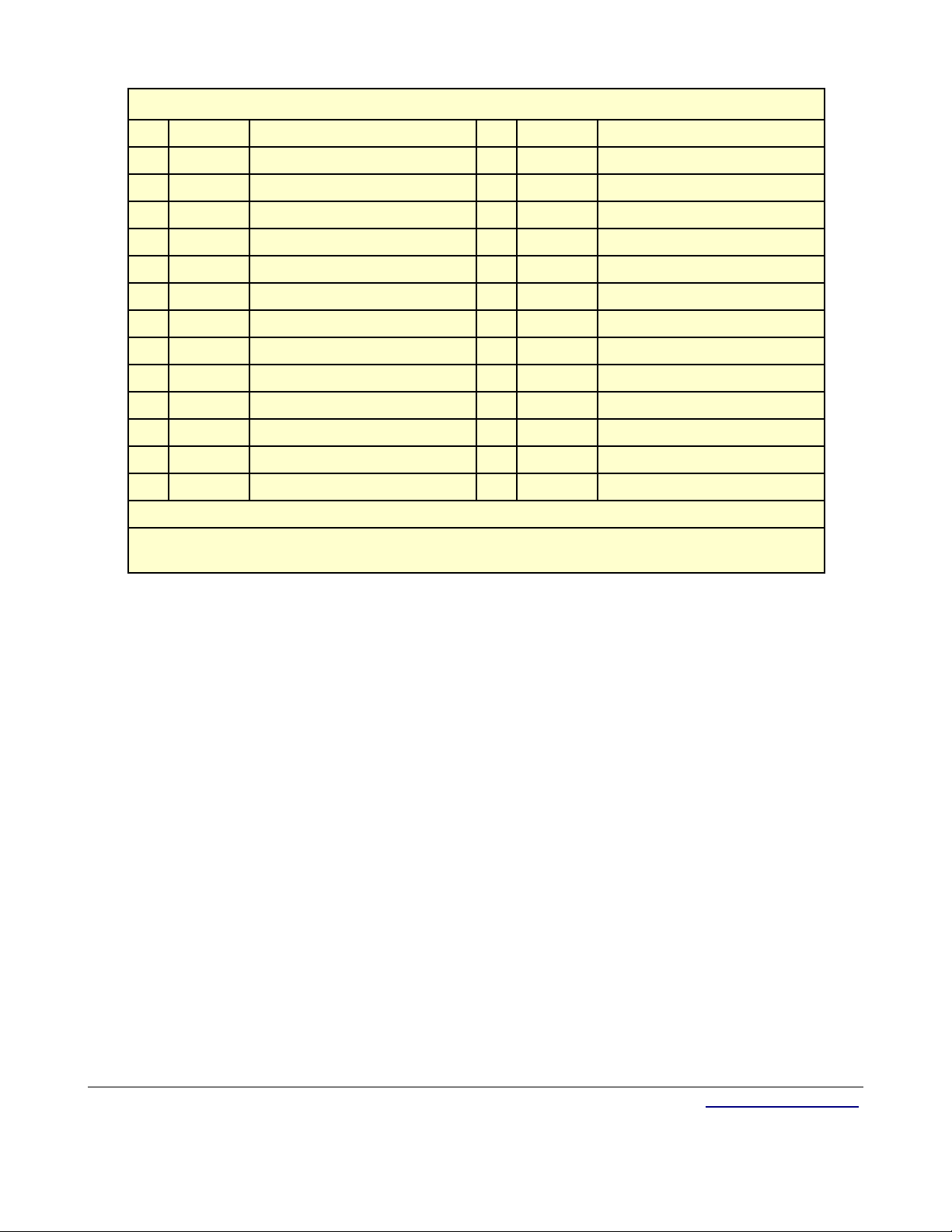

J3 VG 96-pin external expansion connector

PIN FPGA

IO

A7 N2 VG96_IO9 B7 N1 VG96_IO10 C7 N4 VG96_IO11

A6 P2 VG96_IO6 B6 P1 VG96_IO7 C6 N3 VG96_IO8

A5 T2 VG96_IO3 B5 T1 VG96_IO4 C5 P4 VG96_IO5

A4 U2 VG96_IO0 B4 U1 VG96_IO1 C4 P3 VG96_IO2

A3 -- VCCO_IO B3 -- VCCO_IO C3 -- VCCO_IO

A2 -- GND B2 -- GND C2 -- GND

A1 -- 5.0V_EXT B1 -- 5.0V_EXT C1 -- 5.0V_EXT

* GCLK

Comment PIN FPGA

IO

Comment PIN FPGA

IO

Comment

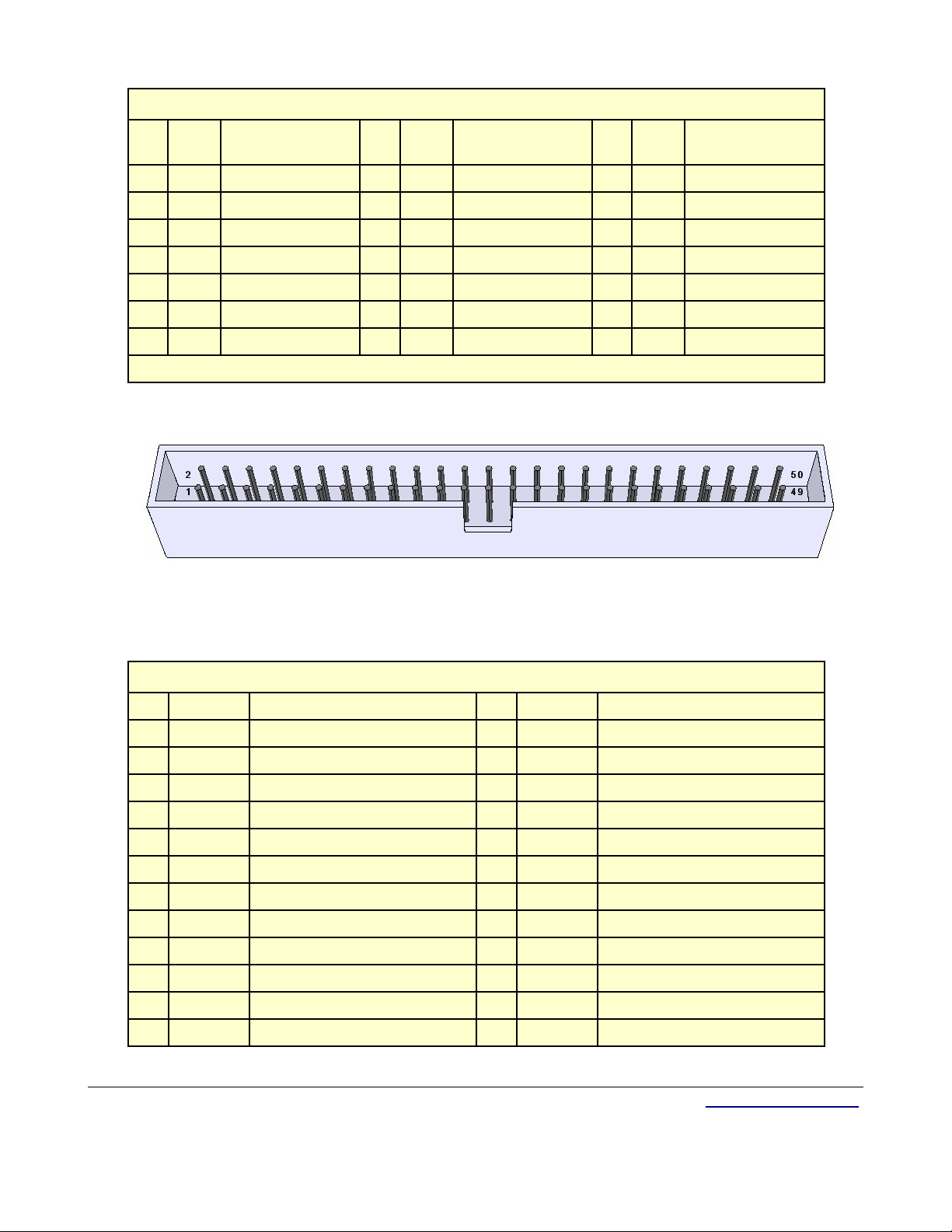

Figure 6: IDC 2x25-Pin external expansion connector J4

J4 IDC 2x25-Pin external expansion connector

PIN FPGA IO Comment PIN FPGA IO Comment

1 -- VCCO_IO 2 -- GND

3 C5 ADD_IO0 4 A5 ADD_IO1

5 C7 ADD_IO2 6 A7 ADD_IO3

7 -- GND 8 -- GND

9 B2 ADD_IO4 10 A2 ADD_IO5

11 B3 ADD_IO6 12 A3 ADD_IO7

13 B4 ADD_IO8 14 A4 ADD_IO9

15 B6 ADD_IO10 16 A6 ADD_IO11

17 -- GND 18 -- GND

19 B8 ADD_IO12 20 A8 ADD_IO13

21 B9 ADD_IO14* 22 A9 ADD_IO15*

23 -- GND 24 -- GND

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -15- preliminary

J4 IDC 2x25-Pin external expansion connector

PIN FPGA IO Comment PIN FPGA IO Comment

25 B11 ADD_IO16 26 A11 ADD_IO17

27 B12 ADD_IO18 28 A12 ADD_IO19

29 B14 ADD_IO20 30 A14 ADD_IO21

31 B16 ADD_IO22 32 A16 ADD_IO23

33 -- GND 34 -- GND

35 C10 ADD_IO24* 36 A10 ADD_IO25*

37 D12 ADD_IO26 38 C12 ADD_IO27

39 -- GND 40 -- GND

41 C13 ADD_IO28 42 A13 ADD_IO29

43 D14 ADD_IO30 44 C14 ADD_IO31

45 C15 ADD_IO32 46 A15 ADD_IO33

47 D4 HSWAPEN** 48 -- GND

49 -- VCCO_IO 50 -- GND

* GCLK

** Enable / Disable optional pull-up resistors during configuration. Pulled HIGH via external

4,7 kOhm resistor. Leave unconnected.

! It is strongly recommended to check the appropriate data sheets of SPARTAN-6

devices about special functionality IO like GCLK, HSWAPEN, ...

TM

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -16- preliminary

FPGA design

Cypress FX-2 LP and USB basics

Several data transfer types are defined in USB 2.0 specification. High-speed bulk transfer

is the one and only mode of interest to end users. USB transfers are packet oriented and

have a time framing scheme. USB packets consist of USB protocol and user payload data.

Payload could have a variable length of up to 512 bytes per packet. Packet size is fixed to

the maximum value of 512 bytes for data communication with CESYS USB cards to

achieve highest possible data throughput. USB peripherals could have several logical

channels to the host. The data source/sink for each channel inside the USB peripheral is

called the USB endpoint. Each endpoint can be configured as “IN”- (channel direction:

peripheral => host) or “OUT”-endpoint (channel direction: host => peripheral) from host

side perspective. CESYS USB cards support two endpoints, one for each direction. FX-2

has an integrated USB SIE (Serial Interface Engine) handling USB protocol and

transferring user payload data to the appropriate endpoint. So end users do not have to

care about USB protocol in their own applications. FX-2 endpoints are realized as 2 kB

buffers. These buffers can be accessed over a FIFO-like interface with a 16 bit tristate data

bus by external hardware. External hardware acts as a master, polling FIFO flags, applying

read- and write-strobes and transferring data. Therefore this FX-2 data transfer mechanism

is called “slave FIFO mode”. As already mentioned, all data is transferred in multiples of

512 bytes. External hardware has to ensure, that the data written to IN-endpoint is aligned

to this value, so that data will be transmitted from endpoint buffer to host. The 512 byte

alignment normally causes no restrictions in data streaming applications with endless data

transfers. Maybe it is necessary to fill up endpoint buffer with dummy data, if some kind of

host timeout condition has to be met. Another FX-2 data transfer mechanism is called

“GPIF (General Programmable InterFace) mode”. The GPIF engine inside the FX-2 acts as

a master to endpoint buffers, transferring data and presenting configurable handshake

waveforms to external hardware. CESYS USB card supports “slave FIFO mode” for data

communication only. “GPIF mode” is exclusively used for downloading configuration

bitstreams to FPGA.

Clocking FPGA designs

The 48 MHz SYSCLK oscillator is an onboard clock source for the FPGA. It is used as

interface clock (IFCLK) between FX-2 slave FIFO bus and FPGA I/Os. So this clock source

must be used for data transfers to and from FPGA over USB! Appropriate timing

constraints can be found in “*.ucf”-files of design examples included in delivery.

It is strictly recommended to use a single clock domain whenever possible. Using a fully

synchronous system architecture often results in smaller, less complex and more

performant FPGA designs (compare XilinxTM white paper WP331 “Timing Closure/Coding

Guidelines”).

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -17- preliminary

In FPGA designs with multiple clock domains asynchronous FIFOs have to be used for

transferring data from one clock domain to the other and comprehensive control signals

have to be resynchronized.

Other clock sources can be added internally by using Spartan-6TM onchip digital clock

managers (DCMs) or PLLs or externally by connecting clock sources to other FPGA global

clock inputs. A wide range of clock frequencies can be synthesized with DCMs and PLLs.

For further details on DCMs/PLLs please see “Spartan-6

TM

FPGA Clocking Resources

User Guide UG382”.

FX-2/FPGA s lave FIFO connection

Only the logical behavior of slave FIFO interface is discussed here. For information about

the timing behavior like setup- and hold-times please see FX-2 datasheet.

All flags and control signals are active low (postfix “#”). The whole interface is synchronous

to IFCLK. The asynchronous FIFO transfer mode is not supported.

• SLWR#: FX-2 input, FIFO write-strobe

• SLRD#: FX-2 input, FIFO read-strobe

• SLOE#: FX-2 input, output-enable, activates FX-2 data bus drivers

• PKTEND#: FX-2 input, packet end control signal, causes FX-2 to send data to host at

once, ignoring 512 byte alignment (so called “short packet”)

• Short packets sometimes lead to unpredictable behavior at host side. So CESYS USB

cards do not support short packets! This signal has to be statically set to HIGH! Dummy

data should be added instead of creating short packets. There is normally no lack of

performance by doing this, because transmission of USB packets is bound to a time

framing scheme, regardless of amount of payload data.

• FIFOADR[1:0]: FX-2 input, endpoint buffer addresses, CESYS USB cards use only two

endpoints EP2 (OUT, ADR[1:0] = b”00”) and EP6 (IN, ADR[1:0] = b”10”)

• Switching FIFOADR[1] is enough to select data direction. FIFOADR[0] has to be

statically set to LOW!

• FLAG#-A/-B/-C: FX-2 outputs, A => EP2 “empty” flag, B => EP2 “almost empty” flag,

meaning one 16 bit data word is available, C => EP6 “almost full” flag, meaning one 16

bit data word can still be transmitted to EP6, there is no real “full” flag for EP6, “almost

full” could be used instead

• FD[15:0]: bidirectional tristate data bus

Introduction to example FPGA designs

The CESYS USBS6 Card is shipped with some demonstration FPGA designs to give you

an easy starting point for own development projects. The whole source code is written in

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -18- preliminary

VHDL. Verilog and schematic entry design flows are not supported.

• The design “usbs6_soc” demonstrates the implementation of a system-on-chip (SoC)

with host software access to the peripherals like GPIOs, external Flash Memory, LPDDR

Memory and internal BlockRAM over USB. This design requires a protocol layer over the

simple USB bulk transfer (see CESYS application note “Transfer Protocol for CESYS

USB products” for details), which is already provided by CESYS software API.

• The design “usbs6_bram” is a minimal example for data transfers from and to the FPGA

over USB and can be used to get for familiar with UDK hardware/software interface.

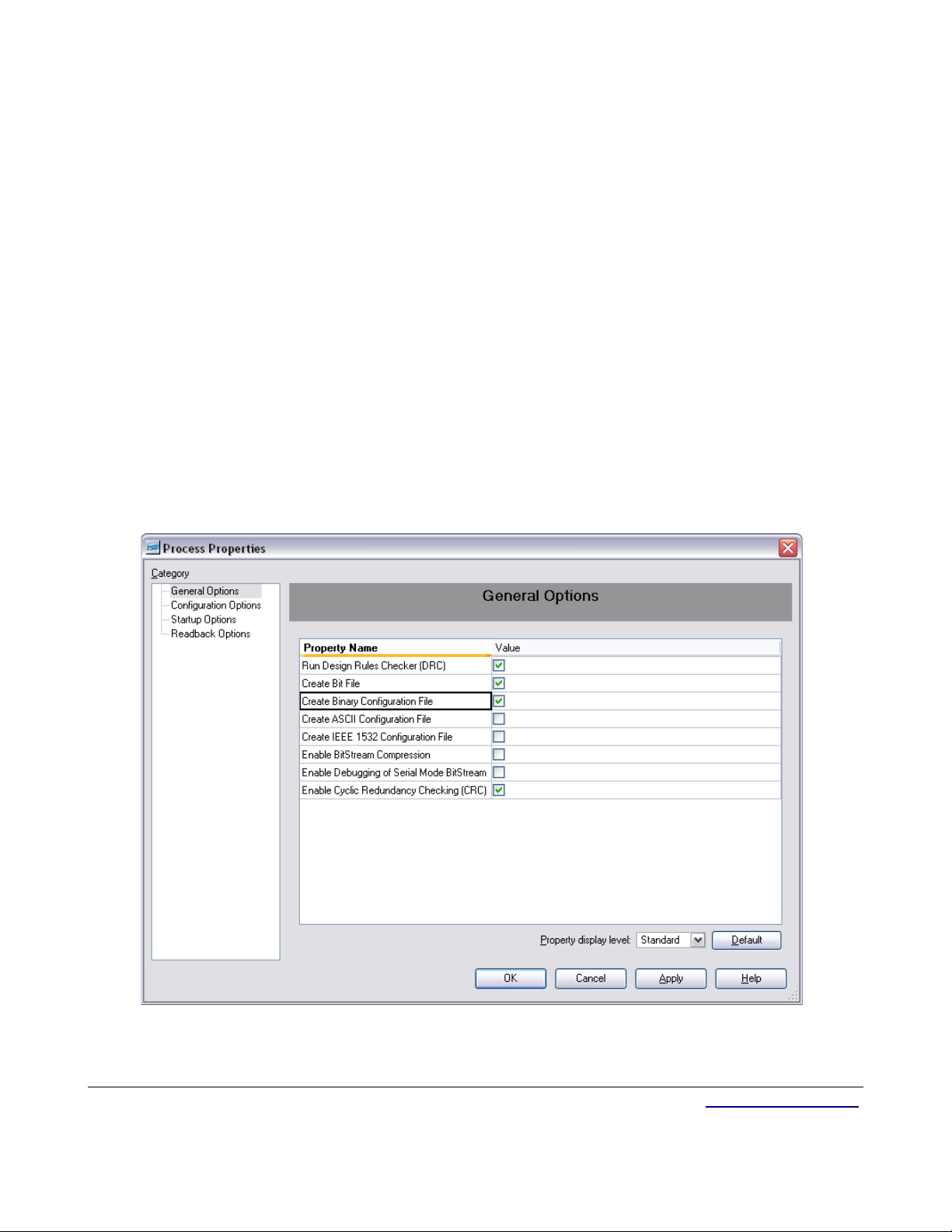

The Spartan-6 XC6SLX16 Device is supported by the free XilinxTM ISE Webpack

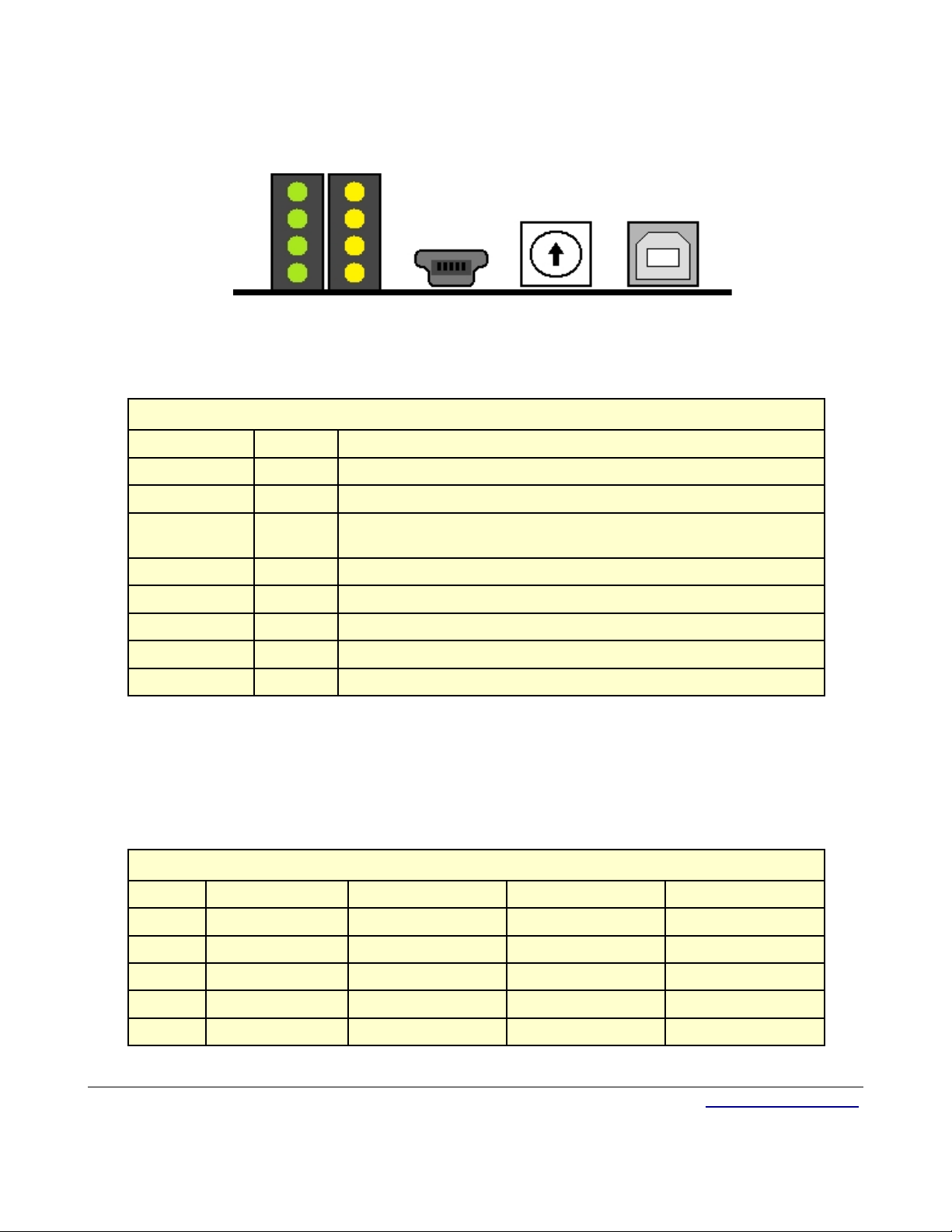

development software. You will have to change some options of the project properties for

own applications.

A bitstream in the “*.bin”-format is needed, if you want to download your FPGA design with

the CESYS software API-functions LoadBIN() and ProgramFPGA(). The generation of

this file is disabled by default in the XilinxTM ISE development environment. Check “create

binary configuration file” at right click “generate programming file”=>properties=>general

options:

Figure 7: ISE Generate Programming File Properties (Gen. Opt.)

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -19- preliminary

After ProgramFPGA() is called and the FPGA design is completely downloaded, the pin

#RESET (note: the prefix # means, that the signal is active low) is automatically pulsed

(HIGH/LOW/HIGH). This signal can be used for resetting the FPGA design. The APIfunction ResetFPGA() can be called to initiate a pulse on #RESET at a user given time.

The following sections will give you a brief introduction about the data transfer from and to

the FPGA over the Cypress FX-2 USB peripheral controller's slave FIFO interface, the

WISHBONE interconnection architecture and the provided peripheral controllers.

CESYS USB cards use only slave FIFO mode for transferring data. For further information

about the FX-2 slave FIFO mode see Cypress FX-2 user manual and datasheet and about

the WISHBONE architecture see specification B.3 (wbspec_b3.pdf).

FPGA source code copyright information

This source code is copyrighted by CESYS GmbH / GERMANY, unless otherwise noted.

FPGA source code license

THIS SOURCECODE IS NOT FREE! IT IS FOR USE TOGETHER WITH THE CESYS

PRODUCTS ONLY! YOU ARE NOT ALLOWED TO MODIFY AND DISTRIBUTE OR USE

IT WITH ANY OTHER HARDWARE, SOFTWARE OR ANY OTHER KIND OF ASIC OR

PROGRAMMABLE LOGIC DESIGN WITHOUT THE EXPLICIT PERMISSION OF THE

COPYRIGHT HOLDER!

Disclaimer of warranty

THIS SOURCECODE IS DISTRIBUTED IN THE HOPE THAT IT WILL BE USEFUL, BUT

THERE IS NO WARRANTY OR SUPPORT FOR THIS SOURCECODE. THE COPYRIGHT

HOLDER PROVIDES THIS SOURCECODE "AS IS" WITHOUT WARRANTY OF ANY

KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE

IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THIS

SOURCECODE IS WITH YOU. SHOULD THIS SOURCECODE PROVE DEFECTIVE,

YOU ASSUME THE COST OF ALL NECESSARY SERVICING, REPAIR OR

CORRECTION.

IN NO EVENT WILL THE COPYRIGHT HOLDER BE LIABLE TO YOU FOR DAMAGES,

INCLUDING ANY GENERAL, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES

ARISING OUT OF THE USE OR INABILITY TO USE THIS SOURCECODE (INCLUDING

BUT NOT LIMITED TO LOSS OF DATA OR DATA BEING RENDERED INACCURATE OR

LOSSES SUSTAINED BY YOU OR THIRD PARTIES OR A FAILURE OF THIS

SOURCECODE TO OPERATE WITH ANY OTHER SOFTWARE-PROGRAMS,

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -20- preliminary

HARDWARE-CIRCUITS OR ANY OTHER KIND OF ASIC OR PROGRAMMABLE LOGIC

FX2

FX2

MCB

MCB

BRAM

BRAM

INTERCONNECTION

INTERCONNECTION

32-Bit SoC

S S

S

Universal Data

Source/Sink

Ext.-Mem.

Access

LPDDR

Slave-FIFO

SPI Multi-I/O

M

S

On-Chip-Bus

Protocol

Engine

UART

UART

Xilinx ®

SIO

Macros

S

GPIO

GPIO

Connectors

LEDs

Hex-Enc.

FLASH

FLASH

Configuration

&

User Flash

Access

0 1 32 4 5 6 7

DESIGN), EVEN IF THE COPYRIGHT HOLDER HAS BEEN ADVISED OF THE

POSSIBILITY OF SUCH DAMAGES.

Design “usbs6_soc”

An on-chip-bus system is implemented in this design. The VHDL source code shows you,

how to build a 32 Bit WISHBONE based shared bus architecture. All devices of the

WISHBONE system support only SINGLE READ / WRITE Cycles. Files and modules

having something to do with the WISHBONE system are labeled with the prefix “wb_”. The

WISHBONE master is labeled with the additional prefix “ma_” and the slaves are labeled

with “sl_”. There is a package for each module with the additional postfix “_pkg”. It contains

the appropriate VHDL component declaration / interface description as well as public

constants like register address offsets.

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -21- preliminary

Figure 8: WISHBONE system overview

Files and modules

src/wishbone_pkg.vhd:

A package containing datatypes, constants, and components needed for the WISHBONE

system. There are VHDL subroutines for a WISHBONE master bus functional model

(BFM), too. These can be used for behavioral simulation purposes.

src/usbs6_soc_top.vhd:

This is the top level entity of the design. The WISHBONE components are instantiated

here.

src/wb_intercon.vhd:

All WISHBONE devices are connected to this shared bus interconnection logic. Some

MSBs of the address are used to select the appropriate slave.

src/wb_ma_fx2.vhd:

This is the entity of the WISHBONE master, which converts the CESYS USB protocol into

one or more 32 Bit single read/write WISHBONE cycles. The low level FX-2 slave FIFO

controller (fx2_slfifo_ctrl.vhd) is used and 16/32 bit data width conversion is done by using

special FIFOs (sfifo_hd_a1Kx18b0K5x36.vhd).

src/wb_sl_bram.vhd:

A internal BlockRAM is instantiated here and simply connected to the WISHBONE

architecture. It can be used for testing address oriented data transactions over USB.

src/wb_sl_gpio.vhd:

This entity provides up to 256 general purpose I/Os to set and monitor non-timing-critical

internal and external FPGA signals. The I/Os can be accessed as eight ports with 32 bits

each. Every single I/O can be configured as an in- or output.

I/O signals of VG96 connector VG96_IO[80:0] are at port0 – port2, bits[80:0], I/O signals of

add-on connector ADD_IO[33:0] are at port3 – port4, bits[129:96], user LEDs are at port5,

bits[163:160] and hex encoder is at port6, bits[195:192].

Port7 is used for monitoring MCB status signals bit[224] => READ ERROR, bit[225] =>

READ OVERFLOW, bit[226] => WRITE ERROR, bit[227] => WRITE UNDERRUN and

bit[228] => CALIBRATION DONE.

src/wb_sl_flash.vhd:

The module encapsulates the low level FLASH controller flash_ctrl.vhd. The integrated

command register supports the BULK ERASE command, which erases the whole memory

by programming all bits to '1'. In write cycles the bit values can only be changed from '1' to

'0'. That means, that it is not allowed to have a write access to the same address twice

without erasing the whole flash before. The read access is as simple as reading from any

other WISHBONE device. Please see the SPI-FLASH data sheet for details on

programming and erasing. There are two instances of this module. One is used for

USBS6 / C1030-5510 http://www.cesys.com/

User Doc V0.3 -22- preliminary

Loading...

Loading...