A

1 1

B

C

D

E

Compal Confidential

2 2

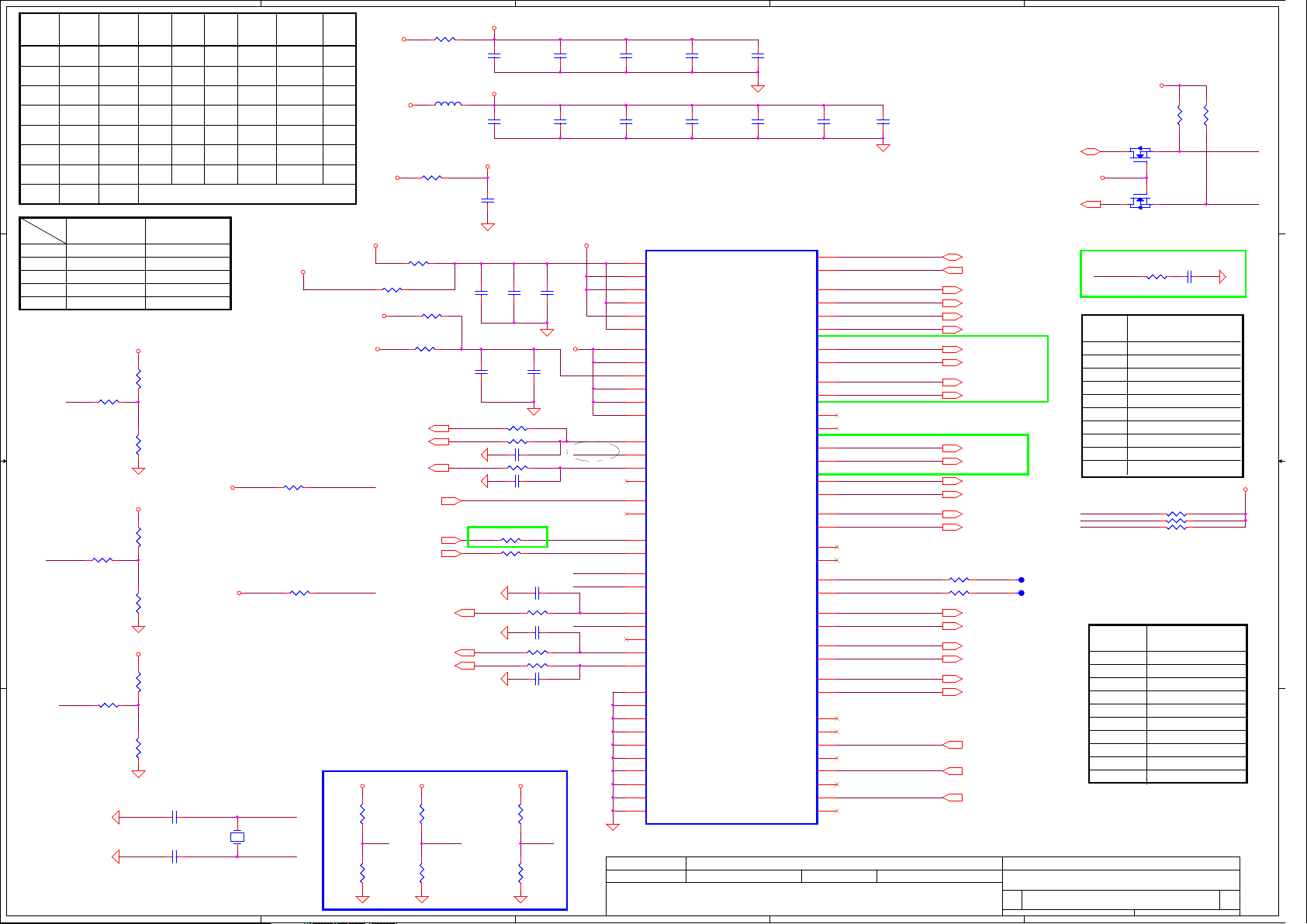

Cougar 2.0

Schematics Document

Intel Cedar Trail Processor/ Tiger point

3 3

2011-11-07

LA-6858P REV:1.0

4 4

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/ 27 2011/6/2 7

2010/06/ 27 2011/6/2 7

2010/06/ 27 2011/6/2 7

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

QBU00

QBU00

QBU00

1 38Monday, November 07, 2 011

1 38Monday, November 07, 2 011

1 38Monday, November 07, 2 011

E

0.3

0.3

0.3

A

B

C

D

E

Compal Confidential

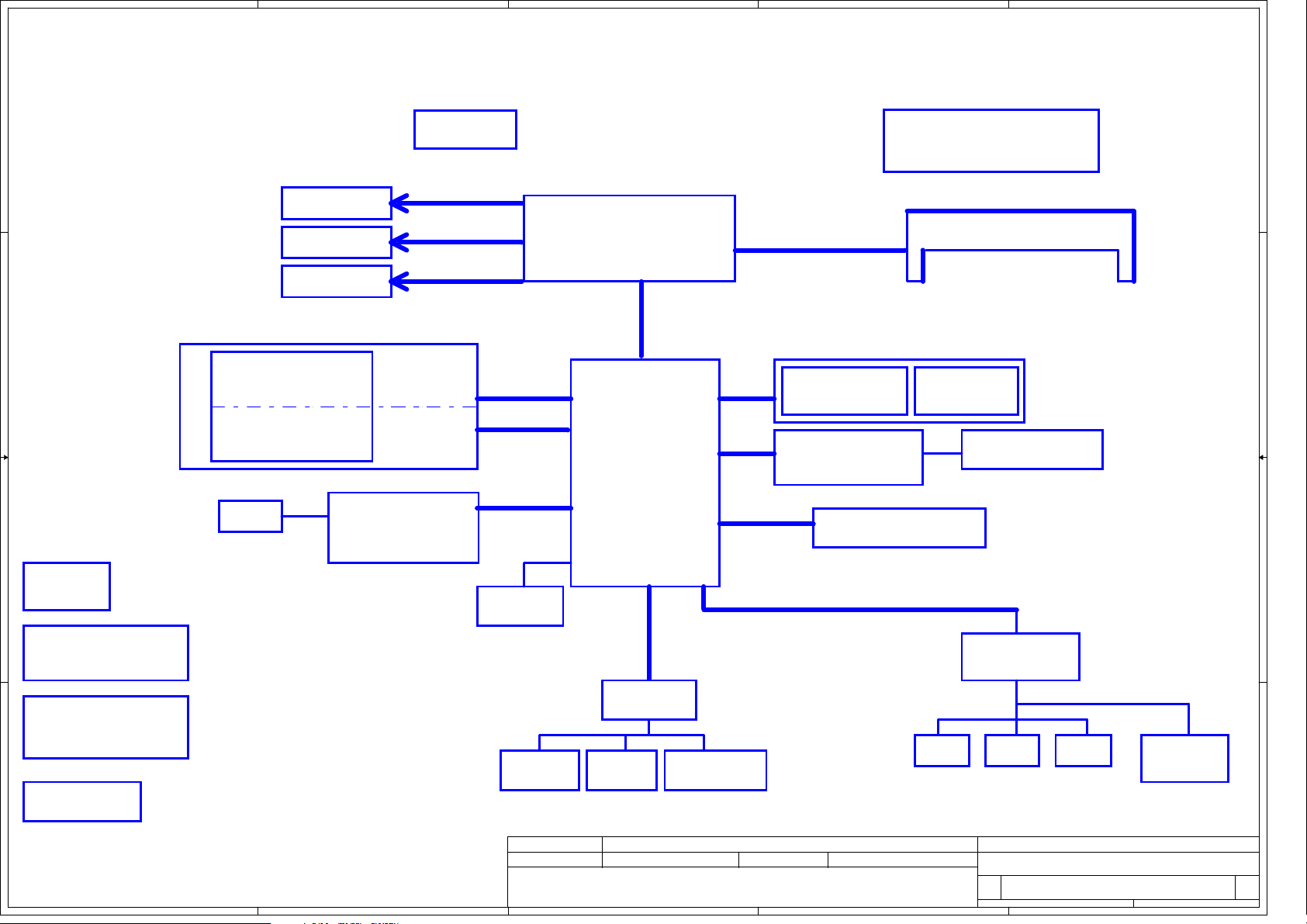

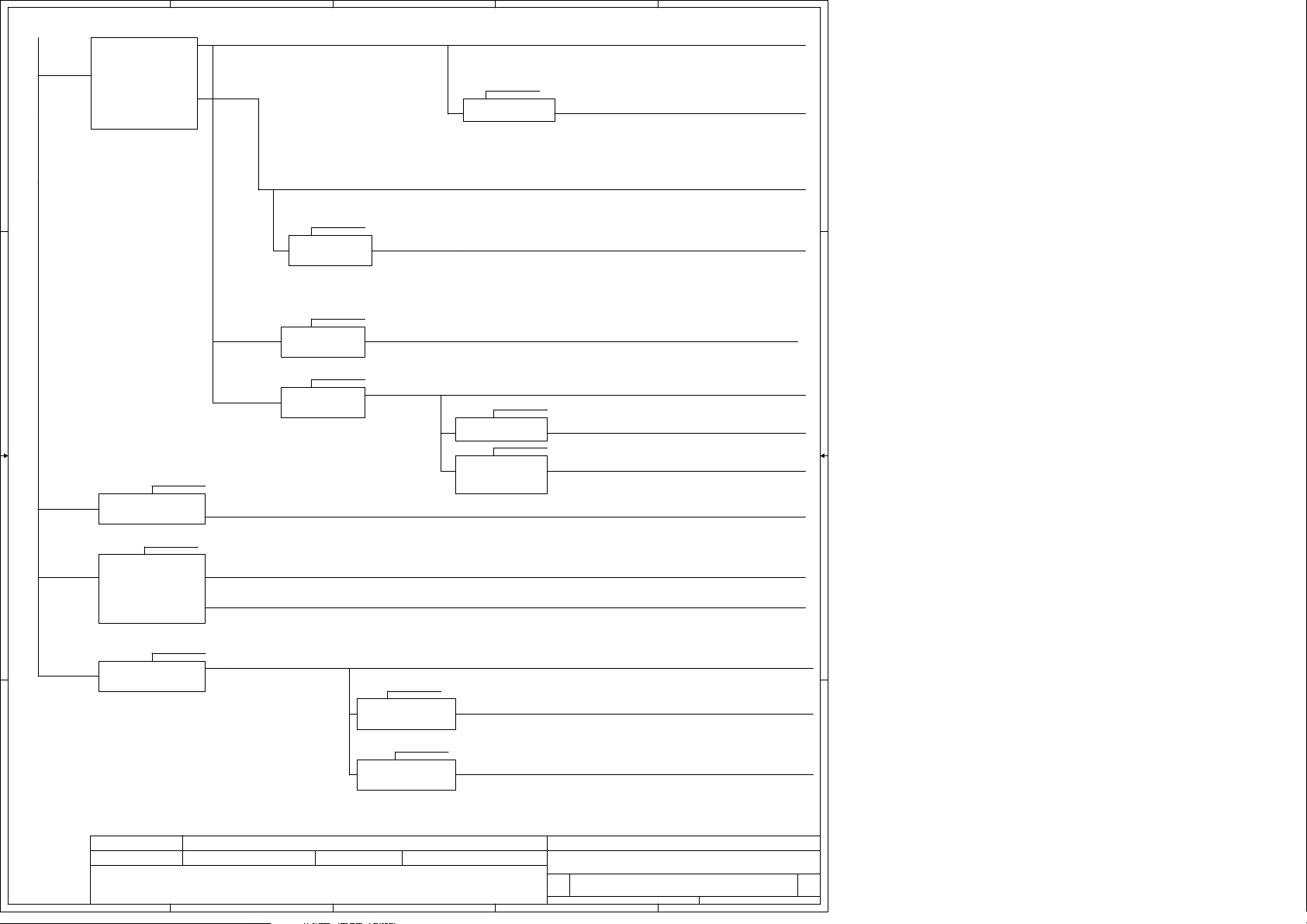

Model Name : Cougar 2.0

Project Code : QBU00

1 1

Fan Control

page 26

Low Power Clock Generator

RTM890N-397

page 9

CRT Conn.

page 15

HDMI Conn.

page 16

LED Conn.

page 17

2 2

RGB

HDMI

LVDS

ONE CHANNEL

Intel Cedarview 2 Core

1.86GHz (6.5W)

(22x22mm)

DMI x 2

page 6,7,8

Memory BUS(DDRIII)

1.5V DDRIII 1066MHz

204pin DDRIII-SO-DIMM

page 10

PCIeMini Card

WWAN

PCIeMini Card

WLAN +BT COMBO

3 3

RTC CKT.

page 13

PCIe port 3

USB port 5

page 18

PCIe port 2

page 18

RJ45

page 23

USB port 6

(FULL)

(HALF)

RTL8105E

10/100 LAN

PCIe port 1

page 23

USB

5V 480MHz

PCIe 1x [2]

1.5V 2.5G Hz(250MB/s)

PCIe 1x

1.5V 2.5G Hz(250MB/s)

SPI ROM

2MB

page 26

Tiger Pointer

(17x17mm)

page 11,12,13,14

USB

5V 480MHz

USB

5V 480MHz

SATA port 0

5V 1.5GHz(1 50MB/s)

HD Audio

USB Conn X3

USB port 0,1,4

page 19

Card Reader

RTL5137

USB port 3

SATA HDD

3.3V 24.576MHz/48Mhz

page 24

Int. Camera

USB port 7

page 17

Card Reader Conn.

page 20

page 24

DC/DC Interface CKT.

page 28

3.3V 33 MHz

LPC BUS

HDA Codec

ALC269

page 21

ENE KB930 E0

Power Circuit DC/DC

page 29~35

Touch Pad

page 27

4 4

Power/B

page 27

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Int.KBD

page 27

page 25

SPI ROM 128KB

page 26

Compal Secret Data

Compal Secret Data

2010/06/ 27 2011/6/2 7

2010/06/ 27 2011/6/2 7

2010/06/ 27 2011/6/2 7

C

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Int.

page 21 page 22 page 22 page 22

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

HP CONN SPK CONNMIC CONNMIC CONN

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

QBU00

QBU00

QBU00

(10A 1X) (10B 2X)

2 38Wednesd ay, June 29, 20 11

2 38Wednesd ay, June 29, 20 11

2 38Wednesd ay, June 29, 20 11

E

0.3

0.3

0.3

A

B

C

D

E

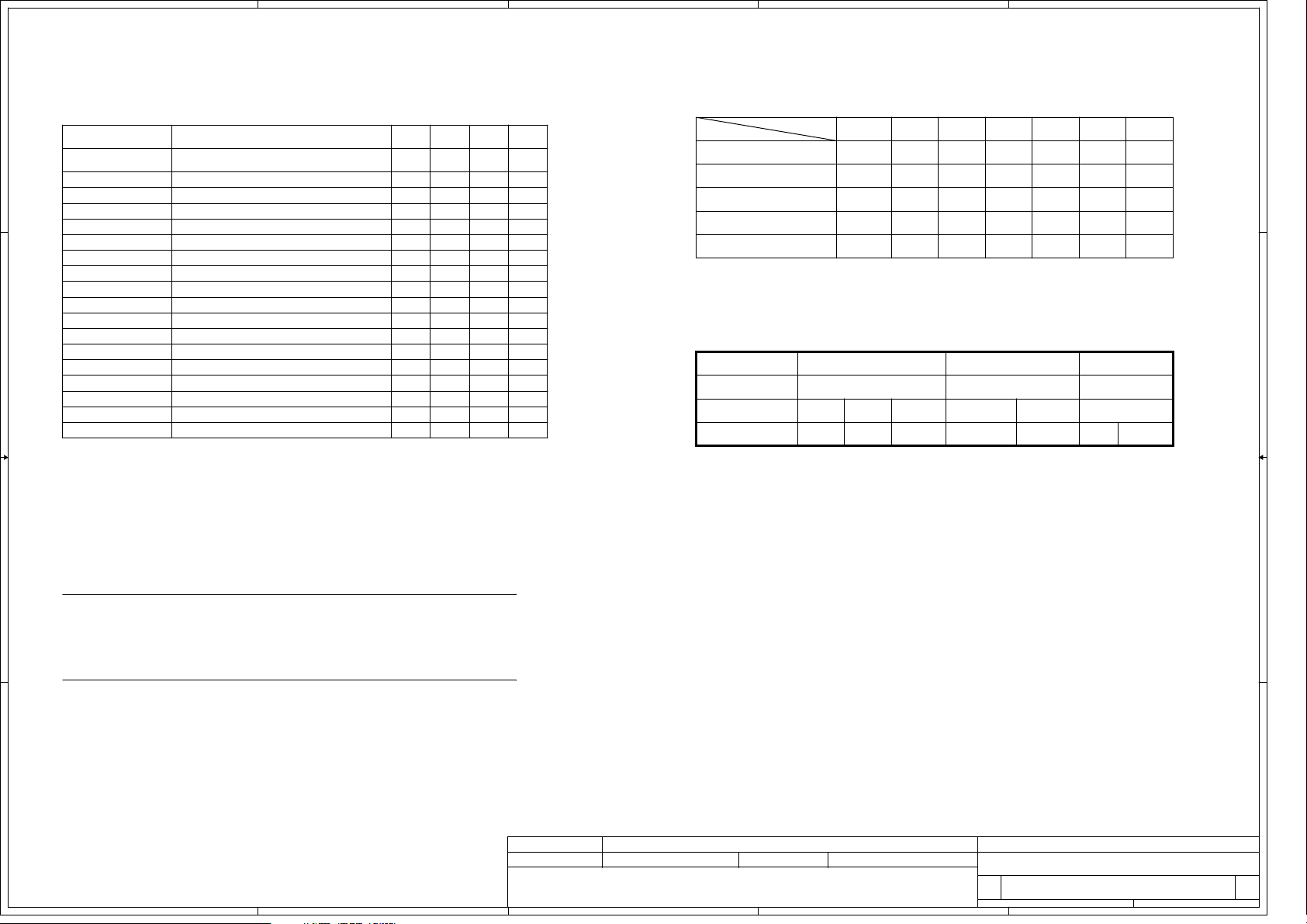

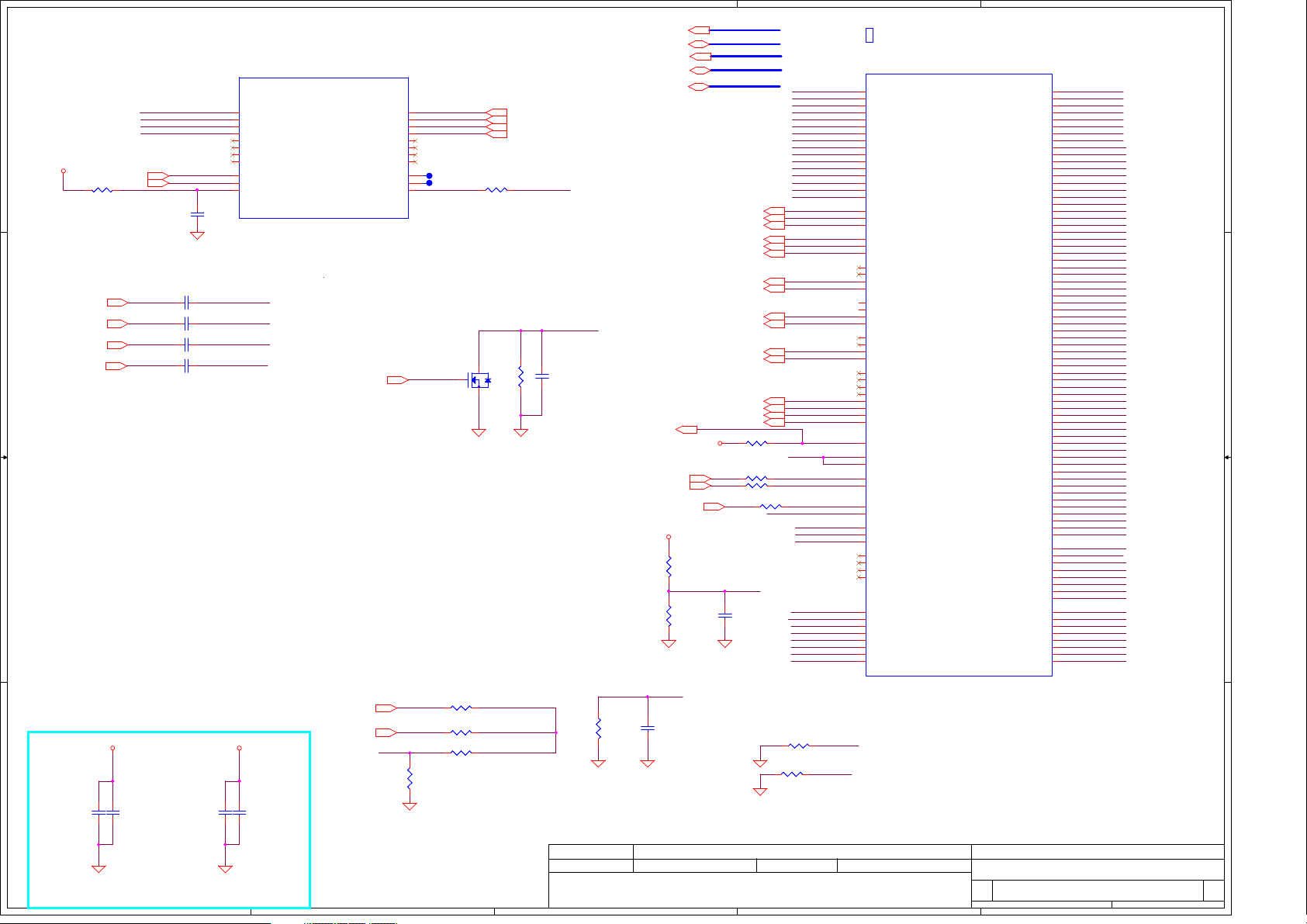

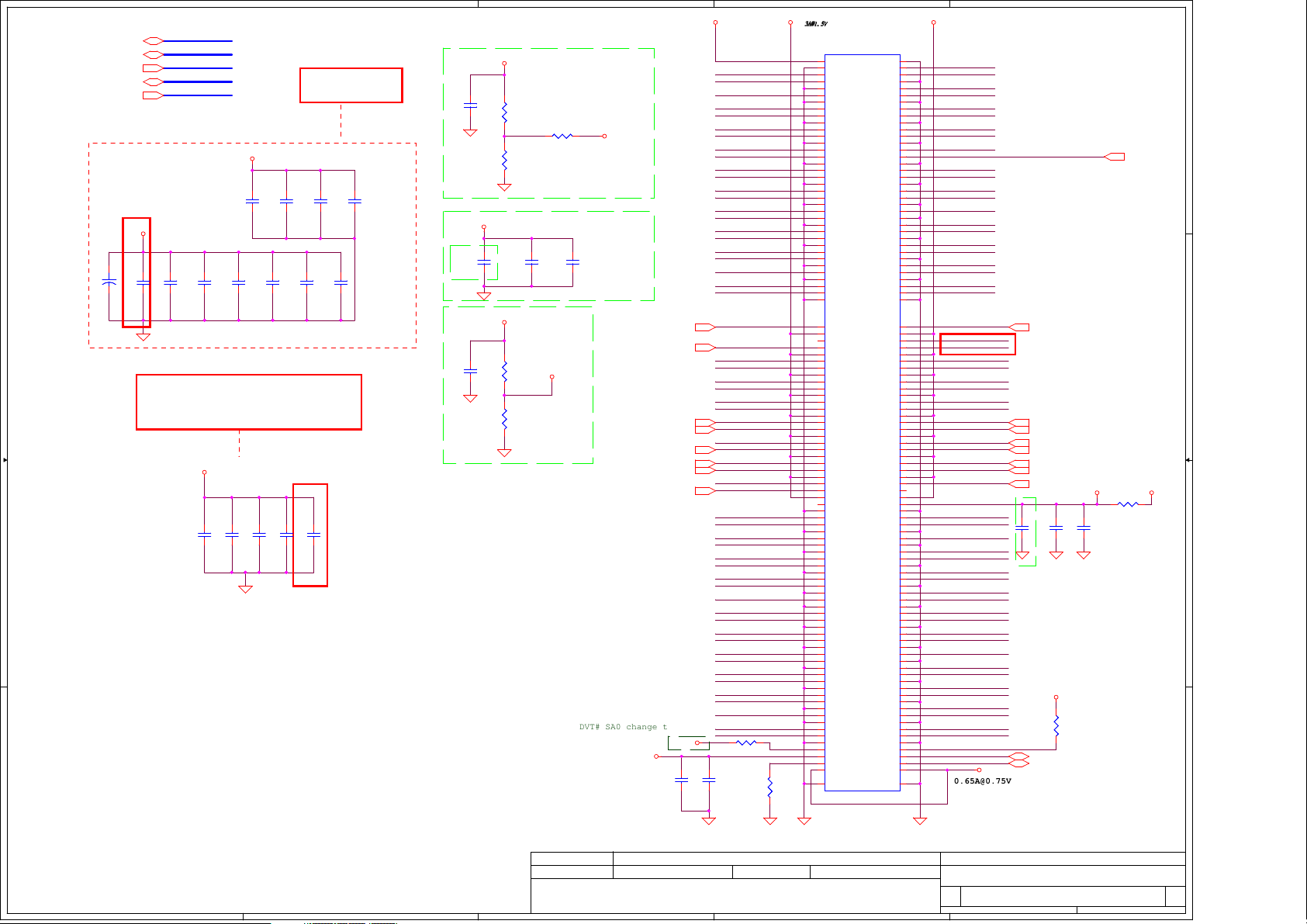

Voltage Rails

1 1

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON

ON

ON

G3

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON

Power Plane

VIN

B+

+CPU_CORE

Description

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

+GFX_CORE GFX support voltage

+0.75VS

+1.05VS

+1.5VS

+1.5V

+1.8VS

+3VALW

0.75V switched power rail for DDR terminator

VCCP switched power rail

1.5V switched power rail

1.5V power rail for DDR

1.8VS switched power rail

3.3V always on power rail

+3V_LAN 3.3V power rail for LAN

2 2

+3VS

+5VALW

+5VS

+VSB

+3V_WLAN

3.3V power rail for LAN

3.3V switched power rail

5V always on power rail

5V switched power rail

VSB always on power rail

+RTCVCC RTC power

+3VS_PRIME 3.3V power rail for CPU and PCH

S1 S3 S5

ON ON ON

ON ON ON ON

ON

OFF

ON

OFF OFF

ON

OFF

ON

OFF OFF

ON

OFF OFF

ON

ON

ON

OFF

ONON ON

ON

ON

ON

OFF

ON

OFF

ON

ON

OFF OFFONOFF

ON

ON

ON

ON

OFF OFF OFF

ON

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

BTO Option Table

Function

description

explain

BTO

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

SIGNAL

Mini PCI-E SLOT

Wi-Fi WWAN

WLAN@

SLP_S3#

SLP_S4#

SLP_S5#

HIGH HIGH HIGH

HIGH

LOW

LOW LOW

LOWLOW

WWAN@3G3G@

+VALW

HIGHHIGHHIGH

ON

ON

HIGH

HIGH

LOW

ON

ON

ON

Display

CRT HDMI

CRT@ HDMI@

+V +VS Clock

ON

ON

ON

OFF

OFF

ON

OFF

OFF

OFF

ONON

LOW

OFF

OFF

OFF

Clock gen

Tpye

low@ normal@

3 3

EC SM Bus1 address

Device

Smart Batte ry

Address

EC SM Bus2 address

Device

EMC1402

Address

1001 010X b0001 011X b

NM10 SM Bus address

Device

Clock Generator

(SLG8SP556VTR)

DDR DIMMA

WWAN/WLAN

4 4

A

Address

1101 001Xb

1010 000Xb

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/ 27 2011/6/2 7

2010/06/ 27 2011/6/2 7

2010/06/ 27 2011/6/2 7

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

QBU00

QBU00

QBU00

3 38Wednesd ay, June 29, 20 11

3 38Wednesd ay, June 29, 20 11

3 38Wednesd ay, June 29, 20 11

E

0.3

0.3

0.3

5

D D

C C

B B

4

3

2

1

A A

5

4

Security Classification

Security Classification

Security Classification

2010/06/27 2011/6/27

2010/06/27 2011/6/27

Issued Date

Issued Date

Issued Date

THIS SHEET OF EN GINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC . AND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC . AND CONTAINS CONFIDENTIAL

THIS SHEET OF EN GINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC . AND CONTAINS CONFIDENTIAL

AND TRADE SECR ET INFORMATION. THIS SHEET M AY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET M AY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECR ET INFORMATION. THIS SHEET M AY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/27 2011/6/27

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

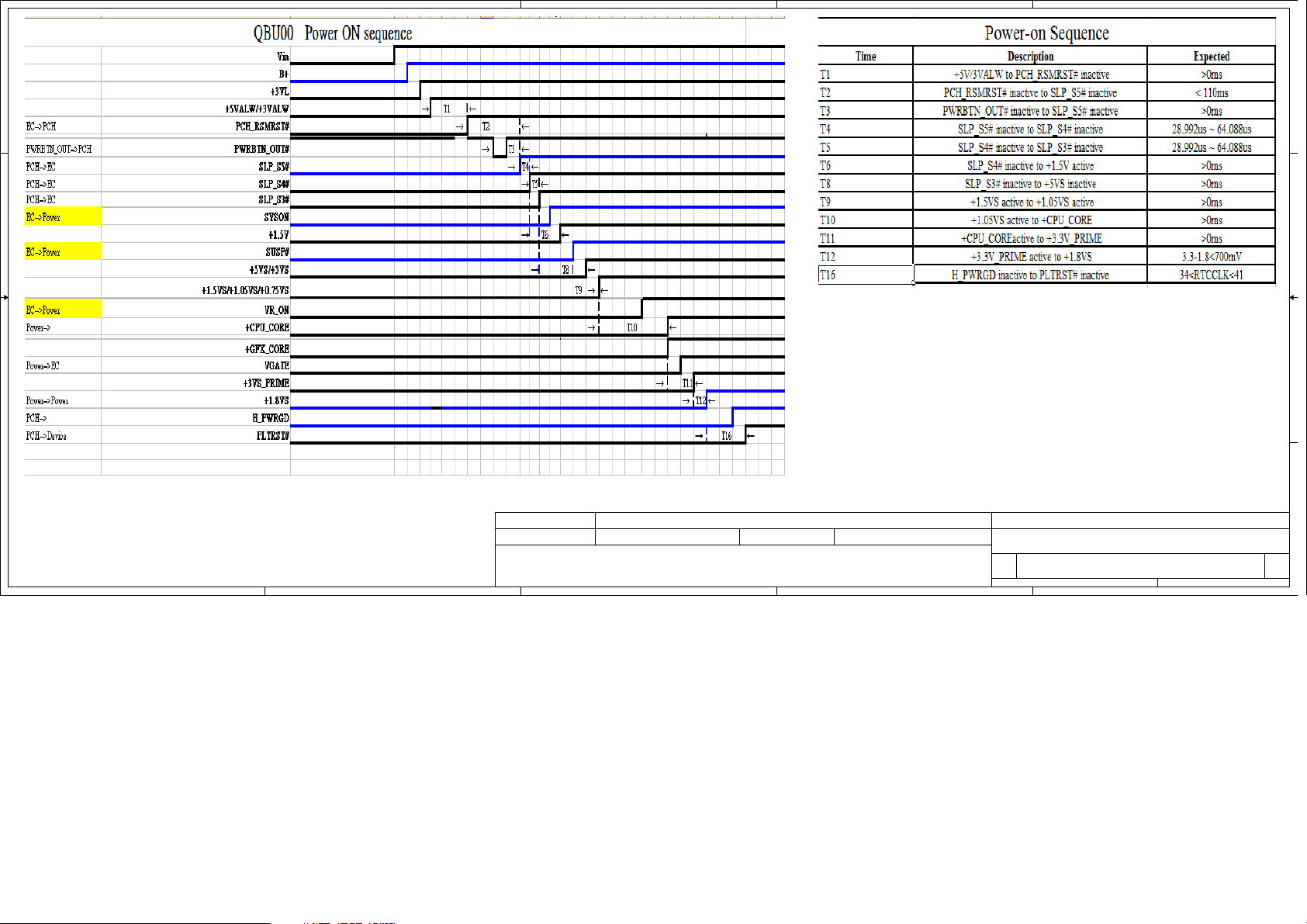

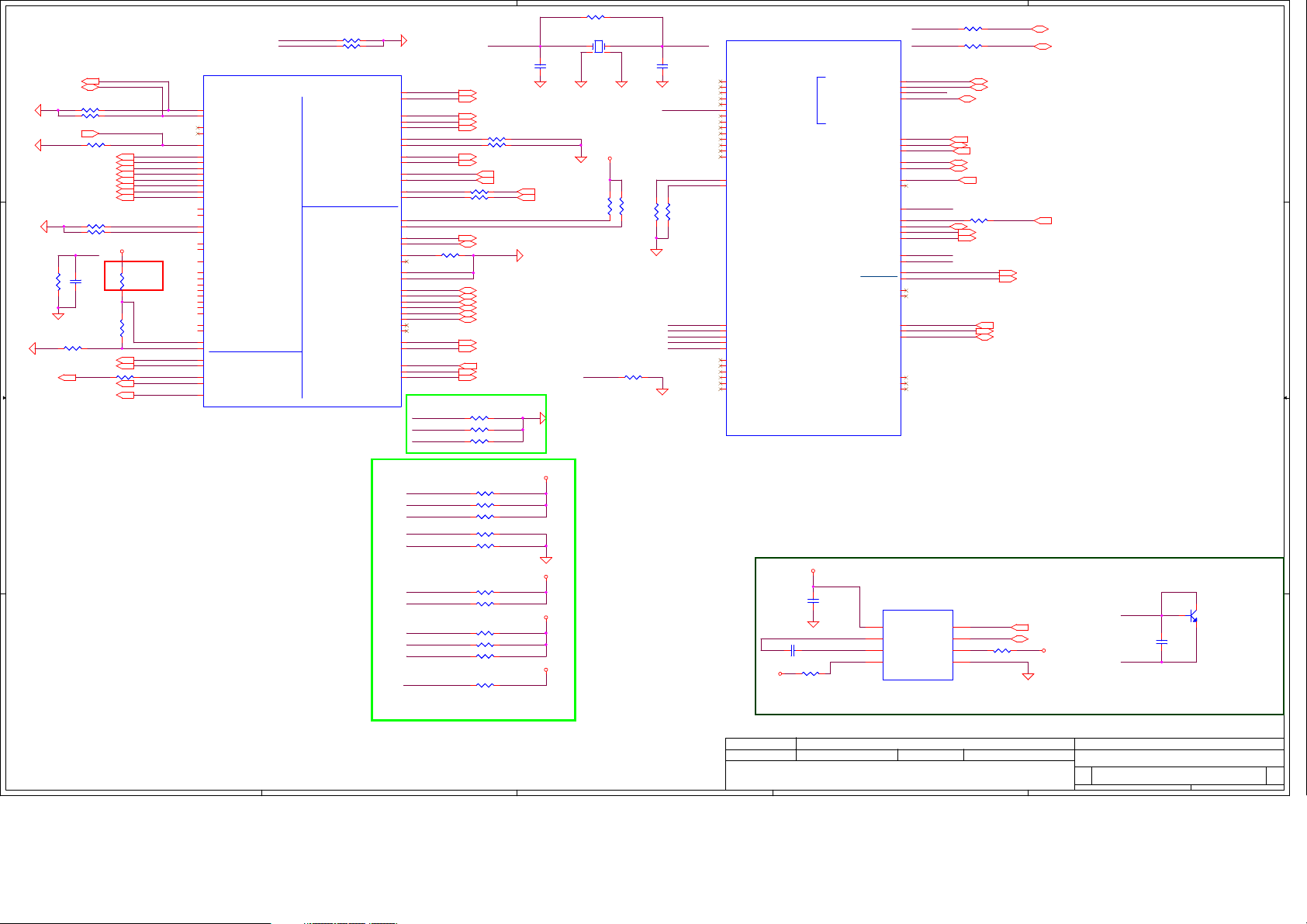

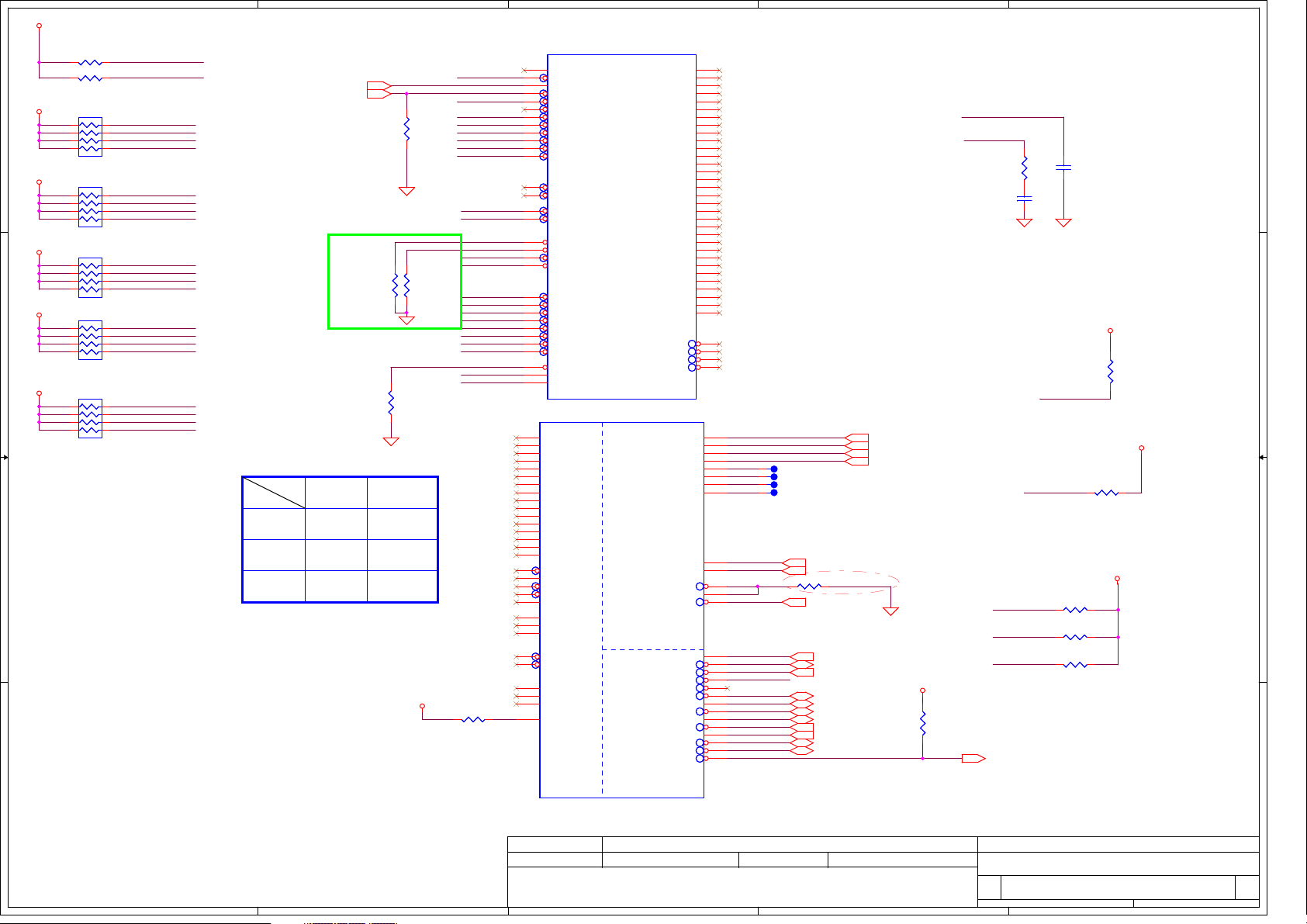

Power sequence

Power sequence

Power sequence

QBU00

QBU00

QBU00

4 38Wednesday, J une 29, 2011

4 38Wednesday, J une 29, 2011

4 38Wednesday, J une 29, 2011

1

0.3

0.3

0.3

DESIGN CURRENT 250mA

B+

5

4

Cougar Power Map

Ipeak=6.97A, Imax=4.88A

3

2

DESIGN CURRENT 522mA

1

+3VALWP +-5%

** The SW just is reserved.

TPS51125ARGER

D D

The power passes by jump or

0-ohm resistor.

** P-CHANNEL

AO3413

WOL_EN#

DESIGN CURRENT 300mA

+3V_LAN

Ipeak=3.98A, Imax=2.8A

DESIGN CURRENT 3010mA

+5VALWP +-5%

SUSP

N-CHANNEL

SI7326DN

DESIGN CURRENT 2286mA

+5VS

VGATE

C C

APL5930KA

DESIGN CURRENT 151mA

SUSP

N-CHANNEL

SI7326DN

P-CHANNEL

AO3413

ENVDD

DESIGN CURRENT 5586mA

DESIGN CURRENT 2000mA

+1.8VS

+3VS

+LCD_VDD

VGATE#

SUSP#

SY8033BDBC +1.05VSP +-5%

Ipeak=1.308A, Imax=4A

SI7326DN

N-CHANNEL

DESIGN CURRENT 294mA

DESIGN CURRENT 3489mA

+3VS_PRIME

VR_ON

B B

Imax=3.5A

RT8165BGQW

DESIGN CURRENT 4500mA

DESIGN CURRENT 2000mA

+CPU_COREP

+GFX_COREP

SYSON

G5603RU1U

Ipeak=19.6A, Imax=13.72A

SI7326DN

DESIGN CURRENT 2270mA

SUSP#

DESIGN CURRENT 2112mA

+1.5VP +-5%

+1.5VSP

SUSP

QBU00

QBU00

QBU00

+0.75VSP

5 38Wednesday, June 29, 2011

5 38Wednesday, June 29, 2011

5 38Wednesday, June 29, 2011

1

0.3

0.3

0.3

G2992F1U

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF CO MPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF CO MPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF CO MPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COM PETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

5

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

4

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

3

DESIGN CURRENT 500mA

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Power tree

Power tree

Power tree

2

5

U1A

N2600@

U1A

N2600@

CEDARVIEW

CEDARVIEW

REV = 1.10

DMI_RXP0_C

D D

+1.5VS

CLK_CPU_EXP<9>

CLK_CPU_EXP#<9>

R973 0_0402_5%R973 0_0402_5%

+1.5V pull up must be placed

within 500 mils from Cedarview

DMI_RXP0<12>

DMI_RXN0<12>

C C

B B

A A

DMI_RXP1<12>

DMI_RXN1<12>

C203

C203

68P_0402_50V8J

68P_0402_50V8J

DMI_RXN0_C

DMI_RXP1_C

DMI_RXN1_C

C948

C948

C949

C949

C950

C950

C951

C951

DMI_REF1P5

1 2

1 2

1 2

1 2

68P_0402_50V8J

68P_0402_50V8J

12

+5VALW +1.5V

1

1

C1050

C1050

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

2

L3

L2

M3

M2

N2

N1

P2

P3

N9

N8

T2

1

C1088

C1088

2

1U_0402_6.3V6K

1U_0402_6.3V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

0.1U_0402_10V6K

1

C204

C204

2

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

DMI_REFCLKP

DMI_REFCLKN

DMI_REF1P5

QB0Z B2 1.6G

QB0Z B2 1.6G

DMI_RXP0_C

DMI_RXN0_C

DMI_RXP1_C

DMI_RXN1_C

1

C1065

C1065

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

REV = 1.10

DMI

DMI

1 OF 6

1 OF 6

XDP_DBREST#<7>

PCH_POK< 13>

4

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

RSVD_TP_R8

RSVD_TP_R7

DMI_RCOMP

SYSON#<28>

?

?

1 2

K6

K5

L5

L6

L9

L8

N5

N6

R8

T1T1

R7

T2T2

T1

SYSON#

2

G

G

R966

R966

@

@

1 2

R967 0_0402_5%R967 0_0402_5%

1 2

1 2

R968

R968

R969

R969

10K_0402_5%

10K_0402_5%

DMI_TXP0 <12>

DMI_TXN0 <12>

DMI_TXP1 <12>

DMI_TXN1 <12>

R493

R493

7.5K_0402_5%

7.5K_0402_5%

Q37

Q37

2N7002_SOT23

2N7002_SOT23

PCH_POK_RDRAM_VR_PWR GD

DMI_REF1P5DMI_IRCOMP

SMPWROK

1

2

1 2

R880 10K_0402_5%@R880 10K_0402_5%

C1063 0.1U_0402_16V4Z@C1063 0.1U_0402_16V4Z

@

@

DDR_DQPU

12

R893

R893

33.2_0402_1%

33.2_0402_1%

1 2

+1.5V pull up must be placed

within 500 mils from Cedarview

13

D

D

S

S

0_0402_5%

0_0402_5%

12.1K_0402_1%

12.1K_0402_1%

3

DDR_A_MA[0..15]<10>

DDR_A_DQS#[0..7]<10>

DDR_A_DM[0..7]<10>

DDR_A_DQS[0..7]<10>

DDR_A_D[0..63]<10>

DRAMRST#<10>

CLK_CPU_MPLL_C<9>

CLK_CPU_MPLL#_C<9>

SM_PWROK<33>

+1.5V

12

R500

R500

1K_0402_1%

1K_0402_1%

12

R504

R504

1K_0402_1%

1K_0402_1%

1

@

@

C952 0.01U_0402_16V7K

C952 0.01U_0402_16V7K

2

DDR_A_WE#<10>

DDR_A_CAS#<10>

DDR_A_RAS#<10>

DDR_A_BS0<10>

DDR_A_BS1<10>

DDR_A_BS2<10>

DDR_CS2#<10>

DDR_CS3#<10>

DDR_CKE2<10>

DDR_CKE3<10>

M_ODT2<10>

M_ODT3<10>

M_CLK_DDR2<10>

M_CLK_DDR#2<10>

M_CLK_DDR3<10>

M_CLK_DDR#3<10>

R878

@R878

@

1 2

+1.5V

10K_0402_5%

10K_0402_5%

R883 0_0402_5%R883 0_0402_5%

1 2

1 2

R892 0_0402_5%R892 0_0402_5%

0_0402_5%

0_0402_5%

R881

R881

1 2

DDR_VREF

1

C953

C953

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_WE#

DDR_A_CAS#

DDR_A_RAS#

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_CS2#

DDR_CS3#

DDR_CKE2

DDR_CKE3

M_ODT2

M_ODT3

M_CLK_DDR2

M_CLK_DDR#2

M_CLK_DDR3

M_CLK_DDR#3

DDR_VREF

CLK_CPU_MPLL

CLK_CPU_MPLL#

SMPWROK

DRAM_VR_PWR GD

DDR_ODTPU

DDR_CMDPU

DDR_DQPU

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

R553

R553

22.6_0402_1%

22.6_0402_1%

R503

R503

DDR_ODTPU

1 2

270_0402_1%

270_0402_1%

AK14

AK16

AJ14

AJ16

AK18

AH18

AJ18

AK20

AJ20

AH20

AJ12

AK21

AJ21

AH22

AJ22

AH10

AJ10

AJ11

AK12

AH13

AK22

AH12

AK11

AH23

AJ24

AK24

AH24

AK10

AG15

AF15

AF17

AG17

AD17

AC17

AC15

AD15

AK25

AJ27

AL28

AC19

AB19

AJ26

AJ25

AK27

AB11

AB13

AF19

AG19

AB26

AE30

AB21

AG11

DDR_CMDPU

2

N2800@

N2800@

U1

U1

QB0Y B2 1.86G

QB0Y B2 1.86G

U1B

U1B

DDR3_MA0

DDR3_MA1

DDR3_MA2

DDR3_MA3

DDR3_MA4

DDR3_MA5

DDR3_MA6

DDR3_MA7

DDR3_MA8

DDR3_MA9

DDR3_MA10

DDR3_MA11

DDR3_MA12

AJ8

DDR3_MA13

DDR3_MA14

DDR3_MA15

DDR3_WE#

DDR3_CAS#

DDR3_RAS#

DDR3_BS0

DDR3_BS1

DDR3_BS2

DDR3_CS#0

AH8

DDR3_CS#1

DDR3_CS#2

AK8

DDR3_CS#3

DDR3_CKE0

DDR3_CKE1

DDR3_CKE2

DDR3_CKE3

DDR3_ODT0

AK7

DDR3_ODT1

AL9

DDR3_ODT2

AJ7

DDR3_ODT3

DDR3_CK0

DDR3_CK#0

DDR3_CK1

DDR3_CK#1

DDR3_CK2

DDR3_CK#2

DDR3_CK3

DDR3_CK#3

DDR3_DRAMRST#

DDR3_VREF

DDR3_VREF_NCTF

DDR3_REFP

DDR3_REFN

AA5

DDR3_DRAM_PW ROK

W7

DDR3_VCCA_PW ROK

DDR3_ODTPU

DDR3_CMDPU

DDR3_DQPU

RSVD_TP_AB11

RSVD_TP_AB13

RSVD_TP_AF19

RSVD_TP_AG19

Y28

DDR3_DM0

DDR3_DM1

DDR3_DM2

DDR3_DM3

DDR3_DM4

AG2

DDR3_DM5

AB8

DDR3_DM6

AA3

DDR3_DM7

QB0Z B2 1.6G

QB0Z B2 1.6G

N2600@

N2600@

DDR3

DDR3

CEDARVIEW

CEDARVIEW

?

?

REV = 1.10

REV = 1.10

DDR3_DQ0

DDR3_DQ1

DDR3_DQ2

DDR3_DQ3

DDR3_DQ4

DDR3_DQ5

DDR3_DQ6

DDR3_DQ7

DDR3_DQ8

DDR3_DQ9

DDR3_DQ10

DDR3_DQ11

DDR3_DQ12

DDR3_DQ13

DDR3_DQ14

DDR3_DQ15

DDR3_DQ16

DDR3_DQ17

DDR3_DQ18

DDR3_DQ19

DDR3_DQ20

DDR3_DQ21

DDR3_DQ22

DDR3_DQ23

DDR3_DQ24

DDR3_DQ25

DDR3_DQ26

DDR3_DQ27

DDR3_DQ28

DDR3_DQ29

DDR3_DQ30

DDR3_DQ31

DDR3_DQ32

DDR3_DQ33

DDR3_DQ34

DDR3_DQ35

DDR3_DQ36

DDR3_DQ37

DDR3_DQ38

DDR3_DQ39

DDR3_DQ40

DDR3_DQ41

DDR3_DQ42

DDR3_DQ43

DDR3_DQ44

DDR3_DQ45

DDR3_DQ46

DDR3_DQ47

DDR3_DQ48

DDR3_DQ49

DDR3_DQ50

DDR3_DQ51

DDR3_DQ52

DDR3_DQ53

DDR3_DQ54

DDR3_DQ55

DDR3_DQ56

DDR3_DQ57

DDR3_DQ58

DDR3_DQ59

DDR3_DQ60

DDR3_DQ61

DDR3_DQ62

DDR3_DQ63

DDR3_DQS0

DDR3_DQS1

DDR3_DQS2

DDR3_DQS3

DDR3_DQS4

DDR3_DQS5

DDR3_DQS6

DDR3_DQS7

DDR3_DQS#0

DDR3_DQS#1

DDR3_DQS#2

DDR3_DQS#3

DDR3_DQS#4

DDR3_DQS#5

DDR3_DQS#6

DDR3_DQS#7

1

DDR_A_D0

Y30

DDR_A_D1

Y29

DDR_A_D2

AC30

DDR_A_D3

AC31

DDR_A_D4

W31

DDR_A_D5

W28

DDR_A_D6

AB28

DDR_A_D7

AB30

DDR_A_D8

AA24

DDR_A_D9

AA22

DDR_A_D10

AE27

DDR_A_D11

AE26

DDR_A_D12

AB27

DDR_A_D13

AA25

DDR_A_D14

AD25

DDR_A_D15

AD27

DDR_A_D16

AD29

DDR_A_D17

AE29

DDR_A_D18

AJ30

DDR_A_D19

AK29

DDR_A_D20

AD28

DDR_A_D21

AD30

DDR_A_D22

AG30

DDR_A_D23

AJ29

DDR_A_D24

AE24

DDR_A_D25

AG24

DDR_A_D26

AD22

DDR_A_D27

AC21

DDR_A_D28

AG27

DDR_A_D29

AG25

DDR_A_D30

AG21

DDR_A_D31

AE21

DDR_A_D32

AD13

DDR_A_D33

AD11

DDR_A_D34

AG8

DDR_A_D35

AG7

DDR_A_D36

AG13

DDR_A_D37

AE13

DDR_A_D38

AD10

DDR_A_D39

AF8

DDR_A_D40

AH2

DDR_A_D41

AG3

DDR_A_D42

AD2

DDR_A_D43

AD3

DDR_A_D44

AH4

DDR_A_D45

AK3

DDR_A_D46

AE2

DDR_A_D47

AD4

DDR_A_D48

AD7

DDR_A_D49

AD6

DDR_A_D50

AA6

DDR_A_D51

AB5

DDR_A_D52

AE8

DDR_A_D53

AE5

DDR_A_D54

AB9

DDR_A_D55

AA8

DDR_A_D56

AB2

DDR_A_D57

AB4

DDR_A_D58

W4

DDR_A_D59

V3

DDR_A_D60

AC2

DDR_A_D61

AB3

DDR_A_D62

Y2

DDR_A_D63

W1

DDR_A_DQS0

AA30

DDR_A_DQS1

AB24

DDR_A_DQS2

AF30

DDR_A_DQS3

AE22

DDR_A_DQS4

AG10

DDR_A_DQS5

AF4

DDR_A_DQS6

AB6

DDR_A_DQS7

Y3

DDR_A_DQS#0

AA31

DDR_A_DQS#1

AB25

DDR_A_DQS#2

AF29

DDR_A_DQS#3

AF22

DDR_A_DQS#4

AF10

DDR_A_DQS#5

AF3

DDR_A_DQS#6

AB7

DDR_A_DQS#7

AA2

?2 OF 6

?2 OF 6

2010.07.12 RF request

5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAIN S CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTR ONICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

Cedarview(1/3)

Cedarview(1/3)

Cedarview(1/3)

QBU00

QBU00

QBU00

6 38Wednesday, November 02, 2011

6 38Wednesday, November 02, 2011

6 38Wednesday, November 02, 2011

1

0.3

0.3

0.3

5

GMCH_CRT_DATA

GMCH_CRT_CLK

U1C

N2600@

U1C

H25

J22

C8

B8

H22

G2

G3

F3

F2

D4

C3

B7

A7

H15

J15

F25

G27

D10

C10

D26

E11

F11

J11

H11

F13

E13

J13

K13

J17

H17

E15

F15

H21

F22

E22

F21

E21

N2600@

DDI0_DDC_S CL

DDI0_DDC_S DA

DDI0_AUXP

DDI0_AUXN

DDI0_HPD

DDI0_TXP0

DDI0_TXN0

DDI0_TXP1

DDI0_TXN1

DDI0_TXP2

DDI0_TXN2

DDI0_TXP3

DDI0_TXN3

RSVD_TP_H1 5

RSVD_TP_J1 5

DDI1_DDC_S CL

DDI1_DDC_S DA

DDI1_AUXP

DDI1_AUXN

DDI1_HPD

DDI1_TXP0

DDI1_TXN0

DDI1_TXP1

DDI1_TXN1

DDI1_TXP2

DDI1_TXN2

DDI1_TXP3

DDI1_TXN3

RSVD_TP_J1 7

RSVD_TP_H1 7

BREF1P5V

BREFREXT

AZIL_BCL K

AZIL_SYNC

AZIL_SDI

AZIL_SDO

AZIL_RST#

QB0Z B2 1.6G

QB0Z B2 1.6G

HDMICLK_C<16>

HDMIDAT_C<16>

R903

0_0402_ 5%

0_0402_ 5%

HDA_SDIN1<13>

CRT@

CRT@

R1002 0 _0402_5%CRT@ R100 2 0_0402_ 5%CRT@

1 2

1 2

R1003 0_0402_5%CRT@ R100 3 0_0402_ 5%CRT@

HPD_C<16>

1 2

R1005 0 _0402_5%CRT@ R100 5 0_0402_ 5%CRT@

HDMI_TXD2+<16>

HDMI_TXD2-<16>

HDMI_TXD1+<16>

HDMI_TXD1-<16>

HDMI_TXD0+<16>

HDMI_TXD0-<16>

HDMI_CLK0 +<1 6>

HDMI_CLK0 -<16>

R1009 0 _0402_5%R10 09 0_0402 _5%

1 2

1 2

R1010 0 _0402_5%R10 10 0_0402 _5%

BREF_1.5 V

12

1

C1120

2

1U_0402_6.3V6K

1U_0402_6.3V6K

HDMI@ C1120

HDMI@

HDMI@ R97 4

HDMI@

7.5K_04 02_1%

7.5K_04 02_1%

1 2

R904 0_ 0402_5%

R904 0_ 0402_5%

HDA_BITCLK_ CPU<13>

HDA_SYNC_CP U<13 >

HDA_SDOUT_C PU<13>

HDA_RST#_CP U<1 3>

R974

1 2

+1.5VS

HDMI@

HDMI@

R90533_0402_5 %

R90533_0402_5 %

1 2

12

HDMICLK_C

HDMIDAT_C

HPD_C

HDMI_TXD2+

HDMI_TXD2HDMI_TXD1+

HDMI_TXD1HDMI_TXD0+

HDMI_TXD0HDMI_CLK0 +

HDMI_CLK0 -

HDMI@

HDMI@

R975

R975

0_0402_ 5%

0_0402_ 5%

BREF_1.5 V

BREFREXT

HDA_BITCLK_ CPU

HDA_SYNC_CP U

HDA_SDIN1 _CPU

HDA_SDOUT_C PU

HDA_RST#_CP U

D D

CRT@ R903

CRT@

C C

B B

A A

CEDARVIEW

CEDARVIEW

DDI

DDI

IHDA

IHDA

?

?

REV = 1.10

REV = 1.10

LVDS VGA

LVDS VGA

3 OF 6

3 OF 6

HDMI@

HDMI@

R10060_0402_5 %

R10060_0402_5 %

12

12

R10070_0402_5 %

R10070_0402_5 %

HDMI@

HDMI@

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_IRTN

CRT_IREF

CRT_DDC_DATA

CRT_DDC_CLK

DPL_REFS SCCLKP

DPL_REFS SCCLKN

DPL_REFCL KP

DPL_REFCL KN

LVDS_CTRL_ CLK

LVDS_CTRL_ DATA

LVDS_DDC_ CLK

LVDS_DDC_ DATA

LVDS_IBG

LVDS_VB G

LVDS_VRE FH

LVDS_VRE FL

LVDS_TXP0

LVDS_TXN0

LVDS_TXP1

LVDS_TXN1

LVDS_TXP2

LVDS_TXN2

LVDS_TXP3

LVDS_TXN3

LVDS_CLK P

LVDS_CLK N

PANEL_B KLTCTL

PANEL_B KLTEN

PANEL_V DDEN

?

?

4

18P_040 2_50V8J

18P_040 2_50V8J

D14

C14

GMCH_CRT_R

B12

GMCH_CRT_G

B11

GMCH_CRT_B

C11

CRT_IRTN

D12

DAC_IREF

A13

E29

E27

CPU_SSCDRE FCLK

F17

CPU_SSCDRE FCLK#

E17

CPU_DREFCL K_C

B9

CPU_DREFCL K#_C

A9

LVDS_VTRL _CLK

F28

LVDS_VTRL _DATA

E24

G24

H24

L_IBG

E10

F10

H2

H3

G10

H10

F8

E8

H7

H8

G5

G6

H4

J4

G22

E25

F29

To be placed <250 mils to U1 ball

GMCH_CRT_R

GMCH_CRT_G

GMCH_CRT_B

XDP_TDI_R

XDP_TMS_R

XDP_TDO_R

XDP_TRST#_R

XDP_TCK_R

XDP_PREQ #

XDP_PRDY#

SVID_ALE RT#

SVID_DATA

H_PROCHOT#

XDP_DBRE ST#

R509

R509

2.37K_0 402_1%

2.37K_0 402_1%

ENBKL

R495

R495

R496

R496

R499

R499

R502

R502

R505

R505

R501

R501

R906

R906

GMCH_CRT_HSYNC <15>

GMCH_CRT_VS YNC <15 >

GMCH_CRT_R <15 >

GMCH_CRT_G <15>

GMCH_CRT_B <15>

R1008 0_0402 _5%CRT@ R100 8 0_0402_5%CRT@

R510 681 _0402_1%CRT@ R510 681_040 2_1%CRT@

GMCH_CRT_DATA <1 5>

GMCH_CRT_CLK <1 5>

R897

@R89 7

@

1 2

1 2

R898 0 _0402_5%@ R898 0 _0402_5%@

LCD_EDID_ CLK <17>

LCD_EDID_ DATA <17>

R509 be placed U1.R22

LCD_TXOUT0+ <17 >

LCD_TXOUT0- <1 7>

LCD_TXOUT1+ <17 >

LCD_TXOUT1- <1 7>

LCD_TXOUT2+ <17 >

LCD_TXOUT2- <1 7>

LCD_TXCLK+ <17>

LCD_TXCLK- <17>

GMCH_INVT_P WM <1 7>

ENBKL <25>

GMCH_ENVDD <17>

RV155 150_040 2_1%CR T@ RV155 150_040 2_1%CRT@

1 2

RV156 150_040 2_1%CR T@ RV156 150_040 2_1%CRT@

1 2

RV157 150_040 2_1%CR T@ RV157 150_040 2_1%CRT@

1 2

1 2

51_0402 _5%

51_0402 _5%

1 2

51_0402 _5%

51_0402 _5%

1 2

51_0402 _5%

51_0402 _5%

1 2

51_0402 _5%

51_0402 _5%

1 2

51_0402 _5%

51_0402 _5%

1 2

51_0402 _5%

51_0402 _5%

1 2

51_0402 _5%

51_0402 _5%

R907

R907

75_0402 _5%

75_0402 _5%

R908

R908

110_040 2_1%

110_040 2_1%

R511

R511

100_040 2_5%

100_040 2_5%

R971

R971

1K_0402 _1%

1K_0402 _1%

CPU_SSCDRE FCLK < 9>

CPU_SSCDRE FCLK# <9>

0_0402_ 5%

0_0402_ 5%

12

12

12

12

C1076

C1076

12

R894 1M_040 2_5%R894 1M_040 2_5%

1 2

Y3

Y3

27MHZ_18 PF_X3S027 000FI1H-X

27MHZ_18 PF_X3S027 000FI1H-X

1 3

2 4

1

2

+3VS

CPU_DREFCL K <9>

CPU_DREFCL K# <9>

R899

2.2K_0402_5%

R899

2.2K_0402_5%

1 2

ENBKL

To be placed <500 mils to U1 ball

+1.05VS

+1.8VS

+1.05VS

+3VS

3

R900

R900

2.2K_0402_5%

2.2K_0402_5%

1 2

R901

R901

R517

R517

100K_04 02_5%

100K_04 02_5%

49.9_0402_1%

49.9_0402_1%

CPU_DREFCL K#_CCPU_DREFCL K_C

1

2

H_RSVD_K 26

12

12

C1077

C1077

18P_040 2_50V8J

18P_040 2_50V8J

49.9_0402_1%

49.9_0402_1%

R902

R902

XDP_TCK_R

XDP_TDI_R

XDP_TDO_R

XDP_TMS_R

XDP_TRST#_R

L26

L27

K28

K25

J28

K26

K27

H27

K30

L29

L30

K29

J31

H30

K24

K23

C25

C24

B25

D24

B24

R5

R6

W25

W26

N24

N25

U1D

N2600@

U1D

N2600@

RSVD_L26

STRAP_L27

STRAP_K28

RSVD_K25

RSVD_J28

RSVD_K26

RSVD_K27

RSVD_H27

RSVD_K30

RSVD_L29

RSVD_L30

RSVD_K29

RSVD_J31

RSVD_H30

HV_GPIO_ RCOMP

MV_GPIO_ RCOMP

TCLK

TDI

TDO

TMS

TRST#

RSVD_R5

RSVD_R6

RSVD_W 25

RSVD_W 26

RSVD_N24

RSVD_N25

QB0Z B2 1.6G

QB0Z B2 1.6G

?

?

CEDARVIEW

CEDARVIEW

C969

C969

1 2

1 2

+3VS

R524 10 K_0402_5%R524 10K_0402 _5%

?

?

REV = 1.10

REV = 1.10

SMI#

NMI/LINT10

RSVD_C18

STPCLK#

ICH

ICH

DPRSTP#

DPLSLP#

CPUSLP#

INIT#

INTR/LINT00

THERMTRIP#

RSVD_L11

PBE#

PROCHOT#

PWRGOO D

RESET#

DBR#

PRDY#

PREQ#

HPLL_REF CLK_P

HPLL_REF CLK

CPU

CPU

4 OF 6

4 OF 6

+3VS

1

C968

C968

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2200P_0 402_50V7 K

2200P_0 402_50V7 K

RSVD_E19

RSVD_F19

SVID_ALE RT#

SVID_CLK

SVID_DATA

RSVD_K21

RSVD_L22

RSVD_L24

CPU THERMAL SENSOR

U2

U2

1

H_THERMDA

H_THERMDC

CPU_THERM#

VDD

2

DP

3

DN

THERM#4GND

EMC1402-1 -ACZL-TR_MSOP8

EMC1402-1 -ACZL-TR_MSOP8

Address:0100_1100 EMC1402-1

Address:0100_1101 EMC1402-2

2

B18

C22

C18

D22

C21

B21

B22

A23

D20

B20

L11

C20

A19

D23

G30

E30

H29

G29

J19

K19

E19

F19

B16

D18

C16

K21

L22

L24

H_FERR#_C PU

1 2

R895 0_0 402_5%R895 0_0402_5 %

1 2

R896 0_0 402_5%R896 0_0402_5 %

H_SMI#

H_NMI

H_A20M#_ C

H_STPCLK#

H_DPRSTP#

H_DPSLP#

H_CPUSLP #

H_INIT#

H_INTR

H_THERMTRIP#

H_FERR#_C PU

H_PROCHOT#

H_PWRG D

PLTRST#

XDP_DBRE ST#XDP_DBRE ST#

XDP_PRDY#

XDP_PREQ #

CLK_CPU_ HPLCLK

CLK_CPU_ HPLCLK#

SVID_ALE RT#

SVID_CLK

SVID_DATA

8

SMCLK

7

SMDATA

6

ALERT#

5

H_SMI# <11>

H_NMI <11>

H_STPCLK# <11>

H_DPRSTP# <13>

H_DPSLP# <13>

H_CPUSLP # <11>

H_INIT# <11>

H_INTR <11>

H_THERMTRIP# <11 >

Close to CPU

R958 0 _0402_5%R9 58 0_040 2_5%

1 2

H_PWRG D <13 >

PLTRST# <13,18 ,23>

XDP_DBRE ST# <6>

SVID_ALE RT# <35>

SVID_CLK <35>

SVID_DATA <35>

EC_SMB_C K2

EC_SMB_D A2

R523 10K_040 2_5%R523 1 0K_0402_5 %

H_FERR#

H_A20M#H_A20M#_ C

VR_HOT

H_FERR# <11 >

H_A20M# <11 >

VR_HOT <35>

2011.05.06 Add 0 ohm for XDP signal.

CLK_CPU_ HPLCLK <9>

CLK_CPU_ HPLCLK# <9>

REMOTE Thermal sensor

H_THERMDA

C190

2200P_0 402_50V7 K

2200P_0 402_50V7 K

H_THERMDC

12

EC_SMB_C K2 <25>

EC_SMB_D A2 <25>

+3VS

place near the hottest spot area for

NB & top SODIMM.

Layout Note:

1

C

C

Q8

Q8

2

B

B

MMBT3904W H_SOT323-3

MMBT3904W H_SOT323-3

E

E

3 1

2

@C190

@

1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Custom

Custom

Custom

Cedarview(2/3)

Cedarview(2/3)

Cedarview(2/3)

QBU00

QBU00

QBU00

1

7 38Wednesday, N ovember 02, 2011

7 38Wednesday, N ovember 02, 2011

7 38Wednesday, N ovember 02, 2011

0.3

0.3

0.3

+1.05VS

723mA

R525

R525

1 2

0_0805_5%

0_0805_5%

C971

C971

@

@

D D

R526

R526

1 2

0_0603_5%

0_0603_5%

R956

R956

1 2

0_0603_5%

0_0603_5%

R910

R910

1 2

0_0603_5%

0_0603_5%

R531

R531

1 2

0_0603_5%

0_0603_5%

C C

CRT@

CRT@

R1004

R1004

1 2

0_0603_5%

0_0603_5%

CRT@

CRT@

+1.5V

1 2

R530

R530

0_0603_5%

0_0603_5%

Please closed U 1 ball

+1.5V

R527

R527

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

1 2

0_1206_5%

0_1206_5%

2

C979

C979

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

R919

R919

1 2

0_0603_5%

0_0603_5%

R922

R922

1 2

0_0603_5%

0_0603_5%

@

@

R927

R927

1 2

0_0603_5%

0_0603_5%

1

B B

+1.5VS

A A

5

R909

1

1

C973

C973

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C973 1UF for

CPU pin V4

1

C1080

C1080

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C1080 1UF for

CPU pin L19

+VCCA_VDDR

1

C1084

C1084

2

@

@

1U_0402_6.3V6K

1U_0402_6.3V6K

+VCCADP_1.05

1

C1086

C1086

2

1U_0402_6.3V6K

1U_0402_6.3V6K

+VCCCK_DDR

1

C993

C993

2

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

+VCCADMI_1.5VS

1U_0402_6.3V6K

1U_0402_6.3V6K

+VCCAGPIO1.5V

C1101

C1101

@

@

0.1U_0402_10V6K

0.1U_0402_10V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1

2

R909

0_0603_5%

0_0603_5%

+1.05VS

C1081

C1081

Close Chipset pin

+3VS_PRIME

+VCC_SM

+VCCDMPL

C1078

C1078

@

@

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

1

+

+

2

330U_D2_2.5VY_R9M

330U_D2_2.5VY_R9M

HDMI@

HDMI@

2

1

R913

R913

1 2

0_0603_5%

0_0603_5%

R914

R914

1 2

0_0603_5%

0_0603_5%

+VCCAZILAON

+VCCPLLCPU0

+VCCPLLCPU1

+VCCAHPLL

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

C1092

C1092

+VCCA_VCCD

+1.05VS_EAST

+VCCA_VCCD

+VCCA_VDDR

+VCCCK_DDR

+VCC_SM

+VCCADP_1.05

+VCCADP0_SFR

+VCCADP1_SFR

+1.05VS_EAST

+VCCAGPIO1.5V

+VCCAGPIO1.8V

+VCCAGPIO3.3V

+VCC_CRT_DAC

+VCCALVDS

+VCCDLVDS

+VCCSFRMPL

+VCCDMPL

+VCCAGPIO3.3V

2

1 2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

+1.8VS

R916

R916

1 2

0_0603_5%

0_0603_5%

1U_0402_6.3V6K

1U_0402_6.3V6K

R921

R921

1 2

0_0603_5%

0_0603_5%

CRT@

CRT@

R535

R535

1 2

0_0603_5%

0_0603_5%

HDMI@

HDMI@

C1125

C1125

CRT@

CRT@

0_0603_5%

0_0603_5%

@

@

1 2

+1.05VS+1.05VS +1.05VS

1

C983

C983

2

0.1uH use

0 ohm replace

+VCC_CRT_DAC+VCC_CRT_DAC

10U_0603_6.3V

10U_0603_6.3V

12

C1125

C1125

R928

R928

0_0603_5%

0_0603_5%

C1106

C1106

@

@

1 2

R918 0_0402_5%R918 0_0402_5%

C1100

C1100

2011.04.25 Add for RGB I/F

R925

R925

0_0603_5%

0_0603_5%

1 2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

1

C1127

C1127

2

2

+VCCA_VCCD

1

1

C972

C972

C970

C970

2

2

@

@

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

22U_0805_6.3V6M

22U_0805_6.3V6M

+1.05VS_EAST

1

C1079

C1079

2

@

@

1U_0402_6.3V6K

1U_0402_6.3V6K

C1079 1UF for

CPU pin N30,N31

1

1

C1083

C1083

C1082

C1082

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

+VCC_DMI

1

2011.04.25 Add for RGB I/F

C994

C994

2

1U_0402_6.3V6K

1U_0402_6.3V6K

+VCCDIO

1

HDMI@

HDMI@

C166

C166

C166

C166

0_0402_5%

0_0402_5%

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C992

C992

2

22U_0805_6.3V6M

22U_0805_6.3V6M

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

2

2

C980

C980

C981

C981

C982

C982

1

1

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

1

C1097

C1097

2

2

1

+1.5VS +1.5VS +1.5VS

R924

R924

0_0603_5%

0_0603_5%

1 2

+VCCADP0_SFR +VCCADP1_SFR

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

C1104

C1104

C1126

C1126

2

@

@

5

+VCCDIO

+VCCAZILAON

2

C1093

1

HDMI@C1093

HDMI@

+VCCAGPIO1.8V

1

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

2.2U_0402_6.3V6M

2.2U_0402_6.3V6M

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4

AA14

AA16

W16

W18

N30

N31

W8

W9

W11

W13

AJ6

AK6

AH14

AH19

AK23

AK5

AL11

AL16

AL21

AG31

K17

L18

L19

L16

N18

D30

D31

B13

L21

B29

A30

AA18

AA11

B27

C29

B30

B26

CRT@

CRT@

C1093

C1093

0_0402_5%

0_0402_5%

+VCCDLVDS

+VCCALVDS

1

C986

C986

2

4

U1E

U1E

VCCADDR_1

VCCADDR_2

VCCADDR_3

VCCADDR_4

VCCRAMXXX_1

VCCRAMXXX_2

V4

VCCRAMXXX_3

VCCACKDDR_1

VCCACKDDR_2

VCCADLLDDR_1

VCCADLLDDR_2

VCCCKDDR_1

VCCCKDDR_2

V_SM_1

V_SM_2

V_SM_3

V_SM_4

V_SM_5

V_SM_6

V_SM_7

V_SM_8

B5

VCCADP_1

C6

VCCADP_2

D6

VCCADP_3

VCCADP0_SFR

VCCADP1_SFR

VCCAGPIO_LV

VCCAGPIO_REF

VCCAGPIO_DIO

VCCAGPIO_1

VCCAGPIO_2

VCCADAC

H5

VCCALVDS

J1

VCCDLVDS

VCCDIO

VCCAZILAON_1

VCCAZILAON_2

VCCSFRMPL

VCCDMPL

VCCPLLCPU0

VCCPLLCPU1_ 1

VCCPLLCPU1_ 2

VCCAHPLL

QB0Z B2 1.6G

QB0Z B2 1.6G

+1.05VS

N2600@

N2600@

R917

R917

1 2

0_0603_5%

0_0603_5%

R920

R920

1 2

0_0603_5%

0_0603_5%

R923

R923

1 2

0_0603_5%

0_0603_5%

@

@

R929

R929

1 2

0_0603_5%

0_0603_5%

3

?

?

CEDARVIEW

CEDARVIEW

REV = 1.10

DDR

DDR

REV = 1.10

POWER

POWER

CPU

CPU

DMI

DMI

VCC_CPU_01

VCC_CPU_02

VCC_CPU_03

VCC_CPU_04

VCC_CPU_05

VCC_CPU_06

VCC_CPU_07

VCC_CPU_08

VCC_CPU_09

VCC_CPU_10

VCC_CPU_11

VCC_CPU_12

VCC_CPU_13

VCC_CPU_14

VCC_CPU_15

VCC_CPU_16

VCC_CPU_17

VCC_CPU_18

VCC_CPU_19

VCC_CPU_20

VCC_CPU_21

VCC_CPU_22

VCC_CPU_23

VCC_CPU_24

VCC_CPU_25

VCC_CPU_26

VCC_CPU_27

VCC_CPU_28

VCC_CPU_29

VCC_GFX_01

VCC_GFX_02

VCC_GFX_03

VCC_GFX_04

VCC_GFX_05

VCC_GFX_06

VCC_GFX_07

VCC_GFX_08

VCC_GFX_09

VCC_GFX_10

VCC_GFX_11

VCCADMI_PLLSFR

PLL

PLL

5 OF 6

5 OF 6

+VCCPLLCPU0

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0805_10V4Z

10U_0805_10V4Z

1

1

2

2

C1094

C1094

C1095

C1095

+VCCPLLCPU1

10U_0805_10V4Z

10U_0805_10V4Z

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

2

2

C1098

C1098

C1099

C1099

+VCCAHPLL

1U_0402_6.3V6K

1U_0402_6.3V6K

10U_0805_10V4Z

10U_0805_10V4Z

1

1

2

2

C1103

C1103

C1102

C1102

R926

R926

0_0603_5%

0_0603_5%

1 2

+VCCSFRMPL

10U_0805_10V4Z

10U_0805_10V4Z

1U_0402_6.3V6K

1U_0402_6.3V6K

1

1

C1109

@

@

C1109

2

2

C1108

C1108

VCC_CPUSENSE

VSS_CPUSENSE

VCC_GFXSENSE

VSS_GFXSENSE

VCCTHRM_1

VCCTHRM_2

?

?

4234mA

1U_0402_6.3V6K

1U_0402_6.3V6K

P18

P19

P21

P28

P29

P30

R22

R23

R24

R25

R26

R27

T19

T21

T29

T30

T31

U22

U23

U24

U25

U26

U27

V18

V19

V21

V28

V29

V30

+GFX_CORE

1938mA

N11

N13

P11

P13

R10

R9

T11

T13

U10

V11

V13

+VCC_DMI

B4

VCCADMI_1

C5

VCCADMI_2

A4

VCCADMI_3

VCCFHV_1

VCCFHV_2

VCCFHV_3

K4

V16

T16

V14

VCCSENSE

M28

VSSSENSE

M30

VCC_GFXSENSE

U8

VSS_GFXSENSE

U7

N16

K2

+VCCADMI_1.5VS

+VCCATHRM

1

C1089

C1089

@

@

2

VCC_GFXSENSE

VSS_GFXSENSE

+GFX_CORE

1

C1005

C1005

2

22U_0805_6.3V6M

22U_0805_6.3V6M

Close Chipset pin

2011.06.14 Stuff C1007,C1008,C1009 for EDS issue

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DR AWING IS THE PR OPRIETARY PROPERT Y OF COMPAL ELECT RONICS, INC. AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGINEERING DR AWING IS THE PR OPRIETARY PROPERT Y OF COMPAL ELECT RONICS, INC. AND CONTAINS CON FIDENTIAL

THIS SHEET OF ENGINEERING DR AWING IS THE PR OPRIETARY PROPERT Y OF COMPAL ELECT RONICS, INC. AND CONTAINS CON FIDENTIAL

AND TRAD E SECRET INFOR MATION. THIS SHEET M AY NOT BE TRANSF ERED FROM T HE CUSTODY OF THE COMPETEN T DIVISION OF R&D

AND TRAD E SECRET INFOR MATION. THIS SHEET M AY NOT BE TRANSF ERED FROM T HE CUSTODY OF THE COMPETEN T DIVISION OF R&D

AND TRAD E SECRET INFOR MATION. THIS SHEET M AY NOT BE TRANSF ERED FROM T HE CUSTODY OF THE COMPETEN T DIVISION OF R&D

DEPARTMEN T EXCEPT AS AUT HORIZED BY COMPA L ELECTRONICS, INC . NEITHER THIS SHE ET NOR THE INF ORMATION IT CONT AINS

DEPARTMEN T EXCEPT AS AUT HORIZED BY COMPA L ELECTRONICS, INC . NEITHER THIS SHE ET NOR THE INF ORMATION IT CONT AINS

DEPARTMEN T EXCEPT AS AUT HORIZED BY COMPA L ELECTRONICS, INC . NEITHER THIS SHE ET NOR THE INF ORMATION IT CONT AINS

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, IN C.

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, IN C.

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, IN C.

3

4.7U_0603_6.3V6K

1

C974

C974

2

1U_0402_6.3V6K

1U_0402_6.3V6K

4.7U_0603_6.3V6K

1

C975

C975

2

1

1

C976

C976

2

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

C977

C977

Please closed U 1 ball

+CPU_CORE

2 x 330uF(9mohm/2)

1

+

+

C984

C984

330U_D2_2.5VY_R9M

330U_D2_2.5VY_R9M

1

C991

C991

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

2

R912

R912

R915

R915

1

C1009

C1009

2

1U_0402_6.3V6K

1U_0402_6.3V6K

2

1

C1085

C1085

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

10U_0805_10V4Z

10U_0805_10V4Z

C1090

C1090

VCC_GFXSENSE <35>

VSS_GFXSENSE <35>

1

1

+

+

C1004

C1004

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

Compal Secret Data

Compal Secret Data

Compal Secret Data

+CPU_CORE

1

1

C990

C990

C989

C989

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

+VCCA_VCCD

R911

R911

1 2

0_0603_5%

0_0603_5%

+GFX_CORE

1U_0402_6.3V6K

1U_0402_6.3V6K

12

100_0402_5%

100_0402_5%

12

100_0402_5%

100_0402_5%

1

1

C1008

C1008

C1007

C1007

C1006

C1006

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

1U_0402_6.3V6K

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

1

1

C988

C988

@

@

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

+CPU_CORE

12

100_0402_5%

100_0402_5%

12

+1.8VS

100_0402_5%

100_0402_5%

1

+

+

C1096

C1096

2

330U_B2_2.5VM_R15M

330U_B2_2.5VM_R15M

330U_B2_2.5VM_R15M

330U_B2_2.5VM_R15M

Deciphered Date

Deciphered Date

Deciphered Date

C987

C987

@

@

R532

R532

R533

R533

+CPU_CORE

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

C996

C996

@

@

2

1

+

+

C985

C985

330U_D2_2.5VY_R9M

330U_D2_2.5VY_R9M

2

VCCSENSE <35>

VSSSENSE <35>

2

1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS_CDVDET

VSSA_CRTDAC

6 OF 6

6 OF 6

1 2

C159 22P_0402_50V8J

C159 22P_0402_50V8J

RF@

RF@

1 2

C150 22P_0402_50V8J

C150 22P_0402_50V8J

RF@

RF@

1 2

C153 22P_0402_50V8JC153 22P_0402_50V8J

1 2

C156 22P_0402_50V8JC156 22P_0402_50V8J

H19

H26

H28

H6

J10

J2

J21

J30

K11

K15

K3

K7

K8

K9

L1

L10

L13

L23

L25

L31

L7

M29

M4

N10

N14

N19

N21

N22

N23

N26

N27

N28

N4

N7

P14

P16

P4

T14

T18

T3

U5

U6

U9

V2

W10

W14

W19

W2

W21

W22

W23

W24

W27

W30

W5

W6

Y4

A27

A29

A3

AH1

AJ1

AJ31

AK1

AK2

AK30

AK31

AL2

AL29

AL3

AL30

AL5

B2

B3

B31

C1

C2

C31

E1

L14

D13

AA10

AA13

AA19

AA21

AA23

AA26

AA27

AA29

AB15

AB17

AB23

AB29

AC10

AC11

AC13

AC22

AC28

AD19

AD21

AD24

AD26

AE10

AE11

AE15

AE17

AE19

AE31

AF11

AF13

AF21

AF24

AF28

AG22

AH26

AH28

AK13

AK19

AK28

AL13

AL19

AL23

AL25

+VCCA_VCCD

+VCCCK_DDR

+GFX_CORE

+CPU_CORE

A11

A16

A21

A25

AA1

AA7

AA9

AC1

AC4

AD5

AD8

AE1

AE3

AF7

AG5

AH6

AH9

AJ2

AJ3

AK9

AL7

B10

B14

B19

B23

C12

C26

C30

D19

D28

F24

G11

G13

G15

G17

G19

G21

G31

H13

C7

D8

D9

E2

E5

E7

F4

G1

G8

?

?

U1F

N2600@

U1F

N2600@

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

QB0Z B2 1.6G

QB0Z B2 1.6G

?

?

CEDARVIEW

CEDARVIEW

REV = 1.10

REV = 1.10

2010.07.12 RF request

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cedarview(3/3)

Cedarview(3/3)

Cedarview(3/3)

QBU00

QBU00

QBU00

1

0.3

0.3

8 38Wednesday, November 02, 2011

8 38Wednesday, November 02, 2011

8 38Wednesday, November 02, 2011

0.3

5

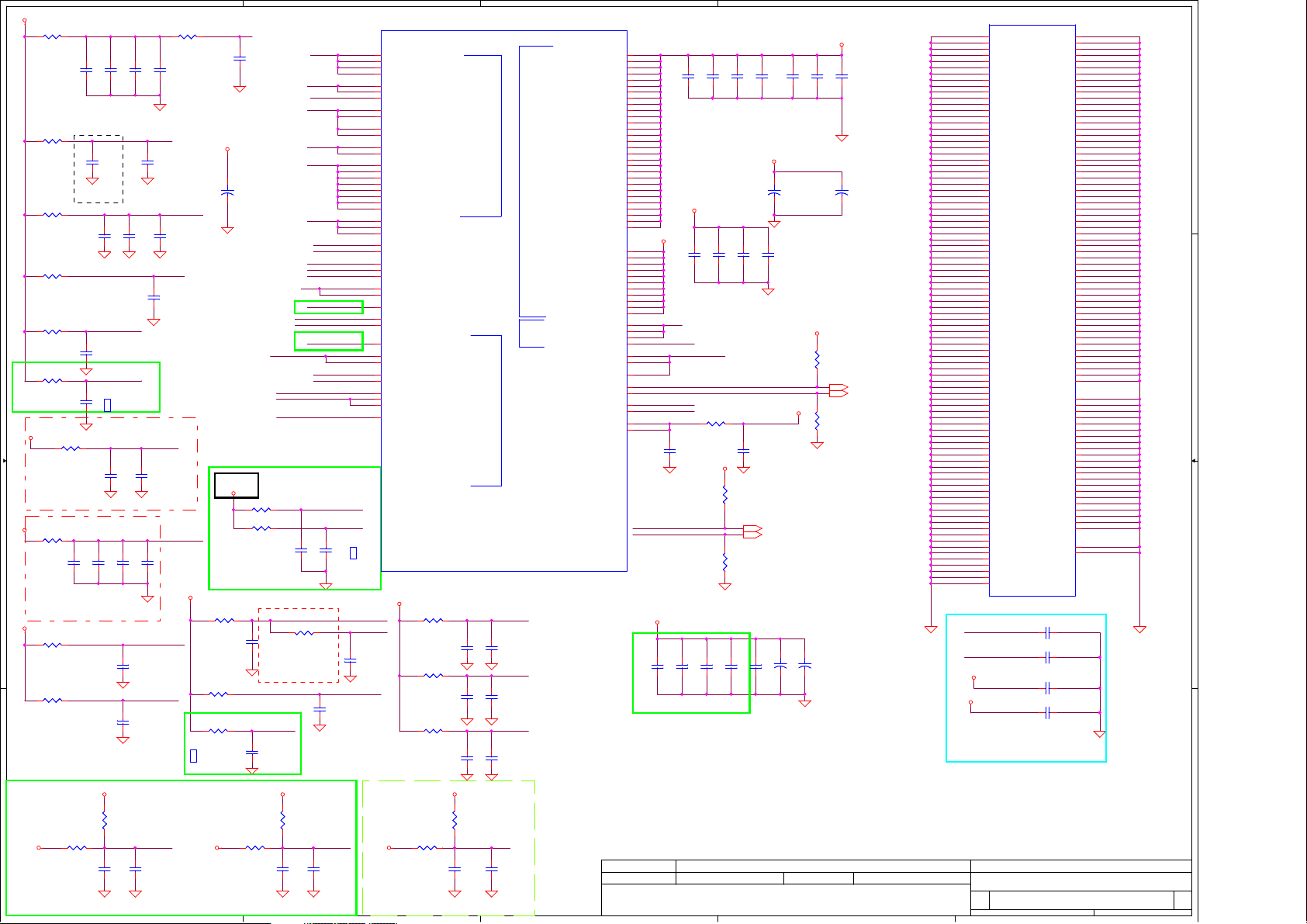

PCI

SRC

CPU

CLKSEL1

0

FSA

CLKSEL0

MHz

266

MHz

1000

MHz

MHz

33.30

14.318 96.0 48.0

DOT_96

MHz

USB

MHz

FSC FSB REF

CLKSEL2

0 1000 133 33.31 14.318 96.0 48.0

0 1001 200 33.30 14.318 96.0 48.0

0 1001 166 33.31 14.318 96.0 48.0

D D

1 1000 333 33.30 14.318 96.0 48.0

1 1000 100 33.31 14.318 96.0 48.0

1 1001 400 33.30 14.318 96.0 48.0

1 1 1

Reserved

Normal Power Low Power

R477 @ Stuff

R478

R479

R480

R483

C C

B B

A A

Stuff

Stuff

@

@

+1.05VS

R482

R482

2.2K_0402_5%

2.2K_0402_5%

FSA

FSB

FSC

R486

R486

1K_0402_5%

1K_0402_5%

R490

R490

10K_0402_5%

10K_0402_5%

12

+1.05VS

12

+1.05VS

12

5

@

@

Stuff

Stuff

12

R481

R481

470_0402_5%

470_0402_5%

12

R484

@R484

@

1K_0402_5%

1K_0402_5%

+3VS

12

R485

@R485

@

470_0402_5%

470_0402_5%

12

R488

R488

0_0402_5%

0_0402_5%

12

R489

R489

470_0402_5%

470_0402_5%

12

R491

@R491

@

0_0402_5%

0_0402_5%

C147 22P_0402_50V8JC147 22P_0402_50V8J

14.31818MHZ 20PF 7A14300003

14.31818MHZ 20PF 7A14300003

C148 22P_0402_50V8JC148 22P_0402_50V8J

Routing the trace at least 10mil

+3VS

12

Y1

Y1

R65

R65

1 2

R608

R608

1 2

CLK_XTAL_IN

CLK_XTAL_OUT

+1.5VM_CK505

+1.05VM_CK505

+1.5VM_CK505

H_STP_CPU#_R

10K_0402_5%

10K_0402_5%

H_STP_PCI#_R

10K_0402_5%

10K_0402_5%

For ITP_EN, 0 =SRC8/SRC8#; 1 = ITP/ITP#

For PCI4_SEL, 0 = Pin24/25 : DOT96 / DOT96#

Pin28/29 : LCDCLK / LCDCLK #

For PCI2_TME:0=Overclocking of CPU and SRC allowed

(ICS only) 1=Overclocking of CPU and SRC NOT allowed

4

+3VM_CK505

R81

R81

1 2

+3VS

0_0603_5%

0_0603_5%

R82

R82

1 2

+1.05VS

FBMH1608HM601-T_0603

FBMH1608HM601-T_0603

R477

R477

1 2

+1.5VS

0_0603_5%

0_0603_5%

LOW@

LOW@

+3VM_CK505

R478

NORMAL@ R478

NORMAL@

R483

LOW@R483

LOW@

1 2

0_0603_5%

0_0603_5%

NORMAL@ R479

NORMAL@

CLK_48M_CR<24>

CLK_PCH_48M<12>

CLK_PCH_14M<13>

1 = Pin24/25 : SRC_0 / SRC_0#

Pin28/29 : 27M/27M_SS

R119

R119

10K_0402_5%

10K_0402_5%

1 2

ITP_EN PCI2_TME

R113

@R113

@

10K_0402_5%

10K_0402_5%

1 2

4

1 2

0_0603_5%

0_0603_5%

1 2

0_0603_5%

0_0603_5%

R480

LOW@R480

LOW@

1 2

0_0603_5%

0_0603_5%

H_STP_CPU#<13>

H_STP_PCI#<13>

CLK_PCI_DDR<18>

CLK_PCI_LPC<25>

CLK_PCI_PCH<11>

R479

VGATE<13,25,28,34,35>

+3VS+3VS

@

@

R118

R118

10K_0402_5%

10K_0402_5%

1 2

R114

R114

10K_0402_5%

10K_0402_5%

1 2

+3VM_1.5VM_R

PCI4_SEL

1

C126

C126

10U_0805_10V4Z

10U_0805_10V4Z

2

+1.05VM_CK505

80 mA

1

C134

C134

10U_0805_10V4Z

10U_0805_10V4Z

2

+1.5VM_CK505

1

C942

C942

2

10U_0805_10V4Z

10U_0805_10V4Z

1

C943

C943

C944

C944

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+1.05VM_1.5VM_R

1

C946

C946

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1 2

1 2

1 2

C143 22P_0402_50V8JC143 22P_0402_50V8J

1 2

1 2

C868 22P_0402_50V8JC868 22P_0402_50V8J

R432 0_0402_5%@R432 0_0402_5%@

1 2

R427 0_0402_5%@R427 0_0402_5%@

1 2

250 mA

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

@

@

C947

C947

1 2

C144 22P_0402_50V8JC144 22P_0402_50V8J

1 2

1 2

C145 22P_0402_50V8JC145 22P_0402_50V8J

1 2

1 2

1 2

C146 22P_0402_50V8JC146 22P_0402_50V8J

+3VS

R112

R112

10K_0402_5%

10K_0402_5%

1 2

@

@

R115

R115

10K_0402_5%

10K_0402_5%

1 2

3

1

C127

C127

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C135

C135

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C128

C128

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C136

C136

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C129

C129

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

C137

C137

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C133

C133

47P_0402_50V8J

47P_0402_50V8J

1

C138

C138

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

1

2

SA00003H730 (Realtek :RTM890N-397-VC-GRT)

Low power CLK Gen.

1

C945

C945

2

47P_0402_50V8J

47P_0402_50V8J

R9210_0402_5% R9210_0402_5%

R9110_0402_5% R9110_0402_5%

R9333_0402_5% R9333_0402_5%

+3VM_CK505

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+1.05VM_CK505

FSA

FSB

FSC

VGATE

H_STP_CPU#_R

H_STP_PCI#_R

CLK_XTAL_IN

CLK_XTAL_OUT

R10333_0402_5% R10333_0402_5%

CLK_PCI_DDR_R

CLK_PCI_DDR_R

PCI2_TME

PCI4_SEL

PCI4_SEL

R10733_0402_5% R10733_0402_5%

ITP_EN

ITP_EN

R10833_0402_5% R10833_0402_5%

U4

LOW@U4

LOW@

55

VDD_SRC

6

VDD_REF

12

VDD_PCI

72

VDD_CPU

19

VDD_48

27

VDD_PLL3

66

VDD_CPU_IO

31

VDD_PLL3_IO

62

VDD_SRC_IO

52

VDD_SRC_IO

23

VDD_IO

38

VDD_SRC_IO

20

USB_0/FS_A

2

FS_B/TEST_MODE

7

REF_0/FS_C/TEST_

8

REF_1

1

CKPWRGD/PD#

11

NC

53

CPU_STOP#

54

PCI_STOP#

5

XTAL_IN

4

XTAL_OUT

13

PCI_1

14

PCI_2

15

PCI_3

16

PCI_4/SEL_LCDCL

17

PCIF_5/ITP_EN

18

VSS_PCI

3

VSS_REF

22

VSS_48

26

VSS_IO

69

VSS_CPU

30

VSS_PLL3

34

VSS_SRC

59

VSS_SRC

42

VSS_SRC

73

VSS

RTM890N-397-VC-GRT QFN

RTM890N-397-VC-GRT QFN

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPE RTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPE RTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPE RTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SE CRET INFORMATION. THIS SHEET MAY NOT B E TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

AND TRADE SE CRET INFORMATION. THIS SHEET MAY NOT B E TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

AND TRADE SE CRET INFORMATION. THIS SHEET MAY NOT B E TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DIVISI ON OF R&D

DEPARTMENT EX CEPT AS AUTHORIZ ED BY COMPAL ELECTRONICS, INC . NEITHER THIS SHE ET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EX CEPT AS AUTHORIZ ED BY COMPAL ELECTRONICS, INC . NEITHER THIS SHE ET NOR THE INFORMA TION IT CONTAINS

DEPARTMENT EX CEPT AS AUTHORIZ ED BY COMPAL ELECTRONICS, INC . NEITHER THIS SHE ET NOR THE INFORMA TION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/06/27 2011/6/27

2010/06/27 2011/6/27

2010/06/27 2011/6/27

SRC_0/DOT_96

SRC_0#/DOT_96#

LCDCLK#/27M_SS

SRC_8/CPU_ITP

SRC_8#/CPU_ITP#

USB_1/CLKREQ_A#

9

SDA

10

SCL

71

CPU_0

70

CPU_0#

68

CPU_1

67

CPU_1#

24

25

28

LCDCLK/27M

29

32

SRC_2

33

SRC_2#

35

SRC_3

36

SRC_3#

2011.03.30 CLK_CPU_EXP change to SRC3

39

SRC_4

40

SRC_4#

57

SRC_6

56

SRC_6#

61

SRC_7

60

SRC_7#

64

63

44

SRC_9

45

SRC_9#

50

SRC_10

51

SRC_10#

48

SRC_11

47

SRC_11#

37

CLKREQ_3#

41

CLKREQ_4#

58

CLKREQ_6#

65

CLKREQ_7#

43

CLKREQ_9#

49

SLKREQ_10#

46

CLKREQ_11#

21

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

C139

C139

0.1U_0402_16V4Z

0.1U_0402_16V4Z

CLK_SMBDATA

CLK_SMBCLK

CLK_CPU_HPLCLK

CLK_CPU_HPLCLK#

CLK_CPU_MPLL_C

CLK_CPU_MPLL#_C

CPU_SSCDREFCLK

CPU_SSCDREFCLK#

CLK_CPU_EXP

CLK_CPU_EXP#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_WLAN

CLK_PCIE_WLAN#

CLK_PCIE_LAN

CLK_PCIE_LAN#

CLK_PCIE_PCH

CLK_PCIE_PCH#

CLK_PCIE_WWAN

CLK_PCIE_WWAN#

WLAN_CLKREQ#

LAN_CLKREQ#

WWAN_CLKREQ#

C141

C141

47P_0402_50V8J

47P_0402_50V8J

CLK_SMBDATA <10,18>

CLK_SMBCLK <10,18>

CLK_CPU_HPLCLK <7>

CLK_CPU_HPLCLK# <7>

CLK_CPU_MPLL_C <6>

CLK_CPU_MPLL#_C <6>

CPU_DREFCLK

CPU_DREFCLK#

2011.06.29 Swap CLK Gen output for

CPU_SCDREFFCLK and CPU_DREFCLK

CPU_ITP

CPU_ITP#

2

CPU_DREFCLK <7>

CPU_DREFCLK# <7>

CPU_SSCDREFCLK <7>

CPU_SSCDREFCLK# <7>

CLK_CPU_EXP <6>

CLK_CPU_EXP# <6>

CLK_PCIE_SATA <11>

CLK_PCIE_SATA# <11>

CLK_PCIE_WLAN <18>

CLK_PCIE_WLAN# <18>

R9800_0402_5% @R9800_0402_5% @

R9830_0402_5% @R9830_0402_5% @

CLK_PCIE_LAN <23>

CLK_PCIE_LAN# <23>

CLK_PCIE_PCH <12>

CLK_PCIE_PCH# <12>

CLK_PCIE_WWAN <18>

CLK_PCIE_WWAN# <18>

WLAN_CLKREQ# <18>

LAN_CLKREQ# <23>

WWAN_CLKREQ# <18>

1

+3VS

R84

R84

2.2K_0402_5%

2.2K_0402_5%

CLK_SMBDATA

CLK_SMBCLK

PCH_SMBDATA<13>

PCH_SMBCLK<13>

2.2K_0402_5%

2.2K_0402_5%

Q1A

Q1A

2N7002DW-T/R7_SOT363-6

2N7002DW-T/R7_SOT363-6

6 1

+3VS

3

Q1B 2N7002DW-T/R7_SOT363-6Q1B 2N7002DW-T/R7_SOT363-6

R83

R83

2

5

4

2011.04.29 Reserve R305,C392 for RF

@

@

@

@

R305

R305

C392

10_0402_5%

10_0402_5%

C392

1 2

22P_0402_50V8J

22P_0402_50V8J

CLK_SMBCLK

1 2

SRC PORT LIST

PORT

SRC0

SRC2

SRC3

SRC4

SRC6

SRC7

SRC8

SRC9

SRC10

SRC11

WLAN_CLKREQ#

WWAN_CLKREQ#

LAN_CLKREQ#

T77T77

T78T78

DEVICE

CPU_DREFCLK

CPU_EXP

PCIE_SATA

PCIE_WLAN

PCIE_LAN

PCIE_PCH

PCIE_WWAN

R99 10K_0402_5%R99 10K_0402_5%

R100 10K_0402_5%R100 10K_0402_5%

R101 10K_0402_5%R101 10K_0402_5%

12

12

12

REQ PORT LIST

DEVICEPORT

REQ_3#

REQ_4#

REQ_6#

REQ_7#

REQ_9#

REQ_10#

REQ_11#

REQ_A#

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Clock Generator CK505

Clock Generator CK505

Clock Generator CK505

QBU00

QBU00

QBU00

PEIC_WLAN

PCIE_LAN

PEIC_WWAN

9 38Wednesday, November 02, 2011

9 38Wednesday, November 02, 2011

9 38Wednesday, November 02, 2011

1

+3VS

0.3

0.3

0.3

5

DDR_A_DQS#[0..7]<6>

DDR_A_D[0..63]<6>

DDR_A_DM[0..7]<6>

DDR_A_DQS[0..7]<6>

DDR_A_MA[0..15]<6>

D D

+1.5V

2011.06.14 Add C119 for ESD issue

+1.5V

1

1

+

+

C106

C106

C119

C119

C107

C107

2