A

1 1

B

C

D

E

Compal Confidential

2 2

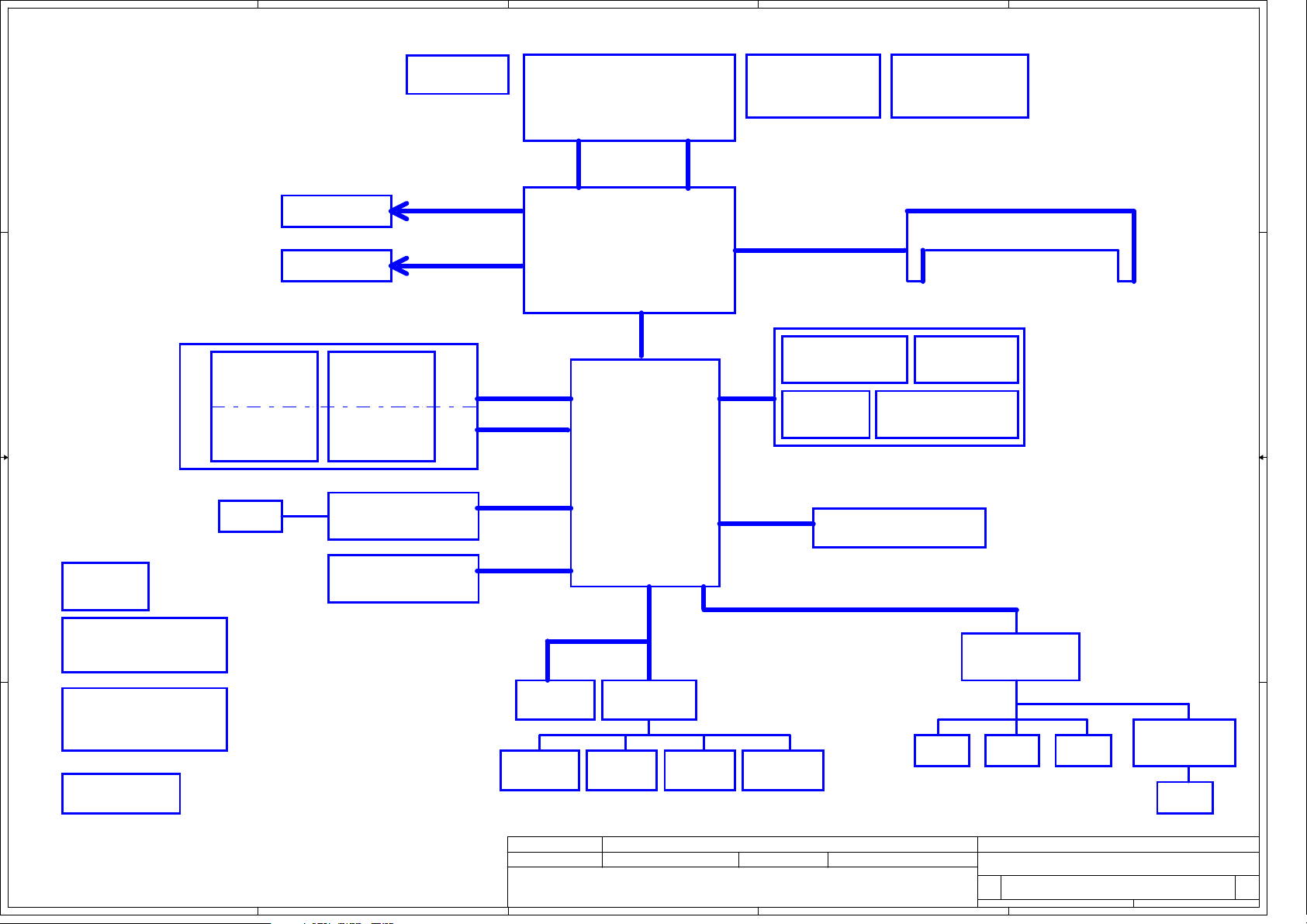

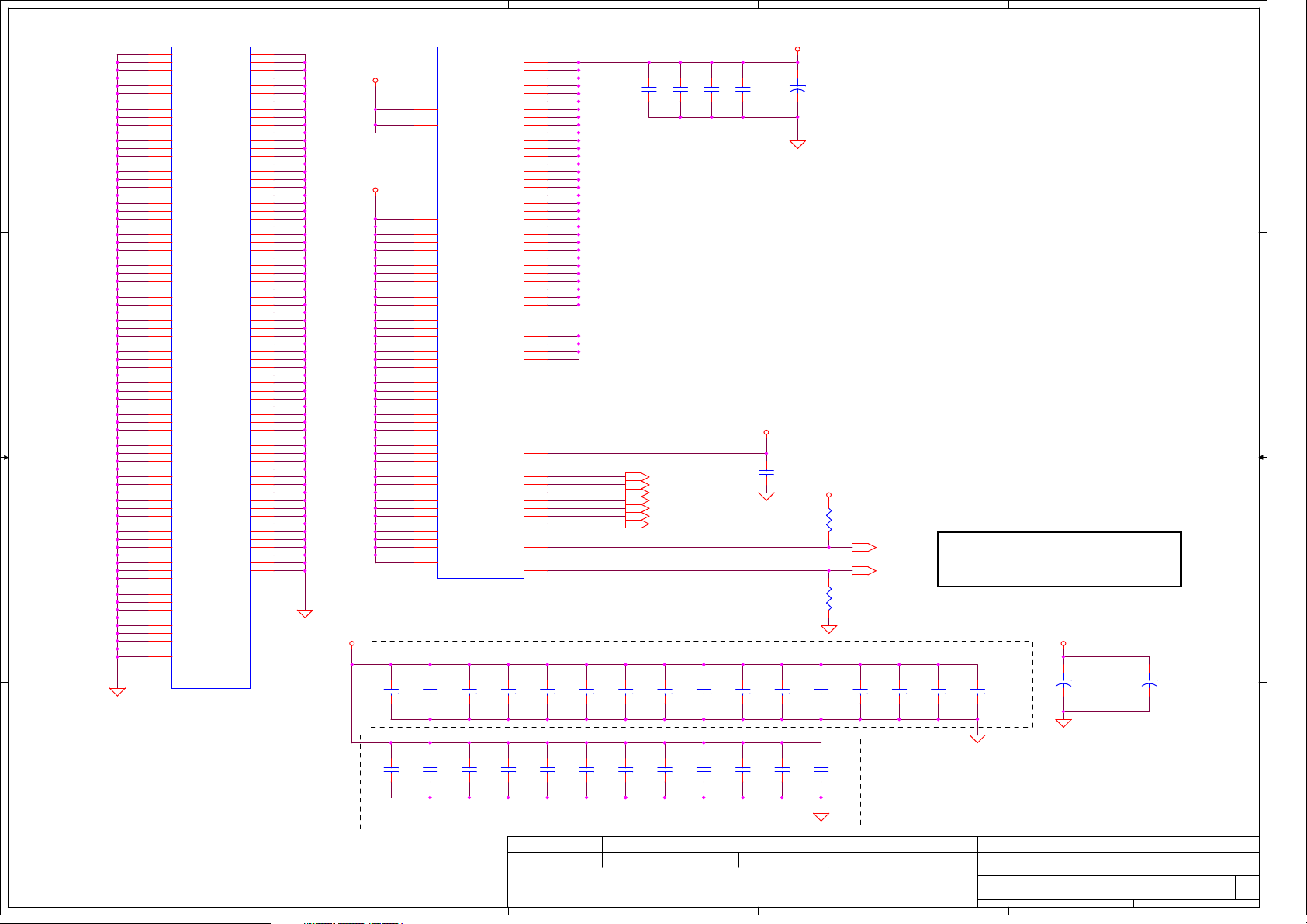

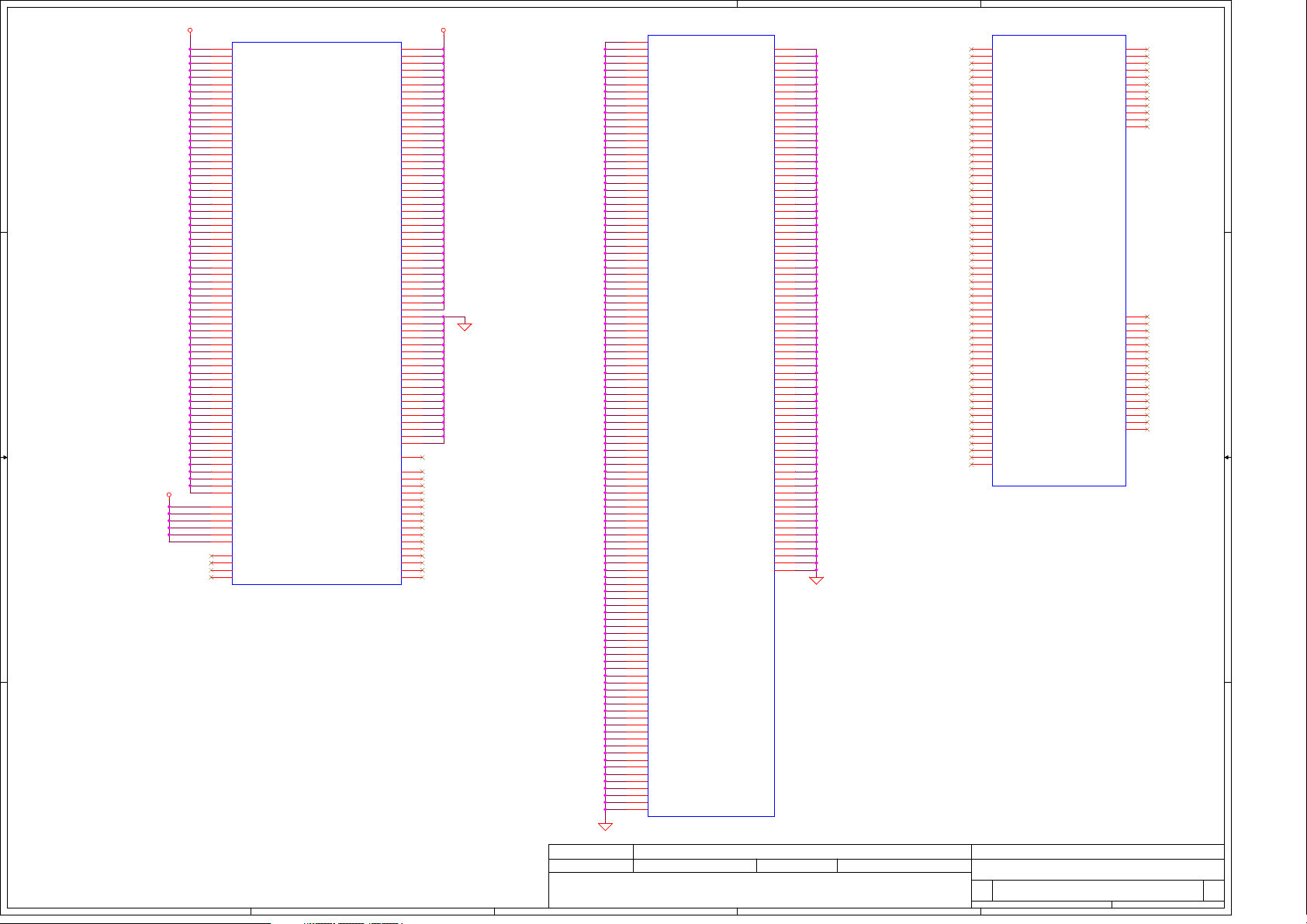

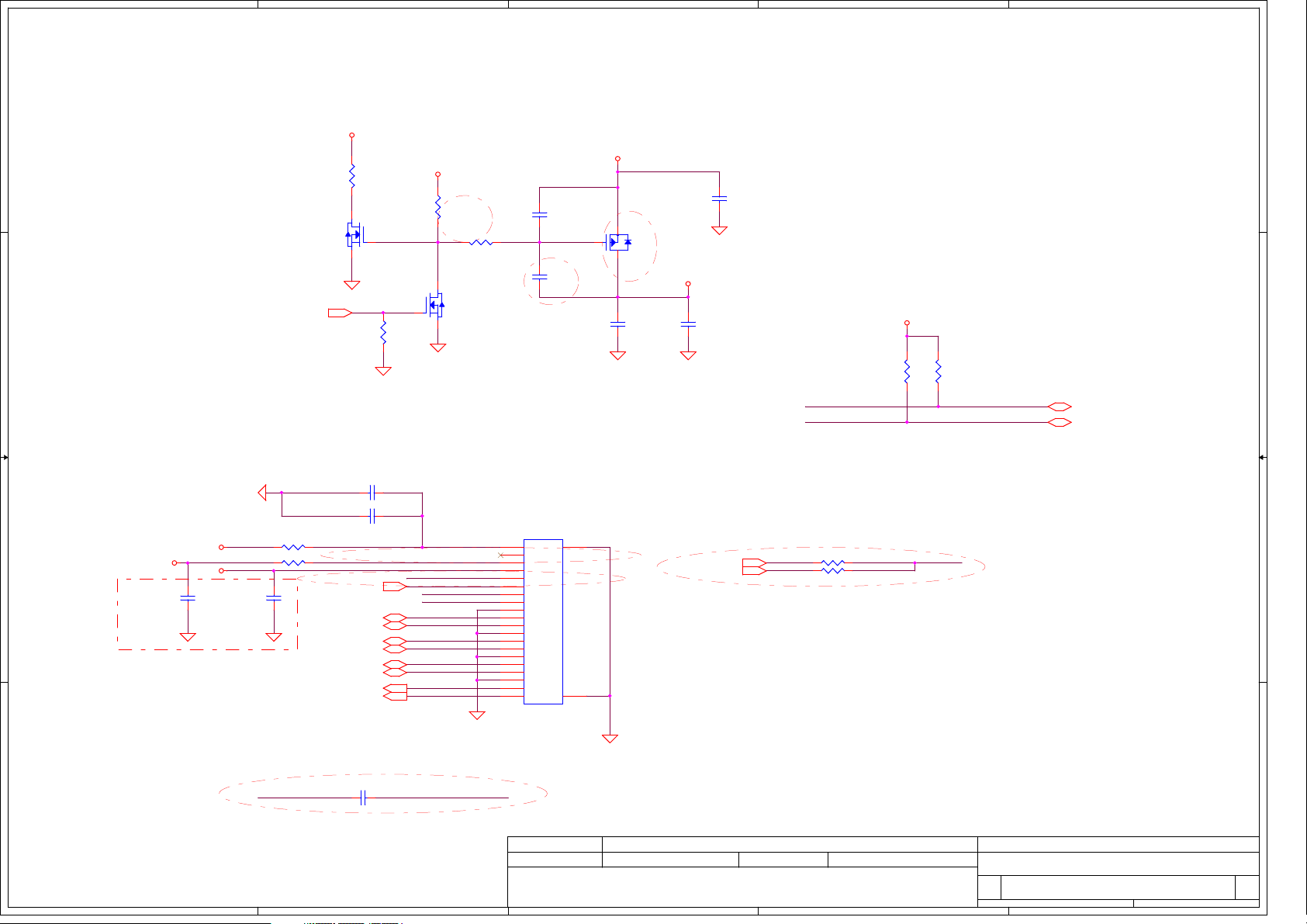

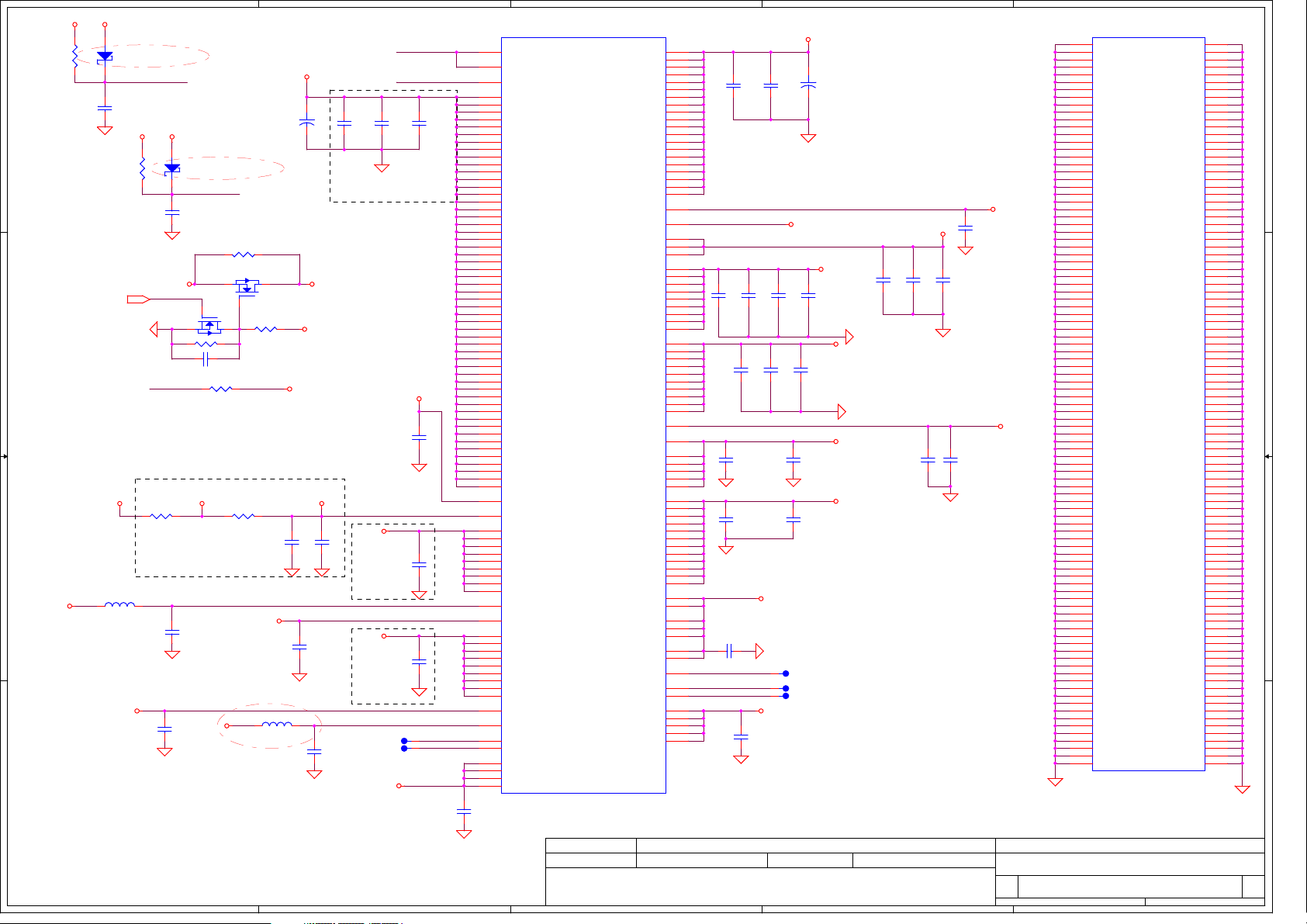

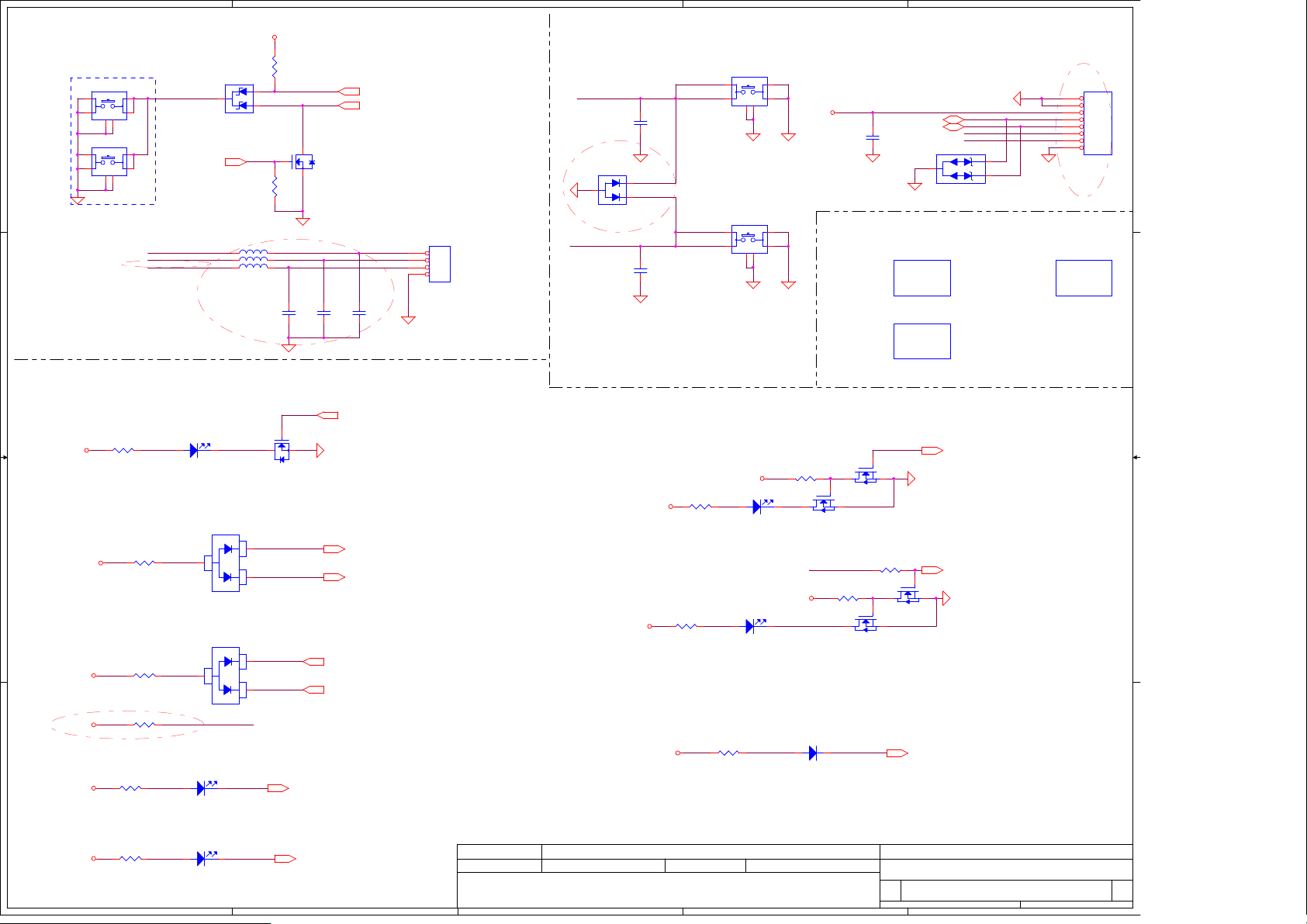

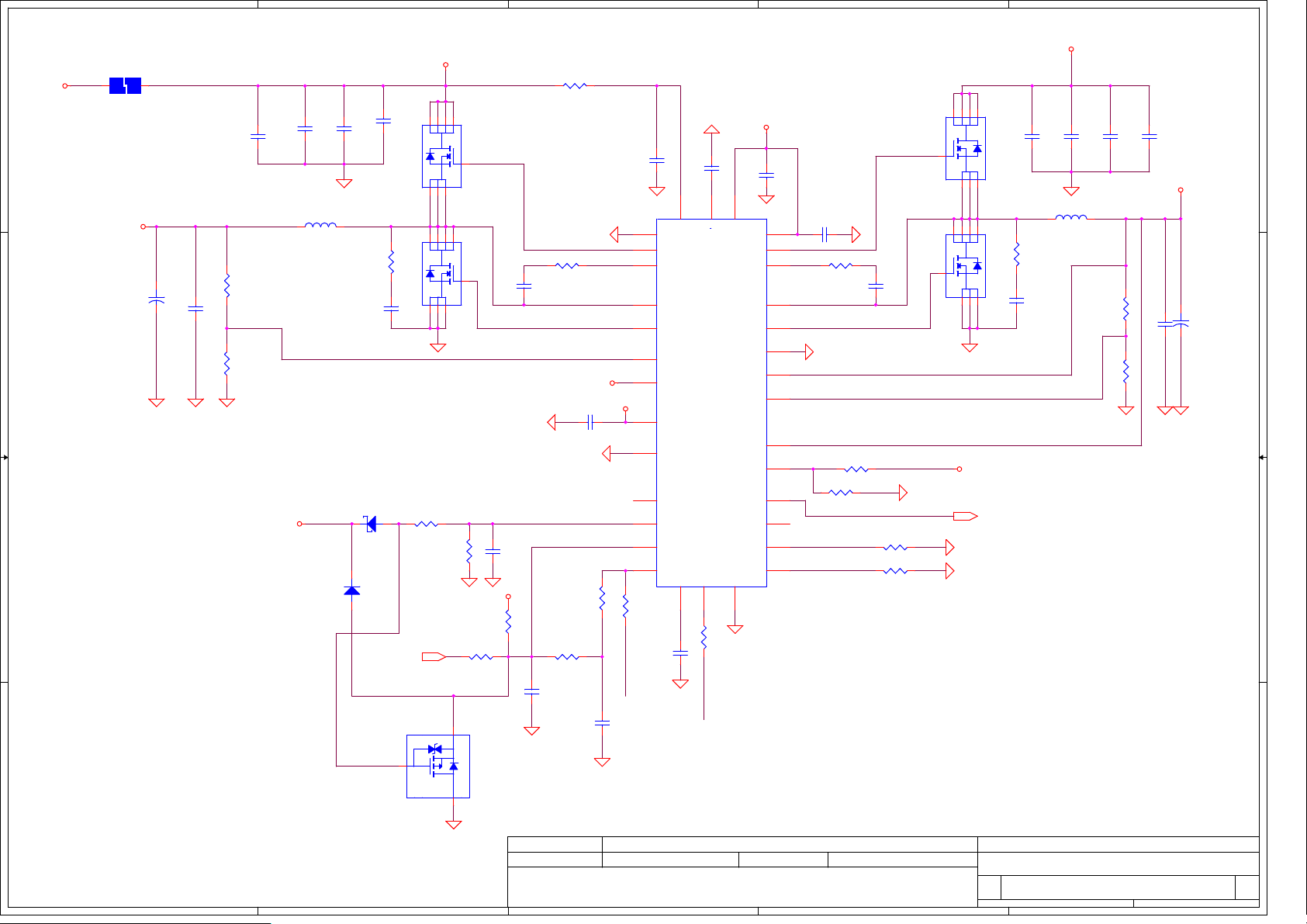

Buffalo KAVAA

LA-5121P Schematics Document

Intel Diamondville Processor/ Calistoga(945GSE)/ ICH7M

3 3

4 4

A

B

2009-03-10

REV: 1.0

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/11/17 2009/11/17

C

Compal Secret Data

Deciphered Date

D

Title

Size Do cumen t Numb er R ev

Cu stom

Da te: Sheet o f

Compal Electronics, Inc.

Cover Page

KAVAA LA-5121P M/B

1 42Tu esday, M arch 10 , 2009

E

1.0

A

Compal Confidential

B

C

D

E

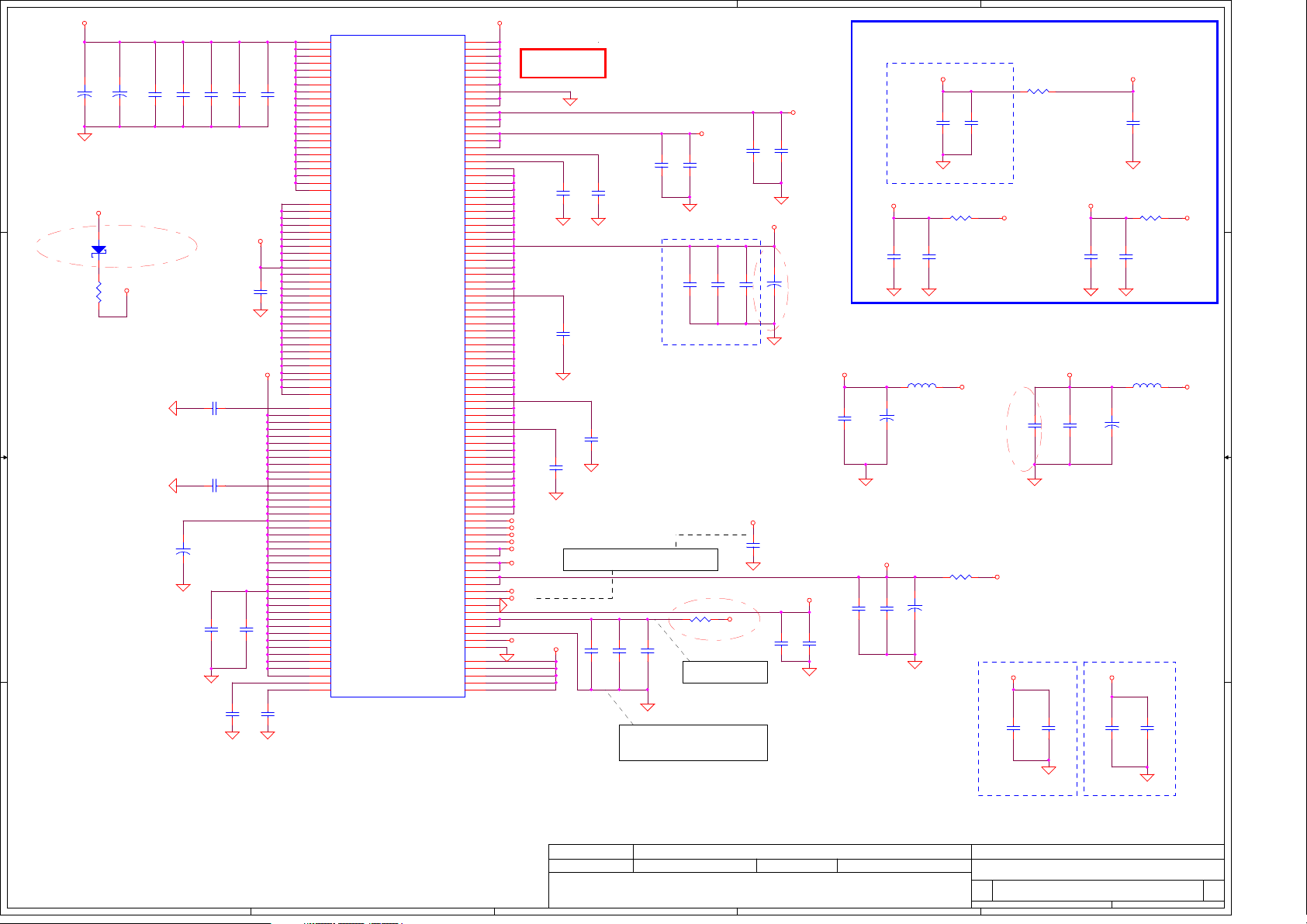

Model Name : KAVAA

File Name : LA-5121P

1 1

CRT Conn.

page 14

Fan Control

page 28

Intel Diamondville SC

FCBGA8-437 Pins

(22x22mm)

H_ A#( 3.. 31 ) H_ D#( 0..6 3)

FSB

400/533MHz

page 4,5

Intel Calistoga GSE

FC B GA 998

LED Conn.

page 13

2 2

PCIeMini Card

WiMax

USB po rt 4

page 19

PCIeMini Card

WLAN

PCIe po rt 2

page 19

PCIeMini Card

3G

USB po rt 5

page 19

PCIeMini Card

GPS

USB po rt 5

page 19

LVDS

ONE CHANNEL

PCI e 1x [ 2,4]

1.5V 2.5GHz(250MB/s)

(27x27mm)

page 6,7,8,9,10

DMI x 2

USB

5V 480MHz

Intel ICH7M

Thermal Sensor

EMC1402

page 4

Memory BUS(DDRII)

1.8V DDRII 400/533

US B Conn X3

USB port 0,2,7

USB

5V 480MHz

BT conn

USB port 6

page 21

page 20

Clock Generator

SLG8SP556VTR

page 12

200pin DDRII-SO-DIMM

Int. Camera

USB port 1

page 21

Touch Screen conn

BTO USB port 4 ,5

page 20

page 11

BG A -652

PC Ie 1x

RJ45

page 24

3 3

RTC CKT.

page 16

RTL8103EL 10/100M

PCIe po rt 3

Card R eader

RTS5159 2IN1

USB port 3

page 24

page 25

1.5V 2.5GHz(250MB/s)

USB

5V 480MHz

(31x31mm)

page 15,16,17,18

SATA port 0

5V 1.5GHz(150MB/s)

HD Audio

SATA HDD&SSD

page 21

3.3V 24.576MHz/48Mhz

DC/DC Interface CKT.

3.3V 33 MHz

page 30

Power Circuit DC/DC

page 31~37

Debug Port

page 28

Touch Pad

4 4

Power /B

page 29

A

B

page 29

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

ENE KB926 D3

Int.KBD

page 28

LPC BUS

page 26

SPI ROM

page 28

2008/11/17 2009/11/17

C

GSENSOR

page 27

Compal Secret Data

Deciphered Date

Int.

MIC CONN

page 23 page 23 page 23

D

HDA Codec

ALC272-GR

page 22

AMP.

E

TPA6017

page 23

SPK CO NN

page 23

2 42Tu esday, M arch 10 , 2009

MIC CONN

Title

Size Do cumen t Numb er R ev

Da te: Sheet o f

HP CONN

Compal Electronics, Inc.

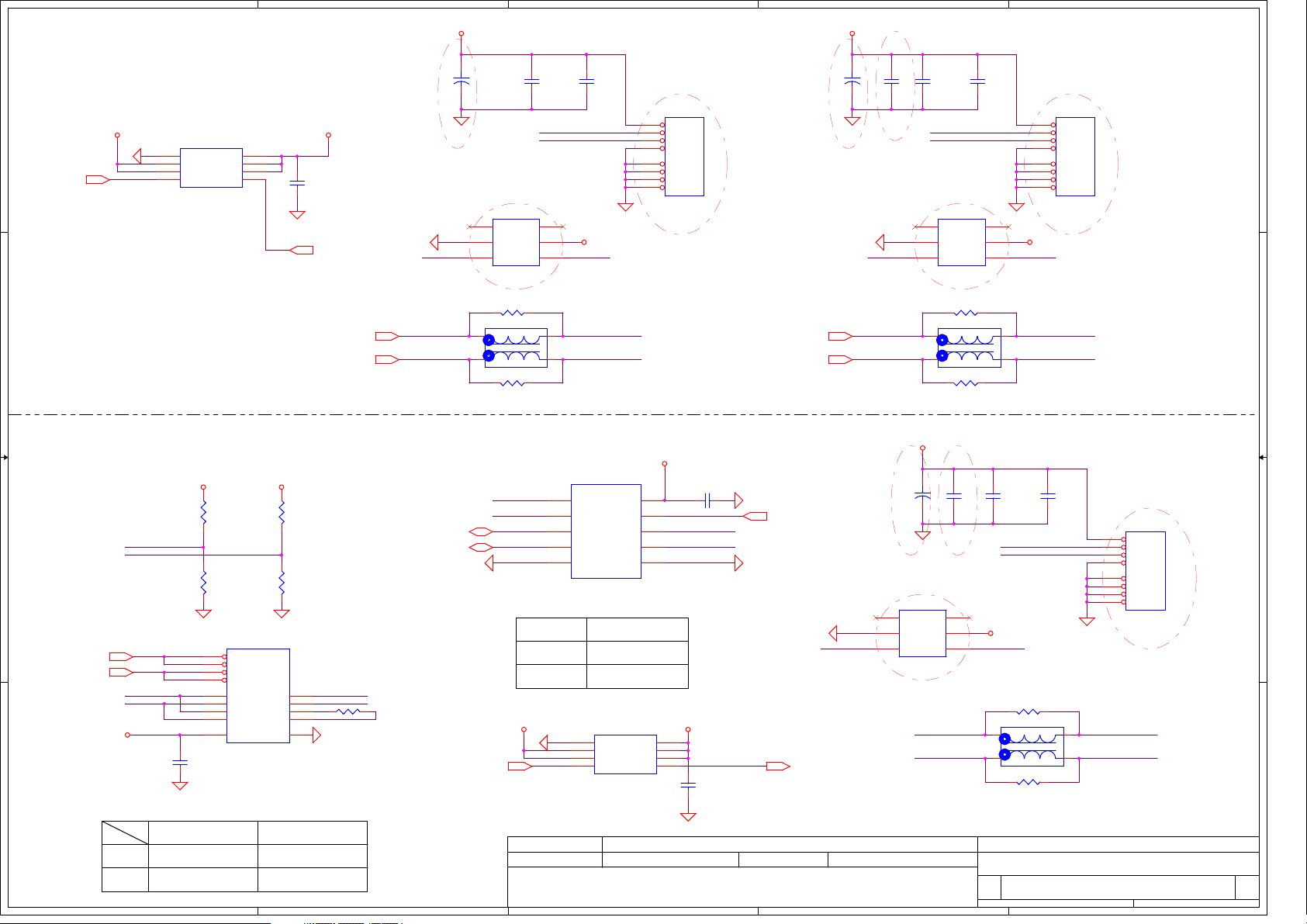

Block Diagrams

KAVAA LA-5121P M/B

1.0

A

B

C

D

E

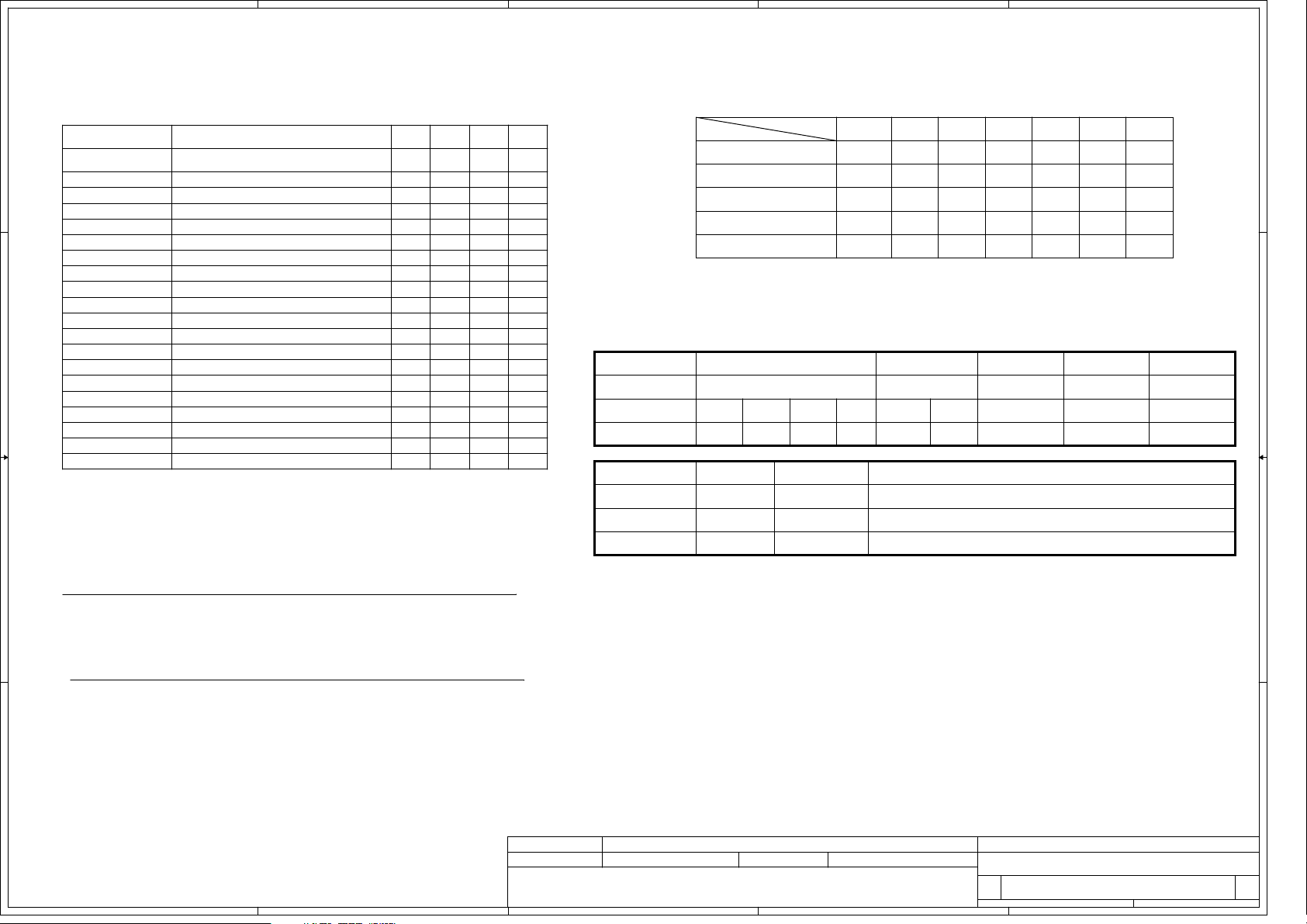

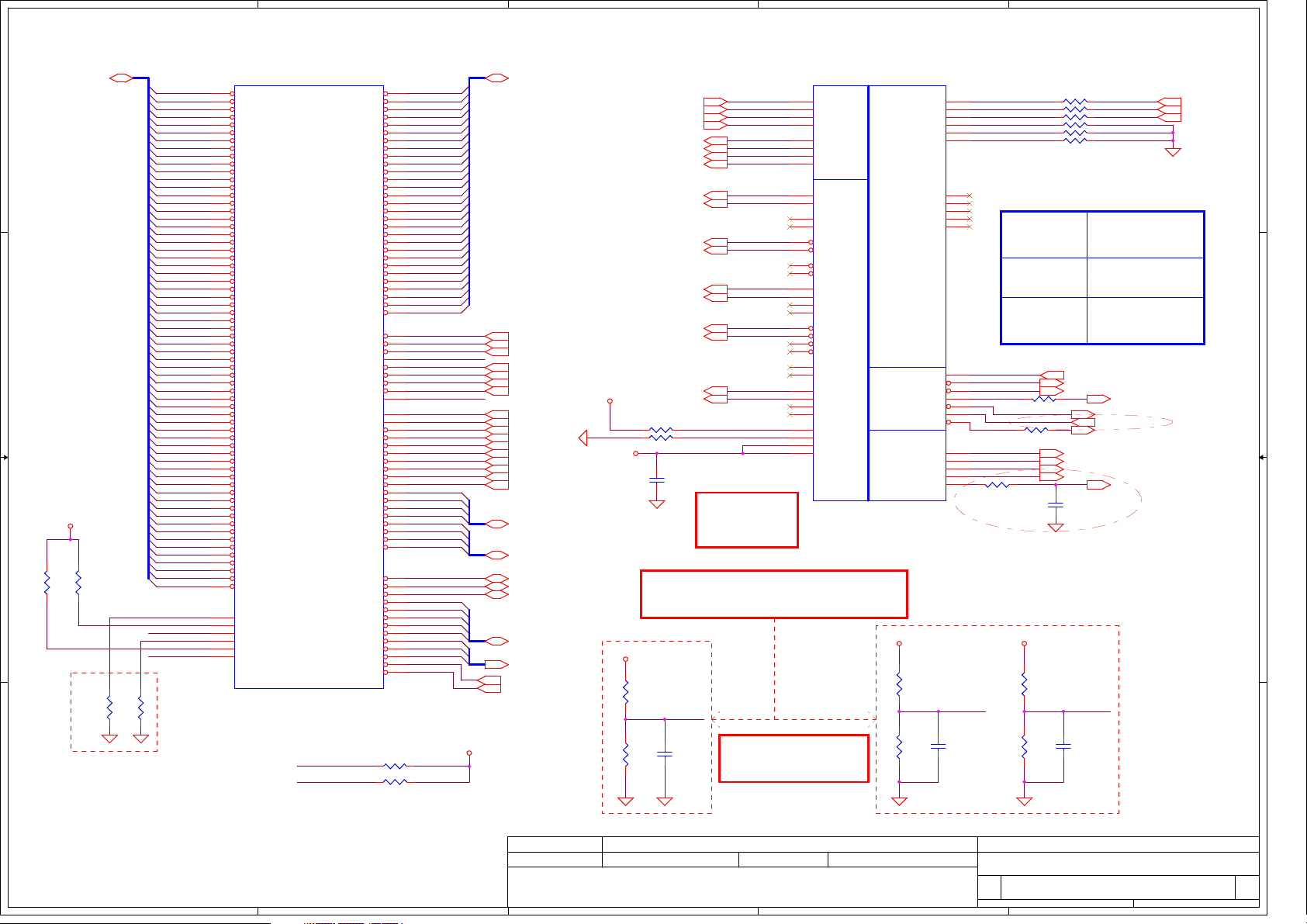

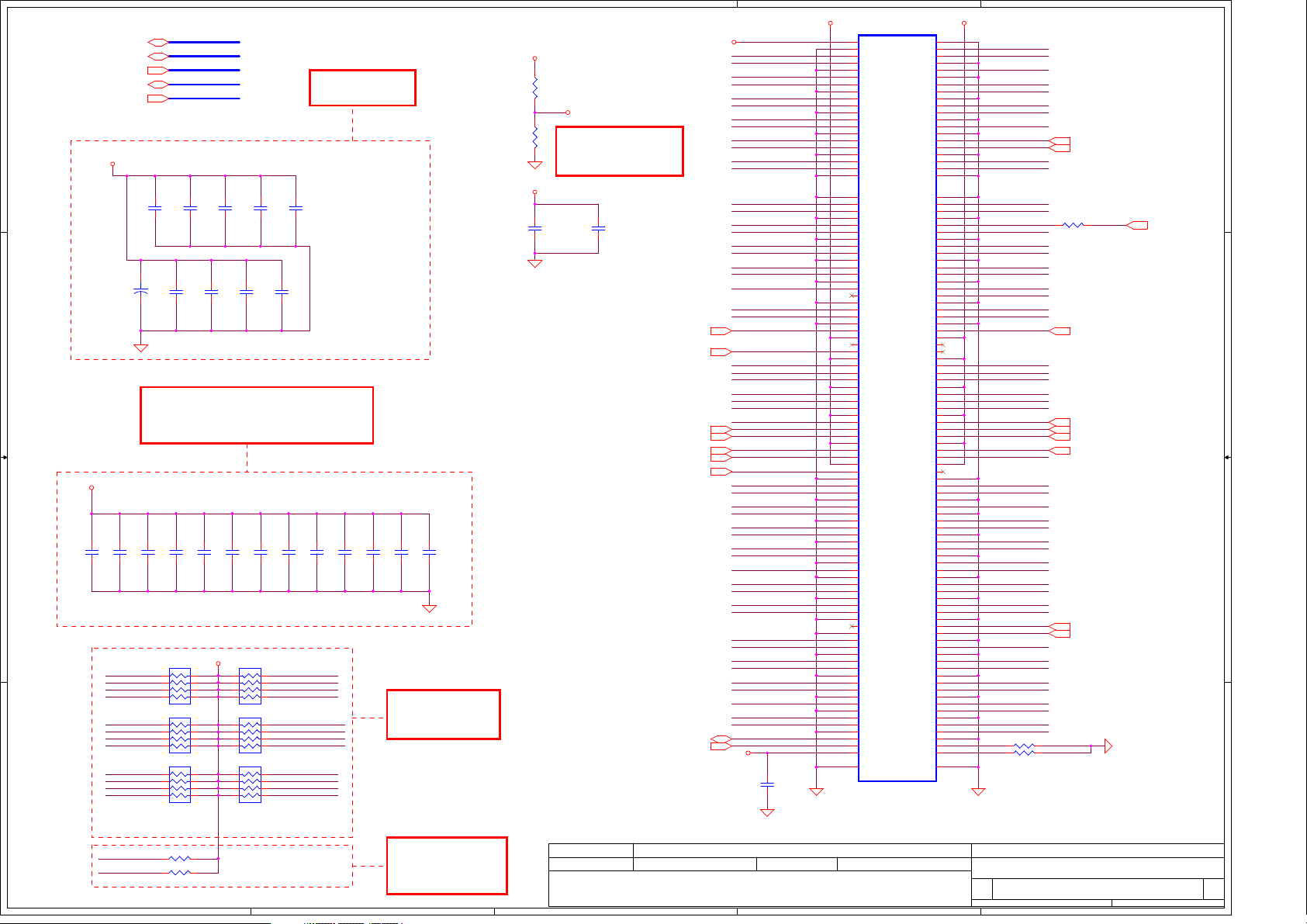

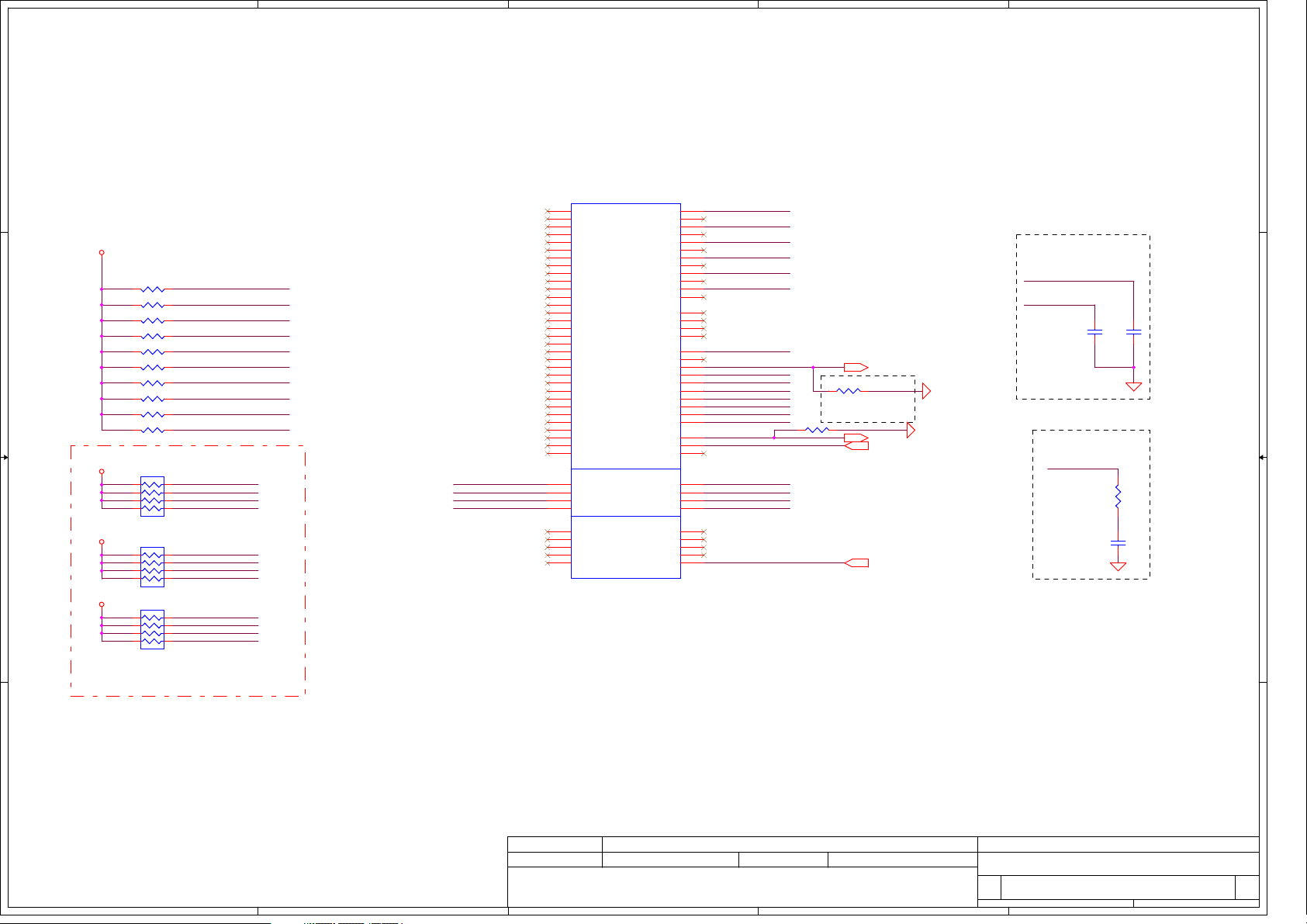

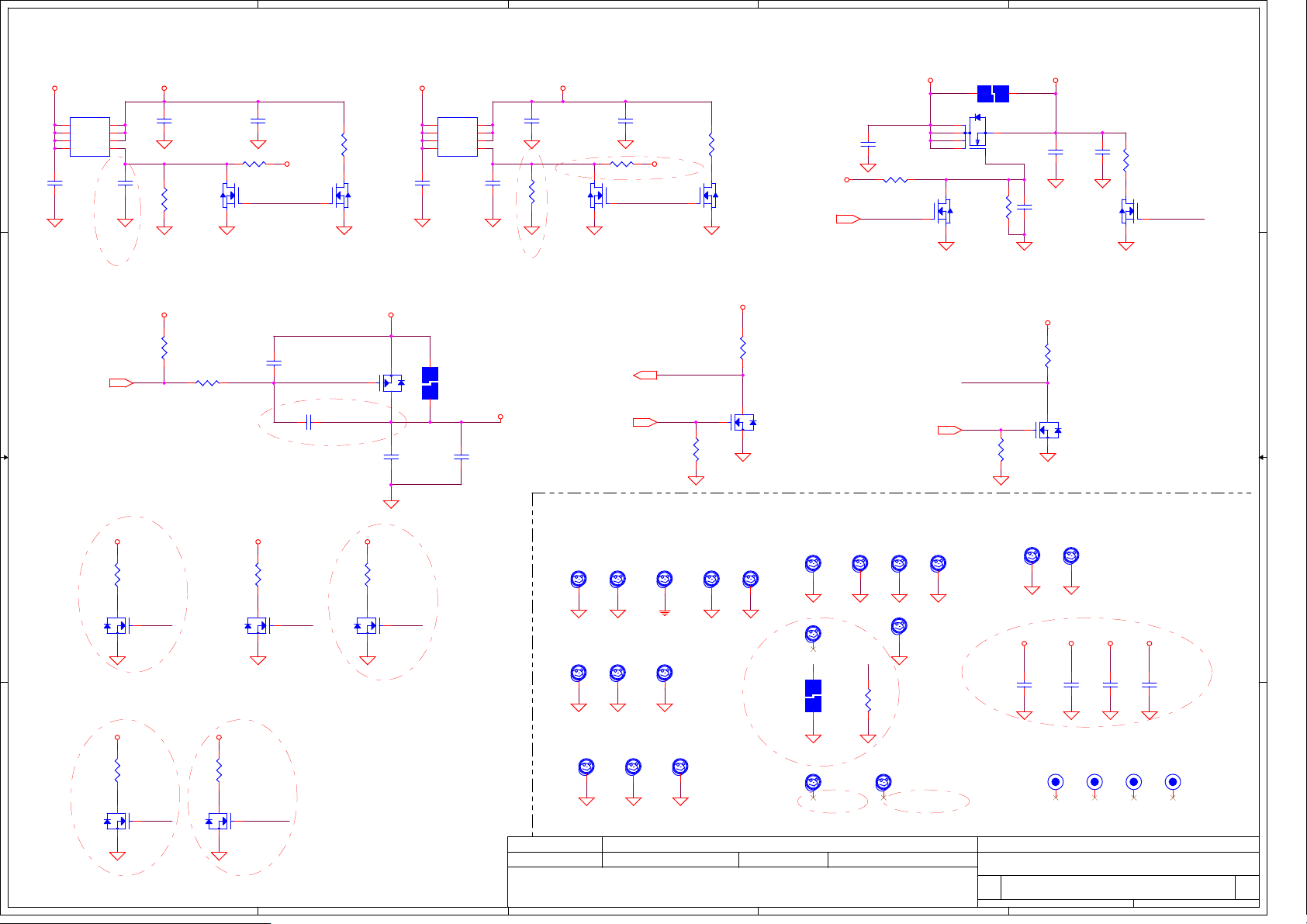

Voltage Rails

1 1

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFF

ON

OFF

OFF OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFFON

OFF+5V_SB 5V power rail for SB

OFF

ON

OFF

OFF

OFF

ON

G3

BTO Option Table

Function

description

explain

BTO

Power Plane Description

VIN

B+

+CPU_CORE

+0.9VS 0.9V switched power rail for DDR terminator

+1.05VS

+1.5VS

+1.8V

+2.5VS 2.5V switched power rail

+3VALW

+3V_SB 3.3V power rail for LAN

+3V_LAN 3.3V power rail for LAN ON

2 2

+3V_WLAN

+3VS

+5VALW

+5VS

+VSB VSB always on power rail ON

+RTCVCC RTC power

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

VCCP switched power rail

1.5V switched power rail

1.8V power rail for DDR

3.3V always on power rail

3.3V power rail for LAN ON ON

3.3V switched power rail

5V always on power rail

5V switched power rail

S1 S3 S5

ON ON ON OFF

ON ON ON ON

ON OFF

ON OFF

ON OFF OFF

ON OFF OFF

ON OFF

ON

ON

OFF

ONON

ON

ON

ON

ON

ON

ON

OFF

ON

ON

OFF

ON

ON

ON

ON

ON

STAT E

Full ON

S1(P ower On Suspend)

S3 ( Susp end to RAM)

S4 ( Susp end to Disk)

S5 ( Soft OFF)

Mini PCI -E SL OT

WLAN @ 3GGP S@

WIMA X@

SIGN AL

3GGP SWi-F i WiMax

SLP_ S3#

SLP_ S4#

SLP_ S5#

HIGH HIGH HIGH

HIGH

LOW

LOW LOW

LOWLOW

CAME RA & MIC

CAME RA MIC

3G

3G@

CAM@ MIC@

HIGHHIGHHIGH

HIGH

HIGH

LOW

+VAL W

ON

ON

ON

ON

ON

BLUE TOOTH

BLUE TOOTH

BT@

+V +VS Cloc k

ON

ON

ON

OFF

OFF

ON

OFF

OFF

OFF

STAR

ONON

LOW

OFF

OFF

OFF

G-SE NSOR

POWE R SA VING H DD P ROTECT

STAR @

GSEN SOR@

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

description

explain

BTO

Function

3 3

EC SM Bus1 address

Device

Smart Battery

Address

EC SM Bus2 address

Device

EMC1402

Address

10 01 010 X b00 01 011 X b

ICH7M SM Bus address

Device

Cloc k Generator

(SL G8SP55 6VTR)

DDR DIMMA

4 4

A

Address

1101 001Xb

10 10 000Xb

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/11/17 2009/11/17

C

Compal Secret Data

Deciphered Date

Title

Size Do cumen t Numb er R ev

Cu stom

D

Da te: Sheet o f

Compal Electronics, Inc.

Notes List

KAVAA LA-5121P M/B

3 42Tu esday, M arch 10 , 2009

E

1.0

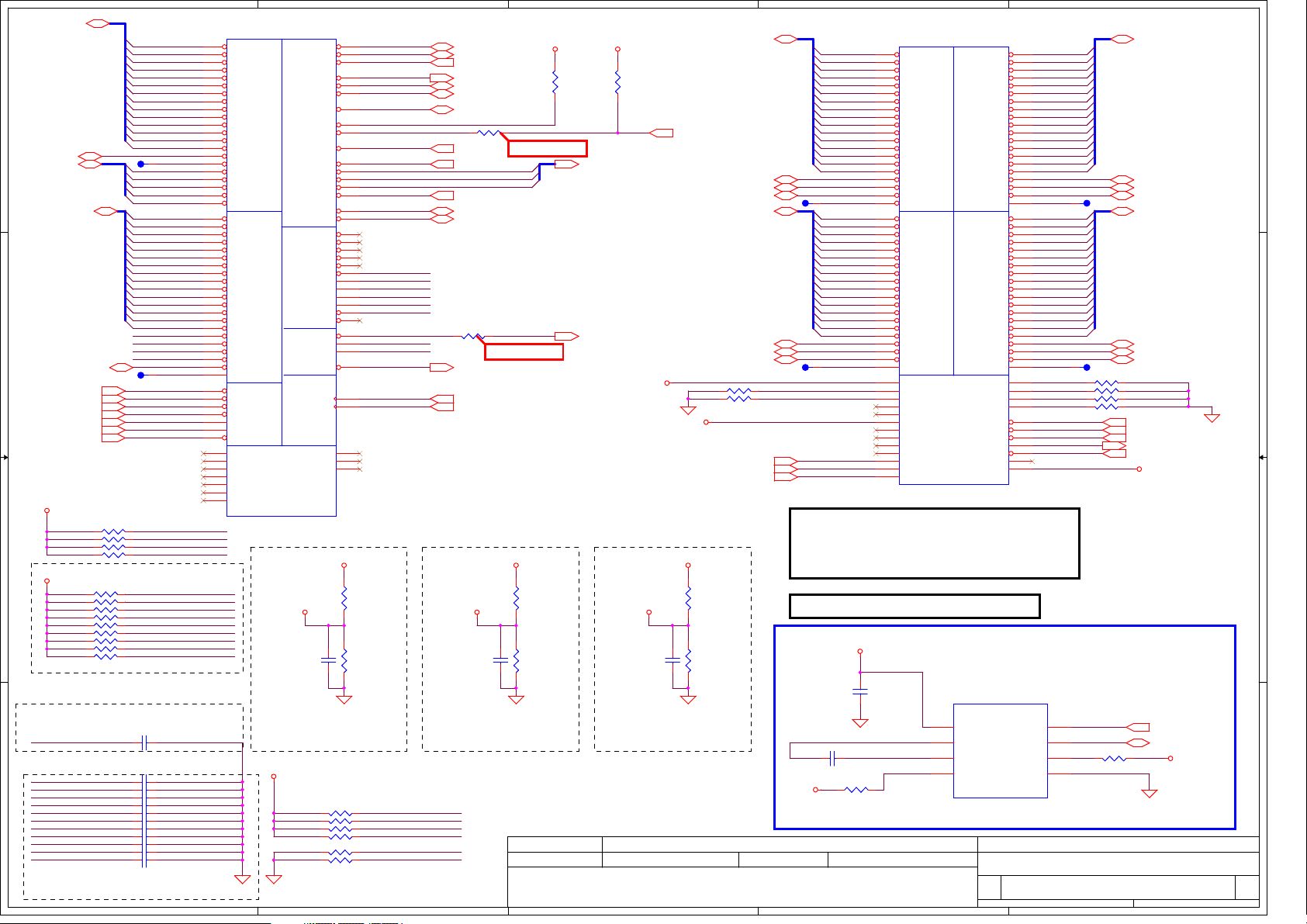

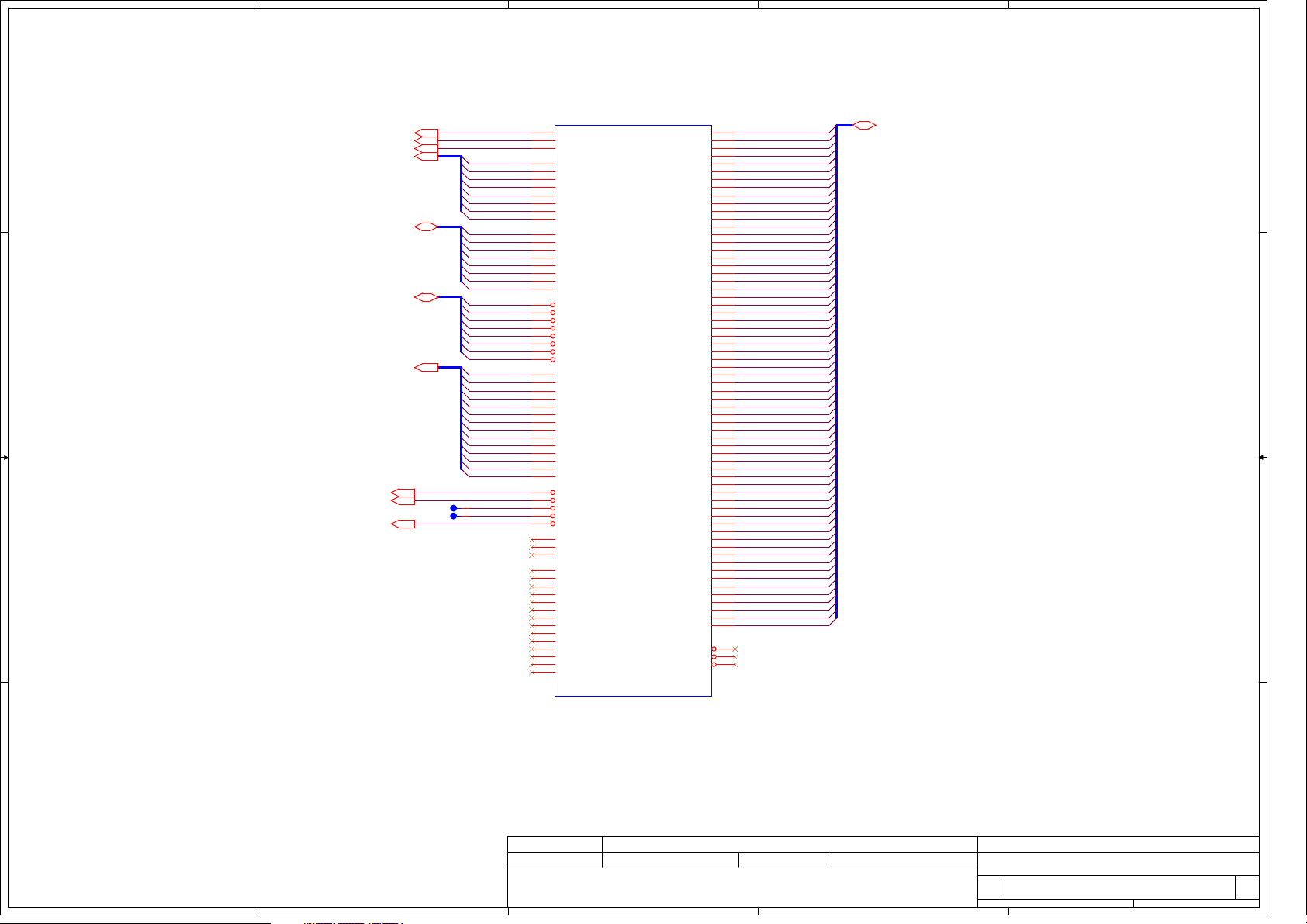

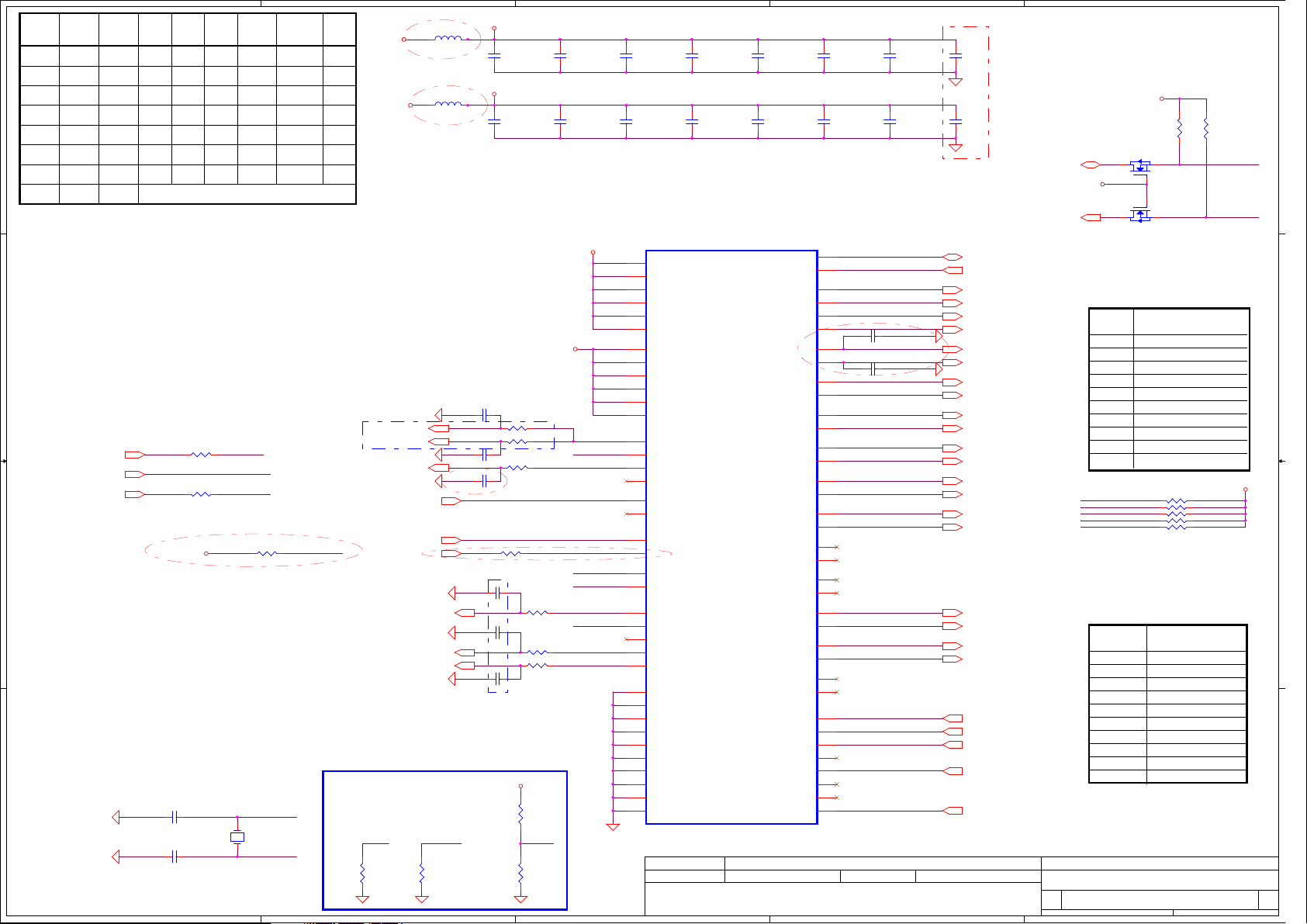

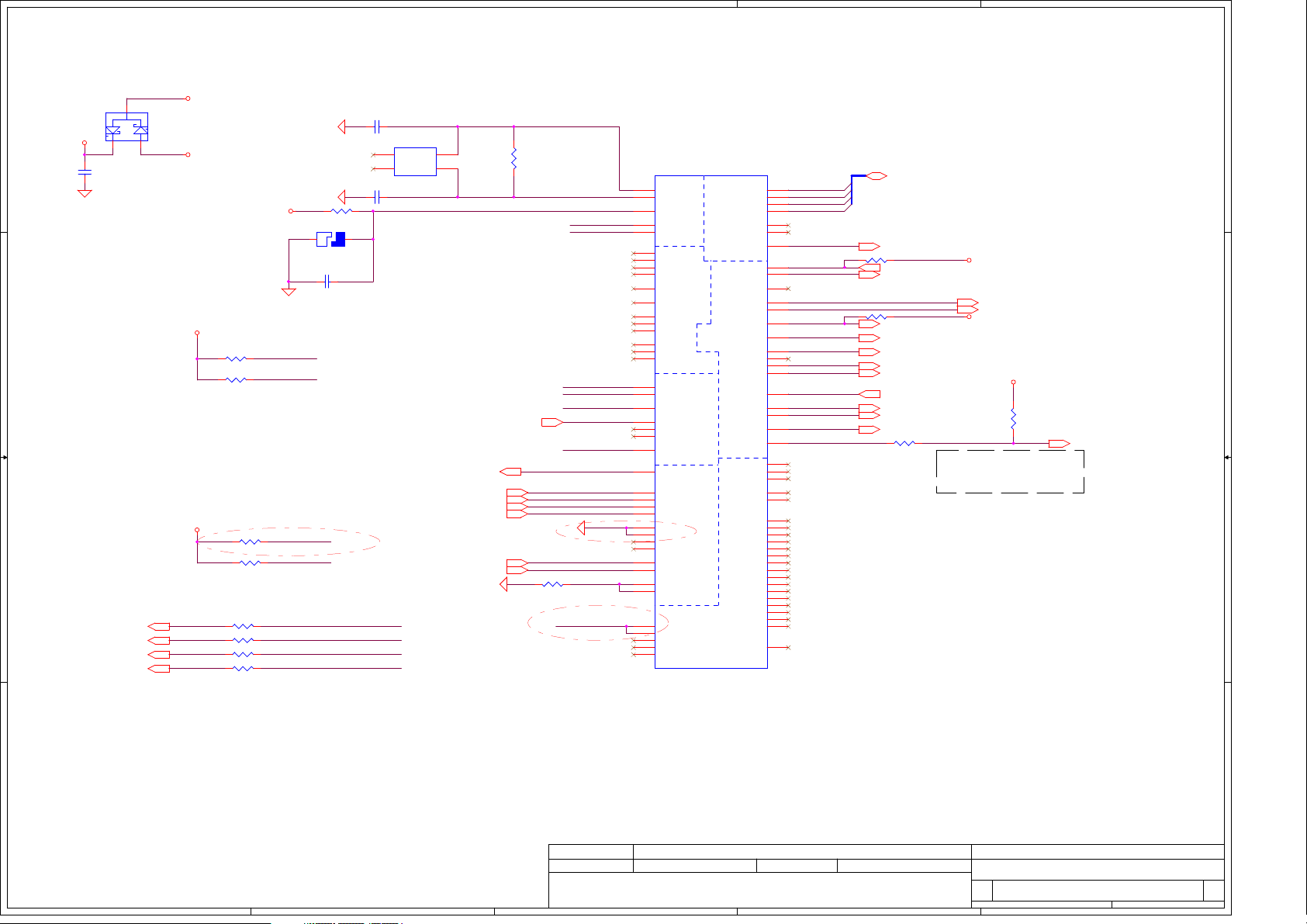

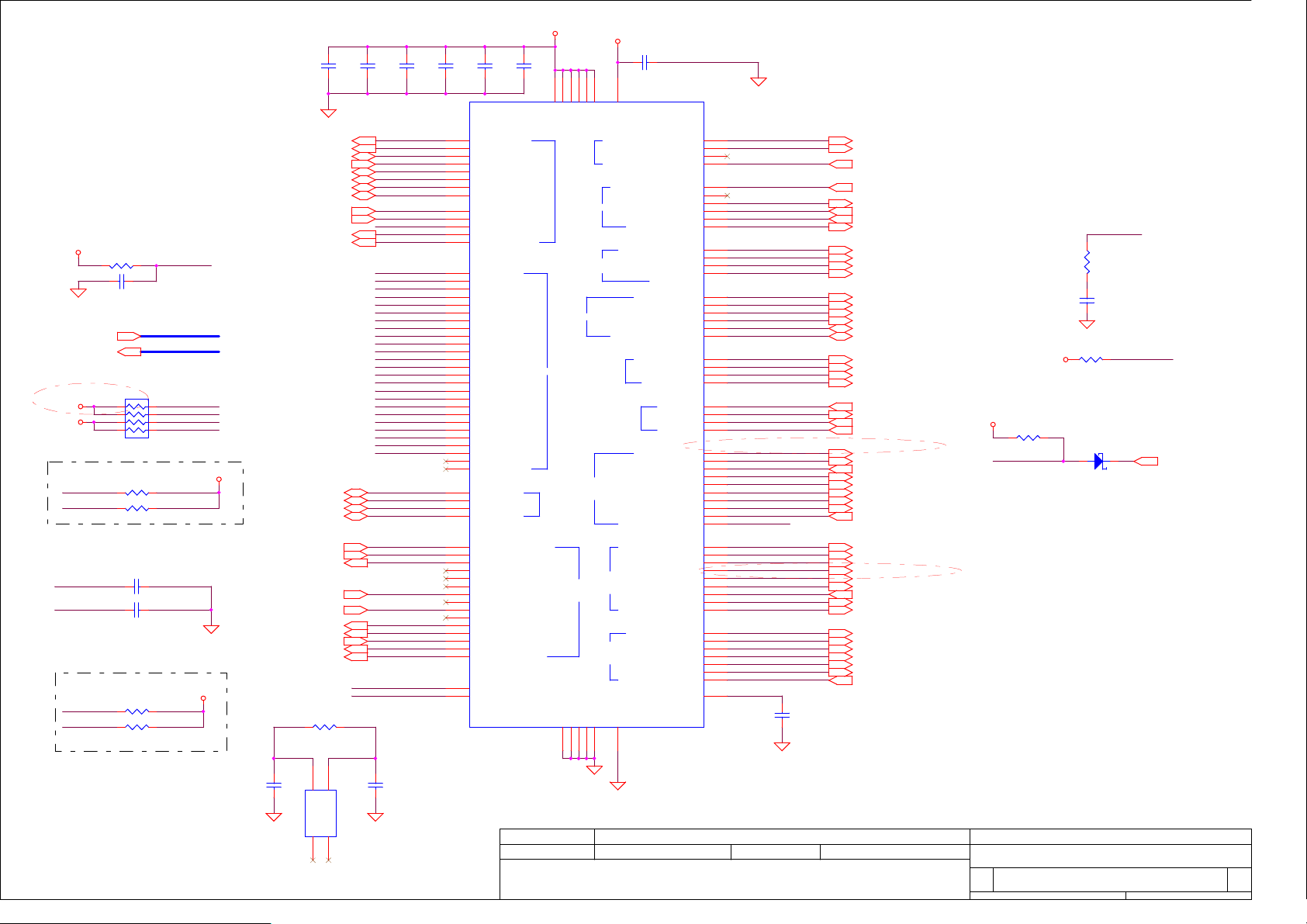

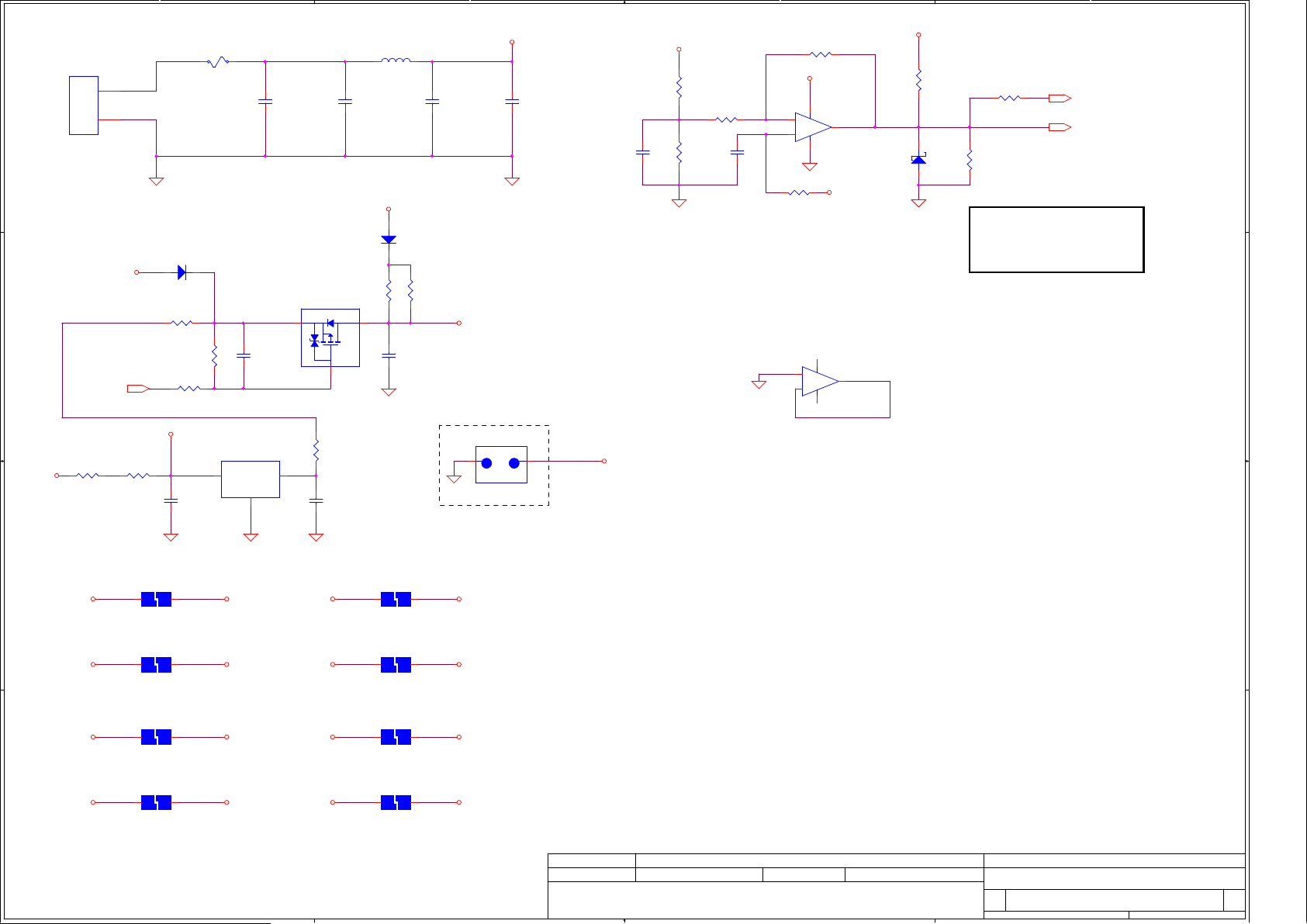

5

H_ A#[3..1 6]<6>

H_A #3

H_A #4

H_A #5

H_A #6

H_A #7

H_A #8

H_A #9

H_A #10

H_A #11

H_A #12

D D

H_A DSTB#0<6>

H_ REQ# [0..4]<6>

H_ A#[17.. 31]< 6>

C C

H_A DSTB#1<6>

H_A20M#<16>

H_ FERR#<16>

H_ IGNNE#< 16>

H_S TPCLK#<16>

H_ INTR<16>

H_ NMI<16>

H_S MI#<16>

+1.05VS

R11 1K_0402 _5%

1 2

R12 1K_0402 _5%

1 2

R16 1K_0402 _5%

1 2

R17 1K_0402 _5%

1 2

B B

+1.05VS

mou nt R1 8, R1 9 fo r KI Z00 proj ect

R18 1K_0402 _5%@

1 2

R19 1K_0402 _5%@

1 2

R23 1K_0402 _5%@

1 2

R24 1K_0402 _5%@

1 2

R25 1K_0402 _5%@

1 2

R26 1K_0402 _5%@

1 2

R27 1K_0402 _5%@

1 2

R28 1K_0402 _5%@

1 2

R29 1K_0402 _5%@

1 2

H_A #13

H_A #14

H_A #15

H_A #16

H_A DSTB#0

H_A P0

T1

H_R EQ#0

PAD

H_R EQ#1

H_R EQ#2

H_R EQ#3

H_R EQ#4

H_A #17

H_A #18

H_A #19

H_A #20

H_A #21

H_A #22

H_A #23

H_A #24

H_A #25

H_A #26

H_A #27

H_A #28

H_A #29

H_A #30

H_A #31

H_A #32

H_A #33

H_A #34

H_A #35

H_A DSTB#1

H_A P1

T6 PAD

H_A20M#

H_ FERR #

H_ IGNNE # CL K_CPU _BCLK#

H_S TPCLK#

H_ INTR

H_ NMI

H_S MI#

CRB rese rved

12/1 8 Re ser ve f or d ebug close

to S outh Brid ge

H_ FERR #

2/2 5 PVT :M ou nt C4 84~C 495 for E MI r eque st

H_S TPCLK#

H_ INIT#_ R

A A

H_A20M#

H_ IGNNE #

H_D PRSTP#

H_ DPWR #

H_D PSLP#

H_ INTR

H_ NMI

H_S MI#

H_P WRGO OD

12/1 8 Re ser ve f or d ebug close

to C PU

C484 220P_04 02_50V7K

1 2

C485 220P_04 02_50V7K

1 2

C486 220P_04 02_50V7K

1 2

C487 220P_04 02_50V7K

1 2

C488 220P_04 02_50V7K

1 2

C489 220P_04 02_50V7K

1 2

C490 220P_04 02_50V7K

1 2

C491 220P_04 02_50V7K

1 2

C492 220P_04 02_50V7K

1 2

C493 220P_04 02_50V7K

1 2

C494 220P_04 02_50V7K

1 2

C495 220P_04 02_50V7K

1 2

5

U1A

P21

A[3]#

H20

A[4]#

N20

A[5]#

R20

A[6]#

J19

A[7]#

N19

A[8]#

G20

A[9]#

M19

A[10]#

H21

A[11]#

L20

A[12]#

M20

A[13]#

K19

A[14]#

J20

A[15]#

L21

A[16]#

K20

ADSTB[0]#

D17

AP0

N21

REQ[0]#

J21

REQ[1]#

G19

REQ[2]#

P20

REQ[3]#

R19

REQ[4]#

C19

A[17]#

F19

A[18]#

E21

A[19]#

A16

A[20]#

D19

A[21]#

C14

A[22]#

C18

A[23]#

C20

A[24]#

E20

A[25]#

D20

A[26]#

B18

A[27]#

C15

A[28]#

B16

A[29]#

B17

A[30]#

C16

A[31]#

A17

A[32]#

B14

A[33]#

B15

A[34]#

A14

A[35]#

B19

ADSTB[1]#

M18

AP1

U18

A20M#

T16

FERR#

J4

IGNNE#

R16

STPCLK#

T15

LINT0

R15

LINT1

U17

SMI#

D6

NC1

G6

NC2

H6

NC3

K4

NC4

K5

NC5

M15

NC6

L16

NC7

AU8 0586GE 025512_FCBG A437

H_A #32

H_A #33

H_A #34

H_A #35

H_A20M#

H_ IGNNE #

H_D PRSTP#

H_ DPWR #

H_D PSLP#

H_ INTR

H_ NMI

H_S MI#

H_P WRGO OD

ADS#

BNR#

BPRI#

ADDR

GROUP

0

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

ADDR GROUP 1

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

BR1#

PROCHOT#

XDP /I TP S IGNAL S

THRMDA

THRMDC

THERMTRIP#

THERM

BCLK[0]

BCLK[1]

H CL K

RSVD3

RSVD2

NC

RSVD1

N7@

.

+1.05VS

+CP U_GTLREF

1

0.1U _0402_16 V4Z

C1

2

Close to CPU pin

within 500mils.

Zo=55ohm

+1.05VS

R32 56_0402 _5%

1 2

R33 56_0402 _5%

1 2

R34 56_0402 _5%

1 2

R35 56_0402 _5%

1 2

R36 56_0402 _5%

1 2

R37 56_0402 _5%

1 2

This shall place near CPU

V19

Y19

U21

T21

T19

Y18

T20

F16

V16

W20

D15

W18

Y17

U20

W19

AA17

V20

K17

J18

H15

J15

K18

J16

M17

N16

M16

L17

K16

V15

G17

E4

E5

H17

V11

V12

C21

C1

A3

12

R13

1K_0402 _1%

12

R20

2K_0402 _1%

4

H_A DS#

H_ BNR#

H_ BPRI#

H_ DEFER #

H_ DR DY#

H_ DBSY#

H_B R0#

H_ IERR#

H_ INIT#_ R

H_L OCK#

H_R ESET#

H_R S#0

H_R S#1

H_R S#2

H_ TRDY#

H_ HIT#

H_H ITM#

PRE Q#

ITP_TCK

ITP_ TDI

ITP_TD O

ITP_TMS

ITP_TRST#

H_P ROCHOT #_R

H_T HERMDA

H_ THERMD C

H_T HERMTRIP#

CLK _CPU_B CLK

4

H_A DS# <6>

H_ BNR# <6>

H_ BPRI# <6>

H_ DEFER # <6>

H_ DR DY# <6>

H_ DBSY# <6 >

H_B R0# <6>

R3 1K_0402 _5%

1 2

H_L OCK# <6>

H_R ESET# <6>

H_ TRDY# <6 >

H_H IT# <6>

H_H ITM# <6>

1 2

R4 22_0402_5 %

H_T HERMTRIP# < 6,16>

CLK _CPU_B CLK <12>

CLK _CPU_B CLK# <12>

+CP U_EXTBGREF

C2

1U_ 0402_6.3V 4Z

Close to CPU

Close to CPU

+1.05VS

12

R14

1K_0402 _1%

12

1

R21

2K_0402 _1%

2

Close to CPU pin

within 500mils.

Zo=55ohm

ITP_TMS

ITP_ TDI

PRE Q#

ITP_TD O

ITP_TCK

ITP_TRST#

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+1.05VS +1.05VS

12

R1

56_0402 _5%

12

H_ RS#[0 ..2] <6>

H_P ROCHOT # <37>

+CP U_GTLREF

0.1U _0402_16 V4Z

Close to CPU pin

within 500mils.

Zo=55ohm

3

H_ D#[0 ..15]<6 >

R2

330_040 2_5%

H_ INIT# <16>

H_D STBN#0<6>

H_D STBP#0<6>

H_ DINV#0<6>

H_ D#[16 ..31]<6>

H_D STBN#1<6>

H_D STBP#1<6>

H_ DINV#1<6>

R6 1K_ 0402_5%@

1 2

R8 1K_ 0402_5%@

1 2

+CP U_EXTBGREF

CPU _BSEL0<6,12>

CPU _BSEL1<6,12>

CPU _BSEL2<6,12>

+1.05VS

12

1

2

R15

1K_0402 _1%

12

R22

2K_0402 _1%

Compal Secret Data

Deciphered Date

+CP U_CMRE F

C3

2008/11/17 2009/11/17

3

H_ D#0

H_ D#1

H_ D#2

H_ D#3

H_ D#4

H_ D#5

H_ D#6

H_ D#7

H_ D#8

H_ D#9

H_D #10

H_D #11

H_D #12

H_D #13

H_D #14

H_D #15

H_D STBN#0

H_D STBP#0

H_ DINV# 0

H_D P#0

T2 PAD

H_D #16

H_D #17

H_D #18

H_D #19

H_D #20

H_D #21

H_D #22

H_D #23

H_D #24

H_D #25

H_D #26

H_D #27

H_D #28

H_D #29

H_D #30

H_D #31

H_D STBN#1 H_D STBN#3

H_D STBP#1

H_ DINV# 1

H_D P#1

T4 PAD

ACL KPH

DC LKPH

CPU _BSEL0

CPU _BSEL1

CPU _BSEL2

Layo ut n ote:

COMP 0,2 connect wit h Z o=27 .4ohm + /-15%, make

trac e le ngth sh orte r than 0.5"

COMP 1,3 connect wit h Z o=55 ohm +/-15%, make

trac e le ngth sh orte r than0.5"

H_TH ERMD A, H_TH ERMD C r outing together.

Trac e wi dth / S paci ng = 10 / 10 mil

C5

1 2

1 2

+3VS

R31 10K_040 2_5%

2

U1B

Y11

W10

Y12

AA14

AA11

W12

AA16

Y10

Y9

Y13

W15

AA13

Y16

W13

AA9

W9

Y14

Y15

W16

V9

AA5

Y8

W3

U1

W7

W6

Y7

AA6

Y3

W2

V3

U2

T3

AA8

V2

W4

Y4

Y5

Y6

R4

A7

U5

V5

T17

R6

M6

N15

N6

P17

T6

J6

H5

G5

AU8 0586GE 025512_FCBG A437

+3VS

1

C4

2

0.1 U_0402_ 16V4Z

H_T HERMDA

H_ THERMD C

2200P_0 402_50V7K

CPU _THERM#

2

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

DP#0

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

DP#1

GTLREF

ACLKPH

DCLKPH

BINIT#

EDM

EXTBGREF

FORCEPR#

HFPLL

MCERR#

RSP#

BSEL[0]

BSEL[1]

BSEL[2]

DATA GRP 0 DATA GRP 1

MI SC

PWRGOOD

CORE_DET

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

DAT A GRP 2

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

DP#2

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

DATA GRP 3

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

DP#3

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

CMREF[1]

N7@

.

R3

R2

P1

N1

M2

P2

J3

N3

G3

H2

N2

L2

M3

J2

H1

J1

K2

K3

L1

M4

C2

G2

F1

D3

B4

E1

A5

C3

A6

F2

C6

B6

B3

C4

C7

D2

E2

F3

C5

D4

T1

T2

F20

F21

R18

R17

U4

V17

N18

A13

B7

CPU THERMAL SENSOR

U2

1

VDD

2

DP

3

DN

4

THERM#

EMC 1402-1-ACZ L-TR_MSOP8

Addres s:0100_1100 EMC1402-1

Addres s:0100_1101 EMC1402-2

SMCLK

SMDATA

ALERT#

GND

Title

Size Do cumen t Numb er R ev

Cu stom

Da te: Sheet o f

1

H_D #32

H_D #33

H_D #34

H_D #35

H_D #36

H_D #37

H_D #38

H_D #39

H_D #40

H_D #41

H_D #42

H_D #43

H_D #44

H_D #45

H_D #46

H_D #47

H_D STBN#2

H_D STBP#2

H_ DINV# 2

H_D P#2

H_D #48

H_D #49

H_D #50

H_D #51

H_D #52

H_D #53

H_D #54

H_D #55

H_D #56

H_D #57

H_D #58

H_D #59

H_D #60

H_D #61

H_D #62

H_D #63

H_D STBP#3

H_ DINV# 3

H_D P#3

COMP0

COMP1

COMP2

COMP3

H_D PRSTP#

H_D PSLP#

H_ DPWR #

H_P WRGO OD

H_C PUSLP#

EC_ SMB_CK2

8

EC_ SMB_DA2

7

6

5

1 2

1 2

R30 10K_0 402_5%@

H_ D#[32 ..47] <6>

H_D STBN#2 <6>

H_D STBP#2 <6>

H_ DINV#2 < 6>

T3PAD

H_ D#[48 ..63] <6>

H_D STBN#3 <6>

H_D STBP#3 <6>

H_ DINV#3 < 6>

T5PAD

R5 27.4 _0402_1%

R7 54.9 _0402_1%

R9 27.4 _0402_1%

12

R10 54 .9_0402_1%

12

H_D PRSTP# <16,37 >

H_D PSLP# <16>

H_D PWR# < 6>

H_P WRGO OD <16>

H_C PUSLP# <6 >

+CP U_CMR EF

EC_ SMB_CK2 <26,27 >

EC_ SMB_DA2 <26,27 >

12

Compal Electronics, Inc.

Diamondville(1/2)

KAVAA LA-5121P M/B

1

+3VS

1.0

4 42Tu esday, M arch 10 , 2009

5

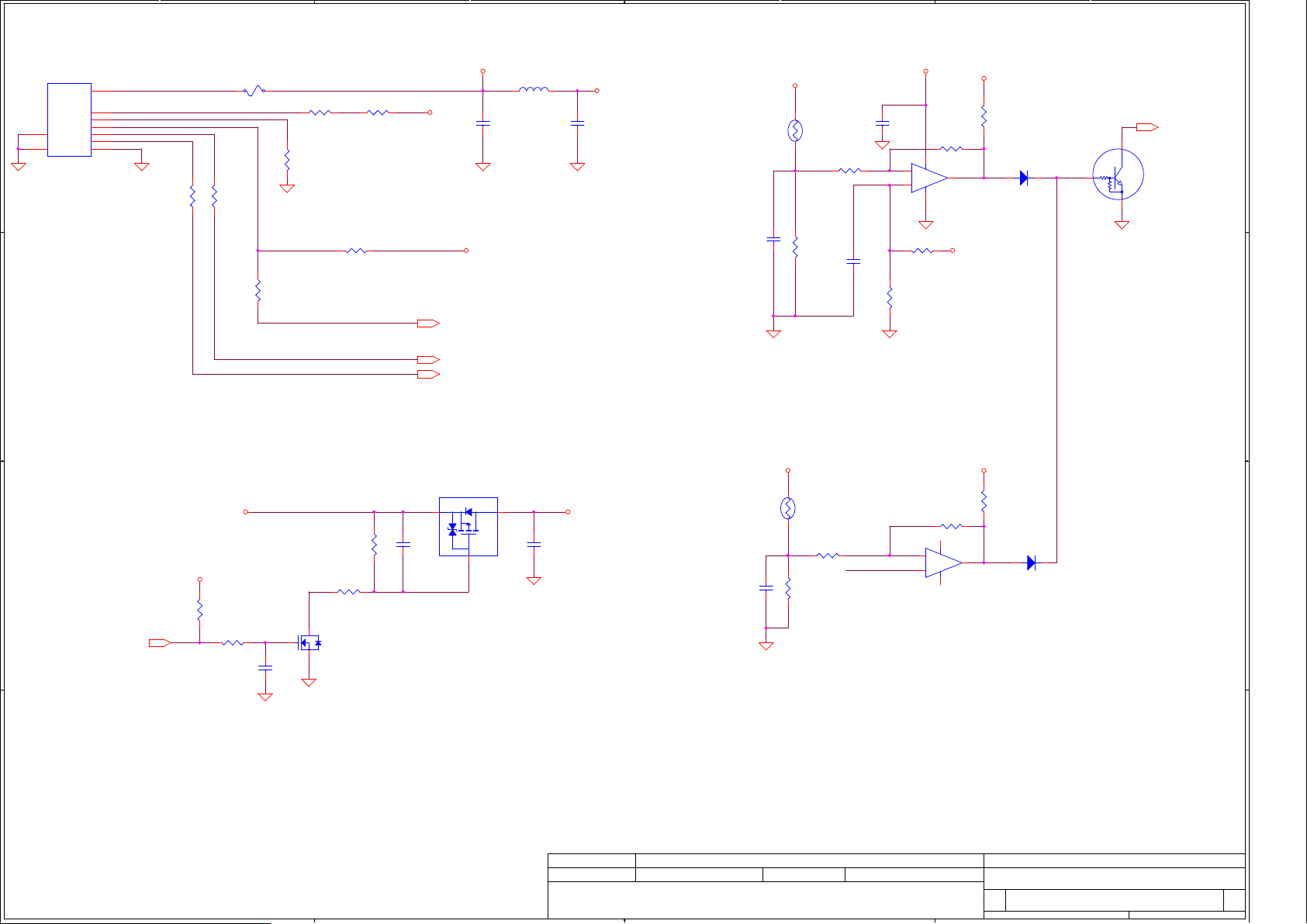

4

3

2

1

1

2

+1.5VS

1

2

1

C25

2

1U_ 0402_6.3V6K

1

C41

2

10U _0805_10V4 Z

+1.05VS

1

+

C7

220 U_B2_2.5VM _R35

2

C12

0.1U _0402_16V7 K

+CP U_COR E

12

12

1U_ 0402_6.3V6K

1

1

C26

2

2

10U _0805_10V4 Z

1

1

C42

2

2

max 1700mA ESR:21~35m ohm

R38

100_040 2_1%

VC CSENSE < 37>

VSS SENSE <37>

R39

100_040 2_1%

1U_ 0402_6.3V6K

1

C27

2

1U_ 0402_6.3V6K

C28

1

2

Length match within 25 mils

The trace space 7 mils,

Zo=27.4ohm

1

C29

2

1U_ 0402_6.3V6K

1U_ 0402_6.3V6K

1

C30

2

+CP U_COR E

2 x 330uF(9mohm/2)

1

+

C13

330 U_D2_2 .5VY_R9M

2

1

+

C14

330 U_D2_2 .5VY_R9M

2

U1 D

A2

VSS1

A4

VSS2

A8

VSS4

A15

VSS5

A18

VSS6

A19

VSS7

A20

VSS8

B1

VSS9

B2

VSS10

D D

C C

B B

A A

B5

VSS11

B8

VSS12

B13

VSS13

B20

VSS14

B21

VSS15

C8

VSS16

C17

VSS17

D1

VSS18

D5

VSS19

D8

VSS20

D14

VSS21

D18

VSS22

D21

VSS23

E3

VSS24

E6

VSS25

E7

VSS26

E8

VSS27

E15

VSS28

E16

VSS29

E19

VSS30

F4

VSS31

F5

VSS32

F6

VSS33

F7

VSS34

F17

VSS35

F18

VSS36

G1

VSS37

G4

VSS38

G7

VSS39

G9

VSS41

G13

VSS42

G21

VSS45

H3

VSS46

H4

VSS48

H7

VSS49

H9

VSS51

H13

VSS52

H16

VSS53

H18

VSS54

H19

VSS55

J5

VSS56

J7

VSS57

J9

VSS58

J13

VSS59

J17

VSS60

K1

VSS61

K6

VSS62

K7

VSS63

K9

VSS64

K13

VSS65

K15

VSS66

K21

VSS67

L3

VSS68

L4

VSS69

L5

VSS70

L6

VSS71

L7

VSS72

L9

VSS73

L13

VSS74

L15

VSS75

L18

VSS76

L19

VSS77

M1

VSS78

M5

VSS79

M7

VSS80

M9

VSS81

M13

VSS82

M21

VSS83

N4

VSS84

AU8 0586GE 025512_FCBG A437

N7@

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

N5

N7

N9

N13

N17

P3

P4

P5

P6

P7

P9

P13

P15

P16

P18

P19

R1

R5

R7

R9

R13

R21

T4

T5

T7

T9

T10

T11

T12

T13

T18

U3

U6

U7

U15

U16

U19

V1

V4

V6

V7

V8

V13

V14

V18

V21

W1

W5

W8

W11

W14

W17

W21

Y1

Y2

Y20

Y21

AA2

AA3

AA4

AA7

AA10

AA12

AA15

AA18

AA19

AA20

+1.05VS

+CP U_COR E

.

+CP U_COR E

1

C15

2

1U_ 0402_6.3V6K

1

C31

2

10U _0805_10V4 Z

U1 C

V10

VCCF

A9

VCCQ1

B9

VCCQ2

A10

VCCP1

A11

VCCP2

A12

VCCP3

B10

VCCP4

B11

VCCP5

B12

VCCP6

C10

VCCP7

C11

VCCP8

C12

VCCP9

D10

VCCP10

D11

VCCP11

D12

VCCP12

E10

VCCP13

E11

VCCP14

E12

VCCP15

F10

VCCP16

F11

VCCP17

F12

VCCP18

G10

VCCP19

G11

VCCP20

G12

VCCP21

H10

VCCP22

H11

VCCP23

H12

VCCP24

J10

VCCP25

J11

VCCP26

J12

VCCP27

K10

VCCP28

K11

VCCP29

K12

VCCP30

L10

VCCP31

L11

VCCP32

L12

VCCP33

M10

VCCP34

M11

VCCP35

M12

VCCP36

N10

VCCP37

N11

VCCP38

N12

VCCP39

P10

VCCP40

P11

VCCP41

P12

VCCP42

R10

VCCP43

R11

VCCP44

R12

VCCP45

AU8 0586GE 025512_FCBG A437

N7@

1U_ 0402_6.3V6K

1

1

C17

C16

2

2

1U_ 0402_6.3V6K

10U _0805_10V4 Z

1

1

C33

C32

2

2

10U _0805_10V4 Z

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VCCPC64

VCCPC63

VCCPC62

VCCPC61

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

PLACE IN CAVITY

1U_ 0402_6.3V6K

1

C18

2

1U_ 0402_6.3V6K

10U _0805_10V4 Z

1

C35

C34

2

10U _0805_10V4 Z

C9

D9

E9

F8

F9

G8

G14

H8

H14

J8

J14

K8

K14

L8

L14

M8

M14

N8

N14

P8

P14

R8

R14

T8

T14

U8

U9

U10

U11

U12

U13

U14

F14

F13

E14

E13

D7

F15

D16

E18

G15

G16

E17

G18

C13

D13

C19

+1.5VS

CP U_VID 0

CP U_VID 1

CP U_VID 2

CP U_VID 3

CP U_VID 4

CP U_VID 5

CP U_VID 6

.

VC CSENSE

VSS SENSE

1U_ 0402_6.3V6K

1

C20

2

10U _0805_10V4 Z

1

C36

2

0.1U _0402_16V7 K

1

C21

2

1U_ 0402_6.3V6K

1

C37

2

10U _0805_10V4 Z

0.1U _0402_16V7 K

1

C9

C8

2

CP U_VID0 < 37>

CP U_VID1 < 37>

CP U_VID2 < 37>

CP U_VID3 < 37>

CP U_VID4 < 37>

CP U_VID5 < 37>

CP U_VID6 < 37>

1U_ 0402_6.3V6K

1

1

C22

2

2

10U _0805_10V4 Z

1

1

C38

2

2

2500mA

1U_ 0402_6.3V6K

1

1

C11

C10

2

2

1U_ 0402_6.3V6K

PLACE IN CAVITY

130mA

1U_ 0402_6.3V6K

1

C23

C24

2

1U_ 0402_6.3V6K

10U _0805_10V4 Z

1

C40

C39

2

10U _0805_10V4 Z

PLACE IN CORRIDOR AND CLOSE TO CPU

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/11/17 2009/11/17

3

Compal Secret Data

Deciphered Date

Title

Size Do cumen t Numb er R ev

Cu stom

2

Da te: Sheet o f

Compal Electronics, Inc.

Diamondville(2/2)

KAVAA LA-5121P M/B

5 42Tu esday, M arch 10 , 2009

1

1.0

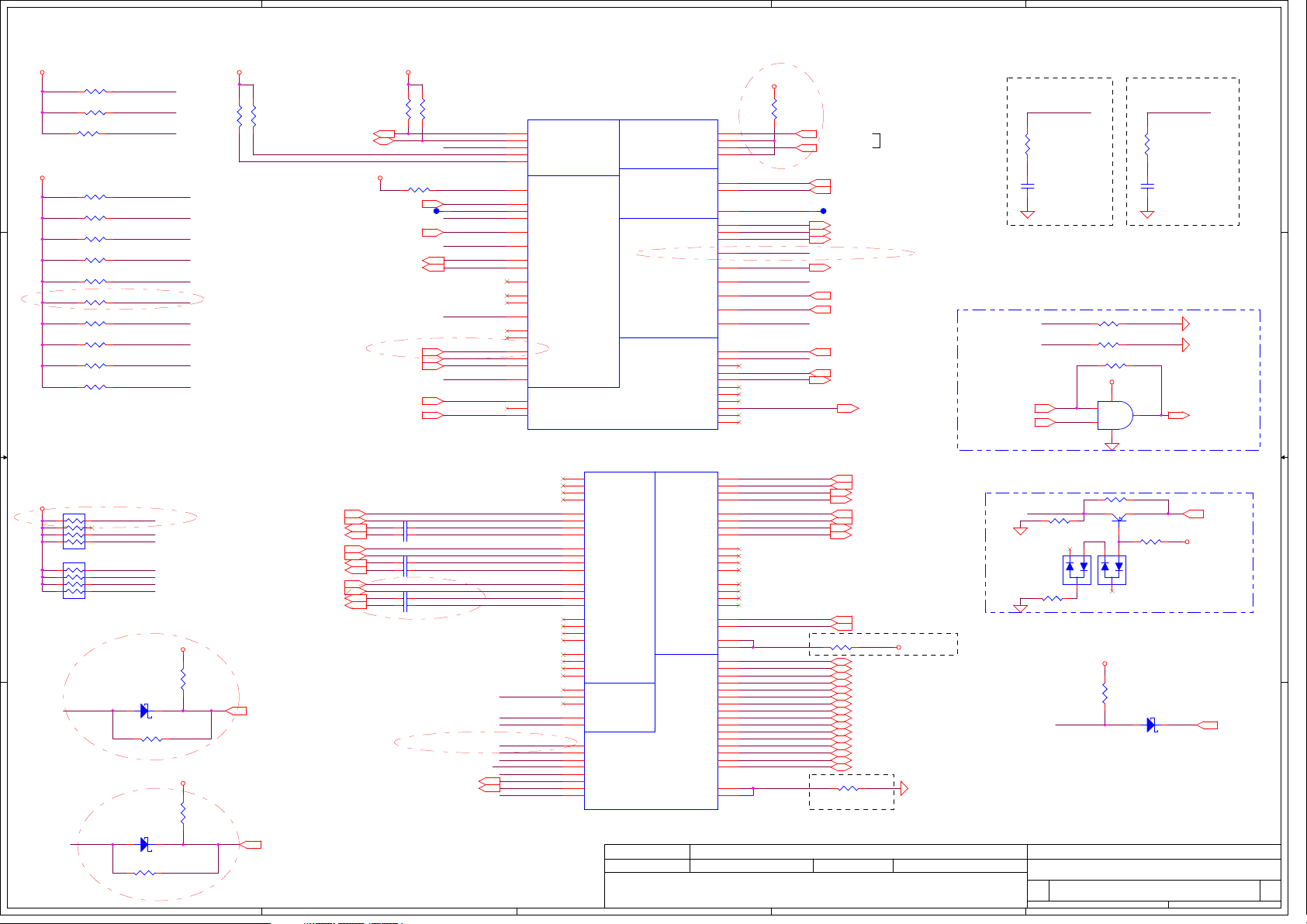

5

4

3

2

1

H_ D#[0. .63]<4 >

D D

C C

+1.05VS

12

12

B B

A A

R4 8

R4 7

54. 9_0402_1%

54. 9_0402_1%

12

R5 3

R5 2

24. 9_0402_1%

24. 9_0402_1%

12

H_ D#0

H_ D#1

H_ D#2

H_ D#3

H_ D#4

H_ D#5

H_ D#6

H_ D#7

H_ D#8

H_ D#9

H_D #10

H_D #11

H_D #12

H_D #13

H_D #14

H_D #15

H_D #16

H_D #17

H_D #18

H_D #19

H_D #20

H_D #21

H_D #22

H_D #23

H_D #24

H_D #25

H_D #26

H_D #27

H_D #28

H_D #29

H_D #30

H_D #31

H_D #32

H_D #33

H_D #34

H_D #35

H_D #36

H_D #37

H_D #38

H_D #39

H_D #40

H_D #41

H_D #42

H_D #43

H_D #44

H_D #45

H_D #46

H_D #47

H_D #48

H_D #49

H_D #50

H_D #51

H_D #52

H_D #53

H_D #54

H_D #55

H_D #56

H_D #57

H_D #58

H_D #59

H_D #60

H_D #61

H_D #62

H_D #63

H_XRCOM P

H_XSCOM P

+H_ SWNG0

H_ YRCO MP

H_ YSCOMP

+H_ SWNG1

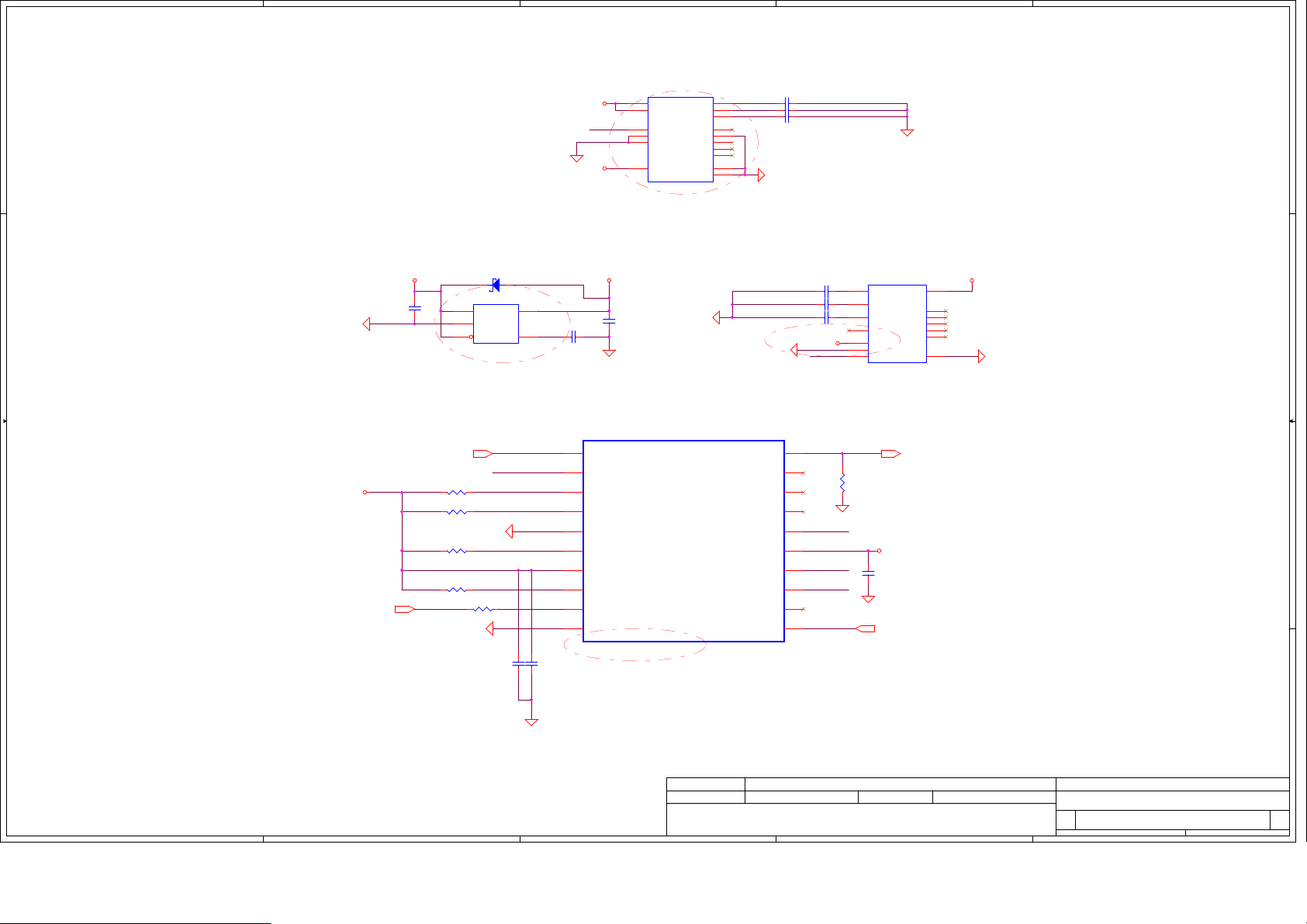

U3A

C4

H_D#_0

F6

H_D#_1

H9

H_D#_2

H6

H_D#_3

F7

H_D#_4

E3

H_D#_5

C2

H_D#_6

C3

H_D#_7

K9

H_D#_8

F5

H_D#_9

J7

H_D#_10

K7

H_D#_11

H8

H_D#_12

E5

H_D#_13

K8

H_D#_14

J8

H_D#_15

J2

H_D#_16

J3

H_D#_17

N1

H_D#_18

M5

H_D#_19

K5

H_D#_20

J5

H_D#_21

H3

H_D#_22

J4

H_D#_23

N3

H_D#_24

M4

H_D#_25

M3

H_D#_26

N8

H_D#_27

N6

H_D#_28

K3

H_D#_29

N9

H_D#_30

M1

H_D#_31

V8

H_D#_32

V9

H_D#_33

R6

H_D#_34

T8

H_D#_35

R2

H_D#_36

N5

H_D#_37

N2

H_D#_38

R5

H_D#_39

U7

H_D#_40

R8

H_D#_41

T4

H_D#_42

T7

H_D#_43

R3

H_D#_44

T5

H_D#_45

V6

H_D#_46

V3

H_D#_47

W2

H_D#_48

W1

H_D#_49

V2

H_D#_50

W4

H_D#_51

W7

H_D#_52

W5

H_D#_53

V5

H_D#_54

AB4

H_D#_55

AB8

H_D#_56

W8

H_D#_57

AA9

H_D#_58

AA8

H_D#_59

AB1

H_D#_60

AB7

H_D#_61

AA2

H_D#_62

AB5

H_D#_63

A10

H_XRCOMP

A6

H_XSCOMP

C15

H_XSWING

J1

H_YRCOMP

K1

H_YSCOMP

H1

H_YSWING

QG8 2945GS E SLB2 R A3_FCBGA998

H_ADSTB#_0

H_ADSTB#_1

HOST

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

PM_EXTTS#0

PM_EXTTS#1

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_VREF0

H_BNR#

H_BPRI#

H_BREQ0#

H_CPURST#

H_VREF1

HCLKN

HCLKP

H_DBSY#

H_DEFER#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

1 2

R57 10K_0 402_5%

1 2

R58 10K_0 402_5%

F8

D12

C13

A8

E13

E12

J12

B13

A13

G13

A12

D14

F14

J13

E17

H15

G15

G14

A15

B18

B15

E14

H13

C14

A17

E15

H17

D17

G17

F10

C12

H16

E2

B9

C7

G8

B10

E1

AA6

AA5

C10

C6

H5

J6

T9

U6

G7

E6

F3

M8

T1

AA3

F4

M7

T2

AB3

C8

B4

C5

G9

E9

G12

B8

F12

A5

B6

G10

E8

E10

@

H_A #3

H_A #4

H_A #5

H_A #6

H_A #7

H_A #8

H_A #9

H_A #10

H_A #11

H_A #12

H_A #13

H_A #14

H_A #15

H_A #16

H_A #17

H_A #18

H_A #19

H_A #20

H_A #21

H_A #22

H_A #23

H_A #24

H_A #25

H_A #26

H_A #27

H_A #28

H_A #29

H_A #30

H_A #31

H_A DS#

H_A DSTB#0

H_A DSTB#1

+H_ VREF

H_ BNR#

H_ BPRI#

H_B R0#

H_R ESET#

+H_ VREF

CLK _MCH_B CLK#

CLK _MCH_B CLK

H_ DBSY#

H_ DEFER #

H_ DINV# 0

H_ DINV# 1

H_ DINV# 2

H_ DINV# 3

H_ DPWR #

H_ DR DY#

H_D STBN#0

H_D STBN#1

H_D STBN#2

H_D STBN#3

H_D STBP#0

H_D STBP#1

H_D STBP#2

H_D STBP#3

H_ HIT#

H_H ITM#

H_L OCK#

H_R EQ#0

H_R EQ#1

H_R EQ#2

H_R EQ#3

H_R EQ#4

H_R S#0

H_R S#1

H_R S#2

H_C PUSLP#

H_ TRDY#

+3VS

H_ A#[3..3 1] <4>

H_A DS# <4>

H_A DSTB#0 <4>

H_A DSTB#1 <4>

H_ BNR# <4>

H_ BPRI# <4>

H_B R0# <4>

H_R ESET# <4>

CLK _MCH_B CLK# <12>

CLK _MCH_B CLK <12>

H_ DBSY# <4 >

H_ DEFER # <4>

H_ DINV#0 < 4>

H_ DINV#1 < 4>

H_ DINV#2 < 4>

H_ DINV#3 < 4>

H_ DPWR # <4>

H_ DR DY# <4>

H_ DSTBN #[0..3] <4>

H_D STBP# [0..3] <4>

H_ HIT# <4>

H_H ITM# <4>

H_L OCK# <4>

H_ REQ# [0..4] <4>

H_ RS#[ 0..2] <4>

H_C PUSLP# < 4>

H_ TRDY# <4 >

DMI_TXN0< 17>

DMI_TXN1< 17>

DMI_TXP0<17>

DMI_TXP1<17>

DMI_R XN0<17 >

DMI_R XN1<17 >

DMI_RX P0< 17>

DMI_RX P1< 17>

M_C LK_DDR 0<11>

M_C LK_DDR 1<11>

M_C LK_DDR #0<11>

M_C LK_DDR #1<11>

DD R_CKE 0<11>

DD R_CKE 1<11>

DD R_CS0 #<11>

DD R_CS1 #<11>

+1.8V

R44 80.6 _0402_1%

1 2

1 2

R46 80.6 _0402_1%

+DIMM _VREF

1

C4 3

2

Layo ut Note:

H_XR COMP / H_YR COMP / H_VREF / H_SWNG0 /

H_SW NG1 trace w idth an d spacing is 10/20.

+1.05VS

12

R5 1

100_0 402_1%

12

C4 6

R5 6

200_0 402_1%

M_ODT0<11>

M_ODT1<11>

10uA

Layout Note:

+DIMM_ VREF trace

width and spacing

0.1 U_0402_ 16V4Z

is 20/20.

+H_ VREF

1

2

0.1 U_0402_ 16V4Z

U3B

DMI_TXN0

DMI_TXN1

DMI_TXP0

DMI_TXP1

DMI_R XN0

DMI_R XN1

DMI_RX P0

DMI_RX P1

M_C LK_DDR0

M_C LK_DDR1

M_C LK_DDR# 0

M_C LK_DDR# 1

DD R_CKE 0

DD R_CKE 1

DD R_CS0 #

DD R_CS1 #

M_ODT0

M_ODT1

SMR COMPN

SMR COMPP

C44 ,C45,C46 be placed

<100mils from GMCH pin

Y29

DMI_RXN_0

Y32

DMI_RXN_1

Y28

DMI_RXP_0

Y31

DMI_RXP_1

V28

DMI_TXN_0

V31

DMI_TXN_1

V29

DMI_TXP_0

V32

DMI_TXP_1

AF33

SM_CK_0

AG1

SM_CK_1

AJ1

SM_CK_2

AM30

SM_CK_3

AG33

SM_CK#_0

AF1

SM_CK#_1

AK1

SM_CK#_2

AN30

SM_CK#_3

AN21

SM_CKE_0

AN22

SM_CKE_1

AF26

SM_CKE_2

AF25

SM_CKE_3

AG14

SM_CS#_0

AF12

SM_CS#_1

AK14

SM_CS#_2

AH12

SM_CS#_3

AJ21

SM_OCDCOMP_0

AF11

SM_OCDCOMP_1

AE12

SM_ODT_0

AF14

SM_ODT_1

AJ14

SM_ODT_2

AJ12

SM_ODT_3

AN12

SM_RCOMPN

AN14

SM_RCOMPP

AA33

SM_VREF_0

AE1

SM_VREF_1

QG8 2945GS E SLB2 R A3_FCBGA998

DMI

DDR2 MUXING

CFG_0

CFG_1

CFG_2

CFG_3

CFG_5

CFG_6

RESERVED1

RESERVED2

RESERVED7

RESERVED8

RESERVED9

CFG/RSVD

PM_ICHSYNC#

PM_BMBUSY#

PM_EXTTS#_0

PM

PM_EXTTS#_1

THRMTRIP#

PWROK

RSTIN#

D_REFCLKN

D_REFCLKP

CLK

D_REFSSCLKN

D_REFSSCLKP

CLKREQ#

+1.05VS

12

R4 9

221_0 402_1%

12

R5 4

100_0 402_1%

C4 4

C18

E18

G20

G18

J20

J18

K32

K31

C17

F18

A3

MCH _CLKSEL0

MCH _CLKSEL1

MCH _CLKSEL2

CF G3

CF G5

CF G6

R403 1K_04 02_5%

1 2

R404 1K_04 02_5%

1 2

R405 1K_04 02_5%

1 2

R40 2.2K_ 0402_5%@

1 2

R41 2.2K_ 0402_5%

1 2

R42 2.2K_ 0402_5%@

1 2

Strap Pin Table

CFG[ 2:0] 001=FS B533

CFG3

CFG6

CFG5

2/25 PVT: Change Net Name to ICH_PWROK

E31

G21

F26

H26

J15

AB29

W27

A27

A26

J33

H33

J22

PM_EXTTS#0

PM_EXTTS#1

PLTRST_ R#

H_T HERMTRIP#

ICH _PW ROK

1 2

R45 100_040 2_5%

12

R416 0_0402_5%

MC H_ICH _SYN C# <15>

PM_ BMBUSY# <17>

PM_EXTTS#0 <11>

12

R43 0_ 0402_5%

CLK _MCH_ DREFCL K# <12>

CL K_MCH_ DREFC LK <12>

MC H_SSCD REFCL K# <12>

MC H_SSC DREFCL K <12>

C511

@

22P_040 2_50V8J

2/5 DVT: For WWLAN request

+1.05VS

12

R5 0

221_0 402_1%

+H_ SWNG0

1

2

0.1 U_0402_ 16V4Z

12

R5 5

+H_ SWNG1

1

C4 5

2

100_0 402_1%

0.1 U_0402_ 16V4Z

000= FSB400

011= FSB667

Rese rved

0=DM I X 2

1=DM I X4

PM_ DPRSLPVR < 17,37>

H_T HERMTRIP# < 4,16>

ICH _PW ROK <17>

PLTRST# < 15,17,1 9,24,28>

MCH _CLKRE Q# <12>

CPU _BSEL0 <4,12 >

CPU _BSEL1 <4,12 >

CPU _BSEL2 <4,12 >

*

*

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/11/17 2009/11/17

3

Compal Secret Data

Deciphered Date

Title

Size Do cumen t Numb er R ev

Cu stom

2

Da te: Sheet o f

Compal Electronics, Inc.

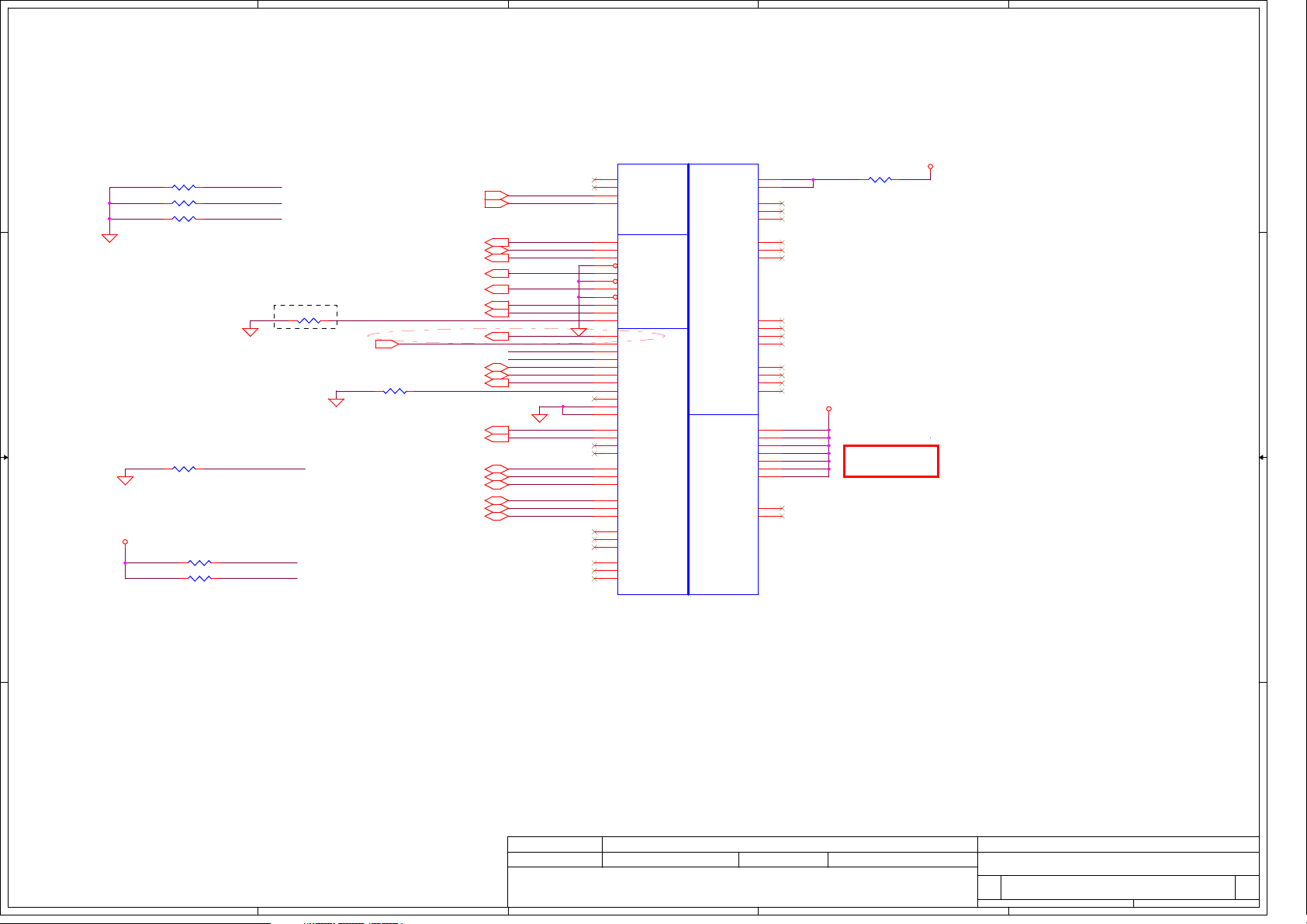

Calistoga(1/5)-GTL/DMI/DDR

KAVAA LA-5121P M/B

6 42Tu esday, M arch 10 , 2009

1

1.0

5

4

3

2

1

D D

C C

B B

DDR _A_BS0<11 >

DDR _A_BS1<11 >

DDR _A_BS2<11 >

DD R_A_ DM[0..7 ]<11>

DD R_A_ DQS[0 ..7]<11>

DD R_A_ DQS#[0 ..7]<11>

DD R_A_M A[0..13 ]<1 1>

DDR _A_CA S#<11>

DDR _A_RA S#<11>

DDR _A_W E#<11>

T7 PAD

T8 PAD

DDR _A_BS0

DDR _A_BS1

DDR _A_BS2

DDR _A_DM0

DDR _A_DM1

DDR _A_DM2

DDR _A_DM3

DDR _A_DM4

DDR _A_DM5

DDR _A_DM6

DDR _A_DM7

DD R_A_DQ S0

DD R_A_DQ S1

DD R_A_DQ S2

DD R_A_DQ S3

DD R_A_DQ S4

DD R_A_DQ S5

DD R_A_DQ S6

DD R_A_DQ S7

DDR _A_DQS #0

DDR _A_DQS #1

DDR _A_DQS #2

DDR _A_DQS #3

DDR _A_DQS #4

DDR _A_DQS #5

DDR _A_DQS #6

DDR _A_DQS #7

DDR _A_MA0

DDR _A_MA1

DDR _A_MA2

DDR _A_MA3

DDR _A_MA4

DDR _A_MA5

DDR _A_MA6

DDR _A_MA7

DDR _A_MA8

DDR _A_MA9

DDR _A_MA10

DDR _A_MA11

DDR _A_MA12

DDR _A_MA13

DD R_A_CA S#

DD R_A_RA S#

SA _RCV ENIN#

SA_ RCVENO UT#

DDR _A_W E#

AK12

AH11

AG17

AB30

AL31

AF30

AK26

AG7

AK5

AH3

AC28

AJ30

AK33

AL25

AN9

AH8

AM2

AE3

AC29

AK30

AJ33

AM25

AN8

AM3

AE2

AJ15

AM17

AM15

AH15

AK15

AN15

AJ18

AF19

AN17

AL17

AG16

AL18

AG18

AL14

AJ17

AK18

AN28

AM28

AH17

AH21

AJ20

AE27

AN20

AL21

AK21

AK22

AL22

AH22

AG22

AF21

AM21

AE21

AL20

AE22

AE26

AE20

AL9

AJ8

U3 C

SA_BS_0

SA_BS_1

SA_BS_2

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

SB_BS_0

SB_BS_1

SB_BS_2

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

DDR2 SYSTEM MEMORY

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SB_CAS#

SB_RAS#

SB_WE#

AB28

AE33

AF32

AC33

AB32

AB31

AE31

AH31

AK31

AL28

AK27

AH30

AL32

AJ28

AJ27

AH32

AF31

AH27

AF28

AJ32

AG31

AG28

AG27

AN27

AM26

AJ26

AJ25

AL27

AN26

AH25

AG26

AM12

AL11

AH9

AK9

AM11

AK11

AM8

AK8

AG9

AF9

AF8

AK6

AF7

AG11

AJ6

AH6

AN6

AM6

AK3

AL2

AM5

AL5

AJ3

AJ2

AG2

AF3

AE7

AF6

AH5

AG3

AG5

AF5

AG19

AG21

AG20

DD R_A_D 1

DD R_A_D 2

DD R_A_D 3

DD R_A_D 4

DD R_A_D 5

DD R_A_D 6

DD R_A_D 7

DD R_A_D 8

DD R_A_D 9

DD R_A_D 10

DD R_A_D 11

DD R_A_D 12

DD R_A_D 13

DD R_A_D 14

DD R_A_D 15

DD R_A_D 16

DD R_A_D 17

DD R_A_D 18

DD R_A_D 19

DD R_A_D 20

DD R_A_D 21

DD R_A_D 22

DD R_A_D 23

DD R_A_D 24

DD R_A_D 25

DD R_A_D 26

DD R_A_D 27

DD R_A_D 28

DD R_A_D 29

DD R_A_D 30

DD R_A_D 31

DD R_A_D 32

DD R_A_D 33

DD R_A_D 34

DD R_A_D 35

DD R_A_D 36

DD R_A_D 37

DD R_A_D 38

DD R_A_D 39

DD R_A_D 40

DD R_A_D 41

DD R_A_D 42

DD R_A_D 43

DD R_A_D 44

DD R_A_D 45

DD R_A_D 46

DD R_A_D 47

DD R_A_D 48

DD R_A_D 49

DD R_A_D 50

DD R_A_D 51

DD R_A_D 52

DD R_A_D 53

DD R_A_D 54

DD R_A_D 55

DD R_A_D 56

DD R_A_D 57

DD R_A_D 58

DD R_A_D 59

DD R_A_D 60

DD R_A_D 61

DD R_A_D 62

DD R_A_D 63

DD R_A_D 0

AC31

DD R_A_ D[0..6 3] <11>

QG8 2945GS E SLB2 R A3_FCBGA998

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/11/17 2009/11/17

3

Compal Secret Data

Deciphered Date

Title

Size Do cumen t Numb er R ev

Cu stom

2

Da te: Sheet o f

Compal Electronics, Inc.

Calistoga(2/5)-DDR2

KAVAA LA-5121P M/B

1

1.0

7 42Tu esday, M arch 10 , 2009

5

D D

4

3

2

1

U3 F

H27

GMCH _CRT_ R

R60 150_040 2_1%

R61 150_040 2_1%

R62 150_040 2_1%

C C

R64 100K_04 02_5%

+3VS

B B

12

GMCH _CRT_G

12

GMCH _CRT_B

12

Clos e to U3.H 25

R63 255_ 0402_1%

3/4 P VT: Ad d sup port DPS T fun ctio n

12

1 2

R66 10K_0 402_5%

1 2

R67 10K_0 402_5%

ENB KL

LCT LA_CLK

LCTLB_D ATA

CLK _MCH_3GPL L#<12>

CLK _MCH_3GPL L<12>

GMCH _CRT_ CLK<14>

GMCH _CRT_DA TA<1 4>

GMCH _CRT_B<14>

GMCH _CRT_G<14>

GMCH _CRT_ R<14>

GM CH_C RT_VSYN C<14>

12

ENB KL<26 >

R65 1.5 K_0402_1%

GM CH_C RT_HS YNC<14>

GMCH _INVT_PW M<1 3>

LVD S_SCL<13>

LVD S_SDA<13>

GM CH_EN VDD<13>

12

LVD S_ACLK#<13>

LVD S_ACLK< 13>

LVD S_A0#<13>

LVD S_A1#<13>

LVD S_A2#<13>

LVD S_A0<13>

LVD S_A1<13>

LVD S_A2<13>

GMCH _CRT_B

GMCH _CRT_G

GMCH _CRT_ R

CR T_IRE F

LCT LA_CLK

LCTLB_D ATA

LVD S_SCL

LVD S_SDA

GM CH_EN VDD

L_IBG

LVD S_ACLK#

LVD S_ACLK

LVD S_A0#

LVD S_A1#

LVD S_A2#

LVD S_A0

LVD S_A1

LVD S_A2

SDVO_CTRLDATA

J27

SDVO_CTRLCLK

Y26

G_CLKN

AA26

G_CLKP

H20

CRT_DDC_CLK

H22

CRT_DDC_DATA

A24

CRT_BLUE

A23

CRT_BLUE#

E25

CRT_GREEN

F25

CRT_GREEN#

C25

CRT_RED

D25

CRT_RED#

F27

CRT_VSYNC

D27

CRT_HSYNC

H25

CRT_IREF

H30

L_BKLTCTL

G29

L_BKLTEN

F28

L_CLKCTLA

E28

L_CTLBDATA

G28

L_DDC_CLK

H28

L_DDC_DATA

K30

L_VDDEN

K27

L_IBG

J29

L_VBG

J30

L_VREFH

K29

L_VREFL

D30

LA_CLKN

C30

LA_CLKP

A30

LB_CLKN

A29

LB_CLKP

G31

LA_DATAN_0

F32

LA_DATAN_1

D31

LA_DATAN_2

H31

LA_DATAP_0

G32

LA_DATAP_1

C31

LA_DATAP_2

F33

LB_DATAN_0

D33

LB_DATAN_1

F30

LB_DATAN_2

E33

LB_DATAP_0

D32

LB_DATAP_1

F29

LB_DATAP_2

QG8 2945GS E SLB2 R A3_FCBGA998

EXP_A_COMPI

EXP_A_ICOMPO

SDVO_TVCLKIN#

SDVO_FLDSTALL#

MISC

SDVO_TVCLKIN

SDVO_FLDSTALL

SDVO

SDVO_RED#

SDVO_GREEN#

SDVO_BLUE#

SDVO_CLKN

SDVO_GREEN

SDVO_BLUE

SDVO_CLKP

TV

LVDS VGA

TV_DCONSEL0

TV_DCONSEL1

SDVO_INT#

SDVO_RED

SDVO_INT

TV_DACA

TV_DACB

TV_DACC

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

R28

M28

N30

R30

T29

M30

P30

T30

P28

N32

P32

T32

N28

M32

P33

R32

A21

C20

E20

G23

B21

C21

D21

G26

J26

PEGCOMP

+1.5VS

1 2

Disable TV

R59

24.9 _0402_1%

+1.5 VS_PC IE

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2008/11/17 2009/11/17

3

Compal Secret Data

Deciphered Date

Title

Size Do cumen t Numb er R ev

Cu stom

2

Da te: Sheet o f

Compal Electronics, Inc.

Calistoga(3/5)-VGA/LVDS/TV

KAVAA LA-5121P M/B

8 42Tu esday, M arch 10 , 2009

1

1.0

5

+1.05VS

D D

C C

+1.05VS

B B

A A

U3H

T25

VCC_NCTF1

R25

VCC_NCTF2

P25

VCC_NCTF3

N25

VCC_NCTF4

M25

VCC_NCTF5

P24

VCC_NCTF6

N24

VCC_NCTF7

M24

VCC_NCTF8

Y22

VCC_NCTF9

W22

VCC_NCTF10

V22

VCC_NCTF11

U22

VCC_NCTF12

T22

VCC_NCTF13

R22

VCC_NCTF14

P22

VCC_NCTF15

N22

VCC_NCTF16

M22

VCC_NCTF17

Y21

VCC_NCTF18

W21

VCC_NCTF19

V21

VCC_NCTF20

U21

VCC_NCTF21

T21

VCC_NCTF22

R21

VCC_NCTF23

P21

VCC_NCTF24

N21

VCC_NCTF25

M21

VCC_NCTF26

Y20

VCC_NCTF27

W20

VCC_NCTF28

V20

VCC_NCTF29

U20

VCC_NCTF30

T20

VCC_NCTF31

R20

VCC_NCTF32

P20

VCC_NCTF33

N20

VCC_NCTF34

M20

VCC_NCTF35

Y19

VCC_NCTF36

P19

VCC_NCTF37

N19

VCC_NCTF38

M19

VCC_NCTF39

Y18

VCC_NCTF40

P18

VCC_NCTF41

N18

VCC_NCTF42

M18

VCC_NCTF43

Y17

VCC_NCTF44

P17

VCC_NCTF45

N17

VCC_NCTF46

M17

VCC_NCTF47

Y16

VCC_NCTF48

P16

VCC_NCTF49

N16

VCC_NCTF50

M16

VCC_NCTF51

Y15

VCC_NCTF52

P15

VCC_NCTF53

N15

VCC_NCTF54

M15

VCC_NCTF55

Y14

VCC_NCTF56

W14

VCC_NCTF57

V14

VCC_NCTF58

U14

VCC_NCTF59

T14

VCC_NCTF60

R14

VCC_NCTF61

P14

VCC_NCTF62

N14

VCC_NCTF63

M14

VCC_NCTF64

T10

VTT_NCTF1

R10

VTT_NCTF2

P10

VTT_NCTF3

N10

VTT_NCTF4

L10

VTT_NCTF5

D1

VTT_NCTF6

M10

RSVD_3

A18

RSVD_4

AB10

RSVD_5

AA10

RSVD_6

QG8294 5GSE SLB2R A3_FCBGA998

NCTF

4

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17

VSS_NCTF18

VSS_NCTF19

CFG_19

RESERVED10

RESERVED11

RESERVED12

RESERVED13

RESERVED14

RESERVED15

RESERVED16

RESERVED17

RESERVED18

RESERVED19

RESERVED20

RESERVED21

RESERVED22

RESERVED23

RESERVED24

RESERVED25

AD25

AC25

AB25

AD24

AC24

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

K14

AD13

Y13

W13

V13

U13

T13

R13

P13

N13

M13

AD12

Y12

W12

V12

U12

T12

R12

P12

N12

M12

AD11

AD10

K10

AN33

AA25

V25

U25

AA22

AA21

AA20

AA19

AA18

AA17

AA16

AA15

AA14

AA13

A4

A33

B2

AN1

C1

K28

K25

K26

R24

T24

K21

K19

K20

K24

K22

J17

K23

K17

K12

K13

K16

K15

+1.5VS

3

U3E

AH33

VSS_1

Y33

VSS_2

V33

VSS_3

R33

VSS_4

G33

VSS_5

AK32

VSS_6

AG32

VSS_7

AE32

VSS_8

AC32

VSS_9

AA32

VSS_10

U32

VSS_11

H32

VSS_12

E32

VSS_13

C32

VSS_14

AM31

VSS_15

AJ31

VSS_16

AA31

VSS_17

U31

VSS_18

T31

VSS_19

R31

VSS_20

P31

VSS_21

N31

VSS_22

M31

VSS_23

J31

VSS_24

F31

VSS_25

AL30

VSS_26

AG30

VSS_27

AE30

VSS_28

AC30

VSS_29

AA30

VSS_30

Y30

VSS_31

V30

VSS_32

U30

VSS_33

G30

VSS_34

E30

VSS_35

B30

VSS_36

AA29

VSS_37

U29

VSS_38

R29

VSS_39

P29

VSS_40

N29

VSS_41

M29

VSS_42

H29

VSS_43

E29

VSS_44

B29

VSS_45

AK28

VSS_46

AH28

VSS_47

AE28

VSS_48

AA28

VSS_49

U28

VSS_50

T28

VSS_51

J28

VSS_52

D28

VSS_53

AM27

VSS_54

AF27

VSS_55

AB27

VSS_56

AA27

VSS_57

Y27

VSS_58

U27

VSS_59

T27

VSS_60

R27

VSS_61

P27

VSS_62

N27

VSS_63

M27

VSS_64

G27

VSS_65

E27

VSS_66

C27

VSS_67

B27

VSS_68

AL26

VSS_69

AH26

VSS_70

W26

VSS_71

U26

VSS_72

AN25

VSS_73

AK25

VSS_74

AG25

VSS_75

AE25

VSS_76

J25

VSS_77

G25

VSS_78

A25

VSS_79

H23

VSS_80

F23

VSS_81

B23

VSS_82

AM22

VSS_83

AJ22

VSS_84

AF22

VSS_85

G22

VSS_86

E22

VSS_87

J21

VSS_88

H21

VSS_89

F21

VSS_90

AM20

VSS_91

AK20

VSS_92

AH20

VSS_93

AF20

VSS_94

D20

VSS_95

W19

VSS_96

R19

VSS_97

AM18

VSS_98

AH18

VSS_99

AF18

VSS_100

U18

VSS_101

H18

VSS_102

D18

VSS_103

AK17

VSS_104

V17

VSS_105

T17

VSS_106

F17

VSS_107

B17

VSS_108

AH16

VSS_109

U16

VSS_110

QG8294 5GSE SLB2R A3_FCBGA998

2

J16

VSS_111

AL15

VSS_112

AG15

VSS_113

W15

VSS_114

R15

VSS_115

F15

VSS_116

D15

VSS_117

AM14

VSS_118

AH14

VSS_119

AE14

VSS_120

H14

VSS_121

B14

VSS_122

F13

VSS_123

D13

VSS_124

AL12

VSS_125

AG12

VSS_126

H12

VSS_127

B12

VSS_128

AN11

VSS_129

AJ11

VSS_130

AE11

VSS_131

AM9

VSS_132

AJ9

VSS_133

AB9

VSS_134

W9

VSS_135

R9

VSS_136

M9

VSS_137

J9

VSS_138

F9

VSS_139

C9

VSS_140

A9

VSS_141

AL8

VSS_142

AG8

VSS_143

AE8

VSS_144

U8

VSS_145

AA7

VSS_146

V7

VSS_147

R7

VSS_148

N7

VSS_149

H7

VSS_150

E7

VSS_151

B7

VSS_152

AL6

VSS_153

AG6

VSS_154

AE6

VSS_155

AB6

VSS_156

W6

VSS_157

T6

VSS_158

M6

VSS_159

K6

VSS_160

AN5

VSS_161

AJ5

VSS_162

B5

VSS_163

AA4

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

V4

R4

N4

K4

H4

E4

AL3

AD3

W3

T3

B3

AK2

AH2

AF2

AB2

M2

K2

H2

F2

V1

R1

VSS

U3G

W33

NC1

AM33

NC2

AL33

NC3

C33

NC4

B33

NC5

AN32

NC6

A32

NC7

AN31

NC8

W28

NC9

V27

NC10

W29

NC11

J24

NC12

H24

NC13

W32

NC14

G24

NC15

F24

NC16

E24

NC17

D24

NC18

K33

NC19

A31

NC20

E21

NC21

C23

NC22

AN19

NC23

AM19

NC24

AL19

NC25

AK19

NC26

AJ19

NC27

AH19

NC28

AN3

NC29

Y9

NC30

J19

NC31

H19

NC32

G19

NC33

F19

NC34

E19

NC35

D19

NC36

C19

NC37

B19

NC38

A19

NC39

Y8

NC40

G16

NC41

F16

NC42

E16

NC43

D16

NC44

C16

NC45

B16

NC46

AN2

NC47

A16

NC48

Y7

NC49

AM4

NC50

AF4

NC51

AD4

NC52

AL4

NC53

AK4

NC54

W31

NC55

AJ4

NC56

AH4

NC57

AG4

NC58

AE4

NC59

AM1

NC60

QG8294 5GSE SLB2R A3_FCBGA998

NC

RESERVED26

RESERVED27

RESERVED28

RESERVED29

RESERVED30

RESERVED31

RESERVED32

RESERVED33

RESERVED34

RESERVED35

RESERVED36

RESERVED37

RESERVED38

RESERVED39

RESERVED40

RESERVED41

RESERVED42

1

NC61

NC62

NC63

NC64

NC65

NC66

NC67

NC68

NC69

NC70

NC71

NC72

W30

Y6

AL1

Y5

Y10

W10

W25

V24

U24

V10

U10

K18

Y25

Y24

AB22

AB21

AB19

AB16

AB14

AA12

W24

AA24

AB24

AB20

AB18

AB15

AB13

AB12

AB17

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/11/17 2009/11/17

Compal Secret Data

Deciphered Date

Title

Size D ocument N umber Re v

Cus tom

2

Date: Sheet of

Compal Electronics, Inc.

Calistoga(4/5)-PWR/GND

KAVAA LA-5121P M/B

9 42Tuesday, March 10, 2009

1

1.0

2940mA

1

1

+

+

C48

@

2

2

220U_B2_2.5VM_R35

+1.05VS

21

D1

CH751H-40PT_S OD323-2

12

+2.5VS

5

1

C49

2

10U_0805_10V4Z

1

1

C51

C50

2

2

10U_0805_10V4Z

0.1U_0402_16V4Z

C73

1 2

0.47U_0603_10V7K

C80

1 2

0.47U_0603_10V7K

1

+

C81

2

220U_B2_2.5VM_R35

C86

4.7U_06 03_6.3V6K

C93

0.47U_0603_10V7K

C52

1250mA

1

2

0.1U_0402_16V4Z

780mA

10mil

10mil

C87

4.7U_06 03_6.3V6K

10mil

1

2

C53

0.1U_0402_16V4Z

+1.5VS

C71

0.1U_0402_16V4Z

+1.05VS

1

2

1

2

U4_A14

U4_A7

U4_AA1

U4_F1

10mil

1

C94

0.47U_0603_10V7K

2

W18

W17

W16

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AC27

AD26

AC26

AB26

AE19

AE18

AF17

AE17

AF16

AE16

AF15

AE15

T26

R26

P26

N26

M26

V19

U19

T19

V18

T18

R18

U17

R17

V16

T16

R16

V15

U15

T15

H10

AE9

AD9

AD8

AD7

AD6

A14

D10

AA1

J14

J10

U9

P9

L9

D9

P8

L8

D8

P7

L7

D7

A7

P6

L6

G6

D6

U5

P5

L5

G5

D5

Y4

U4

P4

L4

G4

D4

Y3

U3

P3

L3

G3

D3

Y2

U2

P2

L2

G2

D2

F1

+1.05VS

C47

D D

220U_B2_2.5VM_R35

R71

10_0402_5%

1/1 3 DVT :C ha nge D 1 P /N to SC1 H751 H010

C C

B B

A A

4

U3D

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCAUX5

VCCAUX6

VCCAUX7

VCCAUX8

VCCAUX9

VCCAUX10

VCCAUX11

VCCAUX12

VCCAUX13

VCCAUX14

VCCAUX15

VCCAUX16

VCCAUX17

VCCAUX18

VCCAUX19

VCCAUX20

VCCAUX21

VCCAUX22

VCCAUX23

VCCAUX24

VCCAUX25

VCCAUX26

VCCAUX27

VCCAUX28

VTT0

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT36

VTT35

VTT37

VTT38

VTT39

VTT40

QG8294 5GSE SLB2R A3_FCBGA998

VCCATVDACA0

VCCATVDACA1

VCCATVDACB0

VCCATVDACB1

VCCATVDACC0

VCCATVDACC1

VCCDTVDAC

VCCDQTVDAC

POWER

VCCDHMPLL1

VCCDHMPLL2

VCCTXLVDS0

VCCTXLVDS1

VCCACRTDAC0

VCCACRTDAC1

VSSACRTDAC

VCCATVBG

VSSATVBG

VCCDLVDS0

VCCDLVDS1

VCCDLVDS2

VCCHV0

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCAMPLL

VCCAHPLL

VCCADPLLA

VCCADPLLB

VCC3G0

VCC3G1

VCCA3GPLL

VCCA3GBG

VSSA3GBG

VCCSYNC

VCCALVDS

VSSALVDS

VTT41

VTT42

VTT43

VTT44

VTT45

B20

A20

B22

A22

D22

C22

D23

E23

F20

F22

C28

B28

A28

E26

D26

C26

AB33

AM32

AN29

AM29

AL29

AK29

AJ29

AH29

AG29

AF29

AE29

AN24

AM24

AL24

AK24

AJ24

AH24

AG24

AF24

AE24

AN18

AN16

AM16

AL16

AK16

AJ16

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AN4

AM10

AL10

AK10

AH1

AH10

AG10

AF10

AE10

AN7

AM7

AL7

AK7

AJ7

AH7

AN10

AJ10

AD1

AD2

B26

J32

AE5

AD5

D29

C29

U33

T33

V26

N33

M33

J23

C24

B24

B25

B31

B32

P1

L1

G1

U1

Y1

+1.5VS

10mA

144mA

Disable TV

20mA

40mA

U4_AB33

U4_AM32

10mil

10mil

10mil

10mil

C79

+1.5VS_MPLL

+1.5VS_HPLL

+1.5VS_DPLLA

+1.5VS_DPLLB

150mA

+1.5VS

60mA

+2.5VS

400mA

+1.5VS_3GPLL

+2.5VS

+2.5VS_CR TDAC

+2.5VS

+1.05VS

3

10mil

1

1

C61

C62

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

1

C72

1U_0402_6.3V6K

2

1

C78

2

1

1U_0402_6.3V6K

2

1U_0402_6.3V6K

45mA

45mA

50mA

50mA

Route +2.5VS fr om GMCH pinN33 to

deco upling ca p <250mil to the edge.

400mA

2mA

70mA

70mA

1

1

2

2

C90

0.022U_0402_16V7K

Route VSSACRTDAC gnd from GMCH to

deco upling ca p ground lead and then

conn ect to the gnd plane .

+3VS

1

1

C60

C59

2

2

10U_0805_10V4Z

0.1U_0402_16V4Z

1

C68

C69

2

1U_0402_6.3V6K

1

C57

2

0.1U_0402_16V4Z

C67

C70

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

PLAC EIN CAVIY

+2.5VS

1

C82

2

10/2 3 EV T check wa ter wave

R73

12

+2.5VS

0_0402_5%

1

C91

C92

2

CRTDAC: Route FB

within 3" of Cal istoga

10U_0805_10V4Z

0.1U_0402_16V4Z

2

+1.5VS

1

C58

2

10U_0805_10V4Z

+1.5VS_MPLL

+1.8V

1

+

@

2

220U_B2_2.5VM_R25M

533 MTS=1720m A

C63

2/6 D VT: Re se rve C67 wit h 220 uf

1

C76

C74

2

0.1U_0402_16V4Z

220U_B2_2.5VM_R35

C84

1

2

10U_0805_10V4Z

+1.5VS_PCIE

C85

10U_0805_10V4Z

0.1U_0402_16V4Z

+2.5VS

1

1

C88

C89

2

2

10U_0805_10V4Z

0.1U_0402_16V4Z

1

PCI-E/MEM/PSB PLL decoupling

+1.5VS_3GPLL

1

1

C55

C54

2

2

10U_0805_10V4Z

0.1U_0402_16V4Z

R68

0_0603_5%

12

PLAC EIN CAVIY

0.1U_0402_16V4Z

1

2

45mA Max.

R69

0_0603_5%

1

C64

2

10U_0805_10V4Z

12

+1.5VS

+1.5VS_HPLL

C65

Plac e as cl ose as p ossible to the edge( <200mils)

L1

1 2

FBMA-L10-160808-301LMT_2P

1

+

2

0_0805_5%

1

1

+

C83

2

2

220U_B2_2.5VM_R35

+1.5VS +1.5VS

2/6 D VT: Fo r ESD team req uest

R72

12

+1.5VS

+2.5VS +2.5VS

C95

+1.5VS_DPLLA+1.5VS_DPLLB

1

1

C77

C514

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C96

2

2

0.1U_0402_16V4Z

4.7U_06 03_6.3V6K

clos e pin C 29/D29 close pin B 31

+1.5VS

0.1U_0402_16V4Z

@

1

C66

2

1

+

C75

2

220U_B2_2.5VM_R35

1

C97

2

0.01U_0402_25V7K

+1.5VS+1.5VS_3GPLL

1

C56

2

0.1U_0402_16V4Z

45mA Max.

R70

0_0603_5%

1

2

10U_0805_10V4Z

50mA Max.50mA Max.

L2

1 2

FBMA-L10-160808-301LMT_2P

C98

0.1U_0402_16V4Z

12

+1.5VS

1

2

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/11/17 2009/11/17

Compal Secret Data

Deciphered Date

Title

Size D ocument N umber Re v

Cus tom

2

Date: Sheet of

Compal Electronics, Inc.

Calistoga(5/5)-PWR/GND

KAVAA LA-5121P M/B

10 42Tuesday, March 10, 2009

1

1.0

5

DDR_A _DQS#[0.. 7]<7>

DDR _A_D[0..6 3]<7>

DDR_A _DM[0..7]<7>

DDR_ A_DQS[0.. 7]<7>

DDR_A _MA[0..13]<7>

D D

+1.8V

2

2

2

C99

1

2.2U_0603_6.3V6K

1

+

@

C106

C107

2

220U_B2_2.5VM_R35

C C

Layou t Note:

Plac e on e cap close to every 2 p ullup

resi stor s termin ated to +0 .9VS

+0.9VS

1

1

1

C113

C112

C111

B B

A A

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

DDR_A_MA0

DDR_A_MA13

DDR_C S0#

M_ODT0

DDR_A_MA1

DDR_A_MA3

DDR_A_MA5

DDR_A _CAS#

DDR_A_W E#

DDR_A_BS 0

M_ODT1

DDR_C S1#

2

C114

2

0.1U_0402_16V4Z

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

1 8

2 7

3 6

4 5

56_0804_8P4R_5%

C101

C100

1

2.2U_0603_6.3V6K

1

1

C108

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

C115

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+0.9VS

RP1

RP3

RP5

C102

1

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

1

C109

2

0.1U_0402_16V4Z

1

C117

C116

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

RP2

56_0804_8P4R_5%

RP4

56_0804_8P4R_5%

RP6

56_0804_8P4R_5%

2

1

C110

1

2

18

27

36

45

18

27

36

45

18

27

36

45

2

C103

1

2.2U_0603_6.3V6K

1

2

0.1U_0402_16V4Z

1

C119

C118

2

0.1U_0402_16V4Z

DDR_A _RAS#

DDR_A_MA4

DDR_A_MA2

DDR_A_BS 1

DDR_C KE1

DDR_A_MA7

DDR_A_MA6

DDR_A_MA11

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA10

Layou t Note:

Plac e near JD DR1

1

2

0.1U_0402_16V4Z

4

+1.8V

12