Page 1

5

4

3

2

1

D

D

Compal Confidential

C

C

QAQ10/11

LA-8581P

B

Intel Ivy Bridge/Pather Point

UMA&OPT

2012-04-23 Rev 1.0

SchematicREV1.0

B

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC .

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC .

2011/09/23 2011/12/30

2011/09/23 2011/12/30

2011/09/23 2011/12/30

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

4019IE

4019IE

4019IE

Friday, August 24, 2012

Friday, August 24, 2012

Friday, August 24, 2012

1 60

of

1 60

of

1 60

of

1

A

B

B

B

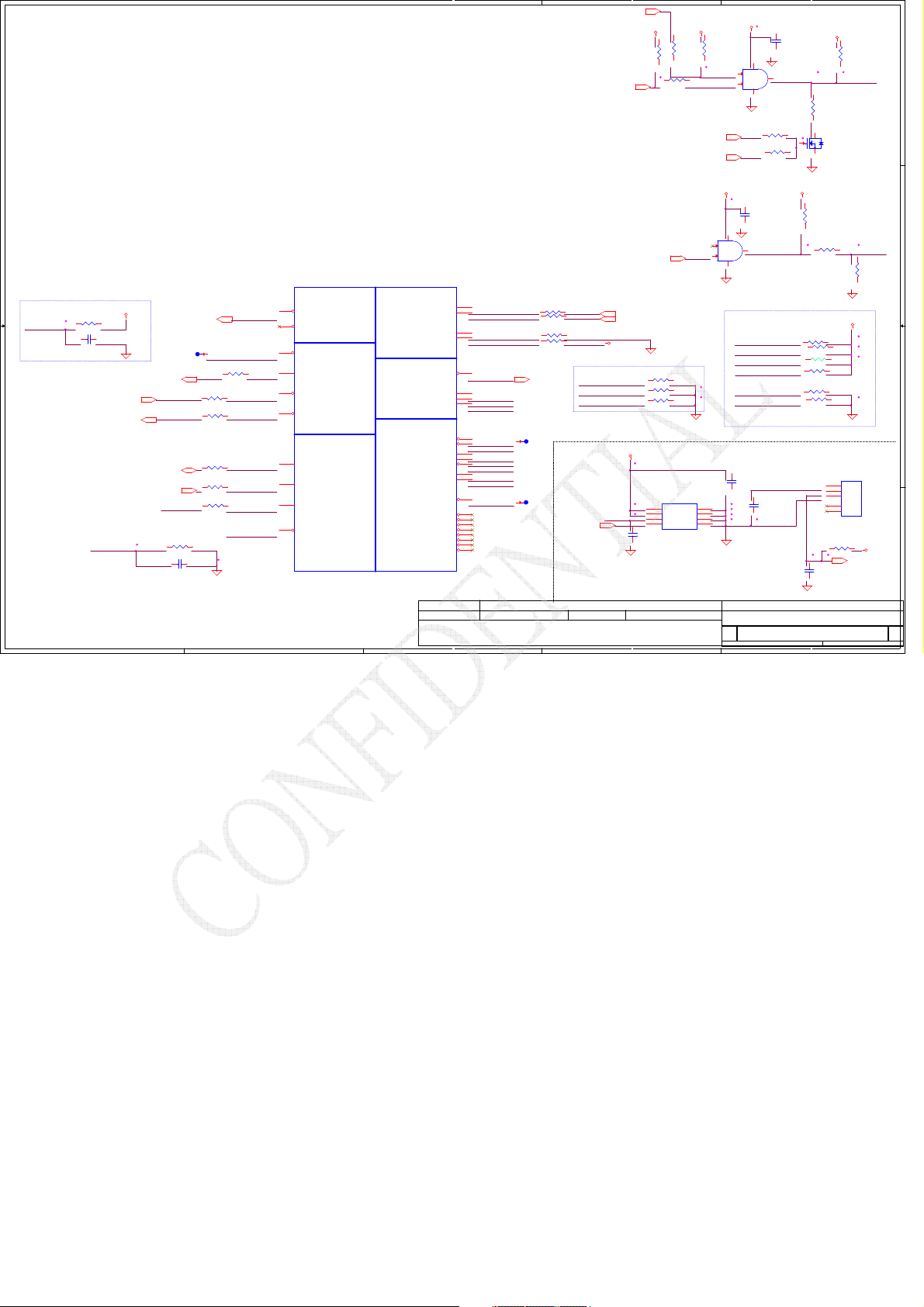

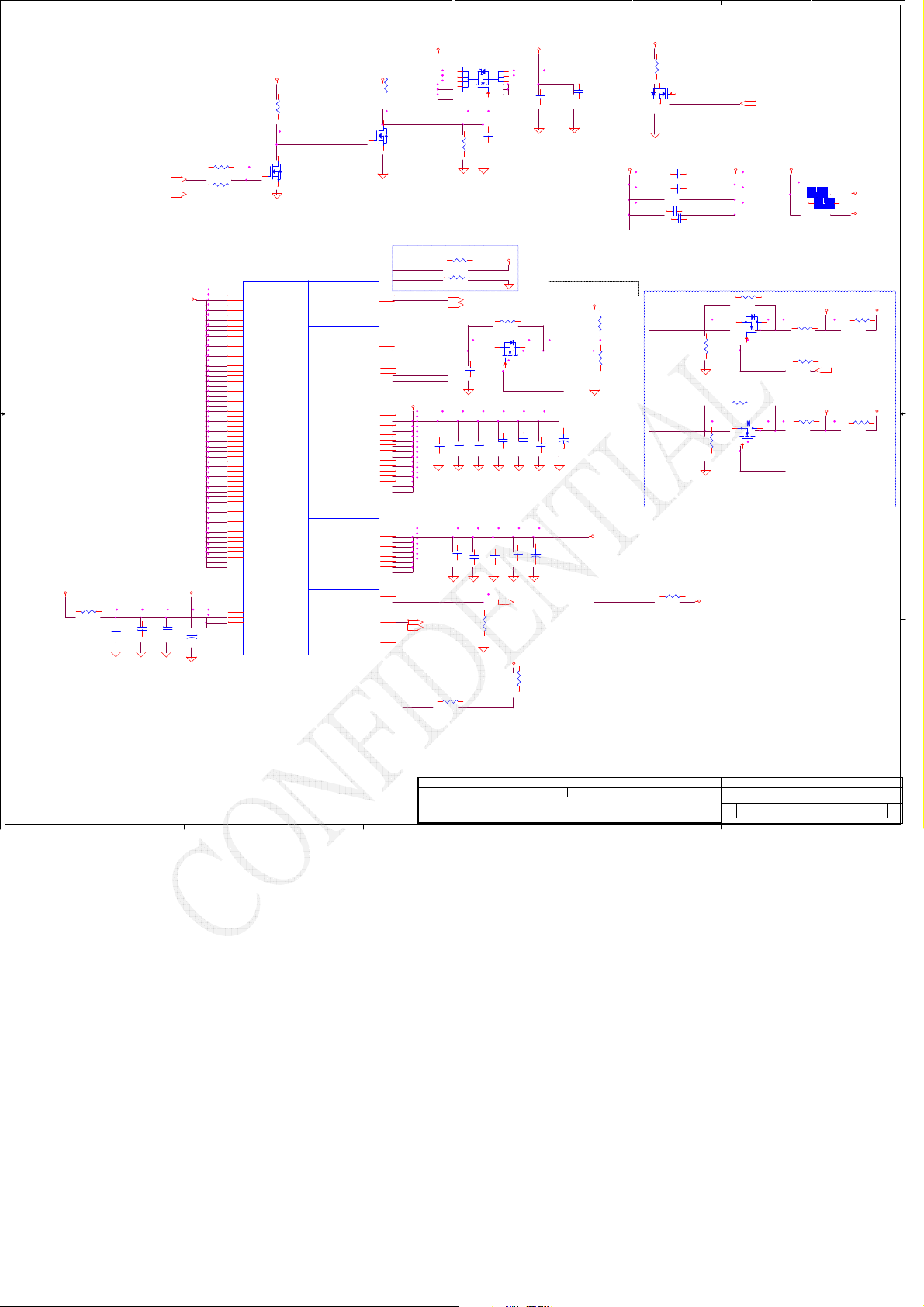

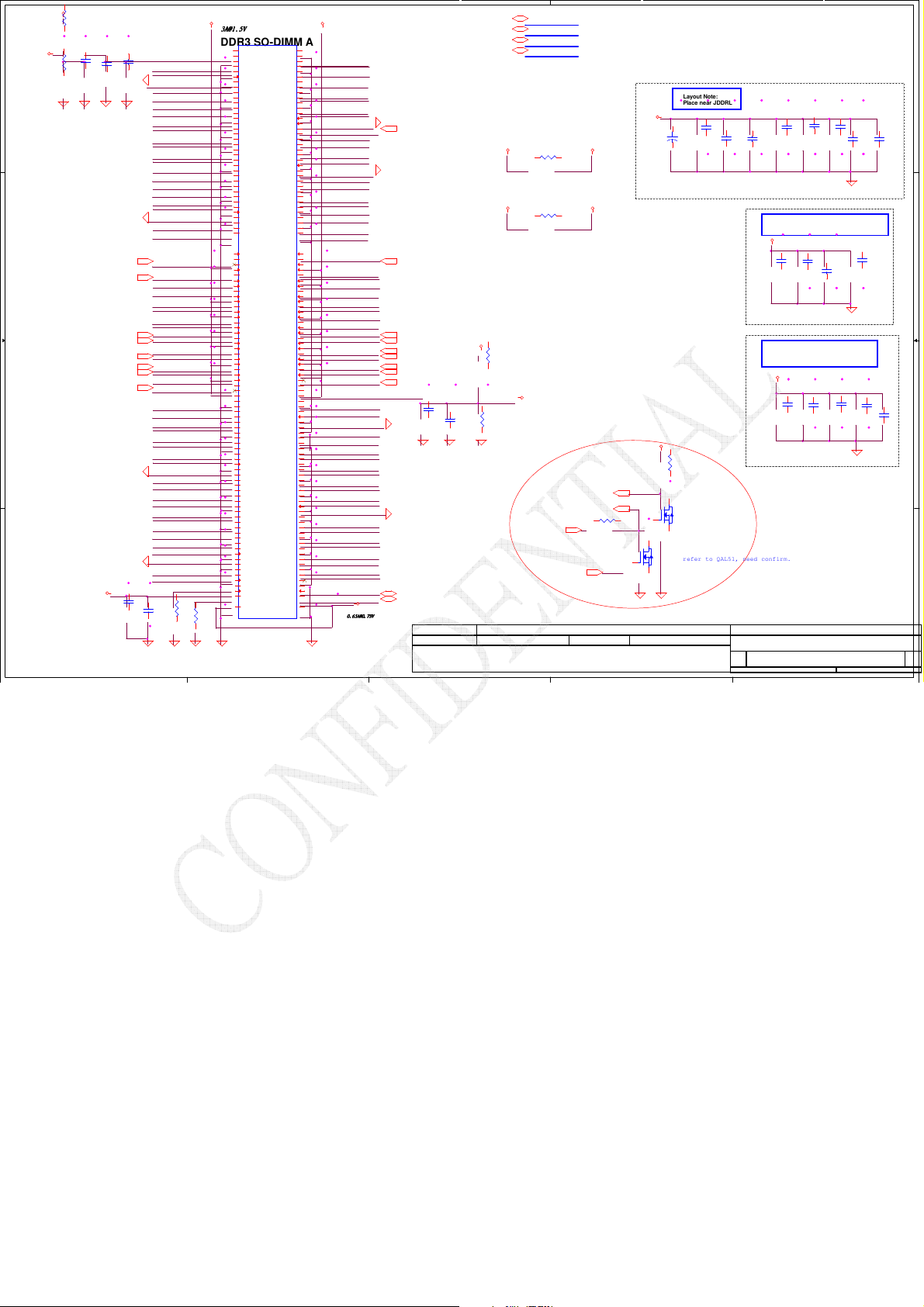

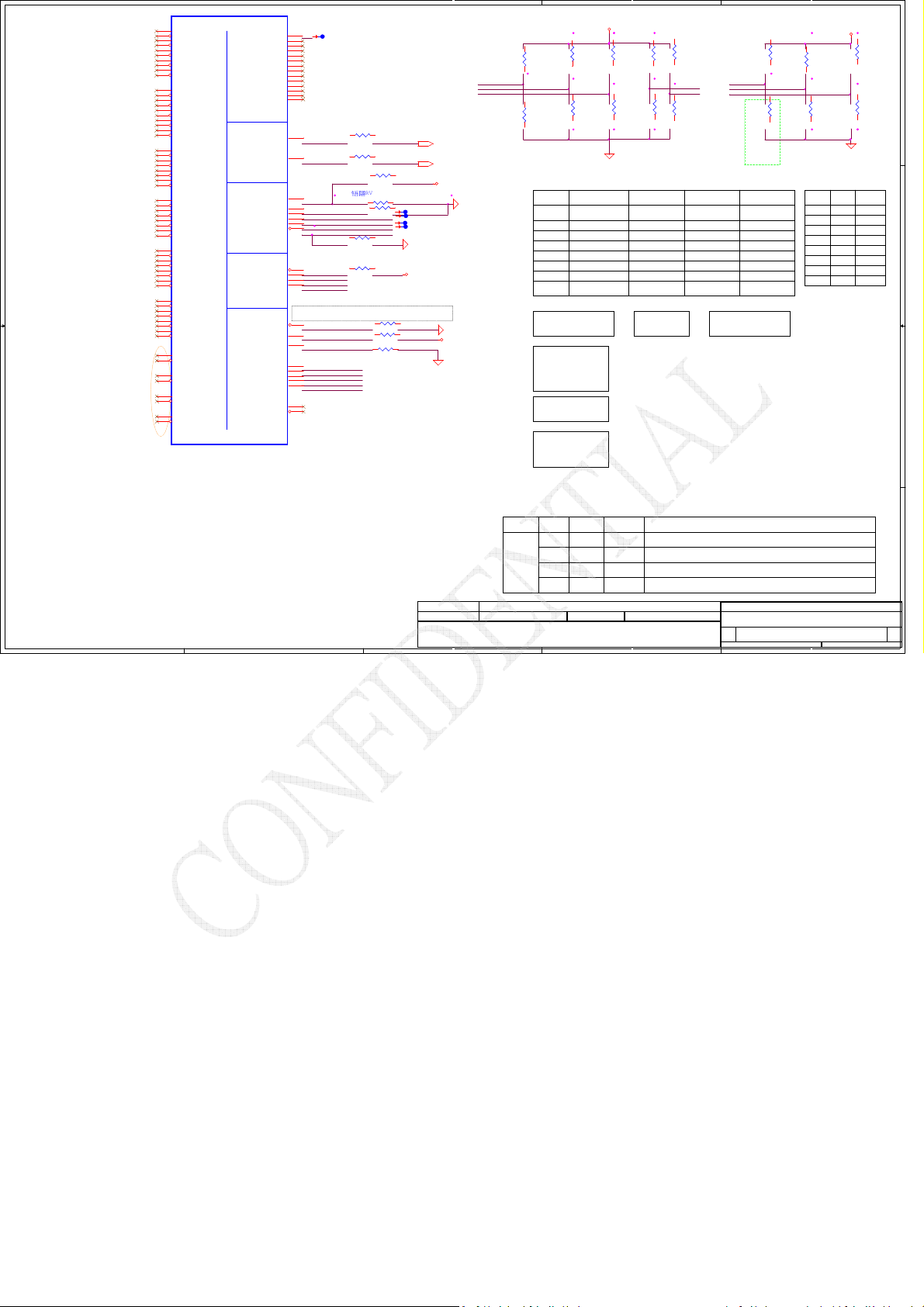

Page 2

Compal Confidential

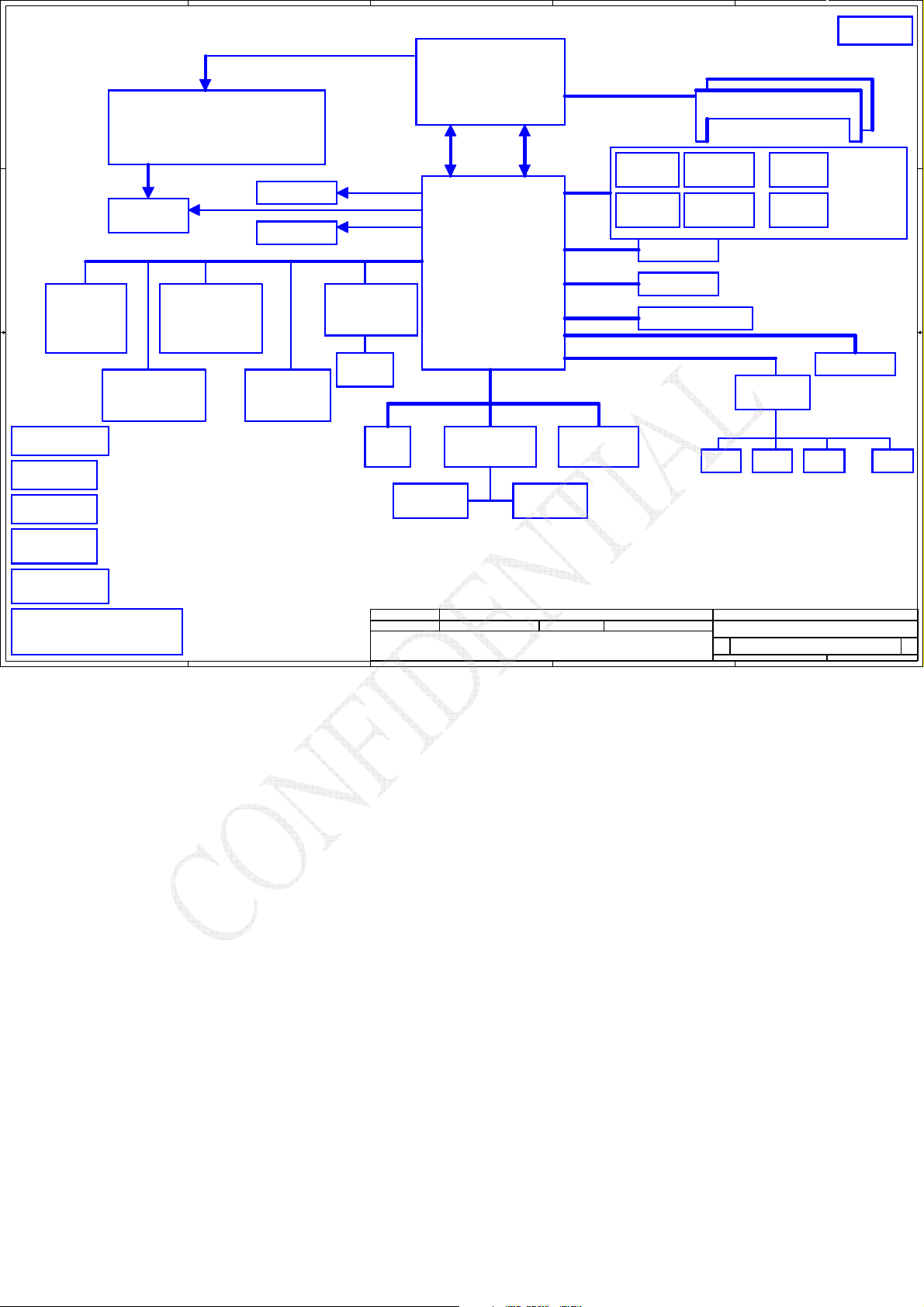

Model Name : QAQ10/11

File Name : LA-8581P

D

C

port 4

PCIeMini Card

WLAN &BT

USB Port 13

PCIe Port 2

page 36

B

USB&Function/B

page 43

Power/B

page 43

Touch Pad/B

page 43

5

PEG(DIS)

4

PCI-E 2.0x16 5GT/s PER LANE100MHz

VGA (DDR3)

NVIDIA N13P-GLP, 128bit with 1GB/2GB

page 13,14,15,16,17,18,19,20,21

page 22

CRT

HDMI Conn.

page 24

port 2 port 1

port 6

PCIe Mini Card WWAN

&SIM

PCIe Port 5

USB Port 12

JMB385/388 Card Reader

&1394

PCIe Port 6

page 37

page 23

LCD Conn.

PCI-Express x 8 (ARD PCIE2.0 2.5GT/s)

port 3

page 36

Express Card

PCIe Port 3

USB port 8

port 5

page 39

RTL8111E&Intel 82579

PCIe port 1

133MHz

OPT & UMA

OPT & UMA

page 35,42

RJ45

page 39

SIO

Page 47

Mobile

37.5mm*37.5mm

100MHz

Touch Pad

3

Ivy Bridge

CPU Dual Core

Socket-rPGA988B/989

page 5,6,7,8,9,10

DMI X4

Intel

Panther Point-M

989pin FCBGA

HM76

page 25 ~ 32

25mm*25mm

LPC BUS

33MHz

ENE KB9012

page 41

page 43

Memory BUS(DDRIII)

FDI

USB

SATA port 0

5V 1.5GHz(150MB/s)

SATA port 2

5V 1.5GHz(150MB/s)

SATA port 4

5V 1.5GHz(150MB/s)

TPM 1.2

Int.KBD

page 40

2

Dual Channel

1.5V DDRIII 1333/1600

USB/B Right

USB port 3,4

page 44

Smart Card

USB port 2

page 39

SATA HDD0

SATA ODD

E-SATA

USB port 3

HD Audio

page 34

204pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

USB Left Port

USB port 1,9

page 43

Int. Camera

USB port 10

page 23

page 34

page 34

page 43

3.3V 24.576MHz/48Mhz

Int.

page 38

MIC

USB3.0

USB port 0

Finger Print

USB port 11

HDA Codec

ALC259

page 38

MIC CONN

page 38

page 40

page 40

1

page 11,12

BIOS ROM

HP CONN

page 38

Fan Control

page 6

page 33

SPK CONN

page 38

D

C

B

RTC CKT.

page 25,47

A

DC/DC Interface

page 45

Power Circuit DC/DC

page 46,47,48,49,50,51 ,52,53,54,55,56,57,58

5

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC .

4

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC .

2011/09/23 2011/12/30

2011/09/23 2011/12/30

2011/09/23 2011/12/30

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

4019IE

4019IE

4019IE

2 60Friday, August 24, 2012

2 60Friday, August 24, 2012

2 60Friday, August 24, 2012

1

B

B

B

of

of

of

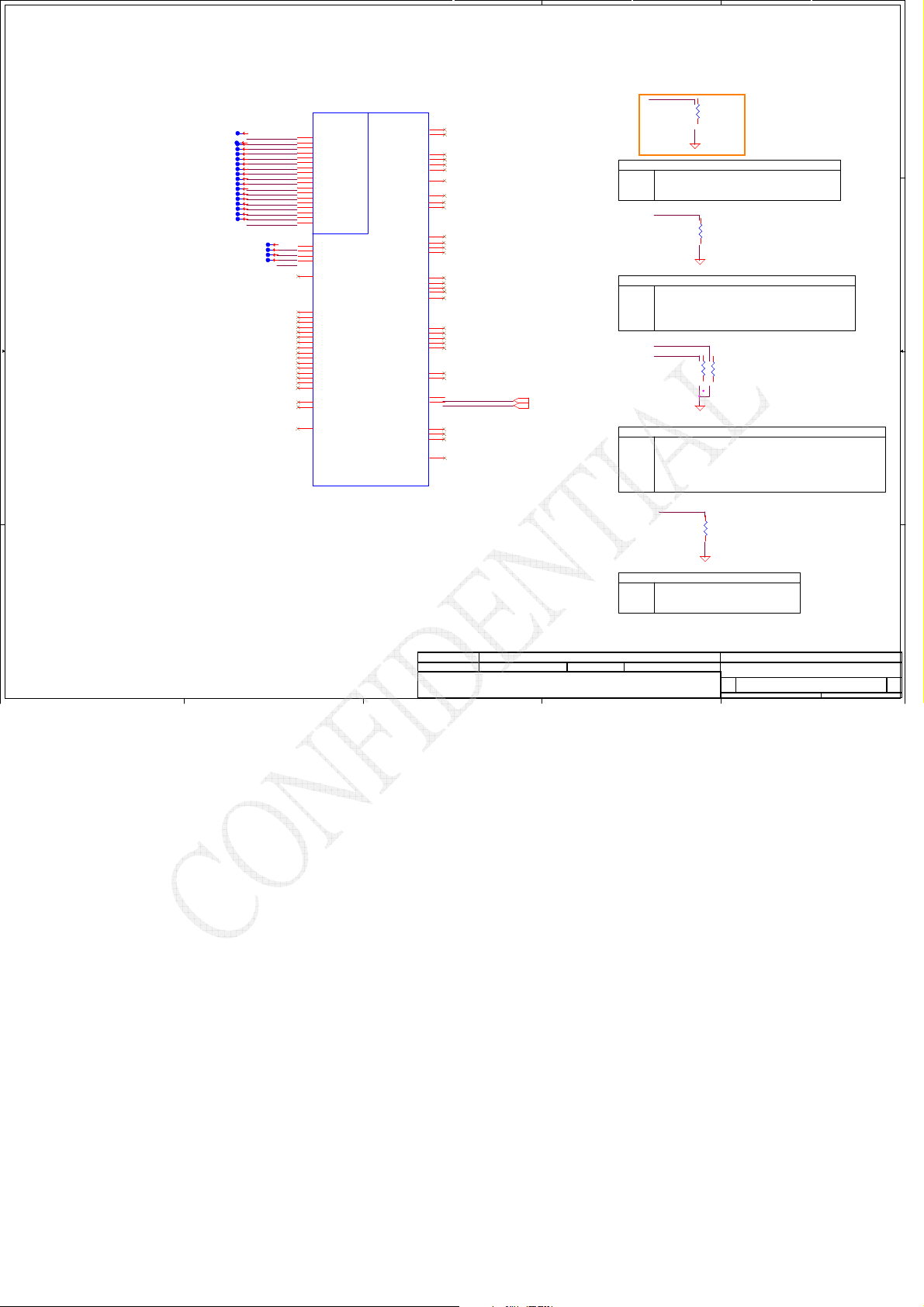

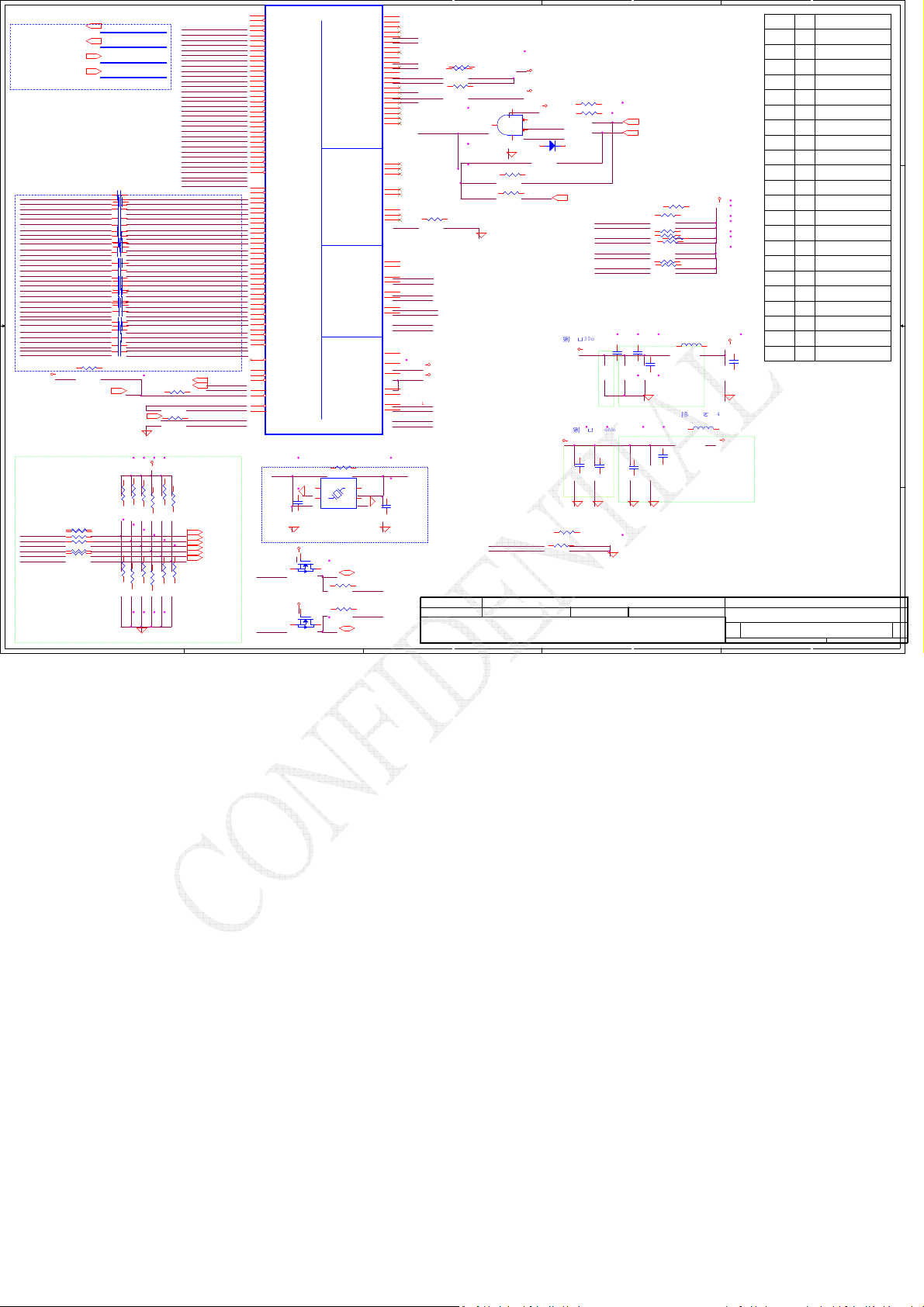

Page 3

3

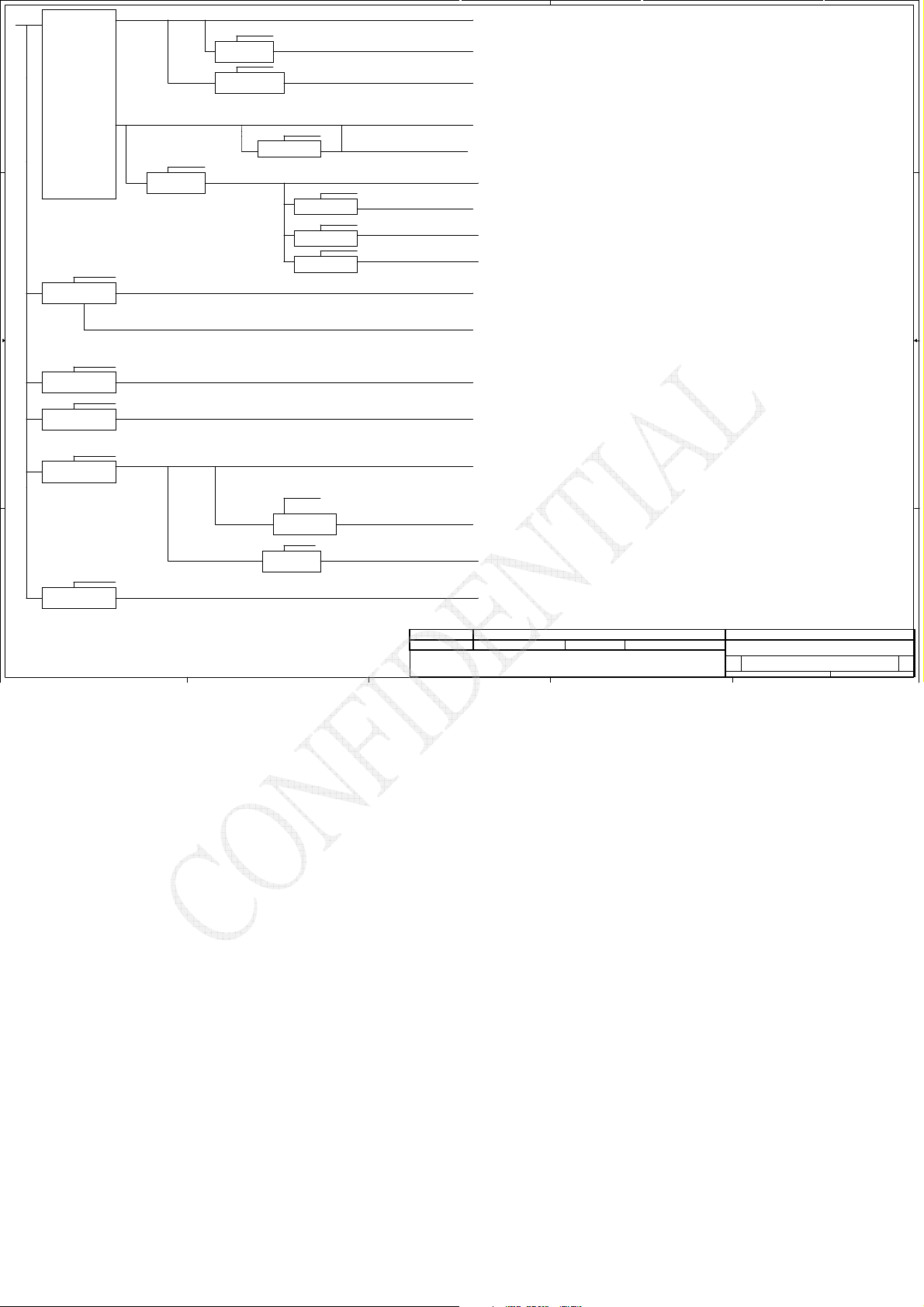

+5VALW

+5VS

+1.8VS

SI4800

4

SUSP

SUSP#

DESIGN CURRENT 5A

DESIGN CURRENT 4A

DESIGN CURRENT 2A

5

B+

Ipeak=5A, Ima x=3.5A, Iocp min=7.9

N-CHANNEL

D

SY8033BDBC

2

1

D

RT8205

Ipeak=5A, Ima x=3.5A, Iocp min=7.7

WOL_EN#

P-CHANNEL

N-CHANNEL

C

SUSP

SI4800

VR_ON

AO-3413

P-CHANNEL

AO-3413

P-CHANNEL

AO-3413

P-CHANNEL

AO-3413

ISL95831CRZ

DESIGN CURRENT 5A

DESIGN CURRENT 330mA

DESIGN CURRENT 4A

VGA_ENVDD

DESIGN CURRENT 1.5A

BT_PWR#

DESIGN CURRENT 180mA

PCIE_OK

DESIGN CURRENT 100mA

DESIGN CURRENT 52A

+3VALW

+3V_LAN

+3VS

+LCD_VDD

+BT_VCC

+3VS_DELAY

+CPU_CORE

C

DESIGN CURRENT 30A

+GFX_CORE

DGPU_PWR_EN / SUSP#

APW7138

SUSP#

G5603RU1U

B

SYSON

G5603RU1U

Ipeak=18A, Im ax=12.6A, Ioc p min=19.8

Ipeak=15A, Im ax=10.5A, Ioc p min=16.5

DESIGN CURRENT 26A

DESIGN CURRENT 18A

DESIGN CURRENT 15A

+VGA_CORE

+1.05VS_VCCP

+1.5V

+1.5V_CPU

B

CPU1.5V_S3_GATE / SUSP

APL5336

SI4856

SUSP

DESIGN CURRENT 2A

DESIGN CURRENT 12A

+0.75VS

+1.5VS

SUSP#

A

G5603RU1U

5

4

DESIGN CURRENT 6A

+VCCSA

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIV ISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIV ISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIV ISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

2011/09/23 2011/12/30

2011/09/23 2011/12/30

2011/09/23 2011/12/30

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

4019IE

4019IE

4019IE

3 60Friday, August 24, 2012

3 60Friday, August 24, 2012

3 60Friday, August 24, 2012

1

of

of

of

A

B

B

B

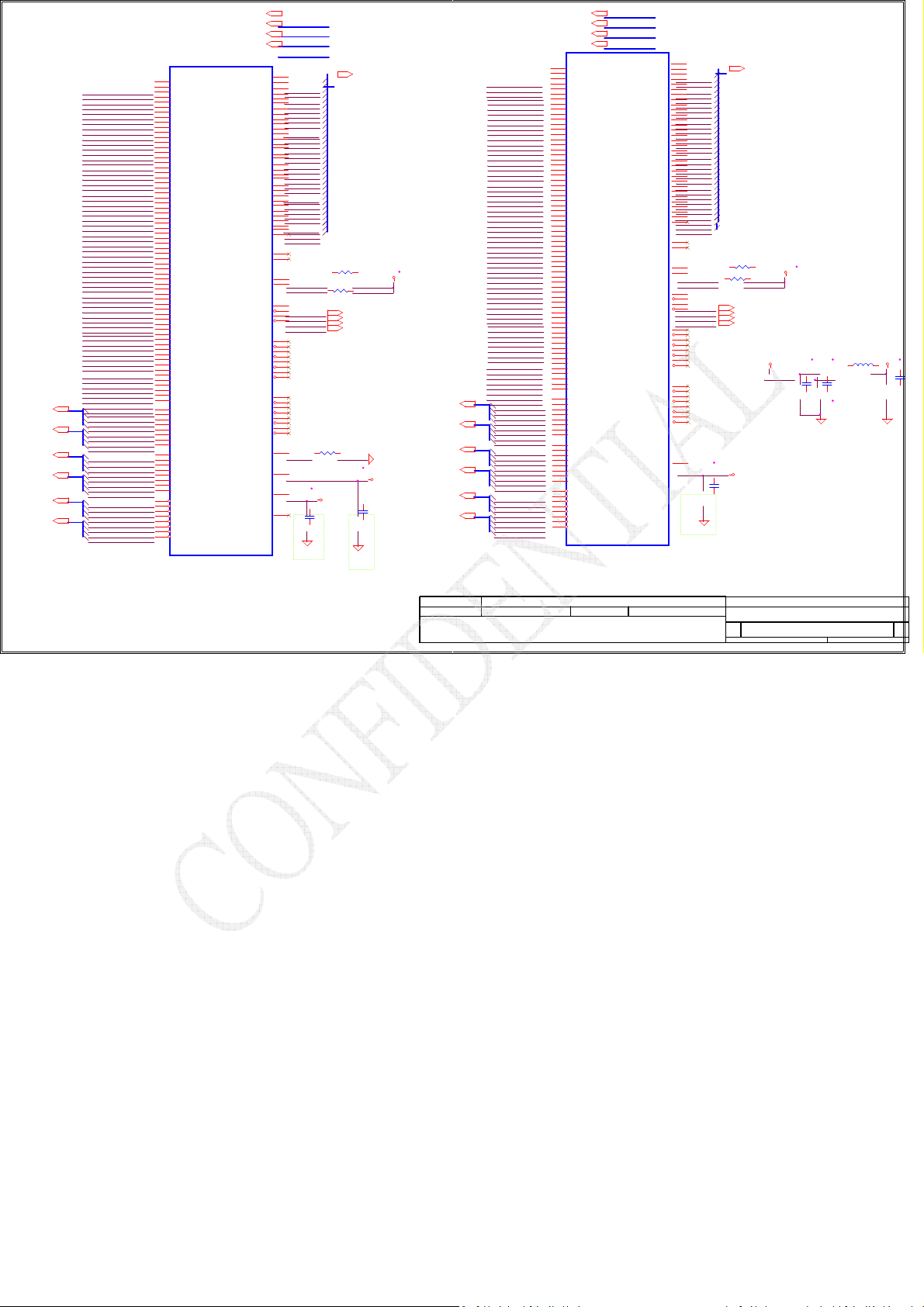

Page 4

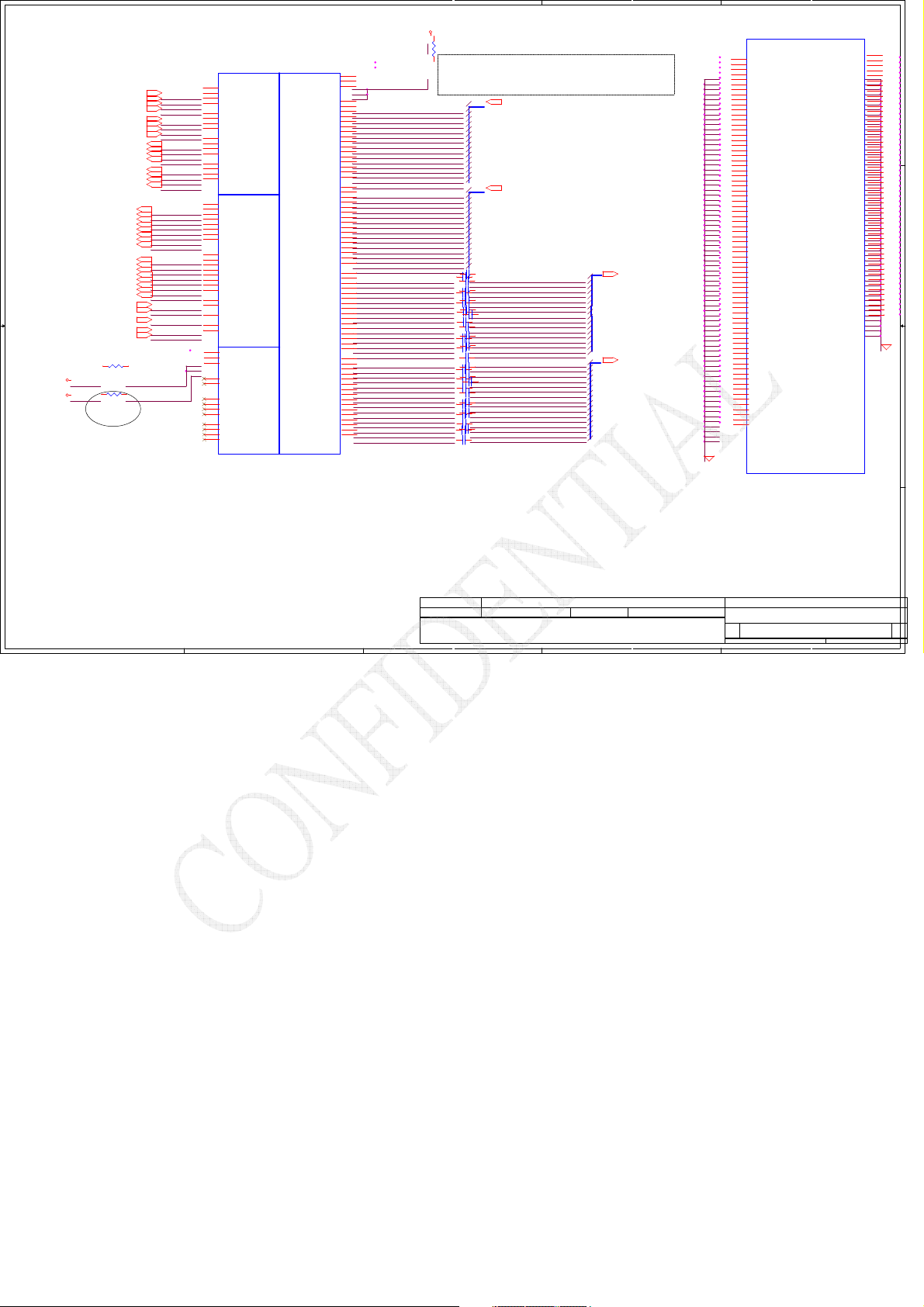

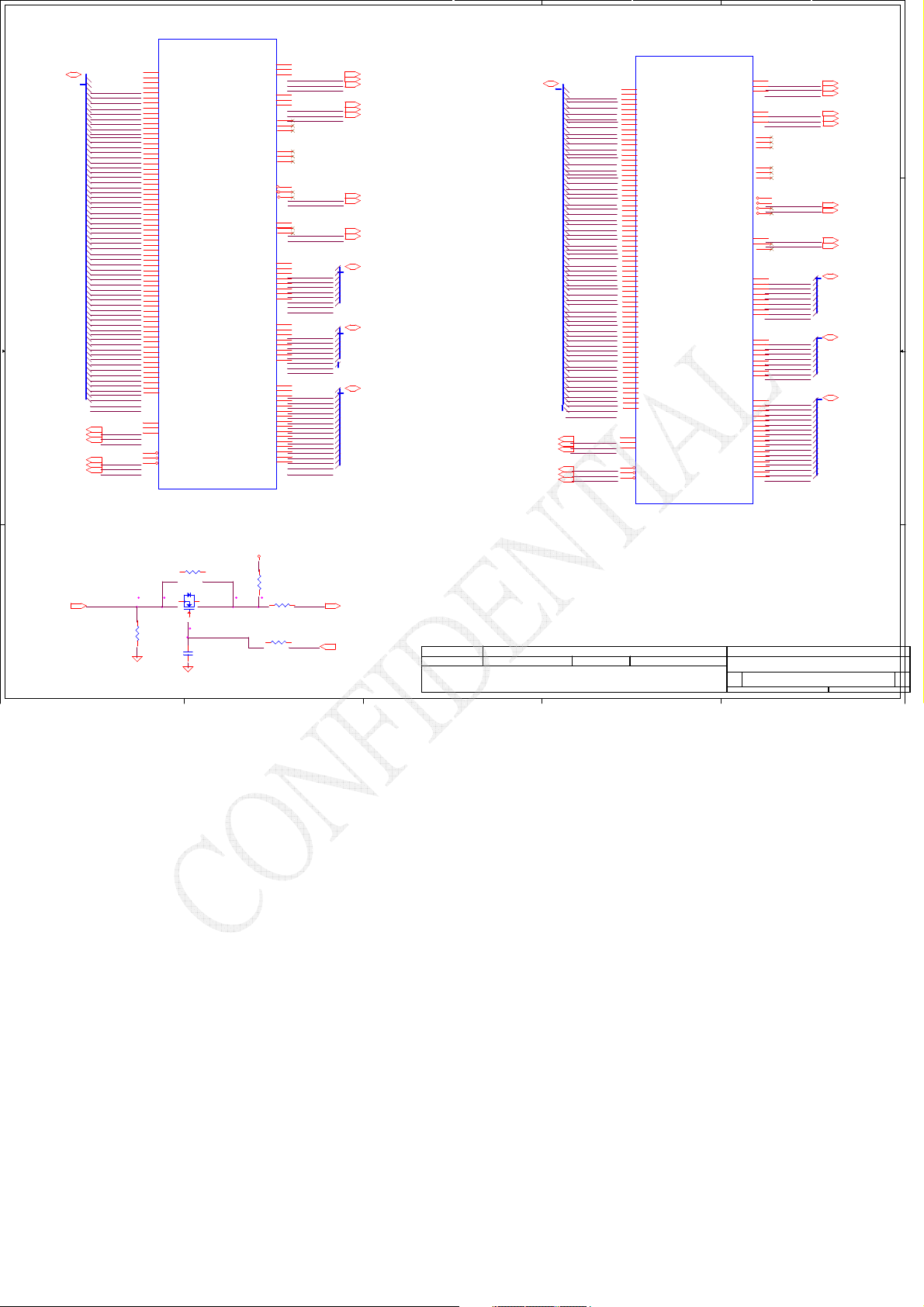

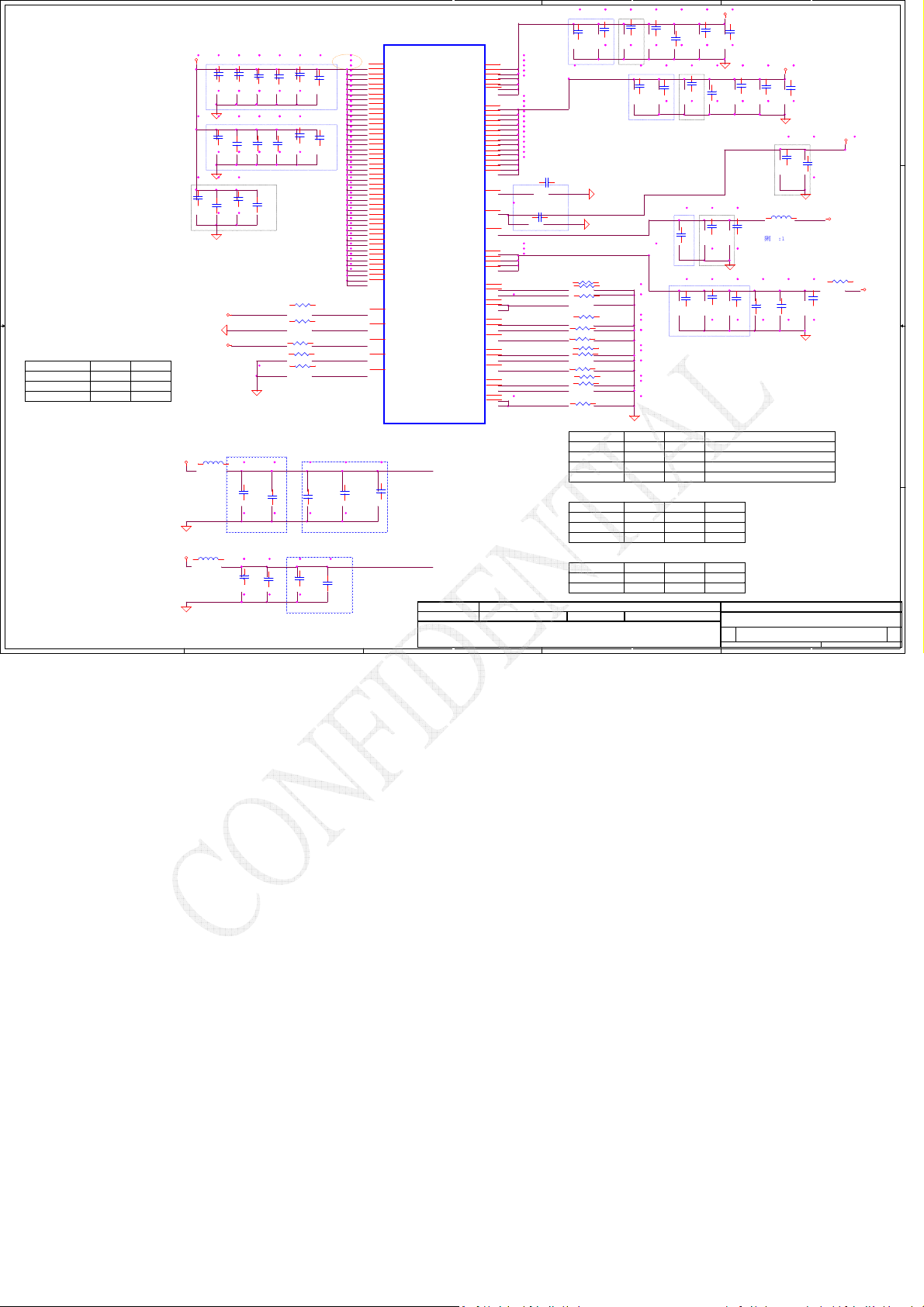

Voltage Rails

5

Power Plane Description

VIN

BATT+ Battery power supply (12.6V) N/A N/A N/A

B+

+VCC_CORE

D

+VGA_CORE

+VGFX_CORE Core voltage for UMA graphic ON OFF OFF

+0.75VS +0.75VP to +0.75VS switched power rail for DDR terminator

+1.0VSDGPU +1.0VSPDGPU to +1.0VSDGPU switched power rail for GPU

+1.05VS_VCCP

+1.05VS_PCH +1.05VS_VCCP to +1.05VS_PCH power for PCH

+1.5V

+1.5VS

+1.5VSDGPU +1.5VS to +1.5VSDGPU switched power rail for GPU ON OFF OFF

+1.8VS (+5VALW or +3VALW) to 1.8V switched power rail to PCH & GPU

+3VALW +3VALW always on power rail

+3VALW_EC + 3VALW always to KBC ON ON ON*

+3V_LAN

+3VALW_PCH

+3VS

C

+5VALW

+5VALW_PCH

+5VS + 5VALW to +5VS switched power rail OFFON OFF

+VSB +VSBP to +VSB always on power rail for sequence control ON ON*

+RTCVCC RTC power

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

B

S5 (Soft OFF)

EC SM Bus1 address

Power Power

+3VL Smart Battery

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

Core voltage for GPU

+1.05VS_VCCPP to +1.05VS_VCCP switched power rail for CPU

+1.5VP to +1.5V power rail for DDRIII ON ON OFF

+1.5V to +1.5VS switched power rail

+3VALW to +3V_LAN power rail for LAN

+3VALW to +3VALW_PCH power rail for PCH (Short Jumper)

+3VALW to +3VS power rail

+5VALWP to +5VALW power rail

+5VALW to +5VALW_PCH power rail for PCH (Short resister)

SIGNAL

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

HIGH

LOW

LOWLOWLOW

LOW LOW LOW LOW

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

ON

EC SM Bus2 address

Device

0x12

0x16

+3VS VGA(N13P-GLP)+3VL charger

+3VS PCH

Device

PCH SM Bus address

Power

Device

PCH

+3VALW

A

+3VS

+3VS

+3VS

+3VS

Clock Generator

DDR DIMMA

DDR DIMMB

Slot#1--WLAN

Address

1101 001x b

1001 000x b

1001 010x b

5

4

S1

N/A N/A N/A

ON

ON

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON

ON

ON ON

ON ON

ON

ON

ON ON

ONONON ON

ON

OFF

OFF

AddressAddress

0X9E

0x96

4

S3 S5

OFF

OFF

OFF

ON ON*

OFF

ON ON*

ON

OFF

OFF

OFF

3

2

1

BOM configu table

SKU Description B om config

QAQ10 UMA GIGA W/HDMI

N/AN/AN/A

OFF

OFF

1

QAQ11 DIS N13PGLP1G W/HDMI

2

QAQ13 DIS GLP2G W/HDMI/TPM

3

DA8@/8111E@/UMA@/TF@/10@/WIN8@/388@/COM@

DA8@/8111E@/OPT@/TF@/11@/WIN8@/388@/COM@

DA8@/8111E@/OPT@/030@/13@/WIN8@/388@/COM@

/TPM@/IN_TPM@

4

5

6

7

8

OFF

ON*

ON*

OFF

ON*

ONONONON

LOW

OFF

OFF

OFF

DA8@/8111E@/PCH@/UMA@/OPT@ /385@/388@/389@/IN_TPM@/TP M@/WB_TPM@/SM@/COM@/030@/T F@

/WIN8@/10@/11@/12@/13@/Rev 02@/Rev03@/Rev04@/Rev10@/V PRO@

388@: with 1394;

389@: without 1394.

IN_TPM@: TPM chip from vendor "INFINEON";

WB_TPM@: TPM chip from vendor "Nuvoton"

With TPM SKUs: mount "TPM@ and IN_TPM@ " or "TPM@ and WB_TPM@".

If has Vpro@, no 8111E@, Rev02@,Rev03@, Rev04@ and Rev10@.

X76 AND VGA configu table

SKU Description Config

Board ID Table

Board ID Rb V min Vtyp Vmax PCB Revision

0

1

2

3

4

5

6

7

4619IE30L11

1

2

4619IE30L21

3

4

5

Ra VCC

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

NC

100K +/- 5% 3.3V +/- 5%

100K +/- 5%

100K +/- 5%

100K +/- 5%

100K +/- 5%

100K +/- 5%

100K +/- 5%

100K +/- 5%

ZZZ

SAM 1G

ZZZ

SAM 2G

SAM1G@

SAM2G@

3.3V +/- 5%

3.3V +/- 5%

3.3V +/- 5%

3.3V +/- 5%

3.3V +/- 5%

3.3V +/- 5%

3.3V +/- 5%

ZZZ

HY1G@

Hynix 1G

ZZZ

HY2G@

Hynix 2G

0V

0.216 V0V0.250 V

0.503 V

0.436 V

0.819 V

0.712 V

1.185 V

1.036 V

1.650 V

1.453 V

2.200 V

1.935 V

3.300 V

2.500 V

0V

0.289 V

0.538 V

0.875 V

1.264 V

1.759 V

2.341 V

3.300 V

4619IE30L01

4619IE30L11

4619IE30L21

QAQ11 DIS N13P-GLP

QAQ13 DIS N13P-GLP

0.1

0.2

0.3

0.4

1.0

VPRO

D

C

B

PCH And PCBA table

UPCH1

BD82HM76 SLJ8E C1 BGA 989P PCH 030!

PCH

8111E@

PCB

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/09/23 2011/12/30

2011/09/23 2011/12/30

2011/09/23 2011/12/30

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

UPCH1

BD82QM77 QPRE C1 BGA 989P PCH

VPRO@

ZZZ

DA8@

PCB LA-8581P REV1 M/B

2

ZZZ

DAZ@

PCB QAQ10

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

4019IE

4019IE

4019IE

4 60Friday, August 24, 2012

4 60Friday, August 24, 2012

4 60Friday, August 24, 2012

1

of

of

of

A

B

B

B

Page 5

VSS

1

F22

VSS234

F19

VSS235

E30

VSS236

E27

VSS237

E24

VSS238

E21

VSS239

E18

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

D

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

C

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

B

5

JCPU1A

D

C

+1.05VS_VCCP

+1.05VS_VCCP

B

DMI_CRX_PTX_N0<27>

DMI_CRX_PTX_N1<27>

DMI_CRX_PTX_N2<27>

DMI_CRX_PTX_N3<27>

DMI_CRX_PTX_P0<27>

DMI_CRX_PTX_P1<27>

DMI_CRX_PTX_P2<27>

DMI_CRX_PTX_P3<27>

DMI_CTX_PRX_N0<27>

DMI_CTX_PRX_N1<27>

DMI_CTX_PRX_N2<27>

DMI_CTX_PRX_N3<27>

DMI_CTX_PRX_P0<27>

DMI_CTX_PRX_P1<27>

DMI_CTX_PRX_P2<27>

DMI_CTX_PRX_P3<27>

FDI_CTX_PRX_N0<27>

FDI_CTX_PRX_N1<27>

FDI_CTX_PRX_N2<27>

FDI_CTX_PRX_N3<27>

FDI_CTX_PRX_N4<27>

FDI_CTX_PRX_N5<27>

FDI_CTX_PRX_N6<27>

FDI_CTX_PRX_N7<27>

FDI_CTX_PRX_P0<27 >

FDI_CTX_PRX_P1<27 >

FDI_CTX_PRX_P2<27 >

FDI_CTX_PRX_P3<27 >

FDI_CTX_PRX_P4<27 >

FDI_CTX_PRX_P5<27 >

FDI_CTX_PRX_P6<27 >

FDI_CTX_PRX_P7<27 >

FDI_FSYNC0<27>

FDI_FSYNC1<27>

FDI_INT<27>

FDI_LSYNC0<27>

FDI_LSYNC1<27>

RC4 24.9_0402_1%

2

1

2

1

10K_0402_5%

R88

@

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

EDP_COMP

EDP_HPD#

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0]

H19

FDI0_TX#[1]

E19

FDI0_TX#[2]

F18

FDI0_TX#[3]

B21

FDI1_TX#[0]

C20

FDI1_TX#[1]

D18

FDI1_TX#[2]

E17

FDI1_TX#[3]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMPIO

A17

eDP_ICOMPO

B16

eDP_HPD#

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0]

E16

eDP_TX#[1]

D16

eDP_TX#[2]

F15

eDP_TX#[3]

TYCO_2013620-2_IVY BRIDGE

CONN@

4

J22

PEG_ICOMPI

J21

PEG_ICOMPO

H22

PEG_RCOMPO

K33

PEG_RX#[0]

M35

PEG_RX#[1]

L34

PEG_RX#[2]

J35

PEG_RX#[3]

J32

PEG_RX#[4]

H34

PEG_RX#[5]

H31

PEG_RX#[6]

G33

PEG_RX#[7]

PCI EXPRESS* - GRAPHICS

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

DMI

Intel(R) FDI

eDP

24.9_0402_1%

PEG_COMP

PCIE_GTX_C_CRX_N0

PCIE_GTX_C_CRX_N1

PCIE_GTX_C_CRX_N2

PCIE_GTX_C_CRX_N3

PCIE_GTX_C_CRX_N4

PCIE_GTX_C_CRX_N5

PCIE_GTX_C_CRX_N6

PCIE_GTX_C_CRX_N7

PCIE_GTX_C_CRX_N8

PCIE_GTX_C_CRX_N9

PCIE_GTX_C_CRX_N10

PCIE_GTX_C_CRX_N11

PCIE_GTX_C_CRX_N12

PCIE_GTX_C_CRX_N13

PCIE_GTX_C_CRX_N14

PCIE_GTX_C_CRX_N15

PCIE_GTX_C_CRX_P0

PCIE_GTX_C_CRX_P1

PCIE_GTX_C_CRX_P2

PCIE_GTX_C_CRX_P3

PCIE_GTX_C_CRX_P4

PCIE_GTX_C_CRX_P5

PCIE_GTX_C_CRX_P6

PCIE_GTX_C_CRX_P7

PCIE_GTX_C_CRX_P8

PCIE_GTX_C_CRX_P9

PCIE_GTX_C_CRX_P10

PCIE_GTX_C_CRX_P11

PCIE_GTX_C_CRX_P12

PCIE_GTX_C_CRX_P13

PCIE_GTX_C_CRX_P14

PCIE_GTX_C_CRX_P15

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_N8

PCIE_CTX_GRX_N9

PCIE_CTX_GRX_N10

PCIE_CTX_GRX_N11

PCIE_CTX_GRX_N12

PCIE_CTX_GRX_N13

PCIE_CTX_GRX_N14

PCIE_CTX_GRX_N15

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_P8

PCIE_CTX_GRX_P9

PCIE_CTX_GRX_P10

PCIE_CTX_GRX_P11

PCIE_CTX_GRX_P12

PCIE_CTX_GRX_P13

PCIE_CTX_GRX_P14

PCIE_CTX_GRX_P15

3

+1.05VS_VCCP

1

RC2

2

PEG_ICOMPI and RCOMPO signals should be shorted and routed

with - max length = 500 mils - typical impedance = 43 mohms

PEG_ICOMPO signals should be routed with - max length = 500 mils

- typical impedance = 14.5 mohms

PCIE_GTX_C_CRX_N[0..15] <13>

PEG signals swapped at VGA side.

PCIE_GTX_C_CRX_P[0..15] <13>

2

1

C222 0.1U_0402_16V7KOPT@

2

1

C136 0.1 U_0402_16V7KOPT@

2

1

C60 0.1U_0402_16V7 KOPT@

2

1

C75 0.1U_0402_16V7 KOPT@

2

1

C67 0.1U_0402_16V7KOPT@

2

1

C220 0.1U_0402_16V7KOPT@

2

1

C118 0.1U_ 0402_16V7KOPT@

2

1

C62 0.1U_0402_16 V7KOPT@

2

1

C59 0.1U_0402_16V7KOPT@

2

1

C115 0.1U_0402_16V7 KOPT@

2

1

C70 0.1U_0402_16V7KOPT@

2

1

C197 0.1U_0402_16V7KOPT@

2

1

C61 0.1U_0402_16 V7KOPT@

2

1

C223 0.1U_0 402_16V7KOPT@

2

1

C88 0.1U_0402_16 V7KOPT@

2

1

C68 0.1U_0402_16V7KOPT@

2

1

C209 0.1U_0402_16V7KOPT@

2

1

C66 0.1U_0402_16 V7KOPT@

2

1

C224 0.1U_0 402_16V7KOPT@

2

1

C89 0.1U_0402_16 V7KOPT@

2

1

C69 0.1U_0402_16V7KOPT@

2

1

C221 0.1U_0402_16V7 KOPT@

2

1

C135 0 .1U_0402_16V7KOPT@

2

1

C71 0.1U_0402_16 V7KOPT@

2

1

C74 0.1U_0402_16 V7KOPT@

2

1

C72 0.1U_0402_16V7KOPT@

2

1

C214 0.1U_0402_16V7KOPT@

2

1

C117 0.1 U_0402_16V7KOPT@

2

1

C78 0.1U_0402_16V7KOPT@

2

1

C87 0.1U_0402_16V7 KOPT@

2

1

C79 0.1U_0402_16V7KOPT@

2

1

C111 0.1U_0 402_16V7KOPT@

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_N3

PCIE_CTX_C_GRX_N4

PCIE_CTX_C_GRX_N5

PCIE_CTX_C_GRX_N6

PCIE_CTX_C_GRX_N7

PCIE_CTX_C_GRX_N8

PCIE_CTX_C_GRX_N9

PCIE_CTX_C_GRX_N10

PCIE_CTX_C_GRX_N11

PCIE_CTX_C_GRX_N12

PCIE_CTX_C_GRX_N13

PCIE_CTX_C_GRX_N14

PCIE_CTX_C_GRX_N15

PCIE_CTX_C_GRX_P0

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_P4

PCIE_CTX_C_GRX_P5

PCIE_CTX_C_GRX_P6

PCIE_CTX_C_GRX_P7

PCIE_CTX_C_GRX_P8

PCIE_CTX_C_GRX_P9

PCIE_CTX_C_GRX_P10

PCIE_CTX_C_GRX_P11

PCIE_CTX_C_GRX_P12

PCIE_CTX_C_GRX_P13

PCIE_CTX_C_GRX_P14

PCIE_CTX_C_GRX_P15

2

PCIE_CTX_C_GRX_N[0..15] <13>

PCIE_CTX_C_GRX_P[0..15] <13>

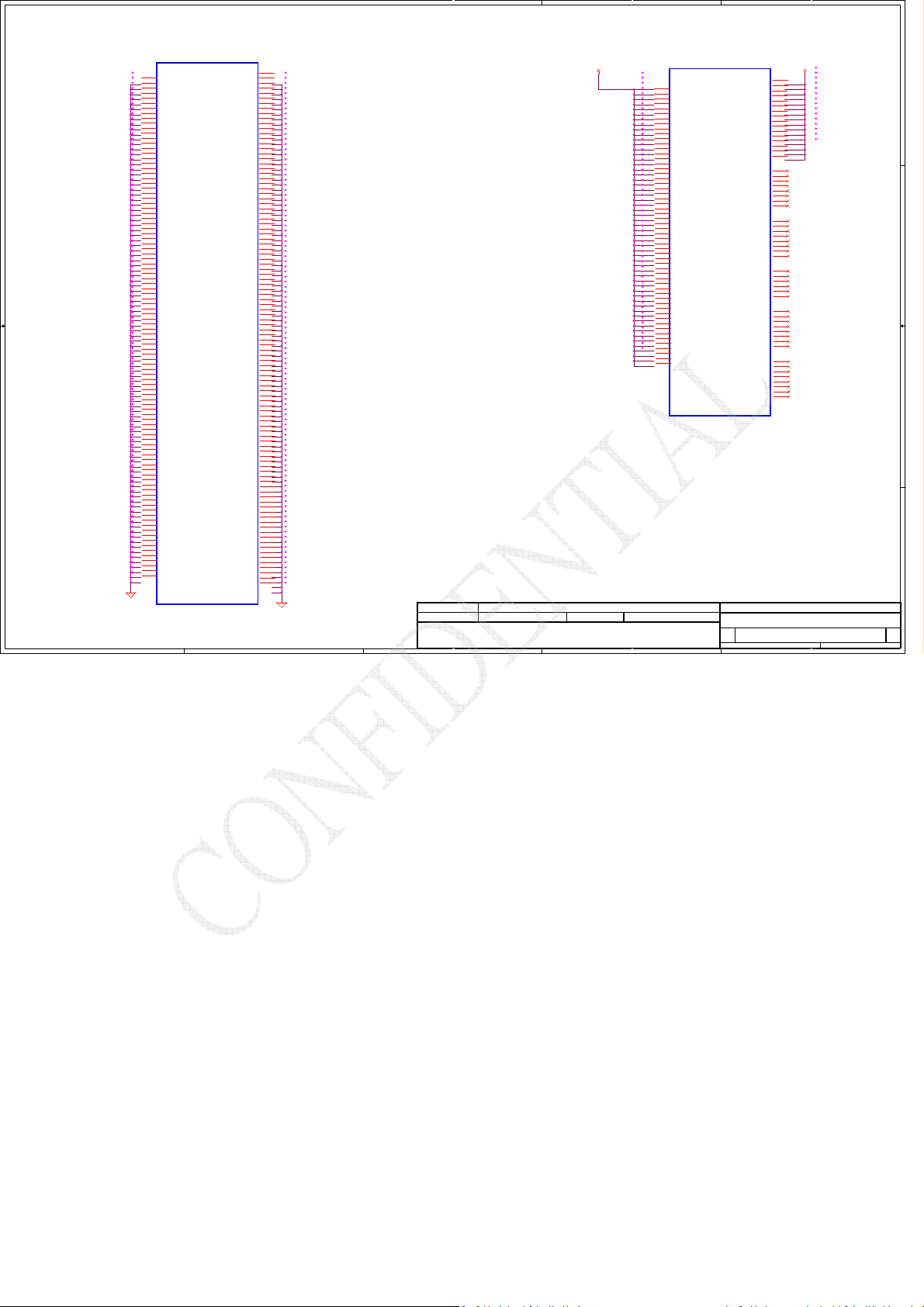

JCPU1I

T35

VSS161

T34

VSS162

T33

VSS163

T32

VSS164

T31

VSS165

T30

VSS166

T29

VSS167

T28

VSS168

T27

VSS169

T26

VSS170

P9

VSS171

P8

VSS172

P6

VSS173

P5

VSS174

P3

VSS175

P2

VSS176

N35

VSS177

N34

VSS178

N33

VSS179

N32

VSS180

N31

VSS181

N30

VSS182

N29

VSS183

N28

VSS184

N27

VSS185

N26

VSS186

M34

VSS187

L33

VSS188

L30

VSS189

L27

VSS190

L9

VSS191

L8

VSS192

L6

VSS193

L5

VSS194

L4

VSS195

L3

VSS196

L2

VSS197

L1

VSS198

K35

VSS199

K32

VSS200

K29

VSS201

K26

VSS202

J34

VSS203

J31

VSS204

H33

VSS205

H30

VSS206

H27

VSS207

H24

VSS208

H21

VSS209

H18

VSS210

H15

VSS211

H13

VSS212

H10

VSS213

H9

VSS214

H8

VSS215

H7

VSS216

H6

VSS217

H5

VSS218

H4

VSS219

H3

VSS220

H2

VSS221

H1

VSS222

G35

VSS223

G32

VSS224

G29

VSS225

G26

VSS226

G23

VSS227

G20

VSS228

G17

VSS229

G11

VSS230

F34

VSS231

F31

VSS232

F29

VSS233

TYCO_2013620-2_IVY BRIDGE

CONN@

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

2011/09/23 2012/12/31

2011/09/23 2012/12/31

2011/09/23 2012/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Title

Title

Title

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

4019IE

4019IE

4019IE

Date: Sheet

Date: Sheet

2

Date: Sheet

5 60Friday, August 24, 2012

5 60Friday, August 24, 2012

5 60Friday, August 24, 2012

1

A

B

B

B

of

of

of

Page 6

4

1

0_0402_5%

1

0.1U_0402_16V4Z

C85

+1.5V_CPU_VDDQ

R81

200_0402_1%

VDDPWRGOOD

R110

39_0402_1%

@

2

@

1

D

@

2

Q5

2N7002_SOT23-3

G

2

@

S

3

D

5

D

4

3

2

SYSTEM_PWROK<27>

1

R104

0_0402_5%

short@

2

RC21 0_0 402_5%

short@

RUN_ON_CPU1.5VS3#<10,45>

+3VS

D_PWG

+3VALW

R289

200_0402_1%

PM_DRAM_PWRGD<27>

RC13

@

10K_0402_5%

SUSP<11,40,43,45>

+3VALW

5

1

P

B

2

A

G

3

RC17

RC16

U5

74AHC1G08DCKR_SC70-5

O

1

0_0402_5%

C

Processor Pullups

H_PROCHOT#

B

A

1

R47

62_0402_5%

CC62

@

220P_0402_25V8J

H_CPUPWRGD_R

5

+1.05VS_VCCP

2

H_PROCHOT#<41,47>

H_THERMTRIP#<29>

PROC_SELECT#:

Sandy Bridge---output high;

Ivy Bridge---output low.

T0501

H_PECI<29,41>

H_PROCHOT#

H_PM_SYNC<27>

H_CPUPWRGD<29>

VDDPWRGOOD

220P_0402_25V8J

H_SNB_IVB#<29>

H_CATERR#

2

1

RC44

43_0402_1%

H_PECI_R

R58

2

1

H_PROCHOT#_R

56_0402_5%

Place R58 close to CPU.

2

1

H_THERMTRIP#_R

R14 0_0402_5%

short@

R15

2

1

H_PM_SYNC_R

0_0402_5%

short@

R16

2

1

H_CPUPWRGD_R

0_0402_5%

short@

R79

2

1

130_0402_1%

VDDPWRGOOD_R

BUF_CPU_RST#

R5010K_0402_5%

C379

@

JCPU1B

C26

PROC_SELECT#

AN34

SKTOCC#

AL33

CATERR#

AN33

PECI

AL32

PROCHOT#

AN32

THERMTRIP#

AM34

PM_SYNC

AP33

UNCOREPWRGOOD

V8

SM_DRAMPWROK

AR33

RESET#

TYCO_2013620-2_IVY BRIDGE

CONN@

4

BCLK

BCLK#

MISCTHERMALPWR MANAGEMENT

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

JTAG & BPM

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

A28

A27

A16

A15

R8

AK1

A5

A4

AP29

AP27

AR26

AR27

AP30

AR28

AP26

AL35

AT28

AR29

AR30

AT30

AP32

AR31

AT31

AR32

XDP_DBRESET#

CLK_CPU_DMI_R

CLK_CPU_DMI#_R

CLK_CPU_DPLL_R

CLK_CPU_DPLL#_R

H_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

XDP_PRDY#_R

XDP_PREQ#_R

XDP_TCK_R

XDP_TMS_R

XDP_TRST#_R

XDP_TDI_R

XDP_TDO_R

short@

2

1

R138 0_040 2_5%

2

1

R139 0_040 2_5%

short@

2

1

R126 1K_04 02_5%

2

1

R115 1K_040 2_5%

H_DRAMRST# <7>

Compal Secret Data

Compal Secret Data

2011/09/23 2012/12/31

2011/09/23 2012/12/31

2011/09/23 2012/12/31

Compal Secret Data

PLT_RST#<28,34,35,36,37,39,41,42,44>

CLK_CPU_DMI <26>

CLK_CPU_DMI# <26>

+1.05VS_VCCP

DDR3 Compensation Signals

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

EN_DFAN1<41>

Deciphered Date

Deciphered Date

Deciphered Date

+FAN1

10mil

+5VS

2

1

1

1

1A

1

C1

10U_0805_10V4Z

2

2

2

2

U58

1

EN

2

VIN

3

VOUT

4

VSET

G996P11U SOP 8P

+3VS

5

U3

1

P

NC

Y

2

A

G

3

+1.05VS_VCCP

0.1U_0402_16V4Z

C84

4

BUFO_CPU_RST#

SN74LVC1G07DCKR_SC70-5

PU/PD for JTAG signals

XDP_TMS_R

XDP_TDI_R

XDP_PREQ#_R

RC42140_0402_1%

RC4325.5_0402_1%

RC45200_0402_1%

XDP_TDO_R

XDP_TCK_R

XDP_TRST#_R

FAN Control Circuit

2

C863

10U_0805_10V4Z

8

GND

7

GND

6

GND

5

GND

+FAN1

1

2

C864

@

1000P_0402_50V7K

1

Compal Electronics, Inc.

Title

Title

Title

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

4019IE

4019IE

4019IE

Date: Sheet

Date: Sheet

Date: Sheet

1

R64

75_0402_5%

2

R72

43_0402_1%

1

C865

0.01U_0402_25V7K

2

1

BUF_CPU_RST#

+1.05VS_VCCP

RC4651_0402_5%

RC4751_0402_5%

RC4851_0402_5% @

RC4951_0402_5%

RC5751_0402_5%

RC5551_0402_5%

JFAN

1

1

2

2

3

3

4

GND

5

GND

ACES_85205-03001

CONN@

R3 1 0K_0402_5%

2

@

1

@

R73

0_0402_5%

2

1

+3VS

FAN_SPEED <41>

6 60Friday, August 24, 2012

of

6 60Friday, August 24, 2012

of

6 60Friday, August 24, 2012

of

C

B

A

B

B

B

Page 7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

1

DDRB_CLK0 <12>

DDRB_CLK0# <12>

DDRB_CKE0 <12>

DDRB_CLK1 <12>

DDRB_CLK1# <12>

DDRB_CKE1 <12>

DDRB_SCS0# <12>

DDRB_SCS1# <12>

DDRB_ODT0 <12>

DDRB_ODT1 <12>

DDR_B_DQS#[0..7] <12>

DDR_B_DQS[0..7] <12>

DDR_B_MA[0..15] <12>

D

C

B

3

DDR_B_D[0..63]<12>

DDR_B_BS0<12>

DDR_B_BS1<12>

DDR_B_BS2<12>

DDR_B_CAS#<12>

DDR_B_RAS#<12>

DDR_B_WE#<12>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

RSVD_TP[1]

RSVD_TP[2]

RSVD_TP[3]

RSVD_TP[4]

RSVD_TP[5]

RSVD_TP[6]

SA_CS#[0]

SA_CS#[1]

RSVD_TP[7]

RSVD_TP[8]

SA_ODT[0]

SA_ODT[1]

RSVD_TP[9]

RSVD_TP[10]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

4

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDRA_CLK0 <11>

DDRA_CLK0# <11>

DDRA_CKE0 <11>

DDRA_CLK1 <11>

DDRA_CLK1# <11>

DDRA_CKE1 <11>

DDRA_SCS0# <11>

DDRA_SCS1# <11>

DDRA_ODT0 <11>

DDRA_ODT1 <11>

DDR_A_DQS#[0..7] <11>

DDR_A_DQS[0..7] <11>

DDR_A_MA[0..15] <11>

5

JCPU1C

C5

DDR_A_D[0..63]<11>

D

C

DDR_A_BS0<11>

DDR_A_BS1<11>

DDR_A_BS2<11>

B

DDR_A_CAS#<11>

DDR_A_RAS#<11>

DDR_A_WE#<11>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

SA_DQ[0]

D5

SA_DQ[1]

D3

SA_DQ[2]

D2

SA_DQ[3]

D6

SA_DQ[4]

C6

SA_DQ[5]

C2

SA_DQ[6]

C3

SA_DQ[7]

F10

SA_DQ[8]

F8

SA_DQ[9]

G10

SA_DQ[10]

G9

SA_DQ[11]

F9

SA_DQ[12]

F7

SA_DQ[13]

G8

SA_DQ[14]

G7

SA_DQ[15]

K4

SA_DQ[16]

K5

SA_DQ[17]

K1

SA_DQ[18]

J1

SA_DQ[19]

J5

SA_DQ[20]

J4

SA_DQ[21]

J2

SA_DQ[22]

K2

SA_DQ[23]

M8

SA_DQ[24]

N10

SA_DQ[25]

N8

SA_DQ[26]

N7

SA_DQ[27]

M10

SA_DQ[28]

M9

SA_DQ[29]

N9

SA_DQ[30]

M7

SA_DQ[31]

AG6

SA_DQ[32]

AG5

SA_DQ[33]

AK6

SA_DQ[34]

AK5

SA_DQ[35]

AH5

SA_DQ[36]

AH6

SA_DQ[37]

AJ5

SA_DQ[38]

AJ6

SA_DQ[39]

AJ8

SA_DQ[40]

AK8

SA_DQ[41]

AJ9

SA_DQ[42]

AK9

SA_DQ[43]

AH8

SA_DQ[44]

AH9

SA_DQ[45]

AL9

SA_DQ[46]

AL8

SA_DQ[47]

AP11

SA_DQ[48]

AN11

SA_DQ[49]

AL12

SA_DQ[50]

AM12

SA_DQ[51]

AM11

SA_DQ[52]

AL11

SA_DQ[53]

AP12

SA_DQ[54]

AN12

SA_DQ[55]

AJ14

SA_DQ[56]

AH14

SA_DQ[57]

AL15

SA_DQ[58]

AK15

SA_DQ[59]

AL14

SA_DQ[60]

AK14

SA_DQ[61]

AJ15

SA_DQ[62]

AH15

SA_DQ[63]

AE10

SA_BS[0]

AF10

SA_BS[1]

V6

SA_BS[2]

AE8

SA_CAS#

AD9

SA_RAS#

AF9

SA_WE#

TYCO_2013620-2_IVY BRIDGE

CONN@

DDR SYSTEM MEMORY A

2

JCPU1D

C9

SB_DQ[0]

A7

SB_DQ[1]

D10

SB_DQ[2]

C8

SB_DQ[3]

A9

SB_DQ[4]

A8

SB_DQ[5]

D9

SB_DQ[6]

D8

SB_DQ[7]

G4

SB_DQ[8]

F4

SB_DQ[9]

F1

SB_DQ[10]

G1

SB_DQ[11]

G5

SB_DQ[12]

F5

SB_DQ[13]

F2

SB_DQ[14]

G2

SB_DQ[15]

J7

SB_DQ[16]

J8

SB_DQ[17]

K10

SB_DQ[18]

K9

SB_DQ[19]

J9

SB_DQ[20]

J10

SB_DQ[21]

K8

SB_DQ[22]

K7

SB_DQ[23]

M5

SB_DQ[24]

N4

SB_DQ[25]

N2

SB_DQ[26]

N1

SB_DQ[27]

M4

SB_DQ[28]

N5

SB_DQ[29]

M2

SB_DQ[30]

M1

SB_DQ[31]

AM5

SB_DQ[32]

AM6

SB_DQ[33]

AR3

SB_DQ[34]

AP3

SB_DQ[35]

AN3

SB_DQ[36]

AN2

SB_DQ[37]

AN1

SB_DQ[38]

AP2

SB_DQ[39]

AP5

SB_DQ[40]

AN9

SB_DQ[41]

AT5

SB_DQ[42]

AT6

SB_DQ[43]

AP6

SB_DQ[44]

AN8

SB_DQ[45]

AR6

SB_DQ[46]

AR5

SB_DQ[47]

AR9

SB_DQ[48]

AJ11

SB_DQ[49]

AT8

SB_DQ[50]

AT9

SB_DQ[51]

AH11

SB_DQ[52]

AR8

SB_DQ[53]

AJ12

SB_DQ[54]

AH12

SB_DQ[55]

AT11

SB_DQ[56]

AN14

SB_DQ[57]

AR14

SB_DQ[58]

AT14

SB_DQ[59]

AT12

SB_DQ[60]

AN15

SB_DQ[61]

AR15

SB_DQ[62]

AT15

SB_DQ[63]

AA9

SB_BS[0]

AA7

SB_BS[1]

R6

SB_BS[2]

AA10

SB_CAS#

AB8

SB_RAS#

AB9

SB_WE#

TYCO_2013620-2_IVY BRIDGE

CONN@

AE2

SB_CLK[0]

AD2

SB_CLK#[0]

R9

SB_CKE[0]

AE1

SB_CLK[1]

AD1

SB_CLK#[1]

R10

SB_CKE[1]

AB2

RSVD_TP[11]

AA2

RSVD_TP[12]

T9

RSVD_TP[13]

AA1

RSVD_TP[14]

AB1

RSVD_TP[15]

T10

RSVD_TP[16]

AD3

SB_CS#[0]

AE3

SB_CS#[1]

AD6

RSVD_TP[17]

AE6

RSVD_TP[18]

AE4

SB_ODT[0]

AD4

AD5

SB_ODT[1]

RSVD_TP[19]

AE5

RSVD_TP[20]

D7

SB_DQS#[0]

F3

SB_DQS#[1]

K6

SB_DQS#[2]

N3

SB_DQS#[3]

AN5

SB_DQS#[4]

AP9

SB_DQS#[5]

AK12

SB_DQS#[6]

AP15

SB_DQS#[7]

C7

SB_DQS[0]

G3

SB_DQS[1]

J6

SB_DQS[2]

M3

SB_DQS[3]

AN6

SB_DQS[4]

AP8

SB_DQS[5]

AK11

SB_DQS[6]

AP14

SB_DQS[7]

DDR SYSTEM MEMORY B

AA8

SB_MA[0]

T7

SB_MA[1]

R7

SB_MA[2]

T6

SB_MA[3]

T2

SB_MA[4]

T4

SB_MA[5]

T3

SB_MA[6]

R2

SB_MA[7]

T5

SB_MA[8]

R3

SB_MA[9]

AB7

SB_MA[10]

R1

SB_MA[11]

T1

SB_MA[12]

AB10

SB_MA[13]

R5

SB_MA[14]

R4

SB_MA[15]

+1.5V

@

R124 0_0402_5%

QC3

BSS138_SOT23

D

S

3

H_DRAMRST#<6>

A

H_DRAMRST#

4.99K_0402_1%

5

R119

1

G

2

C86

0.047U_0402_16V4Z

DDR3_DRAMRST#_R

DRAMRST_CNTRL

R123

1K_0402_5%

R129 1K_0402_5%

short@

R118 0_0402_5%

4

SM_DRAMRST# <11,12>

DRAMRST_CNTRL_PCH <10,26>

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2011/09/23 2012/12/31

2011/09/23 2012/12/31

2011/09/23 2012/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Title

Title

Title

Compal Electronics, Inc.

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

4019IE

4019IE

4019IE

Date: Sh eet

Date: Sh eet

Date: She et

7 60Friday, August 24, 2012

of

7 60Friday, August 24, 2012

of

7 60Friday, August 24, 2012

1

of

A

B

B

B

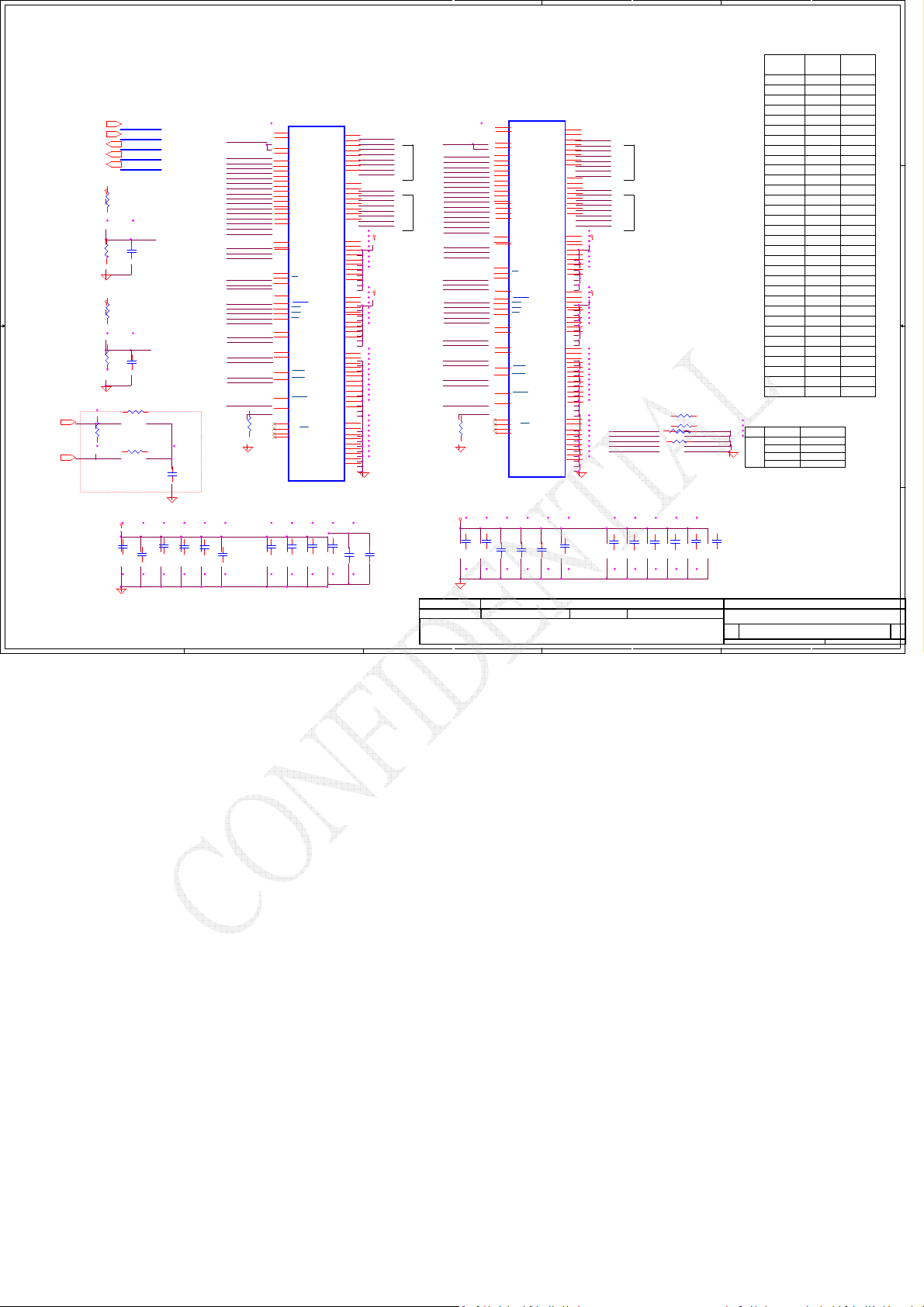

Page 8

5

D

CFG[1:0]: reserved configuration lane.

CFG[3]: reserved

CFG[17:7]: reserved configuration lanes.

CFG[17:0]:

Processor internal pull up 5~15Kohm to VCCIO

C

B

T266 PAD

T251 PAD

T252 PAD

T253 PAD

T254 PAD

T255 PAD

T256 PAD

T257 PAD

T258 PAD

T259 PAD

T260 PAD

T261 PAD

T267 PAD

T268 PAD

T269 PAD

T270 PAD

T262 PAD

T263 PAD

T245 PAD

T246 PAD

T247 PAD

T248 PAD

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

4

JCPU1E

AK28

CFG[0]

AK29

CFG[1]

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

J15

RSVD27

TYCO_2013620-2_IVY BRIDGE

CONN@

CFG

RESERVED

VCC_DIE_SENSE

VSS_DIE_SENSE

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

RSVD40

RSVD_NCTF1

RSVD_NCTF2

RSVD_NCTF3

RSVD_NCTF4

RSVD_NCTF5

RSVD_NCTF6

RSVD_NCTF7

RSVD_NCTF8

RSVD_NCTF9

RSVD_NCTF10

RSVD51

RSVD52

BCLK_ITP

BCLK_ITP#

RSVD_NCTF11

RSVD_NCTF12

RSVD_NCTF13

3

2

1

CFG Straps for Processor

CFG2

AH27

AH26

L7

AG7

AE7

AK2

W8

AT26

AM33

AJ27

T8

J16

H16

G16

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AN35

AM35

AT2

AT1

AR1

B1

KEY

CLK_RES_ITP <26>

CLK_RES_ITP# <26>

PEG Static Lane Reversal - CFG2 is for the 16x

1:(Default) Normal Operation; Lane #

CFG2

definition matches socket pin map definition

0:Lane Reversed

Display Port Presence Strap

1 : Disabled; No Physical Display Port

CFG4

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

PCIE Port Bifurcation Straps

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

CFG[6:5]

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG4

CFG6

CFG5

1K_0402_1%

CFG7

RC51

1K_0402_1%

RC52

@

1K_0402_1%

RC54

@

RC53

@

1K_0402_1%

RC56

@

1K_0402_1%

D

C

B

PEG DEFER TRAINING

1: (Default) PEG Train immediately

CFG7

following RESETB de assertion

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

2011/09/23 2012/12/31

2011/09/23 2012/12/31

2011/09/23 2012/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

0: PEG Wait for BIOS for training

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

Title

Title

Title

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

4019IE

4019IE

4019IE

8 60Friday, August 24, 201 2

8 60Friday, August 24, 201 2

8 60Friday, August 24, 201 2

1

A

B

B

B

of

of

of

Page 9

5

JCPU1H

AT35

VSS1

AT32

VSS2

AT29

VSS3

AT27

VSS4

AT25

VSS5

AT22

VSS6

AT19

D

C

B

A

VSS7

AT16

VSS8

AT13

VSS9

AT10

VSS10

AT7

VSS11

AT4

VSS12

AT3

VSS13

AR25

VSS14

AR22

VSS15

AR19

VSS16

AR16

VSS17

AR13

VSS18

AR10

VSS19

AR7

VSS20

AR4

VSS21

AR2

VSS22

AP34

VSS23

AP31

VSS24

AP28

VSS25

AP25

VSS26

AP22

VSS27

AP19

VSS28

AP16

VSS29

AP13

VSS30

AP10

VSS31

AP7

VSS32

AP4

VSS33

AP1

VSS34

AN30

VSS35

AN27

VSS36

AN25

VSS37

AN22

VSS38

AN19

VSS39

AN16

VSS40

AN13

VSS41

AN10

VSS42

AN7

VSS43

AN4

VSS44

AM29

VSS45

AM25

VSS46

AM22

VSS47

AM19

VSS48

AM16

VSS49

AM13

VSS50

AM10

VSS51

AM7

VSS52

AM4

VSS53

AM3

VSS54

AM2

VSS55

AM1

VSS56

AL34

VSS57

AL31

VSS58

AL28

VSS59

AL25

VSS60

AL22

VSS61

AL19

VSS62

AL16

VSS63

AL13

VSS64

AL10

VSS65

AL7

VSS66

AL4

VSS67

AL2

VSS68

AK33

VSS69

AK30

VSS70

AK27

VSS71

AK25

VSS72

AK22

VSS73

AK19

VSS74

AK16

VSS75

AK13

VSS76

AK10

VSS77

AK7

VSS78

AK4

VSS79

AJ25

VSS80

TYCO_2013620-2_IVY BRIDGE

CONN@

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

4

JCPU1F

+VCC_CORE

AG35

VCC1

AG34

VCC2

97A

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

TYCO_2013620-2_IVY BRIDGE

CONN@

3

POWER

PEG AND DDR

CORE SUPPLY

VSS_SENSE_VCCIO

SENSE LINES SVID

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

AH13

8.5A

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

AJ29

AJ30

AJ28

AJ35

AJ34

B10

A10

VCCSENSE_R

VSSSENSE_R

+1.05VS_VCCP

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

RC61

H_CPU_SVIDDAT

R52 0_0402_5%short@

R51 0_0402_5%

1

1

2

2

+1.05VS_VCCP

0.1U_0402_16V4Z

CC49

130_0402_1%

short@

R168

10_0402_1%

R158

10_0402_1%

H_CPU_SVIDCLK

1

RC60

75_0402_5%

2

43_0402_1%

+1.05VS_VCCP

RC137

Place the PU resistors

R53, R54 close to CPU

2

+1.05VS_VCCP

VCCIO_SENSE <51>

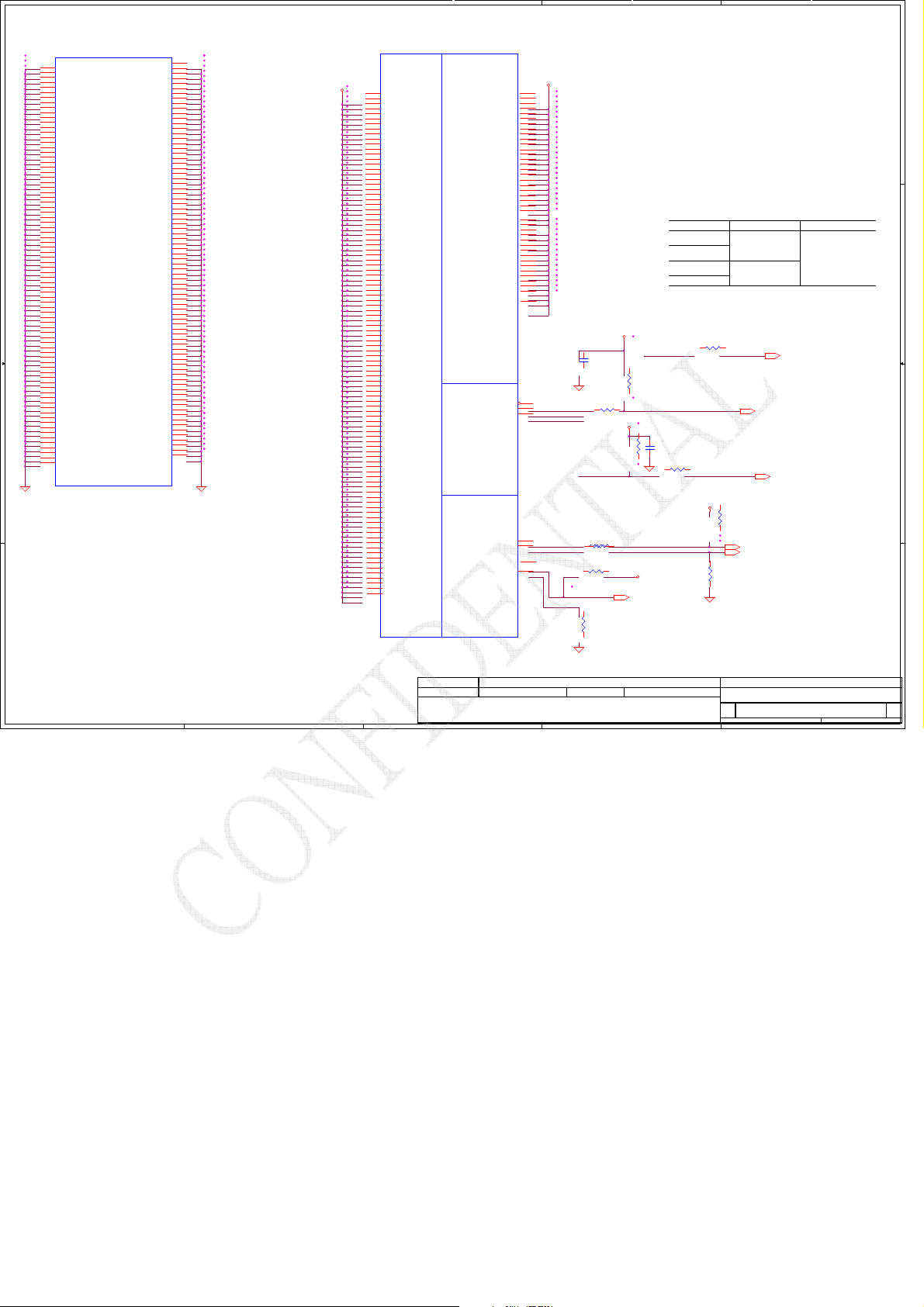

Package Sensing Recommendations--PDDG P30

Sense Trace Impedance Trace Length Match

VCC_SENSE /

VSS_SENSE

VCCAXG_SENSE /

VSSAXG_SENSE

VCCIO_SENSE /

VSS_SENSE_VCCIO

VCCSA

RC59 0_0402_5%

Place the PU resistors

RC60, RC137 close to CPU.

0.1U_0402_16V4Z

CC50

RC65 0_0402_5%

short@

short@

+VCC_CORE

1

2

1

R53

100_0402_1%

2

R54

100_0402_1%

25.5-34.5ohm

55ohm

VR_SVID_ALRT# <54>

VCCSENSE <54>

VSSSENSE <54>

1

D

<25 mils

C

VR_SVID_CLK <54>

B

VR_SVID_DAT <54>

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

2011/09/23 2012/12/31

2011/09/23 2012/12/31

2011/09/23 2012/12/31

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Title

Title

Title

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

SCHEMATICS, MB A8581

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

4019IE

4019IE

4019IE

Date: Sheet

Date: Sheet

2

Date: Sheet

1

B

B

B

9 60Friday, August 24, 201 2

of

9 60Friday, August 24, 201 2

of

9 60Friday, August 24, 20 12

of

Page 10

5

4

3

2

1

+1.5V_CPU_VDDQ

+1.5V

VAXG_SENSE

VSSAXG_SENSE

SM_VREF

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

VCCIO_SEL

1

+VSB

2

3

Q208B

5

2N7002DW-T/R7_SOT363-6

4

AK35

AK34

AL1

B4

D1

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

M27

M26

L26

J26

J25

J24

H26

H25

H23

C22

C24

A19

R135

100K_0402_5%

RUN_ON_CPU1.5VS3

VCC_AXG_SENSE

VSS_AXG_SENSE

VCC_AXG_SENSE

VSS_AXG_SENSE

+V_SM_VREF_CNT

VREFDQ_DIMMA_CPU

VREFDQ_DIMMB_CPU

+1.5V_CPU_VDDQ

6A

+3VALW

1

R134

D

R132

@

+GFX_CORE

1U_0402_6.3V6K

1

2

0_0402_5%

R133

0_0402_5%

AT24

33A

AT23

AT21

AT20

AT18

AT17

AR24

AR23

AR21

AR20

AR18

AR17

AP24

AP23

AP21

AP20

AP18

AP17

AN24

AN23

AN21

AN20

AN18

AN17

AM24

AM23

AM21

AM20

AM18

AM17

AL24

AL23

AL21

AL20

AL18

AL17

AK24

AK23

AK21

AK20

AK18

AK17

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AH24

AH23

AH21

AH20

AH18

AH17

1.5A

B6

A6

330U_X_2VM_R6M

A2

1

CC60

CC61

+

2

SUSP#<39,41,45,50,51 ,52,57>

CPU1.5V_S3_GATE<41>

C

B

10U_0805_6.3V6M

CC58

+1.8VS_VCCPLL

1U_0402_6.3V6K

1

CC59

2

+1.8VS

RC120

0_0805_5%

A

100K_0402_5%

2

6

Q208A

2

2N7002DW-T/R7_SOT363-6

1

POWER

JCPU1G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

VAXG50

VAXG51

VAXG52

VAXG53

VAXG54

VCCPLL1

VCCPLL2

VCCPLL3

1.8V RAIL

TYCO_2013620-2_IVY BRIDGE

CONN@

RUN_ON_CPU1.5VS3#

SENSE

LINES

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREFMISC

GRAPHICS

DDR3 -1.5V RAILS

SA RAIL

8

7

6

5

Close to CPU

1

R86 1 00_0402_1%

1

CC178

10A

10U_0805_6.3V6M

CC51

H_VCCSA_VID0 <53>

H_VCCSA_VID1 <53>

RC113

@

Q7

AO4728L_SO8

1

R136

2

330K_0402_1%

R89

2

2

VCC_AXG_SENSE <54>

VSS_AXG_SENSE <54>

1

2

10U_0805_6.3V6M

CC52

10U_0805_6.3V6M

CC40

0_0402_5%

+1.5V_CPU_VDDQ

1

2

4

C196

0.1U_0603_50V7K

+GFX_CORE

100_0402_1%

RC76 0_04 02_5%

2

0.1U_0402_16V4Z

10U_0805_6.3V6M

CC53

3

3

@

QC5

1

AP2302GN-HF_SOT23-3

RUN_ON_CPU1.5VS3

10U_0805_6.3V6M

10U_0805_6.3V6M

CC54

1

@

@

2

C107

CC38

10U_0805_10V4Z

+V_SM_VREF should

have 20 mil trace width

+V_SM_VREF

10U_0805_6.3V6M

1

+

CC56

CC55

CC57

330U_X_2VM_R6M

2

0.1U_0402_10V6K

+1.5V_CPU_VDDQ

check Confirm QC6, QC7 is low Rdson or not--Joyce 0929

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0603_6.3V6M

@

1

CC43

+

CC44

CC42

CC41

@

0_0402_5%

10K_0402_5%

330U_X_2VM_R6M

2

+VCCSA_SENSE <53>

RC111

VCCSA_VID Configuration --CPU EDS Page99.

VCCSA_VID[0] output default logic state is low for Sandy Bridge processors

+3VS

2

RC112

@

1

+VCCSA

+VCCSA_SENSE

+1.5V_CPU_VDDQ

R131

220_0402_5%

1

D

2

G

Q8

RUN_ON_CPU1.5VS3#

+1.5V_CPU_VDDQ

S

3

2N7002E-T1-GE3_SOT23 -3

C199 0 .1U_0402_10V7K

C201 0 .1U_0402_10V7K

CC47 0.1U_0402_10V7K

CC48 0.1U_0402_10V7K