Page 1

A

1 1

2 2

B

C

D

E

LCFC confidential

Schematics Document

NS-A031 ODD to VGA board schematic

3 3

2012-01-08

REV:1.0

4 4

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

C

2012/07/01

2012/07/01

2012/07/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

2014/07/01

2014/07/01

2014/07/01

Title

ODD to VGA Board

ODD to VGA Board

ODD to VGA Board

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031NS-A031

NS-A031NS-A031

NS-A031NS-A031

Monday, March 18, 2013

Monday, March 18, 2013

Monday, March 18, 2013

1 16

1 16

1 16

E

1.0

1.0

1.0

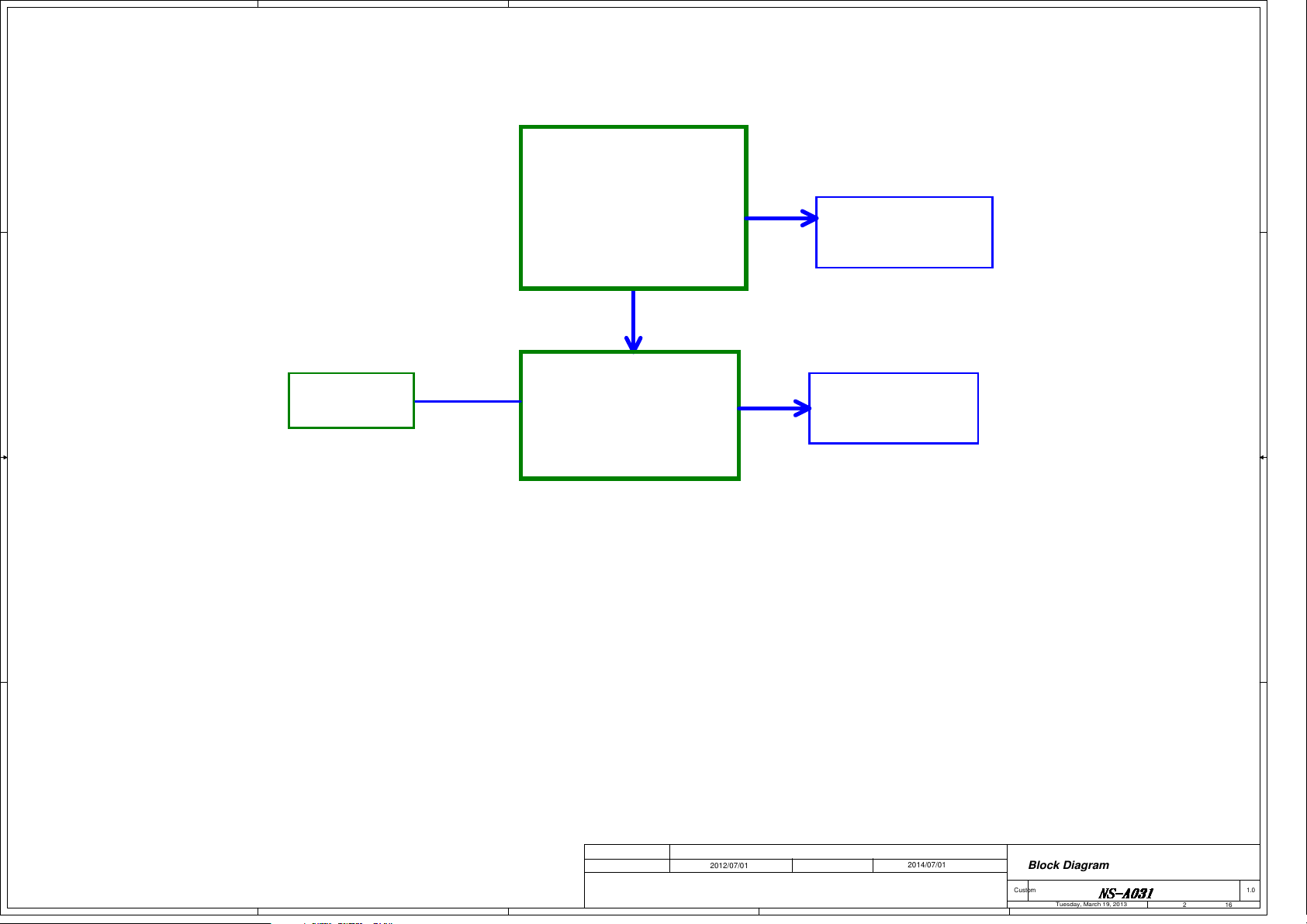

Page 2

A

1 1

B

C

D

E

SLI Connector

from NS-A031 M/B

PWM FAN Conn

Page 3

Page 3

PCI-Express 8X Gen3

2 2

PEG 8~15

2nd VGA

SPI ROM

(VBIOS 256KB)

Page 5

SPI BUS

3.3V 33MHz

N14P-GT

GB4 128 Pin

VRAM 64*32

GDDR5* 8

Page 9,10,11,12

29mm*29mm

Page 4,5,6,7,8,9,10,11,12,13

3 3

4 4

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF LC FUTURE CENTER.

C

2012/07/01

2012/07/01

2012/07/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

2014/07/01

2014/07/01

2014/07/01

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031NS-A031

NS-A031NS-A031

NS-A031NS-A031

Tuesday, March 19, 2013

Tuesday, March 19, 2013

Tuesday, March 19, 2013

2 16

2 16

E

2 16

1.0

1.0

1.0

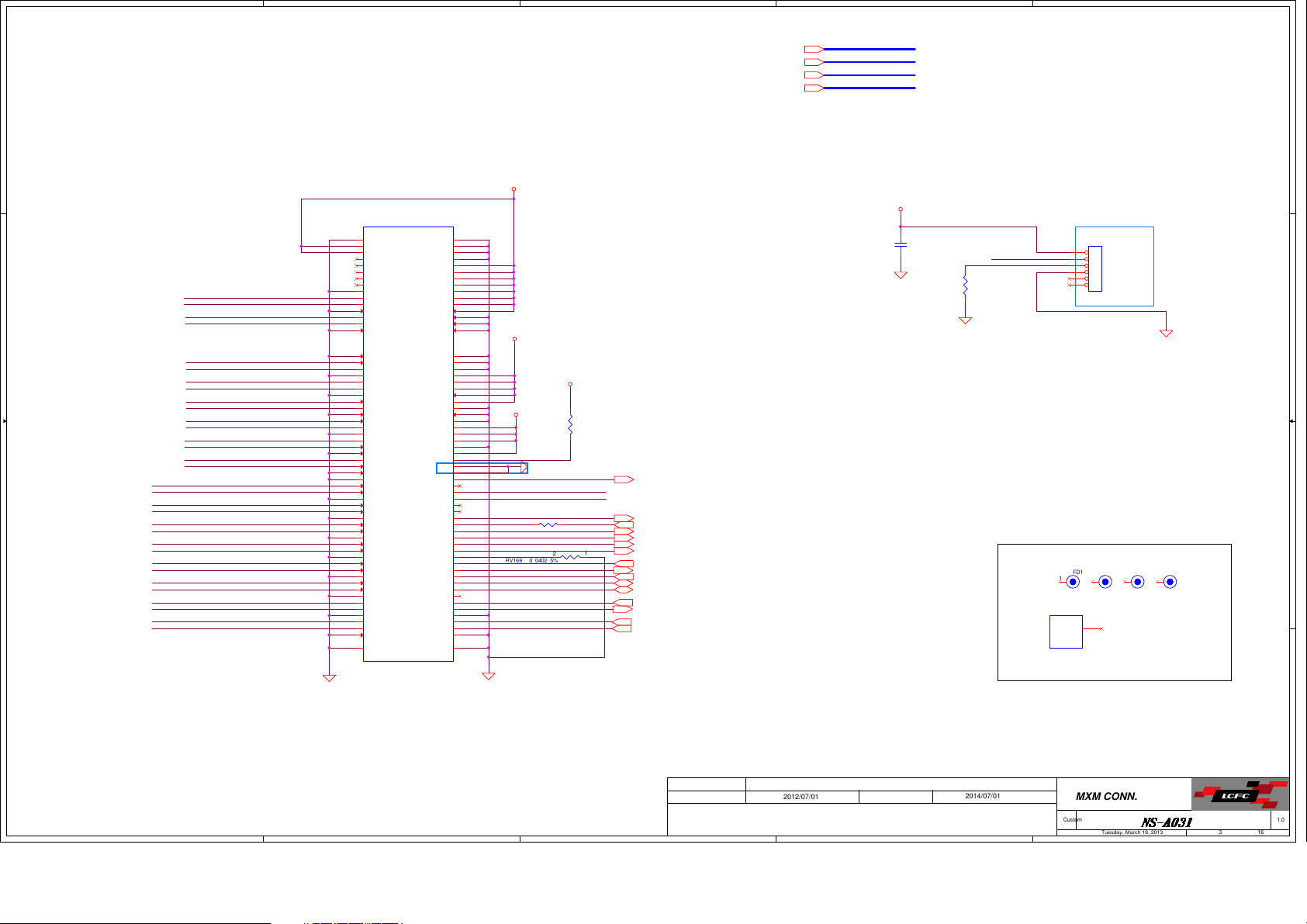

Page 3

5

4

3

2

1

4

PCIE_CTX_GRX_N[0..15]

4

PCIE_CTX_GRX_P[0..15]

4

PCIE_CRX_C_GTX_N[0..15]

4

PCIE_CRX_C_GTX_P[0..15]

D D

B+

SLI

JSLI1

1

GND

3

NC

5

NC

7

NC

9

NC

11

NC

13

NC

15

NC

17

GND

PCIE_CTX_GRX_N15

PCIE_CTX_GRX_P15

C C

B B

PCIE_CTX_GRX_N14

PCIE_CTX_GRX_P14

PCIE_CTX_GRX_N13

PCIE_CTX_GRX_P13

PCIE_CTX_GRX_N12

PCIE_CTX_GRX_P12

PCIE_CTX_GRX_N11

PCIE_CTX_GRX_P11

PCIE_CTX_GRX_N10

PCIE_CTX_GRX_P10

PCIE_CTX_GRX_N9

PCIE_CTX_GRX_P9

PCIE_CTX_GRX_N8

PCIE_CTX_GRX_P8

PCIE_CRX_C_GTX_N15

PCIE_CRX_C_GTX_P15

PCIE_CRX_C_GTX_N14

PCIE_CRX_C_GTX_P14

PCIE_CRX_C_GTX_N13

PCIE_CRX_C_GTX_P13

PCIE_CRX_C_GTX_N12

PCIE_CRX_C_GTX_P12

PCIE_CRX_C_GTX_N11

PCIE_CRX_C_GTX_P11

PCIE_CRX_C_GTX_N10

PCIE_CRX_C_GTX_P10

PCIE_CRX_C_GTX_N9

PCIE_CRX_C_GTX_P9

PCIE_CRX_C_GTX_N8

PCIE_CRX_C_GTX_P8

19

PEG_RX_N7

21

PEG_RX_P7

23

GND

25

PEG_RX_N6

27

PEG_RX_P6

29

GND

31

GND

33

PEG_RX_N5

35

PEG_RX_P5

37

GND

39

PEG_RX_N4

41

PEG_RX_P4

43

GND

45

PEG_RX_N3

47

PEG_RX_P3

49

GND

51

PEG_RX_N2

53

PEG_RX_P2

55

GND

57

PEG_RX_N1

59

PEG_RX_P1

61

GND

63

PEG_RX_N0

65

PEG_RX_P0

67

GND

69

GND

71

PEG_TX_N7

73

PEG_TX_P7

75

GND

77

PEG_TX_N6

79

PEG_TX_P6

81

GND

PEG_TX_N583PWR_GOOD

85

PEG_TX_P5

87

GND

89

PEG_TX_N4

91

PEG_TX_P4

93

GND

PEG_TX_N395TH_OVERT#

97

PEG_TX_P3

99

GND

101

PEG_TX_N2

103

PEG_TX_P2

105

GND

107

PEG_TX_N1

109

PEG_TX_P1

111

GND

113

PEG_TX_N0

115

PEG_TX_P0

117

GND

119

GND

TE_2199015-1_118P

ME@

PEX_STD_SW#

GND

GND

GND

GND

+19V

+19V

+19V

+19V

+19V

+19V

+19V

+19V

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

TH_TACH

TH_PWN

AC_DC

PWR_EN

CLK_REQ#

RSVD

RSVD

RSVD

SMB_DAT

SMB_CLK

WAKE#

RSVD

RSVD

GND

CLK_PCIE_N

CLK_PCIE_P

GND

GND

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

+5V

40

+5V

42

+5V

44

+5V

46

+5V

48

50

52

54

NC

56

+3V

58

+3V

60

62

NC

64

NC

66

NC

68

+3VS_R

NC

70

NC

72

NC

74

76

78

NC

80

82

84

86

88

90

92

94

NC

96

98

NC

100

102

104

106

108

110

112

114

116

118

120

+5VS

+3VS_VGA

DGPU_PWROK_R

SLAVE_PRESENT#

RV169 0_0402_5%

+3VS

RV172

0_0402_5%

1 2

+3VS_R

For Power Protection

SLI_FAN_SPEED

SLI_FAN_PWM

12

RV1580_0402_5%

12

SUSP#

VGA_AC_DET

DGPU_PWROK

DGPU_PWR_EN#

CLK_REQ_GPU#_R

NVDD_PWR_EN

DGPU_HOLD_RST#

PCH_THRMTRIP#_R 4

PLT_RST#

GC6_EVENT_SLI#

EC_SMB_DA2

EC_SMB_CK2

FB_CLAMP

DGPU_PWR_EN

CLK_PCIE_2VGA# 4

CLK_PCIE_2VGA 4

14

4

8,14,15

4

15

4

4

4

4

4

4,8

4

PCIE_CTX_GRX_N[0..15]

PCIE_CTX_GRX_P[0..15]

PCIE_CRX_C_GTX_N[0..15]

PCIE_CRX_C_GTX_P[0..15]

C986

10U_0805_10V6K

+5VS

FAN Conn

2

1

12

R13

1K_0402_5%

SLI_FAN_SPEED

SLI_FAN_PWM

JFAN

ME@

1

1

2

2

3

3

4

4

5

G1

6

G2

ACES_85204-04001

2012.05.31

Del Pin5,6 GND net for layout

location chang e

FD1

1

B1

43J_BARCODE_5

FD2

1

1

1

2012.06.01

Change footpri nt for ME

FD31FD4

1

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2012/07/01

2012/07/01

2012/07/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/07/01

2014/07/01

2014/07/01

Title

MXM CONN.

MXM CONN.

MXM CONN.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031NS-A031

NS-A031NS-A031

NS-A031NS-A031

Tuesday, March 19, 2013

Tuesday, March 19, 2013

Tuesday, March 19, 2013

of

3 16

3 16

1

3 16

1.0

1.0

1.0

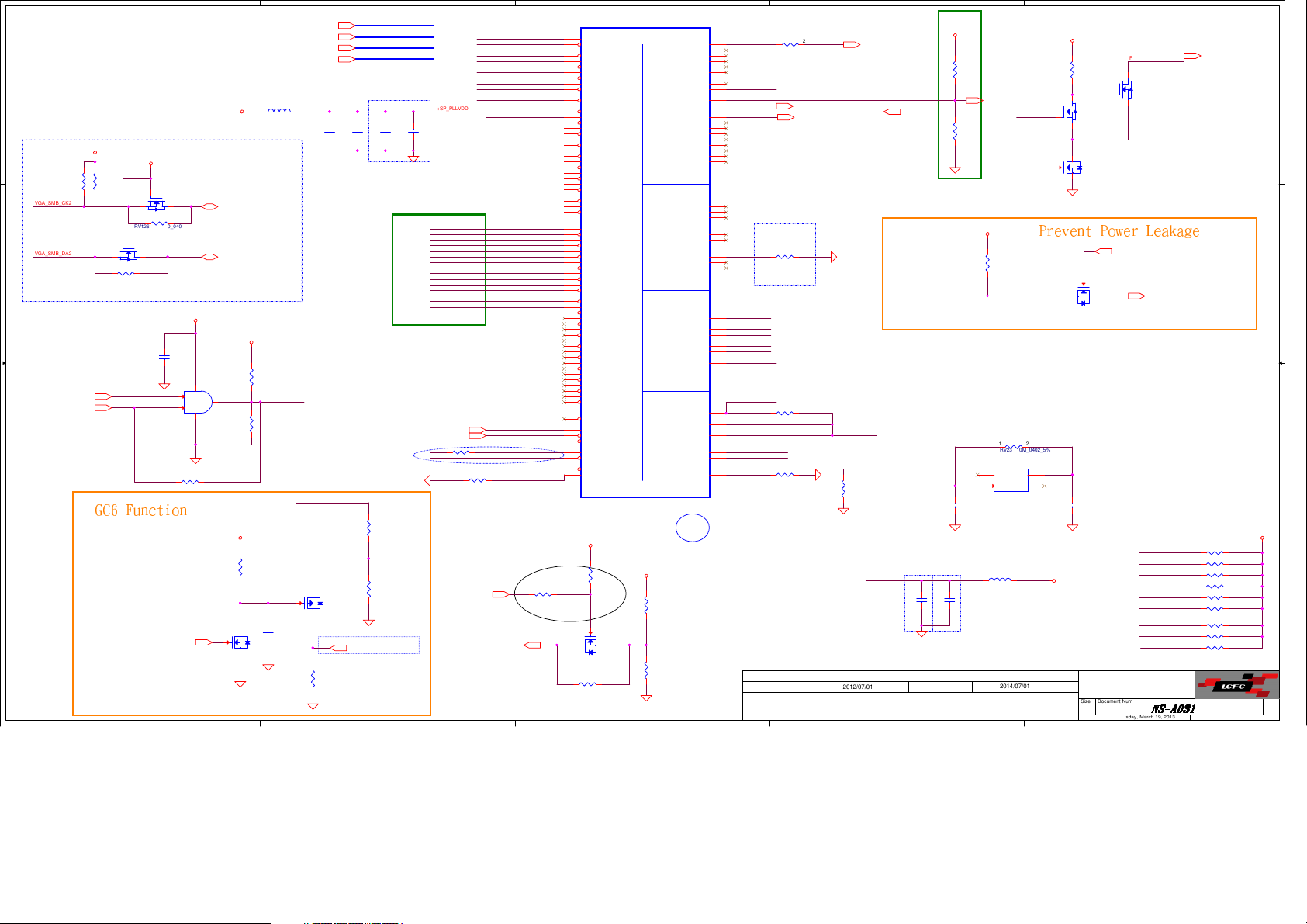

Page 4

5

3

PCIE_CTX_GRX_N[0..15]

3

PCIE_CTX_GRX_P[0..15]

3

PCIE_CRX_C_GTX_N[0..15]

3

PCIE_CRX_C_GTX_P[0..15]

D D

+3VS_VGA

RV24

2.2K_0402_5%

VGA_SMB_CK2

VGA_SMB_DA2

C C

B B

1 2

PLT_RST#3

DGPU_HOLD_RST#3

+3VS_VGA

RV25

2.2K_0402_5%

1 2

4

2N7002DW-T/R7_SOT363-6

RV126 0_0402_5%@

2

QV1A

2N7002DW-T/R7_SOT363-6

1 2

RV137 0_0402_5%@

PLT_RST#

DGPU_HOLD_RST#

5

1 2

61

NC7SZ08P5X_NL_SC70-5

+1.05VS_VGA

180ohms (ESR=0.2) Bead

QV1B

3

PU AT EC SIDE, +3VS AND 4.7K

+3VS_VGA

1

CV6

0.1U_0402_10V7K

2

RV138 0_0402_5%@

2

B

1

A

1 2

5

3

UV2

P

G

10K_0402_5%

Y

EC_SMB_CK2

EC_SMB_DA2

RV106

4

LV1 BLM18PG181SN1D_2P

1 2

+3VS_VGA

@

1 2

PLT_RST_VGA#

RV107

10K_0402_5%

1 2

Under GPU(below 150mils)

1

2

22U_0805_6.3V6M

3

3

Differential signal

FB_CLAMP_MON

GC6 Function

GC6@

RV237

GC6@

2

G

0_0402_5%

GC6@

10K_0402_5%

13

D

GC6@

QV2

S

LP2301ALT1G_SOT-23

For GC6

12

+3VS

12

RV235

10K_0402_5%

GC6@

1

13

GC6@

D

2

G

QV3

CV139

2

S

0.1U_0402_10V7K

10K_0402_5%

A A

3,4

DGPU_PWR_EN

2N7002KW_SOT323-3

5

CV112

RV238

RV236

FB_CLAMP

1

2

4.7U_0402_6.3V6M

4

PCIE_CTX_GRX_N[0..15]

PCIE_CTX_GRX_P[0..15]

PCIE_CRX_C_GTX_N[0..15]

PCIE_CRX_C_GTX_P[0..15]

150mA

1

1

CV4

CV113

CV5

2

2

0.1U_0402_10V7K

0.1U_0402_10V7K

cap location follow MXM3.0 spec

CLK_PCIE_2VGA3

CLK_PCIE_2VGA#3

1 2

12

3,4

3,4,8

4

+SP_PLLVDD

1 2

@

RV20 200_0402_1%

1 2

RV22 2.49K_0402_1%

DGPU_PWR_EN

CLK_REQ_GPU#_R

PCIE_CTX_GRX_P15

PCIE_CTX_GRX_N15

PCIE_CTX_GRX_P14

PCIE_CTX_GRX_N14

PCIE_CTX_GRX_P13

PCIE_CTX_GRX_N13

PCIE_CTX_GRX_P12

PCIE_CTX_GRX_N12

PCIE_CTX_GRX_P11

PCIE_CTX_GRX_N11

PCIE_CTX_GRX_P10

PCIE_CTX_GRX_N10

PCIE_CTX_GRX_P9

PCIE_CTX_GRX_N9

PCIE_CTX_GRX_P8

PCIE_CTX_GRX_N8

PCIE_CRX_C_GTX_P15

PCIE_CRX_C_GTX_N15

PCIE_CRX_C_GTX_P14

PCIE_CRX_C_GTX_N14

PCIE_CRX_C_GTX_P13

PCIE_CRX_C_GTX_N13

PCIE_CRX_C_GTX_P12

PCIE_CRX_C_GTX_N12

PCIE_CRX_C_GTX_P11

PCIE_CRX_C_GTX_N11

PCIE_CRX_C_GTX_P10

PCIE_CRX_C_GTX_N10

PCIE_CRX_C_GTX_P9

PCIE_CRX_C_GTX_N9

PCIE_CRX_C_GTX_P8

PCIE_CRX_C_GTX_N8

CLK_PCIE_2VGA

CLK_PCIE_2VGA#

CLK_REQ_GPU#

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT#

PLT_RST_VGA#

PEX_TERMP

RV231

10K_0402_5%

<BOM Structure>

UV1A

AN12

PEX_RX0

AM12

PEX_RX0_N

AN14

PEX_RX1

AM14

PEX_RX1_N

AP14

PEX_RX2

AP15

PEX_RX2_N

AN15

PEX_RX3

AM15

PEX_RX3_N

AN17

PEX_RX4

AM17

PEX_RX4_N

AP17

PEX_RX5

AP18

PEX_RX5_N

AN18

PEX_RX6

AM18

PEX_RX6_N

AN20

PEX_RX7

AM20

PEX_RX7_N

AP20

PEX_RX8

AP21

PEX_RX8_N

AN21

PEX_RX9

AM21

PEX_RX9_N

AN23

PEX_RX10

AM23

PEX_RX10_N

AP23

PEX_RX11

AP24

PEX_RX11_N

AN24

PEX_RX12

AM24

PEX_RX12_N

AN26

PEX_RX13

AM26

PEX_RX13_N

AP26

PEX_RX14

AP27

PEX_RX14_N

AN27

PEX_RX15

AM27

PEX_RX15_N

AK14

PEX_TX0

AJ14

PEX_TX0_N

AH14

PEX_TX1

AG14

PEX_TX1_N

AK15

PEX_TX2

AJ15

PEX_TX2_N

AL16

PEX_TX3

AK16

PEX_TX3_N

AK17

PEX_TX4

AJ17

PEX_TX4_N

AH17

PEX_TX5

AG17

PEX_TX5_N

AK18

PEX_TX6

AJ18

PEX_TX6_N

AL19

PEX_TX7

AK19

PEX_TX7_N

AK20

PEX_TX8

AJ20

PEX_TX8_N

AH20

PEX_TX9

AG20

PEX_TX9_N

AK21

PEX_TX10

AJ21

PEX_TX10_N

AL22

PEX_TX11

AK22

PEX_TX11_N

AK23

PEX_TX12

AJ23

PEX_TX12_N

AH23

PEX_TX13

AG23

PEX_TX13_N

AK24

PEX_TX14

AJ24

PEX_TX14_N

AL25

PEX_TX15

AK25

PEX_TX15_N

AJ11

PEX_WAKE_N

AL13

PEX_REFCLK

AK13

PEX_REFCLK_N

AK12

PEX_CLKREQ_N

AJ26

PEX_TSTCLK_OUT

AK26

PEX_TSTCLK_OUT_N

AJ12

PEX_RST_N

AP29

PEX_TERMP

N14P-GT-A2 FCBGA 908P

+3VS_VGA

1 2

12

2

QV16

1 3

D

2N7002H 1N_SOT23-3

@

1 2

RV233 0_0402_5%

RV230

10K_0402_5%

@

G

3

S

3

Part 1 of 7

PCI EXPRESS

GT@

+3VS_VGA

1 2

1 2

3

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

GPIO20

GPIO21

DACA_RED

DACA_GREEN

DACA_BLUE

DACA_HSYNC

DACA_VSYNC

DACs

DACA_VDD

DACA_VREF

DACA_RSET

I2CA_SCL

I2CA_SDA

I2CB_SCL

I2CB_SDA

I2CC_SCL

I2C

I2CC_SDA

I2CS_SCL

I2CS_SDA

PLLVDD

SP_PLLVDD

VID_PLLVDD

XTAL_IN

CLK

XTAL_OUT

XTAL_OUTBUFF

XTAL_SSIN

UV1

N14P-GT1-A2 FCBGA 908P

RV30

10K_0402_5%

CLK_REQ_GPU#

RV232

@

10K_0402_5%

P6

FB_CLAMP_MON

M3

L6

P5

P7

L7

M7

N8

M1

M2

L1

M5

N3

M4

N4

P2

R8

M6

R1

P3

P4

P1

AK9

AL10

AL9

AM9

AN9

AG10

AP9

AP8

R4

R5

R7

R6

R2

R3

T4

T3

AD8

AE8

AD7

H3

H2

J4

H1

Internal Thermal Sensor

GT1@

RV173 0_0402_5%

FB_CLAMP_TOGGLE_REQ#

OVERT#

ALERT#

NVVDD PWM_VID

+DACA_VDD

RV57 10K_0402_5%@

For NV request.

Change to @.

VGA_CRT_CLK

VGA_CRT_DATA

I2CB_SCL

I2CB_SDA

VGA_EDID_CLK

VGA_EDID_DATA

VGA_SMB_CK2

VGA_SMB_DA2

60mA

+PLLVDD

RV112 0_0402_5%@

45mA

45mA

XTAL_IN

XTAL_OUT

XTALOUT

XTALSSIN

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT C ONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT C ONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT C ONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENTER .

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENTER .

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENTER .

@

1 2

1 2

1 2

1 2

FB_CLAMP

NVVDD PWM_VID

DPRSLPVR_VGA

RV2610K_0402_5%

RV27

10K_0402_5%

2

FB_CLAMP

15

VGA_AC_DET

15

3,4,8

VGA_AC_DET

Vendor recommand reserve PU/PD resistor

FB_CLAMP_TOGGLE_REQ#

+SP_PLLVDD

12

+PLLVDD

1

2

0.1U_0402_10V7K

Under GPU Near GPU

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

2

Deciphered Date

Deciphered Date

Deciphered Date

2012/07/01

2012/07/01

2012/07/01

+3VS_VGA

RV65

@

10K_0402_5%

1 2

MEM_VREF

3

12

RV223

10K_0402_5%

PLT_RST_VGA#

+3VS_VGA

RV56

10K_0402_5%

GC6@

1 2

1 2

RV23 10M_0402_5%

YV1

4

NC

1

XTAL_IN

OSC

27MHZ 10PF +-10PPM 7V27000050

1

CV37

2

10P_0402_50V8J

30 ohms @100MHz (ESR=0.05)

LV7

1 2

1

22U_0805_6.3V6M

CV40

2

FBMA-10-100505-300T_2P

2014/07/01

2014/07/01

2014/07/01

CV131

+3VS_VGA

OVERT#

9,10,11,12

@

2

2

G

12

@

61

QV7A

DMN66D0LDW-7 2N_SOT363-6

13

D

@

S

RV208

10K_0402_5%

5

QV5

2N7002KW_SOT323-3

PCH_THRMTRIP#_R

3

QV7B

DMN66D0LDW-7 2N_SOT363-6

4

Prevent Power Leakage

PLT_RST_VGA#

G

2

13

D

S

GC6@

QV6

2N7002KW_SOT323-3

3

XTAL_OUT

OSC

2

NC

1

CV38

2

10P_0402_50V8J

+1.05VS_VGA

Title

Title

Title

N14P-PCIE/DAC/GPIO

N14P-PCIE/DAC/GPIO

N14P-PCIE/DAC/GPIO

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Tuesday, March 19, 2013

Tuesday, March 19, 2013

Tuesday, March 19, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

@

3,4

GC6_EVENT_SLI#

VGA_EDID_CLK

VGA_EDID_DATA

VGA_CRT_DATA

VGA_CRT_CLK

I2CB_SCL

I2CB_SDA

OVERT#

VGA_AC_DET

ALERT#

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031NS-A031

NS-A031NS-A031

NS-A031NS-A031

1

PCH_THRMTRIP#_R

3

1 2

RV3 2.2K_0402_5%

1 2

RV4 2.2K_0402_5%

1 2

RV10 2.2K_0402_5%

1 2

RV11 2.2K_0402_5%

1 2

RV12 2.2K_0402_5%

1 2

RV13 2.2K_0402_5%

1 2

RV1 10K_0402_5%

1 2

RV2 10K_0402_5%

1 2

RV7 10K_0402_5%

4 16

4 16

4 16

3

+3VS_VGA

1.0

1.0

1.0

Page 5

5

UV1D

AM6

IFPA_TXC

AN6

IFPA_TXC_ N

AP3

IFPA_TXD0

AN3

IFPA_TXD0 _N

AN5

IFPA_TXD1

AM5

IFPA_TXD1 _N

AL6

IFPA_TXD2

AK6

IFPA_TXD2 _N

AJ6

IFPA_TXD3

D D

C C

B B

A A

AH6

IFPA_TXD3 _N

AJ9

IFPB_TXC

AH9

IFPB_TXC_ N

AP6

IFPB_TXD4

AP5

IFPB_TXD4 _N

AM7

IFPB_TXD5

AL7

IFPB_TXD5 _N

AN8

IFPB_TXD6

AM8

IFPB_TXD6 _N

AK8

IFPB_TXD7

AL8

IFPB_TXD7 _N

AK1

IFPC_L0

AJ1

IFPC_L0_N

AJ3

IFPC_L1

AJ2

IFPC_L1_N

AH3

IFPC_L2

AH4

IFPC_L2_N

AG5

IFPC_L3

AG4

IFPC_L3_N

AM1

IFPD_L0

AM2

IFPD_L0_N

AM3

IFPD_L1

AM4

IFPD_L1_N

AL3

IFPD_L2

AL4

IFPD_L2_N

AK4

IFPD_L3

AK5

IFPD_L3_N

AD2

IFPE_L0

AD3

IFPE_L0_N

AD1

IFPE_L1

AC1

IFPE_L1_N

AC2

IFPE_L2

AC3

IFPE_L2_N

AC4

IFPE_L3

AC5

IFPE_L3_N

AE3

IFPF_L0

AE4

IFPF_L0_N

AF4

IFPF_L1

AF5

IFPF_L1_N

AD4

IFPF_L2

AD5

IFPF_L2_N

AG1

IFPF_L3

AF1

IFPF_L3_N

AG3

IFPC_AUX_ I2CW _SCL

AG2

IFPC_AUX_ I2CW _SDA_N

AK3

IFPD_AUX_ I2CX_SCL

AK2

IFPD_AUX_ I2CX_SDA _N

AB3

IFPE_AUX_ I2CY_SCL

AB4

IFPE_AUX_ I2CY_SDA_N

AF3

IFPF_AUX_ I2CZ_SCL

AF2

IFPF_AUX_ I2CZ_SDA _N

N14P-GT-A2_FCBGA908

4

Part 4 of 7

TEST

SERIAL

LVDS/TMDS

GENERAL

MULTI_STR AP_REF0_GND

NC

VDD_SEN SE

GND_SEN SE

TESTMOD E

JTAG_TC K

JTAG_TD I

JTAG_TD O

JTAG_TM S

JTAG_TR ST_N

ROM_CS_ N

ROM_SCL K

ROM_SI

ROM_SO

BUFRST_ N

CEC

STRAP0

STRAP1

STRAP2

STRAP3

STRAP4

THERMDP

THERMDN

P8

NC

AC6

NC

AJ28

NC

AJ4

NC

AJ5

NC

AL11

NC

C15

NC

D19

NC

D20

NC

D23

NC

D26

NC

H31

NC

T8

NC

V32

NC

L4

VCCSENSE_VGA

L5

VSSSENSE_VGA

AK11

AM10

AM11

AP12

AP11

AN11

H6

H4

H5

H7

RV35 10K_0402_5%

L2

L3

J1

J2

J7

J6

J5

J3

K3

K4

3

VCCSENSE_VGA 15

trace width: 16mils

differential voltage sensing.

differential signal routing.

TESTMODE

1 2

RV34 10K_0402_5%

ROM_CS

ROM_SCLK

ROM_SI

ROM_SO

1 2

RV38 40.2K_0402_1%

STRAP0

STRAP1

STRAP2

STRAP3

STRAP4

VSSSENSE_VGA 15

TV2

TV3

TV4

TV5

ROM_SCLK 13

ROM_SI 13

ROM_SO 13

12

STRAP0 13

STRAP1 13

STRAP2 13

STRAP3 13

STRAP4 13

12

10K_0402_5%

RV33

ROM_CS

ROM_SO

CV295

12

0.1U_0402_16V4Z

RV224 R_short 0_0402_5%

1 2

1 2

RV226 R_short 0_0402_5%

ROM_CS_R

RV229

10K_0402_5%

2

1MB SPI ROM FOR VBIOS ROM (SLI)

+3VS_VGA

20mils

12

UV15

1

CS#

2

DO

3

WP#

4

GND

MX25L2006EM1I-12G SOP 8P

8

VCC

7

HOLD#

6

CLK

5

DIO

For EMI request

Please close to UV15

ROM_HOLD#ROM_SO_R

ROM_SCLK_R

ROM_SI_R

10_0402_5%

RV51

12

RV225

10K_0402_5%

12

@

1

CV296

@

2

10P_0402_50V8J

1

RV228 R_short 0_0402_5%

1 2

1 2

RV227 R_short 0_0402_5%

ROM_SCLK

ROM_SI

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2012/07/01

2012/07/01

2012/07/01

3

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2014/07/01

2014/07/01

2014/07/01

2

Title

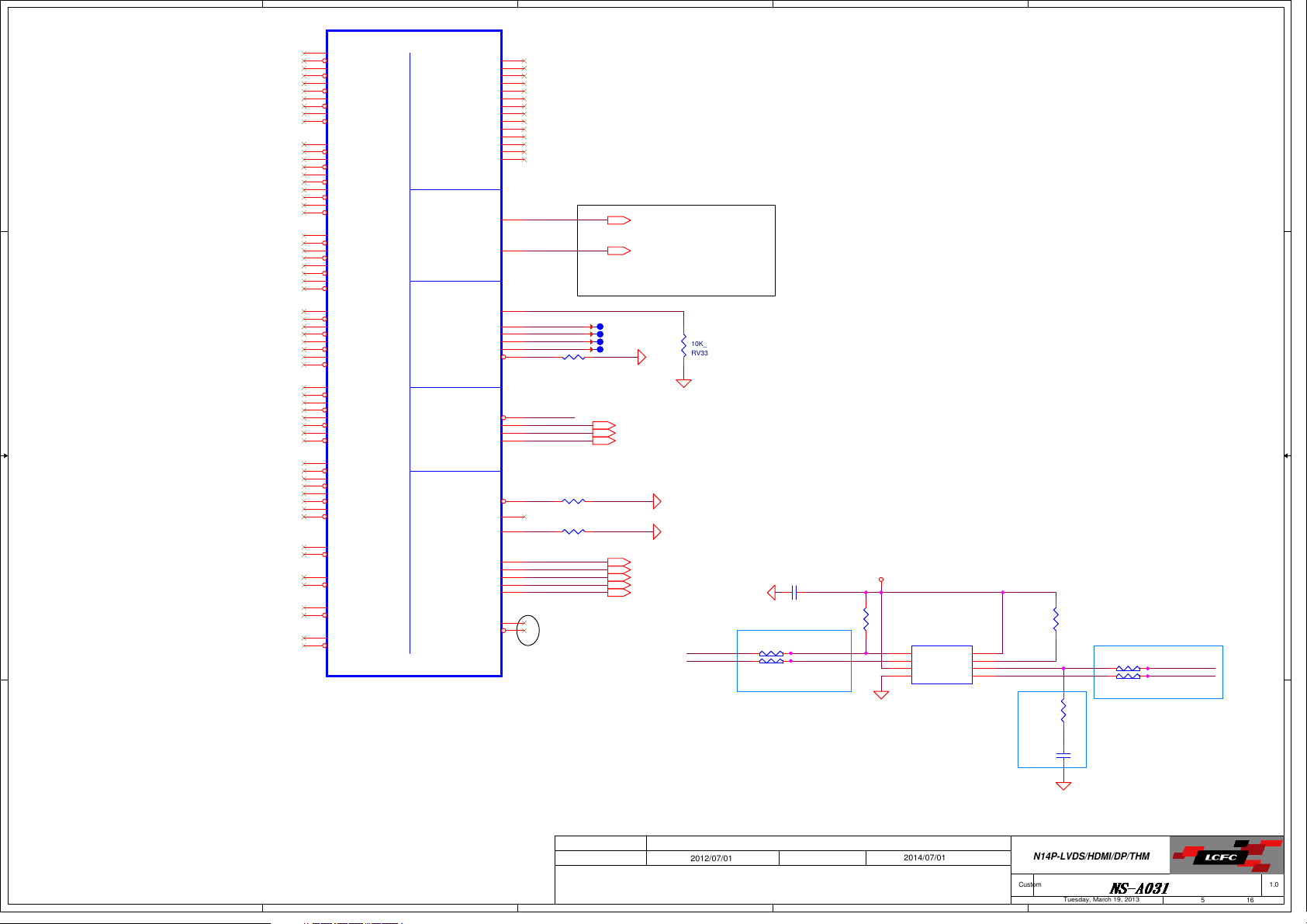

N14P-LVDS/HDMI/DP/THM

N14P-LVDS/HDMI/DP/THM

N14P-LVDS/HDMI/DP/THM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Tuesday, March 19, 2013

Tuesday, March 19, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

Tuesday, March 19, 2013

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031NS-A031

NS-A031NS-A031

NS-A031NS-A031

5 16

5 16

5 16

1

1.0

1.0

1.0

Page 6

5

4

3

2

1

+1.5VS_VGA

D D

+1.5VS_VGA

1

2

1U_0402_6.3V6K

C C

B B

For GDDR5 settin g. Near GPU

1

1

1

CV276

CV275

2

2

22U_0805_6.3V6M

1

CV274

CV273

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

2

2

CV271

CV272

1

1

10U_0603_6.3V6M

22U_0805_6.3V6M

Under GPU(below 150mils)

1

1

1

CV281

CV277

1U_0402_6.3V6K

CV282

2

2

1U_0402_6.3V6K

1

CV278

CV279

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

VDDQ_SENSE

1U_0402_6.3V6K

14

CALIBRATION PIN

FB_CAL_x_PD_VDDQ

FB_CAL_x_PU_GND

FB_CAL_xTERM_GND

CV270

1

10U_0603_6.3V6M

1

CV280

2

2

1

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CV292

2

2

0.1U_0402_10V7K

0.1U_0402_10V7K

1

2

2

CV268

CV269

GDDR5

40.2Ohm

40.2Ohm

60.4Ohm

1

1

CV267

2

4.7U_0603_6.3V6K

CV287

0.1U_0402_10V7K

RV141 R_short 0_0402_5%

1 2

RV142 R_short 0_0402_5%

1 2

1

CV266

CV265

2

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

1

CV284

CV294

2

2

0.1U_0402_10V7K

+1.5VS_VGA

1

1

CV264

CV263

2

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

0.1U_0402_10V7K

4.7U_0603_6.3V6K

1

1

CV285

CV286

2

2

0.1U_0402_10V7K

FB_VDDQ_SENSE

FB_VSS_SENSE

1 2

RV6 40.2_0402_1%

1 2

RV8 40.2_0402_1%

1 2

RV9 60.4_0402_1%

Pl

ace near balls

3.5A

AA27

AA30

AB27

AB33

AC27

AD27

AE27

AF27

AG27

M27

N27

R27

W27

W30

W33

H27

H25

UV1E

B13

B16

B19

E13

E16

E19

H10

H11

H12

H13

H14

H15

H16

H18

H19

H20

H21

H22

H23

H24

H8

H9

L27

P27

T27

T30

T33

V27

Y27

F1

F2

J27

Part 5 of 7

FBVDDQ_0

FBVDDQ_1

FBVDDQ_2

FBVDDQ_3

FBVDDQ_4

FBVDDQ_5

FBVDDQ_6

FBVDDQ_7

FBVDDQ_8

FBVDDQ_9

FBVDDQ_10

FBVDDQ_11

FBVDDQ_12

FBVDDQ_13

FBVDDQ_14

FBVDDQ_15

FBVDDQ_16

FBVDDQ_17

FBVDDQ_18

FBVDDQ_19

FBVDDQ_20

FBVDDQ_21

FBVDDQ_22

FBVDDQ_23

FBVDDQ_24

FBVDDQ_25

FBVDDQ_26

FBVDDQ_27

FBVDDQ_28

FBVDDQ_29

FBVDDQ_30

FBVDDQ_31

FBVDDQ_32

FBVDDQ_33

FBVDDQ_34

FBVDDQ_35

FBVDDQ_36

FBVDDQ_37

FBVDDQ_38

FBVDDQ_39

FBVDDQ_40

FBVDDQ_41

FBVDDQ_42

FBVDDQ_43

FB_VDDQ_SENSE

FB_GND_SENSE

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

N14P-GT-A2_FCBGA908

PEX_IOVDD_0

PEX_IOVDD_1

PEX_IOVDD_2

PEX_IOVDD_3

PEX_IOVDD_4

PEX_IOVDD_5

PEX_IOVDDQ_0

PEX_IOVDDQ_1

PEX_IOVDDQ_2

PEX_IOVDDQ_3

PEX_IOVDDQ_4

PEX_IOVDDQ_5

PEX_IOVDDQ_6

PEX_IOVDDQ_7

PEX_IOVDDQ_8

PEX_IOVDDQ_9

PEX_IOVDDQ_10

PEX_IOVDDQ_11

PEX_IOVDDQ_12

PEX_IOVDDQ_13

PEX_PLL_HVDD

PEX_SVDD_3V3

POWER

PEX_PLLVDD

IFPAB_PLLVDD

IFPC_PLLVDD

IFPD_PLLVDD

IFPEF_PLVDD

IFPAB_RSET

IFPA_IOVDD

IFPB_IOVDD

IFPC_RSET

IFPC_IOVDD

IFPD_RSET

IFPD_IOVDD

IFPEF_RSET

IFPE_IOVDD

IFPF_IOVDD

VDD33_0

VDD33_1

VDD33_2

VDD33_3

2000mA

AG19

AG21

AG22

AG24

AH21

AH25

AG13

AG15

AG16

AG18

AG25

AH15

AH18

AH26

AH27

AJ27

AK27

AL27

AM28

AN28

AH12

AG12

AG26

J8

K8

L8

M8

AH8

+IFPAB_PLLVDD

AJ8

AG8

+IFPAB_IOVDD

AG9

AF7

+IFPC_PLLVDD

AF8

AF6

+IFPC_IOVDD

AG7

+IFPD_PLLVDD

AN2

AG6

+IFPD_IOVDD

AB8

+IFPEF_PLLVDD

AD6

AC7

+IFPE_IOVDD

AC8

1

CV43

2

1U_0402_6.3V6K

1U_0402_6.3V6K

Under GPU(below 150mils)

1

CV54

2

22U_0805_6.3V6M

22U_0805_6.3V6M

+PEX_PLLVDD

+VDD33

+VDD33

@

1 2

@

1 2

RV5310K_0402_5%

@

1 2

RV4210K_0402_5%

@

1 2

RV4410K_0402_5%

@

1 2

RV4510K_0402_5%

1 2

@

RV4710K_0402_5%

@

1 2

RV5510K_0402_5%

@

1 2

RV5410K_0402_5%

1

CV44

2

1

CV53

2

+3VS_VGA_PEX

RV5210K_0402_5%

1

2

1U_0402_6.3V6K

1

2

22U_0805_6.3V6M

RV401K_0402_1%

@

RV431K_0402_1%

@

RV461K_0402_1%

@

RV501K_0402_1%

@

Near GPU

1

1

1

2

1

2

CV46

+1.05VS_VGA

CV55

1

2

4.7U_0603_6.3V6K

CV47

2

4.7U_0603_6.3V6K

1

CV74

2

4.7U_0603_6.3V6K

CV45

1U_0402_6.3V6K

CV56

22U_0805_6.3V6M

1

CV70

2

0.1U_0402_10V7K

2

CV48

CV49

2

1

10U_0603_6.3V6M

4.7U_0603_6.3V6K

0_0603_5%

12

RV14

CV73

2

1

10U_0603_6.3V6M

+3VS_VGA

2

CV51

CV50

1

10U_0603_6.3V6M

+1.05VS_VGA

2

CV52

1

10U_0603_6.3V6M

Under GPU(below 150mils)

Place near balls Place near GPU

1

1

12

12

LVDD

PL

12

12

->NV recommend: un-stuff pull down resistor by default.

2

0.1U_0402_10V7K

、、、、

IOVDD no use

+PEX_PLLVDD

CV109

0.1U_0402_10V7K

1

CV111

2

2

1U_0402_6.3V6K

120mA

1

1

CV65

2

2

1U_0603_10V6K

0.1U_0402_10V7K

0_0603_5%

1

CV75

CV293

2

4.7U_0603_6.3V6K

1

CV3

CV66

2

4.7U_0805_25V6-K

+3VS_VGA

12

RV5

+1.05VS_VGA

LV2

0_0603_5%

12

Place near balls

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2012/07/01

2012/07/01

2012/07/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2014/07/01

2014/07/01

2014/07/01

Title

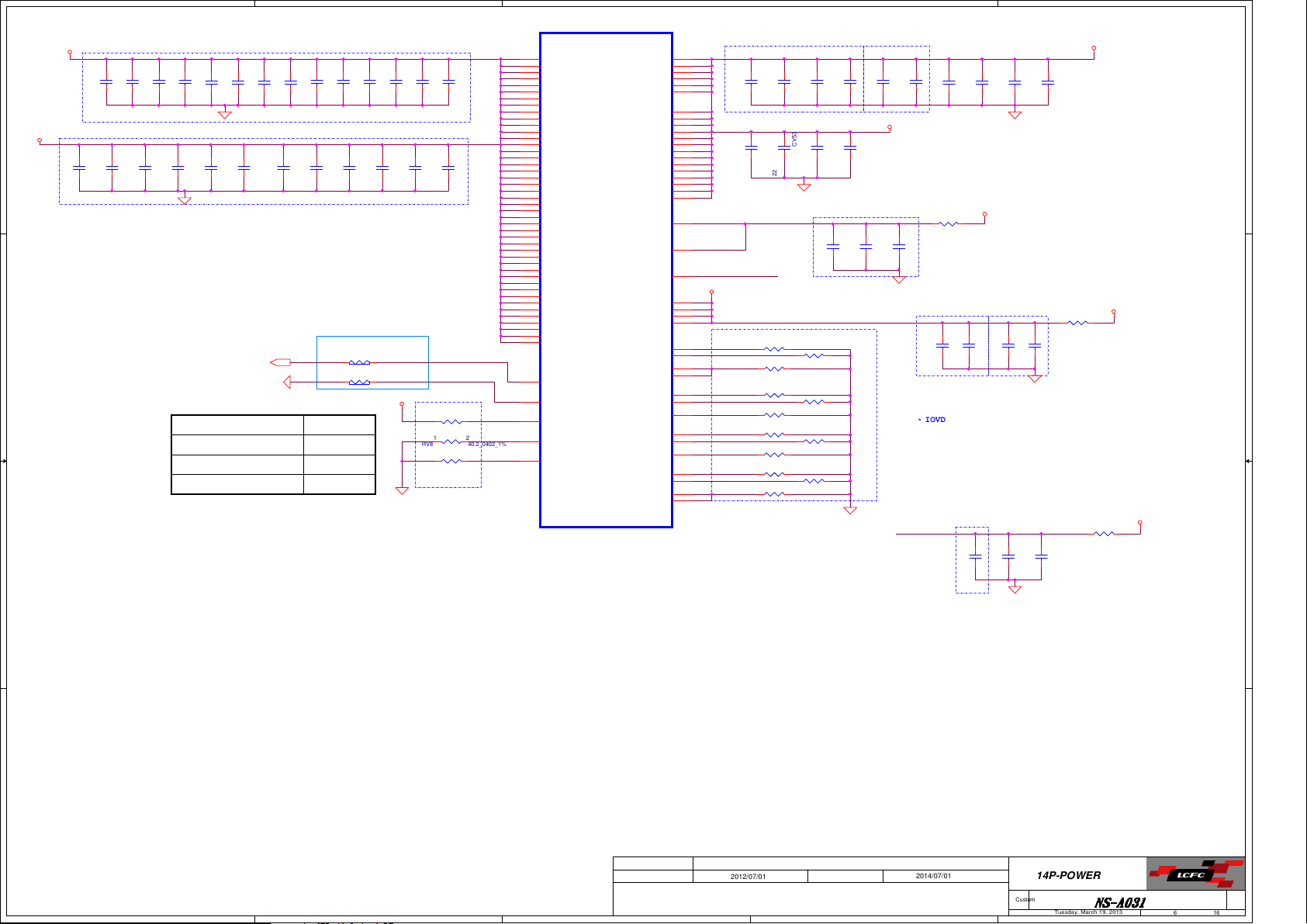

N14P-POWER

N14P-POWER

N14P-POWER

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

Date: Sheet of

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031NS-A031

NS-A031NS-A031

NS-A031NS-A031

Tuesday, March 19, 2013

Tuesday, March 19, 2013

Tuesday, March 19, 2013

of

6 16

6 16

1

6 16

1.0

1.0

1.0

Page 7

5

A2

AA17

AA18

AA20

AA22

AB12

AB14

AB16

D D

C C

B B

A A

5

AB19

AB21

AB23

AB28

AB30

AB32

AC13

AC15

AC17

AC18

AA13

AC20

AC22

AE28

AE30

AE32

AE33

AH10

AA15

AH13

AH16

AH19

AH22

AH24

AH28

AH29

AH30

AH32

AH33

AK10

AL12

AL14

AL15

AL17

AL18

AL20

AL21

AL23

AL24

AL26

AL28

AL30

AL32

AL33

AM13

AM16

AM19

AM22

AM25

AN10

AN13

AN16

AN19

AN22

AN25

AN30

AN34

AP33

AB2

A33

AB5

AB7

AE2

AE5

AE7

AH2

AH5

AH7

AJ7

AK7

AL2

AL5

AN1

AN4

AN7

AP2

B1

B10

B22

B25

B28

B31

B34

B4

B7

C10

C13

C19

C22

C25

C28

C7

4

UV1F

N14P-GT-A2_FCBGA908

GND_0

GND_1

GND_2

GND_3

GND_4

GND_5

GND_6

GND_7

GND_8

GND_9

GND_10

GND_11

GND_12

GND_13

GND_14

GND_15

GND_16

GND_17

GND_18

GND_19

GND_20

GND_21

GND_22

GND_23

GND_24

GND_25

GND_26

GND_27

GND_28

GND_29

GND_30

GND_31

GND_32

GND_33

GND_34

GND_35

GND_36

GND_37

GND_38

GND_39

GND_40

GND_41

GND_42

GND_43

GND_44

GND_45

GND_46

GND_47

GND_48

GND_49

GND_50

GND_51

GND_52

GND_53

GND_54

GND_55

GND_56

GND_57

GND_58

GND_59

GND_60

GND_61

GND_62

GND_63

GND_64

GND_65

GND_66

GND_67

GND_68

GND_69

GND_70

GND_71

GND_72

GND_73

GND_74

GND_75

GND_76

GND_77

GND_78

GND_79

GND_80

GND_81

GND_82

GND_83

GND_84

GND_85

GND_86

GND_87

GND_88

GND_89

GND_90

GND_91

GND_92

GND_93

GND_94

GND_95

GND_96

GND_97

GND_98

GND_99

Part 6 of 7

4

GND

GND_100

GND_101

GND_102

GND_103

GND_104

GND_105

GND_106

GND_107

GND_108

GND_109

GND_110

GND_111

GND_112

GND_113

GND_114

GND_115

GND_116

GND_117

GND_118

GND_119

GND_120

GND_121

GND_122

GND_123

GND_124

GND_125

GND_126

GND_127

GND_128

GND_129

GND_130

GND_131

GND_132

GND_133

GND_134

GND_135

GND_136

GND_137

GND_138

GND_139

GND_140

GND_141

GND_142

GND_143

GND_144

GND_145

GND_146

GND_147

GND_148

GND_149

GND_150

GND_151

GND_152

GND_153

GND_154

GND_155

GND_156

GND_157

GND_158

GND_159

GND_160

GND_161

GND_162

GND_163

GND_164

GND_165

GND_166

GND_167

GND_168

GND_169

GND_170

GND_171

GND_172

GND_173

GND_174

GND_175

GND_176

GND_177

GND_178

GND_179

GND_180

GND_181

GND_182

GND_183

GND_184

GND_185

GND_186

GND_187

GND_188

GND_189

GND_190

GND_191

GND_192

GND_193

GND_194

GND_195

GND_196

GND_197

GND_198

GND_199

GND_OPT

GND_OPT

D2

D31

D33

E10

E22

E25

E5

E7

F28

F7

G10

G13

G16

G19

G2

G22

G25

G28

G3

G30

G32

G33

G5

G7

K2

K28

K30

K32

K33

K5

K7

M13

M15

M17

M18

M20

M22

N12

N14

N16

N19

N2

N21

N23

N28

N30

N32

N33

N5

N7

P13

P15

P17

P18

P20

P22

R12

R14

R16

R19

R21

R23

T13

T15

T17

T18

T2

T20

T22

AG11

T28

T32

T5

T7

U12

U14

U16

U19

U21

U23

V12

V14

V16

V19

V21

V23

W13

W15

W17

W18

W20

W22

W28

Y12

Y14

Y16

Y19

Y21

Y23

AH11

C16

W32

3

+VGA_CORE

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

UV1G

AA12

VDD_0

AA14

VDD_1

AA16

VDD_2

AA19

VDD_3

AA21

VDD_4

AA23

VDD_5

AB13

VDD_6

AB15

VDD_7

AB17

VDD_8

AB18

VDD_9

AB20

VDD_10

AB22

VDD_11

AC12

VDD_12

AC14

VDD_13

AC16

VDD_14

AC19

VDD_15

AC21

VDD_16

AC23

VDD_17

M12

VDD_18

M14

VDD_19

M16

VDD_20

M19

VDD_21

M21

VDD_22

M23

VDD_23

N13

VDD_24

N15

VDD_25

N17

VDD_26

N18

VDD_27

N20

VDD_28

N22

VDD_29

P12

VDD_30

P14

VDD_31

P16

VDD_32

P19

VDD_33

P21

VDD_34

P23

VDD_35

R13

VDD_36

R15

VDD_37

R17

VDD_38

R18

VDD_39

R20

VDD_40

R22

VDD_41

T12

VDD_42

T14

VDD_43

T16

VDD_44

T19

VDD_45

T21

VDD_46

T23

VDD_47

U13

VDD_48

U15

VDD_49

U17

VDD_50

U18

VDD_51

U20

VDD_52

U22

VDD_53

V13

VDD_54

V15

VDD_55

N14P-GT-A2_FCBGA908

2012/07/01

2012/07/01

2012/07/01

Part 7 of 7

POWER

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

VDD_56

VDD_57

VDD_58

VDD_59

VDD_60

VDD_61

VDD_62

VDD_63

VDD_64

VDD_65

VDD_66

VDD_67

VDD_68

VDD_69

VDD_70

VDD_71

XVDD_1

XVDD_2

XVDD_3

XVDD_4

XVDD_5

XVDD_6

XVDD_7

XVDD_8

XVDD_9

XVDD_10

XVDD_11

XVDD_12

XVDD_13

XVDD_14

XVDD_15

XVDD_16

XVDD_17

XVDD_18

XVDD_19

XVDD_20

XVDD_21

XVDD_22

XVDD_23

XVDD_24

XVDD_25

XVDD_26

XVDD_27

XVDD_28

XVDD_29

XVDD_30

XVDD_31

XVDD_32

XVDD_33

XVDD_34

XVDD_35

XVDD_36

XVDD_37

XVDD_38

2

+VGA_CORE

V17

V18

V20

V22

W12

W14

W16

W19

W21

W23

Y13

Y15

Y17

Y18

Y20

Y22

U1

U2

U3

U4

U5

U6

U7

U8

V1

V2

V3

V4

V5

V6

V7

V8

W2

W3

W4

W5

W7

W8

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

AA1

AA2

AA3

AA4

AA5

AA6

AA7

AA8

2014/07/01

2014/07/01

2014/07/01

2

1

Title

Title

Title

N14P-VGA CORE, GND

N14P-VGA CORE, GND

N14P-VGA CORE, GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

Date: Sheet of

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031NS-A031

NS-A031NS-A031

NS-A031NS-A031

Tuesday, March 19, 2013

Tuesday, March 19, 2013

Tuesday, March 19, 2013

of

7 16

7 16

1

7 16

1.0

1.0

1.0

Page 8

5

FBA_D[0..63]

FBA_DBI0#

FBA_DBI1#

FBA_DBI2#

FBA_DBI3#

FBA_DBI4#

FBA_DBI5#

FBA_DBI6#

FBA_DBI7#

9

10

DV4

DAN202UT106_SC70-3

2

1

3

GC6@

1 2

NOGC6@

9,10

UV1B

L28

FBA_D0

FBA_D1

FBA_D2

FBA_D3

FBA_D4

FBA_D5

FBA_D6

FBA_D7

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_D16

FBA_D17

FBA_D18

FBA_D19

FBA_D20

FBA_D21

FBA_D22

FBA_D23

FBA_D24

FBA_D25

FBA_D26

FBA_D27

FBA_D28

FBA_D29

FBA_D30

FBA_D31

FBA_D32

FBA_D33

FBA_D34

FBA_D35

FBA_D36

FBA_D37

FBA_D38

FBA_D39

FBA_D40

FBA_D41

FBA_D42

FBA_D43

FBA_D44

FBA_D45

FBA_D46

FBA_D47

FBA_D48

FBA_D49

FBA_D50

FBA_D51

FBA_D52

FBA_D53

FBA_D54

FBA_D55

FBA_D56

FBA_D57

FBA_D58

FBA_D59

FBA_D60

FBA_D61

FBA_D62

FBA_D63

FBA_DBI0#

FBA_DBI1#

FBA_DBI2#

FBA_DBI3#

FBA_DBI4#

FBA_DBI5#

FBA_DBI6#

FBA_DBI7#

FBA_EDC0

FBA_EDC1

FBA_EDC2

FBA_EDC3

FBA_EDC4

FBA_EDC5

FBA_EDC6

FBA_EDC7

12

RV32

200K_0402_5%

GC6@

M29

L29

M28

N31

P29

R29

P28

J28

H29

J29

H28

G29

E31

E32

F30

C34

D32

B33

C33

F33

F32

H33

H32

P34

P32

P31

P33

L31

L34

L32

L33

AG28

AF29

AG29

AF28

AD30

AD29

AC29

AD28

AJ29

AK29

AJ30

AK28

AM29

AM31

AN29

AM30

AN31

AN32

AP30

AP32

AM33

AL31

AK33

AK32

AD34

AD32

AC30

AD33

AF31

AG34

AG32

AG33

P30

F31

F34

M32

AD31

AL29

AM32

AF34

M31

G31

E33

M33

AE31

AK30

AN33

AF33

M30

H30

E34

M34

AF30

AK31

AM34

AF32

FBVDDQ_PWR_EN

FBA_D0

FBA_D1

FBA_D2

FBA_D3

FBA_D4

FBA_D5

FBA_D6

FBA_D7

FBA_D8

FBA_D9

FBA_D10

FBA_D11

FBA_D12

FBA_D13

FBA_D14

FBA_D15

FBA_D16

FBA_D17

FBA_D18

FBA_D19

FBA_D20

FBA_D21

FBA_D22

FBA_D23

FBA_D24

FBA_D25

FBA_D26

FBA_D27

FBA_D28

FBA_D29

FBA_D30

FBA_D31

FBA_D32

FBA_D33

FBA_D34

FBA_D35

FBA_D36

FBA_D37

FBA_D38

FBA_D39

FBA_D40

FBA_D41

FBA_D42

FBA_D43

FBA_D44

FBA_D45

FBA_D46

FBA_D47

FBA_D48

FBA_D49

FBA_D50

FBA_D51

FBA_D52

FBA_D53

FBA_D54

FBA_D55

FBA_D56

FBA_D57

FBA_D58

FBA_D59

FBA_D60

FBA_D61

FBA_D62

FBA_D63

9

FBA_DQM0

9

FBA_DQM1

9

FBA_DQM2

9

FBA_DQM3

10

FBA_DQM4

10

FBA_DQM5

10

FBA_DQM6

10

FBA_DQM7

FBA_DQS_WP0

FBA_DQS_WP1

FBA_DQS_WP2

FBA_DQS_WP3

FBA_DQS_WP4

FBA_DQS_WP5

FBA_DQS_WP6

FBA_DQS_WP7

FBA_DQS_RN0

FBA_DQS_RN1

FBA_DQS_RN2

FBA_DQS_RN3

FBA_DQS_RN4

FBA_DQS_RN5

FBA_DQS_RN6

FBA_DQS_RN7

N14P-GT-A2_FCBGA908

FBA_D[0..63]

30ohms (ESR=0.01) Bead

P/N;SM010007W00

+1.05VS_VGA +FB_PLLAVDD

D D

C C

B B

200mA

FBMA-L11-160808300LMA25T_2P

1 2

Place close to BGA

+FB_PLLAVDD

LV3

FBA_EDC[3..0]

FBA_EDC[7..4]

For N14P-GT not support GC6

A A

3,4

3,14,15

FB_CLAMP

DGPU_PWROK

FB_CLAMP

RV157 0_0402_5%

5

4

Part 2 of 7

FBA_CMD_RFU0

FBA_CMD_RFU1

MEMORY INTERFACE

A

FBA_WCKB01_N

FBA_WCKB23_N

FBA_WCKB45_N

FBA_WCKB67_N

14

4

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CMD31

FBA_DEBUG0

FBA_DEBUG1

FBA_CLK0

FBA_CLK0_N

FBA_CLK1

FBA_CLK1_N

FBA_WCK01

FBA_WCK01_N

FBA_WCK23

FBA_WCK23_N

FBA_WCK45

FBA_WCK45_N

FBA_WCK67

FBA_WCK67_N

FBA_WCKB01

FBA_WCKB23

FBA_WCKB45

FBA_WCKB67

FB_CLAMP

FB_DLL_AVDD

FBA_PLL_AVDD

FB_VREF

U30

FBA_CS#_L

T31

FBA_MA3_BA3_L

U29

FBA_MA2_BA0_L

R34

FBA_MA4_BA2_L

R33

FBA_MA5_BA1_L

U32

FBA_WE#_L

U33

FBA_MA7_MA8_L

U28

FBA_MA6_MA11_L

V28

FBA_ABI#_L

V29

FBA_MA12_RFU_L

V30

FBA_MA0_MA10_L

U34

FBA_MA1_MA9_L

U31

FBA_RAS#_L

V34

FBA_RST#_L

V33

FBA_CKE_L

Y32

FBA_CAS#_L

AA31

FBA_CS#_H

AA29

FBA_MA3_BA3_H

AA28

FBA_MA2_BA0_H

AC34

FBA_MA4_BA2_H

AC33

FBA_MA5_BA1_H

AA32

FBA_WE#_H

AA33

FBA_MA7_MA8_H

Y28

FBA_MA6_MA11_H

Y29

FBA_ABI#_H

W31

FBA_MA12_RFU_H

Y30

FBA_MA0_MA10_H

AA34

FBA_MA1_MA9_H

Y31

FBA_RAS#_H

Y34

FBA_RST#_H

Y33

FBA_CKE_H

V31

FBA_CAS#_H

R32

AC32

R28

1 2

AC28

1 2

R30

FBA_CLK0

R31

FBA_CLK0#

AB31

FBA_CLK1

AC31

FBA_CLK1#

K31

FBA_WCK0

L30

FBA_WCK0_N

H34

FBA_WCK1

J34

FBA_WCK1_N

AG30

FBA_WCK2

AG31

FBA_WCK2_N

AJ34

FBA_WCK3

AK34

FBA_WCK3_N

J30

J31

J32

J33

AH31

AJ31

FB_CLAMP

AJ32

AJ33

RV66 10K_0402_5%NOGC6@

E1

CV106 0.1U_0402_10V7K

K27

1 2

Place close to ball

U27

H26

Pl

ace close to ball Plac e close to BGA

FBA_CS#_L

FBA_MA3_BA3_L

FBA_MA2_BA0_L

FBA_MA4_BA2_L

FBA_MA5_BA1_L

FBA_WE#_L

FBA_MA7_MA8_L

FBA_MA6_MA11_L

FBA_ABI#_L

FBA_MA12_RFU_L

FBA_MA0_MA10_L

FBA_MA1_MA9_L

FBA_RAS#_L

FBA_RST#_L

FBA_CAS#_L

FBA_CS#_H

FBA_MA3_BA3_H

FBA_MA2_BA0_H

FBA_MA4_BA2_H

FBA_MA5_BA1_H

FBA_WE#_H

FBA_MA7_MA8_H

FBA_MA6_MA11_H

FBA_ABI#_H

FBA_MA12_RFU_H

FBA_MA0_MA10_H

FBA_MA1_MA9_H

FBA_RAS#_H

FBA_RST#_H

FBA_CAS#_H

@

RV5860.4_0402_1%

+1.5VS_VGA

RV5960.4_0402_1%

@

FBA_WCK0

FBA_WCK0_N

FBA_WCK1

FBA_WCK1_N

FBA_WCK2

FBA_WCK2_N

FBA_WCK3

FBA_WCK3_N

+FB_PLLAVDD

1

CV110

2

1U_0402_6.3V6K

9

9

10

10

1

2

22U_0805_6.3V6M

FBA_CLK0

FBA_CLK0#

FBA_CLK1

FBA_CLK1#

12

1

CV107

2

0.1U_0402_10V7K

+FB_PLLAVDD

CV39

FBC_D[0..63]

9

9

9

9

9

+1.5VS_VGA

9

9

9

9

9

9

9

9

9

9

10

10

10

10

10

+1.5VS_VGA

10

10

10

10

10

10

10

10

10

10

9

9

9

9

10

10

10

10

12

RV209

10K_0402_5%

12

RV221

10K_0402_5%

FBC_EDC[3..0]

FBC_EDC[7..4]

3

FBA_CKE_L

FBA_CKE_H

FBC_DBI0#

FBC_DBI1#

FBC_DBI2#

FBC_DBI3#

FBC_DBI4#

FBC_DBI5#

FBC_DBI6#

FBC_DBI7#

FBA_RST#_L

FBA_RST#_H

3

FBC_D[0..63]

FBC_D0

FBC_D1

FBC_D2

FBC_D3

FBC_D4

FBC_D5

FBC_D6

FBC_D7

FBC_D8

FBC_D9

FBC_D10

FBC_D11

FBC_D12

FBC_D13

9

FBC_D14

FBC_D15

FBC_D16

FBC_D17

FBC_D18

FBC_D19

FBC_D20

FBC_D21

FBC_D22

FBC_D23

FBC_D24

FBC_D25

FBC_D26

FBC_D27

FBC_D28

FBC_D29

10

FBC_D30

FBC_D31

FBC_D32

FBC_D33

FBC_D34

FBC_D35

FBC_D36

FBC_D37

FBC_D38

FBC_D39

FBC_D40

FBC_D41

FBC_D42

FBC_D43

FBC_D44

FBC_D45

FBC_D46

FBC_D47

FBC_D48

FBC_D49

FBC_D50

FBC_D51

FBC_D52

FBC_D53

FBC_D54

FBC_D55

FBC_D56

FBC_D57

FBC_D58

FBC_D59

FBC_D60

FBC_D61

FBC_D62

FBC_D63

FBC_DBI0#

FBC_DBI1#

FBC_DBI2#

FBC_DBI3#

FBC_DBI4#

FBC_DBI5#

FBC_DBI6#

FBC_DBI7#

FBC_EDC0

FBC_EDC1

FBC_EDC2

FBC_EDC3

FBC_EDC4

FBC_EDC5

FBC_EDC6

FBC_EDC7

12

RV71

10K_0402_5%

2

11,12

UV1C

Part 3 of 7

FBB_D0

FBB_D1

FBB_D2

FBB_D3

FBB_D4

FBB_D5

FBB_D6

FBB_D7

FBB_D8

FBB_D9

FBB_D10

FBB_D11

FBB_D12

FBB_D13

FBB_D14

FBB_D15

FBB_D16

FBB_D17

FBB_D18

FBB_D19

FBB_D20

FBB_D21

FBB_D22

FBB_D23

FBB_D24

FBB_D25

FBB_D26

FBB_D27

FBB_D28

FBB_D29

FBB_D30

FBB_D31

FBB_D32

FBB_D33

FBB_D34

FBB_D35

FBB_D36

FBB_D37

FBB_D38

FBB_D39

FBB_D40

FBB_D41

FBB_D42

FBB_D43

FBB_D44

FBB_D45

FBB_D46

FBB_D47

FBB_D48

FBB_D49

FBB_D50

FBB_D51

FBB_D52

FBB_D53

FBB_D54

FBB_D55

FBB_D56

FBB_D57

FBB_D58

FBB_D59

FBB_D60

FBB_D61

FBB_D62

FBB_D63

11

FBB_DQM0

11

FBB_DQM1

11

FBB_DQM2

11

FBB_DQM3

12

FBB_DQM4

12

FBB_DQM5

12

FBB_DQM6

12

FBB_DQM7

FBB_DQS_WP0

FBB_DQS_WP1

FBB_DQS_WP2

FBB_DQS_WP3

FBB_DQS_WP4

FBB_DQS_WP5

FBB_DQS_WP6

FBB_DQS_WP7

FBB_DQS_RN0

FBB_DQS_RN1

FBB_DQS_RN2

FBB_DQS_RN3

FBB_DQS_RN4

FBB_DQS_RN5

FBB_DQS_RN6

FBB_DQS_RN7

N14P-GT-A2_FCBGA908

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF LC FU TURE CENTER. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT C ONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT C ONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT C ONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENTER .

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENTER .

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF LC FUTURE CENTER .

FBB_CMD_RFU0

FBB_CMD_RFU1

MEMORY INTERFACE B

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD28

FBB_CMD29

FBB_CMD30

FBB_CMD31

FBB_DEBUG0

FBB_DEBUG1

FBB_CLK0

FBB_CLK0_N

FBB_CLK1

FBB_CLK1_N

FBB_WCK01

FBB_WCK01_N

FBB_WCK23

FBB_WCK23_N

FBB_WCK45

FBB_WCK45_N

FBB_WCK67

FBB_WCK67_N

FBB_WCKB01

FBB_WCKB01_N

FBB_WCKB23

FBB_WCKB23_N

FBB_WCKB45

FBB_WCKB45_N

FBB_WCKB67

FBB_WCKB67_N

FBB_PLL_AVDD

2012/07/01

2012/07/01

2012/07/01

D13

FBC_CS#_L

E14

FBC_MA3_BA3_L

F14

FBC_MA2_BA0_L

A12

FBC_MA4_BA2_L

B12

FBC_MA5_BA1_L

C14

FBC_WE#_L

B14

FBC_MA7_MA8_L

G15

FBC_MA6_MA11_L

F15

FBC_ABI#_L

E15

FBC_MA12_RFU_L

D15

FBC_MA0_MA10_L

A14

FBC_MA1_MA9_L

D14

FBC_RAS#_L

A15

FBC_RST#_L

B15

FBC_CKE_L

C17

FBC_CAS#_L

D18

FBC_CS#_H

E18

FBC_MA3_BA3_H

F18

FBC_MA2_BA0_H

A20

FBC_MA4_BA2_H

B20

FBC_MA5_BA1_H

C18

FBC_WE#_H

B18

FBC_MA7_MA8_H

G18

FBC_MA6_MA11_H

G17

FBC_ABI#_H

F17

FBC_MA12_RFU_H

D16

FBC_MA0_MA10_H

A18

FBC_MA1_MA9_H

D17

FBC_RAS#_H

A17

FBC_RST#_H

B17

FBC_CKE_H

E17

FBC_CAS#_H

C12

C20

G14

G20

D12

E12

E20

F20

F8

E8

A5

A6

D24

D25

B27

C27

D6

D7

C6

B6

F26

E26

A26

A27

H17

@

1 2

1 2

@

FBC_CLK0

FBC_CLK0#

FBC_CLK1

FBC_CLK1#

FBC_WCK0

FBC_WCK0_N

FBC_WCK1

FBC_WCK1_N

FBC_WCK2

FBC_WCK2_N

FBC_WCK3

FBC_WCK3_N

1

CV108

2

0.1U_0402_10V7K

Place close to ball

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

RV6060.4_0402_1%

RV6160.4_0402_1%

FBC_CLK0

FBC_CLK0#

FBC_CLK1

FBC_CLK1#

+FB_PLLAVDD

FBC_CS#_L

FBC_MA3_BA3_L

FBC_MA2_BA0_L

FBC_MA4_BA2_L

FBC_MA5_BA1_L

FBC_WE#_L

FBC_MA7_MA8_L

FBC_MA6_MA11_L

FBC_ABI#_L

FBC_MA12_RFU_L

FBC_MA0_MA10_L

FBC_MA1_MA9_L

FBC_RAS#_L

FBC_RST#_L

FBC_CAS#_L

FBC_CS#_H

FBC_MA3_BA3_H

FBC_MA2_BA0_H

FBC_MA4_BA2_H

FBC_MA5_BA1_H

FBC_WE#_H

FBC_MA7_MA8_H

FBC_MA6_MA11_H

FBC_ABI#_H

FBC_MA12_RFU_H

FBC_MA0_MA10_H

FBC_MA1_MA9_H

FBC_RAS#_H

FBC_RST#_H

FBC_CAS#_H

+1.5VS_VGA

11

11

12

12

FBC_WCK0

FBC_WCK0_N

FBC_WCK1

FBC_WCK1_N

FBC_WCK2

FBC_WCK2_N

FBC_WCK3

FBC_WCK3_N

FBC_RST#_L

FBC_RST#_H

2014/07/01

2014/07/01

2014/07/01

F11

G11

F12

G12

A11

C11

D11

B11

F24

G23

E24

G24

D21

E21

G21

F21

G27

D27

G26

E27

E29

F29

E30

D30

A32

C31

C32

B32

D29

A29

C29

B29

B21

C23

A21

C21

B24

C24

B26

C26

E11

F23

F27

C30

A24

D10

E23

E28

B30

A23

11

12

D22

D28

A30

B23

12

RV72

10K_0402_5%

G9

E9

G8

F9

G6

F5

E6

F6

F4

G4

E2

F3

C2

D4

D3

C1

B3

C4

B5

C5

D8

A8

C8

B8

E3

A3

C9

D5

C3

B9

D9

E4

B2

A9

PU for X16 modePU for X16 mode

11

11

11

11

11

11

11

11

11

11

11

11

11

11

11

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

11

11

11

11

12

12

12

12

+1.5VS_VGA

12

RV210

10K_0402_5%

+1.5VS_VGA

12

RV222

10K_0402_5%

12

1

GDDR5

Mode H - Mirror Mode Mapping

Address

FBx_CMD0

FBx_CMD1

FBC_CKE_L

FBC_CKE_H

RV74

10K_0402_5%

11

FBx_CMD2

FBx_CMD3

FBx_CMD4

FBx_CMD5

FBx_CMD6

FBx_CMD7

FBx_CMD8

FBx_CMD9

12

FBx_CMD10

FBx_CMD11

FBx_CMD12

FBx_CMD13

FBx_CMD14

FBx_CMD15

FBx_CMD16

FBx_CMD17

FBx_CMD18

FBx_CMD19

FBx_CMD20

FBx_CMD21

FBx_CMD22

FBx_CMD23

FBx_CMD24

FBx_CMD25

FBx_CMD26

FBx_CMD27

FBx_CMD28

FBx_CMD29

FBx_CMD30

FBx_CMD31

12

RV73

10K_0402_5%

Title

Title

Title

N14P-MEM Interface

N14P-MEM Interface

N14P-MEM Interface

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Tuesday, March 19, 2013

Tuesday, March 19, 2013

Tuesday, March 19, 2013

Date: Sheet of

Date: Sheet of

Date: Sheet of

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031

NS-A031NS-A031

NS-A031NS-A031

NS-A031NS-A031

1

CS#

A3_BA3

A2_BA0

A4_BA2

A5_BA1

WE#

A7_A8

A6_A11

ABI#

A12_RFU

A0_A10

A1_A9

RAS#

RST#

CKE#

CAS#

DATA Bus

8 16

8 16

8 16

32..630..31

CS#

A3_BA3

A2_BA0

A4_BA2

A5_BA1

WE#

A7_A8

A6_A11

ABI#

A12_RFU

A0_A10

A1_A9

RAS#

RST#

CKE#

CAS#

1.0

1.0

1.0

Page 9

5

Memory Partition A - Lower 32 bits

FBA_EDC0

FBA_EDC2

FBA_DBI0#

FBA_DBI2#

FBA_CLK0

FBA_CLK0#

FBA_CKE_L

FBA_MA2_BA0_L

FBA_MA5_BA1_L

FBA_MA4_BA2_L

FBA_MA3_BA3_L

FBA_MA7_MA8_L

FBA_MA1_MA9_L

FBA_MA0_MA10_L

FBA_MA6_MA11_L

FBA_MA12_RFU_L

12

RV115

1K_0402_1%

12

RV117

12

1K_0402_1%

FBA_ABI#_L

FBA_RAS#_L

FBA_CS#_L

FBA_CAS#_L

FBA_WE#_L

FBA_WCK0_N

FBA_WCK0

FBA_WCK1_N

FBA_WCK1

+FBA_VREFD_L

+FBA_VREFC0

FBA_RST#_L

+FBA_VREFC0

16 mil

CV42

+1.5VS_VGA +1.5VS_VGA

12

+FBA_VREFD_L

12

820P_0402_25V7

1

1

CV69

CV77

2

2

1U_0603_25V6

1U_0603_25V6

8

8

CV155

RV212

1 2

931_0402_1%

QV9

+1.5VS_VGA

FBA_MA2_BA0_L

FBA_MA5_BA1_L

FBA_MA4_BA2_L

FBA_MA3_BA3_L

FBA_MA7_MA8_L

FBA_MA1_MA9_L

FBA_MA0_MA10_L

FBA_MA6_MA11_L

FBA_MA12_RFU_L

+1.5VS_VGA

RV127

549_0402_1%

RV128

1.33K_0402_1%

RV213

1 2

931_0402_1%

4,10,11,12

2

CV166

1

10U_0603_6.3V6M

8

8

FBA_CLK0

FBA_CLK0#

FBA_CKE_L

RV119

FBA_ABI#_L

FBA_RAS#_L

FBA_CS#_L

FBA_CAS#_L

FBA_WE#_L

FBA_WCK0_N

FBA_WCK0

FBA_WCK1_N

FBA_WCK1

FBA_RST#_L

12

12

RV129

549_0402_1%

RV130

1.33K_0402_1%

UV3 SIDE

1

2

1U_0603_25V6

FBA_DBI0#

FBA_DBI2#

121_0402_1%

820P_0402_25V7

+1.5VS_VGA

CV68

1U_0603_25V6

1

2

FBA_D[0..31]

FBA_EDC[3..0]

D D

Follow DG

1 2

FBA_CLK0

RV21 40.2_0402_1%

RV123

160_0402_1%

FBA_CLK0#

MEM_VREF

@

1 2

1 2

RV28 40.2_0402_1%

2

G

1

2

0.01U_0402_25V7K

13

D

S

2N7002W-T/R7_SOT323-3

C C

B B

A A

1

2

1

2

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

CV58

CV78

UV3

MF=0 MF=1 MF=0MF=1

C2

EDC0 EDC3

C13

EDC1 EDC2

R13

EDC2 EDC1

R2

EDC3 EDC0

D2

8

DBI0# DBI3#

D13

DBI1# DBI2#

P13

8

DBI2# DBI1#

P2

DBI3# DBI0#

J12

CK

J11

CK#

J3

CKE#

H11

BA0/A2 BA2/A4

K10

BA1/A5 BA3/A3

K11

BA2/A4 BA0/A2

H10

BA3/A3 BA1/A5

K4

A8/A7 A10/A0

H5

A9/A1 A11/A6

H4

A10/A0 A8/A7

K5

A11/A6 A9/A1

J5

A12/RFU/NC

A5

VPP/NC

U5

VPP/NC

J1

MF

J10

SEN

J13

ZQ

J4

ABI#

G3

RAS# CAS#

G12

CS# WE#

L3

CAS# RAS#

L12

WE# CS#

D5

WCK01# WCK23#

D4

WCK01 WCK23

P5

WCK23# WCK01#

P4

WCK23 WCK01

A10

VREFD

U10

VREFD

J14

VREFC

J2

RESET#

H1

VSS

K1

VSS

B5

VSS

G5

VSS

L5

VSS

T5

VSS

B10

VSS

D10

VSS

G10

VSS

L10

VSS

P10

VSS

T10

VSS

H14

VSS

K14

VSS

G1

VDD

L1

VDD

G4

VDD

L4

VDD

C5

VDD

R5

VDD

C10

VDD

R10

VDD

D11

VDD

G11

VDD

L11

VDD

P11

VDD

G14

VDD

L14

VDD

170-BALL

SGRAM GDDR5

X76@

1

1

CV129

CV132

2

2

0.1U_0402_10V7K

0.1U_0402_10V7K

1

2

0.1U_0402_10V7K

CV133

4

DQ24 DQ0

DQ25 DQ1

DQ26 DQ2

DQ27 DQ3

DQ28 DQ4

DQ29 DQ5

DQ30 DQ6

DQ31 DQ7

DQ16 DQ8

DQ17 DQ9

DQ18 DQ10

DQ19 DQ11

DQ20 DQ12

DQ21 DQ13

DQ22 DQ14

DQ23 DQ15

DQ8 D Q16

DQ9 D Q17

DQ10 DQ18

DQ11 DQ19

DQ12 DQ20

DQ13 DQ21

DQ14 DQ22

DQ15 DQ23

DQ0 D Q24

DQ1 D Q25

DQ2 D Q26

DQ3 D Q27

DQ4 D Q28

DQ5 D Q29

DQ6 D Q30

DQ7 D Q31

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

H5GQ1H24AFR-T2L_BGA170

3

UV4

A4

FBA_D0

A2

FBA_D1

B4

FBA_D2

B2

FBA_D3

E4

FBA_D4

E2

FBA_D5

F4

FBA_D6

F2

FBA_D7

A11

A13

B11

B13

E11

E13

F11

F13

U11

FBA_D16

U13

FBA_D17

T11

FBA_D18

T13

FBA_D19

N11

FBA_D20

N13

FBA_D21

M11

FBA_D22

M13

FBA_D23

U4

U2

T4

T2

N4

N2

M4

M2

B1

D1

F1

M1

P1

T1

G2

L2

B3

D3

F3

H3

K3

M3

P3

T3

E5

N5

E10

N10

B12

D12

F12

H12

K12

M12

P12

T12

G13

L13

B14

D14

F14

M14

P14

T14

A1

C1

E1

N1

R1

U1

H2

K2

A3

C3

E3

N3

R3

U3

C4

R4

F5

M5

F10

M10

C11

R11

A12

C12

E12