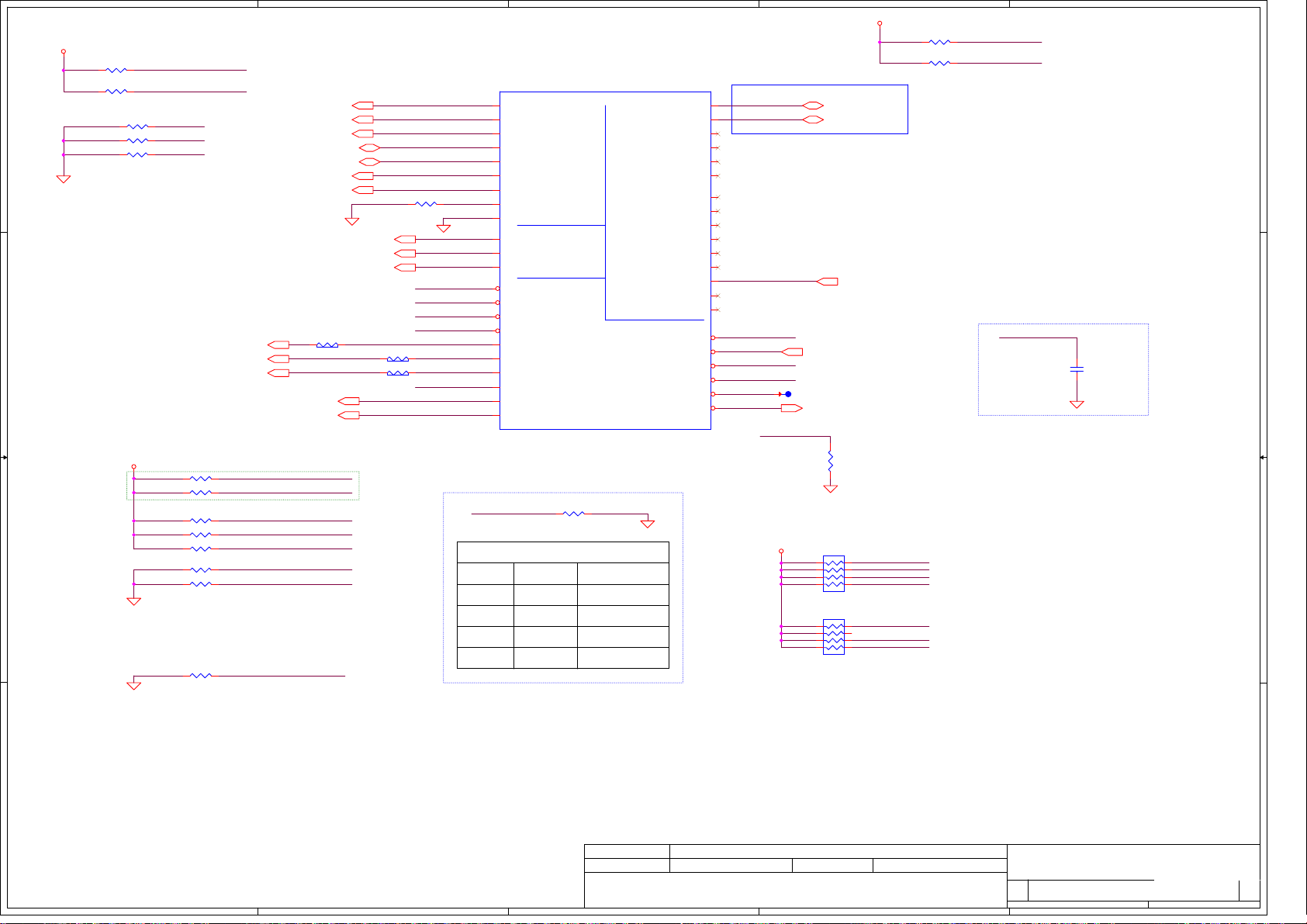

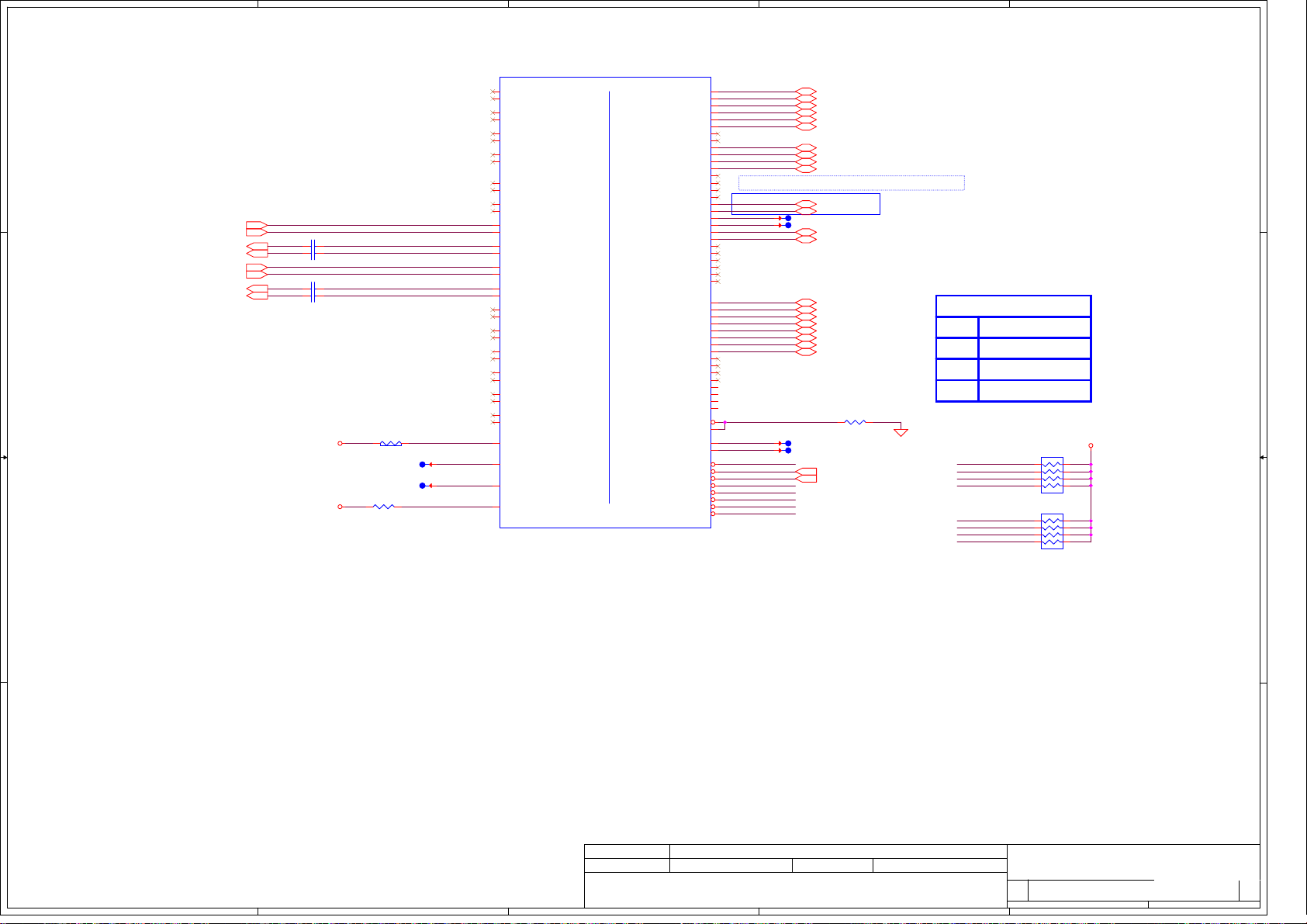

Compal NM-A181 ZX10 AILZA, IdeaPad Z410, IdeaPad Z510, NM-A181 ZX10 AILZB, NM-A181 ZX10 AILZC Schematic

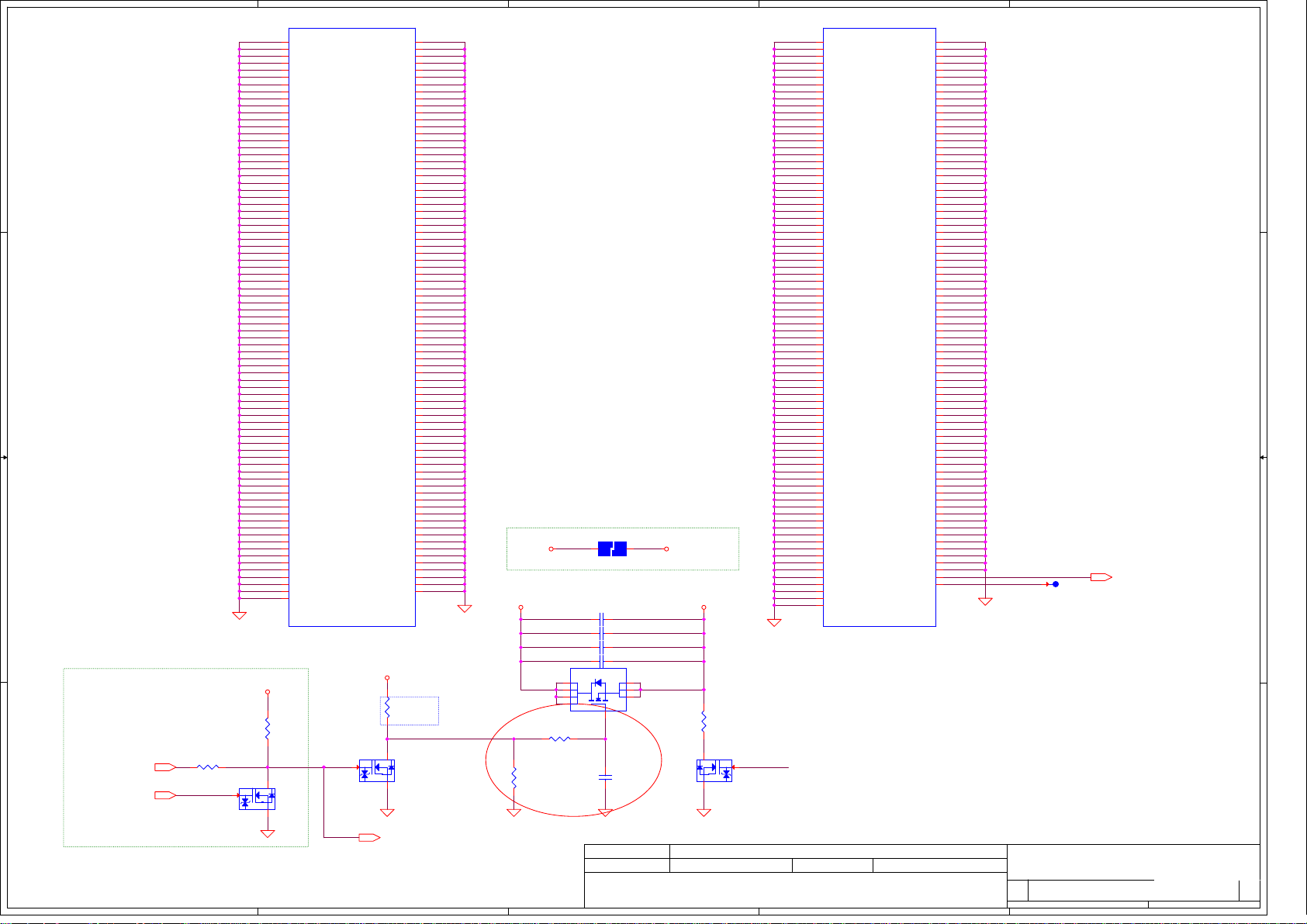

Page 1

A

1 1

B

C

D

E

LCFC Confidential

AILZA/B/C (ZX10)

MB MA181 Schematics

2 2

Intel Haswell Processor with DDRIIIL + Lynx Point HM86

nVIDIA N14P-GV2

2012-12-27

3 3

4 4

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

A

B

REV:1.1

Issued Date

Issued Date

Issued Date

2012/12/14

2012/12/14

2012/12/14

C

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2012/12/21

2012/12/21

2012/12/21

D

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Friday, July 12, 2013

Friday, July 12, 2013

Friday, July 12, 2013

401025

401025

401025

E

of

of

of

161

161

161

1.1

1.1

1.1

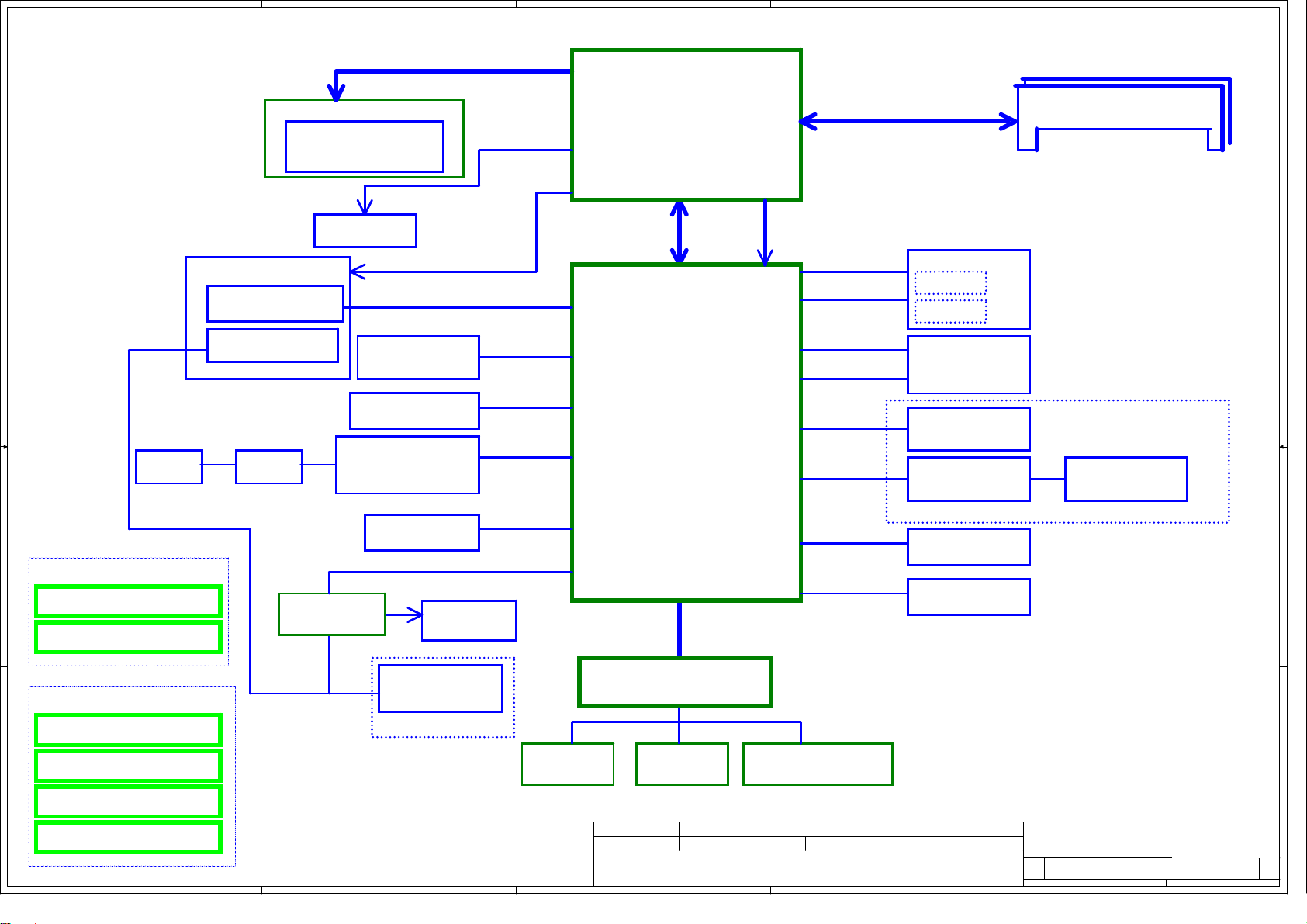

Page 2

A

LCFC confidential

File Name : ZX10

B

PCI-Express 8X Gen3

C

D

E

1 1

N14P-GV2

Page 23,24,25,26,27,32

VRAM 128*16/256*16

DDR3*4

Page 28,29

HDMI Conn.

Edp Conn.

Int. Camera

USB 2.0 Port 0

2 2

Int. MIC Conn.

Page 34 Page 34

Touch Screen

USB 2.0 Port 8

SPI ROM

(4MB+2MB)

Page 17

eDP

USB 2.0 1x

USB 2.0 1x

SPI BUS

Intel CPU

Haswell 37W/47W

rPGA-947

37.5mm*37.5mm

Page 5,6,7,8,9,10

DMI *4

5GT/s

Intel PCH

Lynx point HM86

695 ball FCBGA

FDI *2

20mm*20mm

RJ45 Conn.

3 3

Transform

Page 38Page 38

LAN Realtek

RTL8106E/8111G(S)

Page 37

Page 36

PCIe Port 4

CRT Conn.

Sub-board ( for 14")

POWERBOARD

Codec

ALC282-CG

Page 43

SPK Conn.

(1.5W x 2)

USBBoard

PCIe 1x

VGA

HD Audio

Page 13,14,15,16,17,18,19,20,21,22

LPC BUS

Page 43

Memory BUS (DDR3L)

Dual Channel

1.35V DDR3L 1333/1600 MT/s

USB 2.0 2x

USB 3.0 2x

PCIe 1x

USB 2.0 1x

USB 2.0 1x

USB 2.0 1x

SATA Gen3 Port 2

SATA Gen3 Port 4

USB Left

USB 2.0 Port 1

USB 3.0 Port 1

USB 2.0 Port 2

USB 3.0 Port 2

PCIeMini Card

WLAN&BT

PCIe Port 5

USB 2.0 Port 10

USB right

USB 2.0 Port 5

Cardreader

Genesys GL834L

USB 2.0 Port 4

SATA ODD

SATA Port 2

SATA HDD

SATA Port 4

DDR3-SO-DIMM X2

UP TO 16G

Page 41

Page 40

SD/MMC Conn.

Page 42

Page 42

Page 11,12

USBBoard

Page 45

EC

HP&Mic Combo Conn.

Sub-board ( for 15")

POWERBOARD

USBBoard

4 4

iphone type

USBBoard

Page 45

Touch Pad Int.KBD

ITE ITE8586 128LQFP

Page 44

Thermal Sensor

Page 45 Page 45 Page 39

EMC 1403

LEDBoard

Title

Title

ODDBoard

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

C

2012/12/14

2012/12/14

2012/12/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

2012/12/21

2012/12/21

2012/12/21

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Friday, July 12, 2013

Friday, July 12, 2013

Date: Sheet

Date: Sheet

Date: Sheet

Friday, July 12, 2013

401025

401025

401025

E

of

of

of

261

261

261

1.1

1.1

1.1

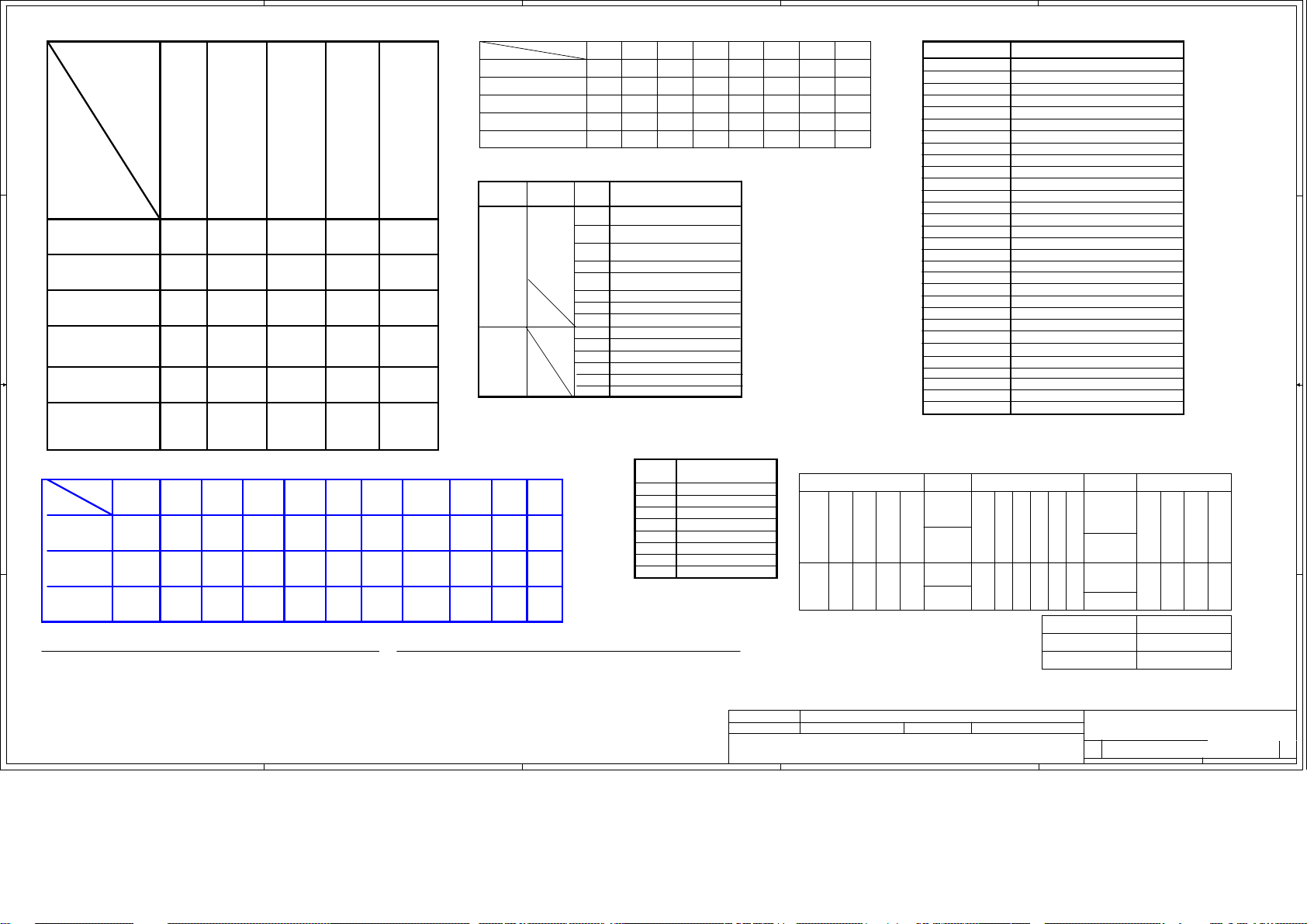

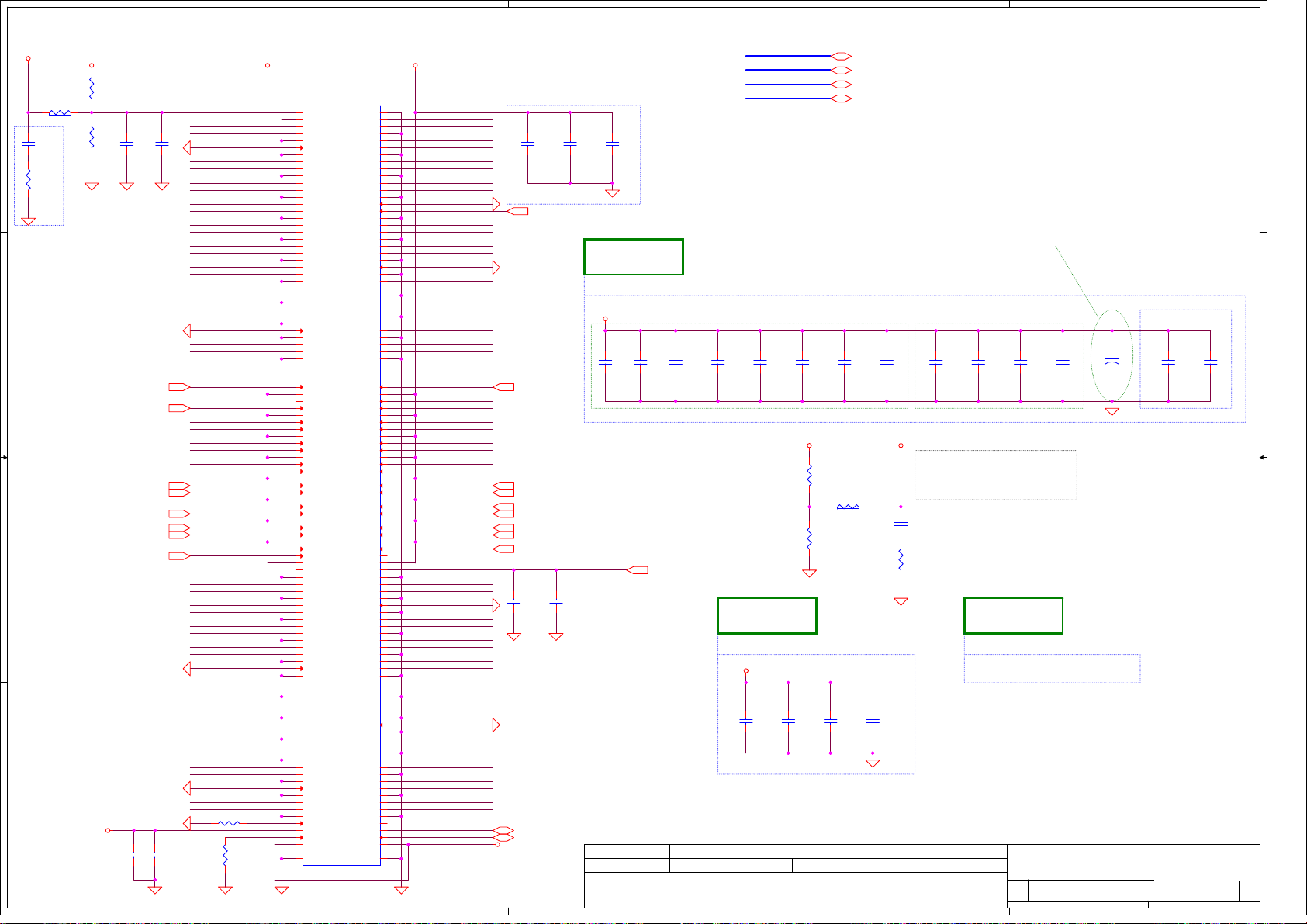

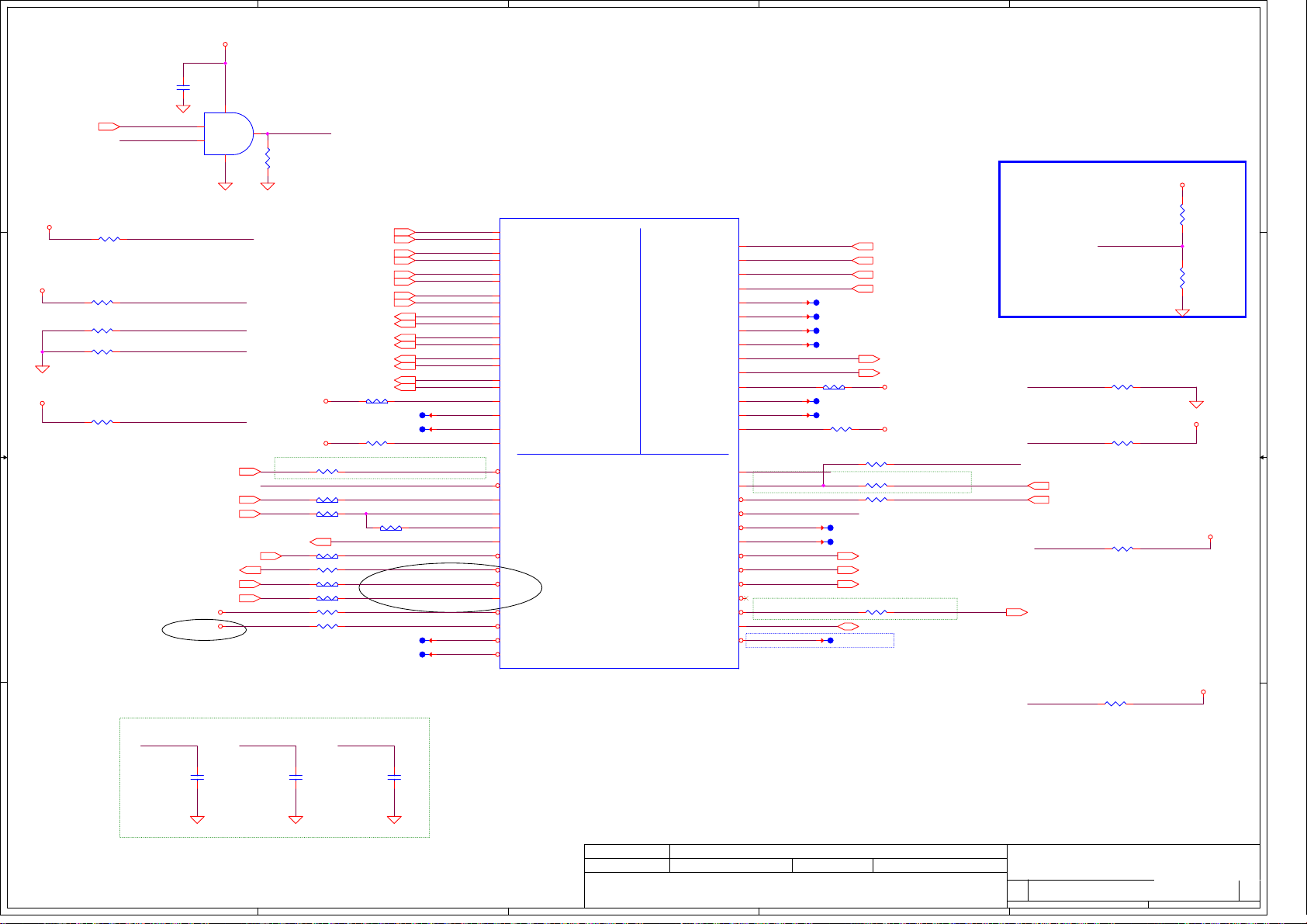

Page 3

A

B

C

D

E

Voltage Rails

Power Plane

1 1

State

S0

S3

2 2

S3

Battery only

S5 S4/AC Only

S5 S4

Battery only

S5 S4

AC & Battery

don't exist

( O --> Means ON , X --> Means OFF )

+3VALW

B+

+5VALW

O

+3V_PCH

OO O

O

O

O X

O

O

O

XX

XX

+1.35V

OO

X

O

X

O

O

O

X

X

X

+5VS

+3VS

+1.5VS

+1.05VS

+0.675VS

+CPU_CORE

+VGA_CORE

+3.3VS_VGA

+1.5VS_VGA

+1.05VS_VGA

X

X

X

X

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

USB Port Table

USB 3.0USB 2.0 Port

XHCI

1

EHCI1

2

EHCI2

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

3 External

USB Port

0

Camera

1

USB Port (Left Side)

2

USB Port (Left Side)

3

Cardreader

4

5

USB Port (Right Side)

6

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

ON

ONONON ON

ON

ON

OFF

OFF

OFF

OFF

OFF

LOW

OFF

OFF

OFF

7

TOUCH PANEL

8

9

Mini Card(WLAN)

10

11

12

13

BOM Structure Table

BTO ItemBOM Structure

AOAC@

OPT@

UMA@

14@

15@

8106@

8111G@

8111GS@

N14PGV2@

GIGA@

Gastube@

NOTS@

GC6@

TS@

@

ME@

XDP@

37@

47@

H2@

M2@

M4@

S2@

S4@

M1GB@

M2GB@

S1GB@

S2GB@

H1GB@

AOAC support part

External GPU SKU ID part

UMA SKU ID part

For Z410 part

For Z510 part

8106E LAN part

8111G LAN Part

8111GS LAN Part

N14P GV2 stuff

GIGA LAN Part

Gastube Part

No Touch screen part

GPU GC6 function part

Touch screen part

Not stuff

Connector

XDP part

37W CPU part

47W CPU part

Hynix 2Gb Vram part

Micron 2Gb Vram part

Micron 4Gb Vram part

Samsung 2Gb Vram part

Samsung 4Gb Vram part

Micron 1GB Vram BOM

Micron 2GB Vram BOM

samsung 1GB Vram BOM

samsung 2GB Vram BOM

hynix 1GB Vram BOM

PCIE PORT LIST

SMBUS Control Table

3 3

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

PCH_SMBCLK

PCH_SMBDATA

EC SM Bus1 address

4 4

Device

Smart Battery

Charger

SOURCE

IT8586EEC_SMB_CK1

+3VALW

IT8586E

+3VS

+3V_PCH +3VS +3VS

VGA BATT SODIMM

X

X

V

+3VS_VGA

PCH

XXX X

IT8586E

V

V

+3VS +3VS

EC SM Bus2 address

Device

0001 011X b

0001 0010 b

A

Thermal Sensor EMC1403-2

VGA

PCH

WLAN

Thermal

WiMAX

Sensor

XXV

X

X

VV

Address

1001_101xb

0x9E

0x96

V

X

V

+3V_PCH

+3V_PCH

PCH SM Bus address

Device Address

DDR DIMMA

DDR DIMMB

Wlan

TP

B

PCH

TP

Module

XX

V

X

V

+3VS

charger

V

X

X

0xA0

0xA2

Rsvd

0x2C for Synaptics

0x15 for ELAN vendor

XDP

+3VS

X

X

V

Port Device

1

2

3

4

LAN

5

WLAN

6

7

8

C

PCIE

3

PCIE

3

FixedSignals

PCIE

PCIE

4

5

PCIE

PCIE

4

5

2012/12/21

2012/12/21

2012/12/21

PCIE

6

PCIE

6

*

FixedSignals

USB3

USB3

1

2

HM86

USB3

USB3

1

2012/12/14

2012/12/14

2012/12/14

2

HM87

QM87

SoftStrap:(USB3P4_PCIEP2_MODE)

00:PCIeLane2isstaticallyassignedtoPCIEExpress(orGbE)

01:PCIeLane2isstaticallyassignedtoUSB3Port4

SoftStrap:(USB3P3_PCIEP1_MODE)

00:PCIeLane1isstaticallyassignedtoPCIEExpress(orGbE)

01:PCIeLane1isstaticallyassignedtoUSB3Port3

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MuxedSignals

NA PCIE

NA NA NA

USB3

USB3

5

6

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

PCIE

1

2

(00)

(00)

USB3

USB3

3

4

(01) (0b) (0b)

(01)

PCIE

PCIE

1

2

USB3

USB3

4

5

Deciphered Date

Deciphered Date

Deciphered Date

D

SATA

6Gb/s

5

PCIE

2

SATA

6Gb/s

5

PCIE

3

Friday, July 12, 2013

Friday, July 12, 2013

Friday, July 12, 2013

SATA

3Gb/s

0

SATA

6Gb/s

0

FixedSignals

SATA

6Gb/s

1

GPIO16,49

11

00PCIE1,PECI2

401025

401025

401025

E

SATA

3Gb/s

2

SATA

3Gb/s

2

MuxedSignals

PCIE

PCIE

SATA

7

8

6Gb/s

4

(1b) (1b)

PCIE

1

PCIE

PCIE

SATA

7

8

6Gb/s

4

PCIE

2

Config

SATA4,SATA5

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

SATA

3Gb/s

3

361

361

361

1.1

1.1

1.1

of

of

of

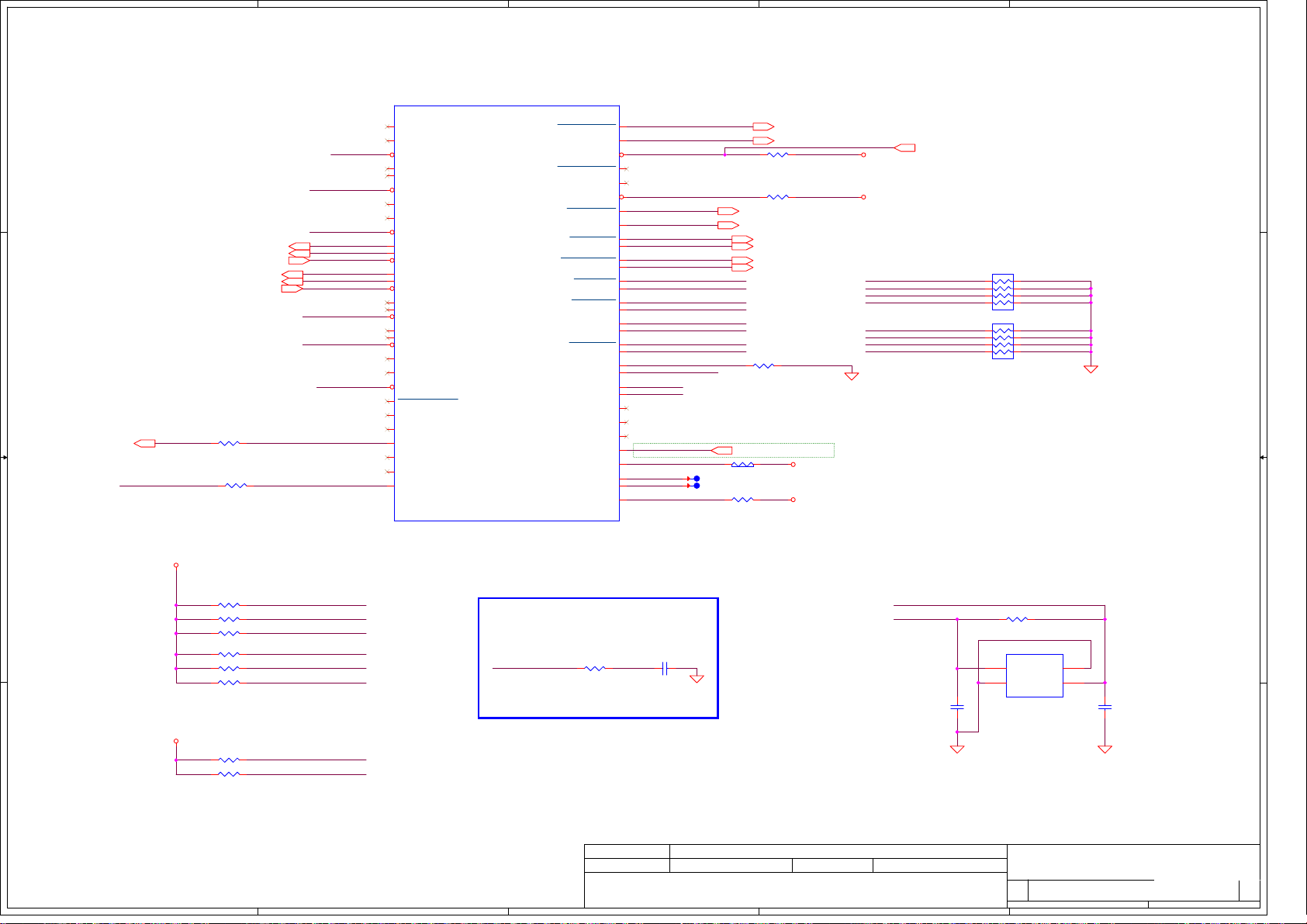

Page 4

5

4

3

2

1

VGA and GDDR3 Voltage Rails (N14P GPIO)

GPIO I/O ACTIVE Function Description

D D

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

C C

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

IN FB Clamp monitorOUT

N/A

OUT

N/A

OUT

N/A

OUT

N/A

N/A

-

OUT

OUT

N/A

I/O

I/O N/A

OUT

N/A

IN

OUT

IN

N/A

IN

N/A

OUT

N/A

IN

N/A

IN

N/A

IN

N/A

Active low FB Clamp toggle request

Thermal Catastrophic Over Temperature

2.2K Pull-up

GPU Core VDD PWM control signal-OUT

AC Power Detect Input

Phase Shedding-

(10K pull High)

Performance Mode P0 TDP at Tj = 102 C* (DDR3)

GPU Mem NVCLK

(4) (1,5) (6)

(W) (W) (MHz)

Products

N14P

64bit

25W TBD 32 TBD 1.7 2.55 TBD TBD 1.98 2.1 TBD TBD TBD TBD TBD TBD

1GB/2GB

DDR3

Physical

Strapping pin

ROM_SCLK

ROM_SI

ROM_SO FB[0]

STRAP0

STRAP1

STRAP2

STRAP3

STRAP4

GPU

Power Rail

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

Device ID

/MCLK NVVDD

(V) (A) (W) (A) (W)

1000MHz TBD

Logical

Strapping Bit3

PCI_DEVID[4]

FB[1]

3GIO_PAD_CFG_ADR[2] 3GIO_PAD_CFG_ADR[1]3GIO_PAD_CFG_ADR[3]

PCI_DEVID[3] PCI_DEVID[2] PCI_DEVID[1] PCI_DEVID[0]

SOR3_EXPOSED

RESERVED PCIE_SPEED_

SMB_ALT_ADDR

(ROM_SO Bit 1)

setting

N14P-GV2 0x1292

ROM_SO ROM_SCLKGPU STRAP2STRAP1STRAP0

ROM_SI

N14P-GV2 PD 45.3K

TBD PU 4.99K PU 45.3K

PU 45.3KPU 4.99K PD 15K

FBVDDQ PCI Express I/O and

FBVDD

(GPU+Mem)

(1.5V)(1.5V)

(A) (W) (W)(A) (W) (W) (W)(mA) (mA) (mA)

Logical

Strapping Bit2

SUB_VENDOR

USER[2] USER[1] USER[0]USER[3]

SOR2_EXPOSED SOR1_EXPOSED

CHANGE_GEN3

I2C Slave addrees ID

0

1

0x9E

0x9C

(1.05V)

Logical

Strapping Bit1

PCI_DEVID5]

RAM_CFG[1]RAM_CFG[3] RAM_CFG[2]

PLLVDD

I/O and

PLLVDD

Logical

Strapping Bit0

PEX_PLL_EN_TERM

RAM_CFG[0]

VGA_DEVICESMB_ALT_ADDR

3GIO_PAD_CFG_ADR[0]

SOR0_EXPOSED

PCIE_MAX_SPEED DP_PLL_VDD33V

(Default)

STRAP3

STRAP4

PD 4.99K

Other

(3.3V)(1.05V)(1.8V)

B B

A A

5

+3VS_VGA

+VGA_CORE

+1.5VS_VGA

+1.05VS_VGA

Other Power rail

+3VS_VGA

tNVVDD >0

tFBVDDQ >0

tPEX_VDD >0

1. all power rail ramp up time should be larger than 40us

Tpower-off <10ms

1.all GPU power rails should be turned off within 10ms

2. Optimus system VDD33 avoids drop down earlier than NVDD and FBVDDQ

4

GPU

FB Memory (DDR3)

Samsung

1GHz

Micron

1GMHz

Hynix

1GMHz

Samsung

900MHz

Micron

900MHz

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

K4W2G1646E-BC1A

128M x 16

MT41J128M16JT-093G:K

128M x 16

128M x 16

K4W4G1646B-HC11

256M x 16

MT41K256M16HA-107G:E

256M x 16

Issued Date

Issued Date

Issued Date

2012/12/14

2012/12/14

2012/12/14

N14P_GV2

ROM_SI

0x7

PD 45.3K

0x5

PD 30.1K

0x4H5TC2G63FFR-11C

PD 24.9K

0x3

PD 20K

0x1

PD 10K

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2012/12/21

2012/12/21

2012/12/21

Title

Title

Title

VGA Notes List

VGA Notes List

VGA Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Friday, July 12, 2013

Friday, July 12, 2013

Friday, July 12, 2013

Date: Sheet

Date: Sheet

Date: Sheet

401025

401025

401025

1

of

of

of

461

461

461

1.1

1.1

1.1

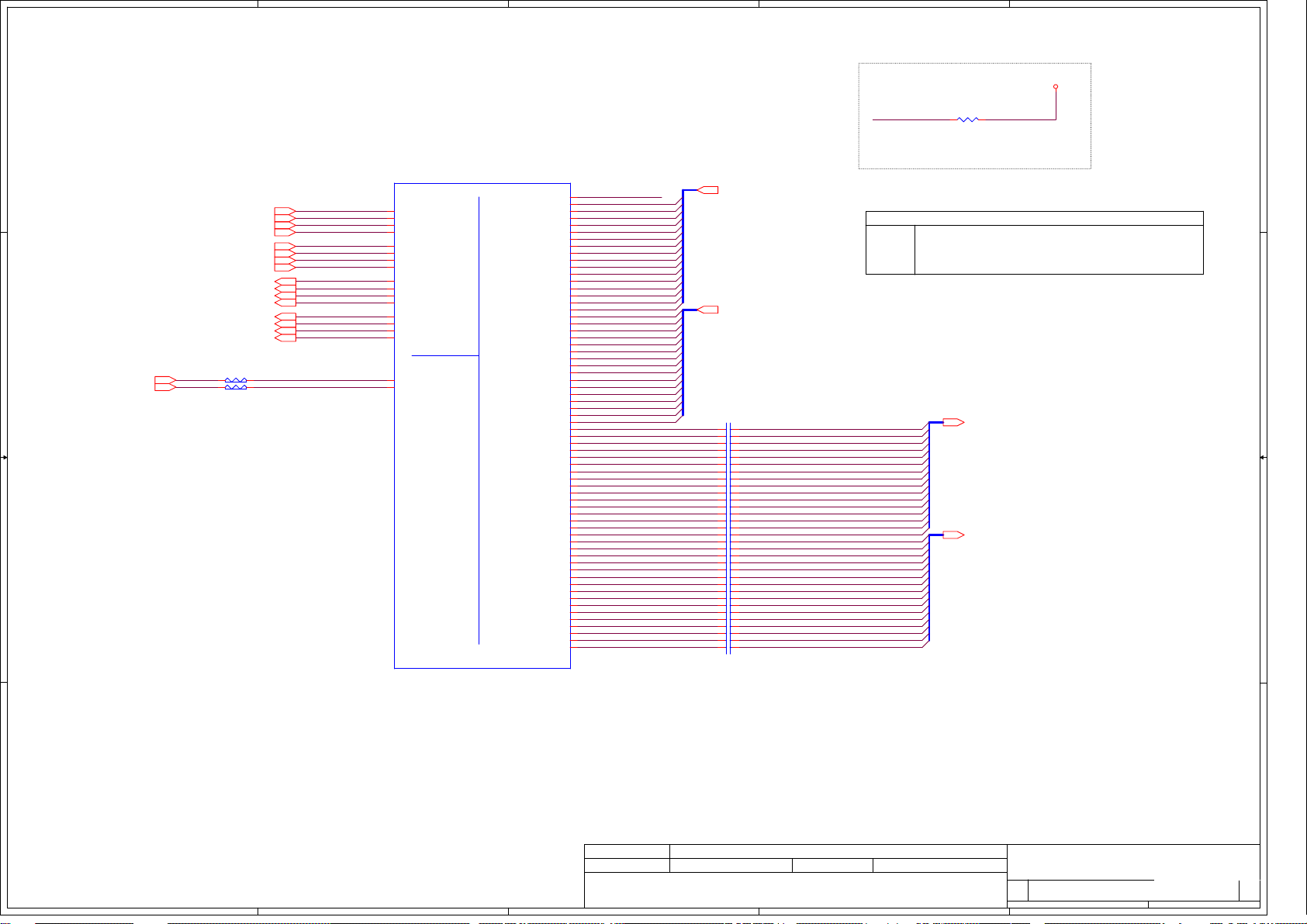

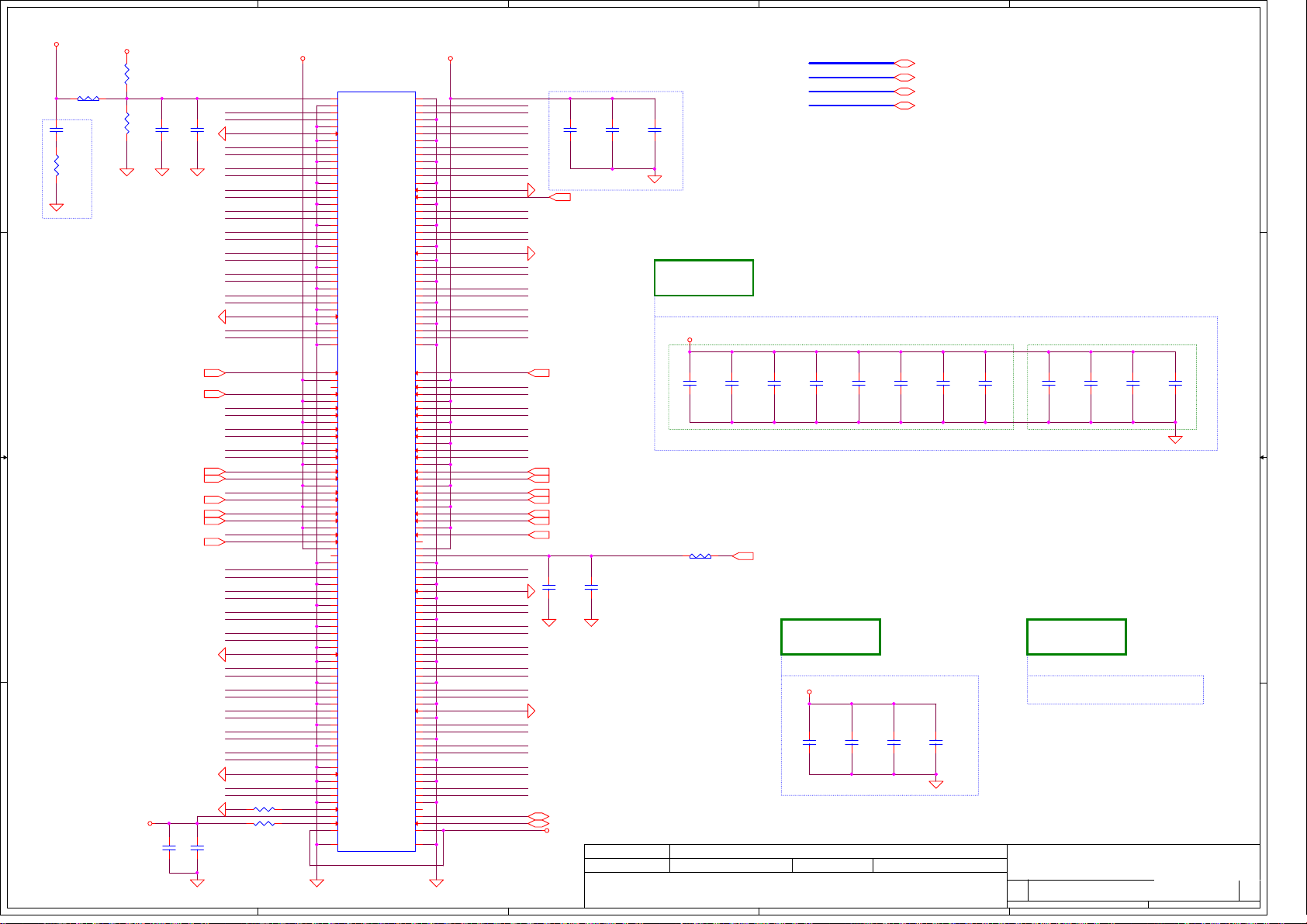

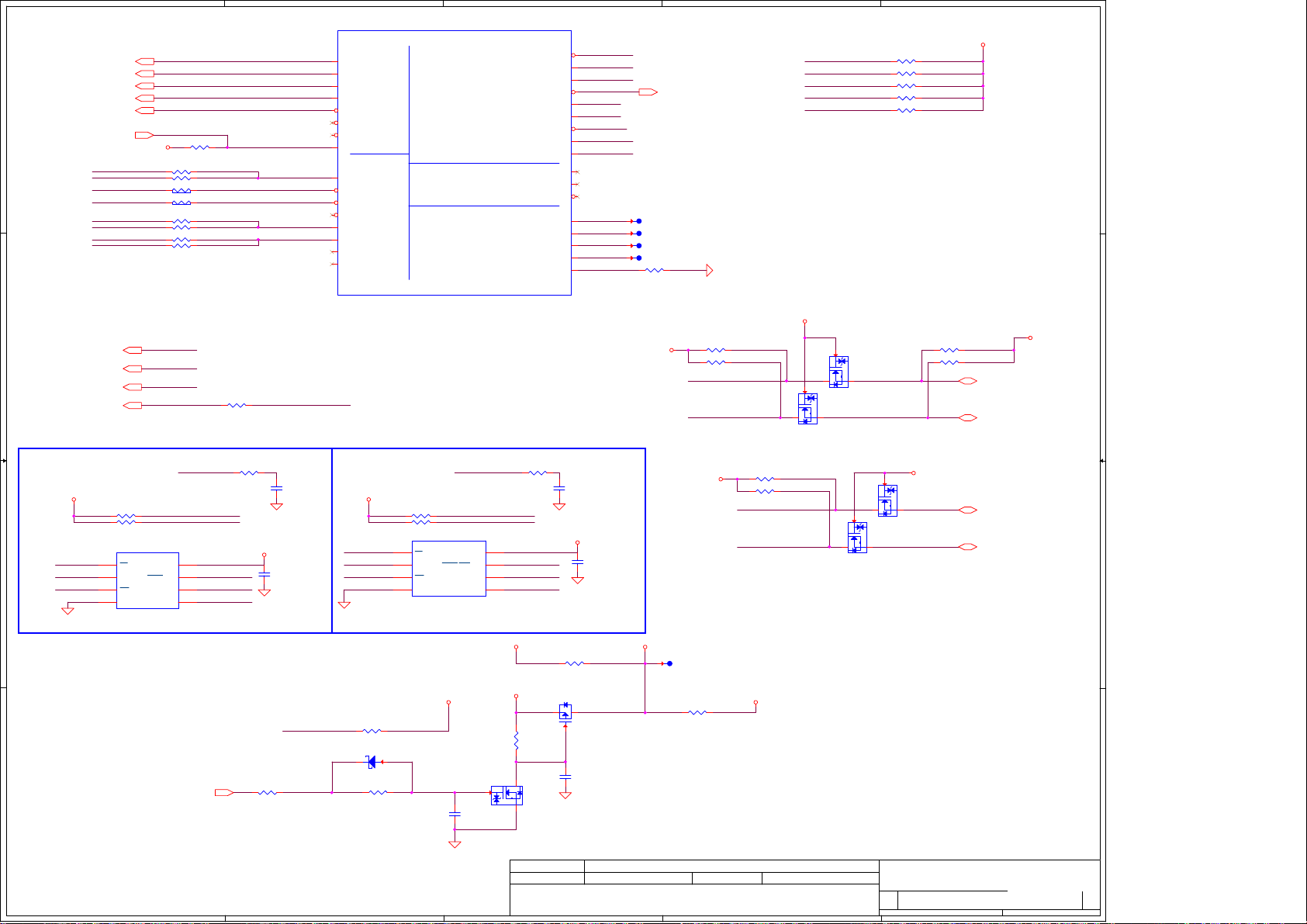

Page 5

5

4

3

2

+VCCIOA_OUT

1

D D

JCPU1A

DMI_CRX_PTX_N015

DMI_CRX_PTX_N115

DMI_CRX_PTX_N215

DMI_CRX_PTX_N315

DMI_CRX_PTX_P015

DMI_CRX_PTX_P115

DMI_CRX_PTX_P215

DMI_CRX_PTX_P315

DMI_CTX_PRX_N015

DMI_CTX_PRX_N115

DMI_CTX_PRX_N215

DMI_CTX_PRX_N315

DMI_CTX_PRX_P015

DMI_CTX_PRX_P115

DMI_CTX_PRX_P215

C C

FDI_CSYNC15

FDI_INT15

B B

DMI_CTX_PRX_P315

1 2

RC2 0_0402_5%@

1 2

RC3 0_0402_5%@

Change RC2,RC3 to 0ohm jump

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

FDI_CSYNC_R

FDI_INT_R

D21

DMI_RXN_0

C21

DMI_RXN_1

B21

DMI_RXN_2

A21

DMI_RXN_3

D20

DMI_RXP_0

C20

DMI_RXP_1

B20

DMI_RXP_2

A20

DMI_RXP_3

D18

DMI_TXN_0

C17

DMI_TXN_1

B17

DMI_TXN_2

A17

DMI_TXN_3

D17

DMI_TXP_0

C18

DMI_TXP_1

B18

DMI_TXP_2

A18

DMI_TXP_3

H29

FDI_CSYNC

J29

DISP_INT

FOX_PZ94726-3641-41H_HASWELL

ME@

Haswell rPGA EDS

FDIDMI

1 OF 9

PEG

PEG_RCOMP

PEG_RXN_0

PEG_RXN_1

PEG_RXN_2

PEG_RXN_3

PEG_RXN_4

PEG_RXN_5

PEG_RXN_6

PEG_RXN_7

PEG_RXN_8

PEG_RXN_9

PEG_RXN_10

PEG_RXN_11

PEG_RXN_12

PEG_RXN_13

PEG_RXN_14

PEG_RXN_15

PEG_RXP_0

PEG_RXP_1

PEG_RXP_2

PEG_RXP_3

PEG_RXP_4

PEG_RXP_5

PEG_RXP_6

PEG_RXP_7

PEG_RXP_8

PEG_RXP_9

PEG_RXP_10

PEG_RXP_11

PEG_RXP_12

PEG_RXP_13

PEG_RXP_14

PEG_RXP_15

PEG_TXN_0

PEG_TXN_1

PEG_TXN_2

PEG_TXN_3

PEG_TXN_4

PEG_TXN_5

PEG_TXN_6

PEG_TXN_7

PEG_TXN_8

PEG_TXN_9

PEG_TXN_10

PEG_TXN_11

PEG_TXN_12

PEG_TXN_13

PEG_TXN_14

PEG_TXN_15

PEG_TXP_0

PEG_TXP_1

PEG_TXP_2

PEG_TXP_3

PEG_TXP_4

PEG_TXP_5

PEG_TXP_6

PEG_TXP_7

PEG_TXP_8

PEG_TXP_9

PEG_TXP_10

PEG_TXP_11

PEG_TXP_12

PEG_TXP_13

PEG_TXP_14

PEG_TXP_15

E23

PEG_COMP

M29

PCIE_CRX_GTX_N0

K28

PCIE_CRX_GTX_N1

M31

PCIE_CRX_GTX_N2

L30

PCIE_CRX_GTX_N3

M33

PCIE_CRX_GTX_N4

L32

PCIE_CRX_GTX_N5

M35

PCIE_CRX_GTX_N6

L34

PCIE_CRX_GTX_N7

E29

PCIE_CRX_GTX_N8

D28

PCIE_CRX_GTX_N9

E31

PCIE_CRX_GTX_N10

D30

PCIE_CRX_GTX_N11

E35

PCIE_CRX_GTX_N12

D34

PCIE_CRX_GTX_N13

E33

PCIE_CRX_GTX_N14

E32

PCIE_CRX_GTX_N15

L29

PCIE_CRX_GTX_P0

L28

PCIE_CRX_GTX_P1

L31

PCIE_CRX_GTX_P2

K30

PCIE_CRX_GTX_P3

L33

PCIE_CRX_GTX_P4

K32

PCIE_CRX_GTX_P5

L35

PCIE_CRX_GTX_P6

K34

PCIE_CRX_GTX_P7

F29

PCIE_CRX_GTX_P8

E28

PCIE_CRX_GTX_P9

F31

PCIE_CRX_GTX_P10

E30

PCIE_CRX_GTX_P11

F35

PCIE_CRX_GTX_P12

E34

PCIE_CRX_GTX_P13

F33

PCIE_CRX_GTX_P14

D32

PCIE_CRX_GTX_P15

H35

PCIE_CTX_GRX_N0

H34

PCIE_CTX_GRX_N1

J33

PCIE_CTX_GRX_N2

H32

PCIE_CTX_GRX_N3

J31

PCIE_CTX_GRX_N4

G30

PCIE_CTX_GRX_N5

C33

PCIE_CTX_GRX_N6

B32

PCIE_CTX_GRX_N7

B31

PCIE_CTX_GRX_N8

A30

PCIE_CTX_GRX_N9

B29

PCIE_CTX_GRX_N10

A28

PCIE_CTX_GRX_N11

B27

PCIE_CTX_GRX_N12

A26

PCIE_CTX_GRX_N13

B25

PCIE_CTX_GRX_N14

A24

PCIE_CTX_GRX_N15

J35

PCIE_CTX_GRX_P0

G34

PCIE_CTX_GRX_P1

H33

PCIE_CTX_GRX_P2

G32

PCIE_CTX_GRX_P3

H31

PCIE_CTX_GRX_P4

H30

PCIE_CTX_GRX_P5

B33

PCIE_CTX_GRX_P6

A32

PCIE_CTX_GRX_P7

C31

PCIE_CTX_GRX_P8

B30

PCIE_CTX_GRX_P9

C29

PCIE_CTX_GRX_P10

B28

PCIE_CTX_GRX_P11

C27

PCIE_CTX_GRX_P12

B26

PCIE_CTX_GRX_P13

C25

PCIE_CTX_GRX_P14

B24

PCIE_CTX_GRX_P15

PCIE_CRX_GTX_N[0..15] 23

PCIE_CRX_GTX_P[0..15] 23

1 2

CC1 0.22U_0402_10V6K@

1 2

CC2 0.22U_0402_10V6K@

1 2

CC3 0.22U_0402_10V6K@

1 2

CC4 0.22U_0402_10V6K@

1 2

CC5 0.22U_0402_10V6K@

1 2

CC6 0.22U_0402_10V6K@

1 2

CC7 0.22U_0402_10V6K@

1 2

CC8 0.22U_0402_10V6K@

1 2

CC9 0.22U_0402_10V6KOPT@

1 2

CC10 0.22U_0402_10V6KOPT@

1 2

CC11 0.22U_0402_10V6KOPT@

1 2

CC12 0.22U_0402_10V6KOPT@

1 2

CC13 0.22U_0402_10V6KOPT@

1 2

CC14 0.22U_0402_10V6KOPT@

1 2

CC15 0.22U_0402_10V6KOPT@

1 2

CC16 0.22U_0402_10V6KOPT@

1 2

CC17 0.22U_0402_10V6K@

1 2

CC18 0.22U_0402_10V6K@

1 2

CC19 0.22U_0402_10V6K@

1 2

CC20 0.22U_0402_10V6K@

1 2

CC21 0.22U_0402_10V6K@

1 2

CC22 0.22U_0402_10V6K@

1 2

CC23 0.22U_0402_10V6K@

1 2

CC24 0.22U_0402_10V6K@

1 2

CC25 0.22U_0402_10V6KOPT@

1 2

CC26 0.22U_0402_10V6KOPT@

1 2

CC27 0.22U_0402_10V6KOPT@

1 2

CC28 0.22U_0402_10V6KOPT@

1 2

CC29 0.22U_0402_10V6KOPT@

1 2

CC30 0.22U_0402_10V6KOPT@

1 2

CC31 0.22U_0402_10V6KOPT@

1 2

CC32 0.22U_0402_10V6KOPT@

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_N3

PCIE_CTX_C_GRX_N4

PCIE_CTX_C_GRX_N5

PCIE_CTX_C_GRX_N6

PCIE_CTX_C_GRX_N7

PCIE_CTX_C_GRX_N8

PCIE_CTX_C_GRX_N9

PCIE_CTX_C_GRX_N10

PCIE_CTX_C_GRX_N11

PCIE_CTX_C_GRX_N12

PCIE_CTX_C_GRX_N13

PCIE_CTX_C_GRX_N14

PCIE_CTX_C_GRX_N15

PCIE_CTX_C_GRX_P0

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_P4

PCIE_CTX_C_GRX_P5

PCIE_CTX_C_GRX_P6

PCIE_CTX_C_GRX_P7

PCIE_CTX_C_GRX_P8

PCIE_CTX_C_GRX_P9

PCIE_CTX_C_GRX_P10

PCIE_CTX_C_GRX_P11

PCIE_CTX_C_GRX_P12

PCIE_CTX_C_GRX_P13

PCIE_CTX_C_GRX_P14

PCIE_CTX_C_GRX_P15

PEG_COMP

CADNote:

Tracewidth=12mils,Spacing=15mil

Maxlength=400mils.

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

1 2

RC1 24.9_0402_1%

1: Normal Operation; Lane # definition matches

socket pin map definition

*

0:Lane Reversed

PCIE_CTX_C_GRX_N[0..15] 23

PCIE_CTX_C_GRX_P[0..15] 23

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2012/12/14

2012/12/14

2012/12/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2012/12/21

2012/12/21

2012/12/21

Title

CPU (1/7) DMI, FDI, PEG

CPU (1/7) DMI, FDI, PEG

CPU (1/7) DMI, FDI, PEG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Friday, July 12, 2013

Friday, July 12, 2013

Date: Sheet

Date: Sheet

Date: Sheet

Friday, July 12, 2013

401025

401025

401025

1

of

of

of

561

561

561

1.1

1.1

1.1

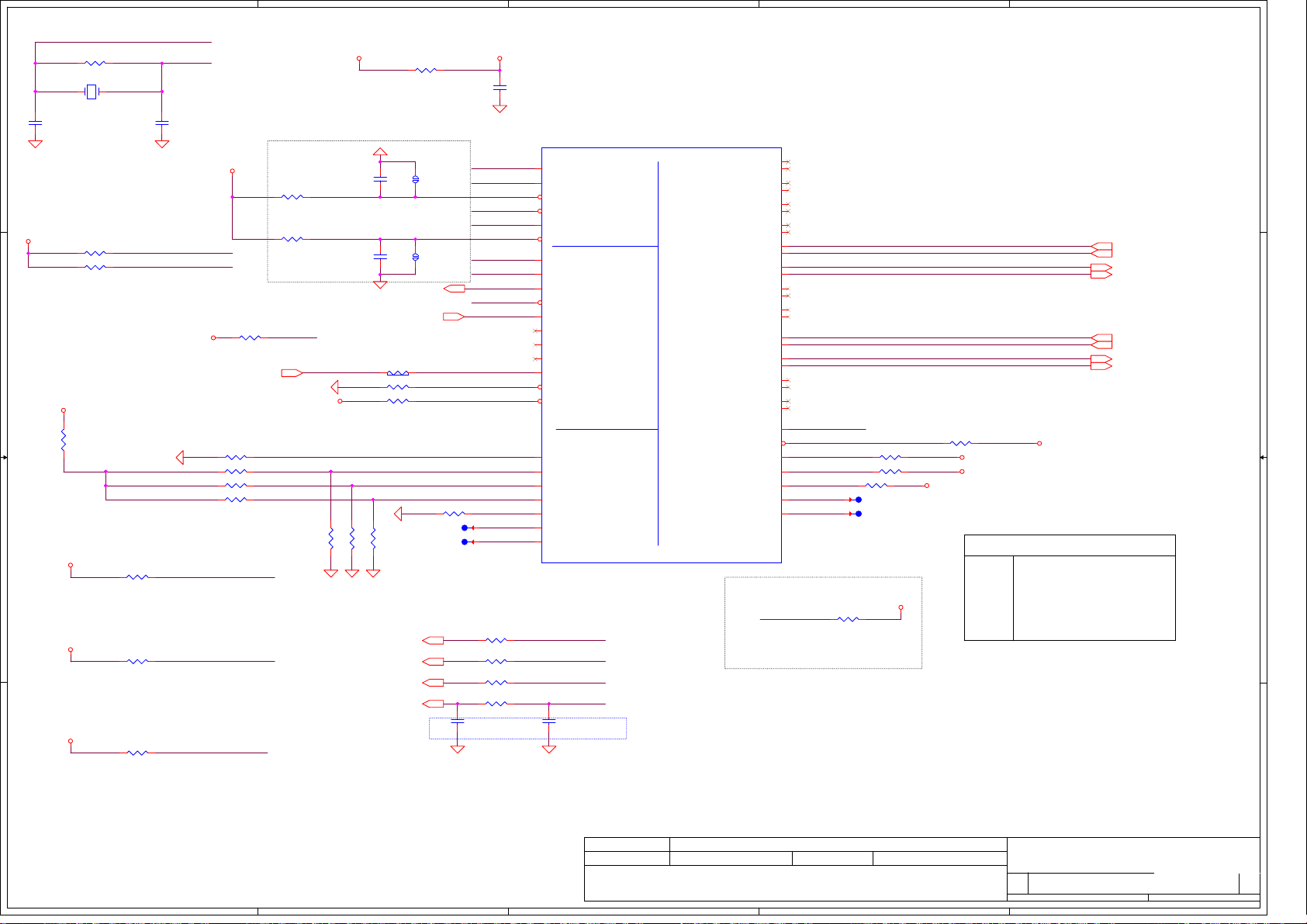

Page 6

5

4

3

2

1

+1.05VS

1 2

RC4 0_0603_5%@

D D

.1U_0402_10V6-K

ReserveforDesignGuideandCRBrecommended.

Buffered Reset to CPU

C C

CPU_PLTRST#19

1.05V

RC22 0_0402_5%@

1 2

Change RC22 to 0ohm jump

B B

+3V_PCH

SM_DRAMPWROKwithDDRPowerGatingTopology

+3VALW

PM_DRAM_PWRGD15

RC79 0_0402_5%@

RC78 0_0402_5%@

SYS_PWROK15,44

VDDQ_PGOOD44,55

RC77

RC39

.01U_0402_16V7-K

Change RC77 to 0ohm jump

A A

CC33

@

12

12

RC35

0_0402_5%

1 2

@

0_0402_5%

@

1 2

10K_0402_5%

CC40

+VCCST

1

1

CC34

4.7U_0603_6.3V6K

@

2

2

H_PROCHOT#44,51,52

CLK_CPU_DPLL#16

CLK_CPU_DPLL16

CLK_CPU_SSC_DPLL#16

CLK_CPU_SSC_DPLL16

BUF_CPU_RST#

ForESDconcern,pleaseputnearCPU

ForESD

+3VDRAM

200_0402_5%

100K_0402_5%

12

12

RC32

RC31

@

@

@

12

1

@

2

CC37

5

1

P

B

2

A

G

3

74AHC1G09GW_TSSOP5

@

RC41 0_0402_5%

RUN_ON_CPU1.5VS3#10

+VCCIO_OUT

12

RC7

62_0402_5%

H_PM_SYNC15

H_CPUPWRGD19

Change RC11,RC13,RC15,RC16,RC17 to 0ohm jump

1

CC35

220P_0402_50V7K

2

@

1 2

@

.1U_0402_10V6-K

4

Y

UC1

12

2

G

+VCCST

1 2

RC9 56_0402_5%

1 2

RC11 0_0402_5%@

1 2

RC13 0_0402_5%@

1 2

RC15 0_0402_5%@

1 2

RC16 0_0402_5%@

1 2

RC17 0_0402_5%@

CLK_CPU_DMI#16

CLK_CPU_DMI16

1

CC36

220P_0402_50V7K

2

@

+1.35V_CPU_VDDQ

RC42

39_0402_5%

@

1 2

13

D

QC2

@

S

2N7002KW_SOT323-3

PAD@

1

TC81

H_PECI44

H_THRMTRIP#19

H_PM_SYNC

VCCPWRGOOD_0_R

PM_DRAM_PWRGD_CPU

BUF_CPU_RST#

CPU_DPLL#

CPU_DPLL

CPU_SSC_DPLL#

CPU_SSC_DPLL

CLK_CPU_DMI#

CLK_CPU_DMI

SSCCLOCKTERMINATION,IFNOTUSED,stuffRC25,RC27

12

RC33

1.8K_0402_1%

@

1 2

RC36

0_0402_5%

Change RC36 to 0ohm jump

12

RC40

3.3K_0402_1%

H_CATERR#

H_PECI

H_PROCHOT#_R

H_THRMTRIP#

PM_DRAM_PWRGD_CPURUNPWROK_AND

AP32

AN32

AR27

AK31

AM30

AM35

AT28

AL34

AC10

AT26

G28

H28

F27

E27

D26

E26

+VCCIO_OUT

@

RC25 10K_0402_5%

@

RC27 10K_0402_5%

JCPU1B

SKTOCC

CATERR

PECI

FC_AK31

PROCHOT

THERMTRIP

PM_SYNC

PWRGOOD

SM_DRAMPWROK

PLTRSTIN

DPLL_REF_CLKN

DPLL_REF_CLKP

SSC_DPLL_REF_CLKN

SSC_DPLL_REF_CLKP

BCLKN

BCLKP

FOX_PZ94726-3641-41H_HASWELL

ME@

12

CPU_SSC_DPLLVCCPWRGOOD_0_RBUF_CPU_RST#

12

CPU_SSC_DPLL#

Haswell rPGA EDS

MISC

THERMAL CLOCK

PWR

DRAMRST_CNTRL_PCH17

DRAMRST_CNTRL7

DRAMRST_CNTRL_EC44

2 OF 9

AP3

SM_RCOMP_0

SM_RCOMP_1

DDR3L

SM_RCOMP_2

SM_DRAMRST

PRDY

PREQ

TCK

TMS

TRST

JTAG

TDO

DBR

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

BPM_N_4

BPM_N_5

BPM_N_6

BPM_N_7

CADNote:

AvoidstubinthePWRGDpath

whileplacingresistorsRC11&RC26

RC37 0_0402_5%

RC38 0_0402_5%

AR3

AP2

AN3

AR29

AT29

AM34

AN33

AM33

AM31

TDI

AL33

AP33

AR30

AN31

AN29

AP31

AP30

AN28

AP29

AP28

4.99K_0402_1%

@

1 2

1 2

@

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

H_DRAMRST#

XDP_PRDY#

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI_R

XDP_TDO_R

XDP_DBRESET#_R

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM3

XDP_BPM4

XDP_BPM5

XDP_BPM6

XDP_BPM7

RC34

ReserveforDeepS3

@

@

@

@

@

@

@

@

@

VCCPWRGOOD_0_R

12

RC26

10K_0402_5%

@

1 2

DRAMRST_CNTRL

1

1

1

1

1

1

1

1

1

S

RC28 0_0402_5%@

G

TC59

PAD

TC61

PAD

TC60

PAD

TC4

PAD

TC5

PAD

TC6

PAD

TC7

PAD

TC8

PAD

TC9

PAD

Change RC28 to 0ohm jump

1 2

D

13

DDR3_DRAMRST#_RH_DRAMRST#

QC1

2N7002KW_SOT323-3

@

2

1

CC39

0.047U_0402_16V7K

@

2

+1.35V

DDR3COMPENSATIONSIGNALS

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

CADNote:

Tracewidth=12~15mil,Spcing=20mils

Maxtracelength=500mil

1 2

RC5 100_0402_1%

1 2

RC6 75_0402_1%

1 2

RC8 100_0402_1%

PU/PDforJTAGsignals

1

CC38

.1U_0402_10V6-K

@

2

12

12

12

12

12

12

12

DDR3_DRAMRST# 11,12

XDP_DBRESET#_R

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TDO_R

XDP_TCLK

XDP_TRST#

12

RC29

1K_0402_5%

@

RC30

1 2

1K_0402_5%

@

RC14 1K_0402_1%

RC18 51_0402_1%@

RC19 51_0402_1%@

RC20 51_0402_1%@

RC21 51_0402_1%@

RC23 51_0402_1%@

RC24 51_0402_1%@

+3VS

+1.05VS

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2012/12/14

2012/12/14

2012/12/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2012/12/21

2012/12/21

2012/12/21

Title

CPU (2/7) PM, XDP, CLK

CPU (2/7) PM, XDP, CLK

CPU (2/7) PM, XDP, CLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Friday, July 12, 2013

Friday, July 12, 2013

Date: Sheet

Date: Sheet

Date: Sheet

Friday, July 12, 2013

401025

401025

401025

1

of

of

of

661

661

661

1.1

1.1

1.1

Page 7

5

4

3

2

1

Haswell rPGA EDS

@

1

TC10 PAD

DDRA_CLK0#11

DDRA_CLK011

DDRA_CKE011

DDRA_CLK1#11

D D

C C

B B

DDRA_CLK111

DDRA_CKE111

DDRA_CS0#11

DDRA_CS1#11

DDRA_ODT011

DDRA_ODT111

DDRA_BS0#11

DDRA_BS1#11

DDRA_BS2#11

DDRA_RAS#11

DDRA_WE#11

DDRA_CAS#11

DDRA_MA[0..15]11

DDRA_DQS#[0..7]11

DDRA_DQS[0..7]11

DDRA_MA0

DDRA_MA1

DDRA_MA2

DDRA_MA3

DDRA_MA4

DDRA_MA5

DDRA_MA6

DDRA_MA7

DDRA_MA8

DDRA_MA9

DDRA_MA10

DDRA_MA11

DDRA_MA12

DDRA_MA13

DDRA_MA14

DDRA_MA15

DDRA_DQS#0

DDRA_DQS#1

DDRA_DQS#2

DDRA_DQS#3

DDRA_DQS#4

DDRA_DQS#5

DDRA_DQS#6

DDRA_DQS#7

DDRA_DQS0

DDRA_DQS1

DDRA_DQS2

DDRA_DQS3

DDRA_DQS4

DDRA_DQS5

DDRA_DQS6

DDRA_DQS7 +VREF_CA_R

JCPU1C

AC7

RSVD27

U4

SA_CKN0

V4

SA_CKP0

AD9

SA_CKE_0

U3

SA_CKN1

V3

SA_CKP1

AC9

SA_CKE_1

U2

SA_CKN2

V2

SA_CKP2

AD8

SA_CKE_2

U1

SA_CKN3

V1

SA_CKP3

AC8

SA_CKE_3

M7

SA_CS_N_0

L9

SA_CS_N_1

M9

SA_CS_N_2

M10

SA_CS_N_3

M8

SA_ODT_0

L7

SA_ODT_1

L8

SA_ODT_2

L10

SA_ODT_3

V5

SA_BS_0

U5

SA_BS_1

AD1

SA_BS_2

V10

VSS330

U6

SA_RAS

U7

SA_WE

U8

SA_CAS

V8

SA_MA_0

AC6

SA_MA_1

V9

SA_MA_2

U9

SA_MA_3

AC5

SA_MA_4

AC4

SA_MA_5

AD6

SA_MA_6

AC3

SA_MA_7

AD5

SA_MA_8

AC2

SA_MA_9

V6

SA_MA_10

AC1

SA_MA_11

AD4

SA_MA_12

V7

SA_MA_13

AD3

SA_MA_14

AD2

SA_MA_15

AP15

SA_DQS_N_0

AP8

SA_DQS_N_1

AJ8

SA_DQS_N_2

AF3

SA_DQS_N_3

J3

SA_DQS_N_4

E2

SA_DQS_N_5

C5

SA_DQS_N_6

C11

SA_DQS_N_7

AP14

SA_DQS_P_0

AP9

SA_DQS_P_1

AK8

SA_DQS_P_2

AG3

SA_DQS_P_3

H3

SA_DQS_P_4

E3

SA_DQS_P_5

C6

SA_DQS_P_6

C12

SA_DQS_P_7

FOX_PZ94726-3641-41H_HASWELL

ME@

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

3 OF 9

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SM_VREF

AR15

AT14

AM14

AN14

AT15

AR14

AN15

AM15

AM9

AN9

AM8

AN8

AR9

AT9

AR8

AT8

AJ9

AK9

AJ6

AK6

AJ10

AK10

AJ7

AK7

AF4

AF5

AF1

AF2

AG4

AG5

AG1

AG2

J1

J2

J5

H5

H2

H1

J4

H4

F2

F1

D2

D3

D1

F3

C3

B3

B5

E6

A5

D6

D5

E5

B6

A6

E12

D12

B11

A11

E11

D11

B12

A12

AM3

F16

F13

DDRA_DQ0

DDRA_DQ1

DDRA_DQ2

DDRA_DQ3

DDRA_DQ4

DDRA_DQ5

DDRA_DQ6

DDRA_DQ7

DDRA_DQ8

DDRA_DQ9

DDRA_DQ10

DDRA_DQ11

DDRA_DQ12

DDRA_DQ13

DDRA_DQ14

DDRA_DQ15

DDRA_DQ16

DDRA_DQ17

DDRA_DQ18

DDRA_DQ19

DDRA_DQ20

DDRA_DQ21

DDRA_DQ22

DDRA_DQ23

DDRA_DQ24

DDRA_DQ25

DDRA_DQ26

DDRA_DQ27

DDRA_DQ28

DDRA_DQ29

DDRA_DQ30

DDRA_DQ31

DDRA_DQ32

DDRA_DQ33

DDRA_DQ34

DDRA_DQ35

DDRA_DQ36

DDRA_DQ37

DDRA_DQ38

DDRA_DQ39

DDRA_DQ40

DDRA_DQ41

DDRA_DQ42

DDRA_DQ43

DDRA_DQ44

DDRA_DQ45

DDRA_DQ46

DDRA_DQ47

DDRA_DQ48

DDRA_DQ49

DDRA_DQ50

DDRA_DQ51

DDRA_DQ52

DDRA_DQ53

DDRA_DQ54

DDRA_DQ55

DDRA_DQ56

DDRA_DQ57

DDRA_DQ58

DDRA_DQ59

DDRA_DQ60

DDRA_DQ61

DDRA_DQ62

DDRA_DQ63

+V_DDR_REFA_R

+V_DDR_REFB_R

DDRA_DQ[0..63] 11

+VREF_CA_R

@

1

TC11 PAD

DDRB_CLK0#12

DDRB_CLK012

DDRB_CKE012

DDRB_CLK1#12

DDRB_CLK112

DDRB_CKE112

DDRB_CS0#12

DDRB_CS1#12

DDRB_ODT012

DDRB_ODT112

DDRB_BS0#12

DDRB_BS1#12

DDRB_BS2#12

DDRB_RAS#12

DDRB_WE#12

DDRB_CAS#12

DDRB_MA[0..15]12

DDRB_DQS#[0..7]12

DDRB_DQS[0..7]12

DDRB_MA0

DDRB_MA1

DDRB_MA2

DDRB_MA3

DDRB_MA4

DDRB_MA5

DDRB_MA6

DDRB_MA7

DDRB_MA8

DDRB_MA9

DDRB_MA10

DDRB_MA11

DDRB_MA12

DDRB_MA13

DDRB_MA14

DDRB_MA15

DDRB_DQS#0

DDRB_DQS#1

DDRB_DQS#2

DDRB_DQS#3

DDRB_DQS#4

DDRB_DQS#5

DDRB_DQS#6

DDRB_DQS#7

DDRB_DQS0

DDRB_DQS1

DDRB_DQS2

DDRB_DQS3

DDRB_DQS4

DDRB_DQS5

DDRB_DQS6

DDRB_DQS7

AG8

Y4

AA4

AF10

Y3

AA3

AG10

Y2

AA2

AG9

Y1

AA1

AF9

P4

R2

P3

P1

R4

R3

R1

P2

R7

P8

AA9

R10

R6

P6

P7

R8

Y5

Y10

AA5

Y7

AA6

Y6

AA7

Y8

AA10

R9

Y9

AF7

P9

AA8

AG7

AP18

AP11

AP5

AJ3

L3

H9

C8

C14

AP17

AP12

AP6

AK3

M3

H8

C9

C15

FOX_PZ94726-3641-41H_HASWELL

ME@

JCPU1D

RSVD28

SB_CKN0

SB_CKP0

SB_CKE_0

SB_CKN1

SB_CKP1

SB_CKE_1

SB_CKN2

SB_CKP2

SB_CKE_2

SB_CKN3

SB_CKP3

SB_CKE_3

SB_CS_N_0

SB_CS_N_1

SB_CS_N_2

SB_CS_N_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_BS_0

SB_BS_1

SB_BS_2

VSS331

SB_RAS

SB_WE

SB_CAS

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_DQS_N_0

SB_DQS_N_1

SB_DQS_N_2

SB_DQS_N_3

SB_DQS_N_4

SB_DQS_N_5

SB_DQS_N_6

SB_DQS_N_7

SB_DQS_P_0

SB_DQS_P_1

SB_DQS_P_2

SB_DQS_P_3

SB_DQS_P_4

SB_DQS_P_5

SB_DQS_P_6

SB_DQS_P_7

Haswell rPGA EDS

4 OF 9

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

AR18

AT18

AM17

AM18

AR17

AT17

AN17

AN18

AT12

AR12

AN12

AM11

AT11

AR11

AM12

AN11

AR5

AR6

AM5

AM6

AT5

AT6

AN5

AN6

AJ4

AK4

AJ1

AJ2

AM1

AN1

AK2

AK1

L2

M2

L4

M4

L1

M1

L5

M5

G7

J8

G8

G9

J7

J9

G10

J10

A8

B8

A9

B9

D8

E8

D9

E9

E15

D15

A15

B15

E14

D14

A14

B14

DDRB_DQ0

DDRB_DQ1

DDRB_DQ2

DDRB_DQ3

DDRB_DQ4

DDRB_DQ5

DDRB_DQ6

DDRB_DQ7

DDRB_DQ8

DDRB_DQ9

DDRB_DQ10

DDRB_DQ11

DDRB_DQ12

DDRB_DQ13

DDRB_DQ14

DDRB_DQ15

DDRB_DQ16

DDRB_DQ17

DDRB_DQ18

DDRB_DQ19

DDRB_DQ20

DDRB_DQ21

DDRB_DQ22

DDRB_DQ23

DDRB_DQ24

DDRB_DQ25

DDRB_DQ26

DDRB_DQ27

DDRB_DQ28

DDRB_DQ29

DDRB_DQ30

DDRB_DQ31

DDRB_DQ32

DDRB_DQ33

DDRB_DQ34

DDRB_DQ35

DDRB_DQ36

DDRB_DQ37

DDRB_DQ38

DDRB_DQ39

DDRB_DQ40

DDRB_DQ41

DDRB_DQ42

DDRB_DQ43

DDRB_DQ44

DDRB_DQ45

DDRB_DQ46

DDRB_DQ47

DDRB_DQ48

DDRB_DQ49

DDRB_DQ50

DDRB_DQ51

DDRB_DQ52

DDRB_DQ53

DDRB_DQ54

DDRB_DQ55

DDRB_DQ56

DDRB_DQ57

DDRB_DQ58

DDRB_DQ59

DDRB_DQ60

DDRB_DQ61

DDRB_DQ62

DDRB_DQ63

DDRB_DQ[0..63] 12

DRAMRST_CNTRL6

+VREF_DQ_DIMMA_R

+VREF_DQ_DIMMB_R

A A

5

4

Change RC43,RC44 to 0ohm jump

DRAMRST_CNTRL

2N7002KW_SOT323-3

RC43 0_0402_5%@

RC44 0_0402_5%@

2N7002KW_SOT323-3

DRAMRST_CNTRL

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

QC3

1 3

D

1 2

1 2

1 3

D

QC4

3

2

G

@

S

+V_DDR_REFA_R

+V_DDR_REFB_R

12

S

@

G

2

2012/12/14

2012/12/14

2012/12/14

RC45

1K_0402_1%

@

12

RC46

1K_0402_1%

@

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2012/12/21

2012/12/21

2012/12/21

Title

Title

Title

CPU (3/7) DDRIII

CPU (3/7) DDRIII

CPU (3/7) DDRIII

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Friday, July 12, 2013

Friday, July 12, 2013

Date: Sheet

Date: Sheet

Date: Sheet

Friday, July 12, 2013

401025

401025

401025

1

of

of

of

761

761

761

1.1

1.1

1.1

Page 8

5

4

3

2

1

+VCCIO_OUT

2

G

12

RC47

10K_0402_5%

1 2

13

D

S

+VCCIOA_OUT

RC4924.9_0402_1%

EDP_HPD_IN#

QC5

2N7002KW_SOT323-3

HPDINVERSIONFOREDP

D D

HDMI D2

HDMI D1

HDMI D0

HDMI CLK

@

1 2

PCH_PWROK15,44

C C

RC50

6.04K_0402_1%

HDMI_TX2-35

HDMI_TX1-35

HDMI_TX0-35

HDMI_CLK-35

VCCST_PWRGD

12

RC75

2.67K_0402_1%

@

HDMI_TX2+35

HDMI_TX1+35

HDMI_TX0+35

HDMI_CLK+35

HDMI_TX2HDMI_TX2+

HDMI_TX1HDMI_TX1+

HDMI_TX0HDMI_TX0+

HDMI_CLKHDMI_CLK+

JCPU1H

T28

DDIB_TXN0

U28

DDIB_TXP0

T30

DDIB_TXN1

U30

DDIB_TXP1

U29

DDIB_TXN2

V29

DDIB_TXP2

U31

DDIB_TXN3

V31

DDIB_TXP3

T34

DDIC_TXN0

U34

DDIC_TXP0

U35

DDIC_TXN1

V35

DDIC_TXP1

U32

DDIC_TXN2

T32

DDIC_TXP2

U33

DDIC_TXN3

V33

DDIC_TXP3

P29

DDID_TXN0

R29

DDID_TXP0

N28

DDID_TXN1

P28

DDID_TXP1

P31

DDID_TXN2

R31

DDID_TXP2

N30

DDID_TXN3

P30

DDID_TXP3

FOX_PZ94726-3641-41H_HASWELL

ME@

Haswell rPGA EDS

DDI

eDP

EDP_AUXN

EDP_AUXP

EDP_HPD

EDP_RCOMP

EDP_DISP_UTIL

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

FDI_TXN_0

FDI_TXP_0

FDI_TXN_1

FDI_TXP_1

8 OF 9

M27

N27

P27

E24

R27

P35

R35

N34

P34

P33

R33

N32

P32

CPU_EDP_AUX#

CPU_EDP_AUX

EDP_HPD_IN#

EDP_COMP

CPU_EDP_TX0CPU_EDP_TX0+

CPU_EDP_TX1CPU_EDP_TX1+

FDI_CTX_PRX_N0

FDI_CTX_PRX_P0

FDI_CTX_PRX_N1

FDI_CTX_PRX_P1

CPU_EDP_AUX# 34

CPU_EDP_AUX 34

1

PAD@

TC12

CPU_EDP_TX0- 34

CPU_EDP_TX0+ 34

CPU_EDP_TX1- 34

CPU_EDP_TX1+ 34

FDI_CTX_PRX_N0 15

FDI_CTX_PRX_P0 15

FDI_CTX_PRX_N1 15

FDI_CTX_PRX_P1 15

CPU_EDP_HPD34

12

RC48

100K_0402_5%

COMPENSATIONPUFOReDP

EDP_COMP

CADNote:Tracewidth=20mils,Spacing=25mil,

Maxlength=100mils.

ReserveforDesignGuideandCRBrecommended.

CFG3

Haswell rPGA EDS

9 OF 9

12

RC192

1K_0402_1%

@

C23

RSVD_TP12

B23

RSVD_TP13

D24

RSVD_TP14

D23

RSVD_TP15

AT31

CFG_RCOMP

CFG_16

CFG_18

CFG_17

CFG_19

RSVD4

FC_G6

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD_TP16

RSVD_TP17

RSVD_TP18

VSS318

VSS319

VSS320

VSS321

NC

AR21

AR23

AP21

AP23

AR33

G6

AM27

AM26

F5

AM2

K6

E18

U10

P10

B1

A2

AR1

E21

E20

AP27

AR26

AL31

AL32

CFG_RCOMPCFG2

CFG16

CFG18

CFG17

CFG19

VCCST_PWRGD

PHYSICAL_DEBUG_ENABLED(DFXPRIVACY)

0:ENABLED

CFG3

SETDFXENABLEDBITINDEBUG

INTERFACEMSR

1:DISABLED

*

1

PAD@

TC18

1

PAD@

TC19

1

PAD@

TC20

1

PAD@

TC16

1

PAD@

TC25

1

PAD@

TC29

1

PAD@

TC24

1

PAD@

TC27

1

PAD@

TC31

1

PAD@

TC33

1

PAD@

TC35

1

PAD@

TC36

1

PAD@

TC38

1

PAD@

TC40

1

PAD@

TC41

1

PAD@

TC44

1

PAD@

TC46

1

PAD@

TC50

1

PAD@

TC52

1

PAD@

TC55

1

PAD@

TC57

CFG[6:5]

*

CFG5

CFG6

12

RC51

1K_0402_1%

@

12

RC52

1K_0402_1%

PCIEPortBifurcationStraps

11:(Default)x16‐Device1functions1and2disabled

10:x8,x8‐Device1function1enabled;function2

disabled

01:Reserved‐(Device1function1disabled;function

2enabled)

00:x8,x4,x4‐Device1functions1and2enabled

12

RC55

1K_0402_1%

@

PEGDEFERTRAINING

1:(Default)PEGTrainimmediately

*

CFG7

followingxxRESETBdeassertion

0:PEGWaitforBIOSfortraining

NeedconfirmwithIntelifthisreservedcircuitcanbedeleted.

JCPU1I

1

PAD @

CFGSTRAPSforCPU

12

RC53

1K_0402_1%@

B B

A A

PEGStaticLaneReversal‐CFG2isforthe16x

1:(Default)NormalOperation;Lane#

*

CFG2

definitionmatchessocketpinmapdefinition

0:LaneReversed

CFG4 CFG7

12

RC54

1K_0402_1%

DisplayPortPresenceStrap

1:Disabled;NoPhysicalDisplayPort

CFG4

attachedtoEmbeddedDisplayPort

0:Enabled;AnexternalDisplayPortdeviceis

*

connectedtotheEmbeddedDisplayPort

TC13

1

PAD @

TC14

1

PAD @

TC15

1

PAD @

TC21

1

PAD @

TC22

1

PAD @

TC17

1

PAD @

TC23

1

PAD @

TC26

1

PAD @

TC28

TC30

TC32

TC34

TC37

TC39

TC56

TC58

TC43

TC45

TC47

TC48

TC49

TC51

TC53

TC54

RC56 49.9_0402_1%

RC57 49.9_0402_1%

RC58 49.9_0402_1%

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

+VCC_CORE

12

12

12

H_CPU_TESTLO_G26

H_CPU_TESTLO_W34

H_CPU_TESTLO_G26

H_CPU_TESTLO_W34

CFG_RCOMP

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

AT1

RSVD_TP1

AT2

RSVD_TP2

AD10

RSVD1

A34

RSVD_TP3

A35

RSVD_TP4

W29

RSVD_TP5

W28

RSVD_TP6

G26

TESTLO_G26

W33

VSS317

AL30

RSVD2

AL29

RSVD3

F25

VCC104

C35

RSVD_TP7

B35

RSVD_TP8

AL25

RSVD_TP9

W30

RSVD_TP10

W31

RSVD_TP11

W34

TESTLO_W34

AT20

CFG_0

AR20

CFG_1

AP20

CFG_2

AP22

CFG_3

AT22

CFG_4

AN22

CFG_5

AT25

CFG_6

AN23

CFG_7

AR24

CFG_8

AT23

CFG_9

AN20

CFG_10

AP24

CFG_11

AP26

CFG_12

AN25

CFG_13

AN26

CFG_14

AP25

CFG_15

FOX_PZ94726-3641-41H_HASWELL

ME@

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2012/12/14

2012/12/14

2012/12/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2012/12/21

2012/12/21

2012/12/21

Title

CPU (4/7) RSVD,CFG

CPU (4/7) RSVD,CFG

CPU (4/7) RSVD,CFG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Friday, July 12, 2013

Friday, July 12, 2013

Date: Sheet

Date: Sheet

Date: Sheet

Friday, July 12, 2013

401025

401025

401025

1

of

of

of

861

861

861

1.1

1.1

1.1

Page 9

5

4

3

2

1

Haswell rPGA EDS

JCPU1E

D D

CC49 .1U_0402_10V6-K

CC50 .1U_0402_10V6-K

75_0402_1%

RC66

130_0402_1%

+1.05VS

12

RC67

150_0402_1%

CPU_PWR_DEBUG#

12

RC68

10K_0402_5%

@

+VCCIO_OUT

+VCCIO_OUT

12

RC76

12

+VCCIO_OUT

+VCCIO2PCH

RC65 43_0402_5%

+1.05VS

1 2

RC63 0_0603_5%@

1 2

RC64 0_0603_5%@

C C

VR_SVID_ALRT#59

VR_SVID_CLK59

VR_SVID_DAT59

B B

TC65

TC64

TC66

TC67

1 2

1 2

TC68

TC69

TC70

TC71

TC72

TC73

TC74

TC75

1 2

TC76

TC77

TC78

TC79

1

1

1

1

@

@

1

1

1

1

1

1

1

1

CPU_PWR_DEBUG#

1

1

1

1

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

PAD @

+1.35V_CPU_VDDQ+1.35V

+VCC_CORE

VCCSENSE_R

+VCCIO_OUT

+VCCIO2PCH

+VCCIOA_OUT

VR_SVID_ALRT#_R

VR_SVID_CLK

VR_SVID_DAT

+VCC_CORE

needconnecttopower

K27

RSVD15

L27

RSVD16

T27

RSVD17

V27

RSVD18

AB11

VDDQ1

AB2

VDDQ2

AB5

VDDQ3

AB8

VDDQ4

AE11

VDDQ5

AE2

VDDQ6

AE5

VDDQ7

AE8

VDDQ8

AH11

VDDQ9

K11

VDDQ10

N11

VDDQ11

N8

VDDQ12

T11

VDDQ13

T2

VDDQ14

T5

VDDQ15

T8

VDDQ16

W11

VDDQ17

W2

VDDQ18

W5

VDDQ19

W8

VDDQ20

N26

RSVD19

K26

VCC103

AL27

RSVD20

AK27

RSVD21

AL35

VCC_SENSE

E17

RSVD22

AN35

VCCIO_OUT

A23

FC_A23

F22

VCOMP_OUT

W32

RSVD23

AL16

RSVD24

J27

RSVD25

AL13

RSVD26

AM28

VIDALERT

AM29

VIDSCLK

AL28

VIDSOUT

AP35

VSS317

H27

PWR_DEBUG

AP34

VSS318

AT35

RSVD_TP19

AR35

RSVD_TP20

AR32

IVR_ERROR

AL26

IST_TRIGGER

AT34

VSS319

AL22

VSS320

AT33

VSS321

AM21

VSS322

AM25

VSS323

AM22

VSS324

AM20

VSS325

AM24

VSS326

AL19

VSS327

AM23

VSS328

AT32

VSS329

Y25

VCC1

Y26

VCC2

Y27

VCC3

Y28

VCC4

Y29

VCC5

Y30

VCC6

Y31

VCC7

Y32

VCC8

Y33

VCC9

Y34

VCC10

Y35

VCC11

FOX_PZ94726-3641-41H_HASWELL

ME@

5 OF 9

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

AA26

AA28

AA34

AA30

AA32

AB26

AB29

AB25

AB27

AB28

AB30

AB31

AB33

AB34

AB32

AC26

AB35

AC28

AD25

AC30

AD28

AC32

AD31

AC34

AD34

AD26

AD27

AD29

AD30

AD32

AD33

AD35

AE26

AE32

AE28

AE30

AG28

AG34

AE34

AF25

AF26

AF27

AF28

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AG26

AH26

AH29

AG30

AG32

AH32

AH35

AH25

AH27

AH28

AH30

AH31

AH33

AH34

AJ25

AJ26

AJ27

AJ28

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

G25

H25

J25

K25

L25

M25

N25

P25

R25

T25

U25

U26

V25

V26

W26

W27

+VCC_CORE

+1.35V_CPU_VDDQ

VCC_SENSE

VCCSENSE59

VSSSENSE59

VDDQDECOUPLING

10U_0603_6.3V6M

1

2

22U_0805_6.3V6M

1

2

CC51

CC63

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CC52

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

CC64

2

2

+VCC_CORE

12

RC59

100_0402_1%

CADNote:RC59SHOULDBEPLACEDCLOSETOCPU

12

VCCSENSE VCCSENSE_R

@

RC600_0402_5%

CADNote:RC62SHOULDBEPLACEDCLOSETOCPU

12

VSSSENSE VSSSENSE_R

CC53

CC65

12

RC62

100_0402_1%

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

1

CC55

CC54

2

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

CC66

1

CC67

2

2

1

2

@

RC800_0402_5%

Change RC60,RC61 to 0ohm jump

10U_0603_6.3V6M

CC57

CC69

10U_0603_6.3V6M

1

1

CC58

CC59

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

CC71

CC70

2

2

10U_0603_6.3V6M

10U_0603_6.3V6M

1

CC56

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

CC68

2

VSSSENSE_R 10

Power

@

10U_0603_6.3V6M

330U_2.5V_M

1

CC61

1

+

CC60

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

1

CC73

CC72

2

2

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2012/12/14

2012/12/14

2012/12/14

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2012/12/21

2012/12/21

2012/12/21

Title

CPU (5/7) PWR, BYPASS

CPU (5/7) PWR, BYPASS

CPU (5/7) PWR, BYPASS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Friday, July 12, 2013

Friday, July 12, 2013

Friday, July 12, 2013

Date: Sheet

Date: Sheet

Date: Sheet

401025

401025

401025

1

961

961

961

of

of

of

1.1

1.1

1.1

Page 10

5

Haswell rPGA EDS

JCPU1F

A10

VSS1

A13

VSS2

A16

VSS3

A19

VSS4

A22

VSS5

A25

VSS6

A27

VSS7

A29

VSS8

A3

VSS9

A31

VSS10

A33

VSS11

A4

D D

C C

B B

VSS12

A7

VSS13

AA11

VSS14

AA25

VSS15

AA27

VSS16

AA31

VSS17

AA29

VSS18

AB1

VSS19

AB10

VSS20

AA33

VSS21

AA35

VSS22

AB3

VSS23

AC25

VSS24

AC27

VSS25

AB4

VSS26

AB6

VSS27

AB7

VSS28

AB9

VSS29

AC11

VSS30

AD11

VSS31

AC29

VSS32

AC31

VSS33

AC33

VSS34

AC35

VSS35

AD7

VSS36

AE1

VSS37

AE10

VSS38

AE25

VSS39

AE29

VSS40

AE3

VSS41

AE27

VSS42

AE35

VSS43

AE4

VSS44

AE6

VSS45

AE7

VSS46

AE9

VSS47

AF11

VSS48

AF6

VSS49

AF8

VSS50

AG11

VSS51

AG25

VSS52

AE31

VSS53

AG31

VSS54

AE33

VSS55

AG6

VSS56

AH1

VSS57

AH10

VSS58

AH2

VSS59

AG27

VSS60

AG29

VSS61

AH3

VSS62

AG33

VSS63

AG35

VSS64

AH4

VSS65

AH5

VSS66

AH6

VSS67

AH7

VSS68

AH8

VSS69

AH9

VSS70

AJ11

VSS71

AJ5

VSS72

AK11

VSS73

AK25

VSS74

AK26

VSS75

AK28

VSS76

AK29

VSS77

AK30

VSS78

AK32

VSS79

E19

VSS80

FOX_PZ94726-3641-41H_HASWELL

ME@

For Deep S3

+3VALW

12

RC70

100K_0402_5%

QC8

2

G

@

RUN_ON_CPU1.5VS3#

13

D

@

S

@

RC73

SUSP40,46,55

A A

CPU1.5V_S3_GATE44

5

1 2

0_0402_5%

2N7002KW_SOT323-3

6 OF 9

2

G

4

AK34

VSS81

AK5

VSS82

AL1

VSS83

AL10

VSS84

AL11

VSS85

AL12

VSS86

AL14

VSS87

AL15

VSS88

AL17

VSS89

AL18

VSS90

AL2

VSS91

AL20

VSS92

AL21

VSS93

AL23

VSS94

E22

VSS95

AL3

VSS96

AL4

VSS97

AL5

VSS98

AL6

VSS99

AL7

VSS100

AL8

VSS101

AL9

VSS102

AM10

VSS103

AM13

VSS104

AM16

VSS105

AM19

VSS106

E25

VSS107

AM32

VSS108

AM4

VSS109

AM7

VSS110

AN10

VSS111

AN13

VSS112

AN16

VSS113

AN19

VSS114

AN2

VSS115

AN21

VSS116

AN24

VSS117

AN27

VSS118

AN30

VSS119

AN34

VSS120

AN4

VSS121

AN7

VSS122

AP1

VSS123

AP10

VSS124

AP13

VSS125

AP16

VSS126

AP19

VSS127

AP4

VSS128

AP7

VSS129

W25

VSS130

AR10

VSS131

AR13

VSS132

AR16

VSS133

AR19

VSS134

AR2

VSS135

AR22

VSS136

AR25

VSS137

AR28

VSS138

AR31

VSS139

AR34

VSS140

AR4

VSS141

AR7

VSS142

AT10

VSS143

AT13

VSS144

AT16

VSS145

AT19

VSS146

AT21

VSS147

AT24

VSS148

AT27

VSS149

AT3

VSS150

AT30

VSS151

AT4

VSS152

AT7

VSS153

B10

VSS154

B13

VSS155

B16

VSS156

B19

VSS157

B2

VSS158

B22

VSS159

+VSB

RC69 need to check on SDV

12

RC69

100K_0402_5%

@

RUN_ON_CPU1.5VS3

13

D

QC6

2N7002KW_SOT323-3

S

@

RUN_ON_CPU1.5VS3# 6

4

3

+1.35V_CPU_VDDQ

J1

2

112

JUMP_43X79

+1.35V +1.35V_CPU_VDDQ

QC9

1 2

470K_0402_5%

12

RC74

470K_0402_5%

@

1 2

CC74 .1U_0402_10V6-K@

1 2

CC75 .1U_0402_10V6-K@

1 2

CC76 .1U_0402_10V6-K@

1 2

CC77 .1U_0402_10V6-K@

8

7

6

5

4

@

RC72

@

AO4304L

Vgs=10V,Id=18A,

Rds<6.7m ohm

P/N: SB00000RV00

1

CC78

.01U_0402_16V7-K

@

2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.