Page 1

A

1 1

B

C

D

E

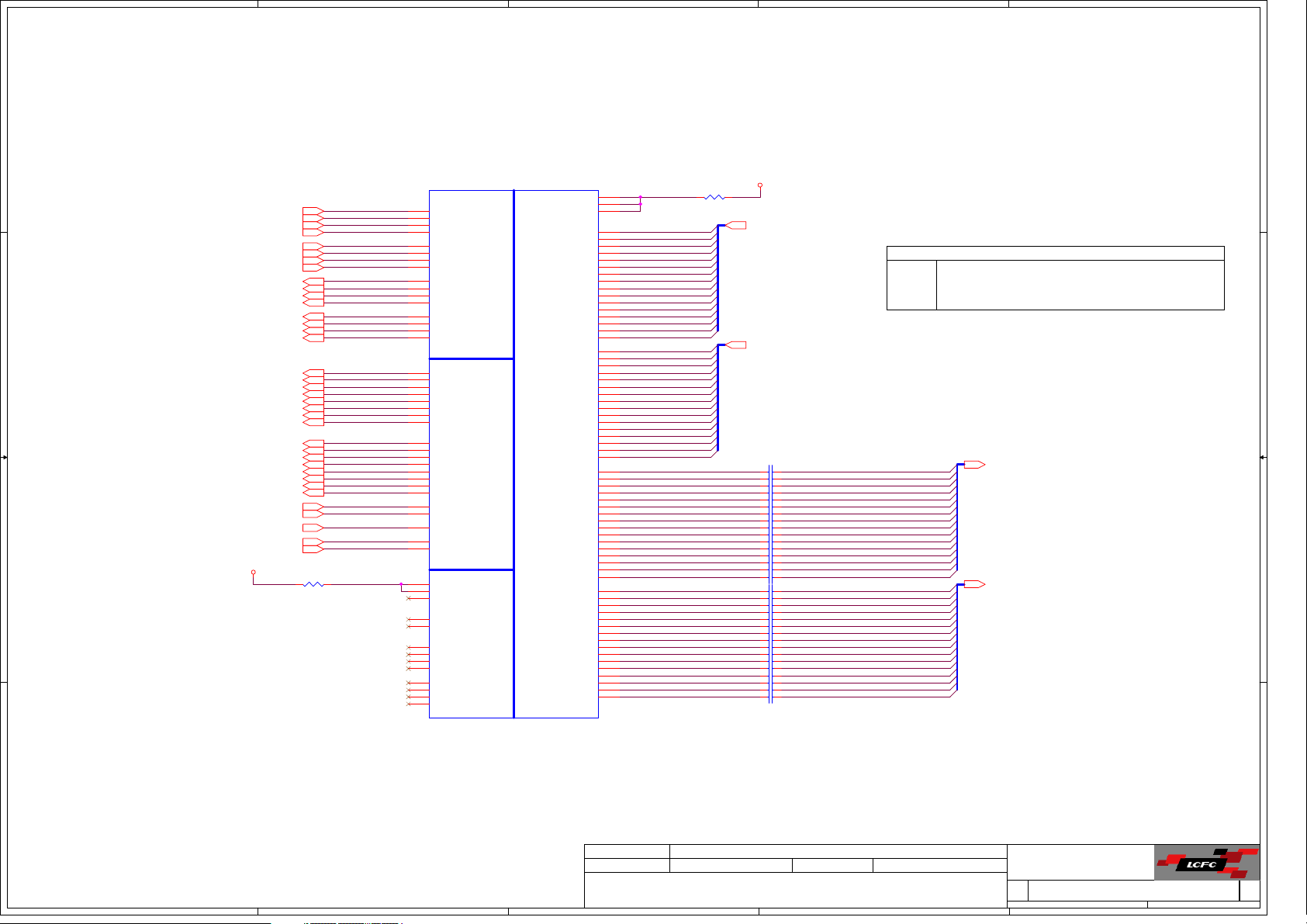

QIQY5

Whisky3.0 (Y400S)

2 2

NM-A141 Rev0.2 Schematic

Intel IVY Bridge Processor with DDRIII + Panther Point PCH

3 3

4 4

A

nVIDIA N14P GT + 2nd VGA N14P GT

2012-10-25-Rev0.2

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

2011/11/ 01

2011/11/ 01

2011/11/ 01

C

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2012/12/ 31

2012/12/ 31

2012/12/ 31

D

Title

Title

Title

COVER PAGE

COVER PAGE

COVER PAGE

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Monday, January 14, 2013

Monday, January 14, 2013

Monday, January 14, 2013

Y400S-NM-A141

Y400S-NM-A141

Y400S-NM-A141

E

1 65

1 65

1 65

of

of

of

1.0

1.0

1.0

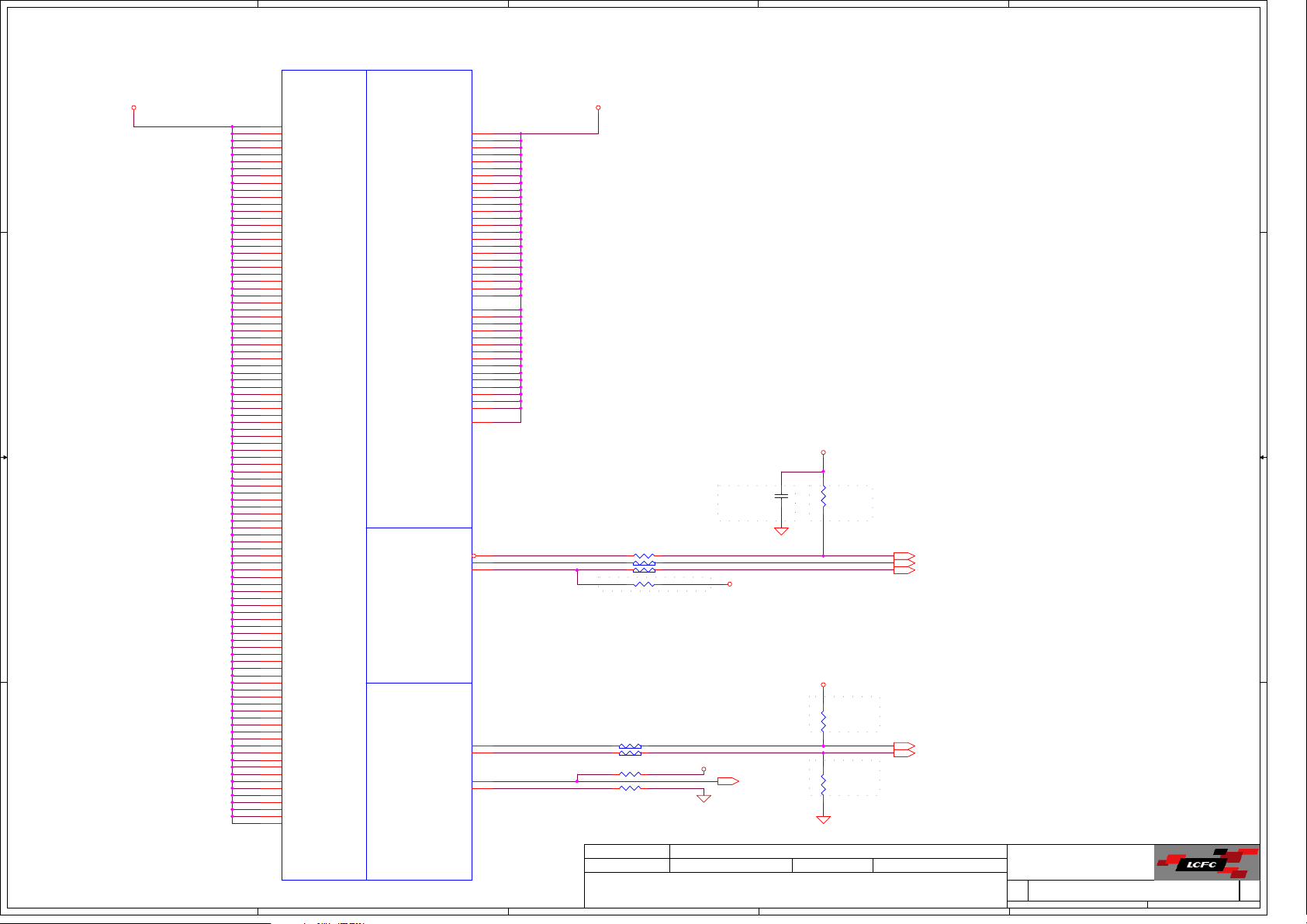

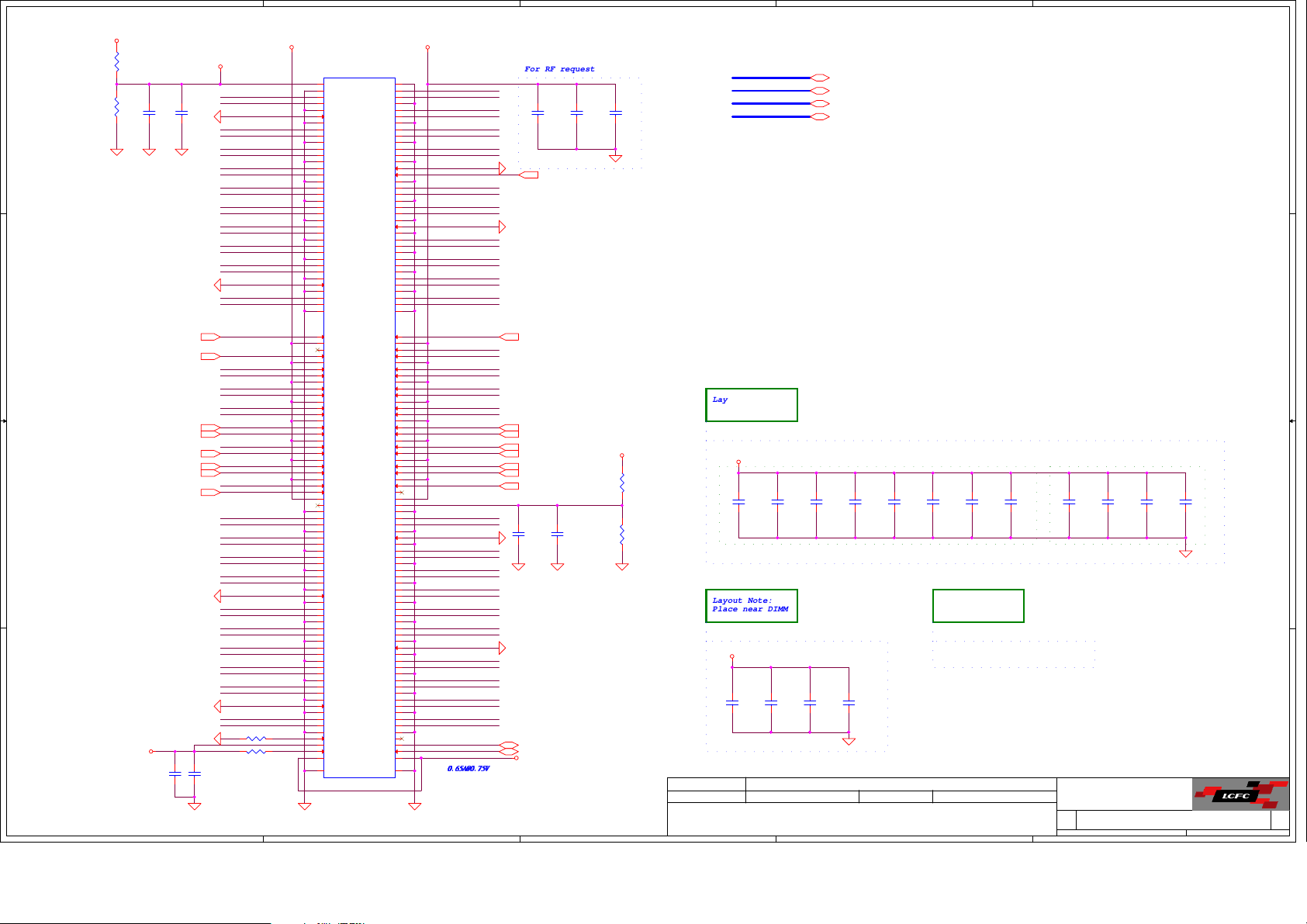

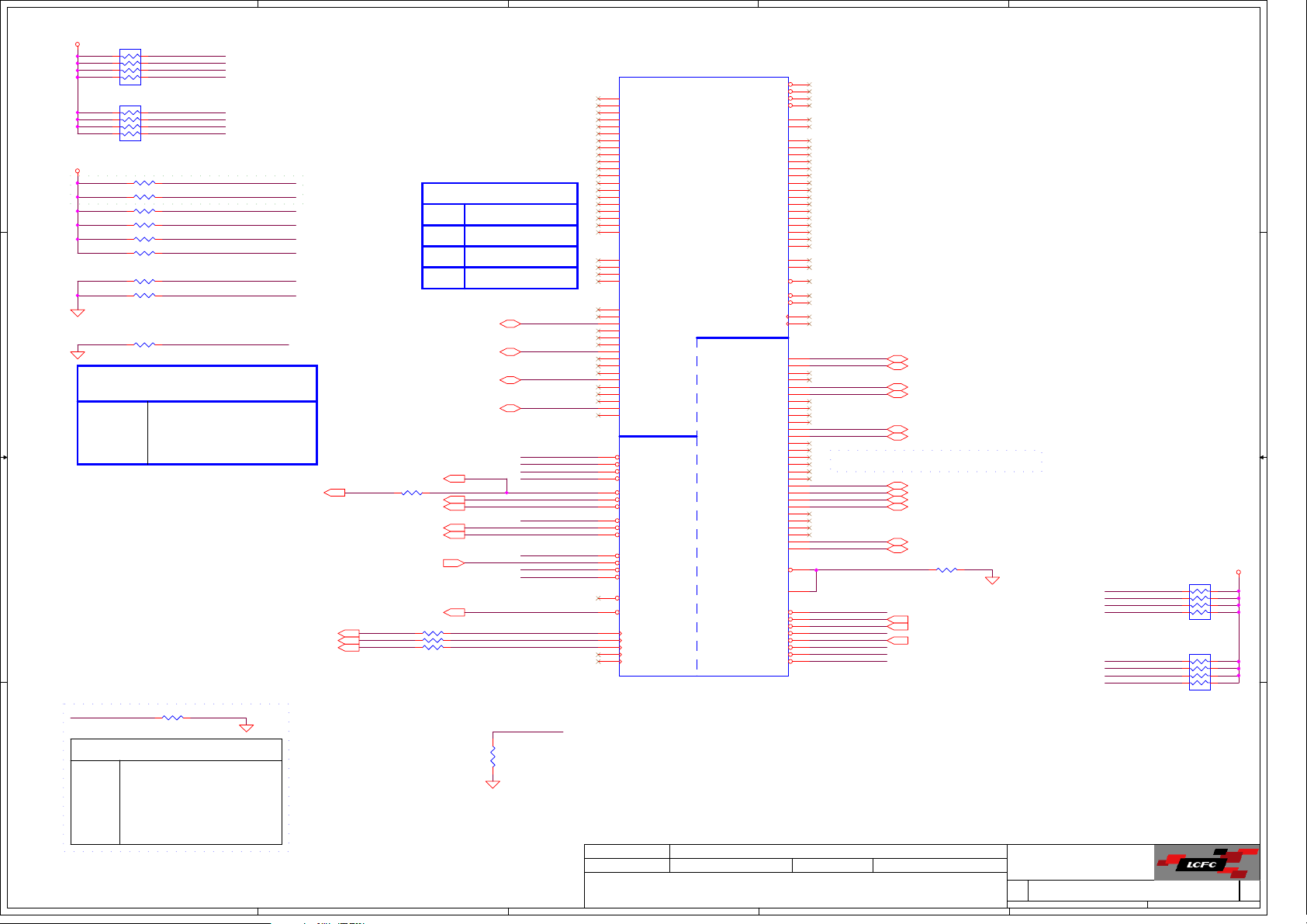

Page 2

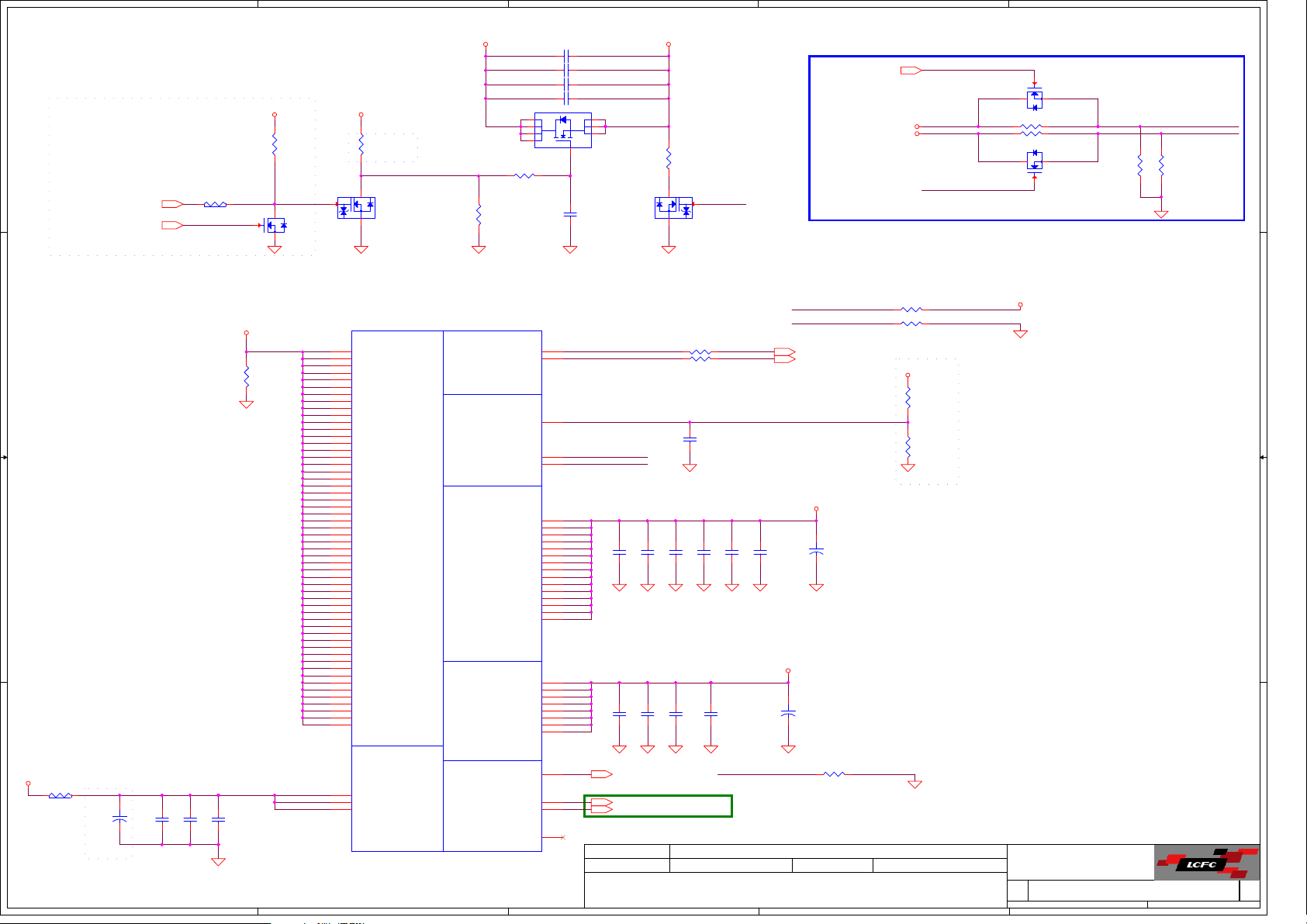

A

B

C

D

E

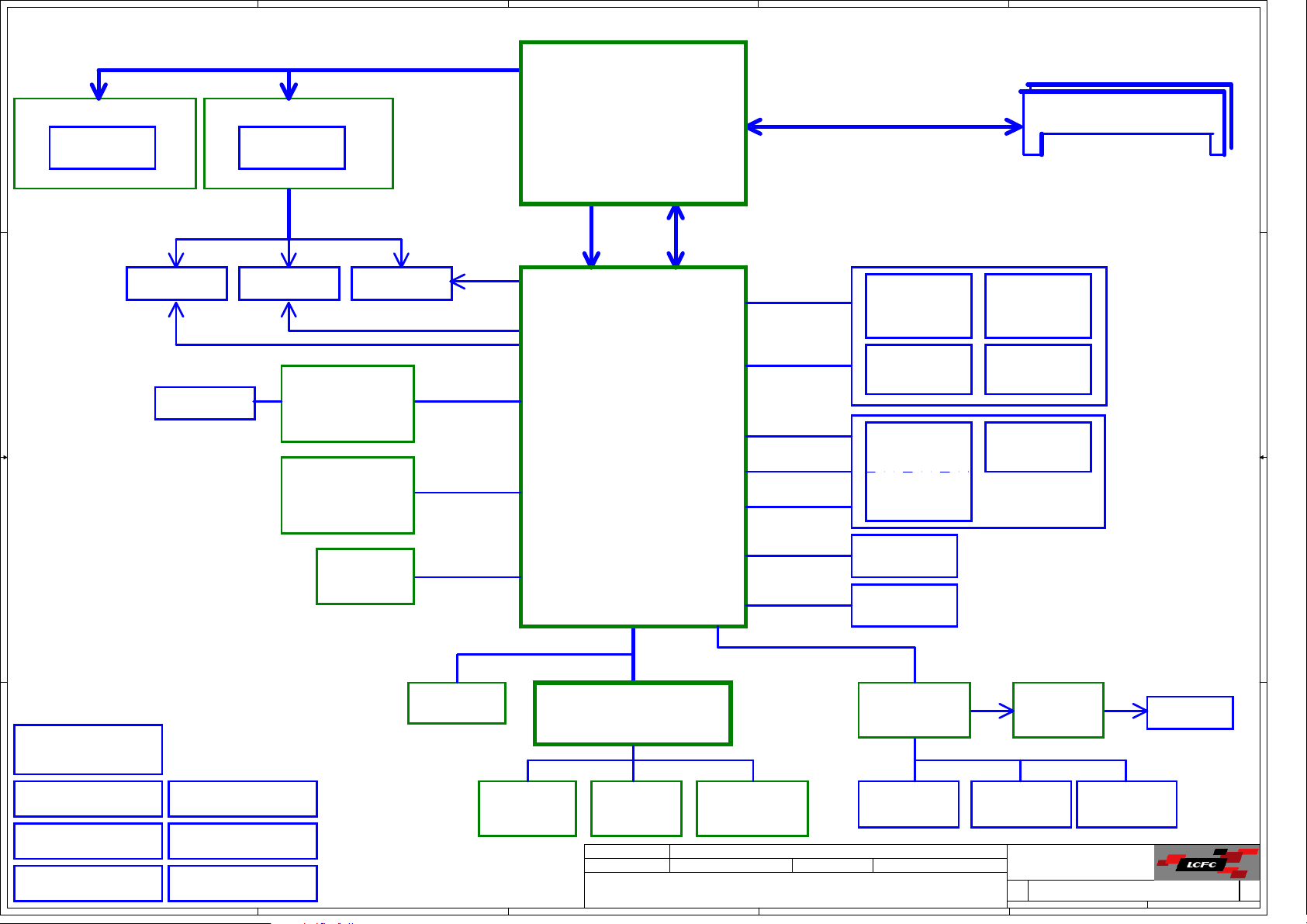

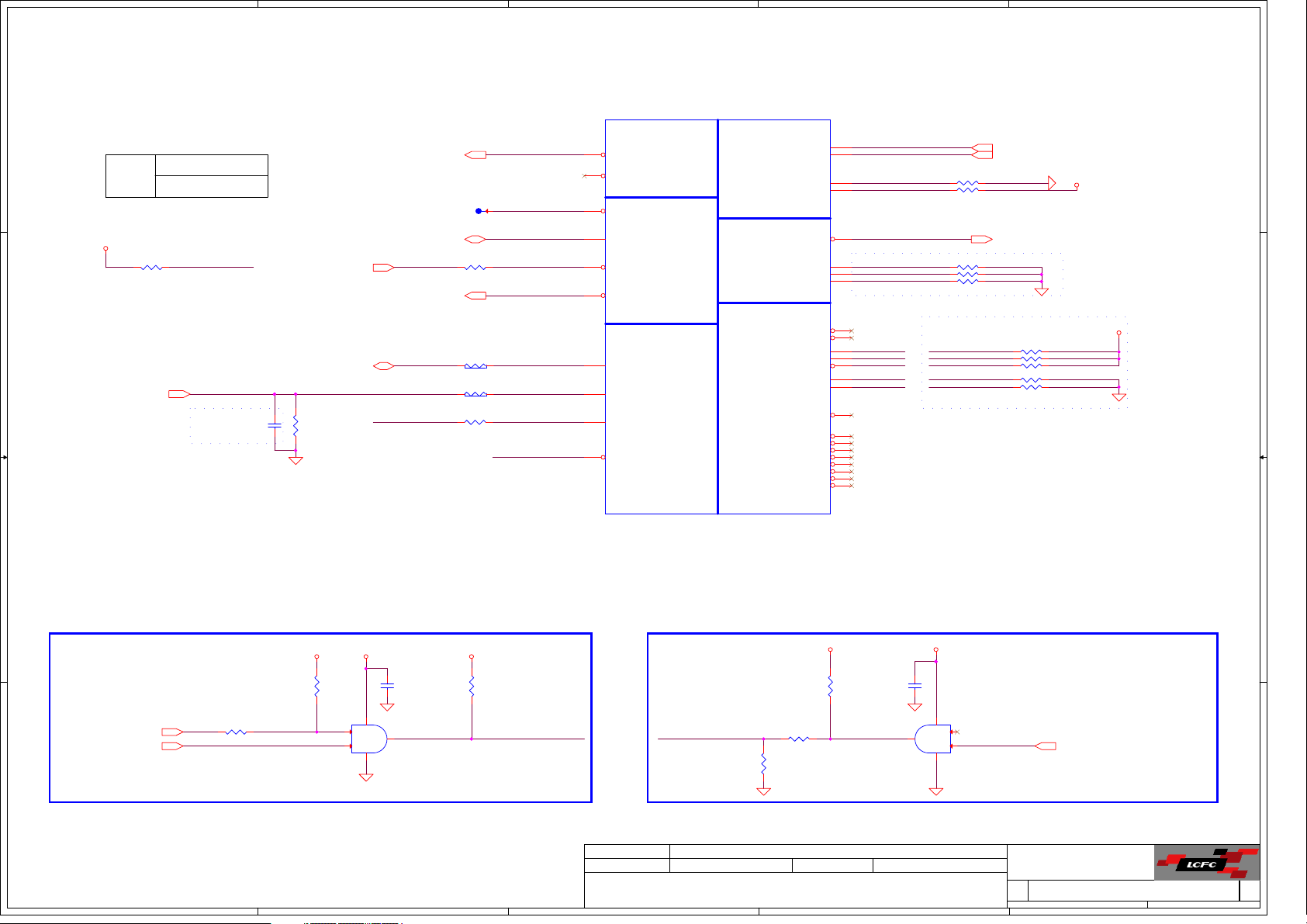

PCI-Express 16X Gen3

EG 8~15

2nd VGA, N14P-GT1

1 1

Sub/B

VRAM 64*32

GDDR5* 8

Page 32 Page 23,24,25,26,27,28,29,30,31

VRAM 64*32

GDDR5* 8

PEG 0~7P

N14P-GT1

Intel CPU

Ivy Bridge

rPGA-989

37.5mm*37.5mm

age 5,6,7,8,9,10,11

P

Memory BUS (DDRIII)

Dual Channel

1.5V DDRIII 1066/1333/1600 MT/s

DDR3-SO-DIMM X2

BANK 0, 1, 2, 3

UP TO 16G

FDI *8

2.7GT/s

HDMI Conn.

Page 36 P

HDMI1.4b

2 2

RJ45 Conn.

Page 39

CRT Conn.

age 35 Page 34

Atheros

A

R8161 1G

AR8151 1G

PCIe port 1

LVDS Conn.

Page 38

PCIe Gen1 1x

1.5V 5GT/s

Intel PCH

anther Point

P

FCBGA-989 Balls

25mm*25mm

CardReader

JMB38C

SD/MMC/MS/XD

PCIe port 4

3 3

(4

Page 44

SPI ROM

MB+2MB)

Page 14

PCIe Gen1 1x

1.5V 5GT/s

SPI BUS

3.3V 33MHz

Page 14,15,16,17,18,19,20,21,22

LPC BUS

3.3V 33MHz

DMI *4

5GT/s

USB 2.0 4x

5V

480MHz

USB 3.0 2x

5V 5GT/s

USB 2.0 1x

5V 480MHz

PCIe Gen1 1x

5V 480MHz

SATA Gen3 Port 0

5V 6GHz(600MB/s)

SATA Gen3 Port 1

5V 6GHz(600MB/s)

SATA Gen1 Port2

3GHz(300MB/s)

5V

HD Audio

24MHz

3.3V

USB Left

USB 2.0 Port 2

USB 3.0 Port 2

Int. Camera

USB 3.0 Port 0

PCIeMini Card

AN

WL

PCIeMini Card

WLAN

SATA HDD

SATA ODD

USB Right

USB 2.0 Port 9

Page 48 Page 49

Page 34

USB 2.0 Port 5, Cha

Sub/B

BT

SB 2.0 Port 13

U

mSATA SSD

PCIe Port 2

page 37

USB Port 10

page 37

SATA Port 1

page 41

SATA Port 1

page 41

Page 47

SATA Port 0

page 37

Debug Port

Page 45

Power Circuit DC/DC

Page 52,53 ,54,55,56, 57,

58,59,60,6 1,62

4 4

DC/DC Interface CKT.

POWER/B Conn. AUDIO, USB/B Conn.

ODD/B Conn.

Page 51

Page 40 Page 49

page 41

A

RTC CKT.

NOVO/B Conn.

Page 52

Page 40

Touch Pad

Page 46

B

EC

E IT8580E-HX

IT

Page 45

Int.KBD

Page 46

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

C

Thermal Sensor

EMC 1403

Page 40

LC Future Center Secret Data

LC Future Center Secret Data

2011/11/01

2011/11/01

2011/11/01

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Codec

A

LC269Q-VC3

Int. MIC Conn.

(JCMOS Conn.)

Page 34 Page 49

2012/12/31

2012/12/31

2012/12/31

D

age 42

P

AMP

MA

X98400B

Page 43

Ext. MIC Conn.

Su

b/B

Title

Title

Title

BlOCK DIAGRAM

BlOCK DIAGRAM

BlOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Monday, January 14, 2013

Monday, January 14, 2013

Monday, January 14, 2013

HP Conn.

ub/B

S

Y400S-NM-A141

Y400S-NM-A141

Y400S-NM-A141

SPK Conn.

Page 49

E

Page 43

of

of

of

2 65

2 65

2 65

1.0

1.0

1.0

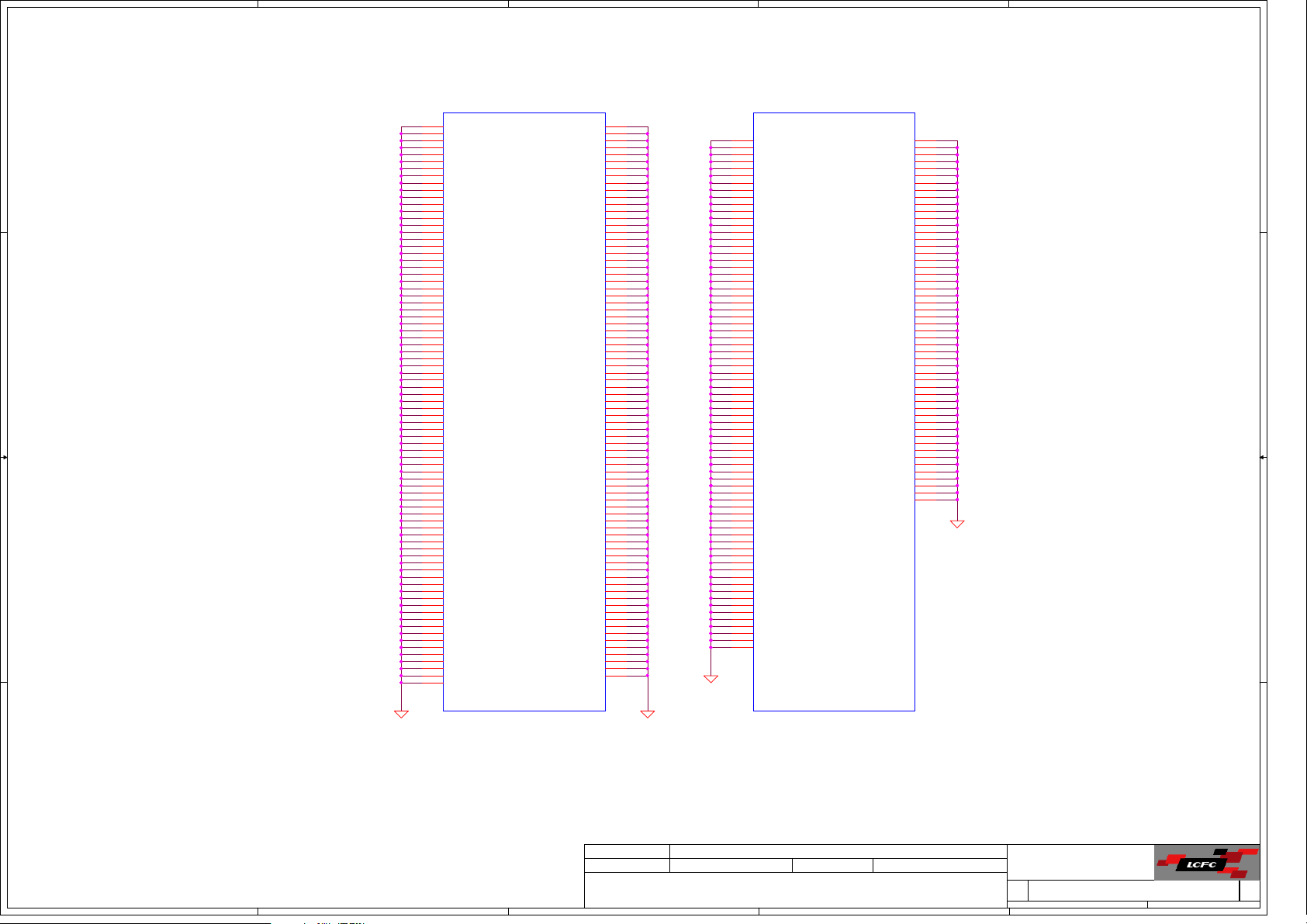

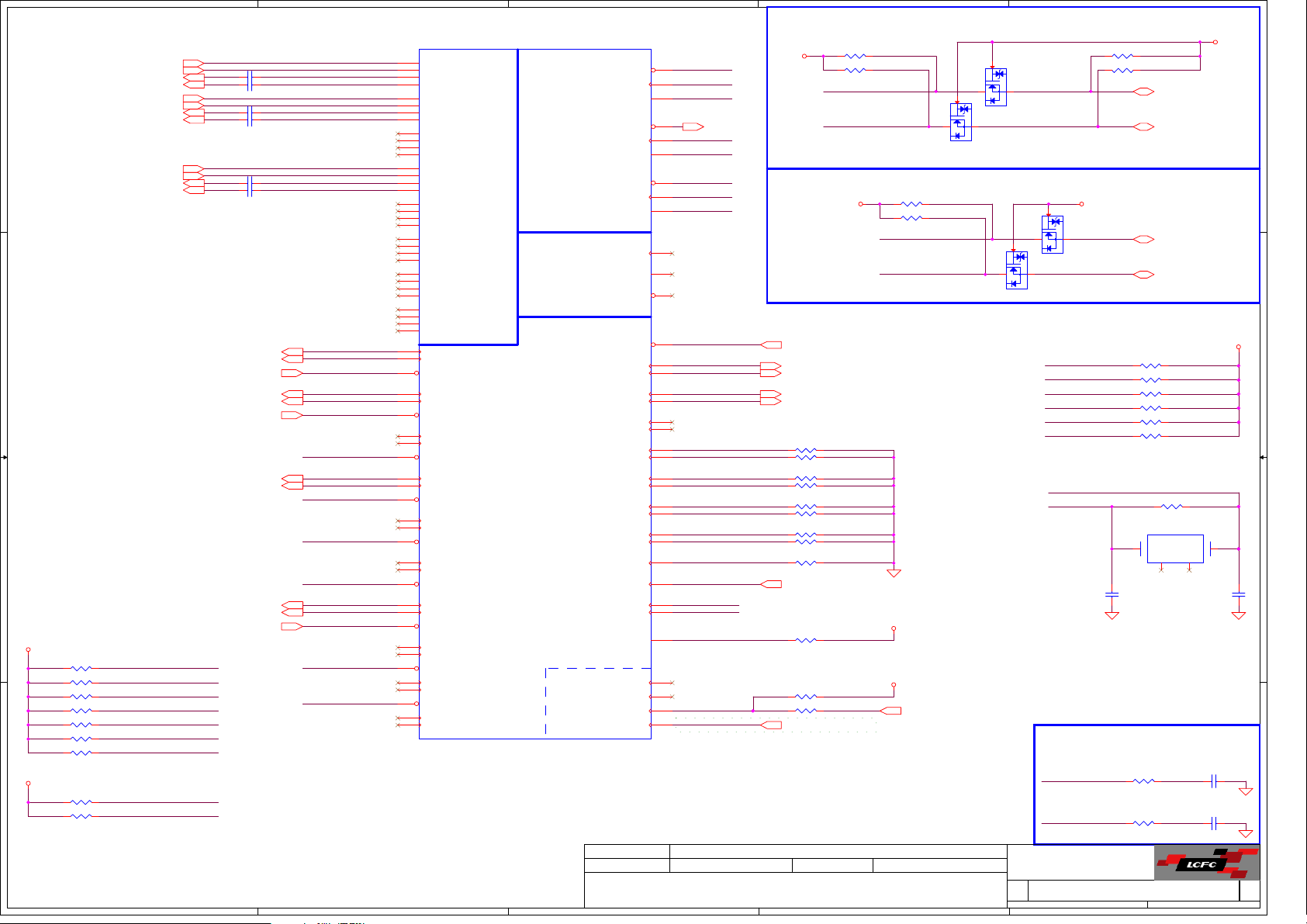

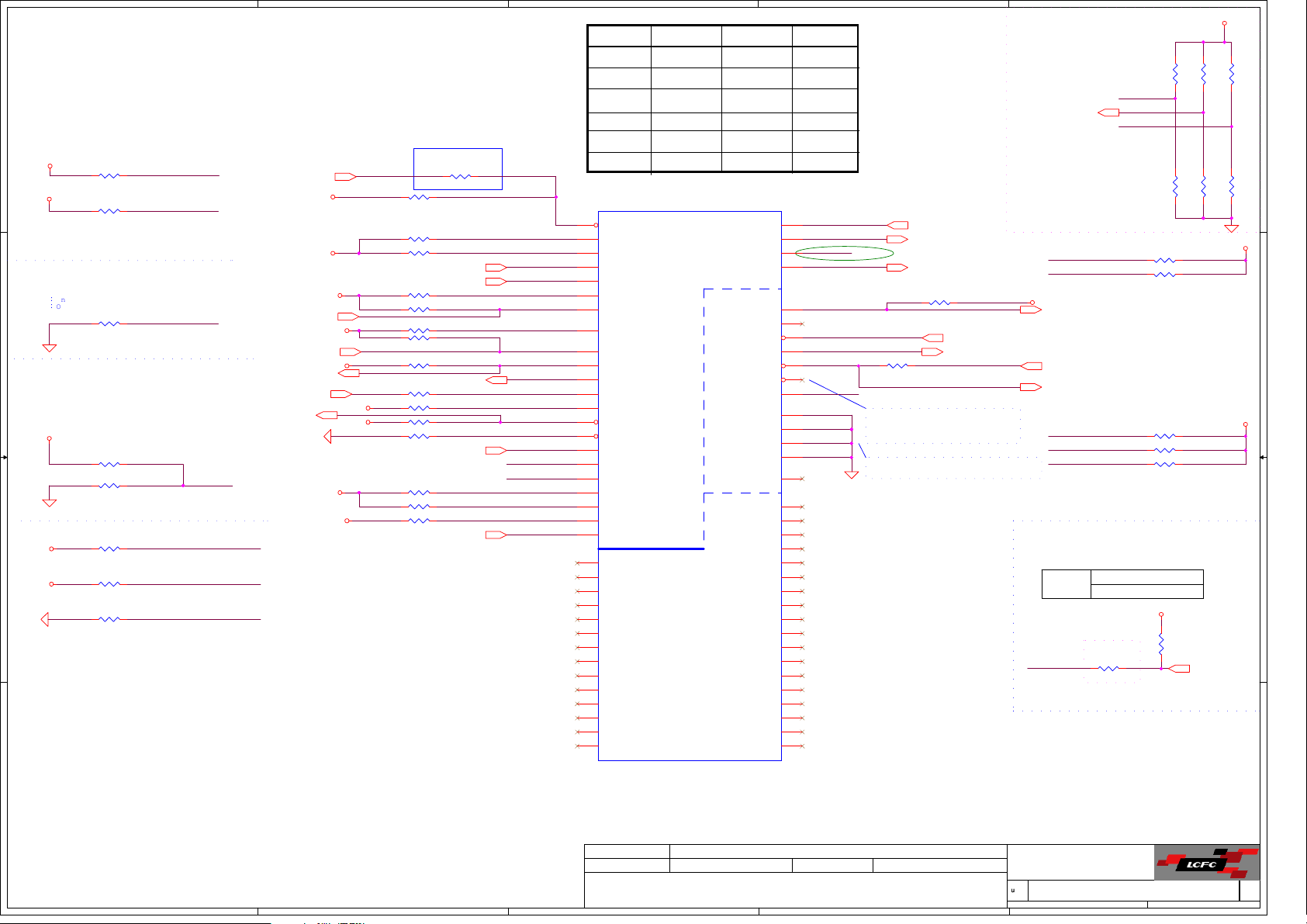

Page 3

A

B

C

D

E

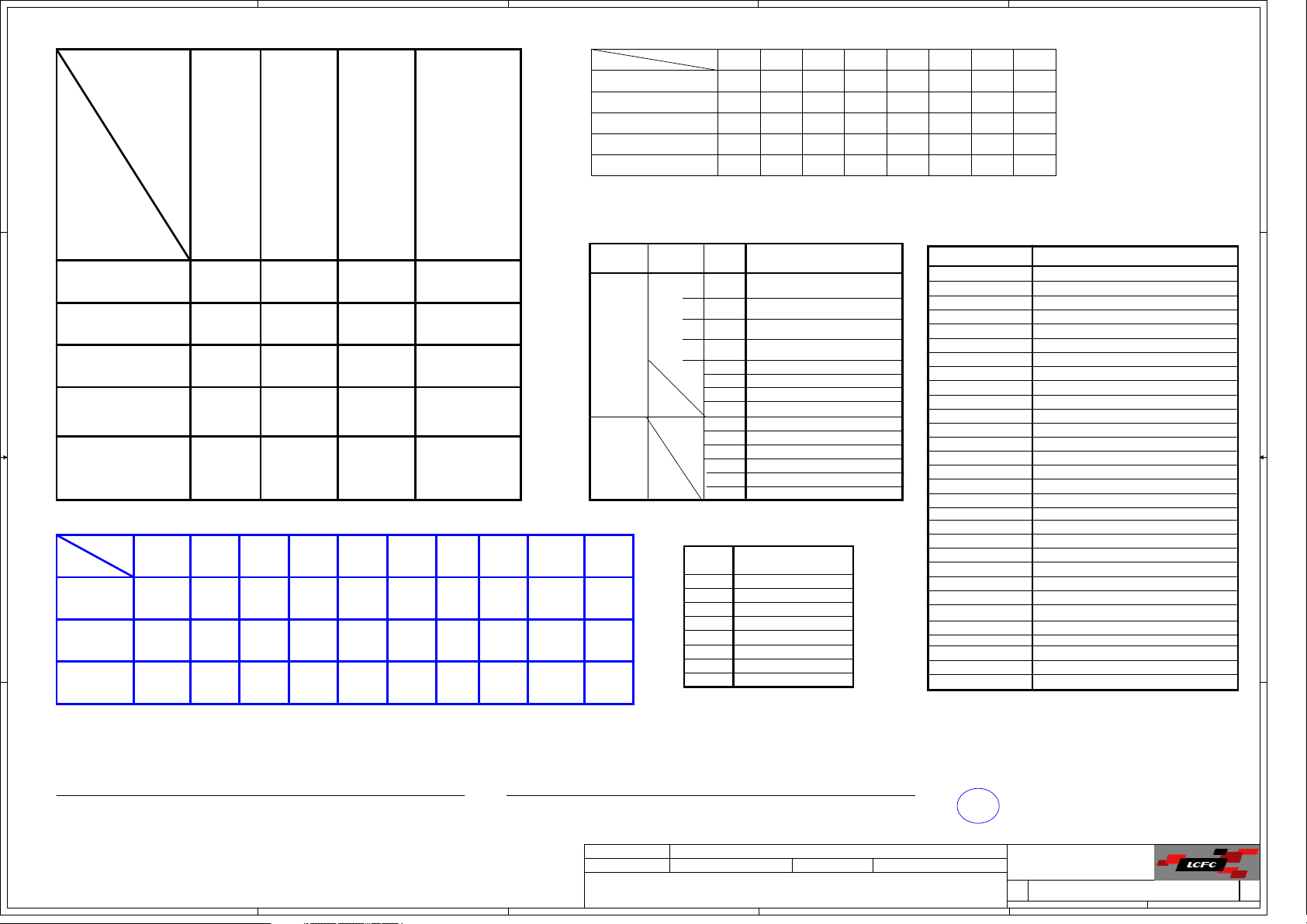

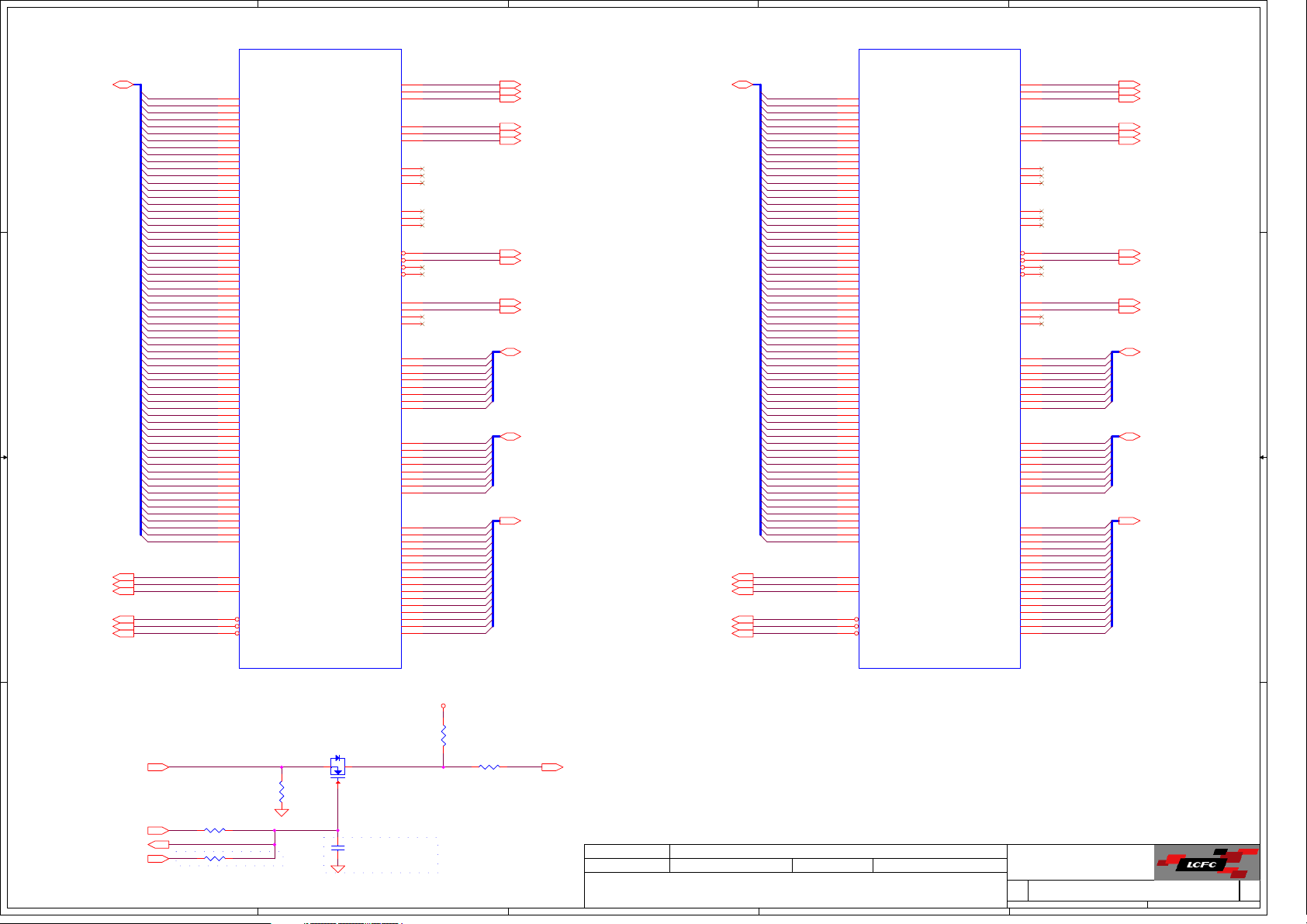

Voltage Rails

( O --> Means ON ,

Power Plane

1 1

B+

S

tate

S0

S

3

2 2

S5 S4/AC Only

S5 S4

Battery only

O

O

O

O

S5 S4

AC & Battery

don't exist

MBUS Control Table

S

SOURCE

3 3

IT

8580EEC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

C_SMB_DA2

E

SMB_CLK_S3

S

MB_DATA_S3

+3VALW

IT8580E

+3VS

PCH

+3VS

X X

Main

V

GA

X

V

+3VS +3VS

X X

X --> Means OFF )

+5VS

+3VS

+1.5VS

+VCCSA

+V1.5S_VCC P

+3VALW

+1.5V

+5VALW

+CPU_CORE

+VGA_CORE

GFX_CORE

+

+1.8VS

+1.05VS

+0.75VS

+3.3VS_VGA

+1.5VS_VGA

+1.05VS_VG A

O O O

OO

O

X

X X

X

2nd

VGA

BATT SODIMM

IT8580E

X X

+3VALW

V

X

X

X X X

X

X

V V

+3VS

WLAN

WiMAX

X

X

V

X

X

X

X

Thermal

Sensor

V

+3VS

PCH

XV

V

+3V_PCH

+3V_PCH+3VS

IGNAL

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

S

USB Port Table

USB 3.0USB 2.0 Port

XHCI

EHCI1

EHCI2

TP

Mo

dule

XX

X

V

+3VS

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

ON

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

0

1

1

2

2

3

3

4

4

5

6

USB Port (Left Side)

USB Port (Right Side)

7

8

9

USB Port (Right Side)

10

Mini Card(WLAN)

11

12

13

HIGH

LOWLOWLOW

4 External

USB Port

Camera

Blue Tooth

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

ON

ON

OFF

ON

OFF

BOM Structure Table

HDMI@

CHG@

NOCHG@

CMOS@

8161@

8151@

8161S@

8151S@

SURGE@

61@

51@

X76@

GC6@

NOGC6@

AOAC@

KBL@

ME@

OPT@

PCIE PORT LIST

Port Device

1

LAN

2

WLAN

3

4

Card Reader

SLI@

DS3@

S3@

GT@

@

5

6

7

8

ON ON

ON

OFF

OFF

OFF

LOW

OFF

OFF

OFF

BTO ItemBOM Structure

HDMI part

USB charger part

No USB charger part

CMOS Camera part

AR8161 LAN part

AR8151 LAN part

AR8161 LAN surge part

A

R8151 LAN surge part

AR8151&8161 LAN surge part --> Delete (201200627)

X76 P/N for AR8161

X76 P/N for AR8151

X76 Level part for VRAM

NV CG6 support part

NV no CG6 support part

AOAC support part

K/B Light part

ME part

For optimus function part

For SLI function part

Deep S3 support part

For S3 function part

NV chip part

Unpop

A

Address

0001 011X b

EC SM Bus2 address

Device

Thermal Sen sor EMC1403-2

Master VGA

Slave VGA

B

Address

1001_101xb

0x9E

0x9C

PCH SM Bus address

Device Address

DDR DIMM0

DDR DIMM2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

C

1001 000Xb

1001 010Xb

2011/11/01

2011/11/01

2011/11/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

2012/12/31

2012/12/31

2012/12/31

4 4

EC SM Bus1 address

Device

Smart Battery

ZZZ1

DAZ00200100

Title

Title

Title

NOTES LIST

NOTES LIST

NOTES LIST

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Tuesday, March 12, 2013

Tuesday, March 12, 2013

Tuesday, March 12, 2013

Y400S-NM-A141

Y400S-NM-A141

Y400S-NM-A141

E

of

of

of

3 65

3 65

3 65

1.0

1.0

1.0

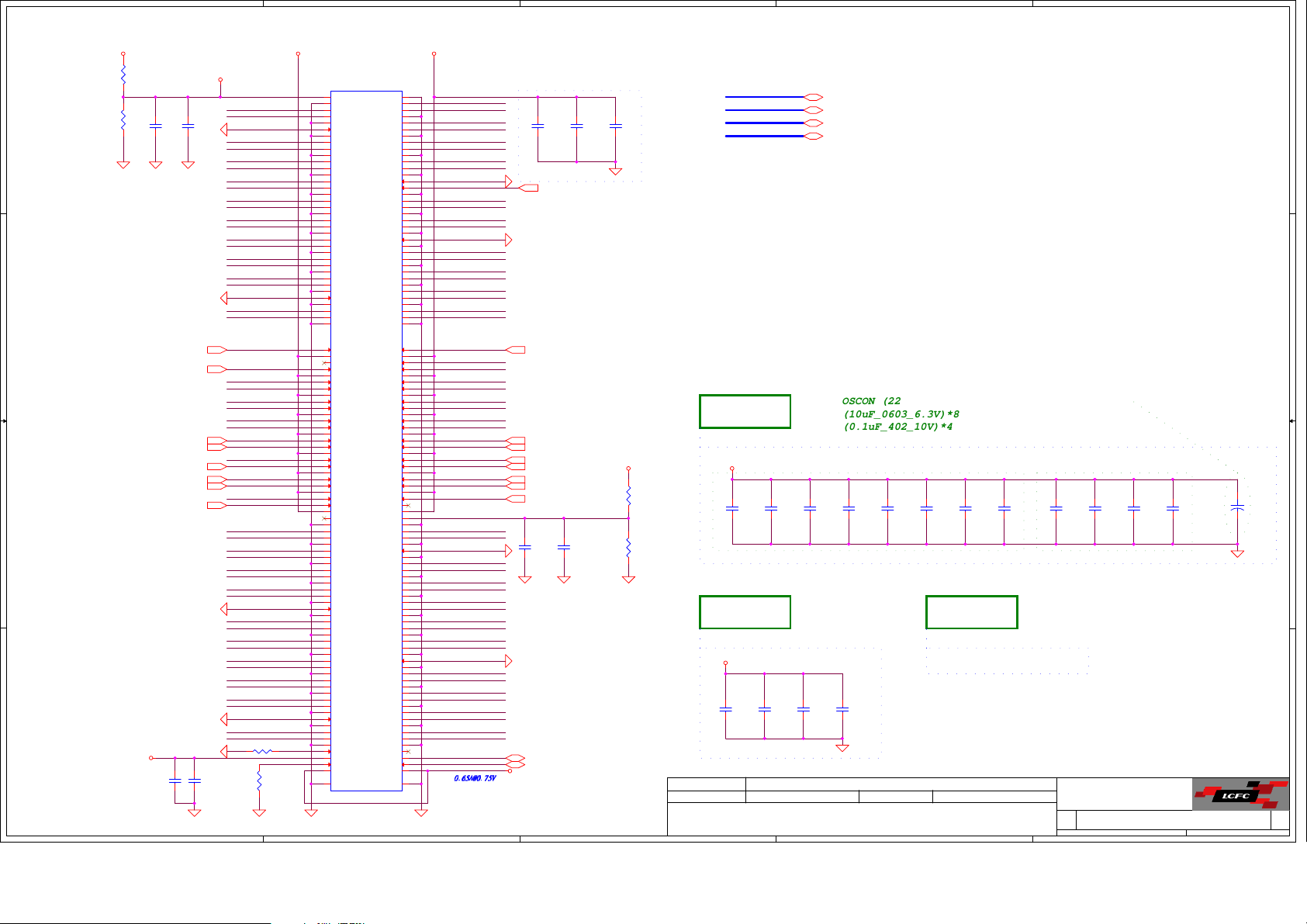

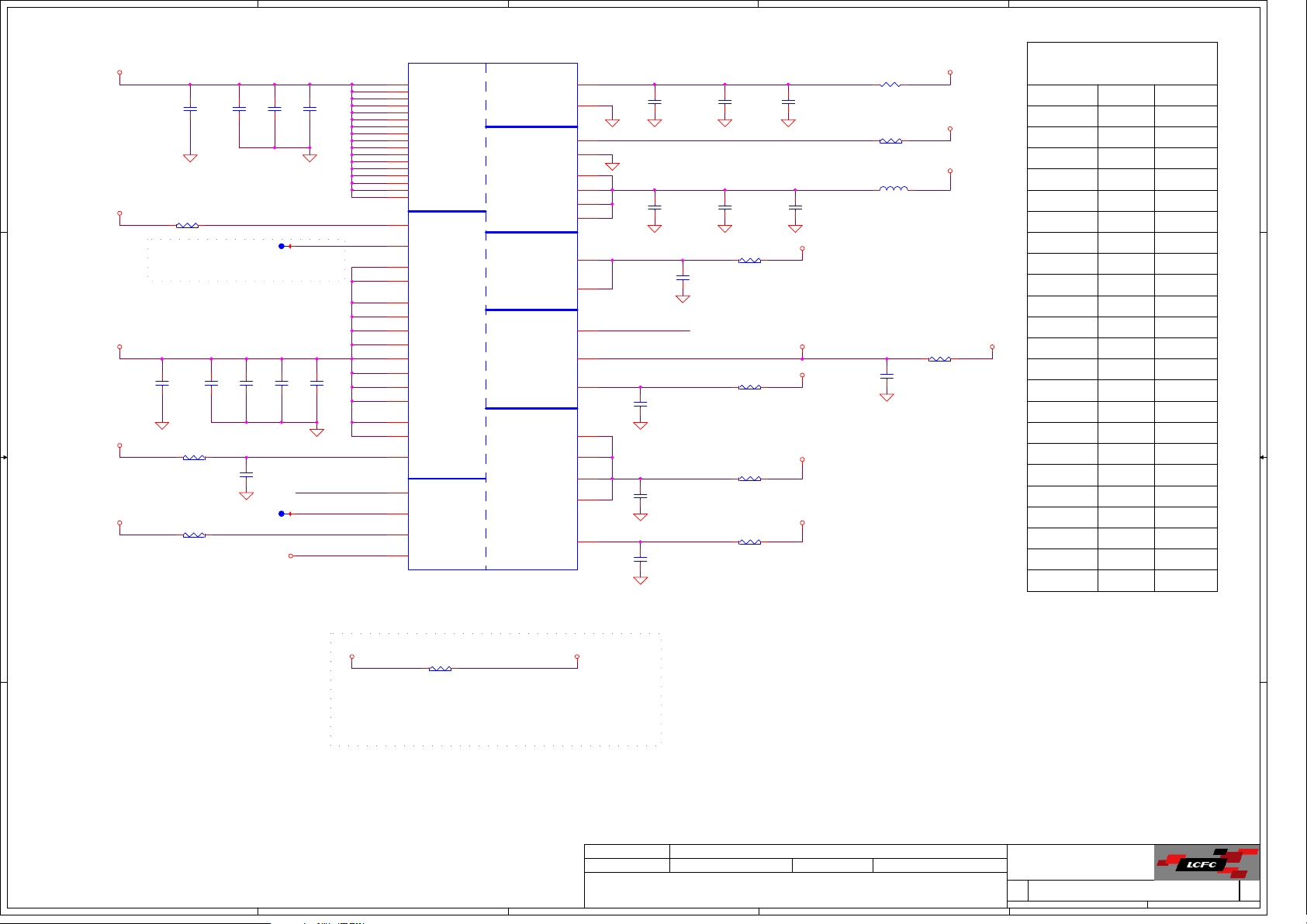

Page 4

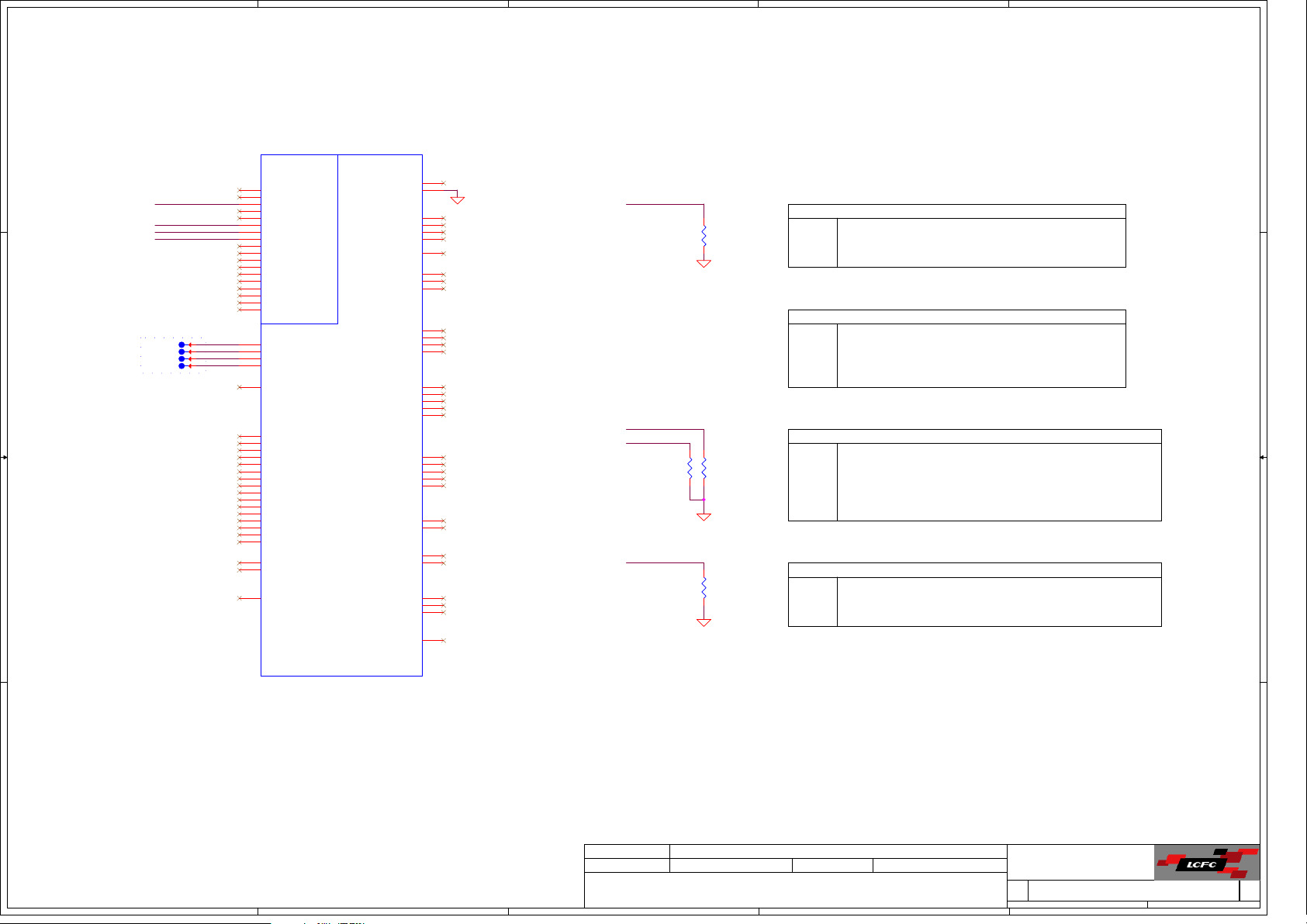

5

ot plug detect for IFP link E

H

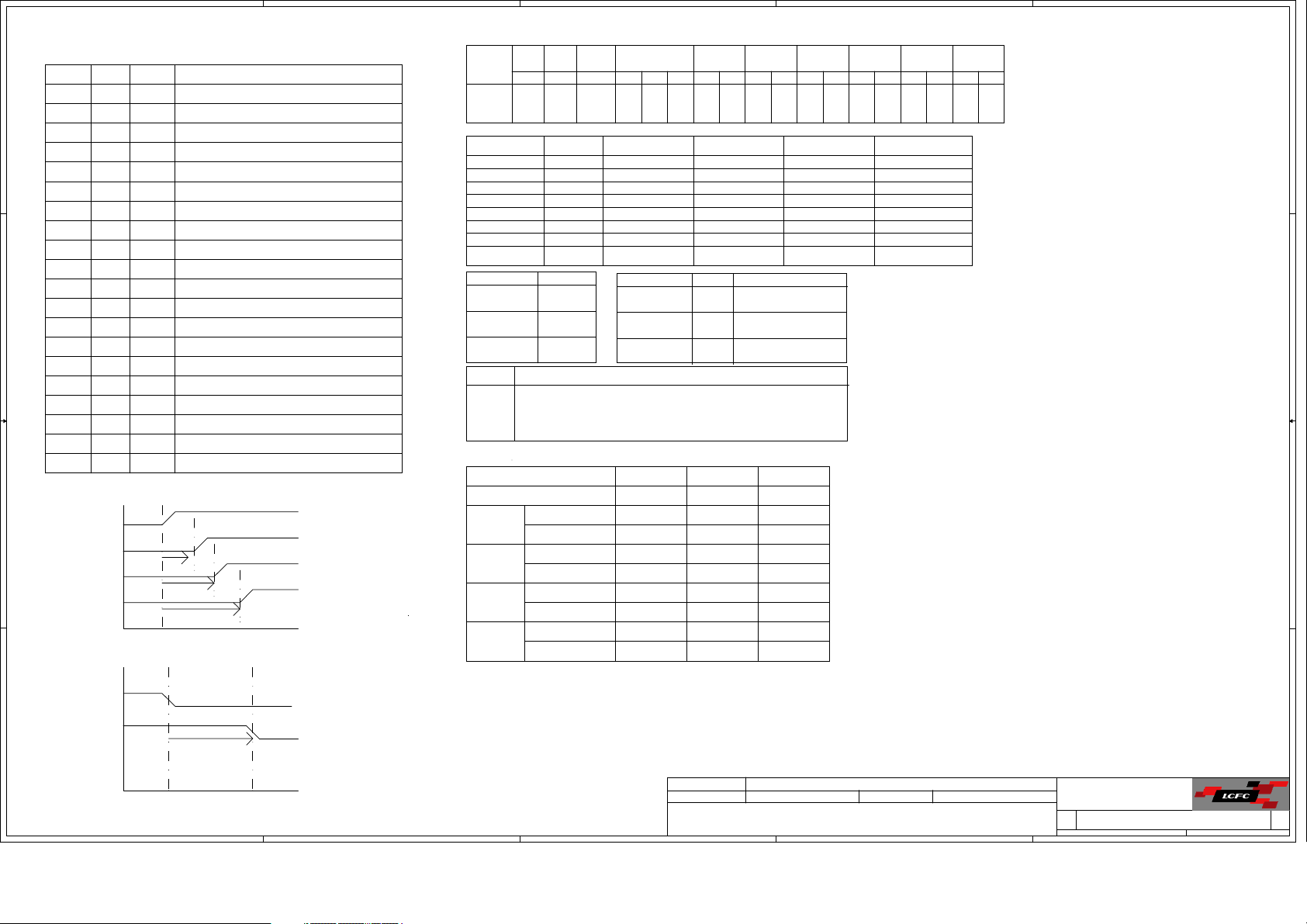

VGA and GDDR5 Voltage Rails (N13Px GPIO)

GPIO I/O ACTIVE Function Description

PIO0

+3VS_VGA

+VGA_CORE

+1.5VS_VGA

+1.05VS_VGA

OUT FB_CLAMP-

OUT

-

OUT

OUT

OUT

OUT

OUT

OUT

I/O

OUT

OUT

VGA_BL_PWM

-

VGA_ENVDD

-

- V

GA_ENBKL

-

FB_CLAMP_TOGGLE_REQ#

-

-

-

OVERT#

-

VGA_ALERT#

-

Memory VREF Control

NVVDD PWM_VID-OUT

-

N

N/A

-

/A

-

-

VGA_AC_DET_R

DPRSLPVR_VGA-

dGPU_HDMI_HPD

tNVVDD >0

tFBVDDQ >0

tPEX_VDD >0

IN

OUT

OUT

IN

OUT

IN

IN

IN

1. all power ra il ramp up tim e should be la rger than 40us

(10K pull High)

G

D D

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

C C

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

B B

4

3

2

1

Performance Mode P0 TDP at Tj = 102 C* (GDDR5)

GPU Mem NVCLK

(4) (1,5) (6)

Products

(W) (W) (MHz)

N13X

128bit

1GB

GDDR5

Physical

Strapping pin

ROM_SCLK

ROM_SI

ROM_SO FB[0]

STRAP0

STRAP1

STRAP2

STRAP3

STRAP4

/MCLK NVVDD

(V) (A) (W) (A) (W)

TBD TBDTBD TBD TBD TBD TBD TBD T BD TBD TBD TBD TBD TBD TBD TBD TBD TBD

Power Rail

+3VS_VGA

+3VS_VGA

+

3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

+3VS_VGA

Logical

Strapping Bit3

PCI_DEVID[4]

AM_CFG[3] RAM_C FG[2]

FB[1]

PCI_DEVID[3] PCI_DEVID[2] PCI_DEVID[1] PCI_DEVID[0]

SOR3_EXPOSED

RESERVED PCIE_SPEED_

Device ID

N13P-GT

(28nm)

0x0FDB

SMB_ALT_ADDR

(ROM_SO Bit 1)

FBVDD

Logical

Strapping Bit2

SUB_VENDOR

SER[2] USER[1] USER[0]USER[3]

U

3GIO_PAD_CFG_AD R[2] 3GIO_PAD_CFG_AD R[1]3GIO_PAD_CFG_AD R[3]

SOR2_EXPOSED SOR1_EXPOSED

CHANGE_GEN3

setting

0

1

ROM_SO

GPU

N13P-GT1

28nm

FB Memory (GDDR5)

Samsung

2500MHz

Hynix

2500MHz

Samsung

2500MHz

2500MHz

ROM_SCLK

PU 25K

PU 45KPU 10K PD 10K

PD 35K

PU 25K PD 35KPU 45KPU 20K PD 10K PD 5K PD 10K

GPU

N13P-GT

ROM_SI

K4G10325FG-HC04

32Mx32

PD 45K

H5GQ1H24BFR-T2C

32Mx32 PD 35K

K4G20325FD-FC04

64Mx32

PD 30K

H5GQ2H24MFR-T2CHynix

64Mx32

PD 25K

FBVDDQ PCI Express I/O and

(GPU+Mem)

(1.35V)(1.35V)

(A) (W) (W)(mA) (W) (W) (W)(mA) (mA) (mA)

(1.05V)

Logical

Strapping Bit1

SLOT_CLK_CFG

RAM_CFG[1]R

PCIE_MAX_SPEED DP_PLL_VDD33V

PLLVDD

I2C Slave addrees ID

0x9E

0x9C

STRAP2STRAP1STRAP0

STRAP3

STRAP4

PU 5K PD 10K

Master

Slave

I/O and

PLLVDD

Logical

Strapping Bit0

PEX_PLL_EN_TERM

R

AM_CFG[0]

VGA_DEVICESMB_ALT_ADDR

3GIO_PAD_CFG_AD R[0]

SOR0_EXPOSED

Other

(3.3V)(1.05V)(1.8V)

Other Power rail

A A

+3VS_VGA

power-off <10ms

T

1.all GPU power rails should be turned off within 10ms

. Optimus syste m VDD33 avoids drop down ear lier than NVDD and FBVDDQ

2

5

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTURE CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF LC FUTURE CENTER.

3

2011/11/01

2011/11/01

2011/11/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2012/12/31

2012/12/31

2012/12/31

Title

VGA NOTES LIST

VGA NOTES LIST

VGA NOTES LIST

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Y400S-NM-A141

Y400S-NM-A141

Y400S-NM-A141

Monday, January 14, 2013

Monday, January 14, 2013

Monday, January 14, 2013

4 65

4 65

1

4 65

1.0

1.0

1.0

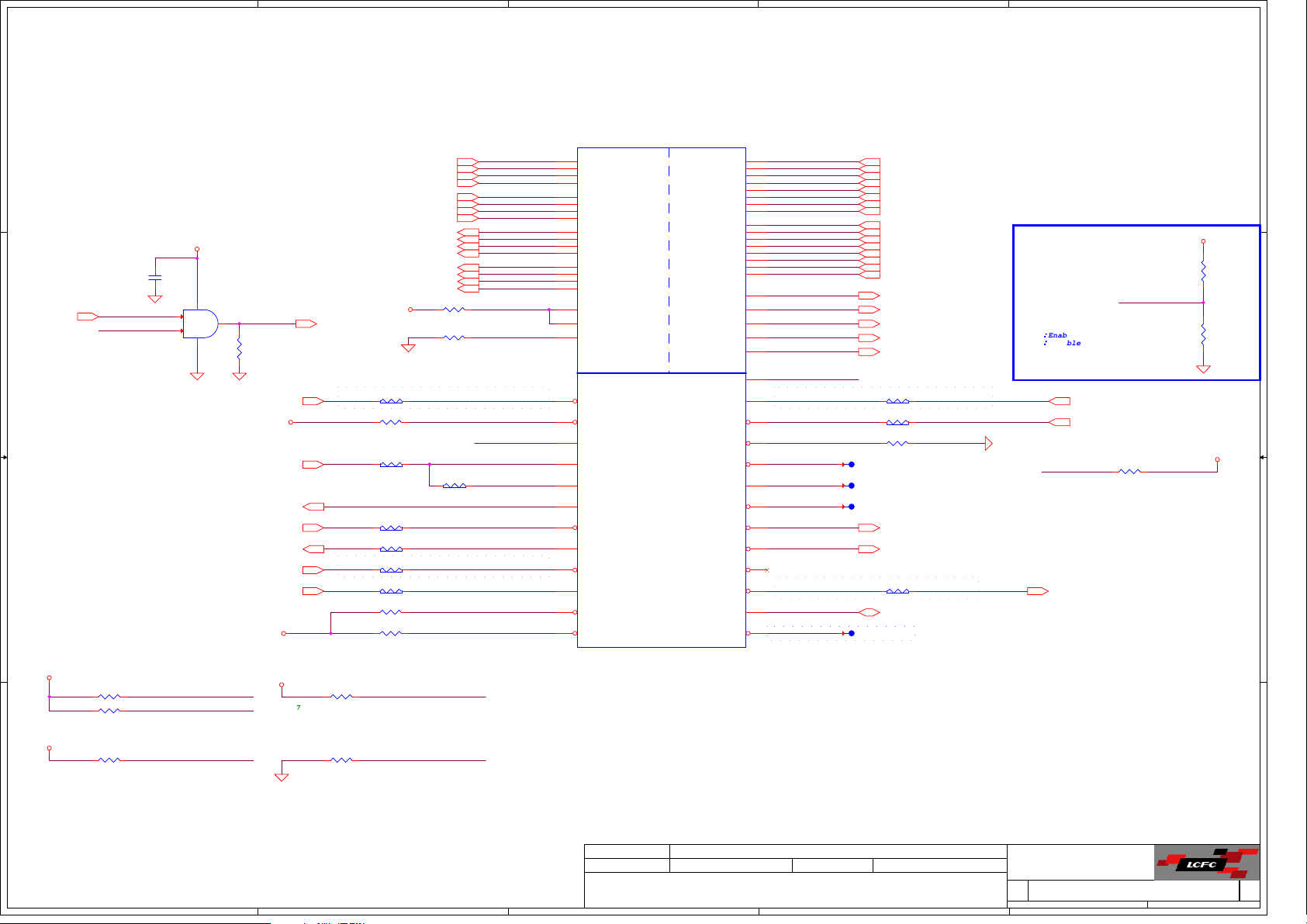

Page 5

5

D D

DMI_CRX_PTX_N0<16 >

DMI_CRX_PTX_N1<16 >

DMI_CRX_PTX_N2<16 >

DMI_CRX_PTX_N3<16 >

DMI_CRX_PTX_P0<16>

DMI_CRX_PTX_P1<16>

DMI_CRX_PTX_P2<16>

DMI_CRX_PTX_P3<16>

DMI_CTX_PRX_N0<16 >

DMI_CTX_PRX_N1<16 >

DMI_CTX_PRX_N2<16 >

DMI_CTX_PRX_N3<16 >

DMI_CTX_PRX_P0<16>

DMI_CTX_PRX_P1<16>

DMI_CTX_PRX_P2<16>

C C

B B

DMI_CTX_PRX_P3<16>

FDI_CTX_PRX_N0<16>

FDI_CTX_PRX_N1<16>

FDI_CTX_PRX_N2<16>

FDI_CTX_PRX_N3<16>

FDI_CTX_PRX_N4<16>

FDI_CTX_PRX_N5<16>

FDI_CTX_PRX_N6<16>

FDI_CTX_PRX_N7<16>

FDI_CTX_PRX_P0<16>

FDI_CTX_PRX_P1<16>

FDI_CTX_PRX_P2<16>

FDI_CTX_PRX_P3<16>

FDI_CTX_PRX_P4<16>

FDI_CTX_PRX_P5<16>

FDI_CTX_PRX_P6<16>

FDI_CTX_PRX_P7<16>

FDI_FSYNC0<16>

FDI_FSYNC1<16>

FDI_INT<16>

FDI_LSYNC0<16>

FDI_LSYNC1<16>

+1.05VS

eDP_COMPIO and ICOMPO signals

should be short ed near balls

and routed with typical

impedance <25 m ohms

R7

1 2

24.9_0402_1%

4

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

EDP_COMP

JCPU1A

ME@

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0]

H19

FDI0_TX#[1]

E19

FDI0_TX#[2]

F18

FDI0_TX#[3]

B21

FDI1_TX#[0]

C20

FDI1_TX#[1]

D18

FDI1_TX#[2]

E17

FDI1_TX#[3]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMPIO

A17

eDP_ICOMPO

B16

eDP_HPD#

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0]

E16

eDP_TX#[1]

D16

eDP_TX#[2]

F15

eDP_TX#[3]

TYCO_2013620-2_IVY BRIDGE

3

J22

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

DMI

Intel(R) FDI

eDP

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PCI EXPRESS* - GRAPHICS

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

J21

H22

K33

PCIE_CRX_GTX_N0

M35

PCIE_CRX_GTX_N1

L34

PCIE_CRX_GTX_N2

J35

PCIE_CRX_GTX_N3

J32

PCIE_CRX_GTX_N4

H34

PCIE_CRX_GTX_N5

H31

PCIE_CRX_GTX_N6

G33

PCIE_CRX_GTX_N7

G30

PCIE_CRX_GTX_N8

F35

PCIE_CRX_GTX_N9

E34

PCIE_CRX_GTX_N10

E32

PCIE_CRX_GTX_N11

D33

PCIE_CRX_GTX_N12

D31

PCIE_CRX_GTX_N13

B33

PCIE_CRX_GTX_N14

C32

PCIE_CRX_GTX_N15

J33

PCIE_CRX_GTX_P0

L35

PCIE_CRX_GTX_P1

K34

PCIE_CRX_GTX_P2

H35

PCIE_CRX_GTX_P3

H32

PCIE_CRX_GTX_P4

G34

PCIE_CRX_GTX_P5

G31

PCIE_CRX_GTX_P6

F33

PCIE_CRX_GTX_P7

F30

PCIE_CRX_GTX_P8

E35

PCIE_CRX_GTX_P9

E33

PCIE_CRX_GTX_P10

F32

PCIE_CRX_GTX_P11

D34

PCIE_CRX_GTX_P12

E31

PCIE_CRX_GTX_P13

C33

PCIE_CRX_GTX_P14

B32

PCIE_CRX_GTX_P15

M29

PCIE_CTX_GRX_C_N0

M32

PCIE_CTX_GRX_C_N1

M31

PCIE_CTX_GRX_C_N2

L32

PCIE_CTX_GRX_C_N3

L29

PCIE_CTX_GRX_C_N4

K31

PCIE_CTX_GRX_C_N5

K28

PCIE_CTX_GRX_C_N6

J30

PCIE_CTX_GRX_C_N7

J28

PCIE_CTX_GRX_C_N8

H29

PCIE_CTX_GRX_C_N9

G27

PCIE_CTX_GRX_C_N10

E29

PCIE_CTX_GRX_C_N11

F27

PCIE_CTX_GRX_C_N12

D28

PCIE_CTX_GRX_C_N13

F26

PCIE_CTX_GRX_C_N14

E25

PCIE_CTX_GRX_C_N15

M28

PCIE_CTX_GRX_C_P0

M33

PCIE_CTX_GRX_C_P1

M30

PCIE_CTX_GRX_C_P2

L31

PCIE_CTX_GRX_C_P3

L28

PCIE_CTX_GRX_C_P4

K30

PCIE_CTX_GRX_C_P5

K27

PCIE_CTX_GRX_C_P6

J29

PCIE_CTX_GRX_C_P7

J27

PCIE_CTX_GRX_C_P8

H28

PCIE_CTX_GRX_C_P9

G28

PCIE_CTX_GRX_C_P10

E28

PCIE_CTX_GRX_C_P11

F28

PCIE_CTX_GRX_C_P12

D27

PCIE_CTX_GRX_C_P13

E26

PCIE_CTX_GRX_C_P14

D25

PCIE_CTX_GRX_C_P15

PEG_COMP

+1.05VS

R1

12

24.9_0402_1%

PCIE_CRX_GTX_N[0..15] <23,32>

PCIE_CRX_GTX_P[0..15] <23,32>

C1 0.22U_0402_1 0V6K

C2 0.22U_0402_1 0V6K

C3 0.22U_0402_1 0V6K

C4 0.22U_0402_1 0V6K

C5 0.22U_0402_1 0V6K

C6 0.22U_0402_1 0V6K

C7 0.22U_0402_1 0V6K

C8 0.22U_0402_1 0V6K

C9 0.22U_0402_1 0V6KSLI@

C10 0.22U_0402_10V 6KSLI@

C11 0.22U_0402_10V 6KSLI@

C12 0.22U_0402_10V 6KSLI@

C13 0.22U_0402_10V 6KSLI@

C14 0.22U_0402_10V 6KSLI@

C15 0.22U_0402_10V 6KSLI@

C16 0.22U_0402_10V 6KSLI@

C20 0.22U_0402_10V 6K

C23 0.22U_0402_10V 6K

C25 0.22U_0402_10V 6K

C30 0.22U_0402_10V 6K

C18 0.22U_0402_10V 6K

C22 0.22U_0402_10V 6K

C28 0.22U_0402_10V 6K

C32 0.22U_0402_10V 6K

C19 0.22U_0402_10V 6KSLI@

C24 0.22U_0402_10V 6KSLI@

C29 0.22U_0402_10V 6KSLI@

C17 0.22U_0402_10V 6KSLI@

C21 0.22U_0402_10V 6KSLI@

C27 0.22U_0402_10V 6KSLI@

C26 0.22U_0402_10V 6KSLI@

C31 0.22U_0402_10V 6KSLI@

2

1. PEG_ICOMPI and RCOMPO signals should be shorted and routed with

a. max length = 500 mils

b. typical impedance = 43 mohms

2. PEG_ICOMPO signals should be routed with

a. max length = 500 mils

b. typical impedance = 14.5 mohms

PEG Static Lane Reversal - CFG2 is for the 16x

1: Normal Operation; Lane # definition matches

socket pin map definition

0

:Lane Reversed

*

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

CFG2

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_N8

PCIE_CTX_GRX_N9

PCIE_CTX_GRX_N10

PCIE_CTX_GRX_N11

PCIE_CTX_GRX_N12

PCIE_CTX_GRX_N13

PCIE_CTX_GRX_N14

PCIE_CTX_GRX_N15

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_P3

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_P8

PCIE_CTX_GRX_P9

PCIE_CTX_GRX_P10

PCIE_CTX_GRX_P11

PCIE_CTX_GRX_P12

PCIE_CTX_GRX_P13

PCIE_CTX_GRX_P14

PCIE_CTX_GRX_P15

1

PCIE_CTX_GRX_N[0..15] < 23,32>

PCIE_CTX_GRX_P[0..15] <23,32>

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUT URE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUT URE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUT URE CENTER.

3

2011/11/01

2011/11/01

2011/11/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2012/12/31

2012/12/31

2012/12/31

Title

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

PROCESSOR(1/7) DMI,FDI,PEG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Monday, January 14, 2013

Monday, January 14, 2013

Monday, January 14, 2013

Y400S-NM-A141

Y400S-NM-A141

Y400S-NM-A141

1

of

of

of

5 65

5 65

5 65

1.0

1.0

1.0

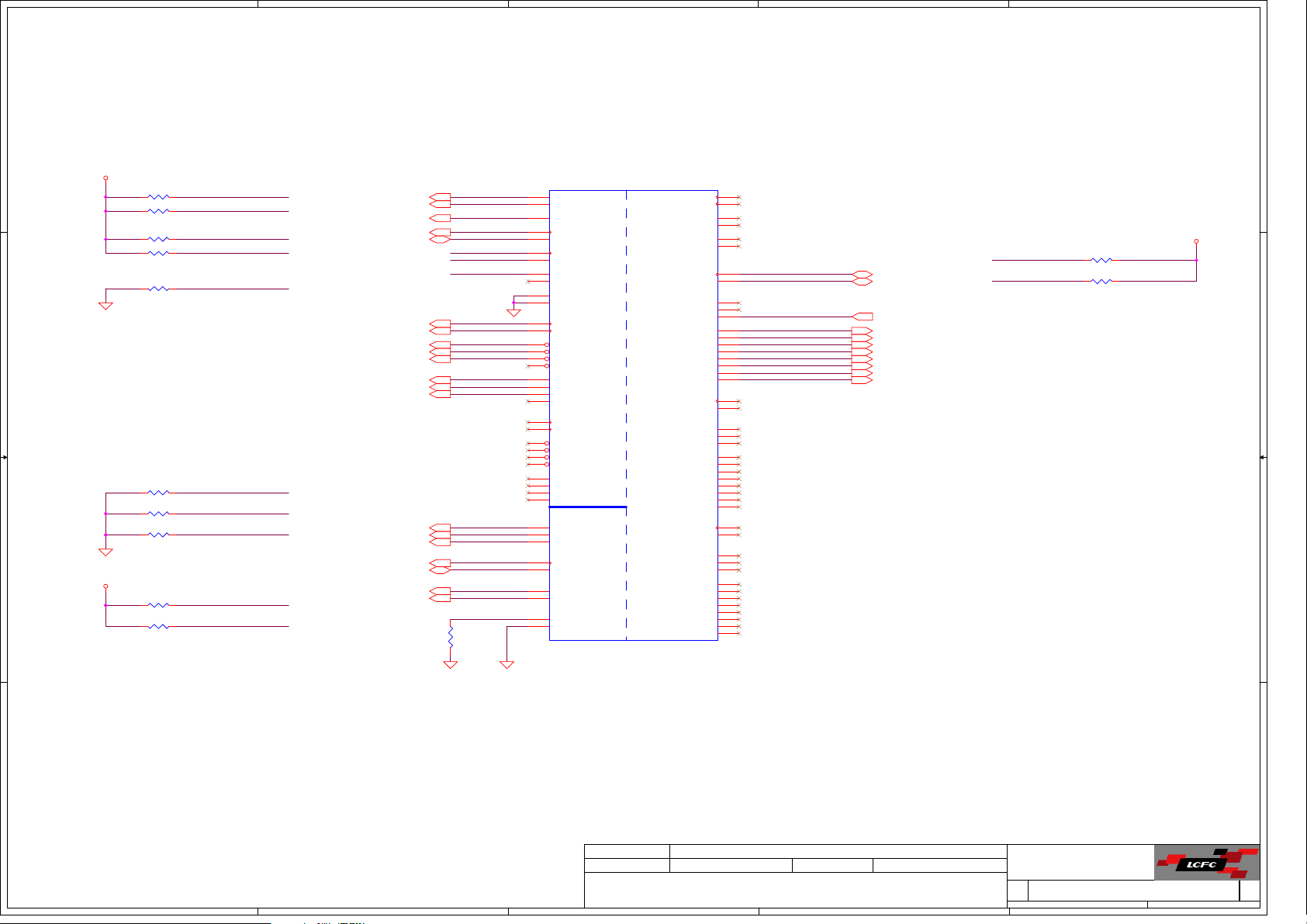

Page 6

5

D D

ROC_SEL

H : Sandy Bridg e

P

L : IVY Bridge

+1.05VS

R9

1 2

62_0402_5%

C C

H_CPUPWRGD<19>

C550

100P_0402_50V8J

9/23 ESD Reques t

1

2

R27

10K_0402_5%

1 2

H_PROCHOT#<45,53>

H_PM_SYNC<16>

4

H_SNB_IVB#<19>

T14 PAD

H_PECI<45>

H_PROCHOT#H_PROCHOT#

H_THRMTRIP#<19>

H_PM_SYNC

H_CPUPWRGD

R15

1 2

56_0402_5%

R22

1 2

R_short 0_0402_5%

R26

1 2

R_short 0_0402_5%

R29

1 2

130_0402_5%

H_SNB_IVB#

H_CATERR#

H_PROCHOT#_R

H_THRMTRIP#

H_PM_SYNC_R

H_CPUPWRGD_R

PM_DRAM_PWR GD_RPM_SYS_PWRGD_BUF

BUF_CPU_RST#

H_PECI

JCPU1B

C26

AN34

AL33

AN33

AL32

AN32

AM34

AP33

V8

AR33

3

ME@

PROC_SELECT#

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

PM_SYNC

UNCOREPWRGOOD

SM_DRAMPWR OK

RESET#

BCLK

BCLK#

MISCTHERMALPWR MANAGEMENT

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

JTAG & BPM

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

2

A28

CLK_CPU_DMI

A27

CLK_CPU_DMI#

A16

A15

R8

AK1

A5

A4

H_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

R12 1K_0402_5%

R13 1K_0402_5%

R16 140_0402_1%

R17 25.5_0402_1%

R18 200_0402_1%

DDR3 Compensation Signals

AP29

AP27

AR26

AR27

AP30

AR28

AP26

AL35

AT28

AR29

AR30

AT30

AP32

AR31

AT31

AR32

XDP_TCK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TDI

XDP_TDO

XDP_TCK

XDP_TRST#

PU/PD for JTAG signals

CLK_CPU_DMI <15>

CLK_CPU_DMI# <15>

12

12

H_DRAMRST# <7>

12

12

12

R20 51_0402_5%

R21 51_0402_5%

R23 51_0402_5%

R24 51_0402_5%

R25 51_0402_5%

+1.05VS

12

12

12

@

12

12

1

+1.05VS

TYCO_2013620-2_IVY BRIDGE

B B

Buffered Reset to CPU

+3VS

1

5

P

B

O

A

G

U1

74AHC1G09GW_TSSOP5

3

4

C33

0.1U_0402_16V4Z

2

4

R338

10K_0402_5%

1 2

1 2

SYS_PWROK<16>

PM_DRAM_PWR GD<16>

A A

5

R65 0_0402_5%@

1

2

+1.5V_CPU_VDDQ+3VALW

12

R30

200_0402_5%

PM_SYS_PWRGD_BUF

1.05V

12

R35

@

0_0402_5%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

3

2011/11/01

2011/11/01

2011/11/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

+1.05VS +3VS

12

R32

75_0402_5%

R34

1 2

43_0402_1%

BUFO_CPU_RST#BUF_CPU_RS T#

Deciphered Date

Deciphered Date

Deciphered Date

0.1U_0402_16V4Z

2

C34

4

2012/12/31

2012/12/31

2012/12/31

1

2

5

P

NC

Y

A

G

3

1

is is NC pin

Th

2

PLT_RST#

U2

SN74LVC1G07DCKR_SC70-5

Title

Title

Title

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

PROCESSOR(2/7) PM,XDP,CLK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

3V

PLT_RST# <18,23,32,37,38,44,45>

Y400S-NM-A141

Y400S-NM-A141

Monday, January 14, 2013

Monday, January 14, 2013

Monday, January 14, 2013

Y400S-NM-A141

1

of

of

of

6 65

6 65

6 65

1.0

1.0

1.0

Page 7

5

JCPU1C

ME@

4

3

JCPU1D

2

ME@

1

DDR_A_D[0..63]<12>

D D

C C

B B

DDR_A_BS0<12>

DDR_A_BS1<12>

DDR_A_BS2<12>

DDR_A_CAS#<12>

DDR_A_RAS#<12>

DDR_A_WE#<12>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

G10

N10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AK8

AK9

AH8

AH9

AL9

AL8

AE8

AD9

AF9

F10

AJ5

AJ6

AJ8

AJ9

C5

D5

D3

D2

D6

C6

C2

C3

F8

G9

F9

F7

G8

G7

K4

K5

K1

J1

J5

J4

J2

K2

M8

N8

N7

M9

N9

M7

V6

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CK[1]

SA_CLK#[1]

SA_CKE[1]

SA_CK[2]

SA_CLK#[2]

SA_CKE[2]

SA_CK[3]

SA_CLK#[3]

SA_CKE[3]

SA_CS#[0]

SA_CS#[1]

SA_CS#[2]

SA_CS#[3]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

M_CLK_DDR0 <12>

M_CLK_DDR#0 <12>

DDR_CKE0_DIMMA <12>

M_CLK_DDR1 <12>

M_CLK_DDR#1 <12>

DDR_CKE1_DIMMA <12>

DDR_CS0_DIMMA# <12>

DDR_CS1_DIMMA# <12>

M_ODT0 <12>

M_ODT1 <12>

DDR_A_DQS#[0..7] <12>

DDR_A_DQS[0..7] <12>

DDR_A_MA[0..15] <12> DDR_B_MA[0..15] <13>

DDR_B_D[0..63]<13>

DDR_B_BS0<13>

DDR_B_BS1<13>

DDR_B_BS2<13>

DDR_B_CAS#<13>

DDR_B_RAS#<13>

DDR_B_WE#<13>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

D10

K10

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA9

AA7

AA10

AB8

AB9

J10

C9

A7

C8

A9

A8

D9

D8

G4

F4

F1

G1

G5

F5

F2

G2

J7

J8

K9

J9

K8

K7

M5

N4

N2

N1

M4

N5

M2

M1

R6

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY B

SB_CK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CK[2]

SB_CLK#[2]

SB_CKE[2]

SB_CK[3]

SB_CLK#[3]

SB_CKE[3]

SB_CS#[0]

SB_CS#[1]

SB_CS#[2]

SB_CS#[3]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AE2

AD2

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

M_CLK_DDR2 <13>

M_CLK_DDR#2 <13>

DDR_CKE2_DIMMB <13>

M_CLK_DDR3 <13>

M_CLK_DDR#3 <13>

DDR_CKE3_DIMMB <13>

DDR_CS2_DIMMB# <13>

DDR_CS3_DIMMB# <13>

M_ODT2 <13>

M_ODT3 <13>

DDR_B_DQS#[0..7] <13>

DDR_B_DQS[0..7] <13>

TYCO_2013620-2_IVY BRIDGE

+1.5V

12

R37

1K_0402_5%

D

S

13

H_DRAMRST#<6>

R39

A A

DRAMRST_CNTRL_PC H<15>

DRAMRST_CNTRL<1 0>

DRAMRST_CNTRL_EC<45>

Reserve for Dee p S3

5

4.99K_0402_1%

1 2

@

R40 0_0402_5%

1 2

DS3@

R64 0_0402_5%

1 2

DRAMRST_CNTRL

DDR3_DRAMRST#_RH_DRAMRST#

Q2

G

BSS138_NL_SOT23-3

2

1

C35

0.047U_0402_16V4Z

2

Module design u sed 0.047u

4

R38

1 2

1K_0402_5%

DDR3_DRAMRST# <12,13>

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

3

2011/11/01

2011/11/01

2011/11/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

TYCO_2013620-2_IVY BRIDGE

2012/12/31

2012/12/31

2012/12/31

2

Title

Title

Title

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

PROCESSOR(3/7) DDRIII

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Monday, January 14, 2013

Monday, January 14, 2013

Monday, January 14, 2013

Y400S-NM-A141

Y400S-NM-A141

Y400S-NM-A141

1

of

of

of

7 65

7 65

7 65

1.0

1.0

1.0

Page 8

5

D D

JCPU1E

ME@

AK28

CFG[0]

AK29

CFG[1]

CFG2

CFG5

CFG6

CFG7

C C

11/24 --> Intel recommend

t

o reserve test point

B B

T56 PAD

T57 PAD

T58 PAD

T59 PAD

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

J15

RSVD27

CFG

4

VCC_DIE_SENSE

VSS

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

RSVD40

RSVD_NCTF1

RSVD_NCTF2

RSVD_NCTF3

RSVD_NCTF4

RSVD_NCTF5

RSVD_NCTF6

RSVD_NCTF7

RESERVED

RSVD_NCTF8

RSVD_NCTF9

RSVD_NCTF10

RSVD51

RSVD52

BCLK_ITP

BCLK_ITP#

RSVD_NCTF11

RSVD_NCTF12

RSVD_NCTF13

KEY

AH27

AH26

L7

AG7

AE7

AK2

W8

AT26

AM33

AJ27

T8

J16

H16

G16

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AN35

AM35

AT2

AT1

AR1

B1

3

CFG Straps for Processor

CFG2

CFG6

CFG5

1K_0402_1%

CFG7

12

R41

@

1K_0402_1%

12

12

R44

R43

@

1K_0402_1%

12

R45

@

1K_0402_1%

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

Display Port Presence Strap

CFG4

PCIE Port Bifurcation Straps

CFG[6:5]

PEG DEFER TRAINING

CFG7

2

1: Normal Operation; Lane # definition matches

*

socket pin map definition

0:Lane Reversed

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

*

0 : Enabled; An external Display Port device is

c

onnected to the Embedded Display Port

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

*

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

: (Default) PEG Train immediately following xxRESETB

1

de assertion

0: PEG Wait for BIOS for training

1

TYCO_2013620-2_IVY BRIDGE

A A

Title

Title

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

3

2011/11/01

2011/11/01

2011/11/01

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2012/12/31

2012/12/31

2012/12/31

Title

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

PROCESSOR(4/7) RSVD,CFG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Monday, January 14, 2013

Monday, January 14, 2013

Monday, January 14, 2013

Y400S-NM-A141

Y400S-NM-A141

Y400S-NM-A141

1

of

of

of

8 65

8 65

8 65

1.0

1.0

1.0

Page 9

5

4

3

2

1

JCPU1F

+VCC_CORE

D D

C C

B B

A A

5

C=94A

Q

DC=53A

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

TYCO_2013620-2_IVY BRIDGE

POWER

ME@

CORE SUPPLY

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

PEG AND DDR

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES SVID

4

+1.05VS

8.5A

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

Reserve 0.1u to avoid noise

AJ29

AJ30

AJ28

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

1 2

R47 43_0402_5%

1 2

R48 R_short 0_0402_5%

1 2

R49 R_short 0_0402_5%

R50 130_0402_5%

12

Place the PU re sistor close t o CPU

AJ35

VCCSENSE_R VCCSENSE

AJ34

VSSSENSE_R

B10

VCCIO_SENSE

A10

VSSIO_SENSE

1 2

R52 R_short 0_0402_5%

1 2

R53 R_short 0_0402_5%

R1294 10_0402_1%

R1297 10_0402_1%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

3

+1.05VS

12

12

0.1U_0402_10V7K

+1.05VS

2011/11/01

2011/11/01

2011/11/01

+1.05VS

1

C36

@

2

+VCC_CORE

VSSSENSE

VCCIO_SENSE <57>

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

12

R46

75_0402_5%

Place the PU re sistor close t o CPU

VR_SVID_ALRT# <59>

VR_SVID_CLK <59>

VR_SVID_DAT <59>

12

R51

100_0402_1%

V

CC_SENCE 100ohm +-1% pull-up to VCC near pr ocessor

VCCSENSE <59>

12

R54

100_0402_1%

VSSSENSE <59>

VSS_SENCE 100oh m +-1% pull-do wn to GND near processor

2012/12/31

2012/12/31

2012/12/31

2

Title

Title

Title

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

PROCESSOR(5/7) PWR,BYPASS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Monday, January 14, 2013

Monday, January 14, 2013

Monday, January 14, 2013

Y400S-NM-A141

Y400S-NM-A141

Y400S-NM-A141

1

of

of

of

9 65

9 65

9 65

1.0

1.0

1.0

Page 10

5

4

3

2

1

+1.5V_CPU_VDDQ

For Deep S3

D D

R1538

SUSP<37,51,55,57>

CPU1.5V_S3_GATE<45>

C C

B B

1 2

R_short 0_0402_5%

0_0402_5%

+3VALW

12

R1537

100K_0402_5%

+VCC_GFXCORE_AXG

@

13

D

2

G

S

4

RV174

SLI@

1 2

@

Q156

2N7002_SOT23

6A

+VSB

12

R56 need to che ck on SDV

R56

100K_0402_5%

61

D

2

G

S

Q4A

2N7002KDWH_SOT363-6

JCPU1G

AT24

VAXG1

AT23

VAXG2

AT21

VAXG3

AT20

VAXG4

AT18

VAXG5

AT17

VAXG6

AR24

VAXG7

AR23

VAXG8

AR21

VAXG9

AR20

VAXG10

AR18

VAXG11

AR17

VAXG12

AP24

VAXG13

AP23

VAXG14

AP21

VAXG15

AP20

VAXG16

AP18

VAXG17

AP17

VAXG18

AN24

VAXG19

AN23

VAXG20

AN21

VAXG21

AN20

VAXG22

AN18

VAXG23

AN17

VAXG24

AM24

VAXG25

AM23

VAXG26

AM21

VAXG27

AM20

VAXG28

AM18

VAXG29

AM17

VAXG30

AL24

VAXG31

AL23

VAXG32

AL21

VAXG33

AL20

VAXG34

AL18

VAXG35

AL17

VAXG36

AK24

VAXG37

AK23

VAXG38

AK21

VAXG39

AK20

VAXG40

AK18

VAXG41

AK17

VAXG42

AJ24

VAXG43

AJ23

VAXG44

AJ21

VAXG45

AJ20

VAXG46

AJ18

VAXG47

AJ17

VAXG48

AH24

VAXG49

AH23

VAXG50

AH21

VAXG51

AH20

VAXG52

AH18

VAXG53

AH17

VAXG54

RUN_ON_CPU1.5VS3

POWER

GRAPHICS

+1.5V

1 2

470K_0402_5%

12

R57

470K_0402_5%

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREFMISC

DDR3 -1.5V RAILS

1 2

C287 0.1U_0402_10V 6K

1 2

C286 0.1U_0402_10V 6K

1 2

C96 0.1U_0402_10V 6K

1 2

C95 0.1U_0402_10V 6K

U3

8

7

6

5

AO4304L_SO8

R1349

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

4

A

Vgs=10V,Id=18A,

Rds<6.7m ohm

P/N: SB00000RV0 0

1

C97

0.01U 50V K X7R 0603

2

AK35

VCC_AXG_SENSE_R

AK34

VSS_AXG_SENSE_R

AL1

+V_SM_VREF_CNT

B4

+V_DDR_REFA_R

D1

+V_DDR_REFB_R

5A

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

6A

M27

M26

L26

J26

J25

J24

H26

H25

O4304L

1

2

3

+1.5V_CPU_VDDQ

12

R1487

@

470_0603_5%

34

D

S

Q4B

2N7002KDWH_SOT363-6

1 2

R1488 0_0402_5%OPT@

1 2

R1489 0_0402_5%

10U_0603_6.3V6M

10U_0603_6.3V6M

C118

C117

1

1

2

+VCCSA

10U_0805_6.3V6M

1

2

1

2

2

10U_0805_6.3V6M

C124

C125

1

1

2

2

5

G

OPT@

1

C114

0.1U_0402_16V4Z

2

10U_0603_6.3V6M

10U_0603_6.3V6M

C119

1

2

10U_0805_6.3V6M

C126

1

@

2

SUSP

C120

10U_0805_6.3V6M

DRAMRST_CNTRL<7>

+VREF_DQ_DIMMA

+VREF_DQ_DIMMB

6/8: Add M3 Circuit (Processor Generated SO-DIMM VREF

VCC_AXG_SENSE

VSS_AXG_SENSE

VCC_AXG_SENSE <59>

VSS_AXG_SENSE <59>

+1.5V_CPU_VDDQ

10U_0603_6.3V6M

10U_0603_6.3V6M

C122

C121

1

1

2

2

C127

+VCCSA

@

1

+

@

2

330U_D2_2.5VY_R9M

C128

1

+

2

R66 100_0402_1%

R90 100_0402_1%

330U_D2_2.5VY_R9M

C123

DRAMRST_CNTRL

DRAMRST_CNTRL

OPT@

12

OPT@

12

+1.5V_CPU_VDDQ

12

R77

1K_0402_1%

12

R88

1K_0402_1%

2

G

Q8 BSS138_SOT23

1 3

D

S

1 2

R74 0_0402_5%@

1 2

R75 0_0402_5%@

1 3

D

Q7 BSS138_SOT23

2

S

G

R139

1K_0402_1%

@

12

+V_DDR_REFA_R

+V_DDR_REFB_R

12

R132

@

1K_0402_1%

_DQ)

+VCC_GFXCORE_AXG

Place the PU/PD resi stor clos e to CPU w ithin 2 i nch

(R

eserve pow er side)

SA RAIL

VCCIO_SEL

H23

C22

C24

A19

+1.8VS

R67

1 2

A A

R_short 0_0805_5%

10U_0805_6.3V6M

1

+

C130

C279

@

2

330U_B2_2.5VM_R15M

1

1

C131

2

2

1U_0402_6.3V6K

1U_0402_6.3V6K

C132

+1.8VS_VCCPLL

1

2

11/24 change 22 U X2 to 330U B 2 size

5

B6

VCCPLL1

A6

VCCPLL2

A2

VCCPLL3

TYCO_2013620-2_IVY BRIDGE

ME@

4

1.8V RAIL

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

+VCCSA_SENSE <56>

H_VCCSA_VID0 <56>

H_VCCSA_VID1 <56>

6/3 modify for VCCSA 4-Level voltage

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF LC FUTUR E CENTER. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY LC FUTURE CENTER NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF LC FUTURE CENTER.

3

+VCCSA_SENSE

2011/11/01

2011/11/01

2011/11/01

1 2

R68 0_0402_5%@

LC Future Center Secret Data

LC Future Center Secret Data

LC Future Center Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

2012/12/31

2012/12/31

2012/12/31

Title

Title

Title

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

PROCESSOR(6/7) PWR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Monday, January 14, 2013

Monday, January 14, 2013

Monday, January 14, 2013

Y400S-NM-A141

Y400S-NM-A141

Y400S-NM-A141

1

of

of

of

10 65

10 65

10 65

1.0

1.0

1.0

Page 11

5

4

3

2

1

D D

C C

B B

AT35

AT32

AT29

AT27

AT25

AT22

AT19

AT16

AT13

AT10

AR25

AR22

AR19

AR16

AR13

AR10

AR7

AR4

AR2

AP34

AP31

AP28

AP25

AP22

AP19

AP16

AP13

AP10

AP7

AP4

AP1

AN30

AN27

AN25

AN22

AN19

AN16

AN13

AN10

AN7

AN4

AM29

AM25

AM22

AM19

AM16

AM13

AM10

AM7

AM4

AM3

AM2

AM1

AL34

AL31

AL28

AL25

AL22

AL19

AL16

AL13

AL10

AK33

AK30

AK27

AK25

AK22

AK19

AK16

AK13

AK10

AK7

AK4

AJ25

JCPU1H

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

AT7

VSS11

AT4

VSS12

AT3

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

AL7

VSS66

AL4

VSS67

AL2

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

M34

H33

H30

H27

H24

H21

H18

H15

H13

H10

G35

G32

G29

G26

G23

G20

G17

G11

JCPU1I

T35

VSS161

T34

VSS162

T33

VSS163

T32

VSS164

T31

VSS165

T30

VSS166

T29

VSS167

T28

VSS168

T27

VSS169

T26

VSS170

P9

VSS171

P8

VSS172

P6

VSS173

P5

VSS174

P3

VSS175

P2

VSS176

N35

VSS177

N34

VSS178

N33

VSS179

N32

VSS180

N31

VSS181

N30

VSS182

N29

VSS183

N28

VSS184

N27

VSS185

N26

VSS186

VSS187

L33

VSS188

L30

VSS189

L27

VSS190

L9

VSS191

L8

VSS192

L6

VSS193

L5

VSS194

L4

VSS195

L3

VSS196

L2

VSS197

L1

VSS198

K35

VSS199

K32

VSS200

K29

VSS201

K26

VSS202

J34

VSS203

J31

VSS204

VSS205

VSS206

VSS207